# RZ FAMILY MICROPROCESSORS

64-Bit & 32-Bit High-performance MPUs

2024.05

## THE NEXT-GENERATION PROCESSOR TO MEET THE NEEDS OF THE SMART SOCIETY HAS ARRIVED.

## **CONTENTS**

| RZ FAMILY PORTFOLIO | _ 04 |

|---------------------|------|

| RZ/V SERIES         | _ 06 |

| RZ/N SERIES         | 12   |

| RZ/T SERIES         | _ 20 |

| RZ/G SERIES         | _ 30 |

| RZ/A SERIES         | _ 40 |

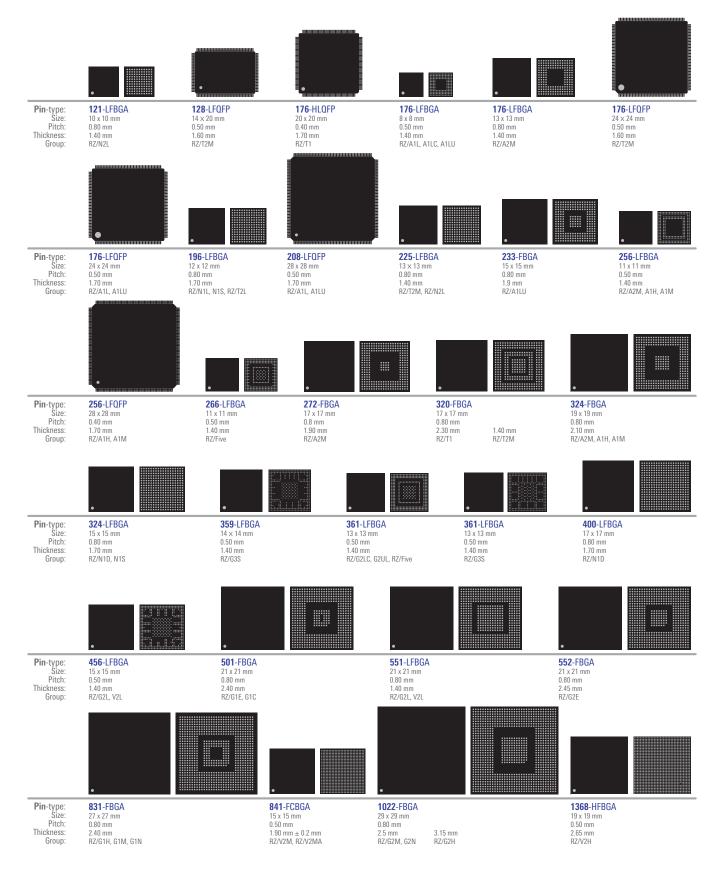

| PACKAGE LINEUP      | _ 46 |

|                     |      |

The utilization of intelligent technology is advancing in all aspects of our lives, including electric household appliances, industrial equipment, building management, power grids, and transportation. The cloud-connected "smart society" is coming ever closer to realization. Microcontrollers are now expected to provide powerful capabilities not available previously, such as high-performance and energy-efficient control combined with interoperation with IT networks, support for human-machine interfaces, and more. To meet the demands of this new age, Renesas has drawn on its unmatched expertise in microcontrollers to create the RZ family of embedded processors. The lineup of these "next-generation processors that are as easy to use as conventional microcontrollers" to meet different customer requirements.

## The Zenith of the Renesas micro

As embedded processors to help build the next generation of advanced products, the RZ family offers features not available elsewhere and brings new value to customer applications.

## Positioning of the RZ Family

| Microcon                       | trollers & Microprocessors, System-on-Chips (SoCs)                                                                                                                  | Analog and Pov                                                                                                                     | ver Devices                                                                                    |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| RENESAS<br>RZ<br>RENESAS<br>RA | High-end 32/64-bit MPUs<br>High-resolution HMI, Industrial network & real-time control<br>Advanced 32-bit MCUs<br>Arm ecosystem, Advanced security, Intelligent IoT | <ul> <li>Analog products</li> <li>Clocks &amp; Timing</li> <li>Interface &amp; Connectivity</li> <li>Memory &amp; Logic</li> </ul> | <ul> <li>RF products</li> <li>Sensor products</li> <li>Space &amp; Harsh environmen</li> </ul> |

| RX                             | High Power Efficiently 32-bit MCUs<br>Motor control, Capacitive touch, Functional safety, GUI                                                                       | <ul><li>Power &amp; Power management</li><li>Programmable Mixed-signal,</li></ul>                                                  |                                                                                                |

| RISC-V<br>products             | General-purpose 64-bit MPUs (RZ/Five Group)<br>Application-specific 32-bit MCUs                                                                                     | ASIC, & IP products                                                                                                                |                                                                                                |

| RENESAS<br>RL78                | Ultra-low Energy 8/16-bit MCUs<br>Bluetooth® Low Energy, SubGHz, LoRa®-based Solutions<br>Automotive actuators & sensors, Low-end ECUs                              | Timing                                                                                                                             | <ul> <li>Power Management</li> </ul>                                                           |

| RENESAS<br>RH850               | Automotive 32-bit MCUs<br>Rich functional safety and embedded security features                                                                                     | <ul><li>Wireless Power</li><li>Battery Management</li></ul>                                                                        | <ul><li>Sensors</li><li>Video &amp; Display</li></ul>                                          |

| RENESAS<br>R-Car               | Automotive SoCs<br>Next generation of automotive computing                                                                                                          | <ul> <li>Power Devices</li> </ul>                                                                                                  |                                                                                                |

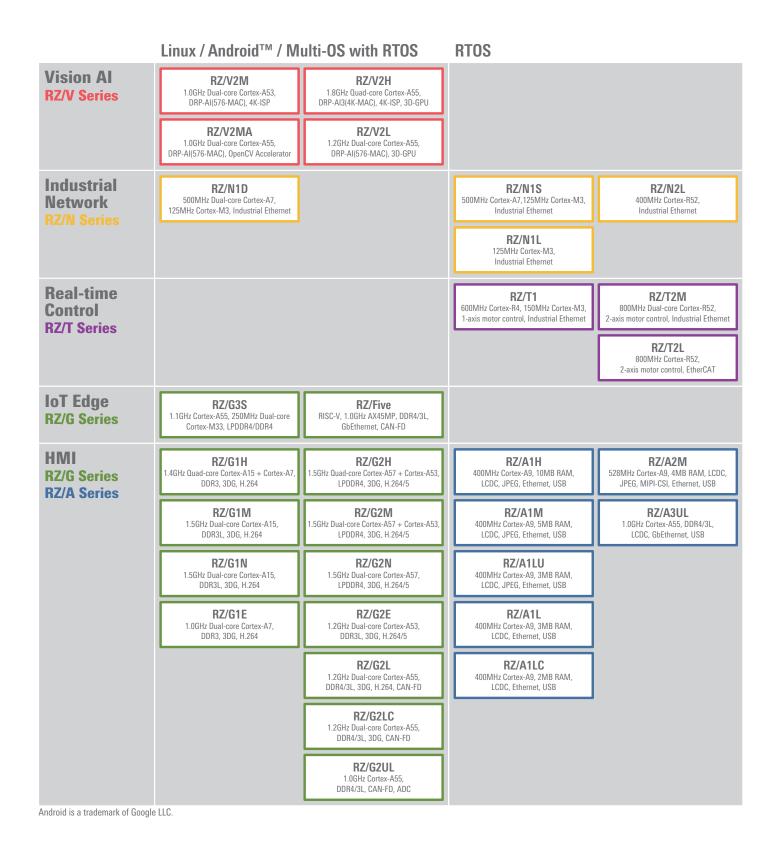

## **RZ Family Portfolio**

## **RZ/V Series**

64-bit Cortex<sup>®</sup>-A CPU, Up to 1.8GHz Low-power Embedded AI for Vision-AI Application

## **RZ/N Series**

32-bit Cortex<sup>®</sup>-A/M/R CPU, Up to 500MHz Multi-protocol Industrial Network and TSN for PLC, Remote IO, Gateway

## **RZ/T Series**

32-bit Cortex<sup>®</sup>-R CPU, Up to 800MHz Real-time Control Multi-protocol Industrial Network and TSN, Multi-protocol Encoder I/F for AC servo, Actuator, Inverter

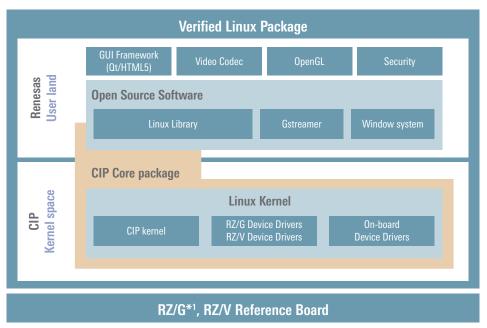

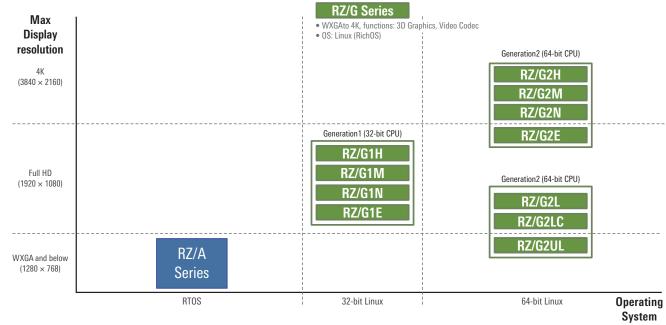

## **RZ/G Series**

32/64-bit Cortex<sup>®</sup>-A CPU, Up to 1.5Hz 64-bit RISC-V CPU, Up to 1.0GHz for HMI and IoT Application

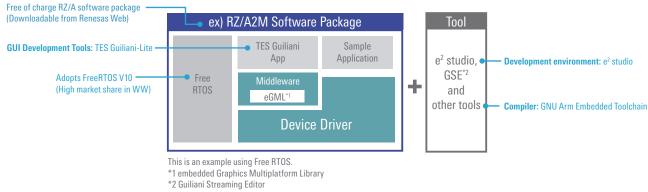

## **RZ/A Series**

32/64-bit Cortex<sup>®</sup>-A CPU, Up to 1GHz - DDR3L/4 (RZ/A3UL) - Up to 10MB Embedded RAM for HMI Application

Arm® and Cortex® are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere.

## **RZ/V Series**

## **RZ/V Series Features**

- Al performance scalability to cover wide range of applications

- Integrates Renesas original AI accelerator DRP-AI to deliver up to 80TOPS

- Realize best AI power efficiency up to 10TOPS/W

- Integrated ISP (upto 4k) and Video Codec

- Provides Vision Processing Accelerator (OpenCV) as DRP library

- Equipped with a 3D Graphics Engine for fast image rendering

- \* DRP: Dynamically Reconfigurable Processor

## **RZ/V Series Application**

Service Robot

AGV/AMR

AI Camera

Retail

Agriculture

Smart Home

Healthcare

Industrial

Smart Building

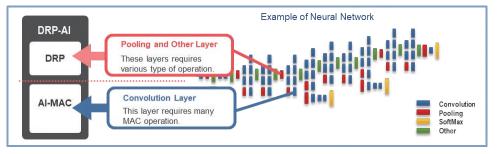

### **Features of DRP-AI**

DRP-AI consists of AI-MAC (multiply-accumulate processor) and DRP (reconfigurable processor). AI processing can be executed at high speed by assigning AI-MAC for operations on the convolution layer and fully connected layer, and DRP for other complex processing such as preprocessing and pooling layer.

For more detailed technical information on DRP-AI, please refer to the following white paper. White Paper: Embedded AI-Accelerator DRP-AI

Next Generation Highly Power-Efficient AI Accelerator (DRP-AI3): 10x Faster Embedded Processing in Advanced AI for Autonomous Systems 🗹

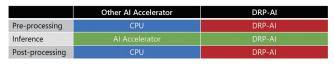

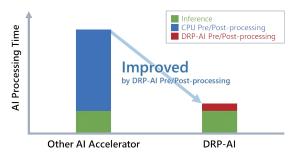

While most AI accelerators specialize only in AI inference and rely on the CPU for pre- and post-processing, DRP-AI integrates pre- and post-processing and AI inference into a single DRP-AI hardware to achieve superior AI processing performance.

## **RZ/V Series Specification**

| Items                                  | NEW RZ/V2H                                     | RZ/V2MA                                       | RZ/V2M                                        | RZ/V2L                                                                                       |

|----------------------------------------|------------------------------------------------|-----------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------|

| Main CPU                               | Cortex®-A55 × 4<br>Cortex®-R8 × 2              | Cortex®-A53 × 2                               | Cortex <sup>®</sup> -A53 × 2                  | Cortex®-A55 × 2                                                                              |

| Sub CPU                                | Cortex®-M33                                    | -                                             | -                                             | Cortex®-M33                                                                                  |

| AI Accelerator Performance<br>(DRP-AI) | 10 TOPS/W<br>Max. 80 TOPS<br>Resnet50: 830 fps | 1 TOPS/W<br>Max. 1 TOPS<br>Resnet50: 28 fps   | 1 TOPS/W<br>Max. 1 TOPS<br>Resnet50: 28 fps   | 1 TOPS/W<br>Max. 0.5 TOPS<br>Resnet50: 17 fps                                                |

| ISP for Camera                         | 4K ISP (option)<br>(hardware)                  | -                                             | 4K ISP<br>(hardware)                          | Simple ISP<br>(software)                                                                     |

| MIPI-CS2 I/F                           | 4-lane × 4ch                                   | -                                             | 4-lane × 1ch                                  | 4-lane × 1ch                                                                                 |

| Computer Vision Accelerator            | OpenCV Accelerator                             | OpenCV Accelerator                            | -                                             | OpenCV Accelerator                                                                           |

| Video Codec                            | H.265, H.264                                   | H.265, H.264                                  | H.265, H.264                                  | H.264                                                                                        |

| Graphics                               | 3D Graphics (option)                           | -                                             | 2D Graphics                                   | 3D Graphics                                                                                  |

| Package                                | 1368pin FHBGA, 19mm × 19mm<br>0.5mm ball pitch | 841pin FCBGA, 15mm × 15mm<br>0.5mm ball pitch | 841pin FCBGA, 15mm × 15mm<br>0.5mm ball pitch | 551pin PBGA, 21mm × 21mm<br>0.8mm ball pitch<br>456pin PBGA, 15mm × 15mm<br>0.5mm ball pitch |

## **RZ/V2M Group**

#### CPU

2× Cortex-A53 (up to 1.0GHz)

Vision and AI

- AI Accelerator; DRP-AI at 1.0 TOPS/W class

- Image Signal Processor (ISP) of multi-stream available

- Camera Interface; 2× MIPI CSI-2

- Face and Human Detection Engine

- Video and Graphics

- H.265/H.264 Multi Codec

- JPEG Codec Engine

- 2D Graphics Engine

- **Display Interface**

- MIPI-DSI (4-lane)

- HDMI 1.4a

- Audio Interface

- Serial Sound Interface × 1ch

- **Communication Interface**

- SD Host × 2ch

- PCI-Express 2.0 (2-lane) × 1ch

- Gigabit Ethernet × 1ch

- USB3.1 Gen1 Host/Function × 1ch

- $I^2C$  Bus  $\times$  4ch

- SCI × 6ch

- UART × 2ch

- Memory Interface

- NAND Flash Interface ONFI1.0 × 1ch

- eMMC 4.5.1 × 1ch

- 32-bit LPDDR4-3200 × 1ch

Security

Hardware Security Engine

## **RZ/V2L Group**

#### CPU

- 2× Cortex-A55 or 1× Cortex-A55 (up to 1.2GHz)

- 1× Cortex-M33 (up to 200MHz)

- Vision and AI

- Al Accelerator; DRP-Al

- \* Image Signal Processor (Simple ISP) Function is provided as DRP Library Camera Interface; 1× MIPI CSI-2 / 1× Digital Parallel

- Video and Graphics

- H.264 Codec

- 3D Graphics Engine

- Display Interface

- MIPI-DSI (4-lane)

- Digital Parallel

- Audio Interface

- Serial Sound Interface × 4ch

- **Communication Interface**

- Gigabit Ethernet × 2ch

- USB2.0 Host × 1ch

- USB2.0 Host/Function × 1ch

- $I^2C$  Bus  $\times$  4ch

- SCI × 2ch

- UART × 5ch

- Memory Interface SPI Multi I/O (8bit DDR) × 1ch

- SDHI (UHS-I) / eMMC × 1ch

- 16-bit DDR3L-1333/DDR4-1600 × 1ch

- Security

- Hardware Security Engine (Option)

#### RZ/V2M block diagram

| System                           | Cł                                              | งป                                              | Peripheral I/F          |

|----------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------|

| Arm Debugger (CoreSight™)        | Arm <sup>®</sup> Cortex <sup>®</sup> -A53: 1GHz | Arm <sup>®</sup> Cortex <sup>®</sup> -A53: 1GHz | SDI (2ch)               |

| DMAC (16ch)                      | L1 I\$: 32KB L1 D\$: 32KB                       | L1 I\$: 32KB L1 D\$: 32KB                       | USB3.1 (1ch)            |

| Power control                    | NEON FPU                                        | NEON FPU                                        | (Host/Peripheral)       |

| Timers                           | L2\$: 5                                         | 512KB                                           | PCIe Gen2 (2Lane)       |

|                                  | 84                                              |                                                 | Gbit Ethernet MAC (1ch) |

| Timer (32ch)                     | RAMA 200KB                                      | RAMB 1MB                                        | I2C (4ch)               |

| PWM (16ch)                       |                                                 |                                                 | CSI (6ch)               |

| WDT (2ch)                        | Sensing an                                      | d Analyzing                                     | UART (2ch)              |

| Image Sensor I/F                 | Al-accelera                                     | tor (DRP-AI)                                    | GPIO                    |

| MIPI CSI-2 v1.2<br>(4Lanes, 2ch) | General Processing<br>Accelerator               | Multi-target detection<br>(Face, Person's body) | Motor Controller        |

| (4Lanes, Zch)                    | Accelerator                                     | (race, reison's body)                           | Environment Sensor I/F  |

| Display I/F                      | Video and                                       | Graphics                                        |                         |

| HDMI v1.4a TX (1ch)              | Camera ISP                                      | 2D Graphics engine                              | External Memory I/F     |

|                                  | H.264/265 Multi Codec                           | JPEG Codec                                      | LPDDR4 (32-bit)         |

| Audio I/F                        |                                                 |                                                 | eMMC (1ch)              |

| I2S (1ch)                        |                                                 | urity                                           | Analog                  |

|                                  | Trusted S                                       | Secure IP                                       | 0                       |

|                                  |                                                 |                                                 | ADC (20ch, 12bit)       |

Temperature sensor (2ch)

#### RZ/V2L block diagram

| System                     | CF                             | vU                                            |        | Peripheral I/F                                             |

|----------------------------|--------------------------------|-----------------------------------------------|--------|------------------------------------------------------------|

| Arm Debugger (CoreSight™)  | Arm® Cortex®-A55: 1.2GHz Arm   | <sup>®</sup> Cortex <sup>®</sup> -A55: 1.2GHz | Arm®   | SDHI (UHS-I, 1ch)                                          |

| DMAC (16ch)                | L1 I\$: 32KB L1 D\$: 32KB L1 I | \$: 32KB L1 D\$: 32KB                         | -M33   | USB2.0 (Host, 1ch)                                         |

| Power control              | NEON FPU N                     | IEON FPU                                      | 200MHz | USB2.0 (Host/Peripheral, 1ch)                              |

| Timers                     | L3\$: 256KB w                  | L3\$: 256KB w/ECC                             |        |                                                            |

| 32-bit Timer (1ch)         | Mem                            | ories                                         |        | I2C (4ch)                                                  |

| 16-bit Timer (8ch)         | RAM 128                        | KB w/ECC                                      |        | SCI 8/9-bit (2ch)                                          |

| PWM (8ch)                  |                                |                                               |        | SCIF(UART) (5ch)                                           |

| WDT (3ch)                  |                                | Sensing and Analyzing                         |        |                                                            |

| . ,                        | AI-accelerator (DRP-AI)        |                                               |        | CAN-FD (2ch)                                               |

| Image Sensor I/F           | Video and                      | Graphics                                      |        | GPIO                                                       |

| MIPI CSI-2 (4Lanes, 1ch)   | Image Scaling Unit (5M pixel)  | 3D GPU (Mali™-0                               | G31)   | Enternal Manager 1/E                                       |

| Parallel (HD-30fps, 1ch)   | H.264 Enc/Dec (1920            | ) × 1080pixel, 30fps)                         |        | External Memory I/F                                        |

| Display I/F                | Security                       | (ontion)                                      |        | DDR3L/DDR4-1600 (16-bit)<br>SPI Multi I/O (8-bit DDR, 1ch) |

| MIPI DSI-2 (4Lanes, 1ch)   | Secure Boot                    | Device Unique                                 | D      | SDHI (UHS-I) / eMMC (1ch)                                  |

| Parallel (WXGA-60fps, 1ch) | Crypto Engine                  | JTAG Disable                                  |        |                                                            |

| A 11 1/2                   | TRNG                           | OTP 4K-bit                                    | ,      | Analog                                                     |

| Audio I/F                  | THING                          | UTF 4K-DIL                                    |        | 12-bit ADC (8ch)                                           |

| SSI (I2S, 4ch)             |                                |                                               |        | Thermal Sensor (1ch)                                       |

| SRC (1ch)                  |                                |                                               |        |                                                            |

## **RZ/V2MA Group**

#### CPU

- 2× Cortex-A53 (up to 1.0GHz)

- Vision and AI

- Al Accelerator; DRP-Al at 1.0 TOPS/W class

- OpenCV Accelerator (DRP)

- Video and Graphics H.265/H.264 Multi Codec

- **Communication Interface** SD Host × 2ch

- PCI-Express 2.0 (2-lane) × 1ch

- Gigabit Ethernet × 1ch USB3.1 Gen1 Host/Function × 1ch

- $I^2C$  Bus × 4ch

- SCI × 6ch

- UART × 2ch

- Memory Interface

- eMMC 4.5.1 × 1ch

- 32-bit LPDDR4-3200 × 1ch

- **RZ/V2H Group**

- CPU

- 4× Cortex-A55 (up to 1.8GHz)

- 2× Cortex-R8 (up to 800MHz)

- 1× Cortex-M33 (up tp 200MHz)

- Vision and AI

- AI Accelerator: DRP-AI at 10TOPS/W class

- OpenCV Accelerator (DRP)

- Camera Interface: MIPI-CSI2 (1/2/4lane) × 4ch Video and Graphics

- H.265/H.264 Multi Codec

- 3D Graphics Engine Mali-G31 (Option)

- Image Signal Processor (ISP) Mali-C55 (Option)

- Display OUT: MIPI-DSI (1/2/4lane) × 1ch

- Communication Interface

- SD Host × 2ch

- PCI-Express 3.0 (4lane × 1/2lane × 2)

- Gigabit Ethernet × 2ch

- USB3.2 × 2ch, USB2.0 × 1ch

- Memory Interface

- eMMC 4.5.1 × 1ch

- 32bit LPDDR4/4X-3200 × 2ch

- Security

- Hardware Security Engine (Option)

#### RZ/V2MA block diagram

| System                    | CF                                              | บ                                               | Peripheral I/F                         |

|---------------------------|-------------------------------------------------|-------------------------------------------------|----------------------------------------|

| Arm Debugger (CoreSight™) | Arm <sup>®</sup> Cortex <sup>®</sup> -A53: 1GHz | Arm <sup>®</sup> Cortex <sup>®</sup> -A53: 1GHz | SDI (2ch)                              |

| DMAC (16ch)               | L1 I\$: 32KB L1 D\$: 32KB<br>NEON FPU           | L1 I\$: 32KB L1 D\$: 32KB<br>NEON FPU           | USB3.1 (1ch)<br>(Host/Peripheral)      |

| Timers                    | L2\$: 5                                         | 12KB                                            | PCle Gen2 (2Lane)                      |

| Timer (32ch)              |                                                 |                                                 | Gbit Ethernet MAC (1ch)                |

| PWM (16ch)                | Memories                                        |                                                 | IIC (4ch)                              |

| WDT (2ch)                 | RAMA 200KB                                      | RAMB 1MB                                        | CSI (6ch)                              |

| Analog                    | Sensing an                                      | d Analyzing                                     | UART (2ch)                             |

| Temperature sensor (2ch)  | Al-accelerator (DRP-AI)                         | Vision Accelerator (DRP)                        | GPIO                                   |

|                           | Video codec<br>H.264/265 Multi Codec            |                                                 | External Memory I/F<br>LPDDR4 (32-bit) |

|                           |                                                 |                                                 | eMMC (1ch)                             |

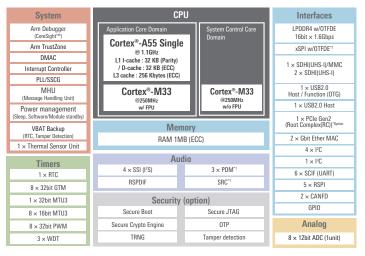

| System                            |                                           | CP                  | ٥U            |                                           | Interfaces                                          |

|-----------------------------------|-------------------------------------------|---------------------|---------------|-------------------------------------------|-----------------------------------------------------|

| Arm Debugger                      | Arm <sup>®</sup> Cortex <sup>®</sup> -A55 | Arm <sup>®</sup> Co |               | Arm <sup>®</sup> Cortex <sup>®</sup> -M33 | LPDDR4/4X w/ECC<br>32-bit × 2 (12.8GB/s × 2)        |

| Arm Trust Zone                    | Quad 1.8GHz (0/D)                         | Dual 80             | DOMHz         | 200MHz                                    | 32-DIL × 2 (12.8GD/S × 2)<br>xSPI × 2 (4.8-bit DTR) |

| Interrupt Controller              | L1:(I=32KB+D=32KB)/core                   | L1:(I=32KB+D        |               | FPU                                       | $SDIO + eMMC \times 1ch$                            |

| PLL / SSCG                        | L3:1MB T                                  | CM:(I=128KB+        | D=128KB)/core | DSP extension                             | SDIO × 2ch<br>- SDIO: v3.0/UHS-I                    |

| Standby                           |                                           |                     |               |                                           | - eMMC: JEDEC 4.5.1                                 |

| DMAC (80ch)                       | Inte                                      | rnal Sha            | red Mem       | ory                                       | USB3.2 (Gen2 × 1)<br>- Host × 2ch                   |

| Event Link Controller             | ł                                         | RAM 6M              | B w/ECC       |                                           | USB2.0<br>- Host / Func. × 1ch<br>- Host × 1ch      |

| Timers                            |                                           |                     |               |                                           | GbEthernet × 2ch (IEEE1588)                         |

| GPTW × 16ch                       | Al Accerelato                             | -                   | Visi          | on Accerelator                            | PCIe Gen3 4L $\times$ 1/2L $\times$ 2 (RC/EP)       |

| BTC                               | DRP-AI 80TOP                              | S                   |               | DRP                                       | IRQ × 16ch                                          |

| $OSTM (32-bit \times 8ch)$        |                                           |                     |               |                                           | NMI                                                 |

| · · · · ·                         | V                                         | ideo and            | Graphics      | S                                         | l <sup>3</sup> C × 1ch                              |

| CMTM (32-bit × 8ch)               | GPU [Mali™ G31] (                         | option)             | ISP [Ma       | ali™ C55] (option)                        | l²C × 9ch                                           |

| WDT × 4ch                         | Camera IN: MIPI-CSI2 4                    | l-lane ×4           | H 264         | /265 Enc./Dec.                            | SCIF × 1ch                                          |

|                                   | Display OUT: MIPI-DSI                     |                     |               | e Scaling Unit                            | RSCI(UART/SPI/I <sup>2</sup> C host) × 10ch         |

| Audio                             | Dispidy OUT. MILLIPI                      | +-Idile X I         | IIIIaų        |                                           | RSPI × 3ch                                          |

| SSI (I <sup>2</sup> C) TDM × 10ch |                                           |                     |               |                                           | CAN-FD × 6ch                                        |

| SPDIF × 3ch                       | S                                         | ecurity II          | P (option     | )                                         | GPIO × 86port                                       |

| ASRC / ADMAC                      | Secure Boot                               |                     | Dev           | ice Unique ID                             | Analog                                              |

| ADG                               | Crypto Engin                              | е                   | J             | rAG Disable                               | 12-bit ADC (8ch)                                    |

| PDM (input) × 6ch                 | TRNG                                      |                     | C             | )TP 32K-bit                               | Thermal Sensor (1ch)                                |

## Flexible Development Kits

These products are evaluation boards with RZ/V series configured as the key device and are capable of easily implementing software development such as camera sensor input image processing, low power consumption AI inference, video streaming, and etc.

#### RZ/V2H Evaluation Board Kit

RZ/V2L Evaluation Board Kit

#### RZ/V2M Evaluation Board Kit

- P/N: RTK0EF0168C04000BJ

- LPDDR4X: 8GB × 2 xSPI Flash Memory: 64MB

- micro SD × 2

- High Speed Interface - Gigabit Ethernet  $\times$  2

- USB3.2 Gen2 × 2

- USB2.0  $\times$  2 (OTG  $\times$  1, Host-only  $\times$  1)

- PCIe Gen3 × 1 (4 lanes max)

- MIPI CSI-2 Camera Interface × 4

- MIPI DSI Display Interface × 1

- P/N: RTK9754L23S01000BE

- P/N: RTK9754L27S01000BE (Secure Type)

- DDR4 SDRAM: 2GB

- eMMC: 64GB

- QSPI NOR Flash: 512MB

- microSD × 1

- A/D Converter Interface

- P/N: V2M\_EVK

- CMOS image sensor equipped board included (SONY/IMX415, CS mount equipped)

- LPDDR4: 32Gbit

- eMMC: 16GB

- HDMI Type-A × 1

- USB3.1 Gen1 Type-C × 1

- microSD × 1

RZ/V2MA Evaluation Board Kit

- P/N: SBEV-RZ/V2MA-KIT

- LPDDR4: 32Gbit

- eMMC: 16GB

- Ethernet × 1

- USB3.1 Gen1 Type-C × 1

- microSD × 1

- PCIe × 4 slot (2-lanes available)

## "Easy to Use" with AI SDK

Visit the webpage below for the latest information on AI SDK <code>https://renesas-rz.github.io/rzv\_ai\_sdk/latest/  $\Box$ </code>

AI SDK eliminates complex build tasks and enables immediate AI evaluation

DISEASE!

cab is det

16

Bicycle enters in restricted area

MI

85 people

The customers only need to select their use case w/o requiring AI training. Provided as a free Open-Source Software on Github and can be used in MP.

#### Agriculture

Smart City

Industrial

#### Healthcare

Smart Building

Smart Home

Retail

## **RZ/N Series**

### **RZ/N Series Features**

- 1. Provides optimized microcontrollers for a variety of industrial network applications

- 2. Integrated Ethernet switch and EtherCAT slave controller alongside support for major Industrial Ethernet protocols and TSN

- 3. Redundant network configuration reduces network downtime to zero

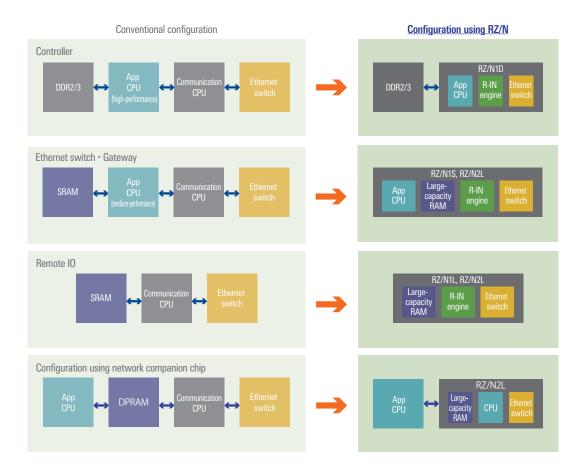

#### 1. Provides optimized microcontrollers for a variety of industrial network applications

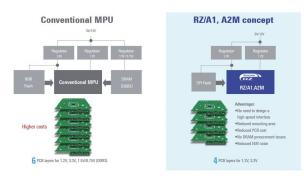

The RZ/N1 series lineup provides a choice of three CPU options and features the Renesas R-IN engine ("R-IN engine") and an on-chip 5-port Gigabit Ethernet switch, making it ideal for a variety of industrial network applications. Integrating the functionality of a communication CPU and key peripheral components helps reduce the BOM cost.

The RZ/N2L is optimized for the role of dedicated network companion chip, simplifying the task of adding network functionality to industrial equipment. Since it handles network-related processing independently of the external CPU, Industrial Ethernet support can be implemented without the need to make major changes to the existing application software.

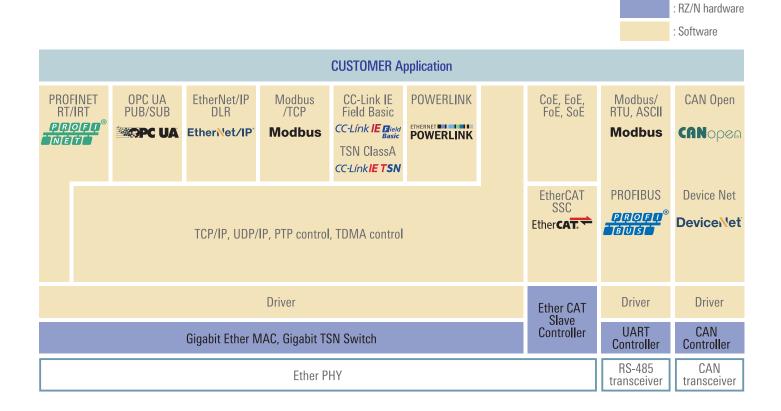

#### 2. Integrated Ethernet switch and EtherCAT slave controller alongside support for major Industrial Ethernet protocols and TSN

A wide range of Industrial Ethernet protocols are supported. Separating application processing and network processing allows for more efficient application control.

#### 3. Redundant network configuration reduces network downtime to zero

Advanced redundant network configuration support helps eliminate network downtime.

- Redundant network connections: Parallel Redundancy Protocol (PRP)

- Looped network connections: HSR (High-availability Seamless Redundancy), DLR (Device Level Ring), RSTP (Rapid Spawning Trees)

## **RZ/N Series Application**

PLC industrial controllers

Industrial switches

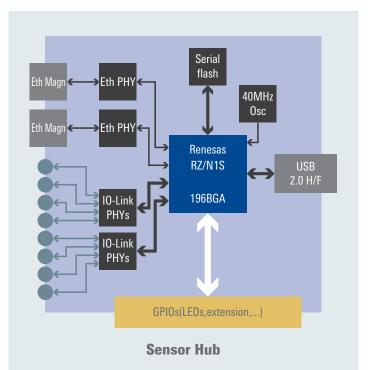

Sensor hubs

Gateways

Communication modules

Remote I/O

## RZ/N2L Group

CPU core

- Arm<sup>®</sup> Cortex<sup>®</sup>-R52

- Operating frequency: 400MHz/200MHz

- Single-precision/double-precision floating-point unit On-chip memory

- Tightly Coupled Memory: 128KB (w/ ECC) + 128KB (w/ ECC)

- = 1.5MB on-chip RAM (with ECC)

- Features

- TSN support

- 3-port Gigabit Ethernet switch

- EtherCAT slave controller

- Parallel host/serial host interface

- PWM timer

- $\Delta \sum$  interface

- ADC

- Trigonometric function unit

- CAN-FD

- USB2.0

- SPI, SCI, I<sup>2</sup>C

- xSPI

- Safety functions

- Register write protection, input clock oscillation stop detection, and CRC Isolated peripheral function access via MPU

- Packages

- 225-pin FBGA (13mm × 13mm, 0.8mm pitch)

121-pin FBGA (10mm × 10mm, 0.8mm pitch)

- Tj = -45°C to +125°C

#### RZ/N2L Group block diagram

| СР                      | U                       |

|-------------------------|-------------------------|

| Cortex<br>400/20        |                         |

| FPU MPU                 | Debug GIC               |

| I Cache:<br>16KB w/ ECC | D Cache:<br>16KB w/ ECC |

| ATCM<br>128KB w/ ECC    | BTCM<br>128KB w/ ECC    |

## Memory

| RAM 1.5M                  | MB w/ ECC                      |

|---------------------------|--------------------------------|

| Ethernet Sub System       | Host I/F                       |

| 1 × EthernetMAC (1Gbps)   | Parallel I/F                   |

| With switch + IEEE1588    | Serial I/F                     |

| EtherCAT Slave Controller | Interfaces                     |

| GMAC                      | 6 × SCI                        |

| System                    | 3 × 1 <sup>2</sup> C           |

| 2 × 8ch DMAC              | $2 \times \text{CAN-FD}$       |

| JTAG Debug                | USB 2.0 HS (Host/Func)         |

| Clock Generation Circuit  | GPIO                           |

| Trigonometric unit        | ∆∑I/F                          |

| Timers                    | Memory Interfaces              |

| 8 × 16-bit + 1 × 32-bit   | $4 \times SPI$                 |

| MTU3                      | 2 × xSPI                       |

| 6 × 16-bit CMT            | SRAM I/F (16-bit bus)          |

| 1 × 32-bit CMTW           | SDRAM I/F (16-bit bus)         |

| 18 × 32-bit GPT           | Burst ROM I/F (16-bit bus)     |

| 1 × 14-bit WDT            | Analan                         |

| Security                  | Analog<br>(4 + 8) × 12-bit ADC |

| Secure boot               |                                |

|                           |                                |

| JTAG w/ disable function  |                                |

### **RZ/N2L Product Lineup**

| Part Number                                          |               | R9A07G084M08GBG                                                                                                                                         | R9A07G084M04GBG             | R9A07G084M08GBA                 | R9A07G084M04GBA |  |

|------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|-----------------|--|

| CPU                                                  |               | Cortex®-R52 (Max 400MHz)                                                                                                                                |                             |                                 |                 |  |

| Tightly Coupled Mer                                  | nory          | ATCM 128KB (w/ECC) / BTCM 128KB (w/ECC)                                                                                                                 |                             |                                 |                 |  |

| RAM                                                  |               | 1.5MB (w/ECC)                                                                                                                                           |                             |                                 |                 |  |

| External bus                                         |               | 8, 1                                                                                                                                                    | 6bit                        | Not Su                          | oported         |  |

| Heat I/E                                             | Serial Host   | OSPI                                                                                                                                                    | /QSPI                       | QS                              | SPI             |  |

| Host I/F                                             | Parallel Host | 8, 1                                                                                                                                                    | 6bit                        | Not Su                          | oported         |  |

| Industrial Ethernet F                                | Protocol      | EtherCAT <sup>®</sup> , PROFINET RT/IRT, EtherNet/IP <sup>™</sup> , TSN (IEC/IEEE 60802 Industrial Profile),<br>CC-Link IE Field Basic, OPC UA over TSN |                             |                                 |                 |  |

| Ether Port                                           |               | 3 p                                                                                                                                                     | orts                        | 2 pc                            | orts            |  |

| Motor Control Perip                                  | herals        | PWM <sup>-</sup>                                                                                                                                        | Timer (MTU3, GPT), ADC*, Σ⊿ | Interface, Trigonometric functi | on unit         |  |

| Security                                             |               | Supported                                                                                                                                               | Not Supported               | Supported                       | Not Supported   |  |

| Power                                                |               |                                                                                                                                                         | 1.1V, 1.                    | 8V, 3.3V                        |                 |  |

| Operating Temperate                                  | ure           |                                                                                                                                                         | Tj = -40 t                  | o +125°C                        |                 |  |

| Package                                              |               | FB                                                                                                                                                      | GA                          | FB                              | GA              |  |

| Pin Count                                            |               | 225                                                                                                                                                     | ōpin                        | 121                             | pin             |  |

| Package Information                                  | 1             | 13mm × 13mm, 0.8mm pitch 10mm × 10mm, 0.8mm pitch                                                                                                       |                             |                                 | n, 0.8mm pitch  |  |

| Power<br>Operating Temperatu<br>Package<br>Pin Count |               | 1.1V, 1.8V, 3.3V           Tj = -40 to +125°C           FBGA           225pin           121pin                                                          |                             |                                 | GA              |  |

\* 225pin only

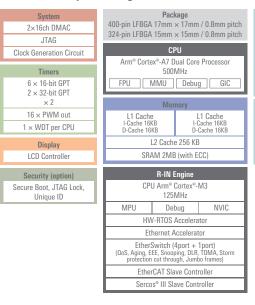

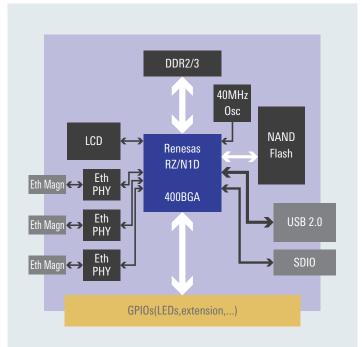

### **RZ/N1D Group**

CPU core

- Arm<sup>®</sup> Cortex<sup>®</sup>-A7 dual-core processor

- Operating frequency: 500MHz

- Cache memory

- L1 I-cache: 16KB × 2, D-cache: 16KB × 2

- L2: 256KB

- Internal memory

- 2MB (ECC)

- External memory DDR2/DDR3 controller

- Quad I/O SPI

- SDIO eMMC

- NAND flash controller

- R-IN engine

- Arm<sup>®</sup> Cortex<sup>®</sup>-M3

- Operating frequency: 125MHz

- HW-RTOS accelerator

- Ethernet accelerator

- Main Ethernet communication functions

- EtherCAT slave controller

- Sercos® III slave controller

- HSR switch (400-pin)

- 5-port Ethernet switch

- Other communication functions

- UART × 8 channels

- $I^2C \times 2$  channels

- USB Host/Function × 1 channel, Host 1 channel

- SPI × 6 channels (master × 4 channels, slave × 2 channels)

CAN

- Other functions

- LCD controller

- ADC: 12-bit × 8 channels × 2 units (400-pin)

- ADC: 12-bit × 8 channels × 1 unit (324-pin) PWM timer, GPT

- Package

- 400-pin: LFBGA, 17 × 17mm, 0.8mm pin pitch

- 324-pin: LFBGA, 15 × 15mm, 0.8mm pin pitch

- Operating temperature

- Tj = -40°C to +110°C

#### RZ/N1D Group block diagram

| IIICHAGES                |

|--------------------------|

| $8 \times UART$          |

| $2 \times I^2C$          |

| $2 \times CAN$           |

| $6 \times SPI$           |

| USB2.0 HS<br>(Host/Func) |

| Memory Interface         |

| Quad SPI                 |

| NAND Flash I/F           |

| DDR2/DDR3 IF             |

|                          |

| 2 × SDIO/eMMC            |

Interfaces

Application example: Programmable logic controller block diagram

## RZ/N1S Group

- CPU core

- Arm<sup>®</sup> Cortex<sup>®</sup>-A7 single-core processor

- Operating frequency: 500MHz

- . Cache memory L1 I-cache: 16KB, D-cache: 16KB

- L2: 128KB

- Internal memory

- 6MB (ECC)

- External memory

- Quad I/O SPI

- SDIO eMMC

- NAND flash controller

- R-IN engine Arm<sup>®</sup> Cortex<sup>®</sup>-M3

- Operating frequency: 125MHz

- HW-RTOS accelerator

- Ethernet accelerator

- Main Ethernet communication functions

- EtherCAT slave controller

- Sercos<sup>®</sup> III slave controller

- 5-port Ethernet switch

- Other communication functions

- UART × 8 channels

- $I^2C \times 2$  channels

- USB Host/Function × 1 channel, Host 1 channel

- SPI × 6 channels (master × 4 channels, slave × 2 channels)

- CAN

- Other functions

- LCD controller

- ADC: 12-bit × 8 channels × 1 unit

- PWM timer, GPT

Package

- 324-pin: LFBGA, 15 × 15mm, 0.8mm pin pitch

196-pin: LFBGA, 12 × 12mm, 0.8mm pin pitch

- Operating temperature

- Tj = -40°C to +110°C

#### RZ/N1S Group block diagram

| System                                       |                                                    | Package                                                                                                   |                                                    |  |  |

|----------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| 2×16ch DMAC                                  |                                                    | 15mm × 15mm                                                                                               |                                                    |  |  |

| JTAG                                         | 196-pin LFBGA                                      | 12mm × 12mm                                                                                               | 1 / U.8mm pitch                                    |  |  |

| Clock Generation Circuit                     |                                                    | CPU                                                                                                       |                                                    |  |  |

| Timers<br>6 × 16-bit GPT<br>2 × 32-bit GPT   |                                                    | (®-A7 Single Cor<br>500MHz<br>MMU Debu                                                                    |                                                    |  |  |

| × 2                                          |                                                    | Memory                                                                                                    |                                                    |  |  |

| 16 × PWM out<br>1 × WDT per CPU              |                                                    | L1 Cache<br>I-Cache 16KB<br>D-Cache 16KB                                                                  |                                                    |  |  |

| Display                                      | l                                                  | 2 Cache 128 KE                                                                                            | }                                                  |  |  |

| LCD Controller                               | SR/                                                | AM 6MB (with E                                                                                            | CC)                                                |  |  |

| Security (option)<br>Secure Boot, JTAG Lock, | CPL                                                | R-IN Engine<br>J Arm® Cortex®-                                                                            | M3                                                 |  |  |

|                                              |                                                    | 12EMU-                                                                                                    |                                                    |  |  |

| Unique ID                                    | MPU                                                | 125MHz<br>Debug                                                                                           | NVIC                                               |  |  |

|                                              | MPU                                                | 125MHz<br>Debug<br>/-RTOS Accelera                                                                        | NVIC                                               |  |  |

|                                              | HW                                                 | Debug                                                                                                     | itor                                               |  |  |

|                                              | HW<br>Etl<br>(QoS, Aging, E                        | Debug<br>/-RTOS Accelera                                                                                  | itor<br>tor<br>1port)<br>, TDMA, Storm             |  |  |

|                                              | HW<br>Ethers<br>(QoS, Aging, E<br>protection       | Debug<br>/-RTOS Accelera<br>hernet Accelerat<br>Switch (4port +<br>EE, Snooping, DLR                      | itor<br>tor<br>1port)<br>TDMA, Storm<br>po frames) |  |  |

|                                              | HW<br>Etl<br>(QoS, Aging, E<br>protection<br>Ether | Debug<br>/-RTOS Accelera<br>hernet Accelerai<br>Switch (4port +<br>EE, Snooping, DLR<br>cut through, Jumi | tor<br>tor<br>TDMA, Storm<br>tof frames)<br>roller |  |  |

| Interfaces               |

|--------------------------|

| $8 \times \text{UART}$   |

| $2 \times I^2C$          |

| $2 \times CAN$           |

| $6 \times SPI$           |

| USB2.0 HS<br>(Host/Func) |

| Memory Interface         |

| Quad SPI                 |

| NAND Flash I/F           |

| 2 × SDIO/eMMC            |

Application example: Sensor Hub block diagram

## **RZ/N1L Group**

R-IN engine

- Arm<sup>®</sup> Cortex<sup>®</sup>-M3

- Operating frequency: 125MHz

- HW-RTOS accelerator

- Ethernet accelerator

- Internal memory 6MB (ECC)

- External memory

- Quad I/O SPI

- SDIO eMMC

- NAND flash controller

- Main Ethernet communication functions

- EtherCAT slave controller

- Sercos<sup>®</sup> III slave controller

- GbE Ethernet switch

- Other communication functions

- UART × 8 channels

- $I^2C \times 2$  channels

- USB Host/Function × 1 channel, Host 1 channel

- SPI  $\times$  6 channels (master  $\times$  4 channels, slave  $\times$  2 channels)

- CAN × 2 channels

- Other functions

- LCD controller

- ADC: 12-bit × 8 channels × 1 unit

- PWM timer, GPT

- Package

- 196-pin: LFBGA, 12 × 12mm, 0.8mm pin pitch

- Operating temperature Tj =  $-40^{\circ}$ C to  $+110^{\circ}$ C

#### **RZ/N1L Group block diagram**

| System<br>2×16ch DMAC            | <b>Package</b><br>196-pin LFBGA 12mm × 12mm / 0.8mm pit |                                                          | n / 0.8mm pitch                       |

|----------------------------------|---------------------------------------------------------|----------------------------------------------------------|---------------------------------------|

| JTAG                             |                                                         | Memory                                                   |                                       |

| Clock Generation Circuit         | SRA                                                     | AM 6MB (with E                                           | CC)                                   |

| Timers                           |                                                         | R-IN Engine                                              |                                       |

| 6 × 16-bit GPT<br>2 × 32-bit GPT | CPU Arm <sup>®</sup> Cortex <sup>®</sup> -M3<br>125MHz  |                                                          |                                       |

| × 2                              | MPU                                                     | Debug                                                    | NVIC                                  |

| 16 × PWM out                     | HV                                                      | /-RTOS Accelera                                          | ator                                  |

| 1 × WDT per CPU                  | Ethernet Accelerator                                    |                                                          |                                       |

|                                  | Ether<br>(QoS, Aging, E<br>protection                   | Switch (2port +<br>EE, Snooping, DLR<br>cut through, Jum | 1port)<br>, TDMA, Storm<br>bo frames) |

|                                  | Ether                                                   | rCAT Slave Cont                                          | roller                                |

|                                  | Serco                                                   | s® III Slave Con                                         | troller                               |

| Interfaces               |

|--------------------------|

| $8 \times UART$          |

| $2 \times I^2C$          |

| $2 \times CAN$           |

| 6 × SPI                  |

| USB2.0 HS<br>(Host/Func) |

| Memory Interface         |

| Quad SPI                 |

| NAND Flash I/F           |

| 1 × SDIO/eMMC            |

|                          |

## **RZ/N2L:** Development Environments (Integrated Development Environments)

|                             | iar.                                                                                                   | RENESAS                                                                          |

|-----------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Development<br>environments | IAR Embedded Workbench® for Arm®                                                                       | • e <sup>2</sup> studio <sup>*1</sup><br>e <sup>2</sup> studio                   |

| Compilers                   | • IAR C/C++ compiler*2                                                                                 | • GNU tool*4                                                                     |

| Other tools                 | <ul> <li>AP4 and FSP Smart Configurator code generation tools from<br/>Renesas can be used.</li> </ul> | • Code generation function available as a plug-in.                               |

| ICEs                        | <ul> <li>I-jet™/I-jet Trace™ for Arm Cortex®-A/R/M</li> <li>JTAGjet-Trace</li> </ul>                   | <ul> <li>J-Link LITE from Segger</li> <li>J-Link series from Segger*5</li> </ul> |

\*1. Eclipse-based development environment from Renesas (http://renesas.com/e2studio)

\*2. Two versions of the software are available for download free of charge. One limits the code size to 32KB and can be used with no time limitation. The other has no limit on code size and expires after 30 days. [https://www.iar.com/EWARM] \*3. Arm CC is included in DS-5. In addition to the popularly priced DS-5 RZ/A and RZ/T editions, a fully functional evaluation version of DS-5 that expires after 30 days is available free of charge. Contact your DS-5 dealer for details.

\*4. GNU TOOLS & SUPPORT Website (https://llvm-gcc-renesas.com/)

\*5. Renesas does not handle ICEs from Segger. Contact a sales agent for details.

## RZ/N2L: Development Tools (Debuggers, ICEs)

|           | Kyoto Microcomputer Co., Ltd.                                                                                                 | Our insight, your value                                |                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------|

| Debuggers | • PARTNER-Jet2                                                                                                                | • microVIEW-PLUS                                       | TRACE32 PowerView                                                                   |

| ICEs      |                                                                                                                               | • adviceLUNA II                                        | TRACE32 PowerDebug & PowerTrace                                                     |

|           | <ul> <li>exeGCC from Kyoto Microcomputer</li> <li>GNU tool*1</li> <li>Arm CC*2</li> <li>IAR C/C++ compiler,*3 etc.</li> </ul> | <ul> <li>Arm CC*2</li> <li>GNU tool,*1 etc.</li> </ul> | <ul> <li>Arm CC*2</li> <li>GNU tool*1</li> <li>IAR C/C++ compiler*3 etc.</li> </ul> |

\*1. GNU TOOLS & SUPPORT Website (https://llvm-gcc-renesas.com/)

\*2. Arm CC is included in DS-5. In addition to the popularly priced DS-5 RZ/A and RZ/T editions, a fully functional evaluation version of DS-5 that expires after 30 days is available free of charge. Contact your DS-5 dealer for details.

\*3. Two versions of the software are available for download free of charge. One limits the code size to 32KB and can be used with no time limitation. The other has no limit on code size and expires after 30 days. (https://www.iar.com/EWARM)

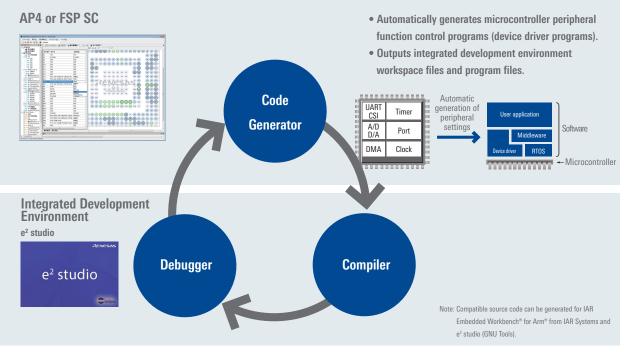

### Code Generation Support: Flexible Software Package (FSP) + Smart Configurator (SC)

The FSP includes everything you'll need to start developing software: board-dependent programs, peripheral function drivers, middleware, and documentation on how to use them.

Smart Configurator is a utility based on the concept of "combining software components freely." The intuitive GUI makes it easy to configure pins and FSP driver settings and to generate source code customized for your use case. It works together with integrated development environments such as IAR Embedded Workbench® for Arm from IAR Systems and e<sup>2</sup> studio.

| FreeRTOS<br>Reel-time tesks                                  |                                                   |         | Conne<br>FreeRTO         |              |            |                    |

|--------------------------------------------------------------|---------------------------------------------------|---------|--------------------------|--------------|------------|--------------------|

| Mutexes                                                      |                                                   | Hardwar | e Abstractio             | h Layer (HA  | L) Drivers |                    |

| Software timer<br>execution trace function<br>Stack overflow | USBHS<br>USBFS                                    | ADC     | Delta-Sigma<br>Interface | IOPORT       | POE3       | POEG               |

| detection<br>RAM allocation                                  | SCI 12C<br>SCI SPI                                | xSPI    | GPT                      | CMT<br>CMTW  | ELC        | GMAC               |

| Preemptive scheduler                                         | I <sup>2</sup> C Master<br>I <sup>2</sup> C Slave | CRC     | WDT                      | Core to Core | DMA        | Ethernet<br>Switch |

| Inter-task<br>communication                                  | MTU3                                              | CAN     | RTC                      | CGC          | DOC        | TSU                |

| Memory management                                            | LPM                                               | ERROR   | ICU                      | SHM          |            |                    |

### **Renesas Starter Kit+ for RZ/N2L**

#### https://www.renesas.com/rskrzn2l

- The board is mounted with a RZ/N2L with a 225BGA package and can be used to evaluate almost all of the device's functions.

- Emulator circuit is mounted, can start program debugging by simply connecting USB cable to PC.

- Ordering number: RTK9RZN2L0S0000BE

- 225-pin RZ/N2L MPU (R9A07G084M04GBG)

- Gigabit Ethernet PHY

- Octal flash memory

- Pmod<sup>™</sup>, Grove<sup>®</sup>, QWIIC<sup>®</sup>, and mikroBUS<sup>™</sup> connectors

- Pin header for external expansion

- Includes a USB power cable that can also be used to connect an emulator.

#### that Network SOIVI KIL https://www.renesas.com/yconnect-it-rzn21

- YCONNECT-IT-RZN2L is a compact reference kit for evaluating applications using Industrial Ethernet communication

- Flexible power supply from either USB or 24V DC terminal or Arduino host board

- Ordering number: YCONNECT-IT-RZN2L

- 2x Gigabit Industrial Ethernet connectors

- 2x PMOD connectors

- Arduino dual-use connector

- 9-pin connector for external debugger connection and Segger J-Link OB for debugging via USB

\_\_\_\_\_

**CONNECT IT! ETHERNET RZ/N**

#### https://www.renesas.com/RZN-YConnect-It 🖸

- CONNECT IT! ETHERNET RZ/N is the perfect solution kit for developers new to developing with the RZ/N1.

- The kit comes with not only an evaluation board, but also a JTAG emulator and various sample software.

- It is possible to evaluate master communication / slave communication of industrial networks.

- JTAG emulator

- IAR I-jet Lite (20-pin flat ribbon/USB cable)

- 2 USB cables

- Startup manuals

- Pin setting toolRZ/N Solution Kit DVD

- User's manual

- OS (Linux, ThreadX<sup>®</sup>(Evaluation version), HW-RTOS)

- Software PLC Codesys

- Protocol stacks

### **RZ Ecosystem Solutions from Partner Companies**

Visit the webpage below for the information on RZ/N series solutions from partner companies. https://www.renesas.com/products/microcontrollers-microprocessors/rz-mpus/rz-partner-solutions  $\square$

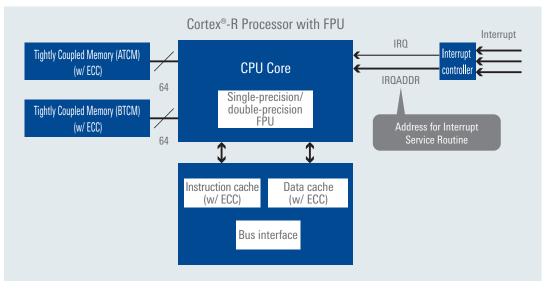

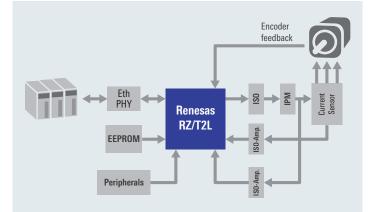

## **RZ/T Series**

## **RZ/T Series Features**

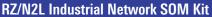

- High-performance, high-speed real-time control

- Integrated peripheral functions

### High-performance, high-speed real-time control

- High-speed RAM directly coupled to the CPU allows fast processing and bypassing of the cache for reliable real-time responsiveness.

- ECC for enhanced reliability

- Assures responsive interrupt handling suitable for embedded control applications.

#### Integrated peripheral functions

- Integrates communication ASSP that would previously have been implemented as an external device.

- Integrates encoder interface that would previously have been implemented by an FPGA or ASIC.

|                                                 | EnDat 2.2                                                                                             | BiSS-C                                                                                                                                                                                                                                                    | NIKON A-format                                              | FA-CODER                                                                                                                                    | HIPERFACE DSL                                                                                                                                                                                                                                            |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Related specifications                          | Heidenhein Corp<br>http://www.heidenhain.de                                                           | iC-Haus GmbH<br>http://www.biss-interface.com                                                                                                                                                                                                             | NIKON Corporation<br>http://www.nikon.co.jp                 | TAMAGAWA SEIKI CO.,LTD.<br>http://www.tamagawa-seiki.co.jp                                                                                  | SICK STEGMANN GmbH<br>http://www.sick.com                                                                                                                                                                                                                |

| Communication system                            | Clock synchronous                                                                                     | Clock synchronous                                                                                                                                                                                                                                         | Asynchronous                                                | Asynchronous                                                                                                                                | Asynchronous                                                                                                                                                                                                                                             |

| Transmission<br>link                            | RS-485                                                                                                | RS-422                                                                                                                                                                                                                                                    | RS-485                                                      | RS-485                                                                                                                                      | RS-485                                                                                                                                                                                                                                                   |

| Supported<br>frequencies/data<br>transfer rates | 100kHz to 16.7MHz                                                                                     | 62.5kHz to 10MHz                                                                                                                                                                                                                                          | 2.5Mbps, 4Mbps,<br>6.67Mbps, 8Mbps,<br>16Mbps               | 2.5Mbps                                                                                                                                     | 9.375Mbps                                                                                                                                                                                                                                                |

| I/O pin count/<br>signal level                  | 4/3.3V TTL level                                                                                      | 2 / 3.3V TTL level                                                                                                                                                                                                                                        | 3 / 3.3V TTL level                                          | 3 / 3.3V TTL level                                                                                                                          | 3 / 3.3V TTL level                                                                                                                                                                                                                                       |

| Compatible<br>functions on<br>T series          | <ul> <li>Propagation delay<br/>function</li> <li>Not supported for<br/>incremental signals</li> </ul> | <ul> <li>Delay compensation<br/>function</li> <li>Supported in C mode (not<br/>supported in B mode)</li> <li>Not supported for<br/>incremental signals</li> <li>Supported on 1-to-1<br/>connections (not<br/>supported on bus<br/>connections)</li> </ul> | - Supported on 1-to-1<br>connections and bus<br>connections | <ul> <li>Baseband NRZ code<br/>support</li> <li>Not supported for<br/>incremental signals or<br/>synchronous Manchester<br/>code</li> </ul> | <ul> <li>External synchronous<br/>communication (sync<br/>mode)</li> <li>Asynchronous<br/>communication (free<br/>running mode)</li> <li>Estimator function<br/>(position estimation when<br/>error occurs)</li> <li>RSSI, quality monitoring</li> </ul> |

## **RZ/T Series Application**

A fast CPU operating at 300MHz to 800MHz and large-capacity tightly-coupled memory provide the high performance and advanced functionality required by industrial applications such as industrial motors or AC servo drives. The RZ/T series is powerful enough to handle Industrial Ethernet processing of various types while still maintaining real-time performance.

Medical Equipment

Elevator

Wind Turbine

Conveyor

## **RZ/T2M Group**

#### CPU core

- Arm<sup>®</sup> Cortex<sup>®</sup>-R52 × 2

- Operating frequency: 800MHz/400MHz/200MHz

- Single-precision/double-precision floating-point unit

- On-chip memory

- Tightly Coupled Memory: 512KB (W/ ECC) + 64KB (W/ ECC)

- 2MB on-chip RAM (with ECC)

- Features

- Low latency peripheral port (LLPP) bus

- TSN support

- 3-port Gigabit Ethernet switch

- EtherCAT slave controller

- Encoder interface

- PWM timer

- △∑ interface

- ADC

- Trigonometric function unit

- xSPI

- CAN-FD

- USB2.0

- SPI, SCI, I<sup>2</sup>C

- Safety functions

- Register write protection, input clock oscillation stop detection, and CRC

Isolated peripheral function access via MPU

- Packages

- 320-pin FBGA (17mm × 17mm, 0.8mm pitch)

- 225-pin FBGA (13mm × 13mm, 0.8mm pitch)

- 176-pin LQFP (24mm × 24mm, 0.5mm pitch)

- = 128-pin LOFP (14mm × 20mm, 0.5mm pitch)

- Tj = -45°C to +125°C

### RZ/T2M Group block diagram

**Robot Gripper**

| C                                                                                                                                                                                                                                             | PU                                                                                                  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| Cortex®-R52           800/400/200MHz           FPU         MPU           Debug         GIC           1-cache         D-cache           16KB w/ ECC         16KB w/ ECC           ATCM         BTCM           512KB w/ ECC         64KB w/ ECC | Cortex®-R52<br>800/400/200MHz<br>FPU MPU Debug GIC<br>I-cache<br>16KB w/ ECC D-cache<br>16KB w/ ECC |  |  |

|                                                                                                                                                                                                                                               | mory<br>1B w/ ECC                                                                                   |  |  |

| System<br>2 × 16ch DMAC                                                                                                                                                                                                                       | Interfaces<br>6 × SCI                                                                               |  |  |

| JTAG Debug                                                                                                                                                                                                                                    | 2 × 1 <sup>2</sup> C                                                                                |  |  |

| Clock Generation Circuit<br>Trigonometric unit                                                                                                                                                                                                | 2 × CAN-FD<br>USB 2.0 HS (Host/Func)                                                                |  |  |

| Ethernet Sub System                                                                                                                                                                                                                           | GPIO                                                                                                |  |  |

| 1 × EthernetMAC (1Gbps)<br>With switch + IEEE1588                                                                                                                                                                                             | ∆∑I/F<br>Memory Interfaces                                                                          |  |  |

| EtherCAT Slave Controller<br>GMAC                                                                                                                                                                                                             | 4 × SPI                                                                                             |  |  |

| GMAC                                                                                                                                                                                                                                          | 2 × xSPI<br>SRAM I/F (32-bit bus)                                                                   |  |  |

| 8 × 16-bit + 1 × 32-bit<br>MTU3                                                                                                                                                                                                               | SDRAM I/F (32-bit bus)<br>Burst ROM I/F (32-bit bus)                                                |  |  |

| 6 × 16-bit CMT<br>1 × 32-bit CMTW                                                                                                                                                                                                             | Analog                                                                                              |  |  |

| 18 × 32-bit GPT<br>2 × 14-bit WDT                                                                                                                                                                                                             | (8 + 16) × 12-bit ADC                                                                               |  |  |

| 2 × 14-bit WDT                                                                                                                                                                                                                                | Encoder interfaces (2ch)                                                                            |  |  |

| Secure boot (option)                                                                                                                                                                                                                          |                                                                                                     |  |  |

| JTAG w/ disable function                                                                                                                                                                                                                      |                                                                                                     |  |  |

| Security                        | R9A07G075M28GBG                                                                              | R9A07G075M26GBG        | R9A07G075M28GBA                           | R9A07G075M26GBA                    | R9A07G075M27GBA | —                                     | R9A07G075M05GFP          | R9A07G075M05GFA          |

|---------------------------------|----------------------------------------------------------------------------------------------|------------------------|-------------------------------------------|------------------------------------|-----------------|---------------------------------------|--------------------------|--------------------------|

| Non-Security                    | R9A07G075M24GBG                                                                              | R9A07G075M22GBG        | R9A07G075M24GBA                           | R9A07G075M22GBA                    |                 | R9A07G075M21GBA                       | R9A07G075M01GFP          | R9A07G075M01GFA          |

| CPU                             |                                                                                              |                        | Dual Cortex®-R5                           | 2 (800+800MHz)                     |                 |                                       | Single Cortex®-          | R52 (800MHz)             |

| System RAM                      |                                                                                              |                        | 2.0MB                                     | w/ECC                              |                 |                                       | 1.5MB                    | w/ECC                    |