### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# μPD1700 SERIES EV-1709

**USER'S MANUAL**

**NEC Corporation**

# μPD1700 SERIES EV-1709 USER'S MANUAL

#### TABLE OF CONTENTS

| CHAPT | TER 1 | I. INT | RODUCTIO         | ·N         |             |         |         | <b></b> . |            |      |           |      | 1  |

|-------|-------|--------|------------------|------------|-------------|---------|---------|-----------|------------|------|-----------|------|----|

| CHAPT | TER 2 | 2. SPE | CIFICATIO        | NS         |             |         |         |           | . <i></i>  |      |           |      | 2  |

| CHAPT | TER 3 | B. BLO | OCK DIAGR        | AM         |             |         | <b></b> |           | <i></i>    |      |           | • .• | 4  |

| CHAPT |       |        | ERATING P        |            |             |         |         |           |            |      |           |      |    |

| 4.1   | EV-1  | 709 US | ED FOR μPD1      | 709 WITH ! | EVAKIT-     | 1700    |         |           |            |      |           |      | 5  |

| 4.2   | EV-1  | 709 US | ED FOR μPD1      | 716 WITH 1 | EVAKIT-     | 1700    |         |           |            |      |           |      | €  |

| 4.3   | EV-1  | 709 US | ED FOR μPD1      | 709 WITH 9 | SE-1700     |         |         |           | <i></i> .  | •••• |           |      | 8  |

| 4.4   | EV-1  | 709 US | ED FOR µPD1      | 716 WITH 9 | SE-1700     |         |         |           | <i></i> .  |      |           |      | 10 |

| 4.5   | EXT   | ERNAL  | DRIVER CIR       | CUIT       |             |         |         |           | <i></i>    |      |           |      | 12 |

| 4.6   | EXT   | ERNAL  | PRESCALER        | CIRCUIT .  |             |         |         |           |            |      |           |      | 14 |

| 4.7   | OPER  | RATIO  | NAL PRECAU       | TIONS      |             |         |         |           |            |      |           |      | 14 |

| CHAP1 | TER 5 | DE     | SCRIPTION        | OF EV-17   | 09 OPE      | RATION  | ł       |           |            |      |           |      | 16 |

| 5.1   | PB A  | ND PC  | PORTS            |            |             |         |         |           |            |      |           |      | 16 |

| 5.2   | SERI  | AL I/0 |                  |            |             |         |         |           | <b>.</b> . |      |           |      | 16 |

| 5.3   | A/D ( | CONVE  | RTER             |            |             |         |         |           | <i></i>    |      |           |      | 16 |

| 5.4   | CGP   | OUTPL  | ут <i>.</i>      |            |             |         |         |           | <i></i>    |      |           |      | 18 |

| CHAPT | rer e | S. CO  | NNECTOR P        | IN TABLE   | ES          |         |         |           |            |      |           |      | 19 |

| 6.1   | CN1   | PIN TA | BLE              |            |             |         |         |           |            |      |           |      | 19 |

| 6.2   | •     |        | DRRESPONDE       |            | •           |         |         |           |            |      |           |      |    |

|       |       |        | EVAKIT-170       |            |             |         |         |           |            |      |           |      | 20 |

| 6.3   |       |        | RRESPONDE        |            |             |         |         |           |            |      |           |      |    |

|       | USEC  | WITH   | SE-1700)         |            |             |         |         |           |            |      |           |      | 21 |

| 6.4   | μPD1  | 716 CC | RRESPONDE        | NCE TABL   | E (WHEN     | EV-1709 | IS      |           |            |      |           |      |    |

|       | USEC  | WITH   | EVAKIT-170       | 0)         |             |         |         | <i></i>   |            |      |           |      | 22 |

| 6.5   | μPD1  | 716 CC | PRESPONDE        | NCE TABLE  | E (WHEN     | EV-1709 | IS      |           |            |      |           |      |    |

|       | USEC  | WITH   | SE-1700)         |            | • • • • • • |         |         |           |            |      | • • • • • | • •  | 23 |

| APPEN | IDIX  | i      | P1 AND P2        | PIN TABI   | LES         |         |         |           |            |      |           |      | 24 |

| APPEN | IDIX  | H      | μ <b>PD1700B</b> | PIN CONN   | 1ECTIO      | N DIAG  | RAM     |           |            |      |           |      | 26 |

| APPEN | IDIX  | 111    | μPD1709 P        | N CONNE    | ECTION      | DIAGR   | AM .    |           |            |      |           |      | 27 |

| APPEN | IDIX  | IV     | μPD1716 P        | N CONNE    | ECTION      | DIAGR   | AM .    |           | . <b></b>  |      |           |      | 28 |

| APPEN | IDIX  | ٧      | μPD1709 IN       | ISTRUCT    | ION SET     | г       |         |           |            |      |           |      | 29 |

| ΔPPFN | אוחו  | FIGU   | RF EV.1700       | CIRCUIT    | LDIAGE      | RΔM     |         |           |            |      | 2         | n ~  | 22 |

#### CHAPTER 1. INTRODUCTION

EV-1709 is designed for developing programs for  $\mu$ PD1709 and  $\mu$ PD1716 using the EVAKIT-1700 and SE-1700 option I/O board.

The  $\mu$ PD1709 functions handled by EV-1709 include the PB<sub>0</sub> to PB<sub>3</sub>, PC<sub>2</sub> to PC<sub>3</sub>, AD, CGP, and serial I/O functions.

Since  $\mu$ PD1716 has functions similar to  $\mu$ PD1709 functions, this user's manual has been prepared for use in developing programs for both devices, but with main emphasis on  $\mu$ PD1709.

When using EV-1709/EV-1716, also refer to the EVAKIT-1700 User's Manual and SE-1700 Operation Manual (EEP-554 and EEP-1004 respectively).

#### EV-1709 Accessories

- 1. One 34-pin socket and cable for CN1

- 2. One 16-pin IC socket and cable for CN2

#### CHAPTER 2. SPECIFICATIONS

Product name

**Functions**

Operating temperature range

Storage temperature range

Power supply

Board dimensions

EV-1709

$\mu$ PD1709 and  $\mu$ PD1716 I/O emulation

0 to 40 °C

-10 to 50 °C (but without condensation)

+5 V 1A MAX.

+15 V 100mA MAX.

-15 V 100mA MAX.

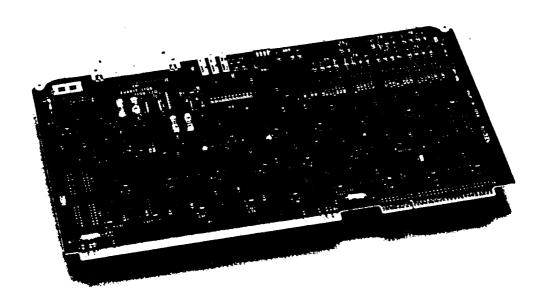

304.8 x 171.5 x 12.7mm

$(12.00 \times 6.75 \times 0.5 \text{ inches})$

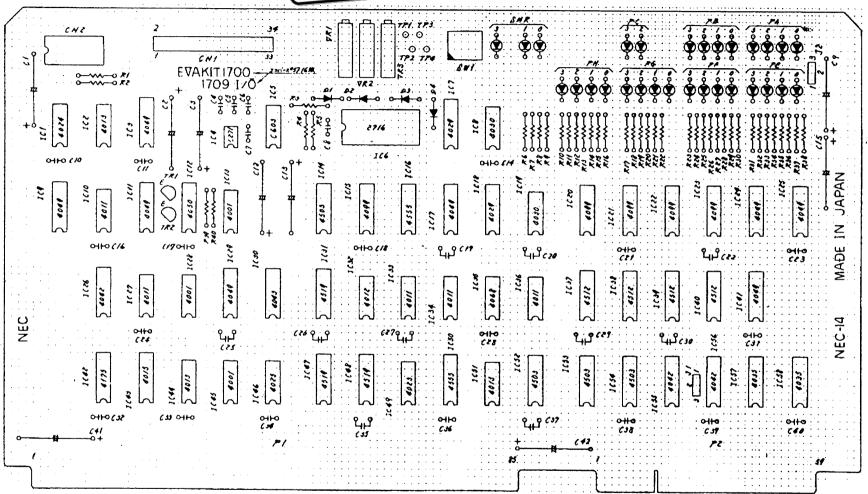

Fig. 2-1 EV-1709 Component Layout

#### CHAPTER 3. BLOCK DIAGRAM

#### CHAPTER 4. OPERATING PROCEDURES

#### 4.1 EV-1709 USED FOR μPD1709 WITH EVAKIT-1700

When used for  $\mu$ PD1709 with EVAKIT-1700, set up EV-1709 in the following way.

#### (1) Jumper settings (EVAKIT-1700 CPU board)

Short-circuit the J2 (2-3) jumper on the CPU board to put the CPU board KEY input circuit into 1709 mode.

#### (2) Jumper settings (EVAKIT-1700 PLA board)

Short-circuit the J1 (1–15, 2–16, 3–17, 4–18, 5–19, 6–20, and 7–21) jumpers on the PLA board to put the segment output into CMOS push-pull mode.

Although the  $\mu$ PD1709 segment output is the N-ch open drain, the EVAKIT-1700 PLA board is not equipped with a corresponding output circuit. Therefore, the PLA board segment output is put into CMOS push-pull mode before connecting the external N-ch open drain driver. Details on this external driver circuit are given in Section 4.5.

#### (3) Jumper settings (EV-1709 board)

Short circuit  $\underline{J2}$  (1-2) to connect the power supply to the LED used to indicate port status on the board. Note that since there is an increase in electrical noise on the board when the LED is on, short-circuiting J1 (2-3) can turn the LED off when AD converter is used.

To set the circuit used to initialize the PB and PC ports, short-circuit J1 (2-3).

#### (4) SW1 setting (EV-1709 board)

Set all 4 bits in this switch to the on position.

#### (5) Slot mounting

The EVAKIT-1700 has six slot positions. EV-1709 can be mounted in either of the top two vacant slots.

#### (6) Connector connections (EVAKIT-1700 and EV-1709)

Use the accessory 16-pin flat cable to connect the EVAKIT-1700 CPU board CN4 connector (16-pin IC socket) to CN2 located in the top left hand corner of EV-1709.

This connection carries PA<sub>0</sub> to PA<sub>3</sub> signals from the CPU board to EV-1709.

#### (7) Connections to target system

Connections to the target system are made via the following four connectors.

(1) CPU board CN1 (cable supplied with EVAKIT-1700)

1 to 4. (Not used)

5. CE (input)

6. (Not used)

7. INT (input)

8 to 11. (Not used)

12 to 16. GND

#### ② CPU board CN3 (cable supplied with EVAKIT-1700)

1 to 2. (Not used)

3. FM (VC0H input)

4. GND

5. PSC (output)

6. GND

7 to 8. (Not used)

9. EO<sub>1</sub> (output)

10. GND

11 to 12. (Not used)

#### ③ PLA board CN1 (cable supplied with EV-1700)

An external N-ch open drain driver must be connected to the segment and digit outputs. See Section 4.5 for details on this external driver circuit.

**GND** 1. 2. Sa (output) 3. Sb (output) 4. Sc (output) 5. Sd (output) 6. Se (output) 7. Sf (output) 8. Sg (output) 9 to 10. (not used) 11. D3 (output)..... Used as D2 12. D4 (output) . . . . . Used as D3 13 to 16. (Not used)

4 EV-1709 CN1 (cable supplied with EV-1709)

1 to 2. (Not used) 3. PA<sub>2</sub>/SCK (input/output) PA<sub>3</sub> 4. (input/output) 5. PB<sub>0</sub> (input/output) 6. PB<sub>1</sub> (input/output) 7. PB<sub>2</sub>/SO (input/output) 8. PB3/SI (input/output) 9. PC<sub>2</sub> (output) 10. PC3 (output) 11. CGP (output) 12 to 14. GND 15. AD<sub>0</sub> (input)

16. GND

17 to 34. (Not used)

, , , , , ,

#### 4.2 EV-1709 USED FOR μPD1716 WITH EVAKIT-1700

When used for  $\mu$ PD1716 with EVAKIT-1700, set up EV-1709 in the following way.

#### (1) Jumper settings (EVAKIT-1700 CPU board)

Short-circuit the J2 (2-3) jumper on the CPU board to put the CPU board KEY input circuit into 1716 mode.

#### (2) Jumper settings (EVAKIT-1700 PLA board)

Short-circuit the J1 (1-15, 2-16, 3-17, 4-18, 5-19, 6-20, and 7-21) jumpers on the PLA board to put the segment output into CMOS push-pull mode.

#### (3) Jumper settings (EV-1709 board)

Short circuit <u>J2 (1-2)</u> to connect the power supply to the LED used to indicate port status on the board. Note that since there is an increase in electrical noise on the board when the LED is on, short-circuiting J1 (2-3) can turn the LED off when AD converter is used.

To set the circuit used to initialize the PB and PC ports, short-circuit J1 (2-3).

#### (4) SW1 setting (EV-1709 board)

Set all 4 bits in this switch to the on position.

#### (5) Slot mounting

The EVAKIT-1700 has six slot positions. EV-1709 can be mounted in either of the top two vacant slots.

#### (6) Connector connections (EVAKIT-1700 and EV-1709)

Use the accessory 16-pin flat cable to connect the EVAKIT-1700 CPU board CN4 connector (16-pin IC socket) to CN2 located in the top left hand corner of EV-1709.

This connection carries PA<sub>0</sub> to PA<sub>3</sub> signals from the CPU board to EV-1709.

#### (7) Connections to target system

Connections to the target system are made via the following four connectors.

① CPU board CN1 (cable supplied with EVAKIT-1700)

1 to 4. (Not used)

5. CE (input)

6. (Not used)

7. INT (input)

8 to 11. (Not used)

12 to 16. GND

#### ② CPU board CN3 (cable supplied with EVAKIT-1700)

To emulate the  $\mu$ PD1716 VCOH (FM) input pin, an external prescaler  $\mu$ PB553AC must be connected using the following FM and PSC pins. See Section 4.6 for details on this external driver circuit.

AM (AM VCO input)

2. GND

FM (FM VCO input)

4. GND

5. PSC (output)

6. GND

7 to 8. (Not used)

9. EO<sub>1</sub> (output)

10. GND

11. EO<sub>2</sub> (output)

12. GND

#### ③ PLA board CN1 (cable supplied with EV-1700)

1. GND 2 to 9. (Not used)

10. D<sub>2</sub> (output) . . . . . Used as D<sub>1</sub>

11. D3 (output) . . . . . Used as D2

12. D4 (output) ..... Used as D3

13 to 16. (Not used)

#### 4 EV-1709 CN1 (cable supplied with EV-1709)

| 1.        | $PA_0$               | (input/output) |  |  |

|-----------|----------------------|----------------|--|--|

| 2.        | PA <sub>1</sub>      | (input/output) |  |  |

| 3.        | PA <sub>2</sub> /SCK | (input/output) |  |  |

| 4.        | PA3                  | (input/output) |  |  |

| 5.        | PB <sub>O</sub>      | (input/output) |  |  |

| 6.        | PB <sub>1</sub>      | (input/output) |  |  |

| 7.        | PB <sub>2</sub> /SO  | (input/output) |  |  |

| 8.        | PB3/SI               | (input/output) |  |  |

| 9.        | PC2 (out             | tput)          |  |  |

| 10.       | PC3 (out             | tput)          |  |  |

| 11.       | (Not used            | d)             |  |  |

| 12 to 14. | GND                  |                |  |  |

| 15.       | AD <sub>0</sub> (in  | out)           |  |  |

| 16.       | GND                  |                |  |  |

| 17 to 34. | (Not used            | <b>ქ</b> )     |  |  |

#### 4.3 EV-1709 USED FOR µPD1709 WITH SE-1700

When used for  $\mu$ PD1709 with SE-1700, set up EV-1709 in the following way.

#### (1) Jumper settings (SE-1700)

```

Short (8-9, 10-11, 12-13, 14-15, 16-17, 18-19, and 20-21)

J1

J2

Short (1-2)

J3

Short (1-2)

J4

Short (1-2)

J5

Short (1-2)

J6

Short (1-2)

Short (1-2)

J7

Short (3-5 and 4-6)

J8

J9

Open

```

#### (2) SPLSEL switch setting

J10 Open

Although the SPLSEL value can be set by CL command or when the PLA object is loaded in cases where EVAKIT-1700 is used, this value is set by an on-board switch when SE-1700 is used. After first checking the source list, set to 2 or 3.

On the object board, the SPLSEL takes a value obtained by subtracting 1 from the actual value. That is, SPLSEL is 2 if the actual value is 3, and 1 if the actual value is 2. This change is made automatically by the assembler.

This must be kept in mind, therefore, when setting the SPLSEL switch after checking the object code value.

#### (3) PROM mounting

The PROM used is the 2716 device. Programs are written divided into eight high order bits (PROG-HIGH) and eight low order bits (PROG-LOW) mounted to the respective IC26 and IC25 sockets. The segment PLA (SEG-PLA) is connected to IC17, and the digit PLA (DIG-PLA) is connected to IC5 socket.

Refer to Chapter 5 of the SE-1700 Instruction Manual (EEP-1004) for details on PROM writing procedures.

#### (4) Jumper settings (EV-1709 board)

Short circuit  $\underline{\mathsf{J1}}$  (1–2) to connect the power supply to the LED used to indicate port status on the board. Note that since there is an increase in electrical noise on the board when the LED is on, short-circuiting J1 (2–3) can turn the LED off when AD converter is used.

To set the circuit used in initializing (Hi-Z) the PB and PC ports, short-circuit J2 (2-3).

#### (5) SW1 setting (EV-1709 board)

Set all 4 bits in this switch to the on position.

#### (6) Rack mounting

The rack used with SE-1700 contains four slots. The SE-1700 and EV-1709 boards may be mounted in any slots.

#### (7) Connections SE-1700 and EV-1709

Used the accessory 16-pin flat cable to connect the SE-1700 CN4 connector (16-pin IC socket) to CN2 located in the top left hand corner of EV-1709.

This connection carries PA<sub>0</sub> to PA<sub>3</sub> signals from the CPU board to EV-1709.

#### (8) Connections to target system

Connections to the target system are made via the following four connectors.

① SE-1700 board CN1 (cable supplied with SE-1700)

1 to 4. (Not used)

5. CE (input)

6. (Not used)

7. INT (input)

8 to 11. (Not used)

12 to 16. GND

#### ② SE-1700 board CN3 (cable supplied with SE-1700)

1 to 2. (Not used)

3. FM (FM VCO input)

4. GND

5. PSC (input)

6. GND

7 to 8. (Not used)

9. EO<sub>1</sub> (output)

10. GND

11 to 12. (Not used)

#### SE-1700 CN2 (cable supplied with SE-1700)

With only digit outputs, the N-ch open drain driver must be connected externally. See Section 4.5 for details on the external driver circuit. Unlike EVAKIT-1700, SE-1700 is equipped with the built-in N-ch open drain driver circuit. Therefore, an external driver circuit is not required for segment outputs.

1. GND

2. Sa (output)

Sb (output)

Sc (output)

5. Sd (output)

6. Se (output)

|   | 7.            | Sf   | (outpi        | ut)                |

|---|---------------|------|---------------|--------------------|

|   | 8.            |      | (outpu        |                    |

|   | 9 to 10.      | •    | ot used       |                    |

|   | 11.           | •    |               | ut) Used as D2     |

|   | 12.           | _    |               | ut) Used as D3     |

|   | 13 to 16.     |      | ot used       |                    |

| 4 | EV-1709 CN1 ( | cabl | e supp        | lied with EV-1709) |

|   | 1 to 2.       | (No  | ot used       | )                  |

|   | 3.            | PΑ   | 2/ <u>SCK</u> | (input/output)     |

|   | 4.            | PΑ   | 3             | (input/output)     |

|   | 5.            | PB   | 0             | (input/output)     |

|   | 6.            | PB   | 1             | (input/output)     |

|   | 7.            | PB   | 2/SO          | (input/output)     |

|   | 8.            | PB:  | 3/SI          | (input/output)     |

|   | 9.            | PC:  | 2 (out        | put)               |

|   | 10.           | PC:  | 3 (out        | put)               |

|   | 11.           | CG   | P (out        | put)               |

|   | 12 to 14.     | GN   | D             |                    |

|   | 15.           | ΑD   | o (inp        | ut)                |

|   | 16.           | GN   | -             |                    |

|   | 17 to 34.     | (No  | ot used       | )                  |

|   |               |      |               |                    |

#### (9) Power connections

The power supply voltages are +5V, +15V and -15V. Using the cables supplied with SE-1700, connect to the connectors below the racks.

+5V: Main power supply for SE-1700 and EV-1709

±15V: Power supply for AD converter

#### 4.4 EV-1709 USED FOR μPD1716 WITH SE-1700

When used for  $\mu$ PD1716 with SE-1700, set up EV-1709 in the following way.

#### (1) Jumper settings (SE-1700)

```

J1 Short (8-9, 10-11, 12-13, 14-15, 16-17, 18-19, and 20-21)

```

J2 Short (1-2)

J3 Short (1-2)

J4 Short (1-2)

J5 Short (1-2)

J6 Short (1-2)

J7 Short (1-2)

. J8 Short (3-5 and 4-6)

J9 Open

J10 Open

#### (2) PROM mounting

The PROM used is a 2716 device. Programs are written divided into eight high order bits (PROG-HIGH) and eight low order bits (PROG-LOW) mounted to the respective IC26 and IC25 sockets. And the digit PLA (DIG-PLA) is connected to IC5 socket.

Refer to Chapter 5 of the SE-1700 Operation Manual (EEP-1004) for details on PROM writing procedures.

#### (3) Jumper settings (EV-1709 board)

Short circuit J1 (1-2) to connect the power supply to the LED used to indicate port status on the board. Note that since there is an increase in electrical noise on the board when the LED is on, short-circuiting J1 (2-3) can turn the LED off when an A/D converter is used.

To set the circuit used in initializing (Hi-Z) the PB and PC ports, short-circuit J2 (2-3).

#### (4) SW1 setting (EV-1709 board)

Set all 4 bits in this switch to the on position.

#### (5) Rack mounting

The rack used with SE-1700 contains four slots. The SE-1700 and EV-1709 boards may be mounted in any slots.

#### (6) Connector connections (SE-1700 and EV-1709)

Use the accessory 16-pin flat cable to connect the SE-1700 CN4 connector (16-pin IC socket) to CN2 located in the top left hand corner of EV-1709,

This connection carries PA<sub>0</sub> to PA<sub>3</sub> signals from the CPU board to EV-1709.

#### (7) Connections to target system

Connections to the target system are made via the following four connectors.

(1) SE-1700 board CN1 (cable supplied with SE-1700)

1 to 4. (Not used) 5. CE (input) 6. (Not used) INT (input) (Not used) 8 to 11. 12 to 16. GND

#### SE-1700 board CN3 (cable supplied with SE-1700)

To emulate the μPD1716 VCOH (FM) input pin, an external prescaler μPB553AC must be connected using the following FM and PSC pins. See Section 4.6 for details on this external driver circuit.

1. AM (AM VCO input) 2. **GND** FM (FM VCO input) 3. 4 GND 5. PSC (output) **GND** 6 7 to 8. (Not used) 9. EO<sub>1</sub> (output) 10. GND 11. EO<sub>2</sub> (output)

#### **GND** ③ SE-1700 CN2 (cable supplied with SE-1700)

12.

1. **GND** 2 to 9. (Not used) 10. D2 (output) ..... Used as D1 11. D3 (output) ..... Used as D2 12. D4 (output) ..... Used as D3 13 to 16. (Not used)

#### (4) EV-1709 CN1 (cable supplied with EV-1709)

| 1.        | PA <sub>0</sub>      | (input/output) |

|-----------|----------------------|----------------|

| 2.        | PA <sub>1</sub>      | (input/output) |

| 3.        | PA <sub>2</sub> /SCK | (input/output) |

| 4.        | PA3                  | (input/output) |

| 5.        | $PB_O$               | (input/output) |

| 6.        | PB <sub>1</sub>      | (input/output) |

| 7.        | PB <sub>2</sub> /SO  | (input/output) |

| 8.        | PB3/SI               | (input/output) |

| 9.        | PC <sub>2</sub> (out | put)           |

| 10.       | PC3 (out             | put)           |

| 11.       | (Not used            | )              |

| 12 to 14. | GND                  |                |

| 15.       | AD <sub>0</sub> (inp | out)           |

| 16.       | GND                  |                |

| 17 to 34, | (Not used            | )              |

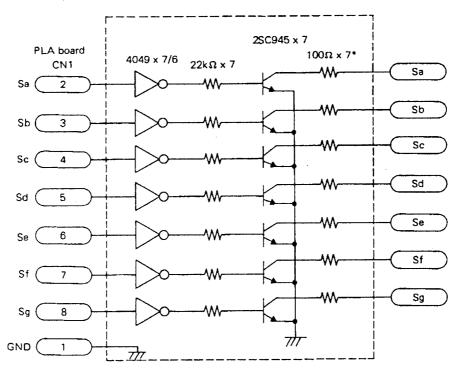

#### 4.5 EXTERNAL DRIVER CIRCUIT

Whereas  $\mu$ PD1709 is equipped with both segment and digit outputs,  $\mu$ PD1716 only has digit outputs. The respective output waveforms differ, and direct connections between EVAKIT-1700/SE-1700 and target systems are not possible in some cases (see Table 4-1).

Although the  $\mu$ PD1709 segment output is N-ch open drain, the EVAK1T-1700 PLA board segment output is only P-ch open drain and CMOS Push-Pull where N-ch open drain cannot be selected.

The SE-1700 segment output, on the other hand, has been designed to permit selection of N-ch open drain.

And although the  $\mu$ PD1709 digit output is also N-ch open drain, it cannot be selected on the EVAKIT-1700 PLA board and SE-1700 board.

Although EV-1709 does not require an external driver when used as  $\mu$ PD1716 (see Table 4-1), the driver circuit outlined in Figure 4-1 has to be connected when used as  $\mu$ PD1709.

Table 4-1 Target System Direct Connections

|                                          | EVAKIT-1700   | SE-1700       |  |

|------------------------------------------|---------------|---------------|--|

| μPD1709<br>segment output<br>(N-ch Open) | Not permitted | Permitted     |  |

| μPD1709<br>digit output<br>(N-ch Open)   | Not permitted | Not permitted |  |

| μPD1716<br>digit output<br>(Push-Pull)   | Permitted     | Permitted     |  |

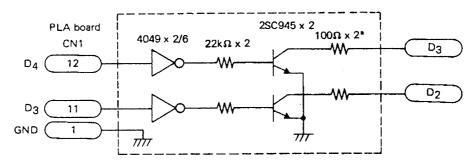

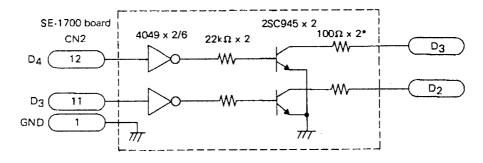

#### (1) Segment driver (EV-1709 used as μPD1709 with EVAKIT-1700)

#### (2) Digit driver (EV-1709 used as $\mu$ PD1709 with EVAKIT-1700)

#### (3) Digit driver (EV-1709 used as $\mu$ PD1709 with SE-1700)

Fig. 4-1 External Driver Circuit (segment/digit)

<sup>\*</sup>The 100  $\Omega$  connected to the 2SC945 collector is a current limiter resistance which may not be required with some user circuits.

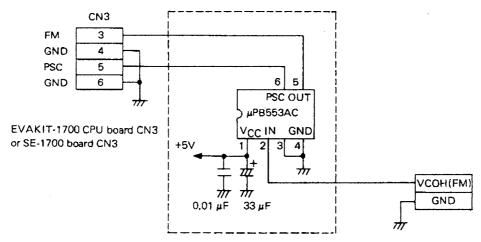

#### 4.6 EXTERNAL PRESCALER CIRCUIT

The  $\mu$ PB553AC prescaler must be connected externally to emulate the  $\mu$ PD1716 VCOH (FM) input pin. Although the EVAKIT-1700 and SE-1700 boards are equipped with a pin (FM150M) for built-in prescaler devices, this pin cannot be used with  $\mu$ PD1716. Therefore, an external prescaler circuit like that shown in Figure 4-2 must be prepared.

Also note that  $\mu$ PD1716 is not equipped with the HF and VHF instructions used in  $\mu$ PD1708 and  $\mu$ PD1713. If these instructions are executed, the result is equivalent to executing the NOP instruction without effecting EVAKIT-1700 or SE-1700, but without any guarantee of operation on the actual chip. Therefore, in addition to keeping this fact in mind when instructions are entered in batches, also make sure that the HF and VHF instructions have not been used when a mask is ordered.

Fig. 4-2 External Prescaler Circuit

#### 4.7 OPERATIONAL PRECAUTIONS

Take careful note of the following precautions when using EV-1709.

- (1) EV-1709 is used in combination with EVAKIT-1700 or SE-1700. But because of the 2048-steps ROM and the built-in 256-words RAM, check the source list to ensure that the area being used does not exceed the specified limits. Also note that EV-1709 can be operated by instructions not included in  $\mu$ PD1709 and  $\mu$ PD1716.

- (2) SIO instructions cannot be skipped by skip instructions (ADS, AIS, etc). Program operation cannot be guaranteed if these instructions are preceded by a skip instruction. And also make sure that none of these instructions is located at the point of return by RTS instruction.

Although there is no such restriction on the actual chip, it is necessary to keep this fact in mind from the beginning when designing for program evaluation by EV-1709.

(3) The A/D converter consists of a D/A converter (IC5) and comparator (IC4). The resolution and linearity are not exactly the same as in an actual chip. And because of the possible effects of on-board digital noise, evaluate by carefully observing the waveforms of the basic voltage (pin 3) and input voltage (pin 2) of the comparator (IC4) by oscilloscope.

(4) The port and RAM status are initially unstable when the power is switched on. The initialized status of the EVAKIT-1700 and SE-1700 boards vary, and the desired initialized state may be achieved accidently without specific initialization by program. Therefore, since there is a limit to external evaluation, the source list must always be checked.

When evaluating with EVAKIT-1700, note that the RD instruction (Randomize Data) which destroys RAM contents can be used.

- (5) Although  $\mu$ PD1709 pin functions are emulated by EVAKIT-1700, SE-1700, and EV-1709, the electrical characteristics differ on each board.

- (6) For PLL-related evaluations, carefully observe the VCO output level, frequency, and the degree of distortion, and check that the PLL is properly locked. Note that the PLL can also be locked by higher harmonics even if the divisor value N is incorrectly set by program.

#### CHAPTER 5. DESCRIPTION OF EV-1709 OPERATION

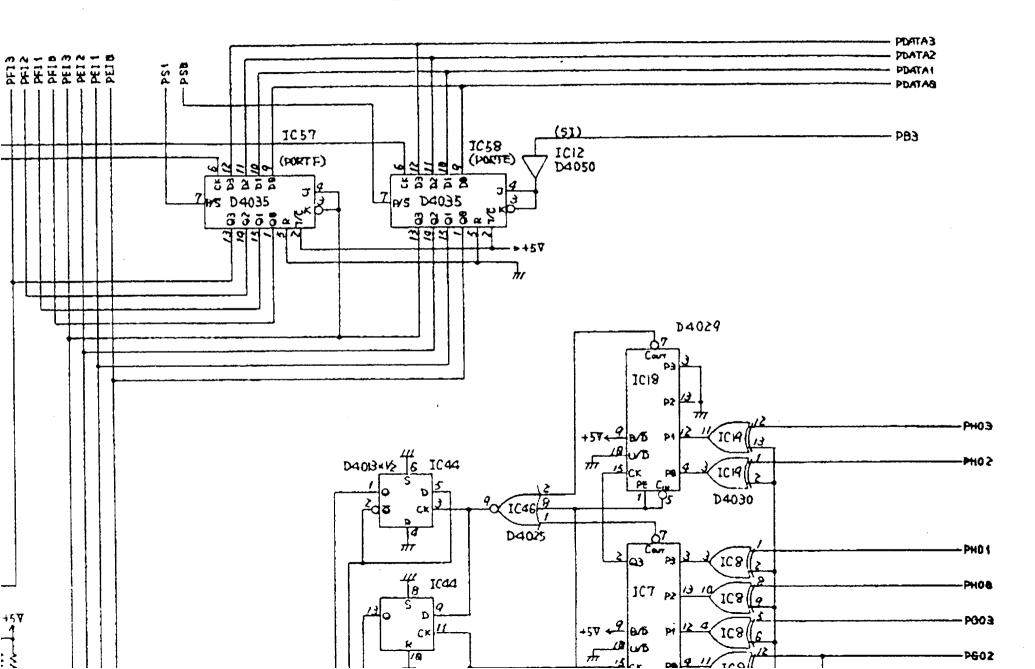

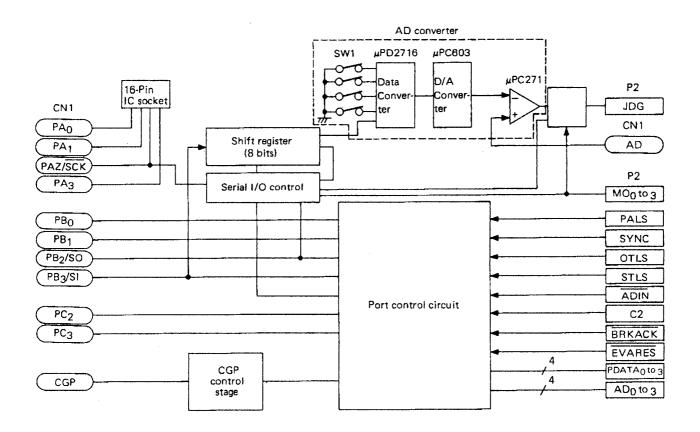

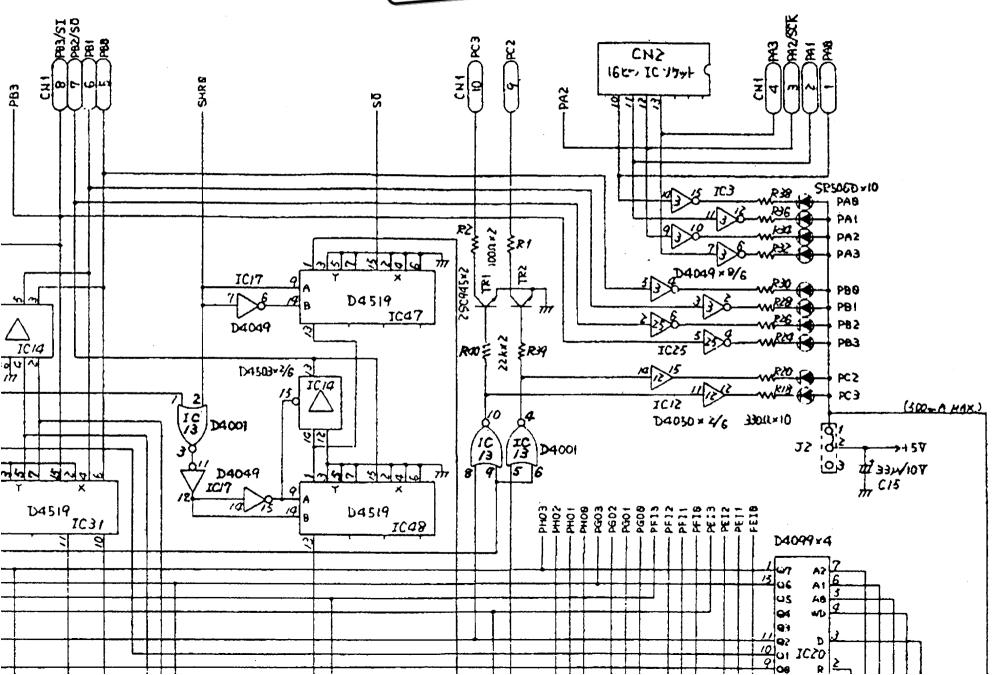

The  $\mu$ PD1709 functions emulated by the EV-1709 board include PB and PC ports, serial I/O, A/D converter, and CGP output functions. All other functions are handled by EVAKIT-1700 or SE-1700 where the evaluation chip is mounted. EV-1709 operations are outlined below with reference to the circuit diagrams in the Appendix.

#### 5.1 PB AND PC PORTS

PB is a 4-bits input/output port and PC is a 2-bits dedicated N-ch open drain output port with a 2SC945 device used as the driver. These ports are connected to EVAKIT-1700 or SE-1700 via PDATA0—3 of P2. The PDATA0—3 output port addresses are latched according to PALS (Port Address Latch Strobe) timing, and the contents of the output port data on PDATA0—3 are latched according to OTLS (Output Latch Strobe) timing. And when used as an input, the port status is transferred to EVAKIT-1700 or SE-1700 via PDATA0—3 according to ADIN timing.

The PB ports are switched to input mode and the PC ports are all switched to high impedance (Hi-Z) when the EVACHIP is reset by switching the power on, when the R (Reset) command is executed by EVAKIT, and when the clock is stopped.

Since the PB and PC internal output latch status is unstable when the power is switched on, always initialize the ports by program.

#### 5.2 SERIAL I/O

The following three pins are related to serial I/O.

SI (also used as PB3) : Serial data input pin

SO (also used as PB<sub>2</sub>) : Serial data output pin

SCK (also used as PA<sub>2</sub>) : Shift clock input/output pin

The serial I/O shift register consists of 4035 devices (IC57 and IC58) connected to the PF (IC57) and PE (IC58) internal ports. These shift register outputs are also used as A/D converter data.

When an internal clock is used as the shift clock, use is made of a 15 kHz signal obtained by dividing the  $\overline{ADIN}$  (30 kHz) output signal from the EVAKIT-1700 or SE-1700 EVACHIP by a 4013 device (IC2). When SMR3 is 1, pin 15 of the 4503 device (IC54) is changed to low level, and a 15 kHz clock is passed to the PA3/SCK pin. If both SMR0 and SMR1 are 1 at this time, the shift register contents are transferred sequentially beginning with the MSB from the PB2/SO pin synchronized with the clock signal. When 8 pulses of the clock are counted by the 4024 device (IC1), pin 8 of 4011 (IC10) is changed to low level, resulting in suspension of the  $\overline{ADIN}$  input, and automatic stopping of clock generation.

#### 5.3 A/D CONVERTER

The A/D converter consists of the 6-bits  $\mu$ PC603 D/A converter (IC5) and the  $\mu$ PC271 comparator (IC4). The AD input pin is applied directly to pin 2 of the comparator. The 4-bits data PE3 to PE0, on the other hand, is passed to the D/A converter (IC5) with the resultant output voltage being applied as a comparison voltage to pin 3 of the comparator (IC4) where it is compared with the input voltage from the AD input pin. The comparator output on pin 7 is low if the AD input voltage is higher than the comparison voltage, and high if lower than that voltage. This comparison result is transferred as the JDG signal (pin 28 of P2) to EVAKIT-1700 or SE-1700 when the TADT or TADF instruction is executed.

The input stage of the  $\mu$ PC603 D/A converter (IC5) includes a data converting device  $\mu$ PD2716 (IC6). Whereas the PE internal port output is "active high", the  $\mu$ PC603 input is "active low". The data is therefore inverted by IC6. The A/D converter also includes 15 data patterns for converter adjustment purposes, the patterns being selected by the 4-bits SW1. Normally, all SW1 bits are switched to the on position.

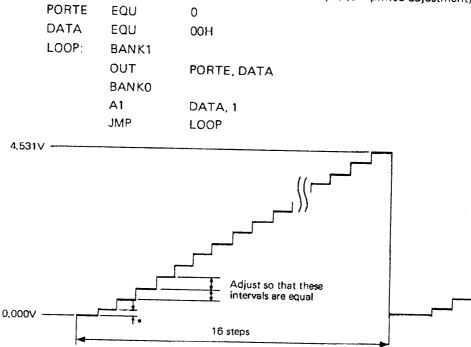

The A/D converter adjustment procedure is described below. Three variable resistance controls (VR1, VR2,

and VR3) are mounted on the board. (a) First, all SW1 bits are switched OFF to obtain maximum D/A converter (IC5) output voltage ( $V_{ref}$ ). A voltmeter is connected to TP1 (IC5 output) and adjusted to read 10.0V by turning VR2 (500 $\Omega$ ). (b) The voltmeter is then connected to TP2 (IC4 input) and adjusted to read 5.0V by turning VR1 (100k $\Omega$ ). (c) VR3 (5M $\Omega$ ) is used for adjusting linearity, and with the voltmeter still connected to TP2 the SW1 settings are changed to obtain the voltages shown in Table 5-1. Since the V<sub>ref</sub> adjusted in step (a) is altered when VR3 is adjusted, steps (a) and (c) are repeated until no further adjustment is necessary. Note that all SW1 bits must be in the ON position when the adjustment is completed.

Since precise adjustment of the linearity is very time consuming, run the following program and make the necessary adjustments while observing the TP2 waveform in an oscilloscope. (Simplified adjustment)

Fig. 5-1 TP2 Oscilloscope Waveform

<sup>\*</sup>The width of the first step only is half the width of the other steps.

Table 5-1 SW1 Settings

(0 = ON 1 = OFF)

|    | SW1 status |    | ·  | IC6 output             | TP2 v                 | 1                         |                          |

|----|------------|----|----|------------------------|-----------------------|---------------------------|--------------------------|

| #3 | #2         | #1 | #0 | (2716)                 | (X V <sub>ref</sub> ) | V (V <sub>ref</sub> ≈ 5V) |                          |

| 0  | 0          | 0  | 0  | Dependent on PE status | <b>←</b>              | +                         | ← Normal setting         |

| 0  | 0          | 0  | 1  | 7F                     | 0/16                  | 0.000                     | ← MIN. value             |

| 0  | 0          | 1  | 0  | 7B                     | 0.5/16                | 0.156                     |                          |

| 0  | 0          | 1  | 1  | 73                     | 1.5/16                | 0.469                     |                          |

| 0  | 1          | 0  | 0  | 6B                     | 2.5/16                | 0.781                     | ]                        |

| 0  | 1          | 0  | 1  | 63                     | 3.5/16                | 1.094                     |                          |

| 0  | 1          | 1  | 0  | 5B                     | 4.5/16                | 1,406                     | 1                        |

| 0  | 1          | 1  | 1  | 53                     | 5.5/16                | 1.719                     |                          |

| 1  | 0          | 0  | 0  | 4B                     | 6.5/16                | 2.031                     |                          |

| 1  | 0          | 0  | 1. | 43                     | 7.5/16                | 2.344                     |                          |

| 1  | 0          | 1  | 0  | 3B                     | 8,5/16                | 2,656                     | -                        |

| 1  | 0          | 1  | 1  | 33                     | 9,5/16                | 2.969                     |                          |

| 1  | 1          | 0  | 0  | 1B                     | 12.5/16               | 3.906                     |                          |

| 1  | 1          | 0  | 1  | 13                     | 13,5/16               | 4.219                     | 1                        |

| 1  | 1          | 1  | 0  | 08                     | 14.5/16               | 4,531                     | ← MAX, value             |

| 1  | 1          | 1  | 1  | 00                     | 16/16                 | 5.000                     | ← V <sub>ref</sub> value |

#### 5.4 CGP OUTPUT

The CGP (Clock Generator Port) is equipped with both VDP (Variable Duty Pulse) generator and SG (Signal Generator) functions, and can be controlled by the PG and PH internal ports. The CGP can exist in four modes which are specified by PG<sub>0</sub> and PG<sub>1</sub>.

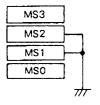

The CGP circuit employs 4029 (IC7 and IC18) as a presettable down-counter. When in VDP mode, an XOR stage is inserted prior to the preset data input to set the high level and low level intervals. The SG mode reference clock may be either 18kHz or 180kHz, the 18kHz being obtained by dividing the C2 signal (90kHz) by 5 in 4015 (IC43). The 180kHz clock is obtained by ORing the C2 signal (90kHz) with the three signals PALS, SYNC, and OTLS (all 30kHz and all mutually out of phase from each other).

The CGP output is CMOS push-pull with 4049 used as the driver. The CGP output is switched to high level when the EVACHIP is switched power on or reset, when the R (reset) command is executed in the EVAKIT, and when the clock is stopped.

And since the CGP output internal latch (PG and PH) status is unsteady when the power is first switched on, always initialize the output by program.

#### CHAPTER 6. CONNECTOR PIN TABLES

#### 6.1 CN1 PIN TABLE

Board connector

Yamaichi Electronics Co., Ltd.

FAP-34-07#2

Cable connector Yamai

Yamaichi Electronics Co., Ltd. FAS-34-17

| No. | Pin name             | Input/output | No. | Pin name        | Input/output |

|-----|----------------------|--------------|-----|-----------------|--------------|

| 1   | PAO                  | Input/output | 2   | PA <sub>1</sub> | Input/output |

| 3   | PA <sub>2</sub> /SCK | Input/output | 4   | PA3             | Input/output |

| 5   | PBO                  | Input/output | 6   | PB <sub>1</sub> | Input/output |

| 7   | PB <sub>2</sub> /SO  | Input/output | 8   | PB3/SI          | Input/output |

| 9   | PC <sub>2</sub>      | Output       | 10  | PC3             | Output       |

| 11  | CGP                  | Output       | 12  | GND             |              |

| 13  | GND                  |              | 14  | GND             | ·            |

| 15  | AD                   | Input        | 16  | GND             |              |

| 17  |                      |              | 18  |                 |              |

| 19  |                      |              | 20  |                 |              |

| 21  |                      |              | 22  |                 |              |

| 23  |                      |              | 24  |                 |              |

| 25  |                      |              | 26  |                 |              |

| 27  |                      |              | 28  |                 |              |

| 29  |                      |              | 30  |                 |              |

| 31  |                      |              | 32  |                 |              |

| 33  |                      |              | 34  |                 |              |

<sup>(1)</sup> Since GND (16) has been mounted specifically for the A/D converter, it is to be isolated from other ground lines. This analog GND is connected to digital GND at a single point on the EV-1709 board.

<sup>(2)</sup> Note that driving capacity of the port outputs (PA<sub>0</sub> to PA<sub>3</sub>, PB<sub>0</sub> to PB<sub>3</sub>, PC<sub>2</sub> to PC<sub>3</sub>, and CGP) differs from that on actual chips.

### 6.2 $\mu$ PD1709 CORRESPONDENCE TABLE (WHEN EV-1709 IS USED WITH EVAKIT-1700)

|     | μPD1709              |              | EVAKIT-1700 |         |                     |  |

|-----|----------------------|--------------|-------------|---------|---------------------|--|

| No. | Pin name             | Input/output | Board       | Pin No. | Input/output device |  |

| 1   | Sa                   | Output       | PLA         | *1      | 2SC945              |  |

| 2   | Sb                   | Output       | PLA         | *1      | 2SC945              |  |

| 3   | Sc                   | Output       | PLA         | *1      | 2SC945              |  |

| 4   | Sd                   | Output       | PLA         | *1      | 2SC945              |  |

| 5   | Se                   | Output       | PLA         | *1      | 2SC945              |  |

| 6   | Sf                   | Output       | PLA         | *1      | 2SC945              |  |

| 7   | Sg                   | Output       | PLA         | *1      | 2SC945              |  |

| 8   | GND                  |              |             |         |                     |  |

| 9   | PB <sub>0</sub>      | Input/output | EV-1709     | CN1-5   | 4503, 4519          |  |

| 10  | PB <sub>1</sub>      | Input/output | EV-1709     | CN1-6   | 4503, 4519          |  |

| 11  | PB <sub>2</sub> /SO  | Input/output | EV-1709     | CN1-7   | 4503, 4519          |  |

| 12  | PB3/SI               | Input/output | EV-1709     | CN1-8   | 4503, 4519          |  |

| 13  | AD-IN                | Input        | EV-1709     | CN1-15  | μPC271              |  |

| 14  | VDD                  |              |             |         |                     |  |

| 15  | EO                   | Output       | CPU         | CN3-9   | EVACHIP             |  |

| 16  | CE                   | Input        | CPU         | CN1-5   | EVACHIP             |  |

| 17  | ΧI                   | Input        |             |         |                     |  |

| 18  | XO                   | Output       |             |         |                     |  |

| 19  | INT                  | Input        | CPU         | CN1-7   | EVACHIP             |  |

| 20  | PSC                  | Output       | CPU         | CN3-5   | EVACHIP             |  |

| 21  | IN                   | Input        | CPU         | CN3-3   | EVACHIP             |  |

| 22  | CGP                  | Output       | EV-1709     | CN1-11  | 4049                |  |

| 23  | PC <sub>2</sub>      | Output       | EV-1709     | CN1-9   | 2SC945              |  |

| 24  | PC3                  | Output       | EV-1709     | CN1-10  | 2SC945              |  |

| 25  | D <sub>2</sub>       | Output       | PLA         | *2      | 2SC945              |  |

| 26  | D3                   | Output       | PLA         | *2      | 2SC945              |  |

| 27  | PA <sub>2</sub> /SCK | Input/output | EV-1709     | CN1-3   | EVACHIP             |  |

| 28  | PA <sub>3</sub>      | Input/output | EV-1709     | CN1-4   | EVACHIP             |  |

<sup>(1) \*1</sup> and \*2 denote connection via external driver circuit to be added. See Section 4.5 for details.

<sup>(2)</sup> Since the A/D converter GND has been included specifically for CN1—16, it is to be isolated from other ground lines. This analog GND is connected to other digital GND at a single point on the EV-1709 board.

<sup>(3)</sup> Other GND connections are to be made to the GND pins in the respective connectors.

### 6.3 μPD1709 CORRESPONDENCE TABLE (WHEN EV-1709 IS USED WITH SE-1700)

|     | μPD1709              | )            | SE-1700 |         |                     |  |

|-----|----------------------|--------------|---------|---------|---------------------|--|

| No. | Pin name             | Input/output | Board   | Pin no, | Input/output device |  |

| 1   | Sa                   | Output       | SE-1700 | CN2-2   | 2SC945              |  |

| 2   | Sb                   | Output       | SE-1700 | CN2-3   | 2SC945              |  |

| 3   | Sc                   | Output       | SE-1700 | CN2-4   | 2SC945              |  |

| 4   | Sd                   | Output       | SE-1700 | CN2-5   | 2SC945              |  |

| 5   | Se                   | Output       | SE-1700 | CN2-6   | 2SC945              |  |

| 6   | Sf                   | Output       | SE-1700 | CN2-7   | 2SC945              |  |

| 7   | Sg                   | Output       | SE-1700 | CN2-8   | 2SC945              |  |

| 8   | GND                  |              |         |         |                     |  |

| 9   | PB <sub>0</sub>      | Input/output | EV-1709 | CN1-5   | 4503, 4519          |  |

| 10  | PB <sub>1</sub>      | Input/output | EV-1709 | CN1-6   | 4503, 4519          |  |

| 11  | PB <sub>2</sub> /SO  | Input/output | EV-1709 | CN1-7   | 4503, 4519          |  |

| 12  | PB3/SI               | Input/output | EV-1709 | CN1-8   | 4503, 4519          |  |

| 13  | AD-IN                | Input        | EV-1709 | CN1-15  | μPC271              |  |

| 14  | VDD                  |              |         |         |                     |  |

| 15  | EO                   | Output       | SE-1700 | CN3-9   | EVACHIP             |  |

| 16  | CE                   | Input        | SE-1700 | CN1-5   | EVACHIP             |  |

| 17  | · XI                 | Input        |         |         |                     |  |

| 18  | XO                   | Output       |         |         |                     |  |

| 19  | INT                  | Input        | SE-1700 | CN1-7   | EVACHIP             |  |

| 20  | PSC                  | Output       | SE-1700 | CN3-5   | EVACHIP             |  |

| 21  | IN                   | Input        | SE-1700 | CN3-3   | EVACHIP             |  |

| 22  | CGP                  | Output       | EV-1709 | CN1-11  | 4049                |  |

| 23  | PC <sub>2</sub>      | Output       | EV-1709 | CN1-9   | 2SC945              |  |

| 24  | PC <sub>3</sub>      | Output       | EV-1709 | CN1-10  | 2SC945              |  |

| 25  | D <sub>2</sub>       | Output       | SE-1700 | *1      | 2SC945              |  |

| 26  | D3                   | Output       | SE-1700 | *1      | 2SC945              |  |

| 27  | PA <sub>2</sub> /SCK | Input/output | EV-1709 | CN1-3   | EVACHIP             |  |

| 28  | PA <sub>3</sub>      | Input/output | EV-1709 | CN1-4   | EVACHIP             |  |

<sup>(1) \*1</sup> denotes connection via external driver circuit to be added. See Section 4.5 for details.

<sup>(2)</sup> Since the A/D converter GND has been included specifically for CN1-16, it is to be isolated from other ground lines. This analog GND is connected to other digital GND at a single point on the EV-1709 board.

<sup>(3)</sup> Other GND connections are to be made to the GND pins in the respective connectors.

### 6.4 $\mu$ PD1716 CORRESPONDENCE TABLE (WHEN EV-1709 IS USED WITH EVAKIT-1700)

| <del> </del> | μPD1716              | 6            | EVAKIT-1700 |         |                     |  |

|--------------|----------------------|--------------|-------------|---------|---------------------|--|

| No.          | Pin name             | Input/output | Board       | Pin no. | Input/output device |  |

| 1            | PA <sub>3</sub>      | Input/output | EV-1709     | CN1-4   | EVACHIP             |  |

| 2            | PA <sub>2</sub> /SCK | Input/output | EV-1709     | CN1-3   | EVACHIP             |  |

| 3            | PA <sub>1</sub>      | Input/output | EV-1709     | CN1-2   | EVACHIP             |  |

| 4            | PA <sub>0</sub>      | Input/output | EV-1709     | CN1-1   | EVACHIP             |  |

| 5            | GND                  |              |             |         |                     |  |

| 6            | PB3/SI               | Input/output | EV-1709     | CN1-8   | 4503, 4519          |  |

| 7            | PB2/SO               | Input/output | EV-1709     | CN1-7   | 4503, 4519          |  |

| 8            | PB <sub>1</sub>      | Input/output | EV-1709     | CN1-6   | 4503, 4519          |  |

| 9            | PB <sub>0</sub>      | Input/output | EV-1709     | CN1-5   | 4503, 4519          |  |

| 10           | GND                  |              |             |         |                     |  |

| 11           | A/D                  | Input        | EV-1709     | CN1-15  | μPC271              |  |

| 12           | VDD                  |              |             |         |                     |  |

| 13           | INT                  | Input        | CPU         | CN1-7   | EVACHIP             |  |

| 14           | VDD                  |              |             |         |                     |  |

| 15           | CE                   | Input        | CPU         | CN1-5   | EVACHIP             |  |

| 16           | ΧI                   | Input        |             |         |                     |  |

| 17           | xo                   | Output       |             |         |                     |  |

| 18           | VDD                  | Output       |             |         |                     |  |

| 19           | EO <sub>1</sub>      | Output       | CPU         | CN3-9   | EVACHIP             |  |

| 20           | EO <sub>2</sub>      | Output       | CPU         | CN3-11  | EVACHIP             |  |

| 21           | GND                  |              |             |         |                     |  |

| 22           | VCOH (FM)            | Input        | CPU         | *1      | μPB553A             |  |

| 23           | VCOL (AM)            | Input        | CPU         | CN3-1   | EVACHIP             |  |

| 24           | D <sub>1</sub>       | Output       | PLA         | CN1-9   | 4050                |  |

| 25           | D <sub>2</sub>       | Output       | PLA         | CN1-10  | 4050                |  |

| 26           | D3                   | Output       | PLA         | CN111   | 4050                |  |

| 27           | PC <sub>2</sub>      | Output       | EV-1709     | CN1-9   | 2SC945              |  |

| 28           | PC3                  | Output       | EV-1709     | CN1-10  | 2SC945              |  |

<sup>(1) \*1</sup> denotes connection via external prescaler circuit to be added. See Section 4.6 for details.

<sup>(2)</sup> Since the EV-1709 PC $_2$  and PC $_3$  outputs are passed out via the 2SC945 open collector, they must be pulled up externally (by about 33k $\Omega$ ) by +5V.

<sup>(3)</sup> Since the A/D converter GND has been included specifically for CN1—16, it is to be isolated from other ground lines. This analog GND is connected to other digital GND at a single point on the EV-1709 board.

<sup>(4)</sup> Other GND connections are to be made to the GND pins in the respective connectors.

### 6.5 μPD1716 CORRESPONDENCE TABLE (WHEN EV-1709 IS USED WITH SE-1700)

|     | μPD1716              | 5            | SE-1700 |         |                     |  |

|-----|----------------------|--------------|---------|---------|---------------------|--|

| No. | Pin name             | Input/output | Board   | Pin no. | Input/output device |  |

| 1   | PA3                  | Input/output | EV-1709 | CN1-4   | EVACHIP             |  |

| 2   | PA <sub>2</sub> /SCK | Input/output | EV-1709 | . CN1-3 | EVACHIP             |  |

| 3   | PA <sub>1</sub>      | Input/output | EV-1709 | CN1-2   | EVACHIP             |  |

| 4   | PA <sub>0</sub>      | Input/output | EV-1709 | CN1-1   | EVACHIP             |  |

| 5   | GND                  |              |         |         |                     |  |

| 6   | PB3/SI               | Input/output | EV-1709 | CN1-8   | 4503, 4519          |  |

| 7   | PB2/SO               | Input/output | EV-1709 | CN1-7   | 4503, 4519          |  |

| 8   | PB <sub>1</sub>      | Input/output | EV-1709 | CN1-6   | 4503, 4519          |  |

| 9   | PB <sub>0</sub>      | Input/output | EV-1709 | CN1-5   | 4503, 4519          |  |

| 10  | GND                  |              |         |         |                     |  |

| 11  | A/D .                | Input        | EV-1709 | CN1-15  | μPC271              |  |

| 12  | VDD                  |              |         |         |                     |  |

| 13  | ĪNT                  | Input        | SE-1700 | CN1-7   | EVACHIP             |  |

| 14  | V <sub>DD</sub>      |              |         |         |                     |  |

| 15  | CE                   | Input        | SE-1700 | CN1-5   | EVACHIP             |  |

| 16  | ΧI                   | Input        |         |         |                     |  |

| 17  | XO                   | Output       |         |         |                     |  |

| 18  | VDD                  | Output       |         |         |                     |  |

| 19  | EO <sub>1</sub>      | Output       | SE-1700 | CN3-9   | EVACHIP             |  |

| 20  | EO <sub>2</sub>      | Output       | SE-1700 | CN3-11  | EVACHIP             |  |

| 21  | GND                  |              |         |         |                     |  |

| 22  | VCOH (FM)            | Input        | SE-1700 | *1      | μPB553A             |  |

| 23  | VCOL (AM)            | Input        | SE-1700 | CN3-1   | EVACHIP             |  |

| 24  | D <sub>1</sub>       | Output       | SE-1700 | CN2-9   | 4050                |  |

| 25  | D <sub>2</sub>       | Output       | SE-1700 | CN2-10  | 4050                |  |

| 26  | D3                   | Output       | SE-1700 | CN2-11  | 4050                |  |

| 27  | PC <sub>2</sub>      | Output       | EV-1709 | CN1-9   | 2SC945              |  |

| 28  | PC3                  | Output       | EV-1709 | CN1-10  | 2SC945              |  |

<sup>(1) \*1</sup> denotes connection via external prescaler circuit to be added. See Section 4.6 for details.

<sup>(2)</sup> Since the EV-1709 PC<sub>2</sub> and PC<sub>3</sub> outputs are passed out via the 2SC945 open collector, they must be pulled up externally (by about  $33k\Omega$ ) by +5V.

<sup>(3)</sup> Since the A/D converter GND has been included specifically for CN1-16, it is to be isolated from other ground lines. This analog GND is connected to other digital GND at a single point on the EV-1709 board.

<sup>(4)</sup> Other GND connections are to be made to the GND pins in the respective connectors.

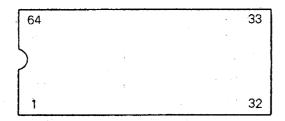

#### APPENDIX I P1 AND P2 PIN TABLES

#### P1 pin table

| ······································ | · · · · · · · · · · · · · · · · · · · | ponent mounting side) |

|----------------------------------------|---------------------------------------|-----------------------|

| 1                                      | 1                                     | GND                   |

| 2                                      | 3                                     | +5V                   |

| 3                                      | 5                                     | +5V                   |

| 4                                      | 7                                     | +12V                  |

| 5                                      | 9                                     |                       |

| 6                                      | 11                                    | GND                   |

| 7                                      | 13                                    | BCLK *                |

| 8                                      | 15                                    | BPRN *                |

| 9                                      | 17                                    | BUSY *                |

| 10                                     | 19                                    | MEMR *                |

| 11                                     | 21                                    | IOR *                 |

| 12                                     | 23                                    | XACK *                |

| 13                                     | 25                                    |                       |

| 14                                     | 27                                    | BHEN *                |

| 15                                     | 29                                    | CBRQ *                |

| 16                                     | 31                                    | CCLK *                |

| 17                                     | 33                                    | ĪNTA *                |

| 18                                     | 35                                    | INT6 *                |

| 19                                     | 37                                    | INT4 *                |

| 20                                     | 39                                    | ĪNT2 •                |

| 21                                     | 41                                    | INTO *                |

| 22                                     | 43                                    | ADRE *                |

| 23                                     | 45                                    | ADRC *                |

| 24                                     | 47                                    | ADRA *                |

| 25                                     | 49                                    | ADR8 *                |

| 26                                     | 51                                    | ADR6 *                |

| 27                                     | 53                                    | ADR4 *                |

| 28                                     | 55                                    | ADR2 *                |

| 29                                     | 57                                    | ADRO *                |

| 30                                     | 59                                    |                       |

| 31                                     | 61                                    |                       |

| 32                                     | 63                                    |                       |

| 33                                     | 65                                    |                       |

| 34                                     | 67                                    | DB6 *                 |

| 35                                     | 69                                    | DB4 *                 |

| 36                                     | 71                                    | DB2 *                 |

| 37                                     | 73                                    | DB0 *                 |

| 38                                     | 75                                    | GND                   |

| 39                                     | 77                                    | 3.10                  |

|                                        |                                       | _12\/_*               |

| 40                                     | 79                                    | =12 V                 |

| 41                                     | 81                                    | +5V                   |

| 42                                     | 83                                    | +5V                   |

| 43                                     | 85                                    | GND                   |

| P1 | (soldering side) |   |

|----|------------------|---|

| 2  | GND              |   |

| 4  | +5V              |   |

| 6  | +5V              |   |

| 8  | +12V             |   |

| 10 |                  |   |

| 12 | GND              |   |

| 14 | INIT             | * |

| 16 | BPRO             | * |

| 18 | BREQ             | * |

| 20 | MWTC             | * |

| 22 | IOWC             | * |

| 24 | INH1             | * |

| 26 | INH2             | * |

| 28 | AD10             | * |

| 30 | AD11             | * |

| 32 | AD12             | * |

| 34 | AD13             | * |

| 36 | INT7             | • |

| 38 | INT5             | * |

| 40 | ĪNT3             | + |

| 42 | INT1             | * |

| 44 | ADRF             | • |

| 46 | ADRD             | * |

| 48 | ADRB             | * |

| 50 | ADR9             | * |

| 52 | ADR7             | * |

| 54 | ADR5             | * |

| 56 | ADR3             | + |

| 58 | ADR1             | * |

| 60 |                  |   |

| 62 |                  |   |

| 64 |                  |   |

| 66 |                  |   |

| 68 | DB7              | * |

| 70 | DB5              | * |

| 72 | DB3              | * |

| 74 | DB1              | * |

| 76 | GND              | 7 |

| 78 |                  |   |

| 80 | -12V             | * |

| 82 | +5V              |   |

| 84 | +5∨              |   |

| 86 | GND              |   |

| L  |                  |   |

Note: Signals marked by an asterisk are not used by EV-1709.

#### P2 pin table

|    | P2 (component mounting side) |       |          |  |  |  |  |  |

|----|------------------------------|-------|----------|--|--|--|--|--|

| 1  | 1                            | GND   |          |  |  |  |  |  |

| 2  | 3                            | MS0   |          |  |  |  |  |  |

| 3  | 5                            | MS2   |          |  |  |  |  |  |

| 4  | 7                            | C2    | (φ2)     |  |  |  |  |  |

| 5  | 9                            | PALS  | (M1·φ1)  |  |  |  |  |  |

| 6  | 11                           | PDATA | .1       |  |  |  |  |  |

| 7  | 13                           | PDATA | /3       |  |  |  |  |  |

| 8  | 15                           | OTLS  | (M3•φ1)  |  |  |  |  |  |

| 9  | 17                           | SEGCU | T *      |  |  |  |  |  |

| 10 | 19                           | SEGSE | L3 *     |  |  |  |  |  |

| 11 | 21                           | GND   | (analog) |  |  |  |  |  |

| 12 | 23                           | +15V  |          |  |  |  |  |  |

| 13 | 25                           | -15V  |          |  |  |  |  |  |

| 14 | 27                           | LCD   | *        |  |  |  |  |  |

| 15 | 29                           | EVARE | S        |  |  |  |  |  |

| 16 | 31                           | AD1   |          |  |  |  |  |  |

| 17 | 33                           | AD3   |          |  |  |  |  |  |

| 18 | 35                           | AD5   | *        |  |  |  |  |  |

| 19 | 37                           | AD7   | *        |  |  |  |  |  |

| 20 | 39                           | AD9   | *        |  |  |  |  |  |

| 21 | 41                           | AD11  | *        |  |  |  |  |  |

| 22 | 43                           | AD13  | *        |  |  |  |  |  |

| 23 | 45                           | AD15  | *        |  |  |  |  |  |

| 24 | 47                           | MO1   |          |  |  |  |  |  |

| 25 | 49                           | МОЗ   |          |  |  |  |  |  |

| 26 | 51                           | DIG1  | *        |  |  |  |  |  |

| 27 | 53                           | DIG3  | *        |  |  |  |  |  |

| 28 | 55                           | LCDG0 | +        |  |  |  |  |  |

| 29 | 57                           | LCDG2 | #        |  |  |  |  |  |

| 30 | 59                           | BRKAC | K        |  |  |  |  |  |

|    |                              |       |          |  |  |  |  |  |

| F  | 22 (soldering side) |

|----|---------------------|

| 2  | GND                 |

| 4  | MS1                 |

| 6  | MS3                 |

| 8  | ADIN (M2)           |

| 10 | PDATA0              |

| 12 | PDATA2              |

| 14 | STLS (M1·42)        |

| 16 | SGLS (M3·ø1)        |

| 18 | SEGSEL2 *           |

| 20 | SYNC (M2•φ1)        |

| 22 | GND (analog)        |

| 24 | +15V                |

| 26 | -15V                |

| 28 | JDG                 |

| 30 | AD0                 |

| 32 | AD2                 |

| 34 | AD4                 |

| 36 | AD6 *               |

| 38 | AD8 *               |

| 40 | AD10 *              |

| 42 | AD12 *              |

| 44 | AD14 *              |

| 46 | MO0                 |

| 48 | MO2                 |

| 50 | DIG0 *              |

| 52 | DIG2 *              |

| 54 | DIGCUT *            |

| 56 | LCDG1 •             |

| 58 | LCDG3 *             |

| 60 | CE *                |

Note: Since the P2 bus is specifically for use by EV-1709, it is not compatible with the IEEE 796 bus.

Signals marked by an asterisk are not used by EV-1709.

#### APPENDIX II µPD1700B PIN CONNECTION DIAGRAM

| Pin no. | Pin name         | 1/0 | Pin no. | Pin name            | 1/0 |

|---------|------------------|-----|---------|---------------------|-----|

| 1       | CE               |     | 33      | GND                 |     |

| 2       | SD               | 1   | 34      | PDATA3              | 1/0 |

| 3 .     | INT              |     | 35.     | PDATA2              | 1/0 |

| 4       | DIG CUT          | 0   | 36      | PDATA <sub>1</sub>  | 1/0 |

| 5       | DIG <sub>3</sub> | 0   | 37      | PDATAO              | 1/0 |

| 6       | DIG <sub>2</sub> | 0   | 38      | PALS                | 0   |

| 7       | DIG <sub>1</sub> | 0   | 39      | STLS                | 0   |

| 8       | DIGO             | 0   | 40      | OTLS                | 0   |

| 9       | К3               | 1   | 41      | PA <sub>3</sub>     | 1/0 |

| 10      | K <sub>2</sub>   | 1   | 42      | PA <sub>2</sub>     | 1/0 |

| 11      | K <sub>1</sub>   | 1   | 43      | PA <sub>1</sub>     | 1/0 |

| 12      | K <sub>0</sub>   | 1   | 44      | PA <sub>0</sub>     | 1/0 |

| 13      | BRKACK           | 0   | 45      | SEGSEL <sub>2</sub> | 0   |

| 14      | RWE              | 0   | 46      | SEGSEL3             | 0   |

| 15      | SYNC             | 0   | 47      | SGLS                | 0   |

| 16      | C <sub>2</sub>   | 0   | 48      | SEG CUT             | 0   |

| 17      | ADIN             | 0   | 49      | AD <sub>0</sub>     | 1/0 |

| 18      | STACK3/1         | 1   | 50      | AD <sub>1</sub>     | 1/0 |

| 19 :    | RAMRÆ            | 1   | 51      | AD <sub>2</sub>     | 1/0 |

| 20      | RUN/BRK          | ı   | 52      | AD3                 | 1/0 |

| 21      | RES              | 1   | 53      | AD4                 | 1/0 |

| 22      | CKSEL            | ı   | 54      | AD <sub>5</sub>     | 1/0 |

| 23      | DEVSEL           | ı   | 55      | AD <sub>6</sub>     | 1/0 |

| 24      | fy               | 0   | 56      | AD <sub>7</sub>     | 1/0 |

| 25      | × <sub>1</sub>   | 1   | 57      | AD8                 | 1/0 |

| 26      | x <sub>0</sub>   | 0   | 58      | AD9                 | 1/0 |

| 27      | PSC              | 0   | 59      | AD10                | 1/0 |

| 28      | FM               | ı   | 60      | AD11                | 1/0 |

| 29      | AM               | 1   | 61      | AD <sub>12</sub>    | 1/0 |

| 30      | EO <sub>1</sub>  | 0   | 62      | AD <sub>13</sub>    | 1/0 |

| 31      | EO <sub>2</sub>  | 0   | 63      | AD <sub>14</sub>    | 1/0 |

| 32      | VDD              |     | 64      | AD <sub>15</sub>    | 1/0 |

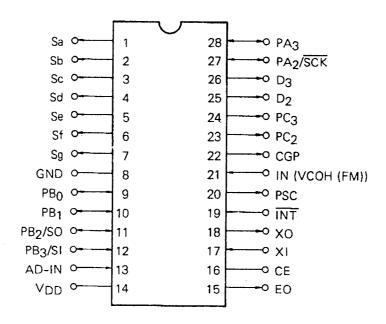

#### APPENDIX III µPD1709 PIN CONNECTION DIAGRAM

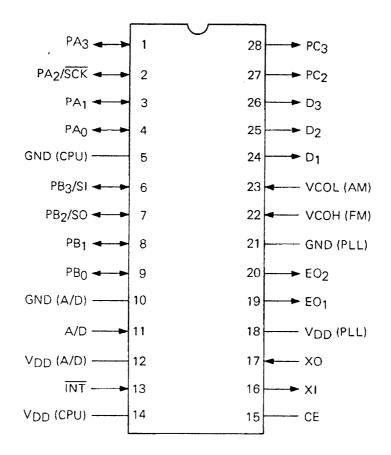

#### APPENDIX IV $\mu$ PD1716 PIN CONNECTION DIAGRAM

#### APPENDIX V $\mu$ PD1709 INSTRUCTION SET

|                 | \     | Ь                                 | 15 b | 14 | 4 00                               |                        | 01   |    | 10 |                              |    | 11               |      |    |   |

|-----------------|-------|-----------------------------------|------|----|------------------------------------|------------------------|------|----|----|------------------------------|----|------------------|------|----|---|

| b <sub>13</sub> | b12 l | b <sub>11</sub> b <sub>10</sub> 0 |      | 1  |                                    | 2                      |      |    | 3  |                              |    |                  |      |    |   |

| 0               | 0     | 0                                 | 0    | 0  | NOP<br>SIO                         | N                      |      |    |    | DIG                          | r  |                  | ST   | М, | r |

| 0               | 0     | 0                                 | 1    | 1  | SPB<br>SS<br>BANK1<br>EI<br>STC    | P, N<br>N1             | ORI  | Μ, | ı  | SEG                          | Dį | -1, r            | MVRS | Μ, | r |

| 0               | 0     | 1                                 | 0    | 2  | JMP                                | ADDR<br>(page 1)       | MVI  | М, | I  | OUT                          | Ρ, | r                | IN   | r, | Р |

| 0               | 0     | 1                                 | 1    | 3  | PPB<br>RS<br>BANKO<br>DI<br>RSC    | P, N<br>N1             | ANI  | М, | l  | CKSTP                        |    |                  | MVRD | r, | М |

| 0               | 1     | 0                                 | 0    | 4  | RT                                 |                        | AI   | Μ, | I  | MVSR                         | М1 | , M <sub>2</sub> | AD   | r, | М |

| 0               | 1     | 0                                 | 1    | 5  | RTS                                |                        | SI   | Μ, | 1  | EXL                          | r, | М                | SU   | r, | M |

| 0               | 1     | 1                                 | 0    | 6  | JMP                                | ADDR<br>(page 0)       | AIC  | Μ, | 1  | LD                           | r, | М                | AC   | r, | М |

| 0               | 1     | 1                                 | 1    | 7  | CAL                                | ADDR<br>(page 0)       | SIB  | Μ, | 1  |                              | ·  |                  | SB   | r, | М |

| 1               | 0     | 0                                 | 0    | 8  | SBKO<br>TPF<br>TSF<br>TCEF<br>TITF | P, N<br>N <sub>2</sub> | AIN  | M, | ı  | TSET<br>TSEF<br>TADT<br>TADF |    |                  | ADN  | r, | М |

| 1               | 0     | 0                                 | 1    | 9  | SBK1<br>TPT<br>TST<br>TCET<br>TITT | P, N<br>N <sub>2</sub> | SIN  | Μ, | ı  | TTM<br>TIP                   |    |                  | SUN  | r, | M |

| 1               | 0     | 1                                 | 0    | А  | TMF                                | M, N                   | AICN | Μ, | ļ  | TUL                          |    |                  | ACN  | r, | М |

| 1               | 0     | 1                                 | 1    | В  | TMT                                | M, N                   | SIBN | М, |    | PLL                          | М, | r                | SBN  | r, | М |

| 1               | 1     | 0                                 | 0    | С  | SLTI                               | М, І                   | AIS  | Μ, | l  | SLT                          | r, | M                | ADS  | r, | М |

| 1               | 1     | 0                                 | 1    | D  | SGEI                               | M, I                   | SIS  | Μ, | ł  | SGE                          | r, | М                | SUS  | r, | М |