Author: Jozef Froniewski Date: September 3, 2015

#### **Metal detection applications**

Metal detection is finding increasing importance for proximity detection, security, industrial automation, locators, and treasure finders. The design presented is a pulse induction (PI), single coil design implemented with a single GreenPAK4 IC. PI designs have the advantage of tolerance to ground effects, and work even when submerged in water. It also performs well on non-ferrous metals. Presented is a new circuit design example which uses an analog comparator, digital timing vernier, and digital averaging to provide an LED bar display and audio indication. A sample video of this circuit in operation can be found at https://youtu.be/04K8UqhMfbY

### **Pulse Induction (PI) basics**

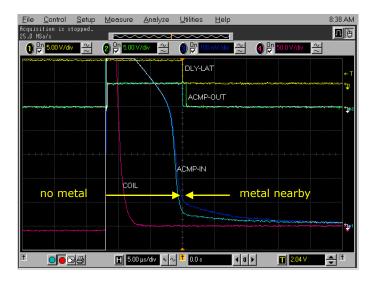

An electromagnetic field is produced by building up a current in a single search coil, and then switching off that current to allow that field to collapse. As the field collapses, it induces a voltage back into the (appearing as high voltage undershoot or flyback) and also into objects near the coil. Ferrous or non-ferrous objects will have eddy currents induced in them producing a small magnetic field which then opposes the decay of the original field. So when the search coil is near metal, the magnetic field around the search coil decays differently, as does the voltage that was induced back in the search coil. The tail end of this decay voltage is what is analyzed by this circuit. Fig. 1 shows the change in coil voltage when metal is brought near.

Fig 1a. Voltage decay with metal nearby

### **New Circuit Implementation**

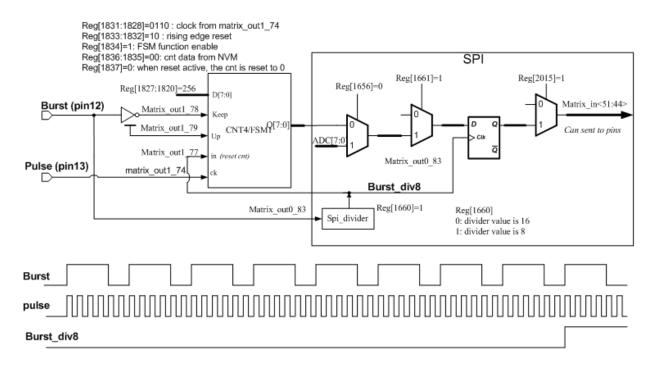

Typical PI designs incorporate a high gain op amp to amplify the last mV of decay signal, then try to deal with offset, saturation, noise, bandwidth, and filtering issues. The design shown in this app note is a new circuit that does not use a high gain op amp. The circuit uses an analog comparator to compare the decay voltage against a fixed threshold of 50-100mV. The resulting timing edge (ACMPOUT) is compared against a fixed delay time (DLY-LAT) from when the coil was deenergized. Since the change in delay is very small, a timing vernier is used with a 4nS resolution.

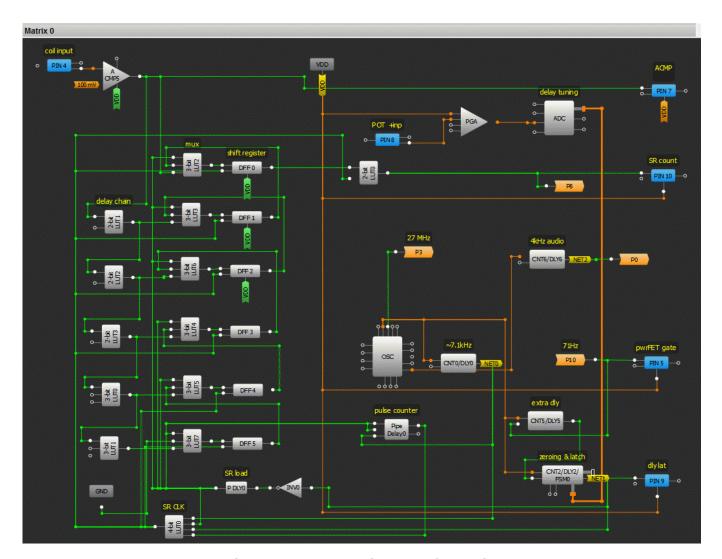

The timing vernier is constructed with a delay chain that propagates the decayed coil voltage logic "0" past the inputs of a parallel input shift register. The schematic is shown in Fig. 2a.

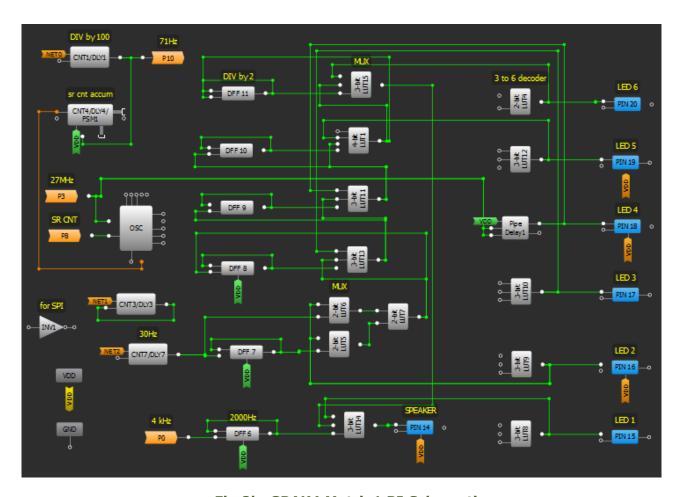

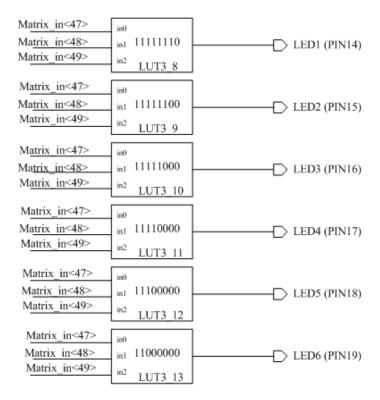

The tuning potentiometer-ADC-DLY2 path generates the (dly lat) signal which latches the register inputs. So the longer the decay(closer to metal object), the more 1's will still remain to get latched. The contents of the shift register then get shifted out(by SR CLK) to a counter(CNT4) in Fig. 2b, which accumulates how many 1's. This cycle continues to repeat. Counter CNT4 binary output bits 0,1,2 are ignored, while bits 3,4,5 are sent to a 3 to 8(actually 6 in this case) line decoder. This results in digital averaging to reduce the effects of voltage and timing noise. These averaged/decoded bits drive an LED bar graph display, and also go to a muxed input divider chain to generate audible beeps. The closer a metal object, the faster the beeps will sound. The beeps are generated by a small piezo transducer driven directly from the GreenPAK output pin. 2kHz was chosen because that frequency was sufficiently loud with only 5V drive signal.

**Other circuitry**

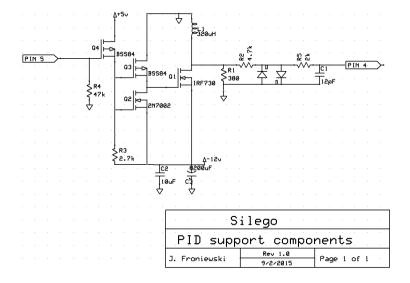

The coil drive requires a high voltage MOSFET connected to a 12V power supply. In this case I have chosen to leave the analog comparator input ground based, so the coil will actually be driven to the -12V connection. This way the induced coil voltage at shutoff will go positive, and the decay voltage will fall from there down to GND. The vertical scale units in Fig 1. are correct... the coil voltage does swing up to 400V, and is the reason for using a high voltage NMOS MOSFET for Q1. The diodes clamp the input to the ACMP within the region of interest. The remaining circuitry is simply level shifting from +5V logic levels down to -12V gate drive level as shown in Fig 2c.

The potentiometer at pin 8 could be any voltage divider between 0-5V supply so that it can provide a tuning voltage to the AD converter which subsequently tunes the metal detector.

Fig 1b. Example search coil

### Sensing coil

The coil in this example was wound from speaker wire, a total of 34 turns and measured 320uH inductance. The insulation is kept on to reduce the self capacitance of the coil. Of course smaller coils and different shapes can be used, such as oblong for a security wand. When different coil inductance is designed in, it may be necessary to adjust the DLY5 delay setting to reasonably center dly lat signal. The coil windings should be held securely in place or embedded in epoxy to eliminate any vibration, which causes loss of efficiency. The coaxial cable is RG62, also having low capacitance. Another benefit of using an NMOS for Q1 is that its parasitic capacitance is lower than an equivalent PMOS. All this consideration to minimizing parasitic capacitance increases the amount of remaining signal we are trying to detect.

Resistor R1 in Fig 2c is a damping resistor and determined empirically so that the coil ACMP input won't have undershoot.

#### **Schematic considerations**

Some connections in this design required the use of extended features not readily available in the graphic schematic editor. It really amounts to swapping of available matrix connections at the programming bit level.

In this case the reward was fitting the design into a single GreenPAK4 IC. Specific for this design, getting the parallel outputs from CNT4 required using the SPI block for its access. The SPI outputs are shared with OSC connections in Matrix 1, and those are used in this design to connect to the 3-to-8(6) decoder so that the digital average can drive the LED bar and audio.

Fig 2a. GPAK4 Matrix0 PI schematic

Fig 2b. GPAK4 Matrix1 PI Schematic

Fig 2c. Level shift, coil, and support components

Also note that within the 3-to-6 decoder 2-bit LUT4 and Pipe delay1 are used instead of the traditional 3-input logic gate. This was done because we ran out of 3-input logic gates, and were able to use the other blocks to perform the same logic function for their simplified requirements. Programming at the bit level was accomplished through the emulator.

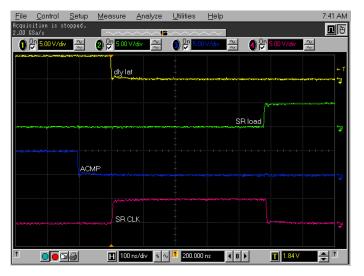

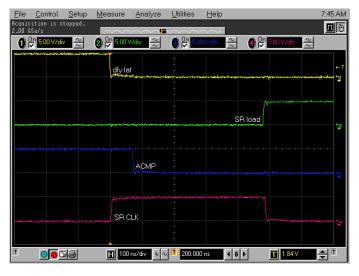

Fig 3a. Vernier timing (no metal)

Fig 3b. Vernier timing (near metal)

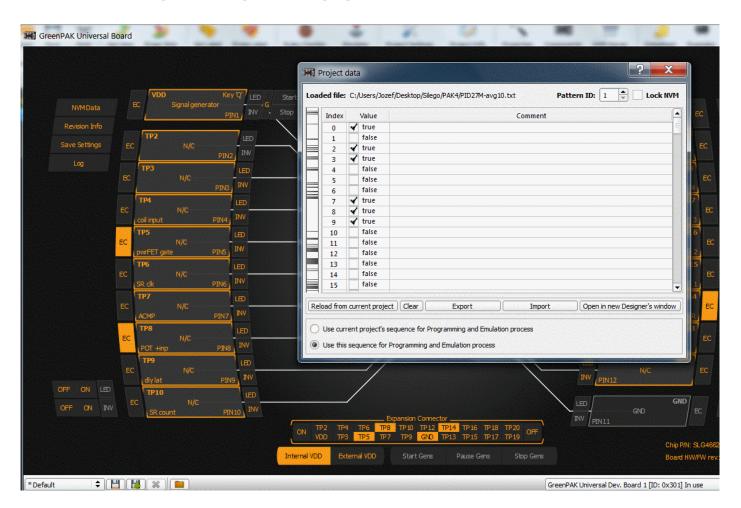

The existing schematic will load its NVM bits into the editable window in the emulator as shown in Fig 5d. Once the bits have been modified, the .txt file can be exported and saved, or program the GreenPAK4 permanently right then. Within the support files for this application note, a fully complete and working .txt file is supplied and ready for IC programming.

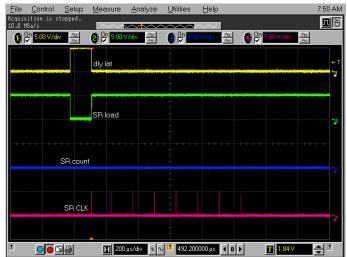

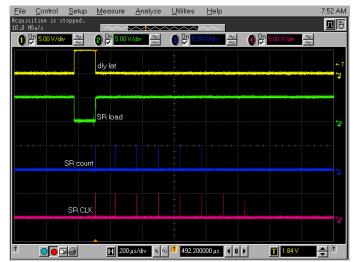

Fig 4a. Shift Register timing (no metal)

Fig 4b. Shift Register timing (near metal)

Figure 5a. FSM to Matrix and Matrix to Pin

Figure 5b. Matrix to Pin

| SPI_OUT<7:0>  |      |      |      |      |      |      |      |      |               |

|---------------|------|------|------|------|------|------|------|------|---------------|

|               |      |      |      |      |      |      |      |      |               |

| decimal value | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | led light num |

| 8             |      |      | 0    | 0    | 1    | 0    | 0    | 0    | 1             |

| 16            |      |      | 0    | 1    | 0    | 0    | 0    | 0    | 2             |

| 24            |      |      | 0    | 1    | 1    | 0    | 0    | 0    | 3             |

| 32            |      |      | 1    | 0    | 0    | 0    | 0    | 0    | 4             |

| 40            |      |      | 1    | 0    | 1    | 0    | 0    | 0    | 5             |

| 48            |      |      | 1    | 1    | 0    | 0    | 0    | 0    | 6             |

Figure 5c. Digital averaging from SPI connections to CNT4

Figure 5d. NVM bit programming in emulation window

#### Conclusion

The design presented successfully demonstrated pulse induction (PI) single coil metal detection using a single GreenPAK4 IC. The new circuit design used the circuitry

available within the IC, and also highlights the use of extended connectivity within GreenPAK4. Because of the flexibility of the GreenPAK family, variants of this design are possible such as smaller search coil, different indicators, more sensitivity, etc.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.