Author: David Riedell Date: March 14, 2017

## Introduction

In this app note we will describe how to generate a one-shot pulse that increases or decreases in length by a set amount every time it is triggered. This may be a useful technique for a medical application for dosage distribution, or for an LED driving circuit.

This design allows the user to determine whether they want an incremented pulse or a nonincremented pulse, i.e. a pulse of the same length as the previous pulse.

# **Implementation**

The way we implemented this design is with a one-shot pulse and a separate counter of the same length. Rather than running continuously, the counter (CNT4/DLY4) is clocked at specific times to create the correct offset from the one-shot pulse (CNT3/DLY3). The output pulse on Pin8 is set HIGH when the counter outputs HIGH, and is reset LOW when the one-shot finishes. Depending on whether we want to increment or decrement the output one-shot pulse length, we either add a clock or skip a clock into the counter. This procedure is explained further in Section 3.

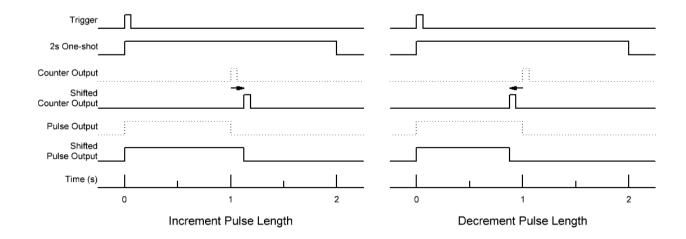

Figure 1 is a timing diagram that shows an overview of how the design works for both incrementing and decrementing. When an incrementing trigger is received, the 2sec one-shot pulse begins, and the pulse ends when the counter outputs HIGH. To increment the pulse length, we shift the counter's output rightward by generating an additional clock edge for the counter. To decrement the pulse length, we shift the counter's output leftwards by skipping a clock edge. If we want a pulse the same length as the previous pulse, we don't shift the counter's output at all.

# **GreenPAK Design**

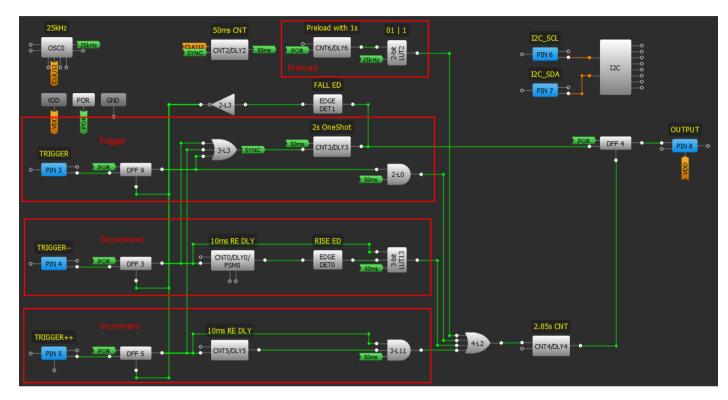

In Figure 2, CNT3/DLY3 is the 2sec one-shot pulse generator and CNT4/DLY4 is the counter. The TRIGGER, TRIGGER--, and TRIGGER++ pins are each connected to their own D-Flip Flop, which are used as latches to indicate which type of trigger was received. The output of the DFFs are OR'd together and used as the input of CNT3/DLY3. This means that if any of the pins goes HIGH, the 2sec one-shot will be triggered. The 3 DFFs are all reset at the falling edge of the 2sec one-shot.

**Figure 1. Timing Diagram**

Figure 2. GreenPAK Design

We decided that we wanted our increments to be 50ms long. We used CNT2/DLY2 to create a pulse every 50ms, and used that 20Hz signal to clock both CNT3/DLY3 and CNT4/DLY4 (through several LUTs). We reset CNT2/DLY2 with a rising edge select based on SYNC, which is the output of 3-bit LUT3. This way we know our counter will be consistently reset when one of the pins goes HIGH.

If Pin3 goes HIGH it means we want a pulse that has the same width as the last pulse, without any incrementing or decrementing. We used DFF9 to latch the input from Pin3. The OR gate 3-bit LUT3 is used to trigger the 2sec one-shot, which clocks DFF4. At this point, Pin8 (OUTPUT) is HIGH. The AND gate 2-bit LUT0 is used to gate the 50ms pulses to clock CNT4/DLY4, which has an inverted output. When CNT4/DLY4 reaches 40, its output will drop LOW for one clock cycle, which will reset DFF4 and cause Pin8 to drop LOW once again.

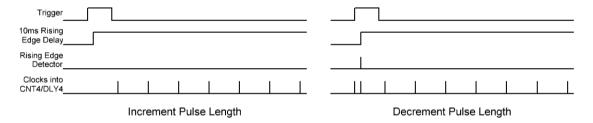

If Pin4 goes HIGH it means we want a decrementing pulse that is 50ms shorter than the previous pulse. In this case we use DFF3 to latch the input from Pin4. A 10ms rising edge delay (CNT0/DLY0) and a rising edge detector are then used to indicate when 10ms have passed since Pin4 went HIGH. The pulse coming out of the rising edge detector is used to clock CNT4/DLY4 asynchronously one additional time, which means that the counter will reach completion exactly 50ms early, causing the output pulse to be 50ms shorter.

Finally, if Pin5 goes HIGH it means we want an incrementing pulse that is 50ms longer than the previous pulse. DFF5 latches the input from Pin5, and an additional 10ms rising edge delay is used to detect when 10ms has elapsed since the pin went HIGH. In this case, however, the 10ms delay is used to gate the clocks into CNT4/DFF4 rather than adding an additional pulse.

These incremented and decremented pulses stack on top of each other. For instance, if you start with a pulse that is 1 second long and increment it twice, the resulting output one-shot pulses will be 1.05 sec and 1.10 sec, respectively. This is illustrated by Table 1 below.

|           | First<br>trigger | Second<br>Trigger | Third<br>Trigger |

|-----------|------------------|-------------------|------------------|

| TRIGGER++ | 1.00             | 1.05              | 1.10             |

| TRIGGER   | 1.00             | 0.95              | 0.90             |

| TRIGGER   | 1.00             | 1.00              | 1.00             |

**Table 1. Pulse lengths**

Rather than starting with an output pulse that is 2 seconds wide, we decided to pre-load the system with a 1sec output pulse.

This is achieved by using CNT6/DLY6, 2-bit LUT2, and 4-bit LUT2 to quickly clock CNT4/DLY4 several times immediately after the chip is powered on. 2-bit LUT2 is used to gate the 25kHz oscillator output using CNT6/DLY6, which is configured as a rising edge delay. When the POR (power on reset) signal goes HIGH, 2-bit LUT2 allows several 25kHz pulses to pass through itself and 4-bit LUT2, until CNT6/DLY6 goes HIGH. This effectively shifts the output of the CNT4/DLY4 leftward by 1 second, so that the first triggered pulse will be 1 second long. The waveforms for this procedure are shown in Figure 4, where:

- Channel 1 (yellow): POR

- Channel 2 (blue): output of CNT6/DLY6

- Channel 3 (pink): output of 2-bit LUT2

Figure 3. Incrementing vs Decrementing technique

Figure 4. Preload the counter with 1sec

## Conclusion

In this app note we used an SLG46536V GreenPAK device to create a one-shot that can be incremented or decremented by a set amount of time depending on which input pins is triggered. This design could be useful in a BLAH scenario. The SLG46536V also has I2C capability, meaning

that the user has the ability to change functionality on the fly with a few I2C commands.

This design leaves several blocks unused, including several look up tables, GPIOs, ACMPs, DFFs, and a handful of other blocks, which means that a designer could easily add more functionality into this project to save room on their board.

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.