Renesas RA Family

# 16-Bit Analog-to-Digital Converter Operation for RA6T2

# Introduction

This application note describes the operation of the Analog-to-Digital Converter (ADC) on the RA6T2, with a focus on the conversion methods that enable 16-bit depth resolution. The note begins with a brief background on oversampling techniques to increase A/D resolution, then dives into the specifics of the oversampling features built into the ADC on the RA6T2. The application note covers the key configurations for capturing data in 16-bit depth mode and details the important functions for ensuring proper operation.

The sample code folder provided with this application note contains 2 projects: one project demonstrates operating the ADC with 16-bit depth in Oversampling Mode, and the other project demonstrates operating the ADC with 12-bit depth in SAR Mode for a performance comparison.

## Target Device

RA6T2

# **Required Resources**

To build and run the example projects accompanying this application note, you will need the following:

#### Development tools and software:

- e<sup>2</sup> studio IDE, version 2024-07 (24.7.0)

- RA Family Flexible Software package (FSP) v5.5.0

- J-Link RTT Viewer, version 7.98b

The FSP and e<sup>2</sup> studio are bundled in a downloadable platform installer available on Renesas' website at: <u>renesas.com/ra/fsp</u>

#### Hardware:

- RA6T2 (240MHz Arm® Cortex®-M33 TrustZone®, High Real-time Engine for Motor Control)

- MCK-RA6T2 (<u>RTK0EMA270S00020BJ Renesas Flexible Motor Control Kit for RA6T2 MCU Group</u>)

- USB-C to USB-A cable

- Host PC running Windows<sup>®</sup> 10

## **Prerequisites and Intended Audience**

This application note assumes you have some experience with the Renesas e<sup>2</sup> studio IDE and RA Family Flexible Software Package (FSP). Before you perform the procedures in this application note, follow the procedure in the *FSP User Manual* to build and run the Blinky project. Doing so enables you to become familiar with e<sup>2</sup> studio and the FSP and validates that the debug connection to your board functions properly. Additionally, this application note assumes that you have some theoretical background on analog topics relating to A/D conversion. The intended audience are users who want to develop applications with 16-bit ADC module using the RA6T2.

# Contents

| 1. Overview of A/D Converters                             | 4  |

|-----------------------------------------------------------|----|

| 1.1 Characterizing an A/D Converter                       | 4  |

| 1.2 Analog Input Types                                    | 4  |

| 1.2.1 Single-Ended Input                                  | 4  |

| 1.2.2 Differential Input                                  | 4  |

| 1.3 Types of ADCs                                         | 4  |

| 1.3.1 Successive Approximation Register ADC               | 5  |

| 1.3.1.1 Key Features and Limitations                      |    |

| 1.3.2 Delta-Sigma Modulation ADC                          | 6  |

| 1.3.2.1 Key Features and Limitations                      | 6  |

| 1.3.3 Additional ADCs                                     | 6  |

| 1.3.4 Noise-Shaping Successive Approximation Register ADC | 7  |

| 1.4 Increasing Resolution                                 | 7  |

| 1.4.1 Oversampling and Noise-Shaping of NS-SAR ADCs       | 7  |

| 1.4.2 Use Cases                                           | 7  |

| 1.4.3 Additional Renesas ADCs                             | 8  |

| 2. Configuring the RA6T2 ADC Module                       | 8  |

| 2.1 ADC Specifications                                    |    |

| 2.1.1 Analog Channels                                     |    |

| 2.1.2 Virtual Channels                                    |    |

| 2.1.3 Scan Groups                                         |    |

| 2.1.4 Analog Input Mode                                   |    |

| 2.1.4.1 Single-Ended Input                                |    |

| 2.1.4.2 Differential Input                                |    |

| 2.1.5 Conversion Methods                                  |    |

| 2.1.5.1 SAR Mode                                          | 12 |

| 2.1.5.2 Oversampling Mode                                 | 13 |

| 2.1.5.3 Hybrid Mode                                       | 13 |

| 2.1.6 Scan Modes                                          | 14 |

| 2.1.6.1 Single Scan Mode                                  | 14 |

| 2.1.6.2 Continuous Scan Mode                              | 14 |

| 2.1.6.3 Background Continuous Scan Mode                   | 15 |

| 2.1.7 A/D Scan Start Conditions                           | 15 |

| 2.1.7.1 ELC Trigger Scan Start                            | 15 |

| 2.1.7.2 GPT Trigger Scan Start                            | 16 |

| 2.1.7.3 External Trigger Scan Start                       | 16 |

| 2.1.8 Interrupt Sources                                   | 17 |

| 2.1.9 Self-Calibration Function                           | 20 |

| 2.1.9.1 Conditions When Self-Calibration is Required      | 20 |

| 2.1.9.2 Self-Calibration Operation and Procedure               | 20 |

|----------------------------------------------------------------|----|

| 2.1.9.3 Self-Calibration Restrictions                          | 21 |

| 2.2 Operating ADC with 16-bit Depth                            | 22 |

| 2.2.1 Oversampling Mode – Single Scan Mode                     | 23 |

| 2.2.2 Oversampling Mode – Continuous Scan Mode                 | 24 |

| 2.2.3 Hybrid Mode – Single Scan Mode                           | 25 |

| 2.2.4 Hybrid Mode – Continuous Scan Mode                       | 26 |

| 2.2.5 Hybrid Mode – Background Continuous Scan Mode            | 27 |

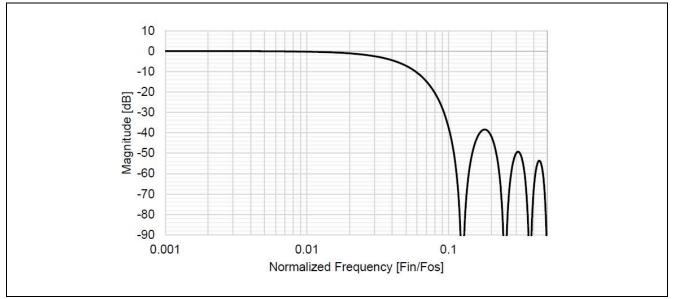

| 2.2.6 Digital Filter Function                                  | 28 |

| 2.2.6.1 Configuration and Characteristics                      | 28 |

| 2.2.6.2 Operating the Digital Filter                           | 29 |

| 2.3 ADC Timing Considerations                                  | 30 |

| 2.3.1 Sampling Rate Calculation                                | 30 |

| 2.3.1.1 Note on 16-bit Conversion Methods                      | 31 |

| 2.3.2 Clock Rate                                               | 32 |

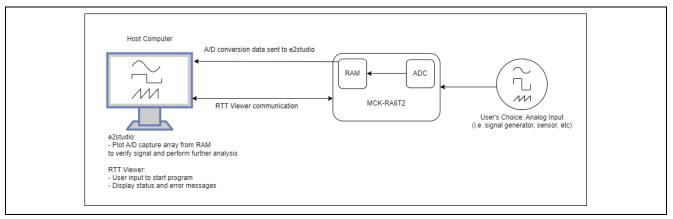

| 3. Introduction to the Application Project                     | 32 |

| 3.1 Project Statement                                          |    |

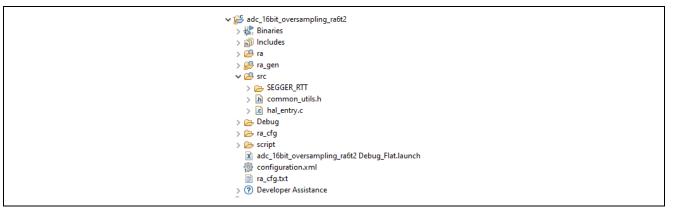

| 3.2 FSP Configurations                                         |    |

| 3.2.1 Clock/Pin Settings                                       |    |

| 3.2.2 Stack Settings                                           |    |

| 3.2.2.1 16-bit Oversampling Mode Project ADC Module Properties |    |

| 3.2.2.2 12-bit SAR Mode Project ADC Module Properties          |    |

| 3.3 FSP APIs Used                                              |    |

|                                                                |    |

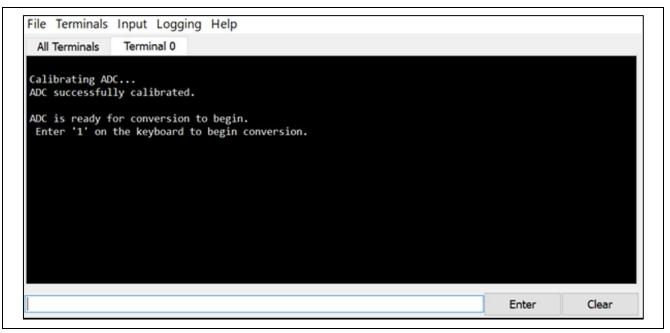

| 4. Running the Application Project                             | 36 |

| 4.1 Importing and Building the Application Project             | 36 |

| 4.2 Running the Application Project                            | 37 |

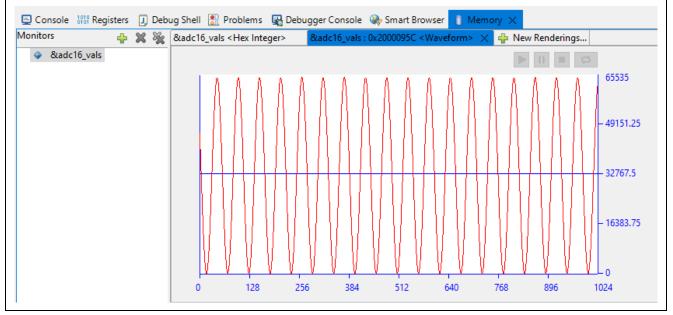

| 5. Verifying the Application Project                           | 30 |

| 5.1 View Raw Values                                            |    |

| 5.2 Plot Values in e <sup>2</sup> studio                       |    |

| 5.3 Export Values for Further Analysis in External Software    |    |

|                                                                |    |

| 6. Performance Analysis                                        | 45 |

| 6.1 Example Project Comparison                                 | 45 |

| 6.2 Voltage Conversion Precision Comparison                    | 46 |

| 6.2.1 16-bit Voltage Conversion                                | 46 |

| 6.2.2 12-bit Voltage Conversion                                | 47 |

| 6.2.3 Example LSB Calculation                                  | 48 |

| 7. References                                                  | 49 |

| Revision History                                               | 51 |

| •                                                              |    |

# 1. Overview of A/D Converters

Analog-to-digital converters (A/D converters, ADCs) are an integral part of data acquisition systems (DAQs) that function by capturing analog signals and converting them into discrete digital signals. ADCs convert analog voltages into numbers for a processor to operate on the values as needed: to store, display or further analyze the captured digital signal.

# **1.1** Characterizing an A/D Converter

A/D converters are generally characterized by three inherent qualities: the **input voltage range**, the **resolution** of the discrete values, and the **conversion rate**.

The **input voltage range** defines the range of acceptable analog input voltages that the ADC can convert to digital values. The input voltage range's maximum value is dependent on the reference voltage that the ADC system uses; typically the upper bound on the input voltage is equal to the value of the internal reference voltage. In the RA6T2, VREFH0 is the input analog reference voltage supply and is defined to lie in the range [2.7 V, 3.6 V] according to Electrical Characteristics.

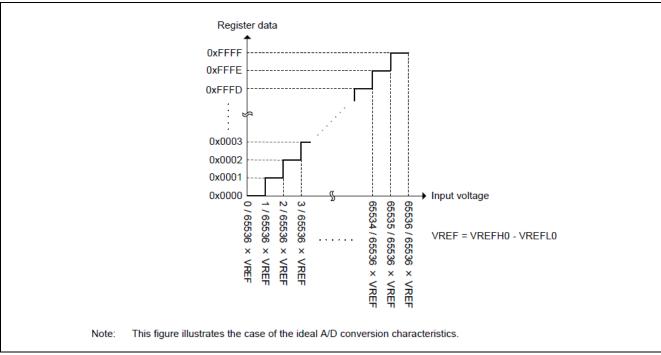

The **resolution** of an A/D converter refers to the smallest incremental voltage measure detected, which causes a change in the value of the converted digital output. The resolution of an ADC is determined by the number of bits used to store the digital converted value. For an n-bit resolution ADC, 2<sup>n</sup> values can be represented digitally.

The **conversion rate** (also referred to as **sampling rate**) describes the amount of time, recorded by the number of clock cycles it takes to convert the analog input to its digital representation. Typically, this value is expressed in Hertz as the number of A/D readings that can be completed each second. The conversion rate is especially important for analyzing acceptable AC signal input frequency rates according to Nyquist rules, to avoid unwanted artifacts like aliasing.

# 1.2 Analog Input Types

Most analog signals are either transmitted in one wire as a single analog voltage or in two wires as a difference between two analog voltages. The ADC on the RA6T2 supports both **single-ended input** and **differential input**.

## 1.2.1 Single-Ended Input

Single-ended input ADCs convert the difference between the voltage of the analog signal source and the analog reference ground voltage. Single-ended input is the most cost efficient in implementation, but the signals are sensitive to noise from electromagnetic interference.

## 1.2.2 Differential Input

Differential input ADCs convert the difference voltage between two complementary signals: a non-inverting and inverting input. Differential input is more costly to implement but has a higher performance and robustness against noise in the signals.

# 1.3 Types of ADCs

There are multiple hardware implementations capable of converting an input voltage to a digital representation. The variations in ADC implementation result in variations of the conversion's characteristics, so your application's requirements guide and influence which ADC type is optimal for that particular use case.

In the current industry, there are five major types of A/D converters: **successive approximation**, **delta-sigma**, **dual slope**, **pipelined**, and **flash** ADCs. When looking for an ADC to function as part of a data acquisition system, the two relevant types are the successive approximation ADC and delta-sigma ADC. The RA6T2 A/D converters have a **hybrid architecture** with features of both the successive approximation type and delta-sigma modulation type.

The following sections provide an overview of the main characteristics and differences of the ADC types, with a greater focus on the successive approximation and delta-sigma modulation ADCs.

## **1.3.1 Successive Approximation Register ADC**

The **Successive Approximation Register** (**SAR**) type ADC converts a continuous analog voltage signal to a discrete digital representation by utilizing a binary search through all possible quantization levels before converging on the digital output. The input analog signal is sampled and held, and the value of each bit of the digital representation is approximated successively, by comparing the input voltage to a reference voltage.

A basic SAR type A/D converter is shown in the following schematic:

Figure 1. Circuit Block Diagram of SAR ADC

## 1.3.1.1 Key Features and Limitations

- Require N clock periods for N-bit SAR

- Low power and physically small

- Lower sampling rates for higher resolutions

- Limited resolution due to limits of comparator

- Circuit size increases as resolution increases

## 1.3.2 Delta-Sigma Modulation ADC

The **Delta-Sigma Modulation** (**DSM**) type ADC first encodes a continuous analog voltage signal to a stream of pulses that represent the change (delta) of the signal. The accuracy of the modulation is improved by then passing the digital output to a 1-bit DAC and summing (sigma) the resulting analog signal to the input signal. The delta-sigma modulation ADC type takes advantage of filtering techniques that improve amplitude axis resolution and reduce the high-frequency noise inherent in SAR designs.

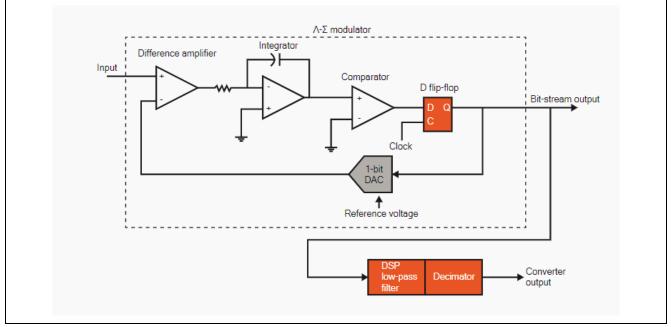

The design of a delta-sigma modulation type A/D converter is shown in the following schematic:

Figure 2. Circuit Block Diagram of Delta-Sigma ADC

## 1.3.2.1 Key Features and Limitations

- Oversampling in the design reduces quantization noise

- Resolution is highest amongst all types

- Sample rates are lower as compared to SAR type

- High clock speed is required to oversample the data

- Multiple samples must be converted per each ADC data value (oversampling) to achieve a higher signal quality

- Best for high-resolution and low-frequency applications

## 1.3.3 Additional ADCs

The other types of common ADCs are better suited for non-DAQ (non-Data Acquisition) applications and are briefly discussed below.

## (1) Dual Slope ADC

Dual slope type ADCs provide very precise and accurate voltage readings but have a slow conversion time due to the iterative methods they employ. Typically, these are found in multimeters and other voltage reading applications where precise conversions are required, but not in a timely manner.

## (2) Pipelined ADC

As indicated by the name, pipelined type ADCs have a pipeline architecture of flash comparators that convert a voltage to a digital representation. The pipeline introduces a latency in conversion of around 3 clock cycles, but this type of ADC is well-suited for applications that need higher sample rates than the SAR and deltasigma type ADCs but not the ultra-high sample rate achievable by the flash type ADC. Typical applications include digital oscilloscopes, spectrum analyzers, RADAR, software radio, among others.

## (3) Flash ADC

Flash type ADCs operate without any latency so they can achieve the highest sample rate among all ADC types. A/D conversion occurs when an incoming voltage is compared to all possible voltages as a reference. To attain N-bit resolution, the flash ADC requires 2<sup>N</sup> reference voltages, which means high resolutions require larger circuits with higher power consumptions. For that reason, resolution is typically no larger than 8 bits.

Flash ADCs are meant for applications that require extremely fast conversions but not large resolution, and as such, they are found in the fastest digital oscilloscopes, microwave measuring, fiber optics, and more.

## 1.3.4 Noise-Shaping Successive Approximation Register ADC

The RA6T2 contains two units of **Noise-Shaping SAR**-type A/D converters (**NS-SAR**). NS-SAR ADCs are an emerging hybrid A/D architecture that have features of the SAR type ADC and the delta-sigma modulation type ADC.

The NS-SAR's hybrid architecture combines the benefits of the SAR and DSM ADC architectures to achieve both high resolution and power efficiency simultaneously, characteristics which typically exist in a tradeoff relationship. NS-SAR type A/D converters benefit from SAR ADC qualities that make them low cost and energy efficient, and they benefit from DSM ADC qualities that provide a high signal-to-noise.

The hybrid architecture of the A/D converter module in the RA6T2 allows for new conversion methods for the peripheral that utilize oversampling and noise-shaping techniques to increase the resolution from 12-bits to 16-bits.

# **1.4 Increasing Resolution**

This section gives an overview of the algorithmic process of oversampling and noise-shaping to increase resolution and explains when this method is most effective.

## 1.4.1 Oversampling and Noise-Shaping of NS-SAR ADCs

The Noise-Shaping Successive Approximation Register ADC units in the RA6T2 contain hardware circuits that implement the algorithmic processes of oversampling and noise-shaping to convert the analog input into a digital representation and obtain 16-bit data resolution. These methods are briefly explained as follows, but the detailed theory is outside the scope of this application note.

Oversampling achieves higher resolution through decimation. Decimation is a process of oversampling an input signal and averaging the samples to increase the number of bits from the A/D conversion that contain valid measurement information. First, the input signal is oversampled, meaning the A/D converter samples the input signal at a higher rate than the Nyquist sampling rate.

After enough samples are collected, their values are accumulated, and the sum is right shifted by n. This results in a final conversion value that has increased bits of useful data.

Noise-shaping is a method that uses the natural residue, or quantization noise, that occurs during A/D conversion. Noise-shaping mitigates the effects of this quantization noise through implementing a negative feedback loop filter.

## 1.4.2 Use Cases

There are many applications that require measuring a wide dynamic range of input values while also detecting slight changes to the input. Such systems need a measurement resolution larger than the typical 12-bit SAR ADCs and might benefit from using a 16-bit NS-SAR ADC instead.

The advantages and disadvantages of oversampling and noise-shaping provide helpful information when determining if oversampling to achieve 16-bit resolution is the right choice for your application:

#### Advantages:

- Implementing a 16-bit DAQ system is cheaper and easier with the RA6T2. The RA6T2 natively supports 16-bit resolution data so there is no need for an external ADC.

- The RA6T2 NS-SAR ADCs increase resolution without affecting CPU usage. Decimation can be implemented in software but that requires the CPU to perform necessary calculations. The dedicated hardware performs oversampling and averaging without the cost of reduced throughput and increased CPU bandwidth.

#### Disadvantages:

- Oversampling requires multiple samples to be captured before a single A/D value is converted. Your system should account for this initial delay period and subsequent group delay periods.

- NS-SAR ADCs produce more precise measurements at the cost of a lower maximum conversion frequency than their SAR counterpart.

Operating the RA6T2 ADC peripheral in its 16-bit operation methods is fitting for applications that require more precise measurements than 12-bit A/D data, but it might not be appropriate for extremely rapidly changing input signals. Carefully determine your data acquisition system's sampling rate requirements and use the RA6T2 Hardware Users' Manual chapter on Electrical Characteristics to determine if the conversion rate is acceptable.

## 1.4.3 Additional Renesas ADCs

If you determine that your system requires an ADC with higher resolution measurements than 16-bits, Renesas offers several options of 24-bit delta-sigma modulation ADCs that you can find on our website at: <u>https://www.renesas.com/us/en/products/analog-products/data-converters/analog-digital-converters-adc-precision/delta-sigma-ad-converters</u>

## 2. Configuring the RA6T2 ADC Module

The RA6T2 MCU contains two units of noise-shaping SAR-type A/D converters that have a hybrid architecture with features of both SAR type and delta-sigma modulation type.

The RA6T2 ADCs differ from other RA MCU ADC modules for the larger number of available features, including the extended 16-bit resolution that takes advantage of oversampling and noise-shaping successive approximation techniques to achieve. The wide variety of settings, features and conversion methods allow a user to tailor the configurations of the converter for their desired application.

# 2.1 ADC Specifications

This section reviews the major available settings and features of the ADC peripheral that are specified in the *RA6T2 Hardware Users' Manual* (HW UM) and/or are configurable with the Flexible Software Package (FSP) APIs. Each setting will be thoroughly explained to understand their impact on A/D operation and conversion.

#### 2.1.1 Analog Channels

Analog channels are the physical source of the analog signal targeted for the A/D conversion. The analog channels consist of the following:

<u>Analog input channels:</u> A/D conversion channels for the analog input from MCU's I/O pin as the signal source.

Extended analog channels: A/D conversion channels for the source of the analog signal inside the MCU, for example, the temperature sensor, internal reference voltage and D/A converters.

Analog channels support both single-ended inputs and differential inputs. In total there are up to 29 analog input channels available, calculated based on the following conditions:

- A/D converter unit 0 (ADC0) can select up to 21 analog channels that support single-ended inputs and up to 12 analog channels that support differential input (capturing up to 6 differential signals).

- A/D converter unit 1 (ADC1) can select up to 17 analog channels that support single-ended inputs and up to 8 analog channels (4 pairs) that support differential inputs.

- ADC0 and ADC1 share 9 analog input channels.

The available configurations of the analog input channels are shown in the following table:

| Analog            | Source of analog signal |                                         |                                                                         | A/D converter unit 0      |                                     | A/D converter unit 1      |                                     |

|-------------------|-------------------------|-----------------------------------------|-------------------------------------------------------------------------|---------------------------|-------------------------------------|---------------------------|-------------------------------------|

| channel<br>number | Analog input            | Programmable<br>Gain Amplifier<br>(PGA) | Channel-<br>dedicated<br>Sample-and-hold<br>Circuit (S&H) <sup>*5</sup> | Single-<br>ended<br>input | Differential<br>input <sup>*6</sup> | Single-<br>ended<br>input | Differential<br>input <sup>*6</sup> |

| 0                 | AN000 (AN000P)*3        | PGAIN0                                  | SHIN0P*3                                                                | 1                         | 1                                   | _                         | _                                   |

| 1                 | AN001 (AN000N)*2        | PGAVSS0                                 | SHIN0N*4                                                                | 1                         |                                     | _                         |                                     |

| 2                 | AN002 (AN002P)*3        | PGAIN1                                  | SHIN1P*3                                                                | 1                         | ✓                                   | -                         | _                                   |

| 3                 | AN003 (AN002N)*2        | PGAVSS1                                 | SHIN1N*4                                                                | 1                         |                                     | _                         |                                     |

| 4                 | AN004 (AN004P)*3        | PGAIN2                                  | SHIN2P*3                                                                | 1                         | ✓                                   | _                         | _                                   |

| 5                 | AN005 (AN004N)*2        | PGAVSS2                                 | SHIN2N*4                                                                | 1                         |                                     | _                         |                                     |

| 6                 | AN006 (AN006P)          | _                                       | SHIN4P                                                                  | _                         | _                                   | 1                         | 1                                   |

| 7                 | AN007 (AN006N)          | _                                       | SHIN4N                                                                  | -                         |                                     | 1                         |                                     |

| 8                 | AN008 (AN008P)          | _                                       | SHIN5P                                                                  | -                         | _                                   | 1                         | 1                                   |

| 9                 | AN009 (AN008N)          | _                                       | SHIN5N                                                                  | -                         |                                     | 1                         |                                     |

| 10                | AN010 (AN010P)          | -                                       | SHIN6P                                                                  | _                         | _                                   | 1                         | 1                                   |

| 11                | AN011 (AN010N)          | _                                       | SHIN6N                                                                  | _                         |                                     | 1                         |                                     |

| 12                | AN012 (AN012P)          | —                                       | —                                                                       | 1                         | ✓                                   | _                         | _                                   |

| 13                | AN013 (AN012N)          | —                                       | —                                                                       | 1                         |                                     | _                         | _                                   |

| 14                | AN014 (AN014P)          | _                                       | _                                                                       | 1                         | ✓                                   | _                         | _                                   |

| 15                | AN015 (AN014N)          | —                                       | _                                                                       | 1                         |                                     | _                         | _                                   |

| 16                | AN016 (AN016P)          | —                                       | —                                                                       | 1                         | ✓                                   | _                         | _                                   |

| 17                | AN017 (AN016N)          | —                                       | —                                                                       | 1                         |                                     | _                         | _                                   |

| 18                | AN018 (AN018P)*3        | PGAIN3 <sup>*3</sup>                    | _                                                                       | -                         | —                                   | 1                         | 1                                   |

| 19                | AN019 (AN018N)*2        | PGAVSS3                                 | _                                                                       | -                         |                                     | ✓*4                       |                                     |

| 20                | AN020*1                 | —                                       | —                                                                       | 1                         | _                                   | 1                         | _                                   |

| 21                | AN021*1                 | _                                       | _                                                                       | 1                         |                                     | 1                         |                                     |

| 22                | AN022*1                 | _                                       | _                                                                       | 1                         | -                                   | 1                         | _                                   |

| 23                | AN023*1                 | _                                       | -                                                                       | 1                         |                                     | 1                         | -                                   |

| 24                | AN024*1                 | _                                       | _                                                                       | 1                         | _                                   | 1                         | _                                   |

| 25                | AN025*1                 | _                                       | _                                                                       | 1                         |                                     | 1                         |                                     |

| 26                | AN026*1                 | _                                       | _                                                                       | 1                         | _                                   | 1                         | _                                   |

| 27                | AN027*1                 | _                                       | _                                                                       | 1                         |                                     | 1                         | -                                   |

| 28                | AN028*1                 | _                                       | _                                                                       | 1                         | _                                   | 1                         | _                                   |

## Table 1. Analog Channel List of Available Configurations

Notes:

- 1. Do not perform A/D conversions of the same signal source from both A/D converter unit 0 and 1.

- 2. Only when the Programmable Gain Amplifier (PGA) is disabled and the PGA is set to single-ended input, the ANx can be used for A/D conversion as an analog input channel. When the PGA is enabled, Anx functions as the PGAVSS pin. Do not perform A/D conversion of Anx. Regardless of the PGA enable/disable setting, when the PGA is set to pseudo-differential input, A/D conversion of Anx is not possible.

- When the PGA is used in single-ended or pseudo-differential input mode, the A/D is converting the output of the PGA, the A/D conversion channel corresponding to PGAINn (n = 0 to 3) should be set to single-ended input.

- 4. When using the PGA or when the PGA is set to pseudo-differential mode, the SHINxN (inverting input (-)) of the channel-dedicated sample-and-hold circuit cannot be used.

- 5. When the channel-dedicated sample-and-hold circuit is used in single-ended input the SHINxP (non-inverting input (+)) channel and the SHINxN (inverting input (-)) channel must not be assigned to the same scan group (x = 0 to 2, 4 to 6).

- 6. When performing A/D conversion with differential input, set the even-numbered channel as the A/D conversion target. For differential input the even-numbered channels function as non-inverting inputs and the odd-numbered channels function as inverting inputs (-).

The available configurations of the extended analog input channels are shown in the following table:

Table 2. Extended Analog Channel List of Available Configurations

| Analog            | Source of analog signal*1  | A/D converter        | unit O                              | A/D converter unit 1                |                                     |

|-------------------|----------------------------|----------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| channel<br>number |                            | Single-ended input*2 | Differential<br>input <sup>*3</sup> | Single-ended<br>input <sup>*2</sup> | Differential<br>input <sup>+3</sup> |

| 96                | Self-diagnosis             | -                    | 1                                   | -                                   | 1                                   |

| 97                | Temperature sensor         | 1                    | -                                   | 1                                   | -                                   |

| 98                | Internal reference voltage | 1                    | -                                   | 1                                   | -                                   |

| 101               | D/A converter channel 0    | 1                    | _                                   | 1                                   | -                                   |

| 102               | D/A converter channel 1    | 1                    | -                                   | 1                                   | -                                   |

| 103               | D/A converter channel 2    | 1                    | -                                   | 1                                   | -                                   |

| 104               | D/A converter channel 3    | 1                    | -                                   | 1                                   | -                                   |

Notes:

- 1. Do not perform A/D conversion of the same signal source from both A/D converter unit 0 and unit 1.

- 2. The extend analog function (except for the self-diagnosis function) is only supported with the single-ended input. Do not set to differential input.

- 3. The self-diagnosis function is only supported with differential input.

## 2.1.2 Virtual Channels

A virtual channel is a group of registers that stores the A/D conversion configurations for an analog channel, including, but not limited to the selection of the analog channels, the optional settings for A/D conversion, the data processing method of the A/D conversion data, the assignment to scan groups, and so forth.

Before performing the A/D conversion, the analog channel should be assigned to any of the virtual channels and the virtual channel should be assigned to a scan group. The relation between analog channels, virtual channels and scan groups is discussed in greater detail in section 2.1.3.

Notes:

- The virtual channel can only be assigned to one scan group.

- Assign the analog channel to several virtual channels if:

- the same analog channel is to be converted in different scan groups, or

- the same analog channel is to be converted several times in the same scan group

- FIFO function should be used in combination when performing A/D conversion more than once using more than one virtual channel within the same scan group for the same analog channel.

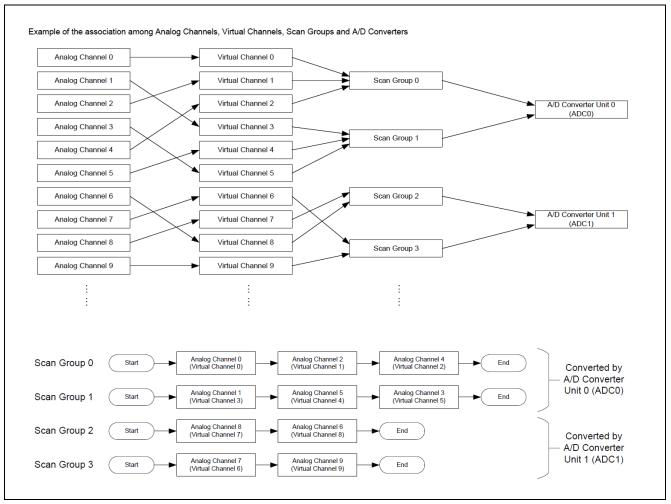

## 2.1.3 Scan Groups

A scan group is a group of analog channels that perform A/D conversion in a scanning operation. To use a scan group, do the following:

- Assign the analog channel for the A/D conversion to the desired virtual channel

- Assign the virtual channel to the scan group

- Assign the scan group to the specific A/D converter

The following image depicts an example of the relationship between analog channels, virtual channels, and scan groups. It shows the analog channel assignments and the resulting order of conversion during the scanning operation for each A/D converter.

#### Figure 3. Example Configuration Depicting the Scan Group assignments

A single scan group can be assigned to multiple virtual channels. The conversion method determines the ranges of virtual channels as follows:

- SAR mode: up to 8 virtual channels per scan group

- Oversampling mode: up to 8 virtual channels per scan group

- Hybrid mode: 2 to 4 virtual channels per scan group

If more than the maximum number of virtual channels is assigned to one scan group, channels are converted in ascending order and any subsequent above the max will not be converted.

Note:

- The virtual channels assigned to a particular scan group should be assigned only the analog channels that can be converted by that ADC unit.

- Any analog channels included that cannot be converted by the specified ADC unit will result in undefined conversions.

- Hybrid mode requires at least 2 virtual channels to be assigned to a scan group for operation to be guaranteed.

- If more than the maximum number of virtual channels is assigned to one scan group, channels are converted in ascending order and any subsequent above the max will not be converted.

# 2.1.4 Analog Input Mode

The ADC peripheral supports both single-ended inputs and differential inputs with the following counts:

- A/D converter unit 0 (ADC0) can select up to 21 analog channels that support single-ended inputs and up to 12 analog channels (6 pairs) that support differential inputs.

- A/D converter unit 1 (ADC1) can select up to 17 analog channels that support single-ended inputs and up to 8 analog channels (4 pairs) that support differential inputs.

The relationship between analog channels and the possible input modes is shown in greater detail in the tables of section 2.1.1 Analog Channels.

## 2.1.4.1 Single-Ended Input

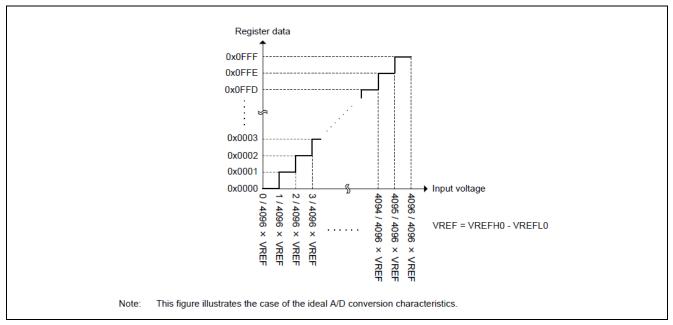

In single-ended input mode, the difference between the voltage of the analog channel's signal source and the analog reference ground voltage (VREFL0) is converted.

For single-ended input, A/D conversion is formatted into unsigned data format based in the setting of the ADDOPCRCn.SIGNSEL (n = 0 to 36), where SIGNSEL should be 1.

## 2.1.4.2 Differential Input

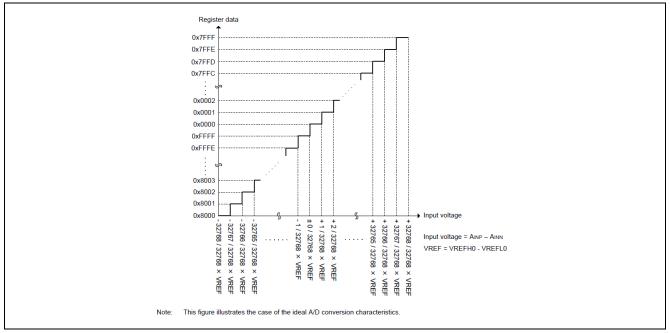

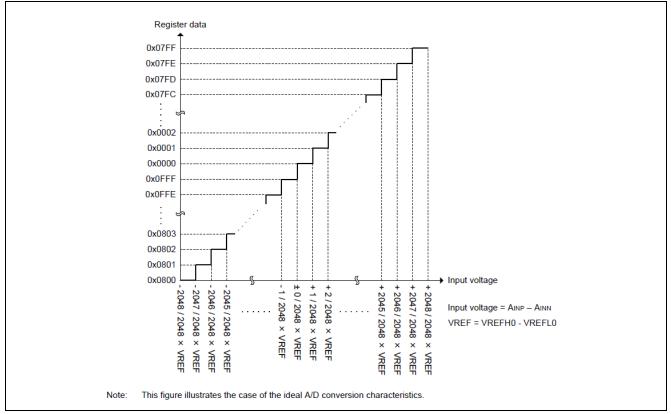

In differential input mode, the even-numbered analog channel is used as the non-inverting input (+) ( $A_{INP}$ ) and the odd-numbered channel is used as the inverting input (-) ( $A_{INN}$ ). The difference between the voltage of the non-inverting input (+) and inverting input (-) ( $A_{INP}$  -  $A_{INN}$ ) is converted.

For differential input A/D conversion is formatted into signed data format based in the setting of the ADDOPCRCn.SIGNSEL (n = 0 to 36), where SIGNSEL should be 0.

For A/D conversion with differential input mode, select the non-inverting input (+) channel of the target of differential pair in ADCHCRn.CNVCS[6:0] (n = 0 to 36) bits, and select the differential input mode in ADCHCRn.AINMD (n = 0 to 36) bits.

Note: The differential input pair is a combination of channels with analog channel number 2i and 2i + 1 (i = 0, 1, 2, 3, ...), and they are named ANxxxP and ANxxxN (xxx = 000, 002, 004, ...). The combination of discontinuous analog channel numbers or the combination of analog channel numbers 2i - 1 and 2i cannot be used as a differential input pair.

## 2.1.5 Conversion Methods

The A/D converter units of the RA6T2 have a hybrid architecture with combined features of a SAR type and delta-sigma type ADC. Because of the unique architecture, each ADC unit can convert in one of three different conversion methods: SAR mode, oversampling mode, and hybrid mode.

The key features, important restrictions, and major differences between the three operating modes are detailed in this section to help guide selection for your own application based on conversion requirements.

A/D conversion characteristics are determined by the combination of the conversion method and the scan mode selected. For more information on how these modes interact and affect processing for achieving 16-bit resolution, see section 2.2, Operating ADC with 16-bit Depth.

## 2.1.5.1 SAR Mode

In SAR mode, the A/D converter operates as a Nyquist rate A/D converter, sampling analog channels one at a time using the SAR method.

#### **Key Features**

- A/D converter samples the signal source once, and converts by SAR method

- Fast A/D conversion

- Supports up to 8 channels per one scan group

- Supports only single-ended input (excluding self-diagnosis function)

- Supports 10-bit and 12-bit resolution

#### Restrictions

#### (1) Resolution and Accuracy:

SAR mode is a 12-bit resolution A/D converter and as such, the accuracy of the data output is only guaranteed for 12 bits.

However, if 14-bit or 16-bit mode is selected, internally the data output from the A/D converter is extended to 16-bits for calculation processing. Select 14-bit or 16-bit length data format in SAR mode to increase the computational resolution, such as when using A/D-converted value addition/averaging function or User's Gain/User's Offset function.

#### (2) Differential Input

SAR mode only supports single-ended input except during the self-diagnosis operation. A/D conversion with differential input mode is only guaranteed during the self-diagnosis operation.

#### (3) Digital Filter Function

Operation is not guaranteed in SAR mode when the digital filter function is enabled.

## 2.1.5.2 Oversampling Mode

In Oversampling mode, the A/D converter operates by oversampling analog channels and converting the analog signal to digital data by the NS-SAR method.

#### **Key Features**

- A/D converter oversamples the signal source, and converts analog-to-digital by NS-SAR method

- High-accuracy A/D conversion

- Supports up to 8 channels per one scan group

- Supports single-ended input and differential input

- Supports 10,12,14 and 16-bit resolution

#### Restrictions

#### (1) Digital Filter Function

The digital filter function is mandatory in Oversampling mode. A/D conversion is not guaranteed without the use of the digital filter function.

#### 2.1.5.3 Hybrid Mode

Hybrid mode has both features of SAR mode and Oversampling mode. In Hybrid mode, the A/D converter operates by oversampling and converting the analog signal to digital data by the NS-SAR method. In Hybrid mode, when switching channels for each sampling, multiple analog channels are oversampled simultaneously.

#### **Key Features**

- A/D converter oversamples the signal source, and converts analog-to-digital by NS-SAR method

- High-accuracy A/D conversion

- High data rate in continuous scanning operation

- Supports up to 4 channels per one scan group

- Supports single-ended input and differential input

- Supports 10,12,14 and 16-bit resolution

#### Restrictions

#### (1) Scan Group Assignment

In Hybrid mode, 2-4 virtual channels must be assigned to a scan group for operation to be guaranteed. Scanning operation with only one virtual channel is prohibited for ADC conversion results to be guaranteed.

#### (2) Virtual Channel Assignment

In Hybrid mode, do not assign the same analog channel to multiple virtual channels assigned to the same scan group for operation to be guaranteed.

## (3) Digital Filter Function

The digital filter function is mandatory in Hybrid mode. A/D conversion is not guaranteed without the use of the digital filter function.

The digital filters selected by the ADDOPCRAn.DFSEL[2:0] (n = 0 to 36) bits must be set to be exclusive among virtual channels in the same scan group, since multiple digital filters are used simultaneously. If the same digital filter is selected from multiple virtual channels in the same scan group, operation is not guaranteed.

#### (4) A/D Converted Value Addition/Averaging Function

When using A/D converted value addition/averaging function in Hybrid mode, set the number of addition/average times for all virtual channels in the same scan group to the same value for operation to be guaranteed.

#### (5) Trigger Interval for Background Continuous Scan Mode

In Hybrid mode – Background Continuous Scan mode, AD conversion start trigger should be input no sooner than after the following intervals:

- When trigger delay function is not used, or software trigger: 8 ADCLK cycles or more

- When trigger delay function is used: (8 + (setting value of ADTRGDLRm.TRGDLYn[7:0])) × ADCLK cycles or more, for m = 0 to 4, n = 0 to 8

If this restriction is violated, the A/D conversion start trigger will not be accepted and will be ignored.

#### 2.1.6 Scan Modes

The scanning operation is the operation of sequential A/D conversion for the analog channels. There are 3 scan modes of the scanning operation selectable: Single Scan mode, Continuous Scan mode, and Background Continuous Scan mode.

The available combinations of scan modes and conversion methods of the ADC units are show in the following table:

#### Table 3. Available Combinations of Scan Modes and Conversion Methods

| Scan mode                       | Operation mode of A/D converter       SAR mode     Oversampling mode       Hybrid mode |   |          |  |

|---------------------------------|----------------------------------------------------------------------------------------|---|----------|--|

|                                 |                                                                                        |   |          |  |

| Single scan mode                | 1                                                                                      | 1 | 1        |  |

| Continuous scan mode            | 1                                                                                      | 1 | ✓        |  |

| Background continuous scan mode | _                                                                                      | _ | <i>✓</i> |  |

Note: ✓: available, —: not available

The scanning operations are performed based on the scan groups. When the scanning operation is started, A/D conversion is performed for each analog channel, based on the virtual channel settings. If the scanning operation starts for 2 or more scan groups assigned to the same A/D converter at the same time, the scanning operation of the group with the lowest scan group number is performed.

The A/D conversion order of analog channels is in ascending order based on the virtual channel numbers assigned to the scan group. The channels with the lowest virtual channel numbers are converted at the beginning of the scan group conversion.

## 2.1.6.1 Single Scan Mode

In single scan mode, one scan group is converted once for each A/D conversion start trigger input. Each time an A/D conversion start trigger occurs, A/D conversion is performed once for each analog channel assigned in the scan group.

## 2.1.6.2 Continuous Scan Mode

Continuous scan mode repeats the scanning operation of one scan group. When an A/D conversion start trigger occurs, A/D conversion of each analog channel assigned to that scan group is repeated until the A/D conversion stop processing occurs.

## 2.1.6.3 Background Continuous Scan Mode

Background continuous scan mode repeats the scanning operation of a single scan group. Scanning operation begins at the input of the first A/D conversion start trigger. Like in continuous scan mode, A/D conversion of each analog channel assigned to that scan group is repeated until the A/D conversion stop processing occurs.

When an A/D conversion start trigger occurs during the continuous scanning operation, the A/D conversion data at that point is output. Without the A/D conversion start trigger, the A/D conversion data are not output. and the values of the A/D data registers and the First In First Out (FIFO) data registers are not updated.

## 2.1.7 A/D Scan Start Conditions

A/D conversion can be triggered from multiple peripheral modules on the MCU. These include the Event Link Controller (ELC), the General Purpose PWM Timer (GPT), and external triggers from the I/O ports. The variety of sources provides flexibility for your signal acquisition system design. Each of these listed triggers is described in further detail in this section.

To perform A/D conversion by a trigger from a peripheral module, the trigger needs to be configured for each scan group and the trigger input needs to be enabled from the peripheral module in the ADTRGENR register.

In addition, there is a trigger delay function that delays the A/D conversion start trigger to adjust the A/D conversion start time for each scan group. The delay function is available for triggers generated by the ELC, GPT, or external source but not for software trigger sources. The delay value to be added is set for each scan group in ADTRGDLRi (i = 0 to 4) register. The delay time added is the register setting value x A/D conversion clock (ADCLK) cycle.

## 2.1.7.1 ELC Trigger Scan Start

A/D conversion can be initiated by an event from the Event Link Controller. To enable scan start by the ELC, configure the scan group using the ELC event in the ADTRGELCn (n = 0 to 8) register and enable the A/D conversion start trigger in the ADTRGENR register.

The following table shows the relationships between the ADTRGELCn register and its corresponding ELC event:

| Table 4. | ELC Event Names and Corresponding Register Bit Setting |

|----------|--------------------------------------------------------|

|----------|--------------------------------------------------------|

| Resister bit      | Event Name |

|-------------------|------------|

| ADTRGELCn.TRGELC0 | ELC_AD00   |

| ADTRGELCn.TRGELC1 | ELC_AD01   |

| ADTRGELCn.TRGELC2 | ELC_AD02   |

| ADTRGELCn.TRGELC3 | ELC_AD10   |

| ADTRGELCn.TRGELC4 | ELC_AD11   |

| ADTRGELCn.TRGELC5 | ELC_AD12   |

Note: n = 0 to 8

# 2.1.7.2 GPT Trigger Scan Start

A/D conversion can also be initiated by an interrupt from the general purpose PWM timer. To enable scan start by the GPT, configure the scan group using the GPT interrupt source in the ADTRGGPTn (n = 0 to 8) register and enable the A/D conversion start trigger in the ADTRGENR register.

The following table shows the relationships between the ADTRGGPTn register and GPT interrupt sources:

#### Table 5. GPT Interrupt Sources and Corresponding Register Bit Setting

| Resister bit       | Event Name  |

|--------------------|-------------|

| ADTRGGPTn.TRGGPTA0 | GPT0_ADTRGA |

| ADTRGGPTn.TRGGPTA1 | GPT1_ADTRGA |

| ADTRGGPTn.TRGGPTA2 | GPT2_ADTRGA |

| ADTRGGPTn.TRGGPTA3 | GPT3_ADTRGA |

| ADTRGGPTn.TRGGPTA4 | GPT4_ADTRGA |

| ADTRGGPTn.TRGGPTA5 | GPT5_ADTRGA |

| ADTRGGPTn.TRGGPTA6 | GPT6_ADTRGA |

| ADTRGGPTn.TRGGPTA7 | GPT7_ADTRGA |

| ADTRGGPTn.TRGGPTA8 | GPT8_ADTRGA |

| ADTRGGPTn.TRGGPTA9 | GPT9_ADTRGA |

| ADTRGGPTn.TRGGPTB0 | GPT0_ADTRGB |

| ADTRGGPTn.TRGGPTB1 | GPT1_ADTRGB |

| ADTRGGPTn.TRGGPTB2 | GPT2_ADTRGB |

| ADTRGGPTn.TRGGPTB3 | GPT3_ADTRGB |

| ADTRGGPTn.TRGGPTB4 | GPT4_ADTRGB |

| ADTRGGPTn.TRGGPTB5 | GPT5_ADTRGB |

| ADTRGGPTn.TRGGPTB6 | GPT6_ADTRGB |

| ADTRGGPTn.TRGGPTB7 | GPT7_ADTRGB |

| ADTRGGPTn.TRGGPTB8 | GPT8_ADTRGB |

| ADTRGGPTn.TRGGPTB9 | GPT9_ADTRGB |

Note: n = 0 to 8

## 2.1.7.3 External Trigger Scan Start

A/D conversion can be initiated by input from an external trigger pin, ADTRG0 and ADTRG1. To enable scan start using an external trigger, configure the scan group using the external trigger source in the ADTRGENR register.

**Note:** External trigger is active low. Before enabling the external trigger (ADTRG0 and ADTRG1), set the external trigger pin to high.

## 2.1.8 Interrupt Sources

There are a variety of interrupt sources and ELC event requests that can be created by the A/D converter peripheral. This section lists the interrupt sources offered and describes the conditions that generate the requests in further detail.

The following table lists the interrupt sources and ELC events that can be created by the ADC module:

#### Table 6. List of Interrupt Sources and ELC Events the ADC Module Can Create

| Interrupt request or ELC event                  | Symbol                   | Description                                                                                                              | Status flag                                                                              |

|-------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| A/D converter error interrupt                   | ADC_ERR0                 | Generated when abnormal operation of ADC0 is detected.                                                                   | ADERSR.ADERF0                                                                            |

|                                                 | ADC_ERR1                 | Generated when abnormal operation of ADC1 is detected.                                                                   | ADERSR.ADERF1                                                                            |

| A/D converter self-calibration end<br>interrupt | ADC_CALEND0              | Generated when self-calibration operation of ADC0 is finished.                                                           | ADCALENDSR.CALENDF0                                                                      |

|                                                 | ADC_CALEND1              | Generated when self-calibration operation of ADC1 is finished.                                                           | ADCALENDSR.CALENDF1                                                                      |

| A/D scan end interrupt                          | ADC_ADI0                 | Generated at the scan end of scan group 0                                                                                | ADSCANENDSR.SCENDF0                                                                      |

|                                                 | ADC_ADI1                 | Generated at the scan end of scan group 1                                                                                | ADSCANENDSR.SCENDF1                                                                      |

|                                                 | ADC_ADI2                 | Generated at the scan end of scan group 2                                                                                | ADSCANENDSR.SCENDF2                                                                      |

|                                                 | ADC_ADI3                 | Generated at the scan end of scan group 3                                                                                | ADSCANENDSR.SCENDF3                                                                      |

|                                                 | ADC_ADI4                 | Generated at the scan end of scan group 4                                                                                | ADSCANENDSR.SCENDF4                                                                      |

|                                                 | ADC_ADI5678              | Generated at the scan end of scan group 5 to 8                                                                           | ADSCANENDSR.SCENDF5<br>ADSCANENDSR.SCENDF6<br>ADSCANENDSR.SCENDF7<br>ADSCANENDSR.SCENDF8 |

| Limitter clip interrupt                         | ADC_LIMCLPI              | Generated when a limiter clip<br>using limiter table 0 to 7 is<br>detected for A/D conversion.                           | ADLIMGRSR.LIMGRFn<br>ADLIMCHSR0.LIMCHFi<br>ADLIMEXSR.LIMEXFj                             |

| A/D conversion overflow interrupt               | ADC_RESOVF0              | Generated when the overflow is<br>detected in A/D conversion result<br>with ADC0.                                        | ADOVFERSR.ADOVFEF0<br>ADOVFCHSR0.OVFCHFi<br>ADOVFEXSR.OVFEXFj                            |

|                                                 | ADC_RESOVF1              | Generated when the overflow is detected in A/D conversion result with ADC1.                                              | ADOVFERSR.ADOVFEF1<br>ADOVFCHSR0.OVFCHFi<br>ADOVFEXSR.OVFEXFj                            |

| Compare match interrupt                         | ADC_CMPI0                | Generated when a compare<br>match with compare match table<br>0 is detected.                                             | ADCMPTBSR.CMPTBF0                                                                        |

|                                                 | ADC_CMPI1                | Generated when a compare<br>match with compare match table<br>1 is detected.                                             | ADCMPTBSR.CMPTBF1                                                                        |

|                                                 | ADC_CMPI2                | Generated when a compare<br>match with compare match table<br>2 is detected.                                             | ADCMPTBSR.CMPTBF2                                                                        |

|                                                 | ADC_CMPI3                | Generated when a compare<br>match with compare match table<br>3 is detected.                                             | ADCMPTBSR.CMPTBF3                                                                        |

| Composite compare match<br>interrupt            | ADC_CCMPM0<br>ADC_CCMPM1 | Generated when a composite<br>compare match with combined<br>conditions using compare match<br>table 0 to 7 is detected. | ADCMPTBSR.CMPTBF0 to<br>ADCMPTBSR.CMPTBF8                                                |

| Interrupt request or ELC event   | Symbol          | Description                                                                                                                                    | Status flag                                                                                          |

|----------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| FIFO data read request interrupt | ADC_FIFOREQ0    | Generated when the number of<br>vacant stages in FIFO for scan<br>group 0 become less than or<br>equal to the specified value.                 | ADFIFOSR0.FIFOST0[3:0]                                                                               |

|                                  | ADC_FIFOREQ1    | Generated when the number of<br>vacant stages in FIFO for scan<br>group 1 become less than or<br>equal to the specified value.                 | ADFIFOSR0.FIFOST1[3:0]                                                                               |

|                                  | ADC_FIFOREQ2    | Generated when the number of<br>vacant stages in FIFO for scan<br>group 2 become less than or<br>equal to the specified value.                 | ADFIFOSR1.FIFOST2[3:0]                                                                               |

|                                  | ADC_FIFOREQ3    | Generated when the number of<br>vacant stages in FIFO for scan<br>group 3 become less than or<br>equal to the specified value.                 | ADFIFOSR1.FIFOST3[3:0]                                                                               |

|                                  | ADC_FIFOREQ4    | Generated when the number of<br>vacant stages in FIFO for scan<br>group 4 become less than or<br>equal to the specified value.                 | ADFIFOSR2.FIFOST4[3:0]                                                                               |

|                                  | ADC_FIFOREQ5678 | Generated when the number of<br>vacant stages in any of FIFO for<br>scan groups 5 to 8 become less<br>than or equal to the specified<br>value. | ADFIFOSR2.FIFOST5[3:0]<br>ADFIFOSR3.FIFOST6[3:0]<br>ADFIFOSR3.FIFOST7[3:0]<br>ADFIFOSR4.FIFOST8[3:0] |

| FIFO data overflow interrupt     | ADC_FIFOOVF     | Generated when FIFO overflow<br>is detected in any of FIFO for<br>scan group 0 to 8.                                                           | ADFIFOERSR.FIFOOVF0 to<br>ADFIFOERSR.FIFOOVF8                                                        |

Note: n = 0 to 8. i = 0 to 28.j = 0 to 2, 5 to 8.

## (1) A/D Converter Error Interrupt

An A/D converter error interrupt can be generated when an error with the A/D converter is detected.

A/D converter error interrupt (ADC\_ERRm (m = 0, 1)) is generated when the ADERINTCR.ADEIEm (m = 0, 1) bit is 1 and ADERSR.ADERFm (m = 0, 1) bit is 1.

#### (2) A/D Converter Self-Calibration End Interrupt

An A/D converter self-calibration end interrupt can be generated at the end of A/D converter self-calibration operation.

A/D converter self-calibration end interrupt (ADC\_CALENDm (m = 0, 1)) is generated when the ADCALINTCR.CALENDIEm (m = 0, 1) bit is 1 and ADCALENDSR.CALENDFm (m = 0, 1) bit is 1.

## (3) A/D Scan End Interrupt

A/D scan end interrupt can be generated at the end of scanning operation of scan group n (n = 0 to 8).

A/D scan end interrupt for scan group 0 to 4 (ADC\_ADI0 to ADC\_ADI4) are generated when ADINTCR.ADIEn (n = 0 to 4) bit is set to 1 and ADSCANENDSR.SCENDFn (n = 0 to 4) bit is set to 1.

The A/D scan end interrupt, for scan groups 5 through 8 (ADC\_ADIn), is generated when the ADINTCR.ADIEn (n = 5 to 8) bit = 1 and the ADSCANENDSR.SCENDFn (n = 5 to 8) bit i= 1 for any of the scan groups 5 through 8.

However, A/D scan end interrupt is not generated when A/D conversion operation (scanning operation) is forcibly stopped by ADSTOPR register.

## (4) Limiter Clip Interrupt

Limiter clip interrupt (ADC\_LIMCLPI) can be generated when a limiter clip with limiter table i (i = 0 to 7) is detected.

Limiter clip interrupt is generated when either the ADLIMINTCR.LIMIEi (i = 0 to 8) bit is 1 or ADLIMGRSR.LIMGRFi (i = 0 to 8) bit is 1.

## (5) A/D Conversion Overflow Interrupt

A/D conversion overflow interrupt can be generated when an A/D conversion result overflow is detected in either ADC unit.

A/D conversion overflow interrupt (ADC\_RESOVFm (m = 0, 1)) is generated when the ADOVFINTCR.ADOVFIEm (m = 0, 1) bit is 1 and ADOVFERSR.ADOVFEFm (m = 0, 1) bit is 1.

## (6) Compare Match Interrupt

Compare match interrupt is generated when a compare match is detected when using the composite compare match function.

Compare match interrupt (ADC\_CMPIj (j = 0 to 3)) is generated when the ADCMPINTCR.CMPIEj (j = 0 to 3) bit is 1 and ADCMPTBSR.CMPTBFj (j = 0 to 3) bit is 1.

## (7) Composite Compare Match Interrupt

Composite compare match interrupt (ADC\_CCMPMk (k = 0, 1)) can be generated by combining the comparison results of two or more compare match tables.

#### (8) FIFO Data Read Request Interrupt

FIFO data read request interrupt can be generated when the number of vacant stages in FIFO becomes less than or equal to the specified value.

FIFO data read request interrupts for scan group 0 to 4 (ADC\_FIFOREQ0 to ADC\_FIFOREQ4) are generated when the ADFIFOINTCR.FIFOIEn (n = 0 to 4) is set to 1 and ADFIFOSRm.FIFOSTn[3:0]  $\leq$  ADFIFOINTLRm.FIFOILVn[3:0] (m = 0 to 2, n = 0 to 4).

FIFO data read request interrupts for scan group 5 to 8 (ADC\_FIFOREQ5 to ADC\_FIFOREQ8) are generated when the ADFIFOINTCR.FIFOIEn (n = 5 to 8) is set to 1 and ADFIFOSRm.FIFOSTn[3:0]  $\leq$  ADFIFOINTLRm.FIFOILVn[3:0] (m = 3 to 4, n = 5 to 8)

**Note**: FIFO read request interrupt is not generated while the ADFIFOERSR.FIFOFLFn (n = 0 to 8) bit corresponding to its interrupt source is set to 1.

#### (9) FIFO Data Overflow Interrupt

FIFO data overflow interrupt (ADC \_FIFOOVF) can be generated when a FIFO overflow is detected in any of FIFO in scan groups 0 to 8.

FIFO data overflow interrupt is generated when ADFIFOINTCR.FIFOIEn (n = 0 to 8) bit is 1 and ADFIFOERSR.FIFOOVFn (n = 0 to 8) bit is 1.

# 2.1.9 Self-Calibration Function

The ADC has a built-in self-calibration function, which serves to normalize the variations of A/D converter characteristics that are caused by chip-to-chip variations.

## 2.1.9.1 Conditions When Self-Calibration is Required

Self-Calibration should be performed any time the ADC operating characteristics are modified, including after reset, releasing module-stop, when returning from Software Standby or Deep Software Standby mode, and each time the R\_ADC\_B\_ScanCfg() function is called. A detailed list of conditions under which self-calibration is required is shown in the following table.

#### Table 7. Conditions When Self-Calibration is Required

| Conditions under which self-calibration is required                                                                 | Internal-circuit<br>Calibration | Gain/Offset<br>Calibration | Channel-<br>dedicated<br>sample-and-hold<br>circuit Gain and<br>Offset<br>Calibration *1 |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------|------------------------------------------------------------------------------------------|

| After reset release                                                                                                 | 1                               | 1                          | 1                                                                                        |

| After releasing the module stop                                                                                     | 1                               | 1                          | 1                                                                                        |

| When returning from Software Standby mode or Deep Software Standby<br>mode                                          | 1                               | 1                          | 1                                                                                        |

| When changed the ADCLK setting<br>(When clock source or frequency is changed)                                       | 1                               | 1                          | 1                                                                                        |

| When changed the operation mode or the scan mode of the A/D converter (When changed ADMDR.ADMDm bit ( $m = 0, 1$ )) | 1                               | 1                          | 1                                                                                        |

| When changed A/D successive approximation time<br>(When changed ADCNVSTR.CSTm bit (m = 0, 1))                       | 1                               | 1                          | 1                                                                                        |

| When changed the operation setting of the channel-dedicated sample-and-<br>hold circuit <sup>11</sup>               | -                               | -                          | 1                                                                                        |

Note: Self-calibration should be performed.

—: Self-calibration is not required.

Note 1. When any of ADSHCRm.SHENn bits are set to 1, or any of ADSHCRm.SHENn bits are changed, perform the channel-dedicated sample-and-hold circuits self-calibration (m = 0, 1, n = 0 to 2, 4 to 6). Not required if the channel-dedicated sample-and-hold circuits are not used.

If a condition shown in this table occurs, self-calibration needs to be performed before using the A/D converter for the conversion results to be guaranteed. If the A/D converter is still operating after a first attempt, stop all A/D converters and perform the self-calibration again.

# 2.1.9.2 Self-Calibration Operation and Procedure

The self-calibration function has the following purposes:

#### (1) Internal Circuit Calibration:

Self-calibration adjusts the operation of the A/D internal circuitry.

#### (2) Gain and Offset Calibration:

Self-calibration measures the A/D converter's gain error and offset error. The calibration processing of the A/D conversion result based on the measured error data is performed after the A/D conversion. This self-calibration should be performed after internal circuit self-calibration is completed.

#### (3) Channel-Dedicated Sample-and-Hold Circuit Gain and Offset Calibration:

Self-calibration measures the A/D converter's gain error and offset error when using the channel-dedicated sample-and-hold circuit. The calibration processing of the A/D conversion result based on the measured error data is performed after the A/D conversion. This self-calibration should be performed after A/D converter Gain/Offset self-calibration is completed.

## 2.1.9.3 Self-Calibration Restrictions

#### (1) Prohibition of Scanning Operation

When performing the scanning operation, start the scanning operation after self-calibration is completed. Operation is not guaranteed when the scanning operation is started during self-calibration.

## (2) Prohibition of Additional Writes to ADCALSTR Register

After the self-calibration is started, writing to ADCALSTR register is prohibited until self-calibration is completed. Operation is not guaranteed if this restriction is violated.

#### (3) Prohibition of Forced Stop

Do not forcibly stop with the ADSTOPR register during self-calibration. Even if the A/D conversion operation needs to be forcibly stopped due to a system error or exception handing, be sure to wait to stop until self-calibration completes for guaranteed operation.

## (4) Restrictions for Channel-Dedicated Sample-and-Hold Circuit

To perform the self-calibration for the channel-dedicated sample-and-hold circuit, all channel-dedicated sample-and-hold circuits connected to the A/D converter should be enabled as follows:

- For ADC0: set 1 for ADSHCR0.SHEN0 to SHEN2 bit

- For ADC1: set 1 for ADSHCR1.SHEN4 to SHEN6 bit

- If there is a channel-dedicated sample-and-hold circuit that is not used, set it to disabled (ADSHCRm.SHENn = 0 (m = 0, 1, n = 0 to 2, 4 to 6) after self-calibration completes.

Operation is not guaranteed when the self-calibration for the channel-dedicated sample-and-hold circuit is performed while any channel-dedicated sample-and-hold circuits are disabled.

#### (5) Restrictions on Self-Calibration Operation and Noise

Self-calibration should be performed for the A/D converters one by one. When one A/D converter is in the selfcalibration operation, the other converters should be idle, that is, not in scan operation and not in self-calibration operation.

If this restriction is violated, the A/D conversion accuracy will be degraded due to noise during the selfcalibration operation. In this case, the A/D converter characteristics are not guaranteed. For the best results, self-calibration operation should be performed under conditions with as little noise as possible.

#### (6) Restrictions on State Setting

The number of states to be set in the ADCALSTCR and ADCALSHCR registers should satisfy the values specified in the Electrical Characteristics section of the RA6T2 Hardware Users' Manual. Also, the number of states involved in self-calibration should be set to satisfy the following restrictions:

#### (a) Restrictions on setting ADCALSTCR register

- ADCALSTCR.CALADSST[9:0] bits

- Depending on the type of self-calibration, set the values to satisfy those in the Electrical Characteristics chapter of the RA6T2's HW UM.

- If the setting value differs according to the type of self-calibration, change the register setting value for each self-calibration.

- ADCALSTCR.CALADCST[5:0] bits

- Set the same value as ADCNVSTR.CSTm[5:0] (m=0,1) bits.

- (ADCALSTCR.CALADCST[5:0] = ADCNVSTR.CSTm[5:0])

#### (b) Restrictions on setting ADCALSHCR register

These only apply when a channel-dedicated sample-and-hold circuit is used.

- ADCALSHCR.CALSHSST[7:0] bits

- Set the value equal to the value of the ADSHSTRm.SHSST[7:0] bits plus 1 (m = 0, 1).

- (ADCALSHCR.CALSHSST[7:0] = ADSHSTRm.SHSST[7:0] + 1)

- If the setting values of ADSHSTR0.SHSST[7:0] and ADSHSTR1.SHSST[7:0] are different, change the register setting values of CALSHSST[7:0] for each self-calibration of ADC0 (SH0 to SH2) and ADC1 (SH4 to SH6).

- ADCALSHCR.CALSHHST[2:0] bits

- Set the same value as ADSHSTRm.SHHST[2:0] (m = 0, 1) bits.

# 2.2 Operating ADC with 16-bit Depth

The ADC peripheral on the RA6T2 MCU is unique in its ability to extend 12-bit resolution to 16-bit resolution by taking advantage of oversampling and averaging techniques. There are 5 different combinations of conversion method - scan mode pairs that can achieve 16-bit resolution, which are highlighted in the following table:

#### Table 8. Highlighted Conversion Method – Scan Mode Pairs Can Provide 16-bit Resolution

| Scan mode                       | Operation mode of A/D converter       |   |       |  |

|---------------------------------|---------------------------------------|---|-------|--|

|                                 | AR mode Oversampling mode Hybrid mode |   |       |  |

| Single scan mode                | 1                                     | 1 | 1     |  |

| Continuous scan mode            | 1                                     | 1 | 1     |  |

| Background continuous scan mode | _                                     | _ | ✓<br> |  |

Note: ✓: available, —: not available

Each pair's scanning operation procedures are described in greater detail in the following sections.

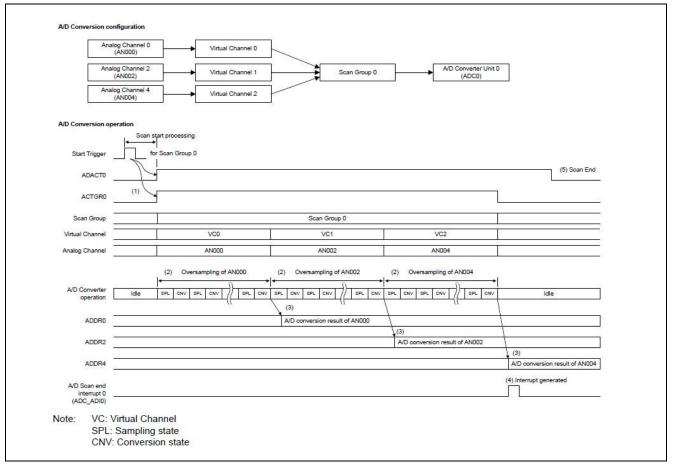

## 2.2.1 Oversampling Mode – Single Scan Mode

The following steps detail the procedure of Oversampling Mode – Single-Scan Mode:

- 1. In oversampling mode single scan mode, scanning operation begins when a software trigger or a peripheral module trigger is input. The scan group corresponding to the trigger is started.

- 2. Each analog channel is oversampled according to the number of taps in the digital filter and the number of A/D-converted value addition/averaging times. The oversampled data stored in the digital filter is discarded after the oversampling of each analog channel is completed.

- A/D conversion data of each analog channel is output after oversampling. The A/D conversion data is stored in the data register (ADDRi (i = 0 to 28), ADEXDRj (j = 0 to 2, 5 to 8)). If FIFO is used, A/D conversion data is also stored in FIFO data register (ADFIFODRk (k = 0 to 8)).

- 4. If the scan end interrupt is enabled, the scan end interrupt corresponding to that scan group is generated when the A/D conversion of all virtual channels assigned to that scan group is completed.

- 5. During the scanning operation, ADGRSR.ACTGRn (n = 0 to 8) bit corresponding to that scan group is set to 1. ADSR.ADACTm (m = 0, 1) bit corresponding to the A/D converter performing the A/D conversion is also set to 1. When scanning operation is complete, each bit is cleared to 0 and A/D converter enters the idle state.

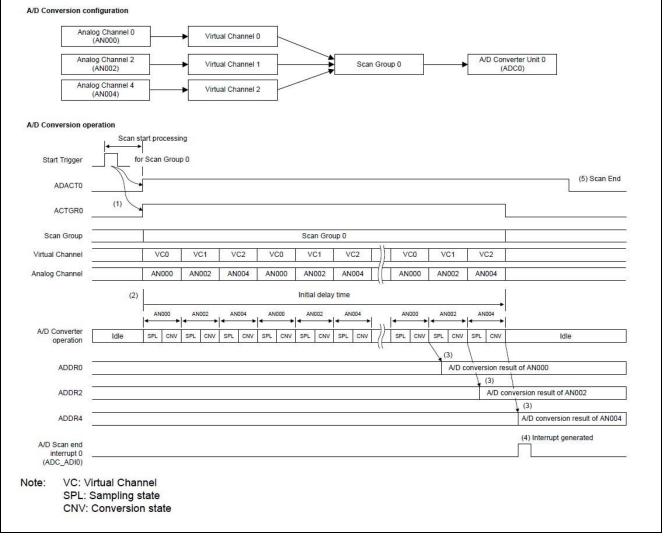

Following is an example timing diagram of the scanning operation in oversampling mode – single scan mode:

#### Figure 4. Timing diagram of Oversampling Mode – Single-Scan Mode

In this example ADC analog channels 0, 2, and 4 are assigned to virtual channels 0, 1, and 2, respectively. All the virtual channels are assigned to scan group 0 and are converted by ADC0. The order of scanning of the virtual and analog channels are shown. Each analog channel is oversampled to convert one ADC data sample.

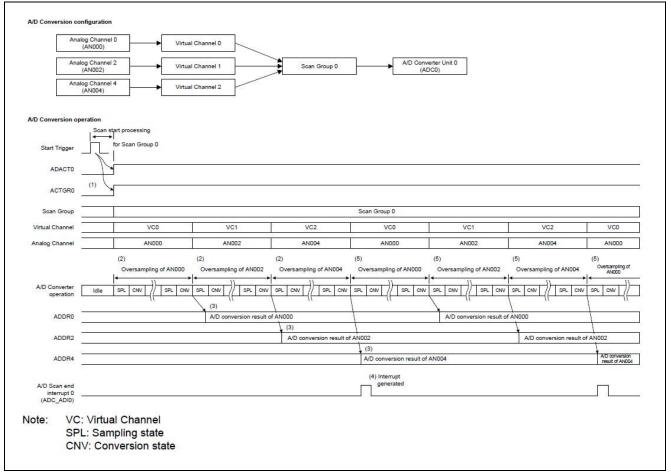

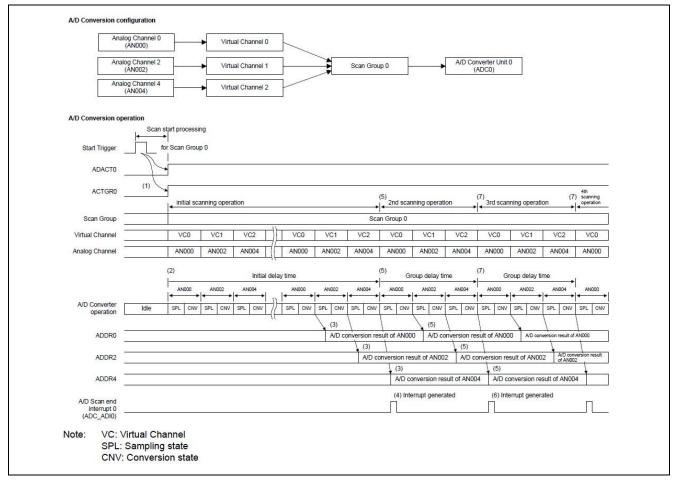

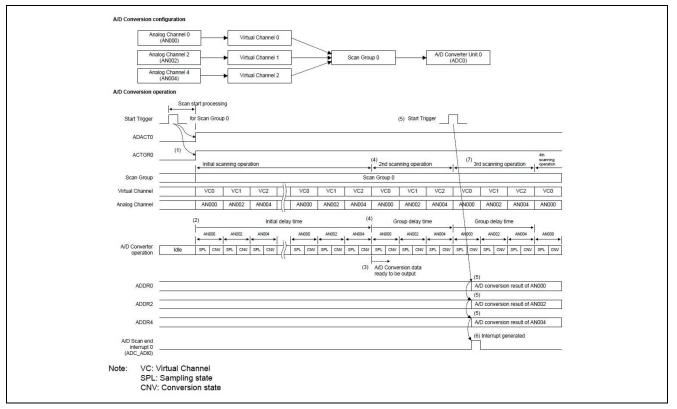

## 2.2.2 Oversampling Mode – Continuous Scan Mode

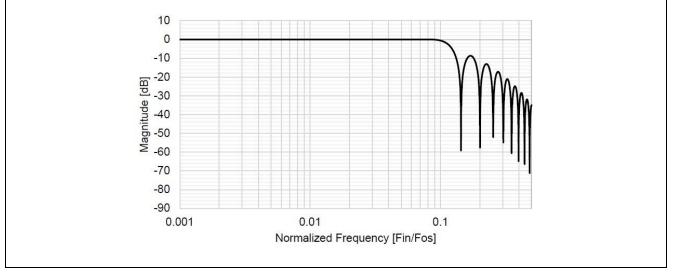

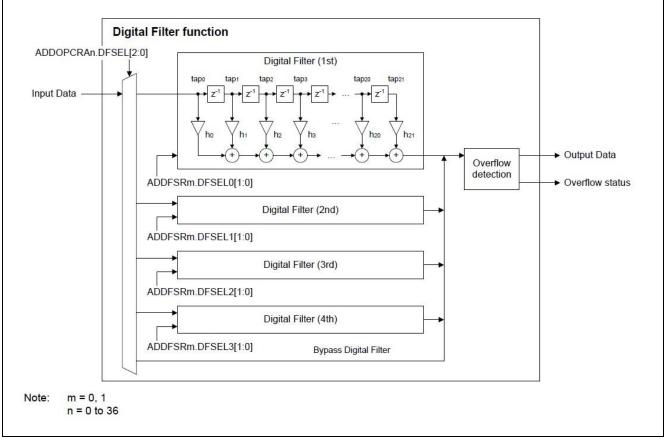

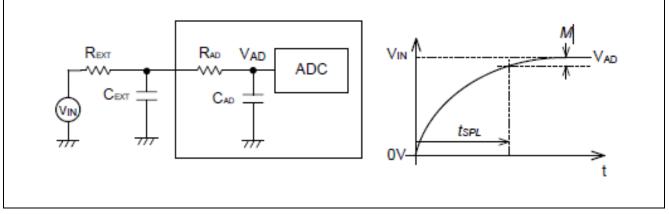

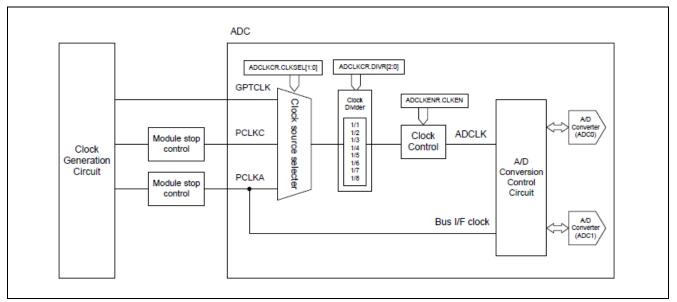

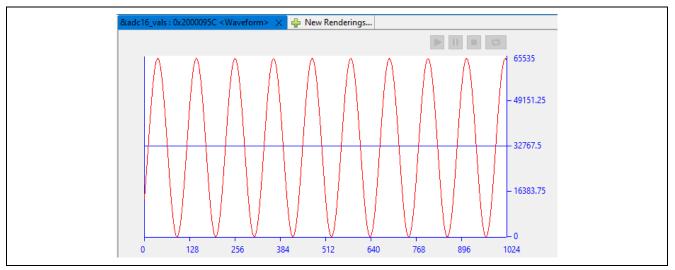

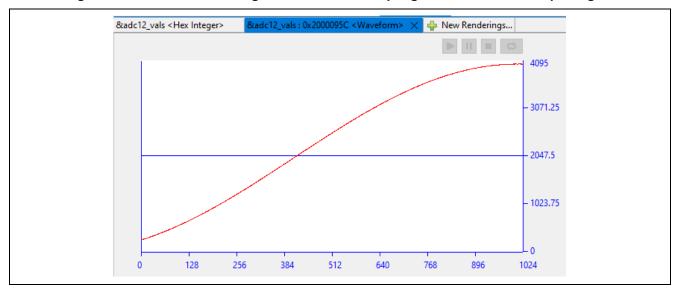

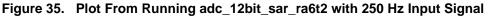

The following steps detail the procedure of Oversampling Mode – Continuous-Scan Mode: