### Introduction

Cascading PLLs is more common practice than most people think. The majority of clock generators use a crystal in the range 20MHz to 40MHz and then use a PLL to synthesize the desired output clock. The application that receives the clock will synthesize it further up to make Gb/s line rates or GHz processor speeds, for example. Sometimes there is a zero-delay buffer involved as well, causing a cascade of three PLLs.

Some literature discourages cascading of PLLs, mostly because jitter peaking adds up when cascading PLLs. This application note shows examples of how jitter peaking accumulates when cascading PLLs and how the accumulation can be limited. It may be easier to adjust PLL properties to allow for cascading than to try and avoid using PLLs altogether.

# **PLL Theory**

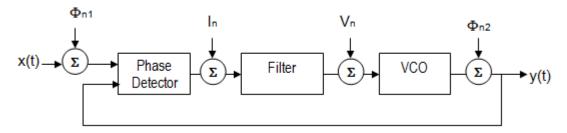

A PLL is a feedback system that adjusts the output such that it is phase aligned with the input. Moreover, in the lock condition, the phase difference between the input and output is constant with time. A simple block diagram of the system is shown in Figure 1. Notice the terms:  $\Phi_{n1}$  – noise from outside the PLL,  $I_n$  – noise from the phase detector and filter,  $V_n$  – noise on the VCO control voltage, and  $\Phi_{n2}$  – noise from the VCO. In an ideal PLL, these terms would not exist and the output, y(t), would be jitter free. However, these noise sources do exist and they manifest themselves as jitter on the output. The first critical observation: PLLs generate jitter. The jitter characteristic is a complex function of all the noise sources.

For phase noise entering at x(t) at the input, the PLL behaves as a low-pass filter. The PLL will track and pass low frequency phase noise and will attenuate high frequency phase noise. It will do that with a  $2^{nd}$  or higher order response. A  $2^{nd}$  order response can have a Q factor that creates some amplification near the loop bandwidth before the curve rolls off to the attenuation side.

Figure 1. PLL Block Diagram

# **Jitter Peaking Accumulation**

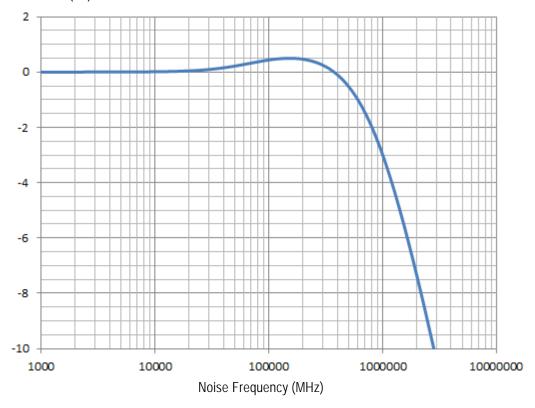

Figure 2 is an example of a PLL noise transfer curve that has a small amount of amplification near the loop bandwidth. This amplification is called jitter peaking. In this example, the jitter peaking is 0.5dB and the loop bandwidth is 1MHz.

Figure 2. Phase Noise Transfer Function with 0.5dB Jitter Peaking

Noise Transfer (dB)

Cascading two PLLs of identical bandwidth with 0.5dB jitter peaking results in a combined jitter peaking of 1dB. Cascading three PLLs of identical bandwidth with 0.5dB jitter peaking results in a combined jitter peaking of 1.5dB. The jitter peaking increases with each added PLL and may increase beyond what the system can tolerate.

There are two ways to prevent combined jitter peaking from increasing:

- 1. Design the individual PLLs with very low jitter peaking so the combined jitter peaking when cascading multiple PLLs is still within the system requirement.

- 2. Use PLLs with different loop bandwidths so the peaking is not accumulating at the same noise frequency. The peaking is distributed over a wider frequency range instead of accumulating in a narrow frequency range.

In practice, a combination of both methods is commonly used to limit jitter peaking in a clock distribution system. A good example of such a clock distribution system is PCI Express<sup>®</sup>. The clock generator can be a CK420, followed by a DB1900 zero-delay buffer to fan-out the clocks. Both are designed to be used in this fashion, with the CK420 bandwidth set to much less than 1MHz and the DB1900Z bandwidth selectable as either 1MHz or 3MHz. The combination of zero-delay ICs meets the PCI Express system requirements. The PCI Express system requirements are 3dB maximum peaking for generations 1 and 2 and 2dB maximum peaking for generations 3 and 4.

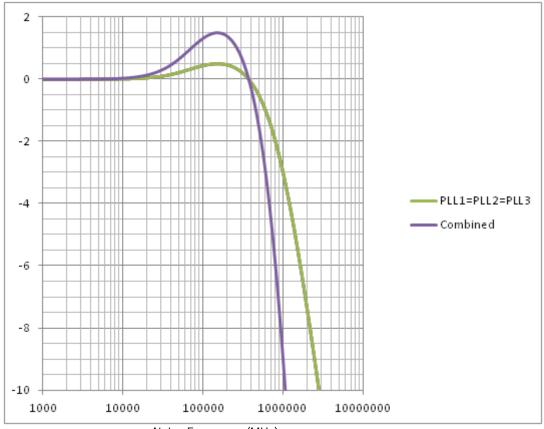

Figure 3 is an example with 3 cascaded PLLs, each with 0.5dB jitter peaking.

Figure 3. Cascading 3 PLLs, each with 0.5dB Jitter Peaking

Noise Transfer (dB)

Noise Frequency (MHz)

The combined transfer function of these three identical PLLs has 1.5dB peaking and still meets all PCI Express requirements.

Worst case is when the three PLLs have exactly the same loop bandwidth where the combined jitter peaking is the sum of the jitter peaking of each individual PLL. To ensure the acceptable combined jitter peaking is not violated, design the individual PLLs with jitter peaking below half the acceptable value, in the case of cascading two PLLs, and below one third the acceptable value in the case of cascading three PLLs.

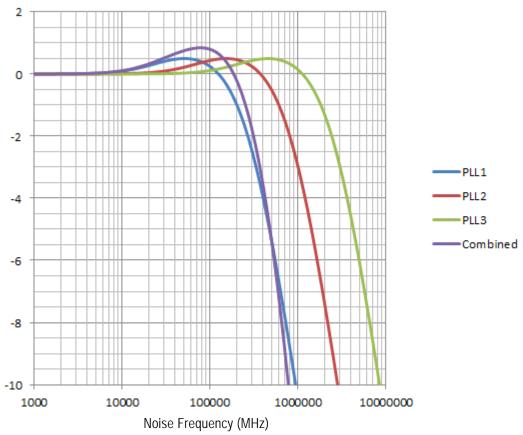

Figure 4 is an example with 3 cascaded PLLs, each with 0.5dB jitter peaking. To limit the peaking of the combined noise transfer, the loop bandwidths are set a factor 3 apart.

Figure 4. Cascading 3 PLLs, a Factor 3 Apart, each with 0.5dB Jitter Peaking

Noise Transfer (dB)

The combined transfer function of these three PLLs shows 0.85dB jitter peaking. With three identical loop bandwidths, the jitter peaking grows from 0.5dB to 1.5dB, a 1dB increase. When spreading the loop bandwidths a factor 3 apart, jitter peaking grows from 0.5dB to 0.85dB, a growth of only 0.35dB.

Spreading the loop bandwidths of cascaded PLLs farther apart can further lower the accumulated jitter peaking. If the PLL bandwidths can be separated by a factor of 10, the combined jitter peaking of three PLLs with individual jitter peaking of 0.5dB, can be lowered to 0.53dB, an increase of only 0.03dB.

A useful rule of thumb is this: the closer a single PLL's jitter peaking is to the system limit in a cascade chain, the further apart the loop bandwidths of the cascaded PLLs need to be. With a 1dB system jitter peaking limit, we have shown that a factor of three bandwidth separation is sufficient for a cascade of three PLLs. The jitter peaking due to this PLL configuration is only 0.85dB, well under the 1dB limit.

Table 1. Jitter Peaking versus Loop Bandwidth Ratio Examples

| Jitter Peaking (dB) |      |      | Loop Bandwidth |          |          | Combined Jitter Peaking |

|---------------------|------|------|----------------|----------|----------|-------------------------|

| PLL1                | PLL2 | PLL3 | PLL1           | PLL2     | PLL3     | (dB)                    |

| 1.0                 | 1.0  | 1.0  | REF / 1        | REF      | REF × 1  | 3.00                    |

|                     |      |      | REF / 2        | REF      | REF × 2  | 2.07                    |

|                     |      |      | REF/3          | REF      | REF × 3  | 1.49                    |

|                     |      |      | REF / 5        | REF      | REF × 5  | 1.17                    |

|                     |      |      | REF / 10       | REF      | REF × 10 | 1.04                    |

|                     | 0.5  | 0.5  | REF / 1        | REF      | REF × 1  | 1.50                    |

| 0.5                 |      |      | REF / 2        | REF      | REF × 2  | 1.15                    |

|                     |      |      | REF/3          | REF      | REF × 3  | 0.85                    |

|                     |      |      | REF / 5        | REF      | REF × 5  | 0.63                    |

|                     |      |      | REF / 10       | REF      | REF × 10 | 0.53                    |

|                     | 0.2  | 0.2  | REF / 1        | REF      | REF × 1  | 0.60                    |

|                     |      |      | REF / 2        | REF      | REF × 2  | 0.51                    |

| 0.2                 |      |      | REF/3          | REF      | REF × 3  | 0.39                    |

|                     |      |      | REF / 5        | REF      | REF × 5  | 0.29                    |

|                     |      |      | REF / 10       | REF      | REF × 10 | 0.22                    |

| 0.5                 | 0.5  | 0.5  | REF / 10       | REF      | REF × 2  | 0.54                    |

| 0.5                 | 0.5  | 0.5  | REF/2          | REF      | REF × 10 | 0.92                    |

| 0.5                 | 0.5  | N/A  | REF            | REF × 1  | N/A      | 1.00                    |

|                     |      |      | REF            | REF × 2  | N/A      | 0.90                    |

|                     |      |      | REF            | REF × 3  | N/A      | 0.78                    |

|                     |      |      | REF            | REF × 5  | N/A      | 0.62                    |

|                     |      |      | REF            | REF × 10 | N/A      | 0.53                    |

The absolute value of the loop bandwidth is irrelevant, so the table above is set up with loop bandwidth ratios. It calls PLL2 the reference and shows the ratio of PLL1 and PLL3 versus the PLL2 loop bandwidth. The last rows are for two PLLs, and PLL1 is used as the reference. The two rows with unequal loop bandwidth ratios for PLL1–2 and PLL2–3 shows how the PLL1–2 ratio is more important than the PLL2–3 ratio. This can also be observed in Figure 4 where the combined jitter transfer plot follows most closely the PLL1 jitter transfer plot. The PLL2 loop bandwidth is the closest to PLL1 and has the largest influence on the combined plot. PLL3 has the largest ratio versus PLL1 and affects the combined plot the least.

## Conclusion

These examples show how to control jitter peaking when cascading PLLs. In practice, a combination of minimizing jitter peaking, and separating loop bandwidths is used. Table 1 shows the results of cascading PLLs with various jitter peaking and bandwidth values.

IDT provides clock generators and zero-delay buffers for PCI Express clock trees. The devices are designed such that cascading the clock generator's PLL, the zero-delay buffer's PLL and the PCIe chipset PLL works without excessive jitter peaking and stays well within the PCI Express requirements. Other markets may have different jitter peaking requirements than PCI Express, but the principles shown in this application note are still applicable.

# **Revision History**

### **Table 2. Revision History**

| Revision Date | Description of Change                                  |  |  |  |

|---------------|--------------------------------------------------------|--|--|--|

| July 21, 2017 | Numerous text updates and changes on pages 2, 4 and 6. |  |  |  |

| June 30, 2017 | Initial release.                                       |  |  |  |

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Disclaimer Rev.5.0-1)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>