# Video Amplifier with Sync Stripper and DC Restore (EL8102)

Application Note

October 19, 2004

AN9514.1

### Introduction

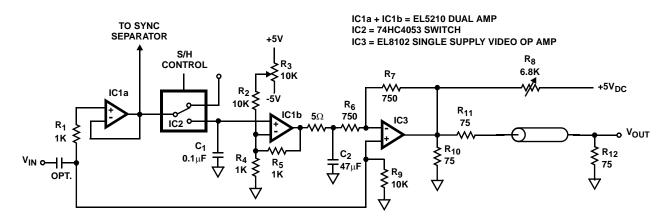

The circuit in Figure 1 transmits 200MHz (-3dB bandwidth) video signals while stripping off the sync pulse and performing DC restoration. It is configured for a typical video cable driver application driving a double-terminated  $75\Omega$  load, where the EL8102 (IC3) is configured for a gain of +2 to ensure unity gain throughout.

# Sync Stripping

In component video systems it is frequently necessary to remove the sync pulse from an RGB signal. Sync is often combined with one or more of the red, green, and blue video signals in video distribution amplifiers, routers and switchers to decrease the number of input and output channels required in a switching network. In many applications, however, as the video signals exit the switching network the sync pulse must be removed.

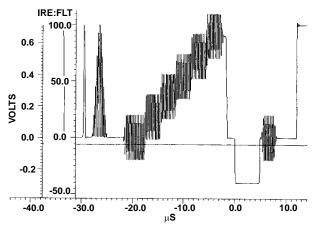

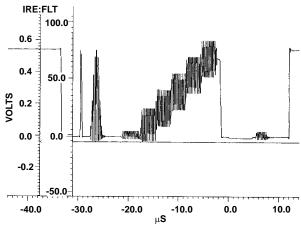

The EL8102 video op amp is specially designed to perform sync stripping. Its open emitter NPN output forms an emitter-follower with the load resistor, and passes the active video signal while virtually eliminating the negative sync pulse (see Figure 2). Residual sync of the EL8102, defined as the remainder of the original -300mV sync pulse, referenced to ground, is only 8mV at the cable output. A particular advantage of sync stripping with the EL8102 is the resultant larger (by 0.7V) output voltage swing, compared to simply using a wideband video op amp with an external emitter-follower.

Because the EL8102 contains no active pull-down, output linearity degrades as the signal approaches ground. To deal with this a  $6.8k\Omega$  pull-up resistor (R<sub>8</sub>) and a  $75\Omega$  pull down resistor (R<sub>10</sub>) on the output ensure a fixed positive voltage offset, in this case +50mV. This offset was arbitrarily chosen as a good compromise between linearity near the DC level and minimum residual sync. Increasing R<sub>8</sub> decreases residual sync, at the expense of linearity. Conversely, decreasing R<sub>8</sub> decreases linearity error, but increases residual sync. Other applications benefitting from sync removal are HDTV systems and video digitizing circuits. Consider a typical 1V<sub>P-P</sub> RGB video signal with a -300mV sync pulse and +700mV video data. By stripping off the unwanted sync pulse and digitizing only the active video, designers can use the full dynamic range of the A/D converter for the +700mV video data. This results in a 30% increase in resolution using the same A/D converter.

## **DC** Restore

Another common video function is DC restoration, used when AC coupled signals have lost their DC reference and must have it periodically reset in order to retain brightness information.

This circuit accomplishes DC restoration using a CA5260 dual op amp (IC1a, IC1b) coupled with a sample-and-hold circuit based on the 74HC4053 switch (IC2).  $V_{IN}$ , consisting of the input video signal and a DC offset ( $V_{DC}$ ), is routed to the non-inverting input of the EL8102 (IC3). The EL8102 is configured in a gain of +2 (to compensate for the attenuation resulting from double terminating the cable), which would result in an output of 2 x  $V_{IN}$  = (2 x Video + 2 x  $V_{DC}$ ), if not for the DC restore circuit.

FIGURE 1. EL8102 BASED VIDEO AMPLIFIER WITH SYNC STRIPPING AND DC RESTORE

## Application Note 9514

$V_{IN}$  also travels through half of the dual CA5260 amplifier to the sample-and-hold circuit, where the  $0.1\mu F$  capacitor (C1) is the hold capacitor. The sample-and-hold control is triggered by a back-porch pulse from a sync separator or by a horizontal video blanking signal. The DC output signal ( $V_{DC}$ ) from the sample-and-hold circuit is then amplified at a gain of +2 by the second op amp (IC1b); the gain is required because  $V_{DC}$  is input to the EL8102s inverting input which provides only a gain of -1, but as discussed earlier, the output contains a term of 2 x  $V_{DC}$ . Thus 2 x  $V_{DC}$  is summed into the EL8102 inverting input, is subtracted from the output signal, and yields a DC restored video signal.

FIGURE 2A. VIDEO AND SYNC GO IN

Because the output impedance of IC1b is high, and would affect the gain at the non-inverting input of the EL8102, a  $47\mu\text{F}$  capacitor (C<sub>2</sub>) is used to provide an AC ground and to maintain good high-frequency gain accuracy.

A potentiometer (R<sub>3</sub>) is used prior to IC1b to null out any offset voltage contributed by the DC restore circuitry.

#### Conclusion

The circuit's resultant output is a 200MHz, DC restored video signal in which the sync pulse has been stripped to a residual level of no more than 8mV.

FIGURE 2B. ONLY VIDEO COMES OUT

FIGURE 2. SIGNALS AT EL8102 INPUT AND CABLE OUTPUT

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com