# **Application Note**

# Analog Front-End for Electrocardiogram Monitor AN-CM-326

## Abstract

This application note describes the design of an analog front-end for an electrocardiography device. The circuit utilizes the commonly used technique of measuring electrical heart activity using three electrodes applied to the arms and legs. These electrodes detect the small electrical signal that results from cardiac muscle contraction (the heartbeat). The unique auto-trim feature of the SLG47004 enables output signal level stabilization in conditions of interference and baseline drift. The application note also contains test results of a hardware prototype.

This application note comes complete with design files which can be found in the References section.

# Contents

| Ab  | stract                                        |                                          | . 1 |  |  |  |

|-----|-----------------------------------------------|------------------------------------------|-----|--|--|--|

| Со  | ntent                                         | S                                        | . 2 |  |  |  |

| Fig | ures.                                         |                                          | . 2 |  |  |  |

| 1   | Term                                          | is and Definitions                       | 3   |  |  |  |

| 2   | Refe                                          | rences                                   | 3   |  |  |  |

| 3   | ECG Basics and Analog Front-End Requirements4 |                                          |     |  |  |  |

| 4   | Тор                                           | Structure of the Analog Front-End        | . 4 |  |  |  |

|     | 4.1                                           | Typical Human ECG Waveform               |     |  |  |  |

| 5   | SLG                                           | 47004 Internal Design                    | 5   |  |  |  |

|     | 5.1                                           | Electrical Schematic of Analog Front-End | 6   |  |  |  |

| 6   | Inter                                         | nal Block Configuration                  | 6   |  |  |  |

|     | 6.1                                           | OpAmp0 and OpAmp1 Configurations         | 6   |  |  |  |

|     | 6.2                                           | Internal OpAmp Configuration             | . 7 |  |  |  |

|     | 6.3                                           | HD Buffer Configuration                  | . 7 |  |  |  |

|     | 6.4                                           | Rheostat0 and Rheostat1 Configuration    | 8   |  |  |  |

|     | 6.5                                           | Oscillator Configurations                | 9   |  |  |  |

|     | 6.6                                           | I <sup>2</sup> C Macrocell Configuration | 9   |  |  |  |

|     | 6.7                                           | GPIO Configurations                      | 9   |  |  |  |

| 7   | Norn                                          | nal Operation Mode1                      | 10  |  |  |  |

| 8   | Prote                                         | otype Testing1                           | 11  |  |  |  |

| 9   | Conclusion                                    |                                          |     |  |  |  |

| Re  | visior                                        | 1 History                                | 13  |  |  |  |

# **Figures**

| Figure 1: Structure of ECG Analog Front-End                      | 4 |

|------------------------------------------------------------------|---|

| Figure 2: Typical ECG of Healthy Heart                           |   |

| Figure 3: Design Configuration of SLG47004                       |   |

| Figure 4: Electrical Schematic of Analog Front-End               |   |

| Figure 5: Operational Amplifier 0 and 1 Settings                 |   |

| Figure 6: Internal OpAmp Settings                                |   |

| Figure 7: HD Buffer and OpAmp0 Vref Settings                     |   |

| Figure 8: Digital Rheostat 0 and 1 Settings                      |   |

| Figure 9: Oscillator 0 and 1 Settings                            |   |

| Figure 10: GPIO Settings                                         |   |

| Figure 11: Seven Second Heart Waveform (500 mV/div, 500 ms/div). |   |

| Figure 12: Zoomed Heart Waveform (100 mV/div, 500 ms/div)        |   |

| Figure 13: Raw Digitized Signal                                  |   |

| Figure 14: Signal Without 50 Hz Noise                            |   |

| Figure 15: Signal After Median Filter                            |   |

**Application Note**

#### **1** Terms and Definitions

| AFE     | Analog Front-End          |

|---------|---------------------------|

| ECG     | Electrocardiogram         |

| HR      | Heart Rate                |

| IC      | Integrated Circuit        |

| OpAmp   | Operational Amplifier     |

| INSTAmp | Instrumentation Amplifier |

#### 2 References

For related documents and software, please visit:

https://www.dialog-semiconductor.com/products/greenpak/analog-greenpaks/slg47004

Download our free GreenPAK Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in a complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] GreenPAK Designer Software, Software Download and User Guide

- [2] AN-CM-326 Analog Front-End for Electrocardiogram Monitor.gp, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

- [5] SLG47004, Datasheet

- [6] Filters for ECG digital signal processing / Ondracek O., Jozef P., Elena C. // International Conference "Trends in Biomedical Engineering". - University of Zilina, September 7 - 9, 2005. P. 91-96

- [7] ECG Noise Cancellation Using Digital Filters / Hosseini H., Nazeran H., Reynolds K. // 2nd International Conference on Bioelectromagnetism, 1998. P. 151-152

Author: Svyatoslav Skalskyy

# 3 ECG Basics and Analog Front-End Requirements

An electrocardiogram is a recorded electrical signal resulting from a contraction of heart muscles. It can detect deviation from a normal heartbeat and can be used to diagnose illnesses or optimize a training load. The signal must first be amplified to a level that is suitable for recording (electrodes on the arms can give voltages in the range of tens of microvolts to a millivolt peak-to-peak). The bandwidth of the signal is from 0.05 to 100 Hz. To amplify such a small signal, an amplifier with a gain of around 1000 should be applied. AC interference from the power grid should be canceled out along with DC offsets from the electrodes. As a rule, an instrumentation amplifier with a large common-mode voltage suppression is used. The common mode voltage is then amplified, inverted, and fed into a leg electrode for active interference suppression. Additionally, a low-pass filter, high pass filter, and band suppression filter are applied after amplification.

All electrical connections of the amplifier have to be isolated from mains and from devices supplied from it. It is difficult to construct a power supply with a small amount of stray capacitance to mains, so we will choose a battery-powered device, which will provide a simple solution for a low cost and isolated power source with a minimum amount of stray capacitance.

The SLG47004 can deliver only one instrumentation amplifier, so we will use AC filtering on the digital side. We will use a simple DC reference point for a leg electrode without active interference cancellation.

## 4 Top Structure of the Analog Front-End

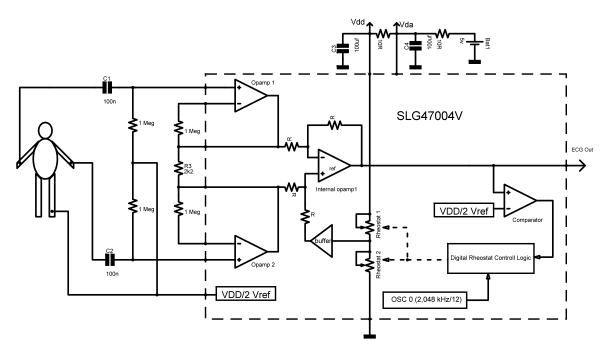

The simplified structural scheme is shown in Figure 1.

Figure 1: Structure of ECG Analog Front-End

| A  |       | 41.0.00 |      |

|----|-------|---------|------|

| AP | piica | τιση    | Note |

#### 4.1 Typical Human ECG Waveform

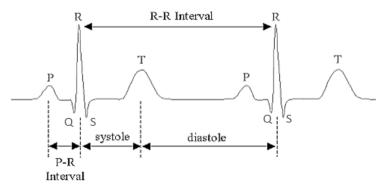

A typical electric signal from a heart, picked up by the electrodes on the arms, is shown in Figure 2. The typical ECG waveform has 5 peaks called P-Q-R-S-T. These peaks correspond to the activity of different parts of the heart.

Figure 2: Typical ECG of Healthy Heart

## 5 SLG47004 Internal Design

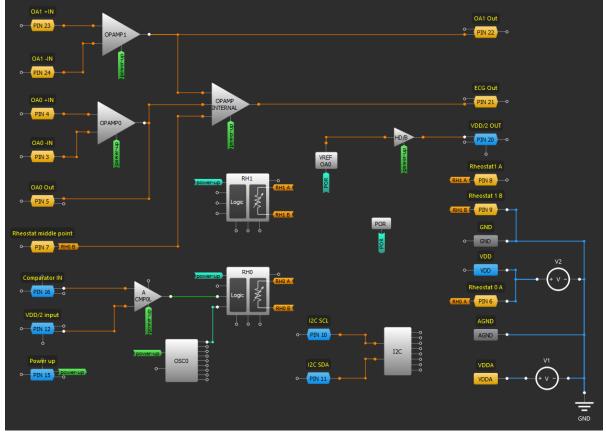

The proposed design configuration is shown in Figure 3.

Figure 3: Design Configuration of SLG47004

| Application Note | Revision 1.0 | 08-Oct-2021 |

|------------------|--------------|-------------|

|                  |              |             |

#### 5.1 Electrical Schematic of Analog Front-End

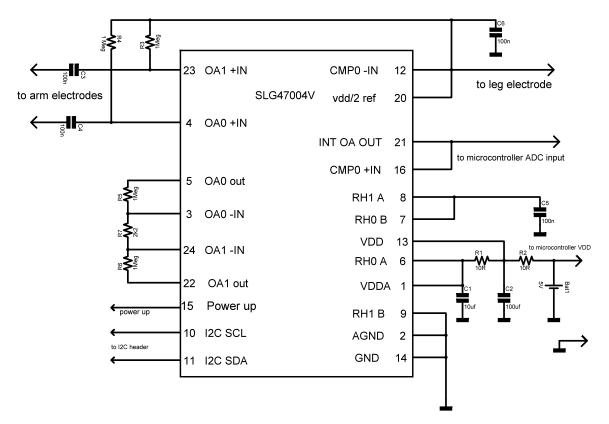

The electrical schematic of the analog front-end is shown in Figure 4.

Figure 4: Electrical Schematic of Analog Front-End

#### 6 Internal Block Configuration

#### 6.1 **OpAmp0 and OpAmp1 Configurations**

OpAmp0 and 1 use the same configuration, shown in Figure 5.

| Mode:                        | OpAmp mode       | - |

|------------------------------|------------------|---|

| Bandwidth<br>Selection:      | 128 kHz          | • |

| Charge Pump:                 | Enable CP        | - |

| Supporting<br>Blocks On/Off: | Always On        | - |

| Vref connection:             | Disconnected     | • |

| Vref:                        | VDDA * (32 / 64) | - |

| 0 5                          | Apply            |   |

Figure 5: Operational Amplifier 0 and 1 Settings

|    | 1.1.1  | 1.1 | N    |

|----|--------|-----|------|

| Δn | nlicat | hon | NOto |

|    | Jiica  |     | Note |

#### 6.2 Internal OpAmp Configuration

The internal OpAmp configuration is shown in Figure 6.

| OPAMP INTERNAL               |           |   |  |  |  |

|------------------------------|-----------|---|--|--|--|

| Bandwidth<br>Selection:      | 128 kHz   | - |  |  |  |

| Charge pump:                 | Enable CP | - |  |  |  |

| Supporting<br>Blocks On/Off: | Always On | • |  |  |  |

| Vref input buffer:           | Enable    | - |  |  |  |

| Vref source:                 | RH0 PIN B | • |  |  |  |

| OpAmp1 Vref:                 | 2048 mV   | Ŧ |  |  |  |

|                              | Apply     |   |  |  |  |

Figure 6: Internal OpAmp Settings

#### 6.3 HD Buffer Configuration

The HD Buffer shares the voltage reference with OpAmp0. In the current project, the internal Vref is disconnected from OpAmp0. The HD Buffer and OpAmp0 Vref configurations are shown in Figure 7.

| HD Buffer                                 |                       |   | VREF                                  | OPAMP0                     |   |

|-------------------------------------------|-----------------------|---|---------------------------------------|----------------------------|---|

| Power up source:<br>Power up<br>register: | From matrix<br>Enable | • | Enable selection:<br>Register enable: | From matrix<br>Vref enable | • |

| Con                                       | nections              |   |                                       |                            | _ |

| Input:                                    | VREF OPAMP0           | - | Input voltage<br>selection:           | VDDA                       | • |

| Output:                                   | PIN 20 (GPIO6)        | - | Output selection:                     | VDDA * (32 / 64)           | • |

|                                           | <b>D</b> Apply        |   |                                       | Apply                      |   |

Figure 7: HD Buffer and OpAmp0 Vref Settings

#### 6.4 Rheostat0 and Rheostat1 Configuration

The rheostat in this project is configured as a digital potentiometer. Its configuration is shown in Figure 8.

| Digita                               | Rheostat0             | Digital | Rheostat1                            |                    |

|--------------------------------------|-----------------------|---------|--------------------------------------|--------------------|

| Mode:                                | None                  | -       | Mode:                                | Potentiometer 💌    |

| Charge Pump<br>Enable:               | Always On 🔻           | •       | Charge Pump<br>Enable:               | From matrix 💌      |

| Charge Pump<br>Clock: <sup>(7)</sup> | OSC1 •                |         | Charge Pump<br>Clock: <sup>(7)</sup> | OSC1 💌             |

| Auto-Trim:                           | Disable -             |         | Auto-Trim:                           | Disable 🔻          |

| Active level for<br>UP/DOWN:         | Up when LOW           | •       | Active level for<br>UP/DOWN:         | Up when HIGH 🔹     |

| Resistance (initial                  | 497                   | \$      | Resistance (initial                  | 526 \$             |

| data):                               | (Range: 0 - 1023)     |         | data):                               | (Range: 0 - 1023)  |

| Con                                  | nections              |         | Con                                  | nections           |

| UP/DOWN<br>source:                   | Ext. (From matrix)    | -       | UP/DOWN<br>source:                   | Chopper ACMP 🔹     |

| Clock:                               | Ext. Clk. (From mat 🔻 |         | Clock:                               | From Chopper ACI 💌 |

|                                      | Apply                 |         |                                      | Apply              |

Figure 8: Digital Rheostat 0 and 1 Settings

#### 6.5 Oscillator Configurations

The configurations of Oscillator 0 and 1 are shown in Figure 9.

| OSC0                                                         |                                        |         | (                                          | OSC1                       |   |

|--------------------------------------------------------------|----------------------------------------|---------|--------------------------------------------|----------------------------|---|

| Control pin<br>mode:<br>OSC power<br>mode:                   | Force on<br>Force Power On             | •       | Control pin<br>mode:<br>OSC power<br>mode: | Force on<br>Force Power On | • |

| Clock selector:                                              | OSC                                    | •       | Clock selector:                            | OSC                        | • |

| 'OSC0' frequency:                                            | 2.048 kHz                              | -       | 'OSC1' frequency:                          | 2.048 MHz                  | Ŧ |

| 'CLK' predivider<br>by:                                      | 1                                      | •       | 'CLK' predivider                           | 1                          | • |

| 'OUT0' second<br>divider by:<br>'OUT1' second<br>divider by: | 12                                     | •       | 'OUT0' second<br>divider by:               | 1                          | • |

| Info                                                         | ormation                               |         | 'OUT1' second<br>divider by:               | 1                          | • |

| Frequency                                                    |                                        |         | Infe                                       | ormation                   |   |

| Clock output config                                          | guration:                              |         |                                            |                            |   |

| RC OSC Output                                                | Value                                  | _       | Frequency                                  |                            |   |

| OUTO                                                         | OSC0 Freq. /12                         | -       | Clock output config                        | guration:                  |   |

| OUT1                                                         | OSC0 Freq.                             |         | RC OSC Output                              | Value                      | _ |

| CLK                                                          | OSC0 Freq.                             |         | OUT0                                       | OSC1 Freq.                 |   |

| CLK /8                                                       | OSC0 Freq. /8                          | -       | OUT1                                       | OSC1 Freq.                 |   |

| CLK /64                                                      | OSC0 Freq. /64                         |         | CLK                                        | OSC1 Freq.                 |   |

| CLK /512 OSC0 Freq. /512                                     |                                        | CLK /8  | OSC1 Freq. /8                              |                            |   |

| CLK /4096 OSC0 Freq. /4096                                   |                                        | CLK /64 | OSC1 Freq. /64                             |                            |   |

| CLK /32768<br>CLK /262144                                    | OSC0 Freq. /32768<br>OSC0 Freq. /26214 |         | CLK /512                                   | OSC1 Freq. /512            |   |

|                                                              | Apply                                  |         |                                            | Apply                      |   |

Figure 9: Oscillator 0 and 1 Settings

#### 6.6 I<sup>2</sup>C Macrocell Configuration

The I<sup>2</sup>C macrocell uses default configurations.

#### 6.7 **GPIO Configurations**

GPIO Pin 17,18,19,10, and 11 have the default configuration. The remaining GPIO configurations are shown in Figure 10.

| Ap | DIIC | ation | Note |

|----|------|-------|------|

|    |      |       |      |

| PIN 21 (GPI0)          |                     | PIN                    | PIN 20 (GPIO6)     |     | PIN 12 (GPIO0)         |                   |  |

|------------------------|---------------------|------------------------|--------------------|-----|------------------------|-------------------|--|

| I/O selection:         | Analog input/out; 🔻 | I/O selection:         | Analog input/out;  | - V | O selection:           | Analog input/out; |  |

| Input mode:<br>OE = 0  | Analog input/out; 🔻 | Input mode:<br>OE = 0  | Analog input/out   |     | nput mode:<br>)E = 0   | Analog input/out  |  |

| Output mode:<br>OE = 1 | Analog input/out; 🔻 | Output mode:<br>OE = 1 | Analog input/out;  |     | output mode:<br>)E = 1 | Analog input/out  |  |

| Resistor:              | Floating *          | Resistor:              | Floating           | ▼ R | esistor:               | Floating          |  |

| Resistor value:        | Floating -          | Resistor value:        | Floating           | - R | esistor value:         | Floating          |  |

| PIN                    | 16 (GPIO2)          | PIN                    | 15 (GPIO1)         |     |                        |                   |  |

| I/O selection:         | Analog input/out; 🔻 | // selection:          | Digital input      | -   |                        |                   |  |

| Input mode:<br>OE = 0  | Analog input/out; 🔻 | Input mode:<br>OE = 0  | Digital in without | •   |                        |                   |  |

| Output mode:<br>OE = 1 | Analog input/out; 🔻 | Output mode:<br>OE = 1 | None               | *   |                        |                   |  |

| Resistor:              | Floating            | Resistor:              | Pull Up            | •   |                        |                   |  |

|                        | Floating            | Resistor value:        | 100K               | -   |                        |                   |  |

Figure 10: GPIO Settings

## 7 Normal Operation Mode

Power up Pin 15 has a  $100k\Omega$  pull-up resistor, and if left floating will by default power up the oscillator, all three op amps, and the rheostat. When Pin 15 is pulled down by external components, all internal blocks shut off and the SLG47004 goes into power saving mode.

Electrodes on the skin and body have a very high impedance, so common-mode AC power interference is accepted by the electrodes.

Instrumentation amplifiers are good at rejecting common-mode signals, and they also have highimpedance inputs, which are needed for amplification of the very small signal produced by heart muscles in the noisy environment. AC signals from arm electrodes go to an RC high-pass filter (R3, R4, C3, and C4 in Figure 4) with a low cut-off frequency, which eliminates a DC offset that might be present at the input due to the electrochemical processes between the electrode, conductive paste, and the skin. An even DC bias of VDD/2 is introduced to both of the op amp inputs to shift the operation point of the op amp, preventing it from going beyond rails. The voltage divider from R6, R7, and R5 (in Figure 4) forms an external negative feedback loop for an instrumentation amplifier from three op amps in the SLG47004 and has a gain of 910.

The Internal op amp has four resistors with the same value, forming a differential amplifier with a gain of 1.

Op amps have an input offset voltage. In our case, the SLG47004 has a max 1000 uV input offset voltage. This will be amplified by a factor of 910 and can produce up to 1 V of output voltage offset and reduce headroom for our signal, clipping it to GND or VCC (keep in mind that VCC is only 5 V).

To compensate for that error, an auto-trim circuit with digital potentiometer is used. This uses an analog comparator to switch the direction of the digital potentiometer change (up/down), which is clocked by the oscillator.

We are using slow tuning of the instrumentation amplifier reference point to cancel out op amp offset voltages. Multiplied by a large gain factor, they will overload the amplifier output without compensation. A slow floating offset voltage presented by muscle shaking, somatic tremor, or

#### **Application Note**

galvanic contact of electrode metals to the skin are all sources of interference that must be canceled out. The entire circuit of the comparator, reference voltage, potentiometers, and a clock signal slowly adjust an average DC level of the amplifier to a reference voltage level, which is set to VDD/2. The rate at which the voltage at the potentiometer output is changing is proportional to a clock frequency, fed into a potentiometer block. Assuming the potentiometer has 1023 steps and is connected to a supply voltage of 5 V, and has a clock of 170 Hz, the auto-trim control loop will have a slew rate of 0.83 V/s. It will also act as a high pass filter with a very low frequency cut-off.

We must consider the error presented by the constant auto-trim process, but in most use cases this is negligible and can be tolerated. If it is undesirable, it can be configured to be switched off after a trimming period using the internal SLG47004 logic.

A reference point of VDD/2 potential is fed into the leg electrode, which also becomes present at both sides of capacitors C3 and C4, preventing them from charging (so you don't have to wait until the output signal settles due to the input capacitors' charging time).

#### 8 **Prototype Testing**

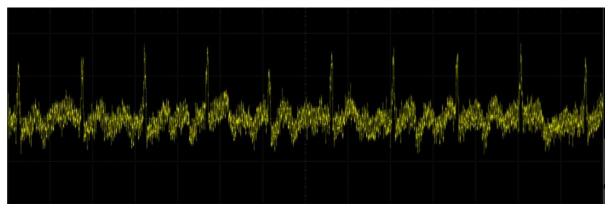

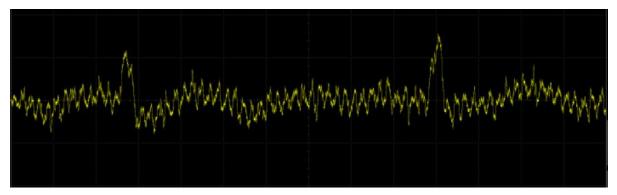

Figure 11 and Figure 12: show the waveform at the analog output of the SLG47004. The raw analog output signal has a high level of 50 Hz noise. Such measurements can't be analyzed, and this is a typical problem for electrocardiography. That's why additional filtering should be applied to the signal.

Figure 11: Seven Second Heart Waveform (500 mV/div, 500 ms/div).

Figure 12: Zoomed Heart Waveform (100 mV/div, 500 ms/div).

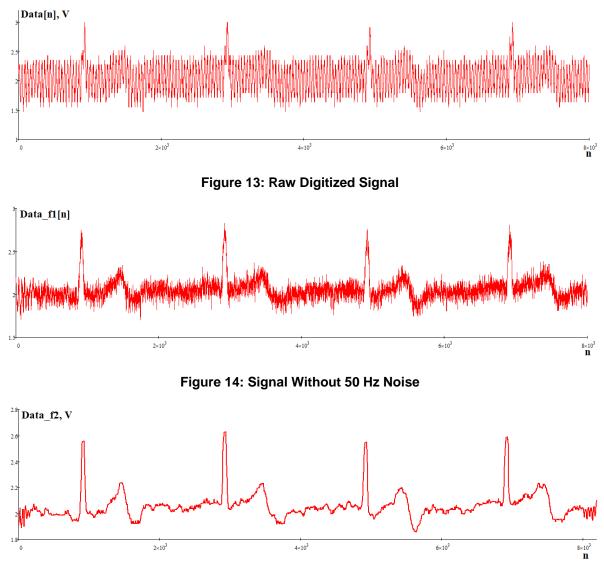

The common approach is to apply digital filters to remove power grid noise as well as other noise components [2]. There are many articles that describe and compare different digital filtering approaches [2,3]. Since the purpose of this application note is to show the performance of the analog front-end, we will skip the digital filter synthesis procedure and show the filtered signal.

#### **Application Note**

Revision 1.0

Figure 13 shows the raw digitized signal. At the 1st filtering stage 50 Hz noise was removed (Figure 14). At the 2nd filtering stage a median filter was applied to the signal (Figure 15).

Figure 15: Signal After Median Filter

## 9 Conclusion

The SLG47004 can be used as a cost-effective integrated solution for the analog front-end of an electrocardiogram monitor. Its unique auto-trim feature allows it to cancel system offset as well as to provide steady output. The embedded instrumentation amplifier provides a good common mode interference rejection, the magnitude of which is much bigger than the signal itself.

**Revision 1.0**

# **Revision History**

| Revision | Date        | Description      |

|----------|-------------|------------------|

| 1.0      | 08-Oct-2021 | Initial version. |

**Application Note**

**Revision 1.0**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.