# Application Note Bidirectional I2C to SPI Bridge AN-CM-334

# Abstract

This application note describes how to use the SLG46811 IC to design a converter between the I2C and SPI data transmission protocols. This application note comes with the design file, which can be found in the Reference section.

# Contents

| Ab  | strac           | t                                            | 1 |  |

|-----|-----------------|----------------------------------------------|---|--|

| Со  | ntent           | S                                            | 2 |  |

| Fig | jures.          |                                              | 2 |  |

| 1   | Tern            | ns and Definitions                           | 3 |  |

| 2   | Refe            | rences                                       | 3 |  |

| 3   | Intro           | duction                                      | 4 |  |

| 4   | How             | Does the Conversion Work?                    | 4 |  |

|     | 4.1             | SPI Data Reception and I2C Data Transmission | 5 |  |

|     | 4.2             | I2C Data Reception / SPI Data Transmission   | 9 |  |

| 5   | Con             | clusion1                                     | 0 |  |

| Re  | evision History |                                              |   |  |

# **Figures**

| Figure 1: Application Circuit                         |   |

|-------------------------------------------------------|---|

| Figure 2: Design Implementation                       | 5 |

| Figure 3: SPI Data Reception                          | 5 |

| Figure 4: I2C Data Transmission                       | 6 |

| Figure 5: EPG Waveform                                | 6 |

| Figure 6: Test Schematic                              | 7 |

| Figure 7: SLG46826 Internal Schematic                 | 7 |

| Figure 8: SPI Data Reception                          | 8 |

| Figure 9: I2C Data Transmission                       |   |

| Figure 10: I2C Data Reception / SPI Data Transmission | 9 |

| Figure 11: EPG Waveform                               | 9 |

| Figure 12: Testing Result                             |   |

|                                                       |   |

| <b>Application Note</b> |

|-------------------------|

|-------------------------|

## **1** Terms and Definitions

| CNT  | Counter                        |

|------|--------------------------------|

| DFF  | D flip flop                    |

| EPG  | Extended pattern generator     |

| I2C  | Inter-integrated circuit (bus) |

| IC   | Integrated circuit             |

| OE   | Output Enable                  |

| SHR  | Shift register                 |

| SPI  | Serial peripheral interface    |

| SRFF | SR flip flop                   |

|      |                                |

### 2 References

For related documents and software, please visit:

https://www.dialog-semiconductor.com/greenpak

Download our free GreenPAK<sup>™</sup> Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] GreenPAK Designer Software, Software Download and User Guide

- [2] AN-CM-334 Bidirectional I2C to SPI bridge.gp file, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

- [5] SLG46811, Datasheet

- [6] Technique: Building a Shift Register, The GreenPAK Cookbook

- [7] Technique: OE PIN, The GreenPAK Cookbook

- [8] Technique: Reading Serial Protocols with a Shift Register, The GreenPAK Cookbook

| <b>Application Not</b> | е |

|------------------------|---|

|------------------------|---|

# 3 Introduction

Many devices interact via the I2C and SPI data protocols. In this app note, we'll show how to convert between these two protocols using the SLG46811 integrated circuit (IC), a good option for this application due to its small size and high functionality combined with low cost and current.

# 4 How Does the Conversion Work?

The SLG46811V can convert in both directions, from I2C to SPI and vice versa.

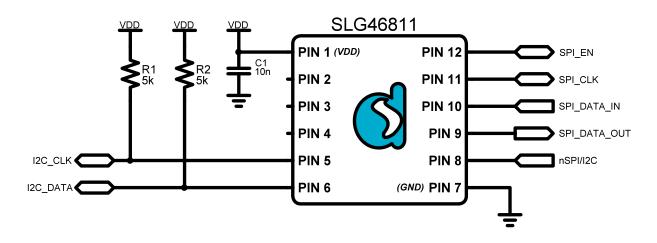

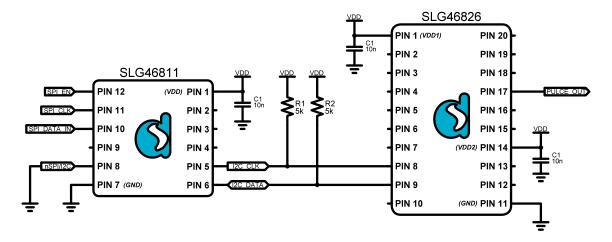

**Figure 1: Application Circuit**

Figure 1 shows a typical schematic for the converter. The I2C bus is connected to PIN5 and PIN6, and the SPI bus is connected to PIN9, PIN10, PIN11 and PIN12. PIN8 is used to control the transmission direction. The I2C bus must be pulled up to VDD.

The conversion direction is selected by the nSPI/I2C signal. This circuit provides the transmission of four bytes, one of which is the I2C control byte.

| te |

|----|

|    |

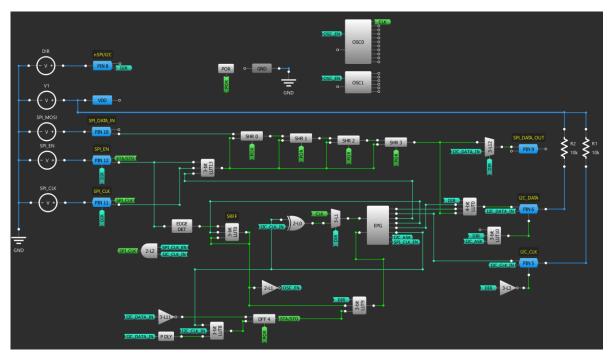

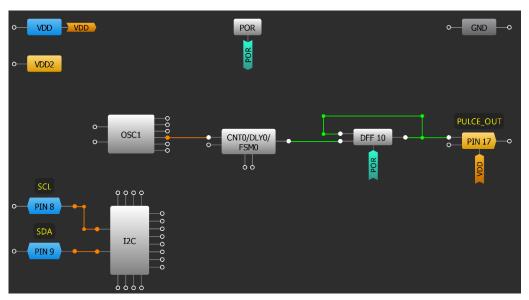

Figure 2: Design Implementation

## 4.1 SPI Data Reception and I2C Data Transmission

When the nSPI/I2C signal is low, the IC receives SPI commands and transmits I2C commands.

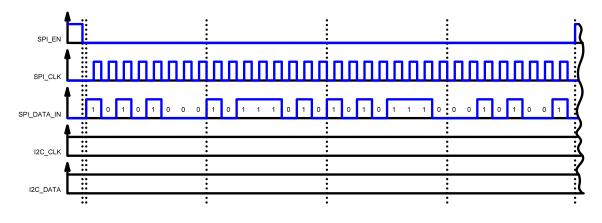

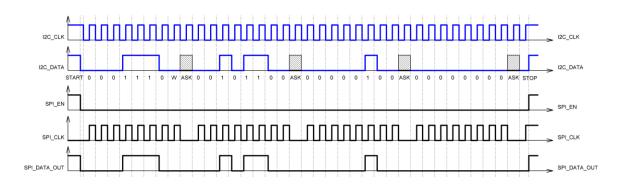

#### Figure 3: SPI Data Reception

The SPI\_EN signal determines the start and stop of SPI data reception. When the signal SPI\_EN changes from high to low, the IC reads from the input SPI\_DATA\_IN. In synch with the clock signal SPI\_CLK, the IC reads the data in the shift registers SHR 0 – SHR 3.

#### Figure 4: I2C Data Transmission

When the data is fully received, the signal SPI\_EN goes to high and the IC begins forming I2C packets. EDGE DET detects when the data is received, which translates the output of the SRFF trigger to 1. This allows the operation of the extended pattern generator (EPG) and the clock generator. The EPG unit deals with the formation of the I2C packets and controls the data issuance process.

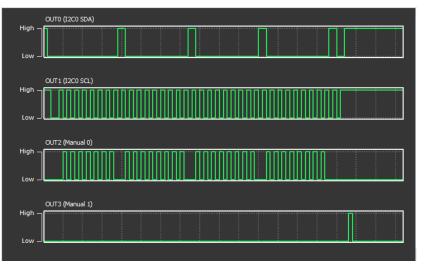

#### Figure 5: EPG Waveform

The EPG unit records a set of patterns for generating I2C operation signals. Output OUT0 is used to form the Start, Stop and ASK bits. Output OUT1 generates a clock signal for I2C\_CLK. The OUT2 signal provides a data offset in the SHR registers. Upon completion of I2C transmission, the OUT3 signal converts the SRFF trigger to 0, after which the system enters the initial state.

For example, we will try to change the counter data CNT0 in the SLG46826 using the SPI/I2C bridge.

| Application Note | Baujajan 4.0 | 04 Apr 2022 |

|------------------|--------------|-------------|

| Application Note | Revision 1.0 | 04-Apr-2022 |

Figure 6: Test Schematic

Figure 6 shows a test connection diagram of the SPI/I2C bridge built on the SLG46811 and the generator built on the SLG46826. The SLG46826 has PIN8 and PIN9 for the I2C bus connection and PIN17 for the pulse output.

Figure 7: SLG46826 Internal Schematic

The following is a legend for Figure 8:

SLG46811

Channel 1 (yellow/top line) – PIN5 (I2C\_CLK) with external  $5k\Omega$  pull up resistor

Channel 2 (light blue/2nd line) – PIN6 (I2C\_DATA) with external  $5k\Omega$  pull up resistor

B1 – I2C data decoding

B2 – SPI data decoding

D0 - PIN12 (SPI\_EN)

D1 – PIN11 (SPI\_CLK)

D2 - PIN10 (SPI\_DATA\_IN)

04-Apr-2022

#### SLG46826

D5 – PIN17 (PULSE\_OUT)

#### Figure 8: SPI Data Reception

Figure 9: I2C Data Transmission

| Application | Note |

|-------------|------|

**Revision 1.0**

## 4.2 I2C Data Reception / SPI Data Transmission

When the nSPI/I2C signal is high, the IC operates in I2C slave / SPI master mode.

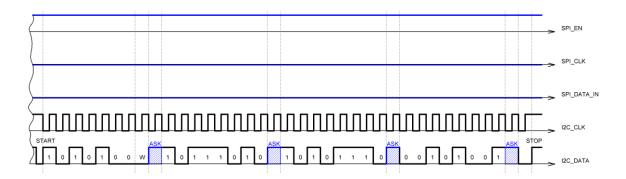

#### Figure 10: I2C Data Reception / SPI Data Transmission

In this mode, I2C data reception and SPI data transmission occur simultaneously. The following components are used to detect the I2C start / stop combination: P DLY in the EDGE mode of the detector, 3-bit LUT8, 3-L11 and DFF4. When the start combination arrives, the output of the trigger DFF4 goes to 0, which allows the EPG to operate and also activates the SPI\_EN signal. The second part of the EPG generates signals for processing data coming from the I2C, and also generates an ASK response signal. Data from I2C is transmitted immediately to the output SPI\_DATA\_OUT. SPI\_CLK is clocked with I2C\_CLK only for the time of service combination arrives, the output of the trigger DFF4 goes to 1, which puts the EPG in the initial state and signals the SPI bus signal SPI\_EN to complete the data transmission. To change the direction of operation, some IC outputs have an output enable (OE) signal.

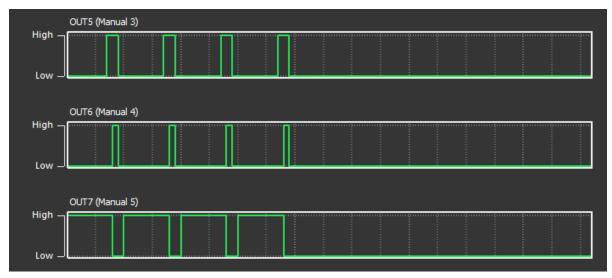

#### Figure 11: EPG Waveform

For receiving I2C commands and transmitting SPI commands we use EPG signals:

OUT5 – blocks the operation of the detector Start / Stop and inverts the CLK signal of the EPG unit when forming the ASK signal.

OUT6 – generates an ASK signal.

OUT7 – controls the SPI clock.

| Application Note | <b>Revision 1.0</b> |   | 04-Apr-2 | 2022 |

|------------------|---------------------|---|----------|------|

|                  |                     | - |          |      |

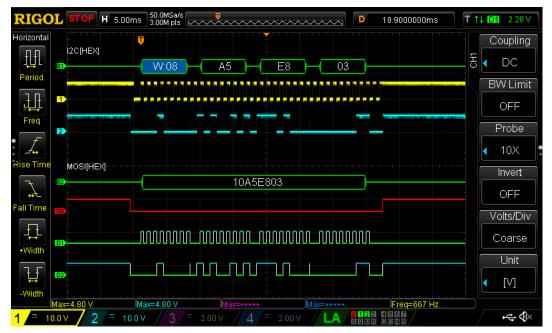

The following is a legend for Figure 12:

Channel 1 (yellow/top line) – PIN5 (I2C\_CLK) with external  $5k\Omega$  pull up resistor

Channel 2 (light blue/2nd line) – PIN6 (I2C\_DATA) with external  $5k\Omega$  pull up resistor

- B1 I2C data decoding

- B2 SPI data decoding

- D0 PIN12 (SPI\_EN)

- D1 PIN11 (SPI\_CLK)

- D2 PIN10 (SPI\_DATA\_OUT)

Figure 12: Testing Result

# 5 Conclusion

In this application note, we implemented an I2C/SPI converter using the GreenPAK SLG46811 IC. GreenPAK ICs offer a large number of functional elements to implement a variety of circuit designs. There are more than 50 ICs in the GreenPAK product family, and each has its own special features and functions. They allow for a significant reduction in the number of external circuit elements, and the ability to develop systems with highly specific requirements. Additionally, GreenPAK products enable very rapid design time and provide low power consumption, small board area, and low cost.

| Δn | plica | tion | Noto |

|----|-------|------|------|

|    | piica |      |      |

# **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 19-Apr-2022 | Initial Version |

**Application Note**

**Revision 1.0**

04-Apr-2022

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.