# Introduction to SLG5100x Protection Features SLG5100x

This application note describes the protection features available in Renesas SLG5100x devices which feature high performance LDOs in addition to integrated GreenPAK resources for use in advance sensor systems and other small multi-rail applications. These devices have start-up and functional current limits, under-voltage lockout (UVLO), thermal shutdown, and configurable temperature alerts. I<sup>2</sup>C is implemented in these devices which allow the user to read various states of the device such as the state of current limits, VOUT\_OK, temperature sensor (on the GPIO), and other various registers.

### **Contents**

| 1. | Types of Protection in SLG5100x                       |                                          |   |  |  |

|----|-------------------------------------------------------|------------------------------------------|---|--|--|

| 2. | Flexibility of Protection Systems in SLG5100x devices |                                          |   |  |  |

|    | 2.1                                                   | Combining Signals with LDOs              | 3 |  |  |

|    | 2.2                                                   | "Device Interrupt Request Block" Details | 4 |  |  |

|    | 2.3                                                   | Signal Flag Output in SLG5100x           | 5 |  |  |

| 3. | Typical Application Use Case for the SLG51000         |                                          |   |  |  |

| 4. | . Conclusion                                          |                                          |   |  |  |

| 5. | Revision History                                      |                                          |   |  |  |

### References

For related documents and software, please visit:

GreenPAK™ Programmable Mixed-Signal Products | Renesas

Download our free Go Configure Software Hub [1] to open the .ppak files [2] and view the proposed circuit design. See the full specifications of SLG5100x in the datasheet [3, 4, 5].

- [1] Go Configure Software Hub, Software Download and User Guide

- [2] AN-CM-377 Introduction to SLG5100x Protection Features, Design File

- [3] SLG51000 Datasheet, SLG51000 Datasheet

- [4] SLG51001 Datasheet, SLG51001 Datasheet

- [5] SLG51002 Datasheet, SLG51002 Datasheet

# 1. Types of Protection in SLG5100x

SLG5100x devices have a variety of protection features that help protect the PMIC itself and other components in the circuit. These protection features allow the device to be safely turned off, while also notifying other microcircuits of the problem, such as a connected microcontroller.

Below is a brief description of the protection blocks that are available in SLG5100x devices:

| Туре                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Trigger                                                                                                                                                                      | Programmability                                           |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Under-voltage Lockout<br>(UVLO)        | When the UVLO trigger event occurs, the device turns off the LDOs and GPIOs in the specified power down sequence. LDOs will therefore not be turned off randomly or simultaneously in order to help prevent damage to the ICs powered by PMIC.                                                                                                                                                                                                                  | An internal UVLO monitor with a programmable threshold monitors the V <sub>DD</sub> input voltage and shuts down the system if the voltage drops below the threshold.        | 2.215 V – 2.658 V<br>(step = 24.6 mV)                     |

| Thermal Shutdown                       | The device turns off the LDOs and GPIOs in the specified power down sequence. After the device cools down to a preset nominal operating temperature, it will turn on again. After restoring the operation of the device, the FAULT logs are available to be read.                                                                                                                                                                                               | Thermal shutdown or over-<br>temperature protection activates<br>when the temperature of the<br>device has reached 140 °C                                                    | The shutdown temperature is set to 140 °C.                |

| Configurable<br>Temperature Alerts     | The temperature sensor (TEMP SENSOR) reads the temperature sensitive node of the bandgap. The temperature threshold warning is programmable within ±5 °C accuracy. The temperature warning flag can be accessed through I <sup>2</sup> C or through a connected GPIO pin.                                                                                                                                                                                       | Temperature warning flag is triggered at temperatures above the set threshold                                                                                                | Temp Warning = 90 /<br>100 / 110 / 120°C<br>Debounce time |

| Voltage Output OK flag<br>for each LDO | For each of the LDOs, a VOUT_OK flag event indicates that the LDO has started up. If VOUT_OK is not raised, it means that the LDO has not reached the target value. It is debounced on the positive edge, with the debounce time controlled for each LDO. It is possible to read this register and then output this signal to a connected GPIO, or with the help of internal combinatorics, the VOUT_OK signals can be combined and connected to a single GPIO. | When V <sub>OUT</sub> reaches 90% of its target value                                                                                                                        | Debounce time                                             |

| Current Limit flag for each LDO        | A current limit flag event can be used to detect a current limit in each LDO. This event is debounced on the falling edge only to allow any current limit detection to be captured. The device has two different current limit settings, startup current limit and functional current limit.                                                                                                                                                                    | Current limitation detected                                                                                                                                                  | Functional and startup current limits Debounce time       |

| Device Interrupt<br>Request            | Device interrupt request is the logic OR of the unmasked event register signal (Faults and IRQ Events). Each IRQ event register has an associated interrupt mask register (IRQ_ <x>), which controls whether the event register signal contributes to the device interrupt request via the logic OR.</x>                                                                                                                                                        | <ul> <li>LDOs Current limits</li> <li>Power-on reset</li> <li>System reset</li> <li>Power sequencer crash</li> <li>Over-temperature</li> <li>Matrix event (input)</li> </ul> | Event sensitivity                                         |

## 2. Flexibility of Protection Systems in SLG5100x devices

SLG5100x devices have internal programmable logic and can be programmed individually. It is possible to create a custom design file in the GUI which is then written to the device. Also, a custom sequence of turning LDOs on and off can be specified and then this sequence can be enabled via I<sup>2</sup>C, GPIO, or simply turning on the device.

Signals such as VOUT\_OK, overcurrent limit events, and temperature warning can each be outputted to separate GPIOs or combined internally and then output to a single GPIO.

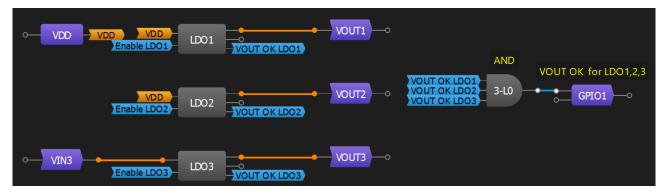

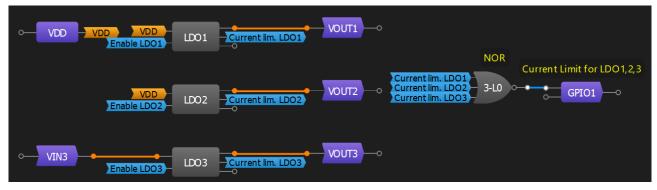

### 2.1 Combining Signals with LDOs

In Figure 1 below, an example design project for an SLG5100x device is shown. The VOUT\_OK flag from each of the LDOs is connected to a logic AND gate. The output of the logic AND is connected to GPIO1, which will be high when LDOs 1, 2, and 3 are enabled. If any of LDO1, LDO2, or LDO3's output has not reached its nominal voltage value, GPIO1's output will be low. Figure 2 features a similar example but shows an example for the current limit flag. If one of these flags is raised, then GPIO1 will be high.

Figure 1: VOUT\_OK signal for three LDOs through the logic AND gate to GPIO1

Figure 2: Current limit flag signal for three LDOs through the logic AND gate to GPIO1

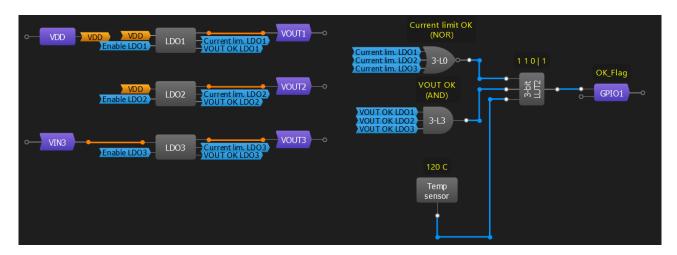

Figure 3 shows an example of using a temperature sensor along with current limit and VOUT\_OK flags. This solution monitors if the device works as expected using GPIO1. When any one of these three possible events is triggered for any one of the LDOs (LDO V<sub>OUT</sub> was not raised, current limit, or temperature sensor), then GPIO1 will assert low.

Figure 3: VOUT\_OK, current limit, and temp sensor signals for LDOs through the 3-bit LUT to GPIO1

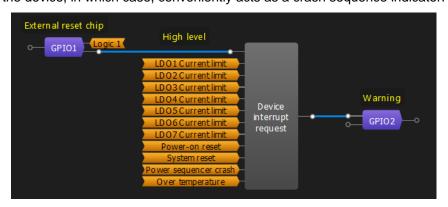

### 2.2 "Device Interrupt Request Block" Details

The device has a functional block that helps to save internal logic elements. Each IRQ event register has an associated interrupt mask register, which controls whether the event register signal contributes to the device interrupt request via the logical OR.

It includes the following events:

- LDO1 Current limit

- LDO2 Current limit

- LDO3 Current limit

- · LDO4 Current limit

- LDO5 Current limit

- LDO6 Current limit

- · LDO7 Current limit

- · Power-on reset

- · System reset

- · Power sequencer crash

- · Over-temperature

- Matrix event (input)

When any of the described conditions above occurs, the device interrupt request output signal will be asserted high and latched high until the device is reset (CS de-asserted). This signal can be routed to the GPIO, or it can be used to turn off the device, in which case, conveniently acts as a crash sequence indicator.

Figure 4: Device Interrupt Request Block

### 2.3 Signal Flag Output in SLG5100x

If any one of the following events such as UVLO detection, over-temperature detection, or CS de-assertion is triggered, the device is powered down according to the programmed power sequencer.

It is possible to read the SLG5100x error registers via I<sup>2</sup>C. Below are the following status and event registers that can be read:

| Parameter                | Status (I <sup>2</sup> C) | Event (I <sup>2</sup> C) | GPIOs (output) |

|--------------------------|---------------------------|--------------------------|----------------|

| POR                      | No                        | Yes                      | No             |

| RESET                    | No                        | Yes                      | No             |

| Over-temperature         | No                        | Yes                      | No             |

| High temperature         | Yes                       | Yes                      | Yes            |

| LDO voltage output flag  | Yes                       | Yes                      | Yes            |

| LDO current limits flag  | Yes                       | Yes                      | Yes            |

| Device interrupt request | No                        | No                       | Yes            |

# 3. Typical Application Use Case for the SLG51000

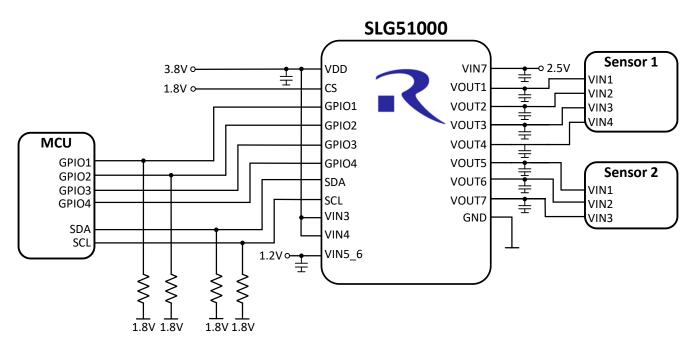

Figure 5 shows a typical use case for the SLG51000 featuring its multiple protection modes. This device has four GPIOs for general use and two GPIOs (SDA and SCL) for I<sup>2</sup>C. If necessary, these GPIOs can be disconnected from I<sup>2</sup>C and can be used in the design for other functions. The device has several separate VINs and seven integrated LDOs.

Figure 5: Typical use case using the SLG51000

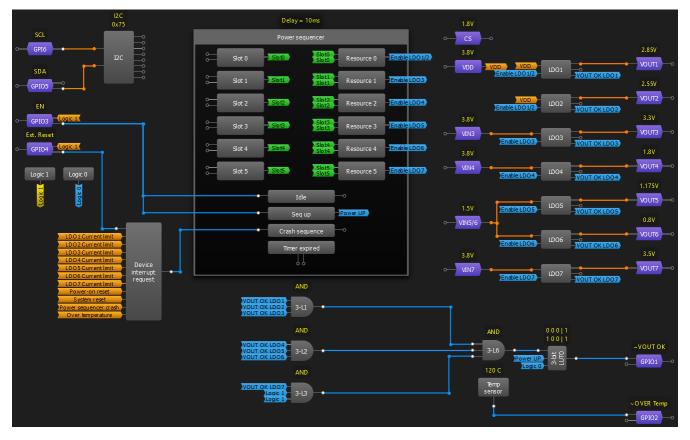

The LDO output voltages, current limits, internal power sequencer, and device operation scenarios can be quickly configured in the GreenPAK Designer software which has a user-friendly GUI. Information about VOUT\_OK, current limit, and high temperature can be routed to GPIOs or used for other purposes. Figure 6

shows the design of the device configuration file in the GUI, which demonstrates some of the device's protection features.

Figure 6: General view of the design in the GUI for the SLG51000

In this Figure 6 example, GPIO3 is configured as an input and triggers the power sequence. The LDOs are turned ON/OFF one by one.

The power sequencer is configured for a delay of 10 ms between turning ON each of the LDOs and 30 ms between turning OFF each of the LDOs once GPIO3 is toggled low-to-high. Additionally, the power sequencer is configured to turn OFF the LDOs with a delay of 10 ms, if the "Crash sequence" event occurs.

The crash sequence transitions the device to the "Reset" state and can be caused by:

- CS de-assertion

- · Over-temperature detection

- Software Reset Request

- UVLO detection

- Crash detection the output of the block "Device interrupt request" connected to it.

The design in Figure 6 includes a "Device Interrupt Request" block, which is connected to the "Power Sequencer" block. The "Power Sequencer" block has a crash sequence mode - which disables the LDOs through the programmed power sequence, and the device will go into it's Reset state (more information about the State Machine can be found in the datasheet).

GPIO4 is connected to this block as an input with a debounce filter. If a logic high level is applied to GPIO4, the output of the device interrupt request block will also go high and the LDOs will be disabled, resulting in the device being reset. The device will remain in this state until CS is de-asserted.

GPIO1 is configured as an output which outputs the ON status of all LDOs through a logic AND gate. When all LDOs are enabled, GPIO1 will be low Otherwise if at least one LDO is not turned on, GPIO1 will remain high. If

there is no VIN for any of the LDOs, or if any of the LDOs did not turn on for any reason, then GPIO1 will stay high.

The value of the over-temperature event is routed to GPIO2, which is configured as an inverted output. If the temperature rises above 120 °C, the temperature sensor will go high and the GPIO2 output will go from a high level to a low level.

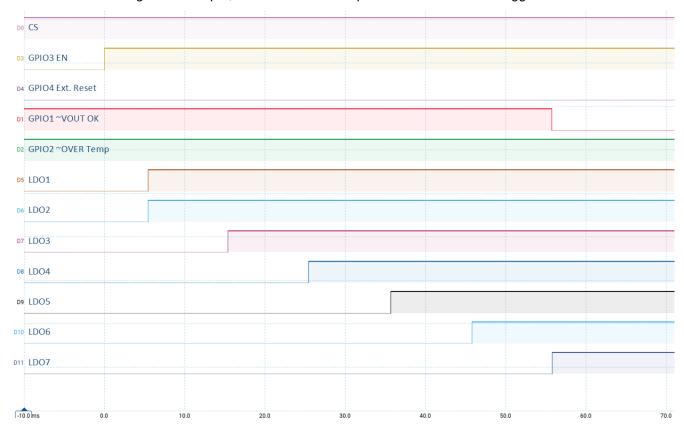

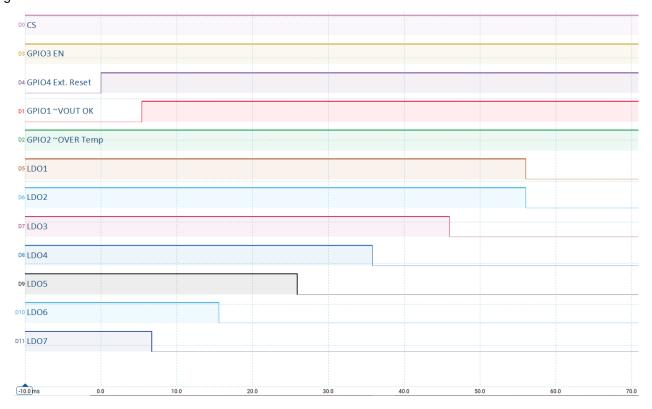

Figure 7 shows the operation of the Power Sequencer block as a part of the SLG51000 chip. After raising GPIO3 (EN), which has a 5 ms debounce, the LDOs start turning ON one by one. Once all LDOs are turned ON, and a current limit event has not been detected, GPIO1 (VOUT OK) goes to a low level. In other words, this means that all LDOs have a voltage at the output, and the current limit protection has not been triggered.

Figure 7: Power-up sequence via GPIO3 (EN)

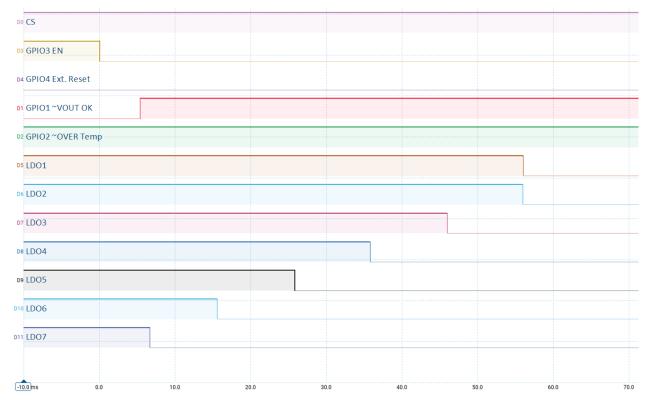

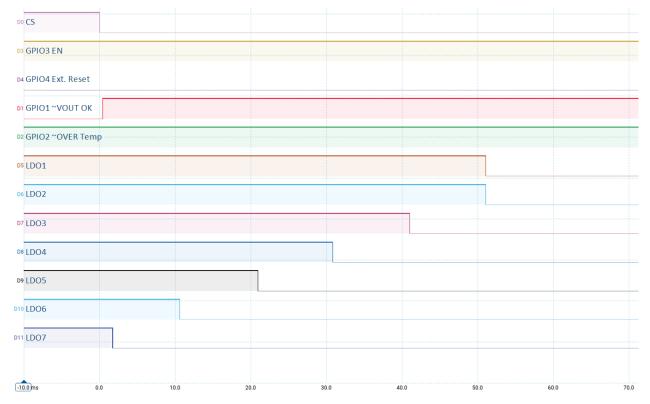

Figure 8 shows the operation of the Power Sequencer block as a part the SLG51000. Once GPIO3 (EN) is toggled from high-to-low, the LDOs begin to turn OFF one by one. After the first LDO is turned OFF, GPIO1 (VOUT OK) goes high.

Figure 8: Power DOWN Sequence via GPIO3: EN

Figure 9 shows the operation of the Power Sequencer block with the Device Interrupt Request block as a part of the SLG51000. After GPIO4 (External Reset) goes high, which is connected to the input of the Device Interrupt Request block, the LDOs begin to turn OFF one by one. Once the first LDO is disabled, GPIO1 (VOUT OK) goes high.

Figure 9: Crash Sequence via GPIO4: External Reset

Figure 10 shows the behavior of the device when CS is de-asserted. In this case all LDOs will be turned off in order of the programmed power sequence. The behavior of the device will be the same for each of the following error conditions: over-temperature detection, UVLO detection, and software reset request.

Figure 10: CS de-assertion sequence

### 4. Conclusion

The SLG5100x devices have a variety of protection features that can detect issues in time and turn off the device in the correct sequence in order to avoid critical damage to the device and other connected components. Furthermore, the device's flexibility allows customers to use it for numerous project applications and still be able to meet their different respective requirements. Users can modify the accompanying design file used in this example to customize it for different needs.

# 5. Revision History

| Revision | Date            | Description     |

|----------|-----------------|-----------------|

| 1.00     | August 21, 2024 | Initial release |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.