# Sinewave Generator with AnalogPAK SLG47003V

### **Contents**

| 1. | References            | 1 |

|----|-----------------------|---|

| 2. | Terms and Definitions | 1 |

| 3. | Introduction          | 2 |

| 4. | Design Operation      | 3 |

| 5. | Conclusion            | 6 |

| 6. | Revision History      | 7 |

#### 1. References

For related documents and software, please visit:

#### AnalogPAK™ | Renesas

Download our free Go Configure Software Hub [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in a complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] Go Configure Software Hub, Software Download and User Guide, Renesas Electronics

- [2] AN-CM-386 Sinewave Generator with AnalogPAK, Design File, Renesas Electronics

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage, Renesas Electronics

- [4] GreenPAK Application Notes, GreenPAK Application Notes, Renesas Electronics

- [5] SLG47003V Datasheet

Author: Rostyslav Marushchak

### 2. Terms and Definitions

EPG Extended Pattern Generator

MF Multi-Function Macrocell

OpAmp Operational Amplifier

Vref Voltage reference

## 3. Introduction

This design is developed to be an analog sine wave source that can be used in a variety of devices which might require a sinewave reference, for example a stand-alone, hybrid solar DC/AC converter. Also, because of the availability of the Extended Pattern Generator (EPG) it is possible to specify other waveforms (rectangular, triangular, and trapezoidal). In this Application Note is we will consider the use of a sinusoidal waveform, since this waveform is perhaps the most common.

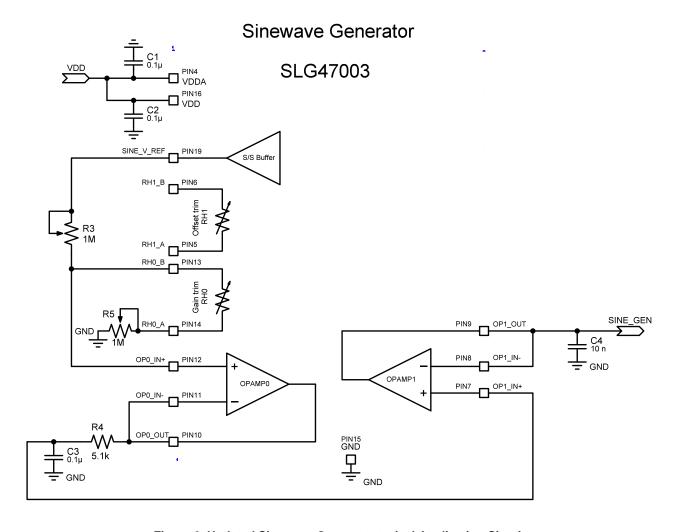

The generation of a sinusoidal signal occurs by means of a cyclic recording of data from the EPG to the rheostat (RH0), which is included on the low side of the voltage divider R3-RH0 (see Figure 1 and Figure 2).

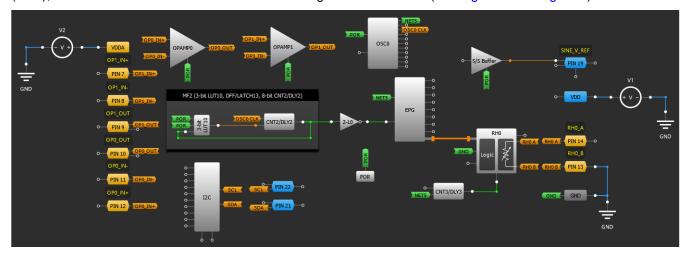

Figure 1. Sinewave Generator Design Block Diagram

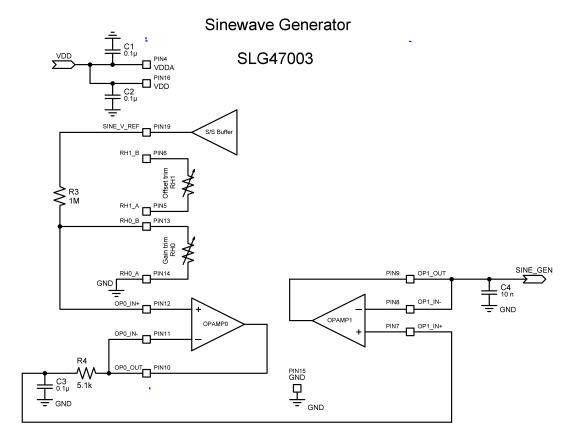

Figure 2. Sinewave Generator Typical Application Circuit

## 4. Design Operation

The operation of the signal generator is based on the ability to control the rheostat (RH0) by writing data to its counter from the EPG via an 8-bit parallel output (a new function implemented in AnalogPAK).

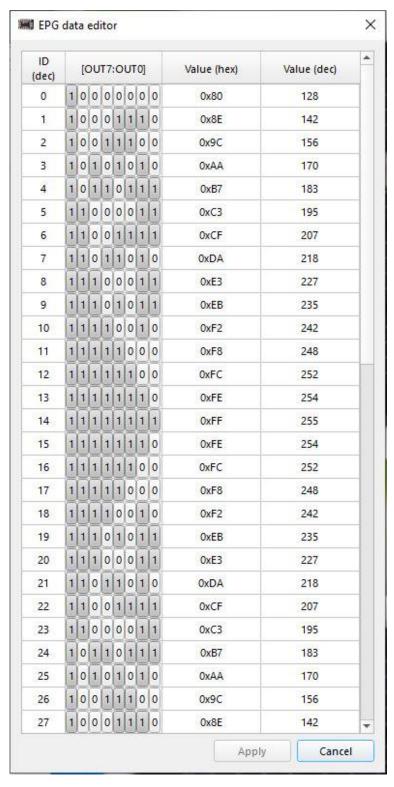

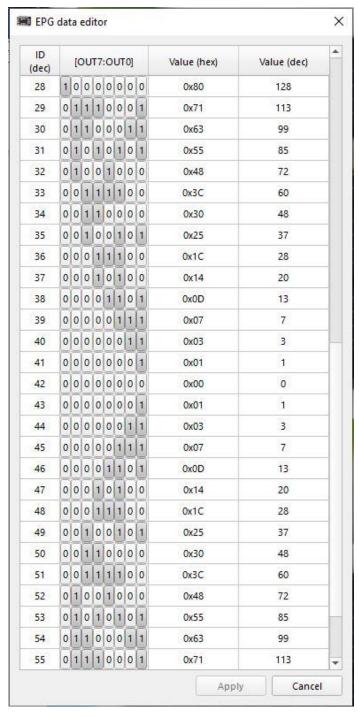

56 values that determine the shape of the output signal (sinusoidal) are recorded in the EPG memory (see Figure 3 and Figure 4).

Figure 3. PGA Data Table for Values 0 to 27

Figure 4. PGA Data Table for Values 28 to 55

Since the rheostat RH0 is included in the low side of the R3-RH0 voltage divider at the non-inverting input of the buffer on OpAmp0, the resistance of RH0 will determine the shape and offset of the output voltage of the buffer relative to the ground.

The maximum value of the amplitude of the output sinusoidal signal is determined by the value of the output voltage of the S/S Buffer macrocell and the resistance of R3 on the high side of the voltage divider R3-RH0 (see Figure 2).

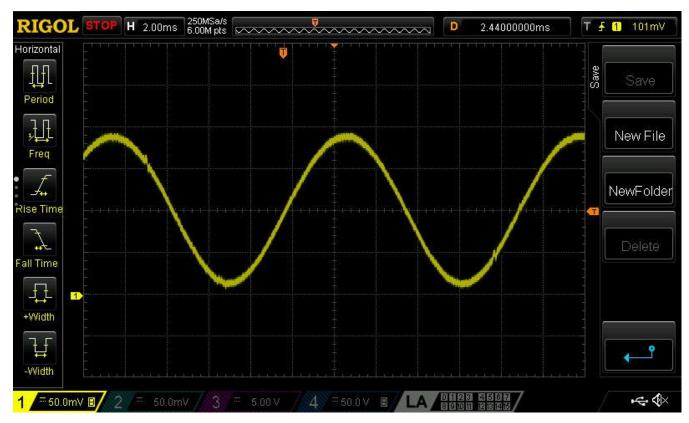

Thanks to the new method of signal formation from the EPG using the patterns set in advance, the output sinusoidal signal does not contain significant noise, higher-order harmonics, etc. Additionally, for the final processing of the signal, a second-order filter R4C3, with a voltage follower on OpAmp1 is used (see Figure 2 and Figure 5).

Figure 5. The Main Design Functionality

In addition, if the circuit is updated as shown in Figure 6, R3 can be used to adjust the amplitude and R5 can be used to adjust the offset of the output signal. I<sup>2</sup>C commands can also set the maximum amplitude of the output signal (the output voltage of the S/S Buffer macrocell) and the output voltage frequency (the oscillator frequency and counter data of the DLY2 macrocell).

Figure 6. Updated Sinewave Generator typical Application Circuit

## 5. Conclusion

New functions introduced in AnalogPAK SLG47003 make it possible to create a universal signal generator (sinusoidal, rectangular, triangular, trapezoidal, etc.) with the help of a trivial amount of resources with the opportunity to adjust the frequency, amplitude, and offset using I<sup>2</sup>C commands and other additional external elements.

## 6. Revision History

| Revision | Date                  | Description      |

|----------|-----------------------|------------------|

| 1.00     | September 10,<br>2024 | Initial release. |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.