# RENESAS

# PCIe Buffer-Mux Layout Recommendations

# Introduction

This document describes the layout recommendations for the Buffer/Mux devices in the PCIe timing portfolio.

# Contents

| 1.                  | PCIe I | Buffer/Mux Devices          | 2  |  |

|---------------------|--------|-----------------------------|----|--|

| 2.                  | PCB L  | Layer Stack-up              | 4  |  |

|                     |        | Sizing Traces               |    |  |

|                     | 2.2    | Common Layout Rules         | 5  |  |

| 3.                  | Layou  | ut Recommendations          | 7  |  |

|                     | 3.1    | Power Supply Layout         | 7  |  |

|                     | 3.2    | Clocking Layout             | 9  |  |

|                     | 3.3    | 13                          |    |  |

|                     |        | 3.3.1 Current Return Path   | 13 |  |

|                     |        | 3.3.2 Crosstalk and Spacing |    |  |

|                     | 3.4    | EPAD Thermal Layout         | 16 |  |

| 4. Revision History |        |                             |    |  |

# Figures

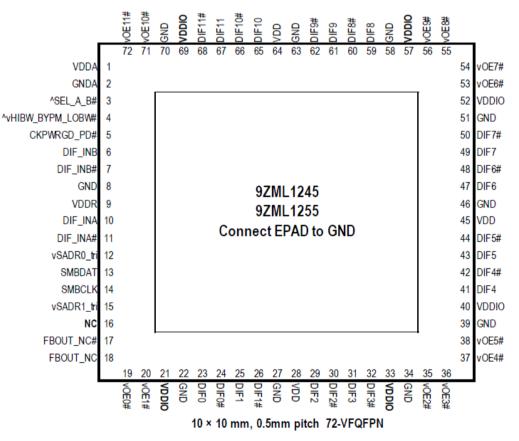

| Figure 1. 9ZML124/55 VFQFPN (single-row pinout)                     | 2  |

|---------------------------------------------------------------------|----|

| Figure 2. 9QXL2001 GQFN (dual-row pinout)                           | 3  |

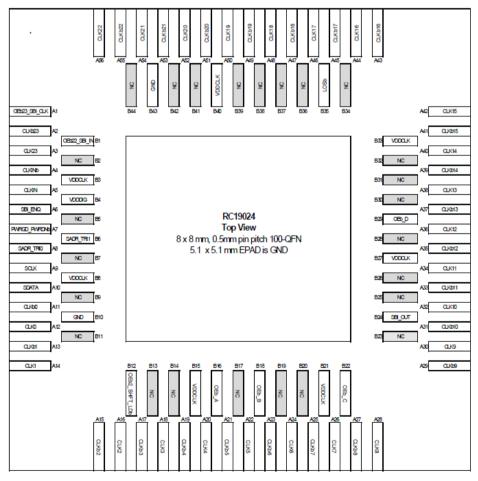

| Figure 3. RC19024 QFN (dual-row pinout)                             | 3  |

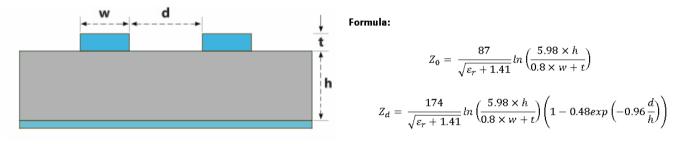

| Figure 4. Microstrip Profile – Impedance Calculation                | 4  |

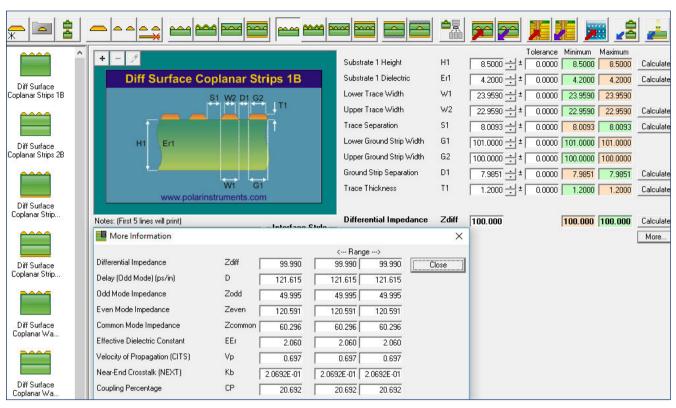

| Figure 5. Polar Instruments – Impedance Calculation                 | 5  |

| Figure 6. Signal Trace Bending                                      | 5  |

| Figure 7. Stub PCB Layout                                           | 6  |

| Figure 8. Stub PCB Routing Layout Practices                         | 6  |

| Figure 9. Decoupling Capacitor Layout Practices                     | 7  |

| Figure 10. Power Filtering Layout Practices                         | 7  |

| Figure 11. Power-GND Plane + Decoupling Capacitors Layout Practices | 8  |

| Figure 12. 9DBL0455 EVB and 9QXL2001 EVB Power Supply Layout        | 8  |

| Figure 13. 9QXL2001 Power Tracks Layout                             | 9  |

| Figure 14. Differential Traces Layout Practices (1)                 | 9  |

| Figure 15. Differential Traces Layout Practices (2)                 | 10 |

| Figure 16. Serpentine Differential Mismatched Length Compensation   | 10 |

| Figure 17. Differential Traces Layout Practices (3)                 | 11 |

| Figure 18. 9DBL0455 EVB Differential Traces Layout                  | 11 |

| Figure 19. 9DBL0455 EVB Differential Traces Layout (2)              | 12 |

| Figure 20. 9QXL2001 Differential Traces Layout (top layer)          | 12 |

| Figure 21. 9QXL2001 Differential Traces Layout (bottom layer)       | 13 |

| Figure 22. Current Return Path                                      | 13 |

| Figure 23. Current Return Path Layout Practices                     | 14 |

| Figure 24. Stitching Via Layout Practices                           | 14 |

| Figure 25. Crosstalk Layout Practices                    | .15 |

|----------------------------------------------------------|-----|

| Figure 26. GND Shielding Layout Practices – XTAL Example | .15 |

| Figure 27. 9DBL0455 EVB and 9QXL2001 EVB EPAD Layout     | .16 |

# 1. PCIe Buffer/Mux Devices

The layout recommendations in this document pertain to the following PCIe Clock Buffer/Mux families:

- 9DBV/9DMV

- 9DBL/9DML

- 9ZXL/9ZML

- RC190/RC192

- RC191/RC193

- 9QXL

There are two categories of pinouts: single-row and dual-row. These categories impact the signal routing and the component placement layout in the part area.

The layout specific examples provided within this document are applicable to the entire family of devices mentioned above.

|   | 1       | 2       | 3     | 4                                          | 5      | 6                 | 7     | 8             | 9           | 10                  | 11      | 12     | _        |   |

|---|---------|---------|-------|--------------------------------------------|--------|-------------------|-------|---------------|-------------|---------------------|---------|--------|----------|---|

| Α | DIF17   | DIF16#  | DIF16 | DIF15#                                     | DIF15  | DIF14#            | DIF14 | DIF13#        | DIF13       | DIF12#              | DIF12   | DIF11# | Α        |   |

| В | DIF17#  | VDDO3.3 | NC    | ^v SADRO_tri                               | NC     | VDDA3.3           | NC    | ^v SADR 1_tri | NC          | vOE12#              | VDDO3.3 | DIF11  | в        |   |

| С | DIF18   | NC      |       |                                            |        |                   |       |               |             |                     | vOE11#  | DIF10# | с        |   |

| D | DIF18#  | NC      |       |                                            |        |                   |       |               |             | NC                  | DIF10   | D      |          |   |

| E | DIF19   | VSBEN   |       |                                            |        |                   |       |               |             | VOE10#/SHF<br>T_LD# | vOE9#   | E      |          |   |

| F | DIF19#  | NC      |       |                                            |        |                   |       |               |             | NC                  | DIF9#   | F      |          |   |

| G | DIF_IN  | NC      |       | 80-GQFN Package<br>Top View<br>EPAD is GND |        |                   |       |               | Top View NC |                     |         |        | DIF9 G   | G |

| Н | DIF_IN# | VDDR3.3 |       |                                            |        |                   |       |               |             |                     |         |        | VOE8# DI |   |

| J | DIF0    | NC      |       |                                            |        |                   |       |               |             | NC                  | DIF8    | J      |          |   |

| ĸ | DIF0#   | NC      |       | v0E7# DIF7                                 |        |                   |       |               |             |                     |         |        |          |   |

| L | DIF1    | VDDO3.3 | NC    | SMBDAT                                     | SMBCLK | NC                | NC    | V OE5#/DATA   | NC          | vOE6#/CLK           | VDD03.3 | DIF7   | L        |   |

| м | DIF1#   | DIF2    | DIF2# | DIF3                                       | DIF3#  | V CKPWRGD<br>_PD# | DIF4  | DIF4#         | DIF5        | DIF5#               | DIF6    | DIF6#  | м        |   |

|   | 1       | 2       | 3     | 4                                          | 5      | 6                 | 7     | 8             | 9           | 10                  | 11      | 12     | •        |   |

Figure 2. 9QXL2001 GQFN (dual-row pinout)

Figure 3. RC19024 QFN (dual-row pinout)

# 2. PCB Layer Stack-up

A PCB has multiple layers of copper and assembled isolation materials. The stack-up is defined by the layer composition (copper and dielectric material), including the number of layers and the thickness.

A quality PCB starts with its circuit design; thus, it is necessary to define a quality layout strategy that optimally interconnects each functional block of the design.

PCB design considerations:

- What is the highest frequency of the design?

- What are the electrical specifications? (voltage, type of signals, impedance, frequency, data rate, etc.)

- Are there sensitive or high-speed signals to route? (power supply, clock, buses, high-speed interfaces, RF, etc.)

- · Create a block diagram that identifies the different interconnections between the function blocks

- · Define the sizing of traces for each interconnection interface that meets the design requirements

There is no fundamental information to define the number of layers. This depends on the number of traces needed to route all signals in the design.

Renesas recommends using the Polar instruments tool to size the stack-up and the traces.

### 2.1 Sizing Traces

To size the clocking traces, Renesas recommends using a PCB toolkit software and targeting the desired impedance with a  $\pm 5\%$  tolerance.

To define the sizing of trace, there are different profiles in the function of the layer configuration based on a microstrip profile.

Figure 4. Microstrip Profile – Impedance Calculation

The microstrip impedance represents the characteristic impedance of the microstrip line, meaning the uniform impedance calculated on the dimensions of copper and materials along the microstrip.

The signals are referenced to GND,

where:

- w = signal trace width

- *d* = distance between the differential trace

- h = distance between the trace and the GND plan

- t = height of trace

- *Er* = dielectric constant

PCIe Buffer-Mux Layout Recommendations Application Note

Figure 5. Polar Instruments – Impedance Calculation

After pre-defining the sizing of traces and the stack-up, it is necessary to submit them to PCB suppliers. These suppliers will provide the guidance to select the best materials for design criteria.

The Saturn PCB tool kit software is another tool for sizing the traces.

### 2.2 Common Layout Rules

To prevent signal routing issues, follow the common layout rules listed below.

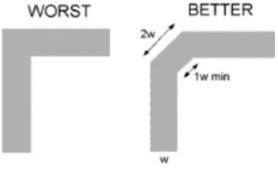

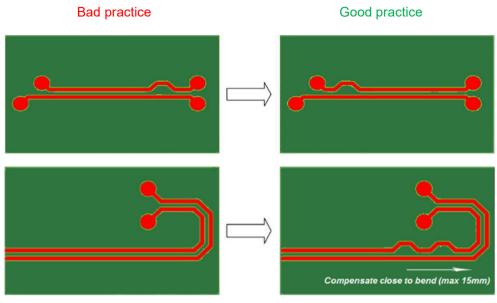

Figure 6. Signal Trace Bending

For bending signal traces, sharp-angle bending is recommended over right-angle bending.

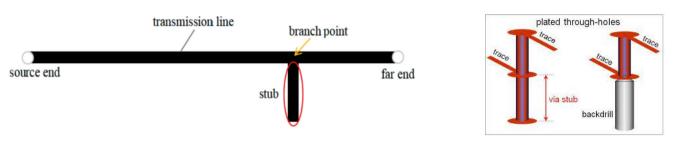

Figure 7. Stub PCB Layout

A stub is a branch off the main line of the transmission line. The mainline is the longest path from the source end (driver) to the far end (receiver or load).

The stub begins to have an impact as of 1/4 wavelength. A reflection could appear on the transmission line generating a signal integrity issue (glitches on the edges, horizontal pedestal on the eye diagram) or EMC issues.

Figure 8. Stub PCB Routing Layout Practices

Figure 8 shows a way to limit the stub effect on a trace. To opt for a daisy chain layout for connecting the components.

- Renesas recommends routing the clock signals point-to-point on the same layer between the driver and the receiver (if possible).

- Renesas recommends trying to limit the stubs and the number of vias on the traces. Reduce them by using back-drilled via and opting for a daisy chain layout

- Single ended traces => Impedance 50 ohm

- Differential traces => Impedance differential 85 or 100 ohm ±5% tolerance (check the part characteristics)

- Renesas recommends applying signal integrity simulations and a rule checking format to verify the design

# 3. Layout Recommendations

### 3.1 Power Supply Layout

The power supply is an important part in a design layout and should be optimally implemented to avoid issues or dysfunctions.

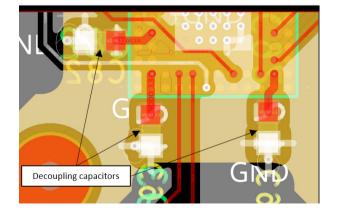

To prevent the power supply noises from other parts, the following action items are recommended:

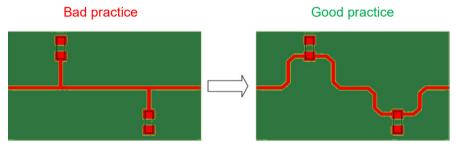

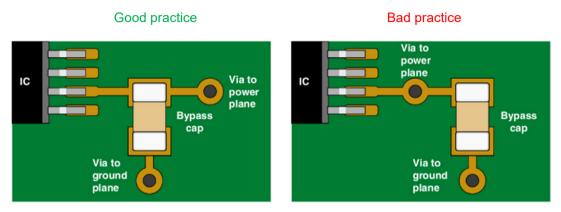

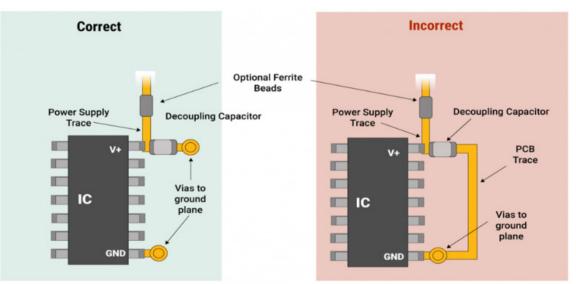

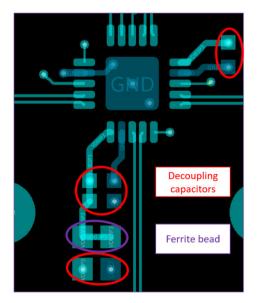

- Place the decoupling capacitors in the same layer of the part with a short connection to ground (see Figure 9)

- Whereas for the BGAs and specific parts (dual-row pinout, for example), place the decoupling capacitors (100nF) as close as possible to pins in the opposite layer of part, along with a short connection to ground

- Place the capacitor on the current path between the power via and the IC

Figure 9. Decoupling Capacitor Layout Practices

Figure 10 shows the practice of implementing the placement of power filtering components in a design.

- Minimize the length of the GND connection to the capacitor, in order to reduce the coil effect.

- Place the capacitor of 100nF or the capacitor with the weaker value close as possible to the pin. It doesn't matter whether the ferrite bead placement is on top or on bottom.

- Don't share the ground via between the decoupling capacitors, each capacitor must have its own ground via.

Figure 10. Power Filtering Layout Practices

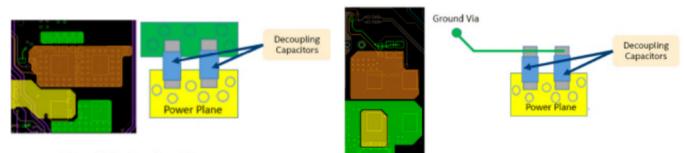

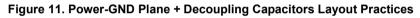

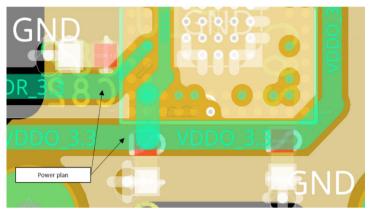

Figure 11 shows how to use Power-GND planes instead of net.

A power plane allows more current to pass than the simple trace, and the GND plane, in addition to vias, improves the efficiency of the decoupling capacitors by reducing the coil effect due to the ground trace (shown in the left-side image of Figure 11).

- Size the Power-GND plane/trace correctly and the number of via in function with the circulating current to avoid a PCB heating or a voltage drop

- Implement a GND plane or allow sufficient spacing between the power planes/nets

- Check the sizing of power planes. Renesas recommends launching a power integrity simulation

- Ensure to have complete Power-GND planes and avoid split planes. Split planes can act as a radiating slot antenna

- Implement a GND plane in the layer below or above in function of the part location.

*Note*: In Figure 11, green represents the GND plan; yellow represents the Power plane.

Good Design Practice

**Bad Design Practice (not Allowed)**

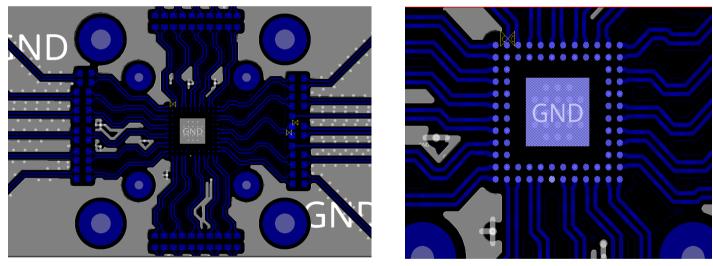

The left image of Figure 12 (9DBL0455 EVB) shows the power layout implementation for a QFPN part with a single-row pinout. All the power components are placed close to the part and on the same layer.

The right image of Figure 12 (9QXL2001 EVB) shows a different implementation due to a dual-row pinout. The power pins are located in the inner row, requiring the decoupling capacitors to be placed on the opposite layer (part on top layer, capacitors on bottom layer).

In both the cases, the capacitors are placed close to the part as possible.

Figure 12. 9DBL0455 EVB and 9QXL2001 EVB Power Supply Layout

Usually, the power tracks are larger than the signal tracks (see Figure 13). The larger power tracks limit the amount of drop voltage.

Power planes are also a good option by providing more current and thermal dissipation.

Figure 13. 9QXL2001 Power Tracks Layout

### 3.2 Clocking Layout

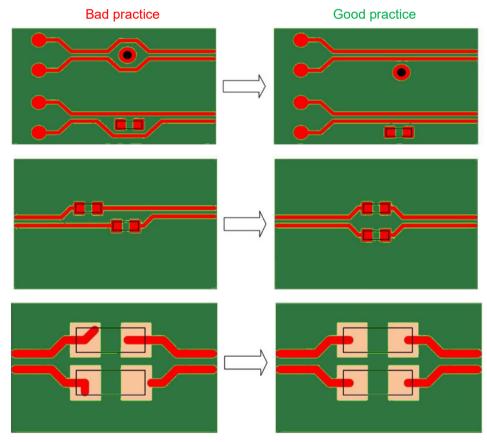

For differential traces, Renesas recommends the following practices:

Differential Traces Layout Practices (1) (see Figure 14)

- Do not place any component or via between the differential pair

- Place the components symmetrically and use a small size for the components (0402 or 0201 are recommended; avoid 0603)

Figure 14. Differential Traces Layout Practices (1)

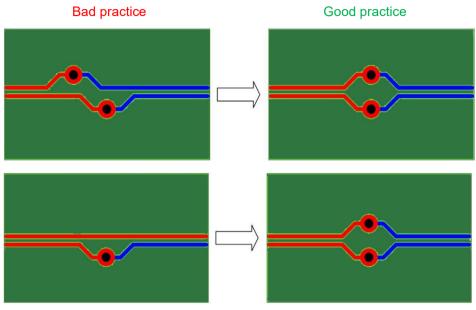

#### Differential Traces Layout Practices (2) (see Figure 15)

- Route the pair on the same layer and place the same number of vias. Place the vias symmetrically

- · Renesas recommends keeping the symmetry of the differential pair on the entirety of the traces

- Renesas recommends ensuring and respecting the length matching to avoid signal integrity issues or common mode issues (propagation delay 1mm => 6ps)

*Note*: In the images below, red represents layer A and blue represents layer B.

Figure 15. Differential Traces Layout Practices (2)

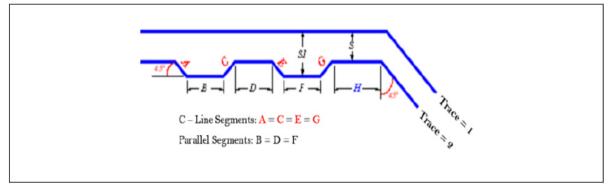

To compensate for the mismatched length, the following practice is recommended (see Figure 16):

- Apply a serpentine to compensate for the length between the differential traces

- Rule: S1 < 2 x S, B = D = F = H = 3 x w, 45-degree bend, where w is the trace width

Figure 16. Serpentine Differential Mismatched Length Compensation

#### Differential Traces Layout Practices (3) (see Figure 17)

In cases of mismatched length, Renesas recommends compensating for it as close as possible to the source of the mismatch in order to propagate the signals in phase on the entirety of the traces

Figure 17. Differential Traces Layout Practices (3)

Figure 18 shows the differential traces implementation for a QFPN part with a single-row pinout. All the clocking traces/components are symmetrically implemented.

Figure 18. 9DBL0455 EVB Differential Traces Layout

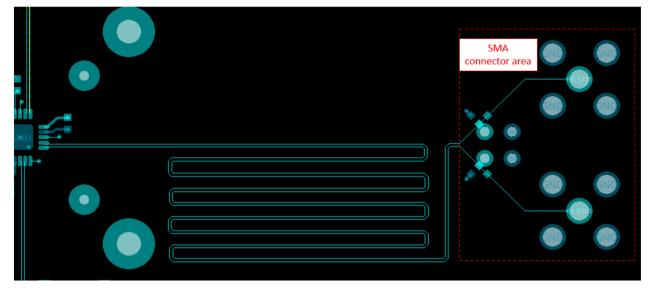

Figure 19 shows the differential traces implementation for a QFPN part with a single-row pinout. All the clocking traces/components are symmetrically implemented to ensure length matches. In the SMA connector area, the differential track is routed in two single-ended tracks due to the SMA connector.

Figure 19. 9DBL0455 EVB Differential Traces Layout (2)

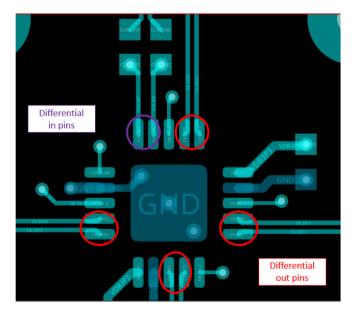

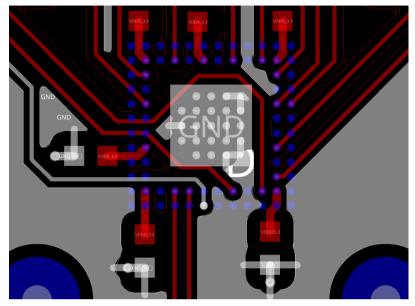

As shown in Figure 20, all the clocking pins are located on the external row pinout and the implementation is symmetrical.

Figure 20. 9QXL2001 Differential Traces Layout (top layer)

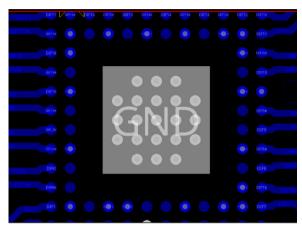

Figure 21 shows how to route traces that are connected to the inner-row pinout. Essentially, these pins are GPIO/miscellaneous/power pins. This design uses the via-inpad method to connect them.

- All the traces are routed on the bottom layer, however, routing them on an inner layer may also be possible

- Keep a sufficient distance between the signal traces and the EPAD GND vias

Figure 21. 9QXL2001 Differential Traces Layout (bottom layer)

### 3.3 EMI-EMC Layout

### 3.3.1 Current Return Path

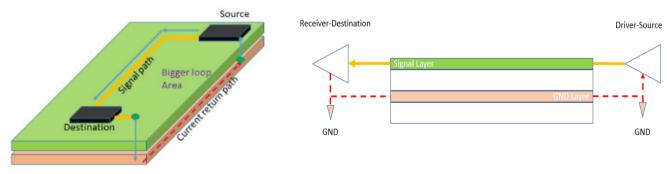

The current return path is used to create a closed circuit with the signal path. It must be implemented using a short return path in order get the lowest resistance (see Figure 22).

- Implement the current return path for the clocking signals and the high-speed signals to avoid any EMI-EMC issues

- Implement a GND plan above or below the signal plan to minimize the return path

- Ensure that the current return path closely follows as much of the signal path as possible. Reference the clock signals to GND.

Figure 22. Current Return Path

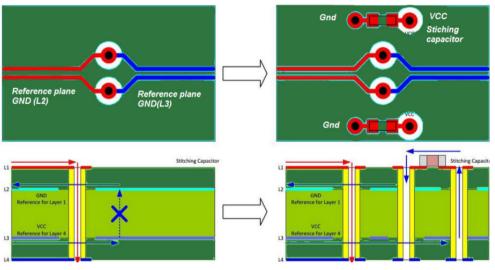

Figure 23 shows how to implement a routing through different planes.

Renesas recommends routing a signal across different planes. If this is not possible, implement a stitching capacitor next to the trace to maintain a short return path (see Figure 24).

*Note*: In the images below, dark green represents the reference GND plane; light green represents the

*Note*: In the images below, dark green represents the reference GND plane; light green represents the Obstruct plane.

Figure 23. Current Return Path Layout Practices

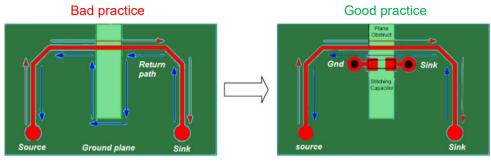

Use a GND via next to the signal via so that when the signal changes a layer, it ensures the integrity of the

return current. Keep a sufficient distance between the GND via and the signal via so that the signal

impedance is not affected.

*Note*: The stitching capacitor isn't mandatory.

Figure 24. Stitching Via Layout Practices

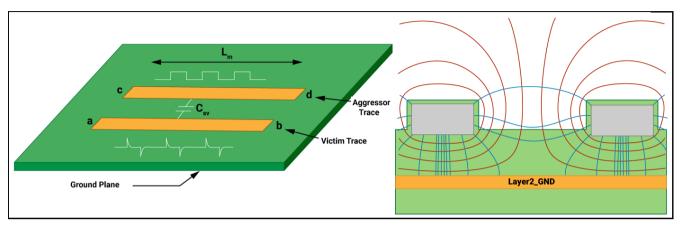

### 3.3.2 Crosstalk and Spacing

A spacing of at least 3x width (5x width, optimal recommendation) is recommended between the clock signals and the other signals. Otherwise, the victim signal could receive noise from the aggressor signal.

If two signals with two different frequencies are in close proximity, the intermodulation products phenomenon could appear (see Figure 25).

Figure 25. Crosstalk Layout Practices

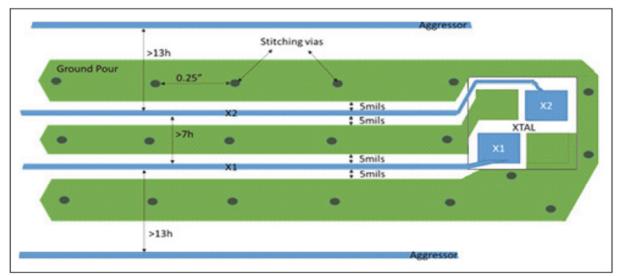

Another way to isolate the traces is by adding a GND plane/trace beside the signal, as well as through all, or some, parts of the signal path. Adding stitching vias also helps to improve the efficiency of shielding (see Figure 26).

Note: The XTAL signals are not considered as a differential pair.

*Important*: This punctilious method must be applied correctly, otherwise the GND plane/net could receive noise from the signal and behave as antenna.

Figure 26. GND Shielding Layout Practices – XTAL Example

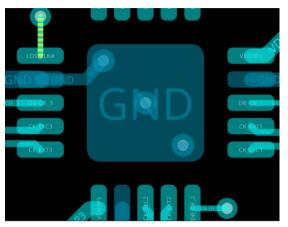

### 3.4 EPAD Thermal Layout

- Place a sufficient amount of thermal/GND vias for the EPAD to connect and dissipate the part correctly

- Refer to <u>AN-842 Thermal Considerations in Package Design and Selection (renesas.com)</u>

- Refer to the device's package outline drawing document

Figure 27 shows the evaluation board (EVB) EPAD layout for the 9DBL0455 EVB (left image) and the 9QXL2001 EVB (right image).

Figure 27. 9DBL0455 EVB and 9QXL2001 EVB EPAD Layout

The recommended minimum number of EPAD thermal vias for the RC190/RC191/RC192/RC193 parts are shown the table below.

| Package                                       | Part Number                               | Thermal Via Array |

|-----------------------------------------------|-------------------------------------------|-------------------|

| 8 × 8 mm 100-VFQFPN<br>(5.1 × 5.1 mm EPAD)    | RC19024A                                  | 7 × 7             |

| 6 × 6 mm 48-VFQFPN<br>(4.2 × 4.2 mm EPAD)     | RC19208A / RC19308A                       | 6 × 6             |

| 6 × 6 mm 80-VFQFPN<br>(2.8 × 2.8 mm EPAD)     | RC19020A / 9QXL2001 / RC19016A            | 4 × 4             |

| 10 × 10 mm 72-VFQFPN<br>(5.95 × 5.95 mm EPAD) | RC19020A072                               | 8 × 8             |

| 9 × 9 mm 64-VFQFPN<br>(5.2 × 5.2 mm EPAD)     | RC19016A                                  | 8 × 8             |

| 7 × 7 mm 56-VFQFPN<br>(5.3 × 5.3 mm EPAD)     | RC19013A                                  | 8 × 8             |

| 5 × 5 mm 40-VFQFPN<br>(3.3 × 3.3 mm EPAD)     | RC19008A / RC19108A                       | 4 × 4             |

| 4 × 4 mm 28-VFQFPN<br>(2.6 × 2.6 mm EPAD)     | RC19004A / RC19104A / RC19204A / RC19304A | 4 × 4             |

| 3 × 3 mm 20-VFQFPN<br>(1.65 × 1.65 mm EPAD)   | RC19002A / RC19102A / RC19202A / RC19302A | 3 × 3             |

1. These recommendations are based on via dimensions of a 0.3mm diameter and 0.8mm pitch.

2. If the EPAD dimensions are the same for other Clock Buffer-Mux families parts mentioned in this document, then the thermal EPAD via recommendation is also valid.

# 4. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.00     | Nov 19, 2024 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.