# Application Note DA913x PCB Layout Guidelines AN-PM-167

# Abstract

The abstract contains a summary of the document: statement of the problem or description of the system aspect, methods of solution, results and conclusions.

# **PCB Layout Guidelines**

# Contents

| Ab  | stract                              | t                                                               | 1 |  |  |  |

|-----|-------------------------------------|-----------------------------------------------------------------|---|--|--|--|

| Co  | ntents                              | S                                                               | 2 |  |  |  |

| Fig | jures.                              |                                                                 | 2 |  |  |  |

| Ta  | bles                                |                                                                 | 2 |  |  |  |

| 1   | Term                                | ns and Definitions                                              | 3 |  |  |  |

| 2   | Refe                                | rences                                                          | 3 |  |  |  |

| 3   | Intro                               | duction                                                         | 4 |  |  |  |

|     | 3.1                                 | Design help and guidance                                        | 4 |  |  |  |

| 4   | General PCB layout guidance         |                                                                 |   |  |  |  |

|     | 4.1                                 | Ground impedance                                                | 4 |  |  |  |

|     | 4.2 Buck-specific layout guidelines |                                                                 |   |  |  |  |

|     | 4.3                                 | Non-power pins                                                  | 5 |  |  |  |

|     |                                     | 4.3.1 AVDD                                                      | 5 |  |  |  |

|     |                                     | 4.3.2 GPIOs                                                     | 5 |  |  |  |

|     | 4.4                                 | Example of PCB layout used in Dialog reference boards           | 5 |  |  |  |

| 5   | Cond                                | clusions                                                        | 0 |  |  |  |

| Ap  | pendi                               | ix A Layout checklist1                                          | 1 |  |  |  |

| •   | A.1                                 | <appendix subsection=""> Error! Bookmark not defined</appendix> |   |  |  |  |

| Re  | vision                              | ۱ History 1                                                     | 2 |  |  |  |

# **Figures**

| Figure 1: Layer 1 (top)            | 5 |

|------------------------------------|---|

| Figure 2: Layer 2 (internal)       |   |

| Figure 3: Layer 3 and 4 (internal) |   |

| Figure 4: Layer 5 (internal)       |   |

| Figure 5: Layer 6 (bottom)         |   |

| Figure 6: Differential feedback    |   |

# **Tables**

No table of figures entries found.

2 of 13

#### **PCB Layout Guidelines**

#### **1** Terms and Definitions

EMIElectromagnetic interferenceEVBEvaluation boardPMICPower management integrated circuit

#### 2 References

- [1] DA9130 Datasheet, Dialog Semiconductor.

- [2] DA9131 Datasheet, Dialog Semiconductor.

- [3] DA9132 Datasheet, Dialog Semiconductor.

Note 1 References are for the latest published version, unless otherwise indicated.

#### PCB Layout Guidelines

# 3 Introduction

PCB layout is a critical part of all switching power supply designs. As there are high switching currents, sensitive control signals in close proximity and a high power-density, control of the PCB layout is needed to ensure the correct electrical and thermal operation of the system. It is important to use ground and power planes with high current power management devices. Dialog recommends that you use both a ground and main system voltage plane underneath the PMIC. The input decoupling can then decouple the planes. As both VDD and GND are planes, inductive cancellation will provide a very low impedance path to the IC.

It is not possible to produce a set of rigid rules for layer construction within a PCB because each design has its own requirements: it is not appropriate for Dialog to suggest which plane should be power and which should be ground. Instead, this application note uses examples from the Dialog PCB range to illustrate practices that have been found useful.

#### 3.1 Design help and guidance

In most sales regions Dialog offers to review customer schematics and PCB layouts. Use of this design-in service is recommended to ensure power management solutions are optimized for reliability and

# 4 General PCB layout guidance

Sections 4.1 and 4.2 discuss general PCB layout rules that can be applied to the whole design. Section 4.3 onwards addresses guidelines for specific parts of a Dialog PMIC, for example buck converters and LDOs.

Key layout principles include:

- Current-carrying traces are as thick as possible

- The board has a low impedance ground

- Sensitive signals are shielded from interference by noisy traces

#### 4.1 Ground impedance

The ground plane should have low impedance for all areas of the PCB. This will help with power control, will improve signal quality and reduce EMI.

The use of a ground layer and flooding of other layers with multiple vias are good methods to keep the impedance low.

#### 4.2 Buck-specific layout guidelines

This section provides guidance for the layout of specific areas of a power supply.

Keep in mind that the top and bottom planes are also used for head dissipation. It is good practice to place micro-vias and filled vias to keep the thermal resistance low. It is necessary to keep the vias around the pass devices (PVDD/Vsys, PGND and LX) to a reasonable amount and density by thinking about both the heat dissipation and the power planes impedance.

A thick through hole filled via is very good at conducting the heat from to to bottom planes, but can reduce the shielding effect and increase the impedance of power planes on internal layers.

The input capacitors should be places as close as possible to the chip, and the inductors should be placed close to the chip, but can be placed further away than the input caps depending on space constrains.

The differential feedback traces should be taken directly from the output at the capacitor pads and should be routed close to each other. It is also possible to take the feedback from the point of load, but this increases the risk of noise being introduced onto this trace because of the extra length it

| Application | Note |

|-------------|------|

|-------------|------|

#### **PCB Layout Guidelines**

would run. Good power planes can avoid the need for such point of load feedback configuration. The feedback traces must be shielded from all noise sources, especially the LX nodes of buck converters. Noise fed into a feedback pin often creates extra voltage ripple on the buck output. In the reference design example of section 4.4, the feedback traces are on the bottom layer and therefore away from the noisy LX nodes.

#### 4.3 Non-power pins

#### 4.3.1 AVDD

AVDD is used for the analog side of the sub-PMIC. It is sensitive to noise and must be decoupled from PVDD.

It is recommended to place a decoupling capacitor as close as possible to the chip's AVDD and AGND pads.

#### 4.3.2 GPIOs

4.4

GPIO pins are usually unaffected by the layout and so can be given a low priority during layout.

Example of PCB layout used in Dialog reference boards

#

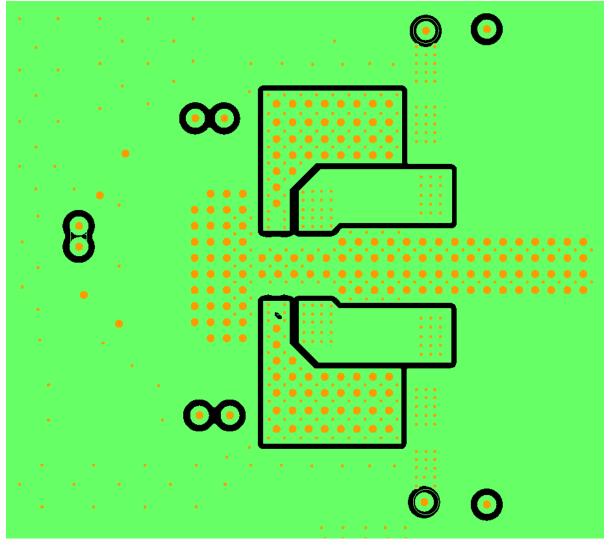

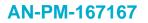

Figure 1: Layer 1 (top)

| Application Note | Revision 1.0 | 10-Dec-2021 |

|------------------|--------------|-------------|

|                  |              |             |

#### **PCB Layout Guidelines**

C13 is placed close to AVDD and AGND pads and connected to Vsys on layers 3-4 and to ground on layers 2-5-6.

The large copper area around Vsys is used as a heatsink and connected to a Vsys power plane on another layer through micro-vias.

The ground pad below the chip extends towards the input capacitors C7 and C8 and is connected to the ground plane on the top side of the board.

LX1 and LX2 pads are connected to the coils L1 and L2 through an internal plane. A choice has been made to prioritize the decoupling capacitors C7 and C8 and place them closer to the Vsys and GND pads.

FB1 and FB2 differential feedback lines are kept away from LX and go below the top layer.

Thin traces extending towards the left and top are GPIOs

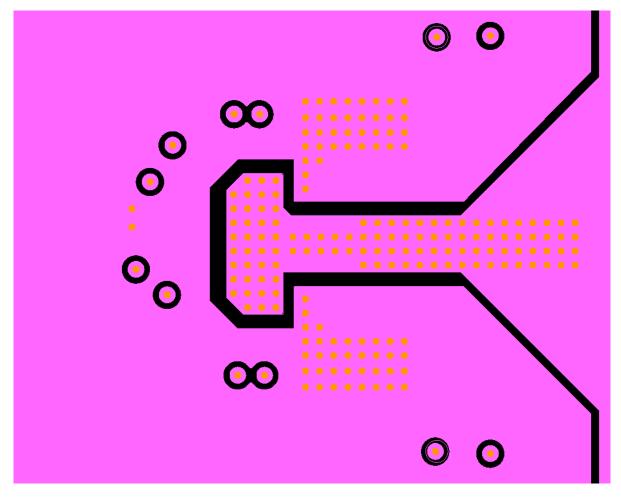

Figure 2: Layer 2 (internal)

This layer Is a ground plane with four polygons: Two LX traces going between the LX1 and LX2 pads on the chip and the coils L1 and L2. The other two polygons connect the Vsys trace to the PVDD pads.

Note the amount of layer 1-2 micro-vias to connect the planes together and the layer 2-4 micro-vias to transfer the heat.

| Application Note | Revision 1.0 |

|------------------|--------------|

| Application Note | Revision 1.0 |

#### **PCB Layout Guidelines**

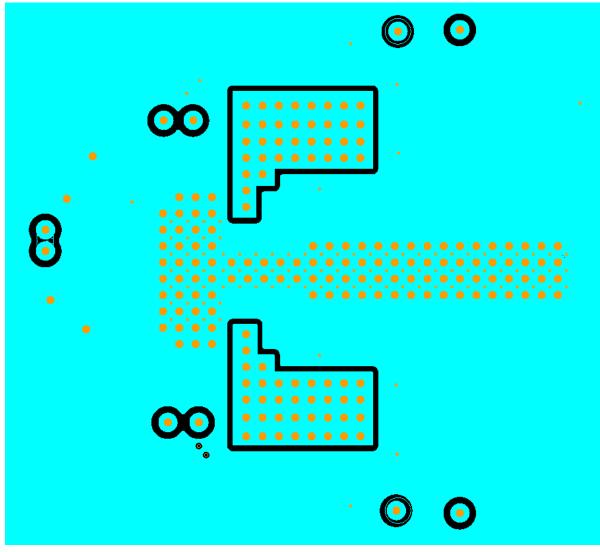

Figure 3: Layer 3 and 4 (internal)

These layers are shared between a ground plane under the chip and on the right side, and a Vsys plane left of the chip. Vias through layers 2, 3, 4 and 5 ensure a low thermal and electrical impedance between the layers.

**Application Note**

#### **PCB Layout Guidelines**

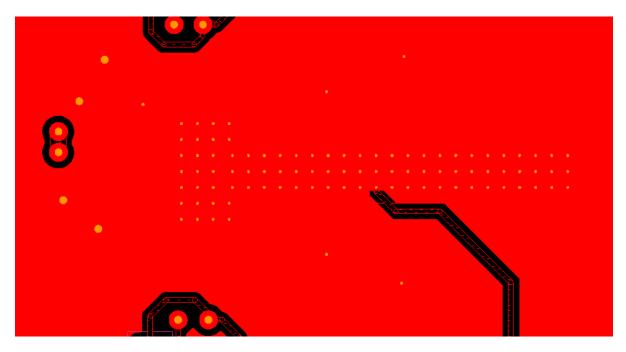

Figure 4: Layer 5 (internal)

This layer is a ground plane with a dissipation area for Vsys, connected to the top layer

#### PCB Layout Guidelines

Figure 5: Layer 6 (bottom)

This layer is a ground plane used mostly for heat dissipation.

The trace on the right is used for probing the ground voltage close to the chip. This can be considered as a quiet ground.

The symmetrical vias on the top and bottom of the chip are the differential feedback lines and are shielded form the noisy power signals.

#### **PCB Layout Guidelines**

Figure 6: Differential feedback

Those two lines connect the ground through R4 and Vout through R3, extending from the output capacitor on the right to the chip's feedback pins on the left. Traces are kept close to each other to limit noise on a sensitive signal.

R3 and R4 are zero-ohm resistors used for measurements and can be removed and shorted on a customer design.

The RC network using the shorting points SP5 and SP9, R1-R2 and C15 is optional and is used as a voltage divider. The typical application is to output 3.3V with Vsel set to 1.65V.

# 5 Conclusions

The PCB layout for integrated power management ICs requires careful consideration if an optimised system is to be achieved. Practical guidelines have been presented together with example layouts of Dialog's own reference boards.

| A | D | D | ica | tio | n | N | ote |

|---|---|---|-----|-----|---|---|-----|

|   |   |   |     |     |   |   |     |

# PCB Layout Guidelines

# Appendix A Layout checklist

<Insert text here>

# PCB Layout Guidelines

# **Revision History**

| Revision | Date        | Description      |

|----------|-------------|------------------|

| 1        | 10-Dec-2021 | Initial version. |

**Application Note**

#### **PCB Layout Guidelines**

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **Disclaimer**

Unless otherwise agreed in writing, the Dialog Semiconductor products (and any associated software) referred to in this document are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of a Dialog Semiconductor product (or associated software) can reasonably be expected to result in personal injury, death or severe property or environmental damage. Dialog Semiconductor and its suppliers accept no liability for inclusion and/or use of Dialog Semiconductor product (or applications and therefore such inclusion and/or use is at the customer's own risk.

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, express or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications. Notwithstanding the foregoing, for any automotive grade version of the device, Dialog Semiconductor reserves the right to change the information published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications, in accordance with its standard automotive change notification process.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document is subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog, Dialog Semiconductor and the Dialog logo are trademarks of Dialog Semiconductor Plc or its subsidiaries. All other product or service names and marks are the property of their respective owners.

© 2022 Dialog Semiconductor. All rights reserved.

#### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

# **Contact Dialog Semiconductor**

General Enquiry: Enquiry Form Local Offices: https://www.dialog-semiconductor.com/contact/sales-offices

**Application Note**

**Revision 1.0**

10-Dec-2021

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.