# ET 6050 Smart Transceiver

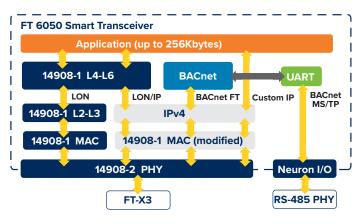

Figure 1. FT 6050 Firmware Protocol Stacks

#### **Product Description**

The FT 6050 Smart Transceiver is a system-on-chip for modernizing and consolidating smart control networks. It is a key product in Adesto's IzoT® platform — the most comprehensive and open control networking platform for the Industrial Internet of Things (IIoT). It offers compatibility with the large installed base of LON FT and BACnet MS/TP devices while adding support for LON/IP and BACnet/IP communication over the reliable and proven Free Topology (FT) channel. It is designed to bring unprecedented flexibility and openness while lowering development and device costs.

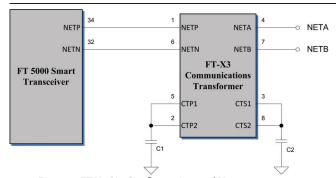

The FT 6050 Smart Transceiver integrates a high-performance Neuron® core with an FT twisted-pair transceiver. Combined with the proven FT-X3 Communications Transformer and inexpensive flash memory, the FT 6050 Smart Transceivers provide a very flexible, low-cost, feature-enhanced LON FT, BACnet MS/TP, LON/IP, and BACnet/IP solution all within the same device with a single application.

A rich set of LonMark and IoT standard profiles and data types is included that you can use to further reduce application development time.

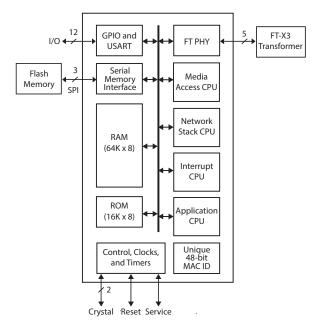

The FT 6050 Smart Transceiver includes four independent 8-bit logical processors to manage the physical MAC layer, the communication protocol stacks, the user application, and interrupts (see Figure 3, on page 2).

#### **Features**

- Built-in LON, LON/IP, BACnet FT, and BACnet MS/TP stacks provide compatibility with millions of LON and BACnet devices and enabling IP access to every FT 6050 based device

- Built-in Free Topology (FT) transceiver provides the most cost-effective, easy-to-install, and easy-to-use interface for communication with twisted-pair cables supporting polarity-insensitive free topology star, daisy chain, bus, loop, or mixed topology wiring and very high noise immunity

- Low-cost and royalty-free IzoT FT 6000 EVK available for rapid application development and testing

- Free and royalty-free IzoT SDKs available for simple integration with other processors

- Integrated quad core processor supports applications up to 256KB for a 5x increase over previous generations

- Supports up to 254 network variables (NVs), 127 aliases and 254 address table entries (16x increase)

- Neuron core supports easy migration of existing applications written for previous generation Neuron chips and smart transceivers

## PRODUCT DESCRIPTION

Q, Q, 1

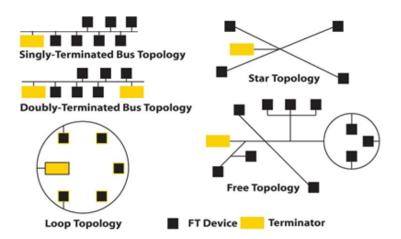

Figure 2. FT Free Topology Network Configurations

The FT 6050 Smart Transceiver supports polarity-insensitive cabling using a star, bus, daisy-chain, loop, or combination topology (see Figure 2). Installers don't have to follow a strict set of wiring rules imposed by other networking technologies. Instead, they can install wiring in the fastest and most cost- effective manner, thereby saving time and money. FT wiring also simplifies network expansion by eliminating restrictions on wire routing, splicing, and device placement. The FT 6050 extends all the benefits of FT wiring to IP devices, allowing an efficient multi-drop IP capability where multiple IP devices can be very simply connected in any topology without the need for switches or hubs.

#### **Multi-Protocol Operation**

The FT 6050 simultaneously supports up to four different communication protocols, as shown in Figure 1 (page 1), allowing device makers unprecedented flexibility in creating control devices for a wide variety of applications using one application. Backward compatibility and future proofing can both be met using a common platform based on the FT 6050 Smart Transceiver.

For LON FT communication, the FT 6050 implements the complete LON stack as defined by ISO/IEC 14908-1 and is fully backward compatible with devices running the LON stack, including devices based on the Neuron 3120, Neuron 3150, or the FT 3120, FT 3150, or FT 5000 Smart Transceiver.

For LON/IP communication, the FT 6050 implements layers 4 through 7 of the ISO/ IEC 14908-1 LON stack running on top of layers 2 and 3 of a UDP/IP stack. This allows the implementation of devices that are fully compatible with classic LON applications while supporting native IP addressing at the device level. This allows LON compatible applications to run unmodified over FT wiring while gaining IP addressing at the device level.

Figure 3. FT 6050 Smart Transceiver

#### Features, continued

- Up to 80MHz system clock provides up to a 16x performance improvement over previous generations

- · On-chip 64KB RAM and 16KB ROM

- 3.3V operation

- User-programmable interrupts, hardware USART, and 12 GPIO pins with 35 configurable I/O drivers

- Compatible with low-cost surface mount FT-X3 Communications Transformer

- Supports a rich set of LonMark® and IoT standard profiles and data types to reduce application development time

- Flash file system for data logging and other applications requiring persistent storage

- Unique 48-bit IEEE MAC ID

- 7mm x 7mm 48-pin QFN package

- -40°C to 85°C industrial temperature range

## PRODUCT DESCRIPTION

For BACnet/IP communication, the FT 6050 implements a BACnet/ IP standard stack running on top of layers 2 and 3 of a UDP/IP stack. This enables BACnet/ IP-compliant applications to run on the easy-to-use and easy-to-install FT channel, pushing BACnet/IP all the way down to the simplest of devices, while leveraging the ease-of-installation provided by LON commissioning tools. Devices thus provisioned are fully compatible and discoverable using industry standard, BTL certified, BACnet management clients.

For BACnet MS/TP communication, the FT 6050 implements a BACnet MS/TP stack that uses one of the FT 6050 USARTS to communicate with an external RS-485 transceiver using the BACnet MS/TP protocol. This enables BACnet MS/TP-compliant applications to be implemented in parallel with LON, LON/IP, and BACnet/ IP applications running on the FT 6050.

For other IP applications, the FT 6050 implements a UDP/IP stack that an application can use to create any type of IP interface that communicates with the easy-to-use and easy-to-install FT channel.

#### Compatibility

The FT 6050 series Smart Transceiver is fully compliant with LON devices implementing the ISO/IEC 14908-1 protocol on the FT channel type defined by ISO/ IEC 14908-2 and can communicate with devices that use Echelon's FTT-10 or FTT- 10A transceivers, FT 3120 or FT 3150 Smart Transceivers, LPT-10 or LPT-11 Link Power Transceivers, or other ISO/IEC 14908-2 compliant transceivers. The Neuron core in the FT 6050 Smart Transceiver uses the same

instruction set and architecture as the previous-generation Neuron core, including instructions for hardware multiplication and division. The FT 6050 Neuron core is source code compatible with applications written for the Series 5000 and 3100 Neuron core.

### Enhanced Performance Neuron Core Speed

The internal system clock for the FT 6050 Smart Transceiver can be user-configured to run from 5MHz to 80MHz. The required external crystal provides a 10MHz clock frequency, and an internal PLL boosts the frequency to a maximum of 80MHz as the internal system clock speed. The Neuron 3120/3150 core divided the external oscillator frequency by two to create the internal system clock. An FT 6050 Smart Transceiver running with an 80MHz internal system clock is thus 16 times faster than a 10MHz Neuron 3120 or Neuron 3150 core.

The Neuron core inside the FT 6050 Smart Transceiver includes a built-in hardware multiplier and divider to increase the performance of arithmetic operations.

#### **Higher Protocol Limits**

The FT 6050 Smart Transceiver supports up to 254 network variables per application, up to 127 aliases, and up to 254 address table entries. This is a significant increase over the previous limits of 62 network variables, 62 aliases, and 15 address table entries which simplifies network installation and supports more complex applications.

#### Interrupts

The FT 6050 Smart Transceiver lets developers define application interrupts to handle asynchronous

events triggered by selected state changes on any of the 12 GPIO pins, by on-chip hardware timercounter units, or by an on-chip highperformance hardware system timer.

#### **MAC Layer Enhancements**

The FT 6050 has an enhanced MAC layer that allows frame sizes up to 1280 bytes. This allows large IP frames to be carried over the FT channel without fragmenting the packet to provide better bandwidth utilization of the FT channel.

The dedicated processor cores for the MAC and network protocol support allows the application to have the same performance independent of the network traffic. Traditional uniprocessor designs running popular transceivers such as RS-485 must be interrupted repeatedly to receive every packet on the network, even when the packet turns out to not be addressed to the device. This increases the demands on the application processor and makes the amount of processing available to the application difficult to predict as it becomes a function of the network load.

#### JTAG Interface

The FT 6050 Smart Transceiver provides an interface for the Institute of Electrical and Electronics Engineers (IEEE) Standard Test Access Port and Boundary-Scan Architecture (IEEE 1149.1-1990) of the Joint Test Action Group (JTAG) to allow an FT 6050 chip to be included in the boundary-scan chain for device production tests.

#### **GPIO**

The FT 6050 Smart Transceiver provides 12 bidirectional GPIO pins that are 5V-tolerant and can be

## PRODUCT DESCRIPTION

1,0,0,1

configured to operate in one or more of 35 predefined standard input/ output modes. The chip also has two 16-bit timer/counters and a hardware USART that reduce the need for external logic and software development.

#### **Memory Architecture**

The FT 6050 Smart Transceiver eliminates the need for external serial EEPROM that the previous generation FT 5000 required and instead relies only on inexpensive external flash memories for nonvolatile application and data storage, and for Neuron firmware upgrades. It has 16KB of ROM and 64KB (44KB user-accessible) of RAM on the chip. Each chip, contains a unique identifier (IEEE MAC ID) in an on-chip, nonvolatile, read-only memory. Typical external flash memory configuration is 1MB of which 256KB is available for application code. This is a five-fold

increase in application size that can be hosted on the FT 6050 compared to previous generations.

The application code and configuration data are stored in the external non-volatile memory (NVM) and copied into the internal RAM during device reset; the instructions then execute from internal RAM. Writes to NVM are shadowed in the internal RAM and pushed out to external NVM by the Neuron firmware. The FT 6050 Smart Transceiver supports serial peripheral interface (SPI) for accessing off-chip, non-volatile memory.

The FT 6050 Smart Transceiver supports a variety of flash devices; we recommend:

## Adesto AT25SF041B or Adesto AT25SF081B

Adesto has also qualified the following SPI flash memory devices

for use with the FT 6050 Smart Transceiver: Macronix MX25L8035E, Micron M25PX80, ON Semiconductor LE25U40CM, Winbond W25X40CL, Winbond W25Q80BV.

#### **Noise Immunity**

A LON device based on the FT 6050 Smart Transceiver is composed of two components: the FT 6050 Series Smart Transceiver and an external communications transformer such as the FT-X3 communications transformer. The transformer enables operation in the presence of high frequency common-mode noise on unshielded twisted-pair networks. Properly designed devices can meet the rigorous Level 3 requirements of EN 61000-4-6 without the need for a network isolation choke. The transformer also offers outstanding immunity from magnetic noise, eliminating the need for protective magnetic shields in most applications.

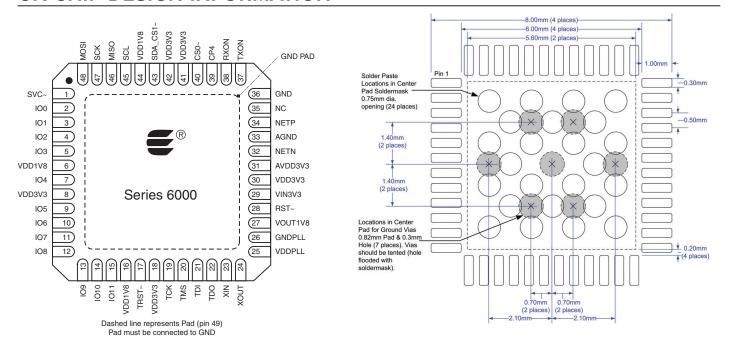

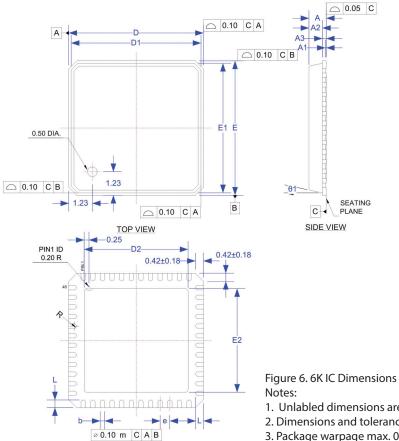

## **6K CHIP DESIGN INFORMATION**

Figure 4. 6K IC Pin Configuration

Figure 5. Recommended 6K Pad Layout

## **6K IC MECHANICAL SPECIFICATION**

| SYMBOL | MIL                          | LIMET | ER   | INCH       |        |       |  |

|--------|------------------------------|-------|------|------------|--------|-------|--|

|        | MIN.                         | NOM.  | MAX. | MIN.       | NOM.   | MAX.  |  |

| Α      |                              |       | 0.90 |            |        | 0.035 |  |

| A1     | 0.00                         | 0.01  | 0.05 | 0.00       | 0.0004 | 0.002 |  |

| A2     |                              | 0.65  | 0.70 |            | 0.026  | 0.028 |  |

| А3     | 0.20 REF.                    |       |      | 0.008 REF. |        |       |  |

| b      | 0.18                         | 0.23  | 0.30 | 0.007      | 0.009  | 0.012 |  |

| D      | 7.00 bsc<br>6.75 bsc         |       |      | 0.276 bsc  |        |       |  |

| D1     |                              |       |      | 0.266 bsc  |        |       |  |

| D2     | 5.20                         | 5.40  | 5.60 | 0.205      | 0.213  | 0.220 |  |

| Е      | 7.00 bsc<br>6.75 bsc         |       |      | 0.276 bsc  |        |       |  |

| E1     |                              |       |      | 0.266 bsc  |        |       |  |

| E2     | 5.20                         | 5.40  | 5.60 | 0.205      | 0.213  | 0.220 |  |

| L      | 0.30                         | 0.40  | 0.50 | 0.012      | 0.016  | 0.020 |  |

| е      | 0.50 bsc                     |       |      | 0.020 bsc  |        |       |  |

| ⊕1     | 0°                           |       | 12°  | 0°         |        | 12°   |  |

| R      | 0.09                         |       |      | 0.004      |        |       |  |

| TOLE   | ERANCES OF FORM AND POSITION |       |      |            |        |       |  |

| aaa    |                              | 0.10  |      | 0.004      |        |       |  |

| bbb    |                              | 0.10  |      | 0.004      |        |       |  |

| ccc    | 0.05 0.002                   |       |      |            |        |       |  |

- 1. Unlabled dimensions are in millimeters.

- 2. Dimensions and tolerances conform to ASME Y14.5M.-1994.

- 3. Package warpage max. 0.08 mm.

- 4. Package corners unless otherwise specified are R0.175±0.025 mm.

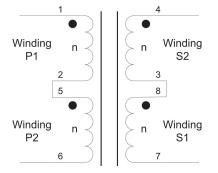

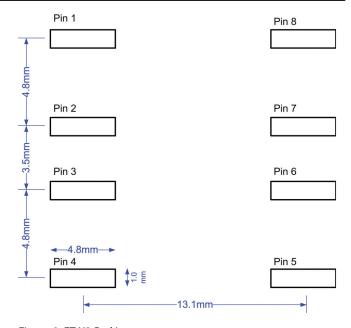

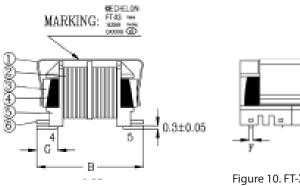

## FT-X3 DESIGN INFORMATION

BOTTOM VIEW

Figure 7. FT-X3 Pin Configuration and Pin-out

Figure 8. FT-X3 Transformer Pin Assignments Note: There is no marking for Pin 1 on the FT-X3 because it is rotationally symmetrical

Figure 9. FT-X3 Pad Layout Note: Add via stothe ends of each pin pad connection (just outside)of the SMT pad rectangles) to provide additional mechanical supportfor the transformer

## FT-X3 MECHANICAL SPECIFICATIONS

UNIT : mm = 12.5 MAX $= 16.5 \pm 0.5$ = 17.0 MAX $= 4.65\pm0.2$  $= 3.55 \pm 0.3$  $= 0.8 \pm 0.1$  $= 3.0\pm0.5$  $= 13.0\pm0.5$

#### Figure 10. FT-X3 Dimensions

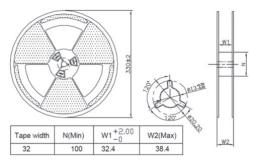

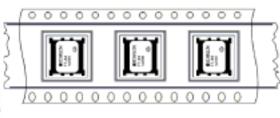

## **6K AND FT-X3 TAPE AND REEL INFORMATION**

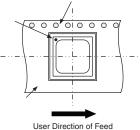

Note: 6K ICs are uniformly loaded in the carrier tape such thatpin1isorientedinquadrant RO.3 MX 1 toward the side of the tape having round sprocket holes.

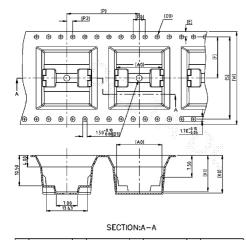

Ø 1.5 +0.1/-0.0 - 12.00 2.00 ±.10 SEE NOTE 3 4.00 SEE NOTE I Notes: 1. All dimensions in mm SECTION A - A 2.Tolerances unless noted: 1PL+ 0.2.2PL + 0.1

Figure 11. 6K Tape and Reel Orientation

13.0 ± .20 (ARBOR HO

TAPE SIZE W2 ₩s + 1.5 8.4- 0.0 4.0 ± 0.25 14.4 MAX. +2.0 12.4-0.0 12mm 5.0 ± 0.50 18.4 MAX. +2.0 16.4-0.0 15mm 7.0 ± 0.50 22.4 MAX. 24mm 11.0 ± 0.50 30.4 MAX. 11.0 ±0.50 32mm 44mm 11.0 ± 0.50 50.4 MAX.

Figure 13. 6K 7 Reel and Hub Dimensions

Figure 15.FT-X3 Reel and Hub Dimensions in mm Note: Tolerances unless noted: 1PL+; 2PL+0.2; 3PL + 0.1; ANG + 0.5"; FRACT +

Figure 12. 6K Carrier Tape Outline

USER OFFICTION OF FRED Figure 14. FT-X3 Reel and Tape Device Placement

hole

Placement"

#### Notes:

1.Material:blackconductivepolystyrenePS

3. 10 Sprocket hole pitch

cumulative tolerance +0.2 4.CambercompliantwithEIA481 5. Pocket position relative to sprocket hole measured as true

position of pocket, not pocket

For more information, refer to EIA-481-B, "Taping of Surface MountComponentsforAutomatic

- 2. Inspect per EIA-481-3 standard.

- 3. Tape thickness: 0.5 ±0.05 mm

- 4. 10 Sprocket hole pitch cumulative tolerance ±0.20

- 5. Carrier chamber is within 1 mm in 100 mm6. Packing length per 22" reel: 10.2 meters

- 7. Packing length per 13" reel: 3.4 meters

- 8. Component load per 13" reel: 100 PCS 9. Compression strength: 1.5 kgf min.

- 10. Environment-related substance must meet DELTA's general spec no. 10000-0162

| ı | W | 32.00±0.30 | Р  | 24.00±0.10 | АΟ | 15.10±0.10 | ВO | 17.80±0.15  |

|---|---|------------|----|------------|----|------------|----|-------------|

| I | s | 28.40±0.10 | P0 | 4.00±0.10  |    |            | В1 | 6.30±0.10   |

| I | Ε | 1.75±0.10  | P2 | 2.00±0.10  |    |            |    |             |

| I | F | 14.20±0.10 | DO | ø1.50±0.10 | KΟ | 13.00±0.10 |    |             |

| I | Т | 0.50±0.04  | D1 | Ø2.00 MIN  | K1 | 12.40±0.10 | CO | LOR: BK/ANT |

Figure 16. FT-X3 Carrier Tape Packing

## APPLICATION DEVELOPMENT

A typical FT 6050 Smart Transceiver-based device requires a power source, crystal, external memory, and an I/O interface to the device being controlled (see Figure 17).

Adesto provides all of the building blocks required to successfully design and field cost-effective, robust products based on the FT 6050 Smart Transceiver. Adesto's end-to-end solutions include a comprehensive set of development tools, network interfaces, routers, and network tools. In addition, pre-production design review services, training, and worldwide technical support (including onsite support) are available through Adesto's Support technical assistance program.

The following development tools are available for developing applications for the FT 6050 Smart Transceiver:

Serial Flash

Memory

Serial Flash

Memory

Serial Flash

Memory

Serial Flash

Memory

FT 6050

SoC

FT 6050

SoC

FT 8050

External

Transformer

10MHz

Crystal

LON FT Channel

Figure 17. Typical FT 6050-based Device

IzoT FT 6000 EVK — a complete hardware and software platform for creating or evaluating LON, LON/ IP, BACnet FT, and BACnet MS/TP devices based on an Adesto smart transceiver or Neuron chip. Using the FT 6000 EVK, developers can create applications that run on the FT 6050 Smart Transceiver using the highly productive Neuron C programming language.

IzoT SDK Premium Edition — a software development kit that enables developers to build communicating devices using any processor that runs Linux for the application and Layers 3 through 7 of the LON/IP and LON protocol stacks. The IzoT SDK Premium Edition includes royalty-free firmware for the FT 6050 Smart Transceiver that enables the FT 6050 to be used as a PHY chip to interface to an FT channel.

IzoT ShortStack SDK — a free software development kit, available at github.com/izot/shortstack, that enables developers to build communicating devices using any processor that can run the application plus a tiny IzoT ShortStack driver. The IzoT ShortStack SDK includes royalty-free firmware for the FT 6050 Smart Transceiver that enables the FT 6050 to be used as a Layer 2 to 6 LON and LON/IP protocol processor with integrated PHY interface to an FT channel.

## PRODUCT SPECIFICATIONS

1.0,0,0

#### **Data Communications Type**

Differential Manchester encoding

#### **Network Polarity**

Polarity insensitive

#### Isolation between Network and FT 6050

0-60Hz, 60 seconds: 1000Vrms; 0-60Hz, continuous: 277Vrms

#### **EMI**

Compliant with FCC Part 15 Subpart B and EN55022 Level B

#### **ESD**

Compliant with EN 61000-4-2, Level 4

#### Radiated Electromagnetic Susceptibility Compliant with EN 61000-4-3, Level 3

Fast Transient/Burst Immunity

## Compliant with EN 61000-4-4, Level 4

#### **Surge Immunity**

Compliant with EN 61000-4-5, Level 3

#### Conducted RF Immunity

Compliant with EN 61000-4-6, Level 3

#### **Transmission Speed**

78 kilobits per second

## Number of Transceivers per Segment

Up to 64

#### **Network Wiring**

24 to 16AWG twisted pair; see *Series* 6000 Chip Data Book or Junction Box and Wiring Guidelines engineering bulletin for qualified cable types

#### Network Length in Free Topology

500m (1640 feet) maximum total wire with no repeaters; 500m (1640 feet) maximum device-to-device distance

## Network Length in Doubly-terminated Bus Topology

2700m (8,850 feet) with no repeaters

## Maximum Stub Length in Doublyterminated Bus Topology

3m (9.8 feet)

#### **Network Termination**

One terminator in free topology; two terminators in bus topology (more details in *Series 6000 Chip Data Book*).

#### **Power-down Network Protection**

High impedance when unpowered

#### **Operating Temperature**

-40° to 85°C

#### **Operating Humidity**

25-90% RH @50°C, non-condensing (FT-X3 Communications Transformer)

#### Non-operating Humidity

95% RH @ 50°C, non-condensing (FT-X3 Communications Transformer)

#### Vibration

1.5g peak-to-peak, 8Hz-2kHz (FT-X3 Communications Transformer)

#### **Mechanical Shock**

100g (peak) (FT-X3 Communications Transformer)

### Reflow Soldering Temperature Profile

Refer to Joint Industry Standard IPC/ JEDEC J-STD-020D.1 (March 2008)

#### Peak Reflow Soldering Temperature

260°C (FT 6050 Smart Transceiver)

245°C (FT-X3 Communications Transformer)

#### Co-planarity

0.12mm (FT-X3 Communications Transformer)

#### Mass

6g (FT-X3 Communications Transformer)

| Model #      | Product Name                    | Product Description                                                  |  |  |  |

|--------------|---------------------------------|----------------------------------------------------------------------|--|--|--|

| 14450R-500   | FT 6050 Smart Transceiver       | Tape and reel package, quantity 500                                  |  |  |  |

| 14255R-100   | FT-X3 Comunications Transformer | Tape and reel package, quantity 100                                  |  |  |  |

| 10070R-43-54 | IzoT FT 6000 EVK                | Hardware and software development kit                                |  |  |  |

| 23360-10     | IzoT SDK Premium Edition        | Software development kit                                             |  |  |  |

| 23400-FV     | IzoT Short Stack SDK            | Software development kit available at www.github.com/izot/shortstack |  |  |  |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.