#### ISL74420M

Radiation Tolerant Quad Clock Fanout IC

### **Description**

The ISL74420M is a radiation tolerant quad output clock fanout IC with an optional internal oscillator. It provides synchronization clocks for any application and is particularly useful in multiphase power converters. Each of the four outputs can be set to a different frequency division and phase delay.

Multiple ISL74420M can be connected together to create more than four synchronized clocks.

The division and delay options can be set through selection pins or over an I<sup>2</sup>C/SMBus interface.

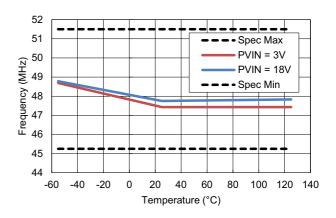

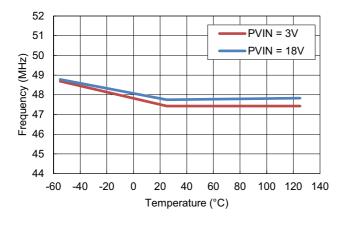

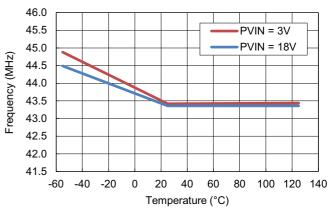

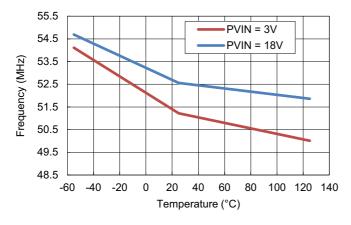

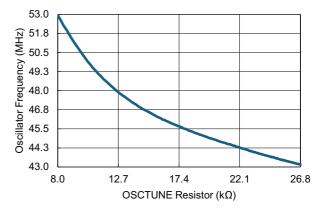

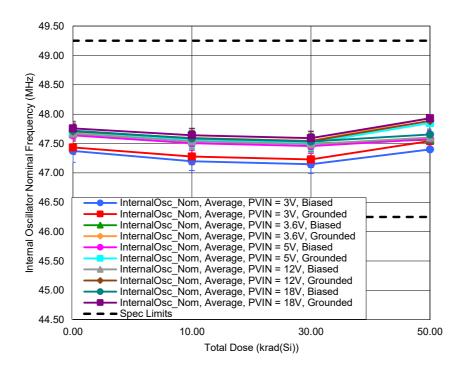

The internal oscillator operates at 48MHz and is tunable ±10% with an external resistor.

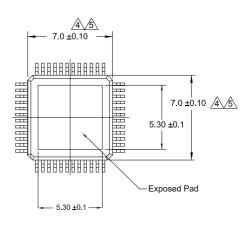

The ISL74420M is offered in a 48 Lead TQFP-EP that is fully specified across the temperature range of -55°C to +125°C.

### **Applications**

- Multiphase power converters

- Synchronizing multiple converters on one board to control EMI and crosstalk

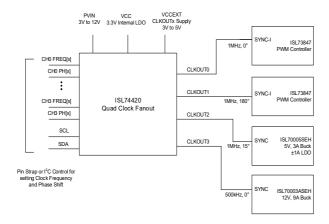

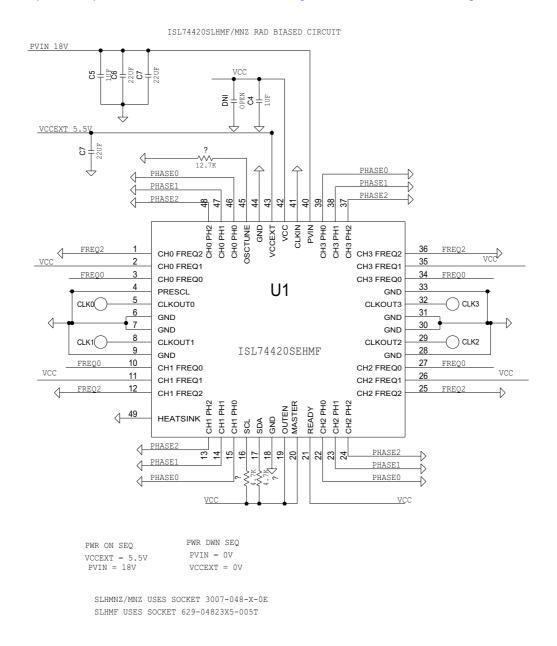

Figure 1. Typical Application

#### **Features**

- Qualified to Renesas Rad Tolerant Screening and QCI Flow (R34TB0004EU)

- PVIN supply range 3V to 18V

- Independent clock output supply 3V to 5.5V

- Programmable output frequency starting at 25kHz

- · Internal or external clock source

- Programmable phase delay as low as 15° increments

- I<sup>2</sup>C/SMBus Compatible

- I<sup>2</sup>C/SMBus or pin strapping to set frequency and phase

- TID Radiation Lot Acceptance Testing (LDR: ≤10mrad(Si)/s)

- ISL74420M30NZ: 30krad(Si)

- ISL74420M50NZ: 50krad(Si)

- SEE Characterization

- No DSEE for PVIN = 20.7V, V<sub>CC</sub> = 5.5V, and VCCEXT = 6.5V at 46MeV·cm<sup>2</sup>/mg

- SEFI <10µm<sup>2</sup> at 46MeV·cm<sup>2</sup>/mg

- No missing pulse SETs and Frequency Deviation SETs <3.6% on CLKOUTx at 46MeV·cm<sup>2</sup>/mg

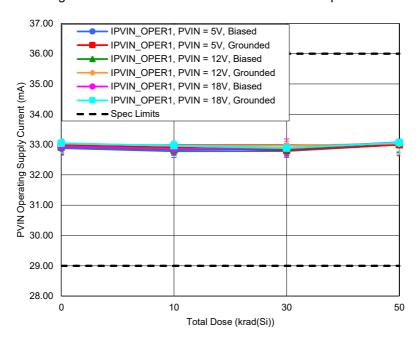

Figure 2. Internal Oscillator Nominal Frequency

Accuracy Over Temp

# **Contents**

| 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                      |                                               |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|-----------------------------------------------|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.1                 | • •                  | • •                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.2                 | Block Dia            | agram                                         | 5  |

| 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Inf             | ormation             |                                               | 6  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.1                 | Pin Assig            | nments                                        | 6  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.2                 | Pin Desc             | riptions                                      | 6  |

| 1.1         Typical Application           1.2         Block Diagram           2. Pin Information         2.1           2.1         Pin Assignments           2.2         Pin Descriptions           3. Specifications         3.1           3.2         Recommended Operating Conditions           3.3         3.2           3.3         Outgas Testing           3.4         Thermal Specifications           3.5         Electrical Specifications           3.6         PC/SMBus Interface Specifications           4. Typical Performance Graphs         Operation           5.1         Frequency and PC/SMBus Address Selection           5.1.1         Internal Oscillator Tuning           5.1.2         CLKOUT Configuration Scenarios           5.1.1         Internal Oscillator Tuning           5.1.2         CLKOUT Configuration Scenarios           5.3         PC/SMBus Communication Device Registers           5.3.1         MISC_CTRL Register           5.3.2         PC/SMBus Communication Device Registers Access Support Tools           5.4         OUTEN and READY           5.4         OUTEN and READY           5.4         OUTEN and READY           5.4         PC/SMBus Sprial Interf | 9                   |                      |                                               |    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                   |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.2                 |                      | · · · · · · · · · · · · · · · · · · ·         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.3                 |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.4                 | -                    | · · · · · ·                                   |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.5                 | Electrical           | Specifications                                | 10 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.6                 | I <sup>2</sup> C/SMB | us Interface Specifications                   | 14 |

| 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Typica              | l Perform            | ance Graphs                                   | 16 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      | •                                             |    |

| <b>J</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                   |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.1                 | •                    |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      | · · · · · · · · · · · · · · · · · · ·         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.2                 |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.4                 |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 5.4.1                | Leader and Follower for More than Four Clocks | 22 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.5                 | Clock Ou             | tput Frequency Accuracy                       | 22 |

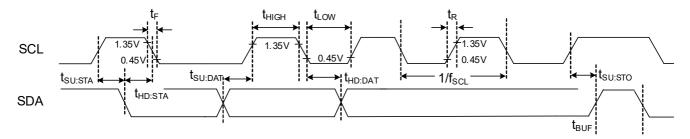

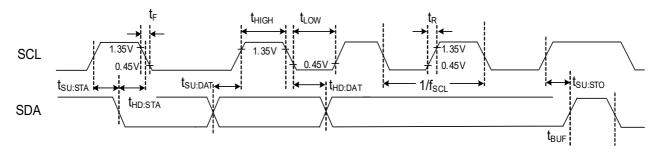

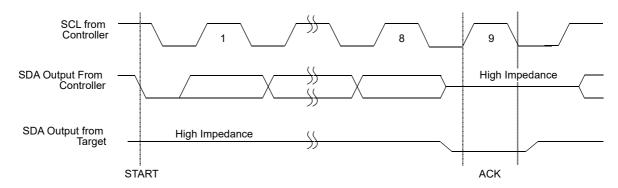

| 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sup>2</sup> C/SM | Bus Seria            | al Interface                                  | 23 |

| •-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      | ·                                             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.3                 |                      |                                               |    |

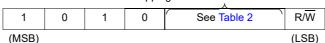

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.4                 | I <sup>2</sup> C/SMB | us Target Device Addressing                   | 24 |

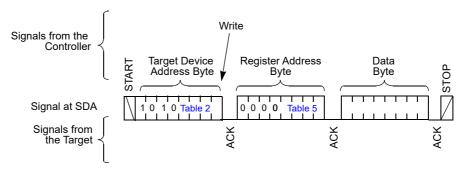

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.5                 | I <sup>2</sup> C/SMB | us Single Byte Write Operation                | 25 |

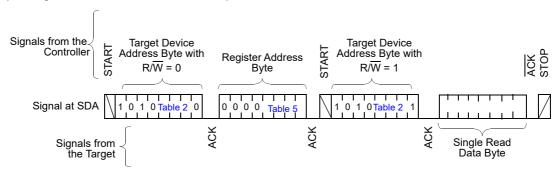

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.6                 | I <sup>2</sup> C/SMB | us Single Byte Read Operation                 | 25 |

| 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Applic              | ation Info           | rmation                                       | 25 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7.2                 |                      |                                               |    |

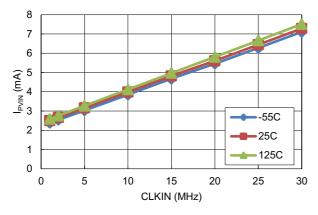

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      | PVIN Current when VCCEXT is Tied to VCC       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 7.2.2                | PVIN Current when VCCEXT is Separate          | 26 |

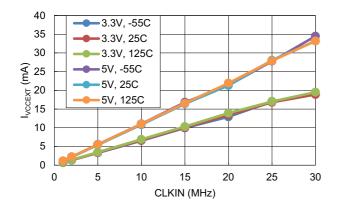

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 7.2.3                | VCCEXT Current                                | 26 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 7.2.4                | Additional Loading of the CLKOUT Pins         | 26 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7.3                 | Leader a             | nd Follower Configuration                     | 27 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7.4                 | Power St             |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 7.4.1                |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                      | Startup Sequence                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                   |                      | ·                                             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7.6                 | Layout R             | ecommendations                                | 28 |

| 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Radiat              | ion Tolera           | ance                                          | 28 |

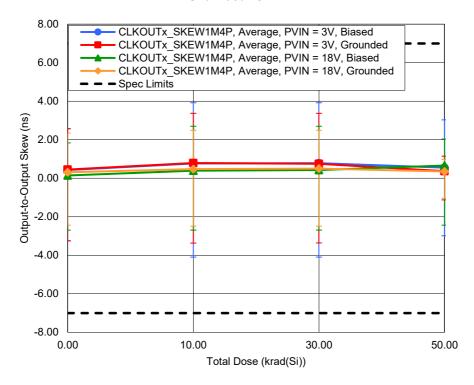

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8.1                 |                      | zing Dose (TID) Testing                       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 8.1.1                | Introduction                                  | 29 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 8.1.2                | Results                                       | 30 |

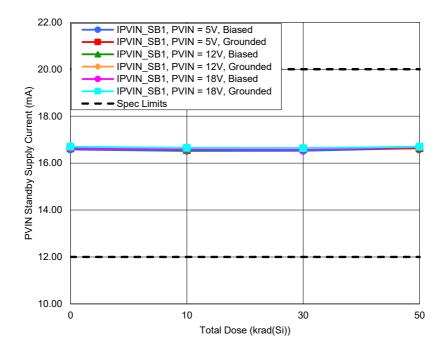

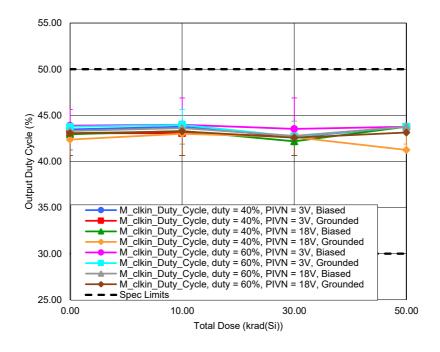

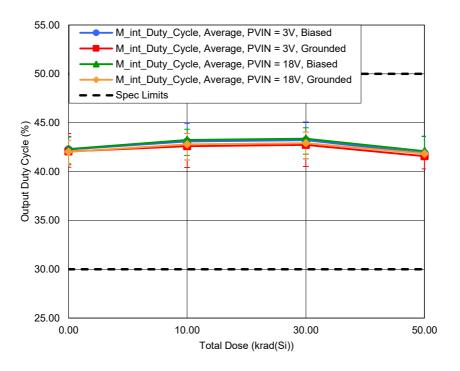

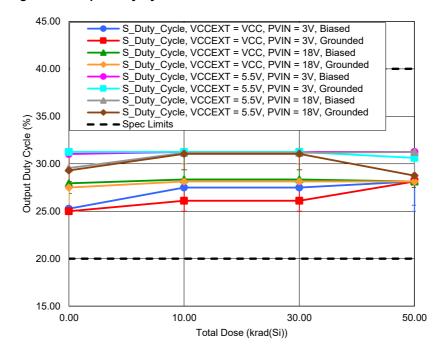

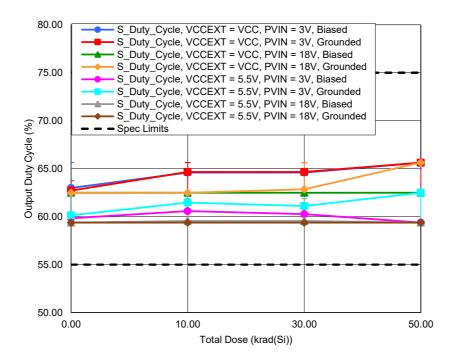

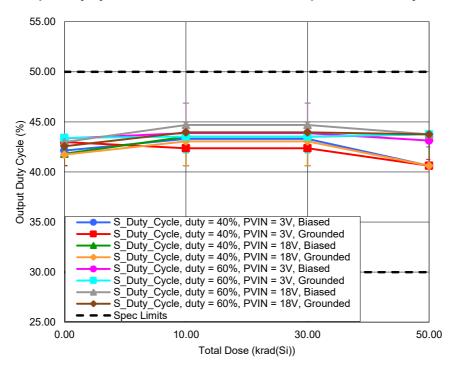

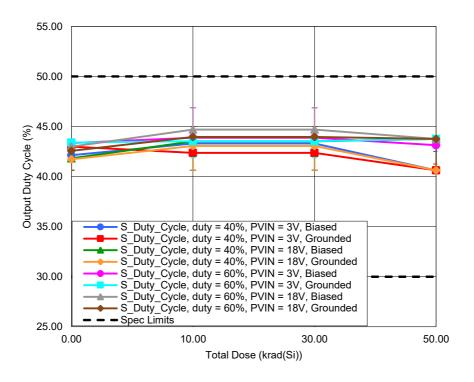

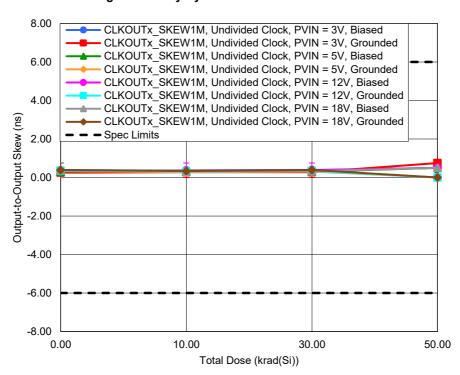

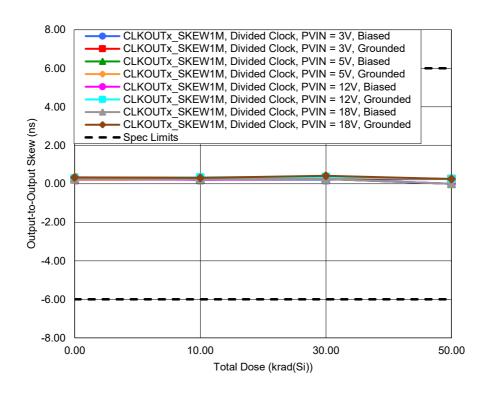

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 8.1.3                | Typical Radiation Performance                 | 31 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 8.1.4                | Conclusion                                    | 36 |

## ISL74420M Datasheet

|     | 8.2   | Single I   | Event Effects Testing                           | 42 |

|-----|-------|------------|-------------------------------------------------|----|

|     |       | 8.2.1      | Introduction                                    | 42 |

|     |       | 8.2.2      | Test Facility                                   | 42 |

|     |       | 8.2.3      | Destructive Single Event Effects (DSEE) Results | 42 |

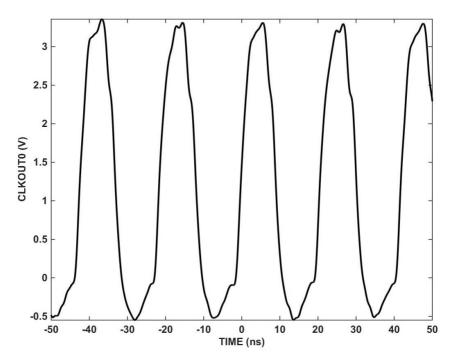

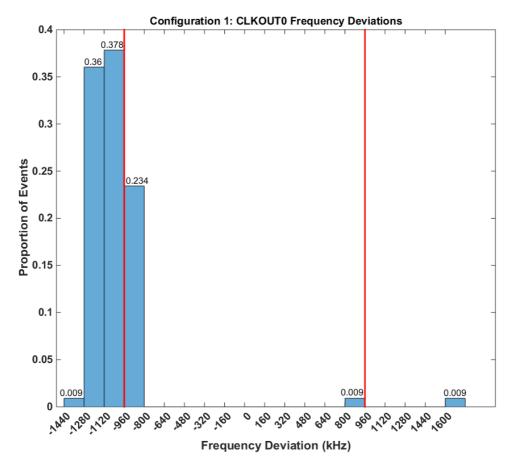

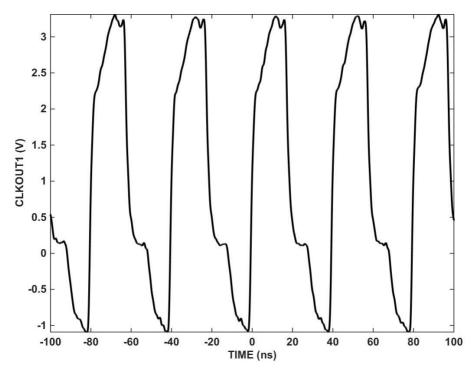

|     |       | 8.2.4      | SET and SEFI Results                            | 43 |

|     |       | 8.2.5      | Conclusion                                      | 46 |

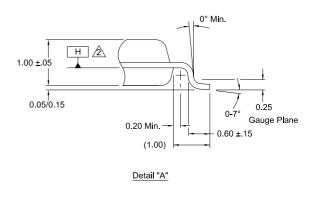

| 9.  | Packa | age Outli  | ne Drawing                                      | 47 |

| 10. | Orde  | ring Infor | mation                                          | 48 |

| 11. | Revis | ion Histo  | rv                                              | 48 |

## 1. Overview

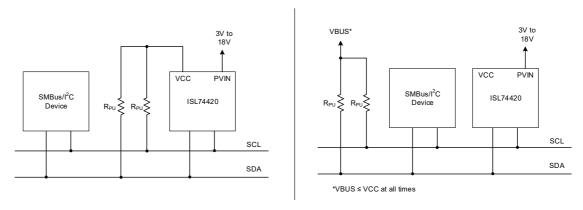

# 1.1 Typical Application

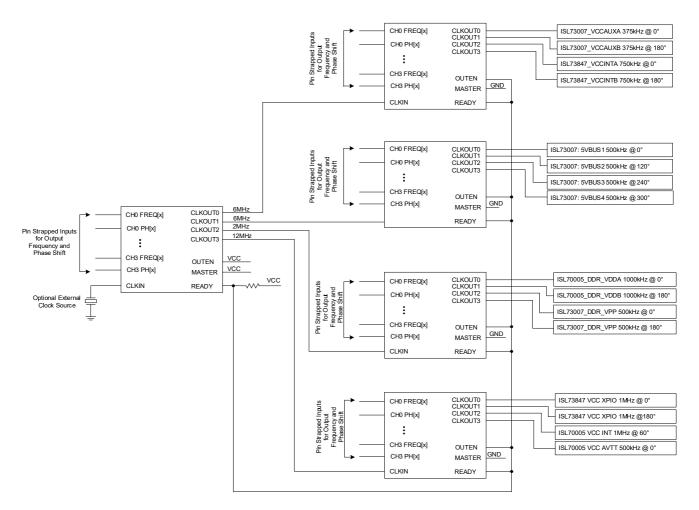

Figure 3. Leader-Follower Configuration for Multi-Channel Application

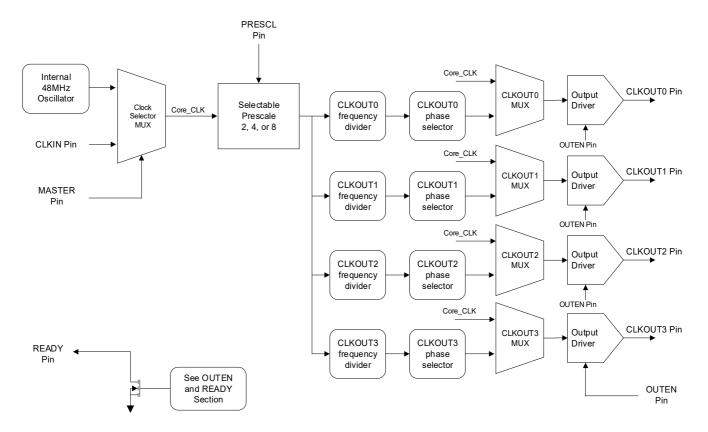

# 1.2 Block Diagram

Figure 4. Block Diagram

# 2. Pin Information

# 2.1 Pin Assignments

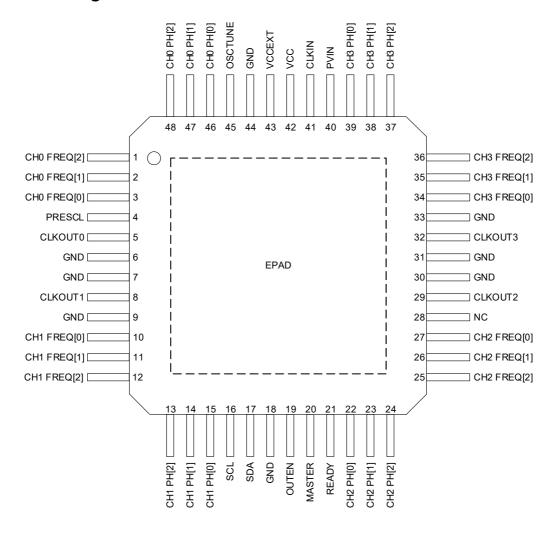

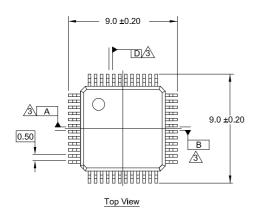

Figure 5. Pin Assignments - Top View

# 2.2 Pin Descriptions

| Pin<br>Number              | Pin<br>Name   | ESD<br>Circuit | Description                                                                                 |

|----------------------------|---------------|----------------|---------------------------------------------------------------------------------------------|

| 1                          | CH0 FREQ[2]   | 1              |                                                                                             |

| 2                          | CH0 FREQ[1]   | 1              | 3-level (tri-level) logic with 3-bit setting for frequency division selection on Channel 0. |

| 3                          | CH0 FREQ[0] 1 |                |                                                                                             |

| 4                          | PRESCL        | 1              | 3-level (tri-level) logic prescale selection for all channels.                              |

| 5                          | CLKOUT0       | 3              | Clock output pin for Channel 0.                                                             |

| 6, 7, 9, 30, 31,<br>33, 44 | GND           | -              | Connect these pins to the PCB ground.                                                       |

| 8                          | CLKOUT1       | 3              | Clock output pin for Channel 1                                                              |

| Pin<br>Number | Pin<br>Name | ESD<br>Circuit                                                                        | Description                                                                                                                                                                                                                                                                                                                        |  |

|---------------|-------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10            | CH1 FREQ[0] | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                    |  |

| 11            | CH1 FREQ[1] | 1                                                                                     | 3-level (tri-level) logic with 3-bit setting for frequency division selection on Channel 1                                                                                                                                                                                                                                         |  |

| 12            | CH1 FREQ[2] | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                    |  |

| 13            | CH1 PH[2]   | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                    |  |

| 14            | Name        | 3-level (tri-level) logic with 3-bit setting for phase delay selection for Channel 1. |                                                                                                                                                                                                                                                                                                                                    |  |

| 15            | CH1 PH[0]   | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                    |  |

| 16            | SCL         | 1                                                                                     | I <sup>2</sup> C/SMBus clock input. SCL requires an external pull-up resistor for proper operation. Tie to VCC through a $4.7 k\Omega$ to $100 k\Omega$ resistor even if I <sup>2</sup> C/SMBus is not going to be used.                                                                                                           |  |

| 17            | SDA         | 1                                                                                     | I <sup>2</sup> C/SMBus data input/output. SDA requires an external pull-up resistor for proper operation. Tie to VCC through a $4.7k\Omega$ to $100k\Omega$ resistor even if I <sup>2</sup> C/SMBus is not going to be used.                                                                                                       |  |

| 18            | GND         | -                                                                                     | Connect this pin to the PCB ground.                                                                                                                                                                                                                                                                                                |  |

| 19            | OUTEN       | 1                                                                                     | Logic level input to enable the CLKOUTx pins.                                                                                                                                                                                                                                                                                      |  |

| 20            | MASTER      | 1                                                                                     | Logic level input to select if the part should use its internal oscillator when no external clock is present. A logic high enables Leader Mode and uses the internal 48MHz oscillator if no CLK-IN signal is present. A logic low enables Follower Mode and the internal oscillator is disabled, relying only on the CLK-IN input. |  |

| 21            | READY       | 1                                                                                     | Open-drain output to indicate if the part is ready to enable the CLKOUTx pins                                                                                                                                                                                                                                                      |  |

| 22            | CH2 PH[0]   | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                    |  |

| 23            | CH2 PH[1]   | 1                                                                                     | 3-level (tri-level) logic with 3-bit setting for phase delay selection for Channel 2.                                                                                                                                                                                                                                              |  |

| 24            | CH2 PH[2]   | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                    |  |

| 25            | CH2 FREQ[2] | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                    |  |

| 26            | CH2 FREQ[1] | 1                                                                                     | 3-level (tri-level) logic with 3-bit setting for frequency division selection on Channel 2.                                                                                                                                                                                                                                        |  |