### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to <a href="http://www.renesas.com/inquiry">http://www.renesas.com/inquiry</a>.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

## MITSUBISHI MICROCOMPUTERS M37735MHLXXXHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

#### **DESCRIPTION**

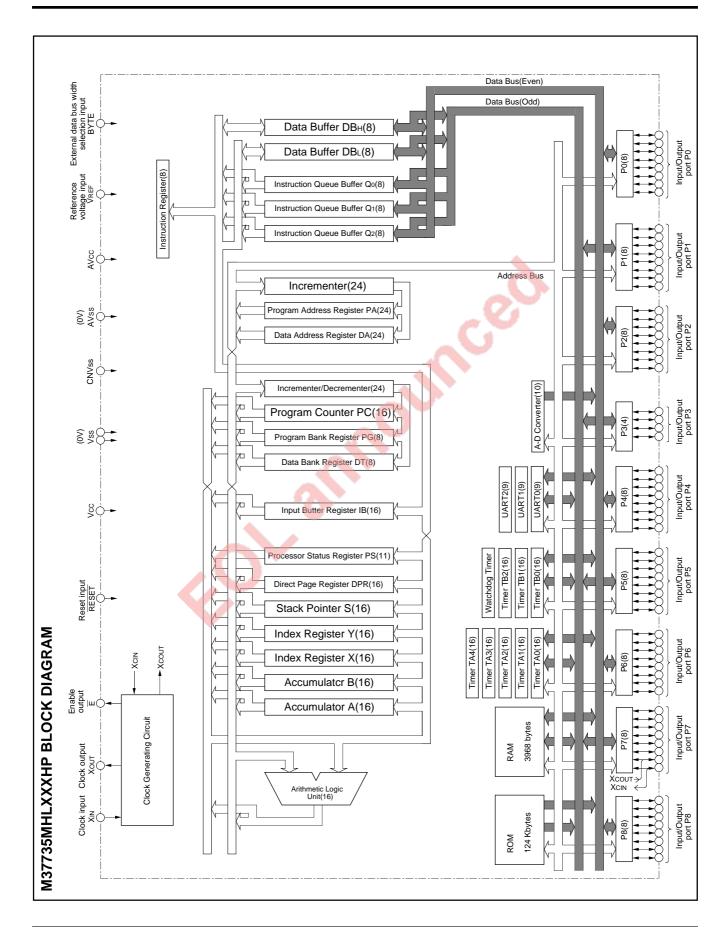

The M37735MHLXXXHP is a single-chip microcomputer using the 7700 Family core. This single-chip microcomputer has a CPU and a bus interface unit. The CPU is a 16-bit parallel processor that can be an 8-bit parallel processor, and the bus interface unit enhances the memory access efficiency to execute instructions fast. This microcomputer also includes a 32 kHz oscillation circuit, in addition to the ROM, RAM, multiple-function timers, serial I/O, A-D converter, and so on.

Its strong points are the low power dissipation, the low supply voltage and the small package.

#### **FEATURES**

| ●Number of basic              | instructions      | 103                             |  |

|-------------------------------|-------------------|---------------------------------|--|

| <ul><li>Memory size</li></ul> | ROM               | 124 Kbytes                      |  |

|                               | RAM               | 3968 bytes                      |  |

| ●Instruction exec             | ution time        |                                 |  |

| The fastest instr             | uction at 12 MHz  | requency 333 ns                 |  |

| ●Single power su              | pply              | 2.7–5.5 V                       |  |

| ●Low power diss               | pation (At 3 V su | pply voltage, 12 MHz frequency) |  |

|                               |                   | 9 mW (Typ.)                     |  |

| ●Interrupts                                | . 19 types, 7 levels |

|--------------------------------------------|----------------------|

| ●Multiple-function 16-bit timer            | 5 + 3                |

| ●Serial I/O (UART or clock synchronous)    | 3                    |

| ●10-bit A-D converter                      | 8-channel inputs     |

| ●12-bit watchdog timer                     |                      |

| ●Programmable input/output                 |                      |

| (ports P0, P1, P2, P3, P4, P5, P6, P7, P8) | 68                   |

| ■Clock generating circuit                  | 2 circuits built-in  |

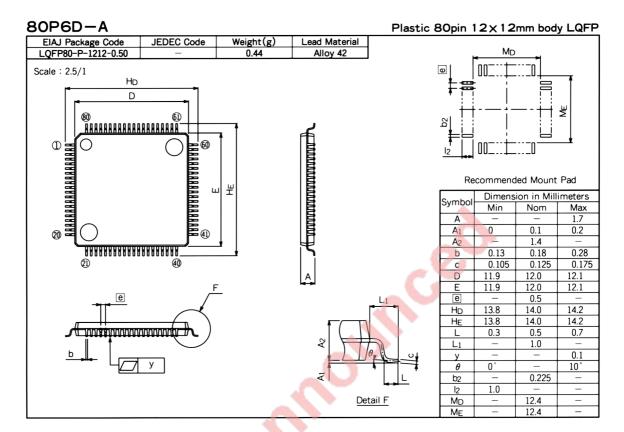

| ●Small package 80-pin plastic mole         | ded fine-pitch QFP   |

| (80P6D-A;0                                 | 0.5 mm lead pitch)   |

#### **APPLICATION**

Control devices for general commercial equipment such as office automation, office equipment, personal information equipment, and so on.

Control devices for general industrial equipment such as communication equipment, and so on.

#### **FUNCTIONS OF M37735MHLXXXHP**

|                                                       | Parameter                          | Functions                                                                                        |  |  |  |

|-------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| Number of basic instructions                          |                                    | 103                                                                                              |  |  |  |

| Instruction execution time                            |                                    | 333 ns (the fastest instruction at external clock 12 MHz frequency                               |  |  |  |

| Memory size                                           | ROM                                | 124 Kbytes                                                                                       |  |  |  |

| Wellery Size                                          | RAM                                | 3968 bytes                                                                                       |  |  |  |

| Input/Output ports                                    | P0 – P2, P4 – P8                   | 8-bit × 8                                                                                        |  |  |  |

| Input/Output ports                                    | P3                                 | 4-bit X 1                                                                                        |  |  |  |

| Multi-function timers                                 | TA0, TA1, TA2, TA3, TA4 16-bit X 5 |                                                                                                  |  |  |  |

| watt-fariction timers                                 | TB0, TB1, TB2                      | 16-bit X 3                                                                                       |  |  |  |

| Serial I/O (UART or clock synchronous serial I/O) X 3 |                                    | (UART or clock synchronous serial I/O) X 3                                                       |  |  |  |

| A-D converter                                         |                                    | 10-bit X 1 (8 channels)                                                                          |  |  |  |

| Watchdog timer                                        |                                    | 12-bit X 1                                                                                       |  |  |  |

| Interrupte                                            |                                    | 3 external types, 16 internal types                                                              |  |  |  |

| Interrupts                                            |                                    | Each interrupt can be set to the priority level $(0-7.)$                                         |  |  |  |

| Clock generating circuit                              |                                    | 2 circuits built-in (externally connected to a ceramic resonator or a quartz-crystal oscillator) |  |  |  |

| Supply voltage                                        |                                    | 2.7 – 5.5 V                                                                                      |  |  |  |

| Power dissipation                                     |                                    | 9 mW (at 3 V supply voltage, external clock 12 MHz frequency)                                    |  |  |  |

| Fower dissipation                                     |                                    | 22.5 mW (at 5 V supply voltage, external clock 12 MHz frequency)                                 |  |  |  |

| Input/Output characteristic                           | Input/Output voltage               | 5 V                                                                                              |  |  |  |

| Input/Output Characteristic                           | Output current                     | 5 mA                                                                                             |  |  |  |

| Memory expansion                                      |                                    | Maximum 1 Mbytes                                                                                 |  |  |  |

| Operating temperature range                           |                                    | −40 to 85 °C                                                                                     |  |  |  |

| Device structure                                      |                                    | CMOS high-performance silicon gate process                                                       |  |  |  |

| Package                                               |                                    | 80-pin plastic molded fine-pitch QFP (80P6D-A;0.5 mm lead pitch)                                 |  |  |  |

#### **MITSUBISHI MICROCOMPUTERS**

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

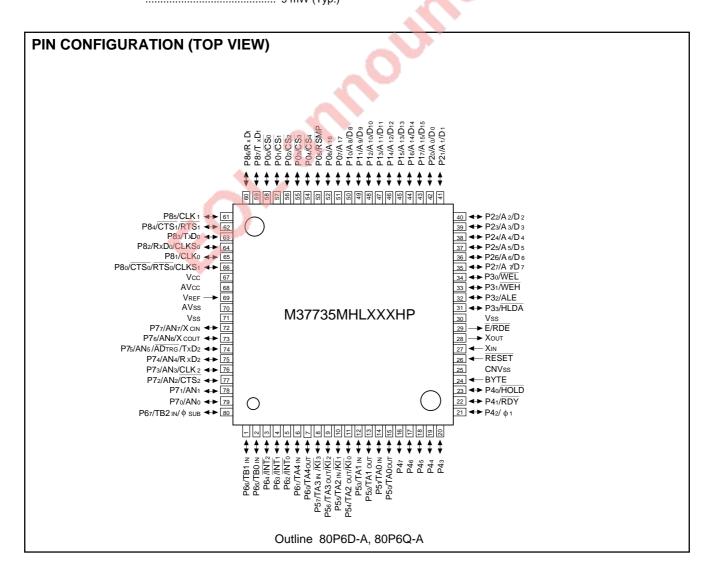

#### **PIN DESCRIPTION**

| Pin                               | Name                                          | Input/Output | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------|-----------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc,                              | Power source                                  |              | Apply 2.7 – 5.5 V to Vcc and 0 V to Vss.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Vss                               |                                               |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CNVss                             | CNVss input                                   | Input        | This pin controls the processor mode. Connect to Vss for the single-chip mode and the memory expansion mode, and to Vcc for the microprocessor mode.                                                                                                                                                                                                                                                                                                       |

| RESET                             | Reset input                                   | Input        | When "L" level is applied to this pin, the microcomputer enters the reset state.                                                                                                                                                                                                                                                                                                                                                                           |

| XIN                               | Clock input                                   | Input        | These are pins of main-clock generating circuit. Connect a ceramic resonator or a quartz-<br>crystal oscillator between XIN and XOUT. When an external clock is used, the clock source should                                                                                                                                                                                                                                                              |

| Хоит                              | Clock output                                  | Output       | be connected to the XIN pin, and the Xo∪⊤ pin should be left open.                                                                                                                                                                                                                                                                                                                                                                                         |

| Ē                                 | Enable output                                 | Output       | In the single-chip mode, this pin functions as the enable signal output pin which indicates the access status in the internal bus.  In the memory expansion mode or the microprocessor mode, this pin functions as the RDE signal output pin.                                                                                                                                                                                                              |

| BYTE                              | External data<br>bus width<br>selection input | Input        | In the memory expansion mode or the microprocessor mode, this pin determines whether the external data bus has an 8-bit width or a 16-bit width. The data bus has a 16-bit width when "L" signal is input and an 8-bit width when "H" signal is input.                                                                                                                                                                                                     |

| AVcc,<br>AVss                     | Analog power source input                     |              | Power source input pin for the A-D converter. Externally connect AVcc to Vcc and AVss to Vss.                                                                                                                                                                                                                                                                                                                                                              |

| VREF                              | Reference voltage input                       | Input        | This is reference voltage input pin for the A-D converter.                                                                                                                                                                                                                                                                                                                                                                                                 |

| P00 – P07                         | I/O port P0                                   | I/O          | In the single-chip mode, port P0 becomes an 8-bit I/O port. An I/O direction register is available so that each pin can be programmed for input or output. These ports are in the input mode when reset.  In the memory expansion mode or the microprocessor mode, these pins output $\overline{CS_0} - \overline{CS_4}$ , $\overline{RSMP}$ signals, and address (A <sub>16</sub> , A <sub>17</sub> ).                                                    |

| P10 – P17                         | I/O port P1                                   | I/O          | In the single-chip mode, these pins have the same functions as port P0. When the BYTE pin is set to "L" in the memory expansion mode or the microprocessor mode and external data bus has a 16-bit width, high-order data (D8 – D15) is input/output or an address (A8 – A15) is output. When the BYTE pin is "H" and an external data bus has an 8-bit width, only address (A8 – A15) is output.                                                          |

| P20 – P27                         | I/O port P2                                   | I/O          | In the single-chip mode, these pins have the same functions as port P0. In the memory expansion mode or the microprocessor mode, low-order data (D <sub>0</sub> – D <sub>7</sub> ) is input/output or an address (A <sub>0</sub> – A <sub>7</sub> ) is output.                                                                                                                                                                                             |

| P30 – P33                         | I/O port P3                                   | I/O          | In the single-chip mode, these pins have the same function as port P0. In the memory expansion mode or the microprocessor mode, WEL, WEH, ALE, and HLDA signals are output.                                                                                                                                                                                                                                                                                |

| P40 – P47                         | I/O port P4                                   | I/O          | In the single-chip mode, these pins have the same functions as port P0. In the memory expansion mode or the microprocessor mode, P40, P41, and P42 become $\overline{\text{HOLD}}$ and $\overline{\text{RDY}}$ input pins, and clock $\phi$ 1 output pin, respectively. Functions of the other pins are the same as in the single-chip mode. However, in the memory expansion mode, P42 also functions as an I/O port.                                     |

| P50 – P57                         | I/O port P5                                   | I/O          | In addition to having the same functions as port P0 in the single-chip mode, these pins also function as I/O pins for timers A0 to A3 and input pins for key input interrupt input (KIo – KI3).                                                                                                                                                                                                                                                            |

| P60 – P67                         | I/O port P6                                   | 1/0          | In addition to having the same functions as port P0 in the single-chip mode, these pins also function as I/O pins for timer A4, input pins for external interrupt input ( $\overline{\text{INT}_0} - \overline{\text{INT}_2}$ ) and input pins for timers B0 to B2. P67 also functions as sub-clock $\phi$ sub output pin.                                                                                                                                 |

| P7 <sub>0</sub> – P7 <sub>7</sub> | I/O port P7                                   | I/O          | In addition to having the same functions as port P0 in the single-chip mode, these pins function as input pins for A-D converter. P72 to P75 also function as I/O pins for UART2. Additionally, P76 and P77 have the function as the output pin (XCOUT) and the input pin (XCIN) of the sub-clock (32 kHz) oscillation circuit, respectively. When P76 and P77 are used as the XCOUT and XCIN pins, connect a resonator or an oscillator between the both. |

| P80 – P87                         | I/O port P8                                   | I/O          | In addition to having the same functions as port P0 in the single-chip mode, these pins also function as I/O pins for UART 0 and UART 1.                                                                                                                                                                                                                                                                                                                   |

#### **BASIC FUNCTION BLOCKS**

The M37735MHLXXXHP has the same functions as the M37735MHBXXXFP except for the package and the reset circuit. Refer to the section on the M37735MHBXXXFP.

#### **RESET CIRCUIT**

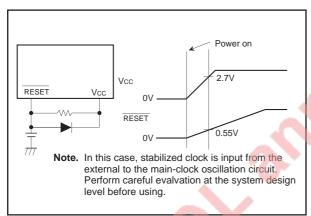

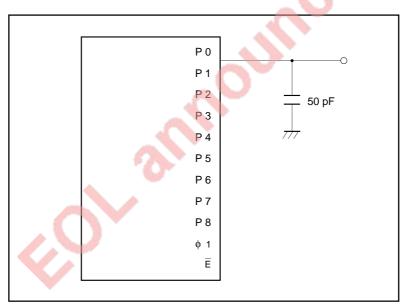

The microcomputer is released from the reset state when the RESET pin is returned to "H" level after holding it at "L" level with the power source voltage at 2.7-5.5 V. Program execution starts at the address formed by setting address  $A_{23}-A_{16}$  to  $00_{16},\,A_{15}-A_8$  to the contents of address FFFF16, and  $A_7-A_0$  to the contents of address FFFE16. Figure 1 shows an example of a reset circuit. When the stabilized clock is input from the external to the main-clock oscillation circuit, the reset input voltage must be  $0.55\,\mathrm{V}$  or less when the power source voltage reaches  $2.7\,\mathrm{V}$ . When a resonator/oscillator is connected to the main-clock oscillation circuit, change the reset input voltage from "L" to "H" after the main-clock oscillation is fully stabilized.

The status of the internal registers during reset is the same as the M37735MHBXXXFP's.

Fig. 1 Example of a reset circuit

#### **ADDRESSING MODES**

The M37735MHLXXXHP has 28 powerful addressing modes. Refer to the "7700 Family Software Manual" for the details.

#### **MACHINE INSTRUCTION LIST**

The M37735MHLXXXHP has 103 machine instructions. Refer to the "7700 Family Software Manual" for the details.

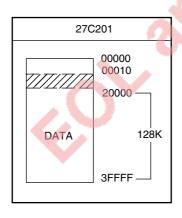

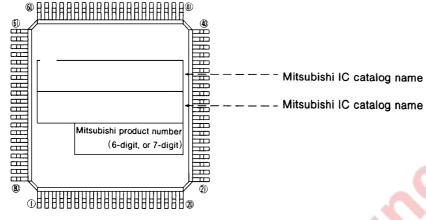

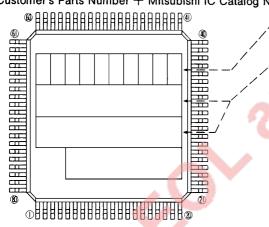

#### DATA REQUIRED FOR MASK ROM ORDERING

Please send the following data for mask orders.

- (1) M37735MHLXXXHP mask ROM order confirmation form

- (2) 80P6D, 80P6Q mark specification form

- (3) ROM data (EPROM 3 sets)

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                                                  | Conditions | Ratings           | Unit |

|--------|------------------------------------------------------------|------------|-------------------|------|

| Vcc    | Power source voltage                                       |            | -0.3 to +7        | V    |

| AVcc   | Analog power source voltage                                |            | −0.3 to +7        | V    |

| Vı     | Input voltage RESET, CNVss, BYTE                           |            | -0.3 to +12       | V    |

|        | Input voltage P00 – P07, P10 – P17, P20 – P27, P30 – P33,  |            |                   |      |

| Vı     | P40 – P47, P50 – P57, P60 – P67, P70 – P77,                |            | -0.3 to Vcc + 0.3 | V    |

|        | P80 – P87, VREF, XIN                                       |            |                   |      |

|        | Output voltage P00 – P07, P10 – P17, P20 – P27, P30 – P33, |            |                   |      |

| Vo     | P40 – P47, P50 – P57, P60 – P67, P70 – P77,                |            | -0.3 to Vcc + 0.3 | V    |

| VO     | P80 – P87, Хоит, <u>Е</u>                                  |            |                   |      |

| Pd     | Power dissipation                                          | Ta = 25 °C | 200               | mW   |

| Topr   | Operating temperature                                      |            | -40 to +85        | °C   |

| Tstg   | Storage temperature                                        |            | -65 to +150       | °C   |

#### RECOMMENDED OPERATING CONDITIONS (Vcc = 2.7 – 5.5 V, Ta = -40 to +85 °C, unless otherwise noted)

| 0         | Description                                                                                                                                  |         | Limits |         |      |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|---------|------|

| Symbol    | Parameter                                                                                                                                    | Min.    | Тур.   | Max.    | Unit |

| \         | f(XIN): Operating                                                                                                                            | 2.7     |        | 5.5     | V    |

| Vcc       | Power source voltage f(XIN) : Stopped, f(XCIN) = 32.768 kHz                                                                                  | 2.7     |        | 5.5     |      |

| AVcc      | Analog power source voltage                                                                                                                  |         | Vcc    |         | V    |

| Vss       | Power source voltage                                                                                                                         |         | 0      |         | V    |

| AVss      | Analog power source voltage                                                                                                                  |         | 0      |         | V    |

| VIH       | High-level input voltage P00 – P07, P30 – P33, P40 – P47, P50 – P57, P60 – P67, P70 – P77, P80 – P87, XIN, RESET, CNVss, BYTE, XCIN (Note 3) | 0.8 Vcc |        | Vcc     | V    |

| ViH       | High-level input voltage P10 – P17, P20 – P27 (in single-chip mode)                                                                          | 0.8 Vcc |        | Vcc     | V    |

| VIH       | High-level input voltage P10 – P17, P20 – P27 (in memory expansion mode and microprocessor mode)                                             | 0.5 Vcc |        | Vcc     | V    |

| VIL       | Low-level input voltage P00 – P07, P30 – P33, P40 – P47, P50 – P57, P60 – P67, P70 – P77, P80 – P87, XIN, RESET, CNVss, BYTE, XCIN (Note 3)  | 0       |        | 0.2Vcc  | V    |

| VIL       | Low-level input voltage P10 – P17, P20 – P27 (in single-chip mode)                                                                           | 0       |        | 0.2Vcc  | V    |

| VIL       | Low-level input voltage P10 – P17, P20 – P27 (in memory expansion mode and microprocessor mode)                                              | 0       |        | 0.16Vcc | V    |

| IOH(peak) | High-level peak output current P00 – P07, P10– P17, P20 – P27, P30 – P33, P40 – P47, P50 – P57, P60 – P67, P70 – P77, P80 – P87              |         |        | -10     | mA   |

| IOH(avg)  | High-level average output current P00 – P07, P10 – P17, P20 – P27, P30 – P33, P40 – P47, P50 – P57, P60 – P67, P70 – P77, P80 – P87          |         |        | -5      | mA   |

| IOL(peak) | Low-level peak output current P00 – P07, P10 – P17, P20 – P27, P30 – P33, P40 – P43, P54 – P57, P60 – P67, P70 – P77, P80 – P87              |         |        | 10      | mA   |

| IOL(peak) | Low-level peak output current P44 – P47, P50 – P53                                                                                           |         |        | 16      | mA   |

| IOL(avg)  | Low-level average output current P00 – P07, P10 – P17, P20 – P27, P30 – P33, P40 – P43, P54 – P57, P60 – P67, P70 – P77, P80 – P87           |         |        | 5       | mA   |

| lOL(avg)  | Low-level average output current P44 – P47, P50 – P53                                                                                        |         |        | 12      | mA   |

| f(XIN)    | Main-clock oscillation frequency (Note 4)                                                                                                    |         |        | 12      | MHz  |

| f(Xcin)   | Sub-clock oscillation frequency                                                                                                              |         | 32.768 | 50      | kHz  |

$\textbf{Notes 1.} \ \ \text{Average output current is the average value of a 100 ms interval.}$

- 2. The sum of IoL(peak) for ports P0, P1, P2, P3, and P8 must be 80 mA or less, the sum of IoH(peak) for ports P0, P1, P2, P3, and P8 must be 80 mA or less, the sum of IoL(peak) for ports P4, P5, P6, and P7 must be 100 mA or less, and the sum of IoH(peak) for ports P4, P5, P6, and P7 must be 80 mA or less.

- 3. Limits VIH and VIL for XCIN are applied when the sub clock external input selection bit = "1".

- **4.** The maximum value of f(XIN) = 6 MHz when the main clock division selection bit = "1".

#### **ELECTRICAL CHARACTERISTICS** (Vcc = 5 V, Vss = 0 V, Ta = -40 to +85 °C, f(XIN) = 12 MHz, unless otherwise noted)

| 0             | Description                                                                                                   | Table of Comp                               |             | Limits |       |      |  |

|---------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------|--------|-------|------|--|

| Symbol        | Parameter                                                                                                     | Test conditions                             | Min.        | Тур.   | Max.  | Unit |  |

| Vон           | High-level output voltage P00 – P07, P10 – P17, P20 – P27, P33, P40 – P47, P50 – P57, P60 – P67, P70 – P77,   | Vcc = 5 V, IOH = -10 mA                     | 3           |        |       | V    |  |

| VOH           | P80 – P87                                                                                                     | Vcc = 3 V, IOH = -1 mA                      | 2.5         |        |       | ] V  |  |

| Voн           | High-level output voltage P00 – P07, P10 – P17, P20 – P27, P33                                                | Vcc = 5 V, loн = -400 μ/                    | 4.7         |        |       | V    |  |

|               |                                                                                                               | Vcc = 5 V, loн = -10 mA                     | 3.1         |        |       |      |  |

| Vон           | High-level output voltage P30 – P32                                                                           | $Vcc = 5 \text{ V, IoH} = -400 \mu\text{/}$ | 4.8         |        |       | V    |  |

|               |                                                                                                               | Vcc = 3 V, loн = -1 mA                      | 2.6         |        |       |      |  |

|               |                                                                                                               | Vcc = 5 V, loн = -10 mA                     | 3.4         |        |       |      |  |

| Voн           | High-level output voltage E                                                                                   | $Vcc = 5 \text{ V, IoH} = -400 \mu$         |             |        |       | V    |  |

|               |                                                                                                               | Vcc = 3 V, loн = -1 mA                      | 2.6         |        |       |      |  |

| Vol           | Low-level output voltage P00 – P07, P10 – P17, P20 – P27, P33,<br>P40 – P43, P54 – P57, P60 – P67, P70 – P77, | Vcc = 5 V, loL = 10 mA                      |             |        | 2     | V    |  |

|               | P80 – P87                                                                                                     | Vcc = 3 V, loL = 1 mA                       |             |        | 0.5   | ,    |  |

| Vol           | Low-level output voltage P44 – P47, P50 – P53                                                                 | Vcc = 5 V, loL = 16 mA                      | A Parket    |        | 1.8   | V    |  |

|               |                                                                                                               | Vcc = 3 V, loL = 10 mA                      |             |        | 1.5   | ·    |  |

| Vol           | Low-level output voltage P00 – P07, P10 – P17, P20 – P27, P33                                                 | Vcc = 5 V, $IoL = 2 mA$                     | ( ) ) James |        | 0.45  | V    |  |

|               |                                                                                                               | Vcc = 5  V,  IoL = 10  mA                   | 1           |        | 1.9   | _    |  |

| Vol           | Low-level output voltage P30 – P32                                                                            | Vcc = 5 V, $IoL = 2 mA$                     | 4           |        | 0.43  | V    |  |

|               |                                                                                                               | Vcc = 3 V, IoL = 1 mA                       |             |        | 0.4   |      |  |

| Vol           |                                                                                                               | Vcc = 5  V,  lol = 10  mA                   |             |        | 1.6   | ١.,  |  |

|               | Low-level output voltage E                                                                                    | Vcc = 5 V, $IoL = 2 mA$                     |             |        | 0.4   | V    |  |

|               | Hysteresis HOLD, RDY, TA0IN – TA4IN, TB0IN – TB2IN,                                                           | VCC = 3  V,  IOL = 1  mA                    |             |        | 0.4   |      |  |

| VT+ – VT–     | INTo – INT2, ADTRG, CTS0, CTS1, CTS2, CLK0,                                                                   | Vcc = 5 V                                   | 0.4         |        | 1     | V    |  |

| VI+ - VI-     | CLK1, CLK2, $\overline{\text{Kl}_0} - \overline{\text{Kl}_3}$                                                 | Vcc = 3 V                                   | 0.1         |        | 0.7   | ] V  |  |

| VT+ – VT–     | Hysteresis RESET                                                                                              | Vcc = 5 V                                   | 0.2         |        | 0.5   | V    |  |

| VI+ - VI-     | Trysteresis Reser                                                                                             | Vcc = 3 V                                   | 0.1         |        | 0.4   | , v  |  |

| VT+ – VT–     | Hysteresis XIN                                                                                                | Vcc = 5 V                                   | 0.1         |        | 0.4   | V    |  |

| V I + - V I - | Trysteresis Ain                                                                                               | Vcc = 3 V                                   | 0.06        |        | 0.26  | , v  |  |

| VT+ - VT-     | Hysteresis Xcın (When external clock is input)                                                                | Vcc = 5 V                                   | 0.1         |        | 0.4   | V    |  |

| V 1 + V 1 -   | , , , , , , , , , , , , , , , , , , , ,                                                                       | Vcc = 3 V                                   | 0.06        |        | 0.26  |      |  |

|               | High-level input current P00 – P07, P10 – P17, P20 – P27, P30 – P33,                                          | Vcc = 5 V, Vi = 5 V                         | '           |        | 5     |      |  |

| Іін           | P40 – P47, P50 – P57, P60 – P67, P70 – P77,<br>P80 – P87, XIN, RESET, CNVss, BYTE                             | Vcc = 3 V, Vı = 3 V                         | ,           |        | 4     | μΑ   |  |

|               | Low-level input current P00 – P07, P10 – P17, P20 – P27, P30 – P33,                                           | Vcc = 5 V, VI = 0 V                         | ,           |        | -5    |      |  |

| lıL           | P40 – P47, P50 – P53, P60, P61, P65 – P67,<br>P70 – P77, P80 – P87, XIN, RESET, CNVss, BYTE                   | Vcc = 3 V, Vı = 0 V                         | ,           |        | -4    | μΑ   |  |

|               | Low-level input current P54 – P57, P62 – P64                                                                  | VI = 0 V, Vcc = 5                           | V           |        | -5    |      |  |

| lıL           |                                                                                                               | without a pull-up transistor Vcc = 3        | V           |        | -4    | μΑ   |  |

| IIL           |                                                                                                               | VI = 0 V,                                   | V -0.25     | -0.5   | -1.0  | 0    |  |

|               |                                                                                                               | with a pull-up transistor Vcc = 3           | V -0.08     | -0.18  | -0.35 | mA   |  |

| VRAM          | RAM hold voltage                                                                                              | When clock is stopped                       | . 2         |        |       | V    |  |

#### **ELECTRICAL CHARACTERISTICS** (Vcc = 5 V, Vss = 0 V, Ta = -40 to +85 °C, unless otherwise noted)

| Symbol Parameter Test conditions |                | Test conditions                                                                    | Limits                                                                                                                                                                                                                            |      |      | Unit |       |

|----------------------------------|----------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                                  | · arameter     |                                                                                    |                                                                                                                                                                                                                                   | Min. | Тур. | Max. | Offic |

|                                  |                |                                                                                    | Vcc = 5 V,<br>f(XIN) = 12 MHz (square waveform),<br>(f(f2) = 6 MHz),<br>f(XCIN) = 32.768 kHz,<br>in operating (Note 1)                                                                                                            |      | 4.5  | 9    | mA    |

|                                  |                |                                                                                    | Vcc = 3 V,<br>f(XIN) = 12 MHz (square waveform),<br>(f(f2) = 6 MHz),<br>f(XCIN) = 32.768 kHz,<br>in operating (Note 1)                                                                                                            |      | 3    | 6    | mA    |

|                                  | Power source n | When single-chip mode, output pins are open, and                                   | Vcc = 3 V,<br>f(XIN) = 12 MHz (square waveform),<br>(f(f2) = 0.75 MHz),<br>f(XCIN) : Stopped,<br>in operating                                                                                                                     |      | 0.4  | 0.8  | mA    |

|                                  |                | .   f(   f(   w     v   v   f(   f(   f(   v   v   v   v   v   v   v   v   f(   f( | $\label{eq:continuous} \begin{array}{l} \text{Vcc} = 3 \text{ V}, \\ \text{f(XIN)} = 12 \text{ MHz (square waveform)}, \\ \text{f(XCIN)} = 32.768 \text{ kHz}, \\ \text{when a WIT instruction is executed (Note 2)} \end{array}$ | 5    | 6    | 12   | μА    |

|                                  |                |                                                                                    | Vcc = 3 V,<br>f(XIN) : Stopped,<br>f(XCIN) = 32.768 kHz,<br>in operating (Note 3)                                                                                                                                                 |      | 30   | 60   | μА    |

|                                  |                |                                                                                    |                                                                                                                                                                                                                                   | 3    | 6    | μА   |       |

|                                  |                |                                                                                    | Ta = 25 °C,<br>when clock is stopped                                                                                                                                                                                              |      |      | 1    | μА    |

|                                  |                |                                                                                    | Ta = 85 °C,<br>when clock is stopped                                                                                                                                                                                              |      |      | 20   | μΑ    |

Notes 1. This applies when the main clock external input selection bit = "1", the main clock division selection bit = "0", and the signal output stop bit = "1".

- 2. This applies when the main clock external input selection bit = "1" and the system clock stop bit at wait state = "1".

- 3. This applies when CPU and the clock timer are operating with the sub clock (32.768 kHz) selected as the system clock.

- 4. This applies when the Xcout drivability selection bit = "0" and the system clock stop bit at wait state = "1".

#### **A-D CONVERTER CHARACTERISTICS**

(Vcc = AVcc = 5 V, Vss = AVss = 0 V, Ta = -40 to +85 °C, f(XIN) = 12 MHz, unless otherwise noted (Note))

| Symbol  | Parameter            | Test conditions |      | Unit |      |       |

|---------|----------------------|-----------------|------|------|------|-------|

| Cymbol  | 1 didifictor         | rest conditions | Min. | Тур. | Max. | Offic |

| _       | Resolution           | VREF = VCC      |      |      | 10   | Bits  |

| _       | Absolute accuracy    | VREF = VCC      |      |      | ± 3  | LSB   |

| RLADDER | Ladder resistance    | VREF = VCC      | 10   |      | 25   | kΩ    |

| tconv   | Conversion time      |                 | 19.6 |      |      | μs    |

| VREF    | Reference voltage    |                 | 2.7  |      | Vcc  | V     |

| VIA     | Analog input voltage |                 | 0    |      | VREF | V     |

**Note.** This applies when the main clock division selection bit = "0" and  $f(f_2) = 6$  MHz.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

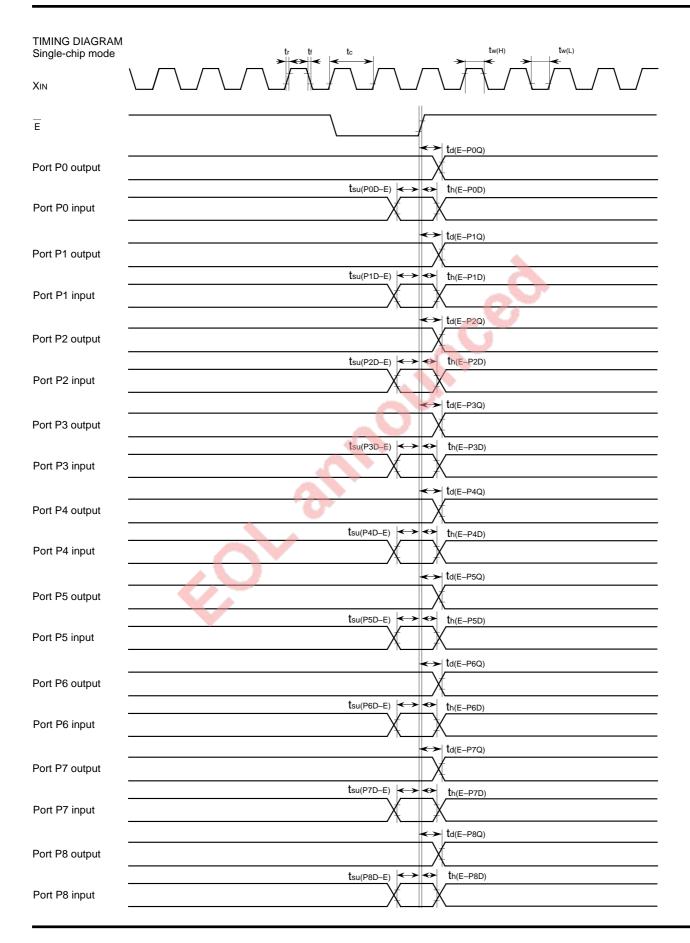

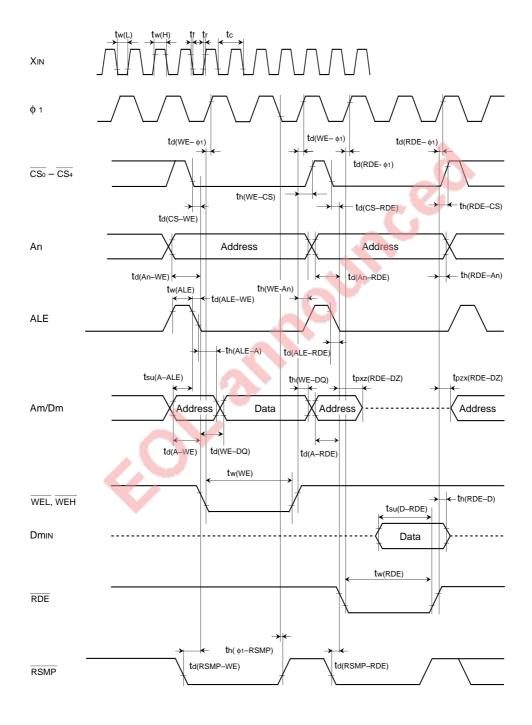

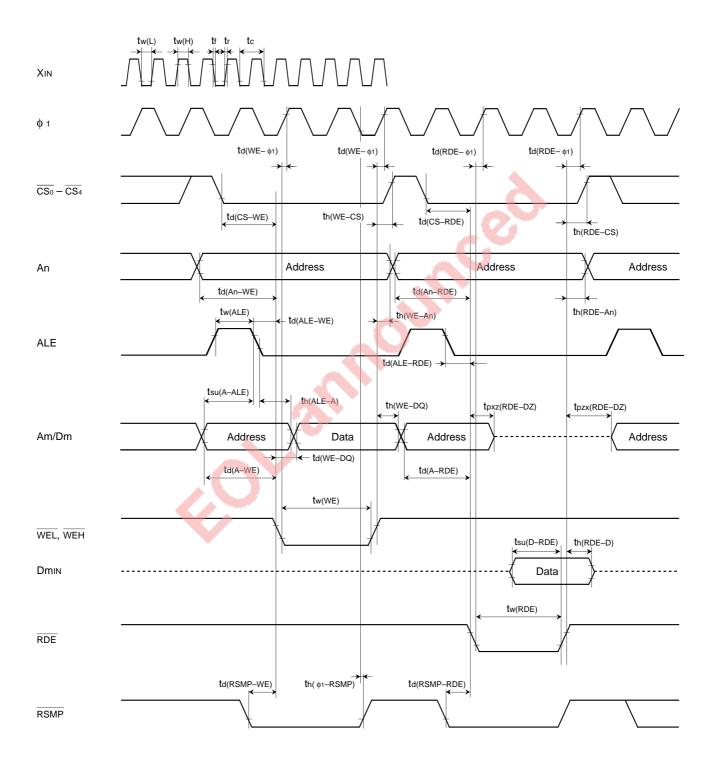

$\textbf{TIMING REQUIREMENTS} \text{ (Vcc = } 2.7-5.5 \text{ V, Vss = } 0 \text{ V, Ta = } -40 \text{ to } +85 \text{ °C, } \\ \text{f(XIN) = } 12 \text{ MHz, unless otherwise noted (Note 1))}$

**Notes 1.** This applies when the main clock division selection bit = "0" and  $f(f_2) = 6$  MHz.

2. Input signal's rise/fall time must be 100 ns or less, unless otherwise noted.

#### **External clock input**

| Symbol | Parameter                                            |      | Limits |      |  |

|--------|------------------------------------------------------|------|--------|------|--|

| Cymbol | i didifficio                                         | Min. | Max.   | Unit |  |

| tc     | External clock input cycle time (Note 1)             | 83   |        | ns   |  |

| tw(H)  | External clock input high-level pulse width (Note 2) | 33   |        | ns   |  |

| tw(L)  | External clock input low-level pulse width (Note 2)  | 33   |        | ns   |  |

| tr     | External clock rise time                             |      | 15     | ns   |  |

| tf     | External clock fall time                             |      | 15     | ns   |  |

**Notes 1.** When the main clock division selection bit = "1", the minimum value of  $t_c$  = 166 ns.

2. When the main clock division selection bit = "1", values of tw(H) / tc and tw(L) / tc must be set to values from 0.45 through 0.55.

#### Single-chip mode

| Symbol     | Parameter                |      | Limits |      |

|------------|--------------------------|------|--------|------|

| Cyrribor   | T dramotor               | Min. | Max.   | Unit |

| tsu(P0D-E) | Port P0 input setup time | 200  |        | ns   |

| tsu(P1D-E) | Port P1 input setup time | 200  |        | ns   |

| tsu(P2D-E) | Port P2 input setup time | 200  |        | ns   |

| tsu(P3D-E) | Port P3 input setup time | 200  |        | ns   |

| tsu(P4D-E) | Port P4 input setup time | 200  |        | ns   |

| tsu(P5D-E) | Port P5 input setup time | 200  |        | ns   |

| tsu(P6D-E) | Port P6 input setup time | 200  |        | ns   |

| tsu(P7D-E) | Port P7 input setup time | 200  |        | ns   |

| tsu(P8D-E) | Port P8 input setup time | 200  |        | ns   |

| th(E-P0D)  | Port P0 input hold time  | 0    |        | ns   |

| th(E-P1D)  | Port P1 input hold time  | 0    |        | ns   |

| th(E-P2D)  | Port P2 input hold time  | 0    |        | ns   |

| th(E-P3D)  | Port P3 input hold time  | 0    |        | ns   |

| th(E-P4D)  | Port P4 input hold time  | 0    |        | ns   |

| th(E-P5D)  | Port P5 input hold time  | 0    |        | ns   |

| th(E-P6D)  | Port P6 input hold time  | 0    |        | ns   |

| th(E-P7D)  | Port P7 input hold time  | 0    |        | ns   |

| th(E-P8D)  | Port P8 input hold time  | 0    |        | ns   |

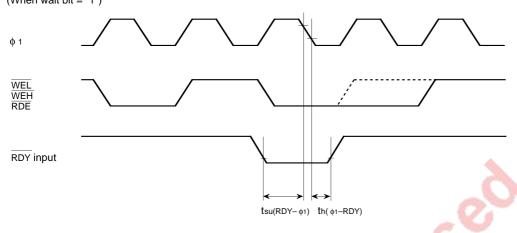

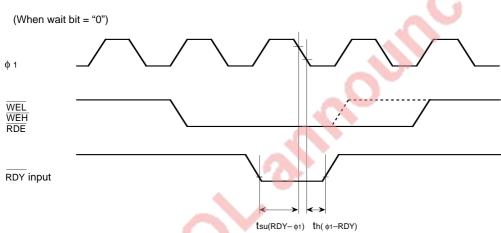

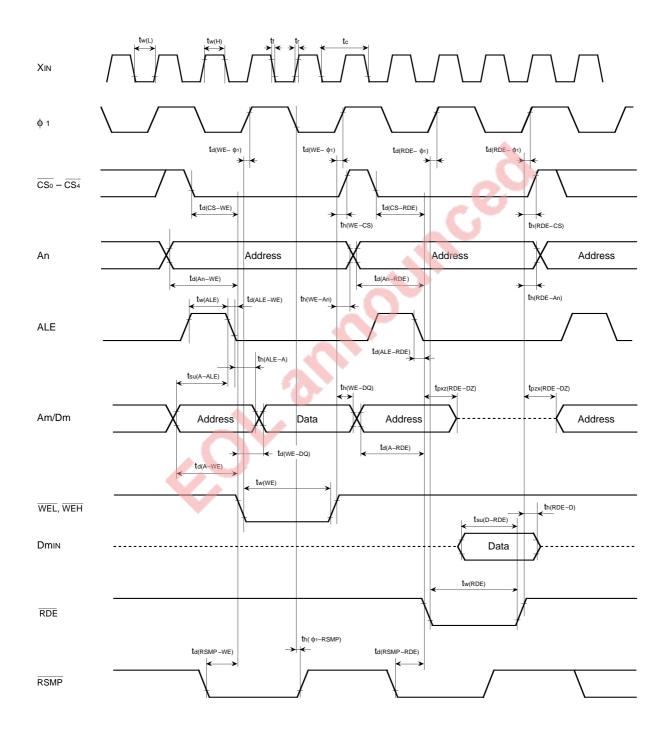

#### Memory expansion mode and microprocessor mode

| Symbol             | Parameter             | Lir  | Unit |       |

|--------------------|-----------------------|------|------|-------|

| Oymbor             | 1 drameter            | Min. | Max. | Offic |

| tsu(D-RDE)         | Data input setup time | 50   |      | ns    |

| tsu(RDY−           | RDY input setup time  | 80   |      | ns    |

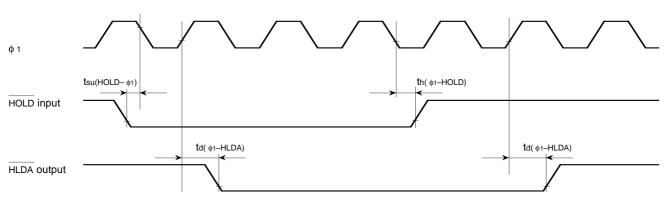

| tsu(HOLD−          | HOLD input setup time | 80   |      | ns    |

| th(RDE-D)          | Data input hold time  | 0    |      | ns    |

| th( φ 1-RDY)       | RDY input hold time   | 0    |      | ns    |

| th( $\phi$ 1-HOLD) | HOLD input hold time  | 0    |      | ns    |

#### SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

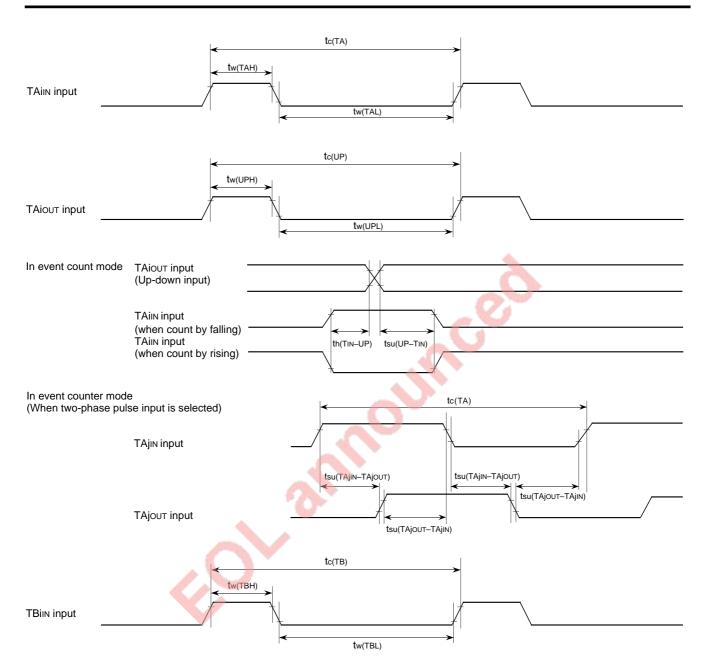

#### Timer A input (Count input in event counter mode)

| Symbol  | Parameter                         | Lir  | Linit |      |

|---------|-----------------------------------|------|-------|------|

|         |                                   | Min. | Max.  | Unit |

| tc(TA)  | TAin input cycle time             | 250  |       | ns   |

| tw(TAH) | TAin input high-level pulse width | 125  |       | ns   |

| tw(TAL) | TAil input low-level pulse width  | 125  |       | ns   |

#### Timer A input (Gating input in timer mode)

| Symbol  | Parameter                                 | Lir  | Linit |      |

|---------|-------------------------------------------|------|-------|------|

|         |                                           | Min. | Max.  | Unit |

| tc(TA)  | TAin input cycle time (Note)              | 666  |       | ns   |

| tw(TAH) | TAiın input high-level pulse width (Note) | 333  |       | ns   |

| tw(TAL) | TAiın input low-level pulse width (Note)  | 333  |       | ns   |

Note. Limits change depending on f(XIN). Refer to "DATA FORMULAS".

#### **Timer A input** (External trigger input in one-shot pulse mode)

| Symbol  | Parameter                         |   |     | Limits     |      | Unit |       |

|---------|-----------------------------------|---|-----|------------|------|------|-------|

| Symbol  | Tarameter                         |   |     | A STATE OF | Min. | Max. | Offic |

| tc(TA)  | TAin input cycle time (Note)      |   | W   | 9          | 666  |      | ns    |

| tw(TAH) | TAil input high-level pulse width | - | AA. |            | 166  |      | ns    |

| tw(TAL) | TAin input low-level pulse width  |   | 2   |            | 166  |      | ns    |

Note. Limits change depending on f(XIN). Refer to "DATA FORMULAS".

#### Timer A input (External trigger input in pulse width modulation mode)

| Symbol  | Parameter                         | Li   | Limits |      |  |

|---------|-----------------------------------|------|--------|------|--|

|         |                                   | Min. | Max.   | Unit |  |

| tw(TAH) | TAil input high-level pulse width | 166  |        | ns   |  |

| tw(TAL) | TAil input low-level pulse width  | 166  |        | ns   |  |

#### Timer A input (Up-down input in event counter mode)

| Symbol      | Parameter                           | Lir       | Unit |      |       |

|-------------|-------------------------------------|-----------|------|------|-------|

|             | i didificiei                        | Falametel | Min. | Max. | UIIII |

| tc(UP)      | TAiout input cycle time             |           | 3333 |      | ns    |

| tw(UPH)     | TAiout input high-level pulse width |           | 1666 |      | ns    |

| tw(UPL)     | TAiout input low-level pulse width  |           | 1666 |      | ns    |

| tsu(UP-Tin) | TAiout input setup time             |           | 666  |      | ns    |

| th(TIN-UP)  | TAiou⊤ input hold time              |           | 666  |      | ns    |

#### Timer A input (Two-phase pulse input in event counter mode)

| Symbol            | Parameter               | Lir  | Unit |       |

|-------------------|-------------------------|------|------|-------|

|                   |                         | Min. | Max. | Offic |

| tc(TA)            | TAjın input cycle time  | 2000 |      | ns    |

| tsu(ТАjın-ТАjоuт) | TAjın input setup time  | 500  |      | ns    |

| tsu(ТАјоит-ТАјім) | TAjout input setup time | 500  |      | ns    |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

#### Timer B input (Count input in event counter mode)

| Symbol  | Parameter                                             | Lir  | Linit |      |

|---------|-------------------------------------------------------|------|-------|------|

|         |                                                       | Min. | Max.  | Unit |

| tc(TB)  | TBiin input cycle time (one edge count)               | 250  |       | ns   |

| tw(TBH) | TBin input high-level pulse width (one edge count)    | 125  |       | ns   |

| tw(TBL) | TBiin input low-level pulse width (one edge count)    | 125  |       | ns   |

| tc(TB)  | TBiin input cycle time (both edges count)             | 500  |       | ns   |

| tw(TBH) | TBiin input high-level pulse width (both edges count) | 250  |       | ns   |

| tw(TBL) | TBin input low-level pulse width (both edges count)   | 250  |       | ns   |

#### Timer B input (Pulse period measurement mode)

| Symbol  | Parameter                                |      | Limits |      |  |

|---------|------------------------------------------|------|--------|------|--|

|         | raidilletei                              | Min. | Max.   | Unit |  |

| tc(TB)  | TBin input cycle time (Note)             | 666  |        | ns   |  |

| tw(TBH) | TBin input high-level pulse width (Note) | 333  |        | ns   |  |

| tw(TBL) | TBiin input low-level pulse width (Note) | 333  |        | ns   |  |

Note. Limits change depending on f(XIN). Refer to "DATA FORMULAS".

#### Timer B input (Pulse width measurement mode)

| Symbol  | Parameter                                | Lir  | Unit |      |

|---------|------------------------------------------|------|------|------|

|         | i arameter                               | Min. | Max. | Unit |

| tc(TB)  | TBin input cycle time (Note)             | 666  |      | ns   |

| tw(TBH) | TBin input high-level pulse width (Note) | 333  |      | ns   |

| tw(TBL) | TBin input low-level pulse width (Note)  | 333  |      | ns   |

Note. Limits change depending on f(XIN). Refer to "DATA FORMULAS".

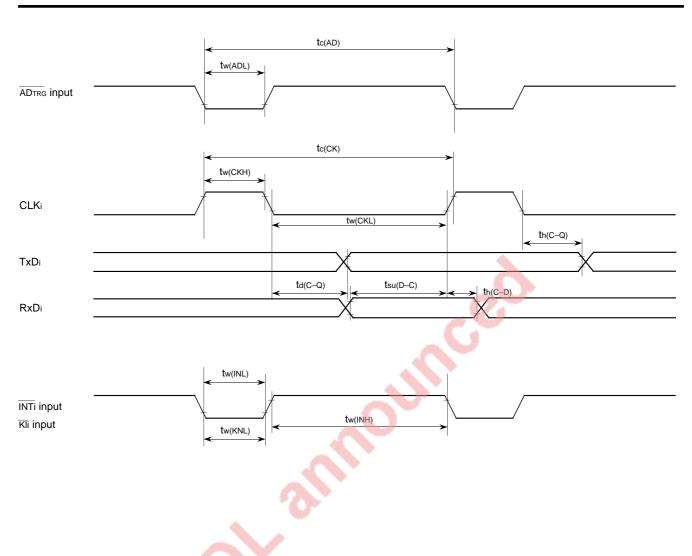

#### **A-D trigger input**

| Symbol  | Parameter                                          | Lir  | Unit |      |

|---------|----------------------------------------------------|------|------|------|

|         |                                                    | Min. | Max. | Unit |

| tc(AD)  | ADTRG input cycle time (minimum allowable trigger) | 1333 |      | ns   |

| tw(ADL) | ADTRG input low-level pulse width                  | 166  |      | ns   |

#### Serial I/O

| Symbol   | Parameter                         | Lir  | Unit |       |

|----------|-----------------------------------|------|------|-------|

| Cymbol   |                                   | Min. | Max. | Offic |

| tc(CK)   | CLKi input cycle time             | 333  |      | ns    |

| tw(CKH)  | CLKi input high-level pulse width | 166  |      | ns    |

| tw(CKL)  | CLKi input low-level pulse width  | 166  |      | ns    |

| td(C-Q)  | TxDi output delay time            |      | 100  | ns    |

| th(C-Q)  | TxDi hold time                    | 0    |      | ns    |

| tsu(D-C) | RxDi input setup time             | 65   |      | ns    |

| th(C-D)  | RxDi input hold time              | 75   |      | ns    |

#### External interrupt INTi input, key input interrupt Kli input

| Symbol  | Parameter                         | Lir  | Unit |       |

|---------|-----------------------------------|------|------|-------|

|         |                                   | Min. | Max. | Offic |

| tw(INH) | INTi input high-level pulse width | 250  |      | ns    |

| tw(INL) | INTi input low-level pulse width  | 250  |      | ns    |

| tw(KIL) | Kli input low-level pulse width   | 250  |      | ns    |

#### **DATA FORMULAS**

#### Timer A input (Gating input in timer mode)

| Symbol  | Parameter                          | Limits                                        |       | Unit |

|---------|------------------------------------|-----------------------------------------------|-------|------|

| Cymbol  | i diameter                         | Min.                                          | Ullit |      |

| tc(TA)  | TAil input cycle time              | 8 X 10 <sup>9</sup><br>2 · f(f <sub>2</sub> ) |       | ns   |

| tw(TAH) | TAilN input high-level pulse width | $\frac{4 \times 10^9}{2 \cdot f(f_2)}$        |       | ns   |

| tw(TAL) | TAiın input low-level pulse width  | $\frac{4 \times 10^9}{2 \cdot f(f_2)}$        |       | ns   |

#### Timer A input (External trigger input in one-shot pulse mode)

| Symbol | Parameter             | Limits                                 | Linit |              |

|--------|-----------------------|----------------------------------------|-------|--------------|

| Cymbol | 1 drameter            | Min.                                   | Max.  | - Unit<br>ns |

| tc(TA) | TAil input cycle time | $\frac{8 \times 10^9}{2 \cdot f(f_2)}$ |       | ns           |

#### Timer B input (In pulse period measurement mode or pulse width measurement mode)

| Symbol  | Parameter                          | Limits                                        |      | Unit  |

|---------|------------------------------------|-----------------------------------------------|------|-------|

| Cymbol  | Talamotor                          | Min.                                          | Max. | Offic |

| tc(TB)  | TBiin input cycle time             | $\frac{8 \times 10^9}{2 \cdot f(f_2)}$        |      | ns    |

| tw(TBH) | ТВіім input high-level pulse width | 4 X 10 <sup>9</sup><br>2 · f(f <sub>2</sub> ) |      | ns    |

| tw(TBL) | TBiin input low-level pulse width  | $\frac{4 \times 10^9}{2 \cdot f(f_2)}$        |      | ns    |

Note. f(f2) represents the clock f2 frequency.

For the relation to the main clock and sub clock, refer to Table 10 in data sheet "M37735MHBXXXFP".

#### **SWITCHING CHARACTERISTICS**

$(Vcc = 2.7 - 5.5 \text{ V}, Vss = 0 \text{ V}, Ta = -40 \text{ to } +85^{\circ}\text{C}, f(Xin) = 12 \text{ MHz}, unless otherwise noted (Note))}$

#### Single-chip mode

| Symbol    | Parameter                      | Test conditions | Lir  | Unit |      |

|-----------|--------------------------------|-----------------|------|------|------|

| Symbol    | i didiffetei                   | rest conditions | Min. | Max. | Unit |

| td(E-P0Q) | Port P0 data output delay time |                 |      | 300  | ns   |

| td(E-P1Q) | Port P1 data output delay time |                 |      | 300  | ns   |

| td(E-P2Q) | Port P2 data output delay time |                 |      | 300  | ns   |

| td(E-P3Q) | Port P3 data output delay time |                 |      | 300  | ns   |

| td(E-P4Q) | Port P4 data output delay time | Fig. 2          |      | 300  | ns   |

| td(E-P5Q) | Port P5 data output delay time |                 |      | 300  | ns   |

| td(E-P6Q) | Port P6 data output delay time |                 |      | 300  | ns   |

| td(E-P7Q) | Port P7 data output delay time |                 |      | 300  | ns   |

| td(E-P8Q) | Port P8 data output delay time |                 |      | 300  | ns   |

Note. This applies when the main clock division selection bit = "0" and  $f(f_2) = 6$  MHz.

Fig. 2 Measuring circuit for ports P0 – P8 and  $\varphi$  1

#### Memory expansion mode and microprocessor mode

$(Vcc = 2.7 - 5.5 \text{ V}, Vss = 0 \text{ V}, Ta = -40 \text{ to } +85 ^{\circ}C, f(XIN) = 12 \text{ MHz}, unless otherwise noted (Note 1))}$

| Symbol                      | Parameter                      | (Note 2)         | Test          | Limits |      | Llait    |

|-----------------------------|--------------------------------|------------------|---------------|--------|------|----------|

| Symbol                      | i diametei                     | Wait modé        | conditions    | Min.   | Max. | Unit     |

| td(CS-WE)                   | Ohio a chart autout delevetice | No wait          |               | 20     |      | ns       |

| td(CS-RDE)                  | Chip-select output delay time  | Wait 1           |               |        |      |          |

| th(WE-CS)                   |                                | Wait 0           |               | 182    |      | ns       |

| th(RDE-CS)                  | Chip-select hold time          |                  |               | 4      |      | ns       |

| td(An–WE)                   |                                | No wait          |               | 20     |      | ns       |

| td(An–RDE)                  | Address output delay time      | Wait 1           |               |        |      |          |

| ,                           |                                | Wait 0           |               | 182    |      | ns       |

| td(A-WE)                    | Address subsub delevities      | No wait          |               | 20     |      | ns       |

| td(A-RDE)                   | Address output delay time      | Wait 1<br>Wait 0 |               | 162    |      | ns       |

| th(WE-An)                   |                                | wait 0           |               |        |      | 113      |

| th(RDE-An)                  | Address hold time              |                  |               | 40     |      | ns       |

|                             |                                | No wait          |               | 40     |      | ns       |

| tw(ALE)                     | ALE pulse width                | Wait 1           | ALL PROPERTY. | _      |      | 110      |

|                             |                                | Wait 0           | <b>1</b> 5    | 123    |      | ns       |

| tou(A ALE)                  | Address sutput setup time      | No wait          | Fig. 2        | 10     |      | ns       |

| tsu(A-ALE)                  | Address output setup time      | Wait 1<br>Wait 0 |               | 93     |      | no       |

|                             |                                | No wait          |               | 93     |      | ns       |

| th(ALE-A)                   | Address hold time              | Wait 1           |               | 9      |      | ns       |

| ,                           | Tradition from the second      | Wait 0           |               | 40     |      | ns       |

| _                           |                                | No wait          |               | 4      |      |          |

| td(ALE-WE)                  | ALE output delay time          | Wait 1           |               | 4      |      | ns       |

| td(ALE-RDE)                 |                                | Wait 0           |               | 40     |      | ns       |

| td(WE-DQ)                   | Data output delay time         | •                |               |        | 90   | ns       |

| th(WE-DQ)                   | Data hold time                 |                  |               | 40     |      | ns       |

|                             |                                | No wait          |               | 131    |      | ns       |

| tw(WE)                      | WEL/WEH pulse width            | Wait 1           |               | 298    |      | ns       |

| tpxz(RDE-DZ)                | Flooting stort deleviting      | Wait 0           |               |        | 10   |          |

| tpzx(RDE-DZ)                | Floating start delay time      |                  |               | 53     | 10   | ns<br>ns |

| tpzx(NDL=DZ)                | Floating release delay time    | No wait          |               | 128    |      | ns       |

| tw(RDE)                     | RDE pulse width                | Wait 1           |               |        |      | 113      |

|                             | TOE Puloe Width                | Wait 0           |               | 295    |      | ns       |

| td(RSMP-WE)                 |                                |                  |               | 0.5    |      |          |

| td(RSMP-RDE)                | RSMP output delay time         |                  |               | 25     |      | ns       |

| th( \$ 1-RSMP)              | RSMP hold time                 |                  |               | 0      |      | ns       |

| td(WE- φ 1)<br>td(RDE- φ 1) | φ 1 output delay time          |                  |               | 0      | 30   | ns       |

| td( φ 1–HLDA)               | HLDA output delay time         |                  |               |        | 120  | ns       |

**Notes 1.** This applies when the main clock division selection bit = "0" and  $f(f_2) = 6$  MHz.

**2.** No wait : Wait bit = "1".

Wait 1: The external memory area is accessed with wait bit = "0" and wait selection bit = "1".

Wait 0: The external memory area is accessed with wait bit = "0" and wait selection bit = "0".

#### Bus timing data formulas (Vcc = 2.7 – 5.5V, Vss = 0 V, Ta = -40 to +85 °C, f(XIN) = 12 MHz (Max.), unless otherwise noted (Note1))

|                |                               |           | Limits                                        |      |      |

|----------------|-------------------------------|-----------|-----------------------------------------------|------|------|

| Symbol         | Parameter                     | Wait mode | Min.                                          | Max. | Unit |

|                |                               | No wait   | 1 X 10 <sup>9</sup>                           |      |      |

| td(CS-WE)      | Chin coloct output delay time |           | $\frac{1}{2 \cdot f(f_2)} - 63$               |      | ns   |

| td(CS-RDE)     | Chip-select output delay time | 144 14 0  | 3 × 10 <sup>9</sup>                           |      |      |

|                |                               | Wait 0    | $\frac{3 \times 10}{2 \cdot f(f_2)} - 68$     |      | ns   |

| th(WE-CS)      | Chip-select hold time         |           | 4                                             |      | nc   |

| th(RDE-CS)     | Chip-select hold time         |           |                                               |      | ns   |

|                |                               | No wait   | $\frac{1 \times 10^9}{1000} - 63$             |      | ns   |

| td(An–WE)      | Address output delay time     | Wait 1    | 2 · f(f2)                                     |      |      |

| td(An–RDE)     |                               | Wait 0    | $\frac{3 \times 10^9}{2 \times 10^9} - 68$    |      | ns   |

|                |                               | No wait   | 2 · f(f <sub>2</sub> )                        |      |      |

| td(A-WE)       |                               | Wait 1    | $\frac{1 \times 10^9}{2 \cdot f(f_2)} - 63$   |      | ns   |

| td(A-WE)       | Address output delay time     |           | 3 ¥ 109                                       |      |      |

| 14(71.11.22)   |                               | Wait 0    | $\frac{3 \times 10}{2 \cdot f(f_2)} - 88$     |      | ns   |

| th(WE-An)      |                               | 1         | 1 🗸 109                                       |      |      |

| th(RDE-An)     | Address hold time             |           | $\frac{12 \cdot f(f_2)}{2 \cdot f(f_2)} - 43$ |      | ns   |

|                |                               | No wait   | 1 X 10 <sup>9</sup> - 43                      |      | no   |

| tw(ALE)        | ALE pulse width               | Wait 1    | 2 · f(f <sub>2</sub> )                        |      | ns   |

|                | 7.12 passo main               | Wait 0    | $\frac{2 \times 10^9}{1000} - 43$             |      | ns   |

|                |                               |           | 2 · f(f2)                                     |      |      |

|                |                               | No wait   | $\frac{1 \times 10^9}{200} - 73$              |      | ns   |

| tsu(A-ALE)     | Address output setup time     | Wait 1    | 2 · f(f <sub>2</sub> )                        |      |      |

|                |                               | Wait 0    | $\frac{2 \times 10^9}{2 \cdot f(f_2)} - 73$   |      | ns   |

|                |                               | No wait   | 2 1(12)                                       |      |      |

|                |                               | Wait 1    | 9                                             |      | ns   |

| th(ALE-A)      | Address hold time             |           | 1 X 10 <sup>9</sup>                           |      |      |

|                |                               | Wait 0    | $\frac{1}{2 \cdot f(f_2)} - 43$               |      | ns   |

|                |                               | No wait   | 4                                             |      |      |

| td(ALE-WE)     | ALE output delay time         | Wait 1    | 4                                             |      | ns   |

| td(ALE-RDE)    |                               | Wait 0    | $\frac{1 \times 10^9}{1000} - 43$             |      | ns   |

|                |                               | Wait 0    | 2 · f(f2)                                     |      | 110  |

| td(WE-DQ)      | Data output delay time        |           |                                               | 90   | ns   |

| th(WE-DQ)      | Data hold time                |           | $\frac{1 \times 10^9}{2 \times 10^9} - 43$    |      | ns   |

|                |                               | 1         | 2 · f(f <sub>2</sub> ) - 43                   |      |      |

|                |                               | No wait   | $\frac{2 \times 10^9}{2 \cdot f(f_2)} - 35$   |      | ns   |

| tw(WE)         | WEL/WEH pulse width           | Wait 1    | 4 ¥ 109                                       |      |      |

|                |                               | Wait 0    | $\frac{7 \times 10}{2 \cdot f(f_2)} - 35$     |      | ns   |

| tpxz(RDE-DZ)   | Floating start delay time     | 1,,,,,,,  |                                               | 10   | ns   |

|                |                               |           | $\frac{1 \times 10^9}{3 \cdot f(f_0)} - 30$   | 1    |      |

| tpzx(RDE-DZ)   | Floating release delay time   |           | ${2 \cdot f(f_2)} = 30$                       |      | ns   |

|                |                               | Noeit     | 2 X 10 <sup>9</sup> - 38                      |      | nc   |

| tw(RDE)        | RDE pulse width               | No wait   | 2 · f(f <sub>2</sub> )                        |      | ns   |

| (1.02)         | TOE PAIGO WIGHT               | Wait 1    | 4 X 10 <sup>9</sup> - 38                      |      | ns   |

| _              |                               | Wait 0    | 2 • f(f2)                                     |      |      |

| td(RSMP-WE)    | RSMP output delay time        |           | $\frac{1 \times 10^9}{2 \times 10^9} - 58$    |      | ns   |

| td(RSMP-RDE)   |                               |           | 2 · f(f2)                                     |      |      |

| th( \$ 1-RSMP) | RSMP hold time                |           | 0                                             |      | ns   |