# RENESAS

# RAA489800

Bidirectional Buck-Boost Voltage Regulator

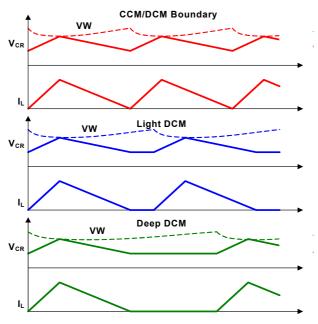

The <u>RAA489800</u> is a bidirectional, buck-boost voltage regulator that provides buck-boost voltage regulation and protection features. The advanced Renesas R3<sup>™</sup> Technology provides high light-load efficiency, fast transient response, and seamless DCM/CCM transitions.

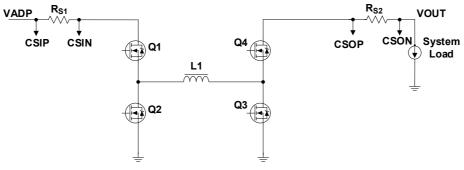

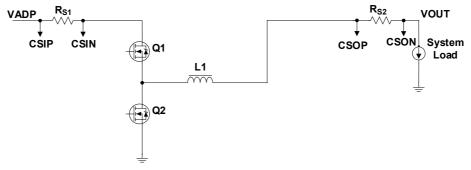

The RAA489800 takes input power from a wide range of DC power sources up to 23V (such as conventional AC/DC adapters (ADP), USB PD ports, travel ADP) and safely converts it to a regulated voltage up to 21V. The RAA489800 can also convert a wide range DC power source connected at its output (system side) to a regulated voltage to its input (ADP side). This bidirectional buck-boost regulation feature makes the RAA489800's application very flexible. In addition to 4-switch buck-boost configuration, it can also support 2-switch Buck mode operation.

The RAA489800 includes various system operation functions such as the Forward mode enable pin, Reverse mode enable pin, programmable soft-start time, and adjustable forward and reverse  $V_{OUT}$ . It also has forward and reverse power-good indicators. The protection functionalities include OCP, OVP, UVP, and OTP.

The RAA489800 has serial communication through SMBus/I<sup>2</sup>C that allows programming of many critical parameters to deliver a customized solution. These programming parameters include, but are not limited to: output current limit, input current limit, and output voltage setting.

### Features

- Bidirectional buck, boost, and buck-boost operation

- Configurable for 4-switch buck-boost or 2-switch buck operation

- Input voltage range: 3.8V to 23V (no dead zone)

- Output voltage: up to 21V

- Up to 1MHz switching frequency

- Pin programmable soft-start time

- LDO output for VDD and VDDP

- System FAULT status ALERT function

- Input/output internal discharge function

- · Active switching for negative voltage transitions

- Pass Through mode in both directions

- Forward and Reverse mode enable pins

- OCP, OVP, UVP, and OTP protection

- Absolute overvoltage protection

- SMBus and auto-increment I<sup>2</sup>C compatible

- Pb-free (RoHS compliant)

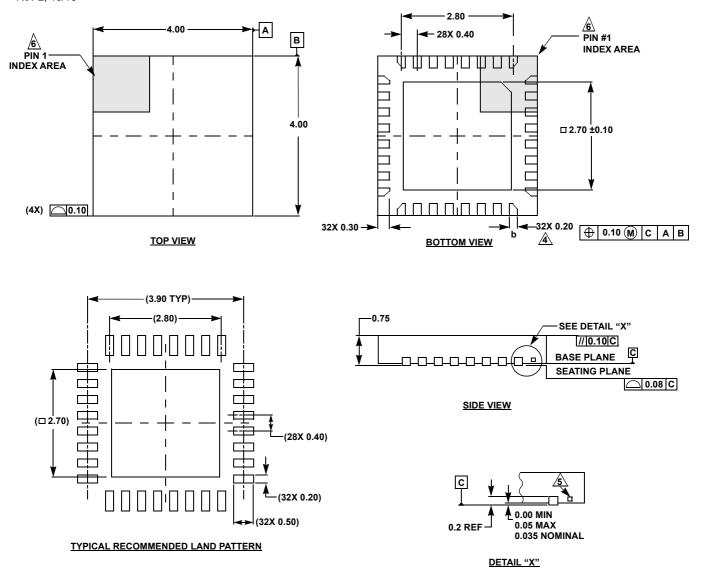

- 32 Ld 4x4 TQFN package

- UL 2367, IEC 62368-1: File No. E520109

#### Applications

• Tablets, Ultrabooks, power banks, mobile devices, and USB-C

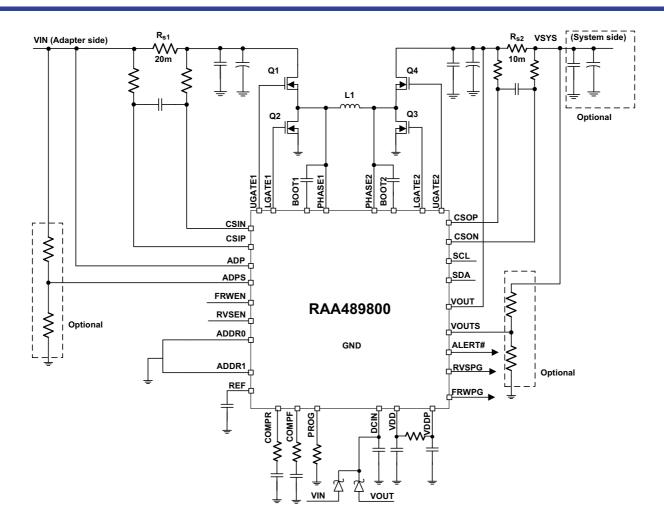

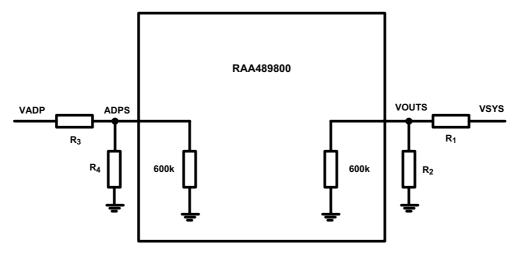

Figure 1. Typical Application Circuit in 4-Switch Buck-Boost Configuration

# Contents

| 1.   | Overview                                                                                       | 5    |

|------|------------------------------------------------------------------------------------------------|------|

| 1.1  | Simplified Application Circuit                                                                 | 5    |

| 1.2  | Block Diagram                                                                                  | 6    |

| 1.3  | Ordering Information                                                                           | 7    |

| 1.4  | Pin Configuration                                                                              | 7    |

| 1.5  | Pin Descriptions                                                                               | 8    |

| 2.   | Specifications                                                                                 | . 10 |

| 2.1  | Absolute Maximum Ratings                                                                       |      |

| 2.2  | Thermal Information.                                                                           |      |

| 2.2  | Recommended Operation Conditions                                                               |      |

| 2.3  | Electrical Specifications                                                                      |      |

| 2.4  | SMBus Timing Specification                                                                     |      |

|      |                                                                                                |      |

| 3.   | Typical Performance Curves                                                                     |      |

| 4.   | General SMBus Architecture                                                                     |      |

| 4.1  | Data Validity                                                                                  | . 19 |

| 4.2  | START and STOP Conditions                                                                      | . 19 |

| 4.3  | Acknowledge                                                                                    | . 20 |

| 4.4  | SMBus Transactions                                                                             | . 20 |

| 4.5  | Byte Format                                                                                    | . 20 |

| 4.6  | SMBus and I <sup>2</sup> C Compatibility                                                       | . 20 |

| 5.   | RAA489800 SMBus Commands                                                                       | . 21 |

| 5.1  | Setting System Side Current Limit                                                              | . 22 |

| 5.2  | Setting Input Current Limit in Forward Mode                                                    |      |

| 5.3  | Setting System Regulating Voltage in Forward Mode                                              |      |

| 5.4  | ALERT# FAULT Interrupt Behavior                                                                | . 25 |

| 5.5  | Setting ALERT# Debounce Time                                                                   | . 26 |

| 5.6  | Control Registers                                                                              | . 26 |

| 5.7  | Regulating Voltage Register in Reverse Mode                                                    | . 30 |

| 5.8  | Output Current Limit Register in Reverse Mode                                                  | . 31 |

| 5.9  | Input Voltage Limit Register.                                                                  |      |

| 5.10 |                                                                                                |      |

| 6.   | Application Information                                                                        | . 34 |

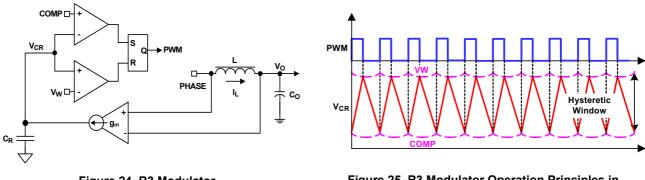

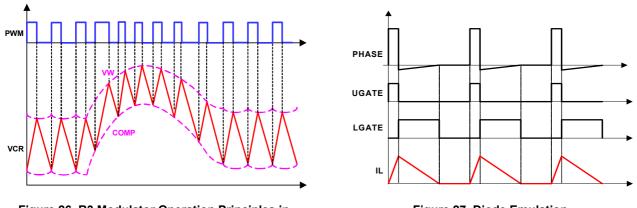

| 6.1  | R3 Modulator                                                                                   |      |

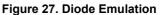

| 6.2  | 4-Switch Bidirectional Buck-Boost Voltage Regulator and 2-Switch Buck Regulator Configurations |      |

| 6.3  | Pass Through Mode.                                                                             |      |

| 6.4  | Soft-Start                                                                                     |      |

| 6.5  | Programming Options                                                                            |      |

| 6.6  |                                                                                                |      |

| 6.7  | Forward Mode                                                                                   |      |

| 6.8  | Reverse Mode for USB OTG (On-The-Go)                                                           |      |

| 6.9  | Overcurrent Warning                                                                            |      |

| 6.10 | -                                                                                              |      |

| 6.11 | -                                                                                              |      |

| 6.12 |                                                                                                |      |

| 0.12 |                                                                                                |      |

#### RAA489800

| 6.13 | 3 Fast Swap                                       | 1  |

|------|---------------------------------------------------|----|

| 6.14 | Way Overcurrent Protection (WOCP) 4               | 1  |

| 6.15 | ADP Input Overvoltage Protection 4                | -2 |

| 6.16 | S System Output Overvoltage Protection 4          | 2  |

| 6.17 | System Output Undervoltage Protection 4           | 2  |

| 6.18 | ADP Output Overvoltage Protection 4               | -2 |

| 6.19 | ADP Output Undervoltage Protection 4              | 2  |

| 6.20 | Over-Temperature Protection                       | -2 |

| 6.21 | Switching Power MOSFET Gate Capacitance           | -2 |

| 6.22 | ADP Side Input Filter                             | 3  |

| 7.   | General Application Information 4                 | 4  |

| 7.1  | Selecting the LC Output Filter                    | 4  |

| 7.2  | Selecting the Input Capacitor                     | -5 |

| 7.3  | Selecting the Switching Power MOSFET 4            | -5 |

| 7.4  | Selecting the Bootstrap Capacitor                 | 6  |

| 7.5  | Selecting the Resistor Divider for VOUTS and ADPS | 7  |

| 7.6  | Selecting the DCIN Filter                         | 7  |

| 8.   | Layout                                            | 8  |

| 9.   | Revision History                                  | 60 |

| 10.  | Package Outline Drawing                           | 51 |

### 1. Overview

### 1.1 Simplified Application Circuit

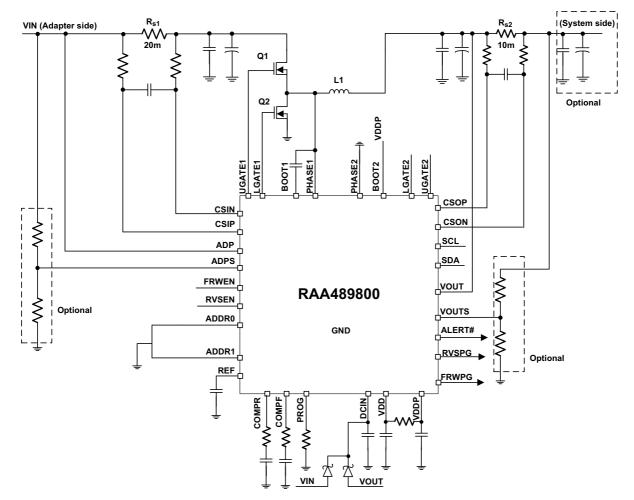

Figure 2. Typical Application Diagram in 2-Switch Buck Configuration

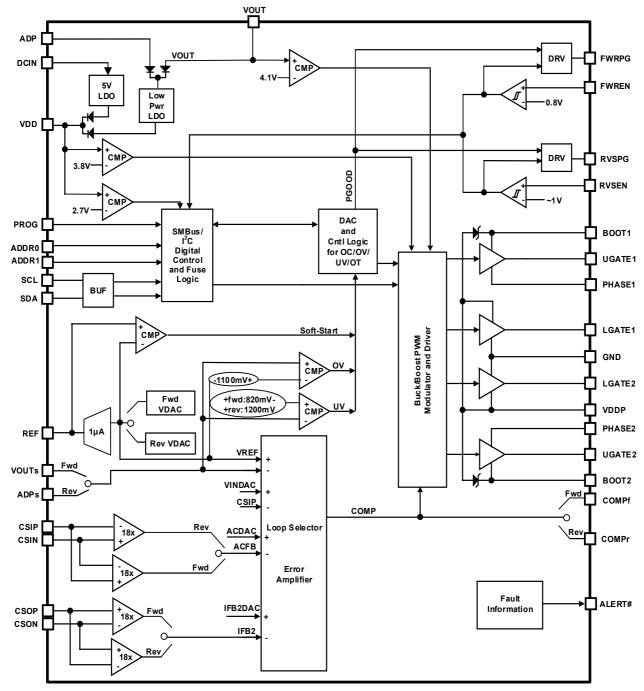

### 1.2 Block Diagram

Figure 3. Block Diagram

### 1.3 Ordering Information

| Part Number<br>( <u>Notes 2</u> , <u>3</u> ) | Part Marking     | Package Description<br>(RoHS Compliant) | Pkg.<br>Dwg. # | Carrier Type<br>( <u>Note 1</u> ) | Temp. Range   |

|----------------------------------------------|------------------|-----------------------------------------|----------------|-----------------------------------|---------------|

| RAA489800ARGNP#AA0                           | 489800           | 32 Ld 4x4 TQFN                          | L32.4x4D       | Tube                              | -10 to +100°C |

| RAA489800ARGNP#HA0                           | ARGNPA           |                                         |                | Reel, 6k                          |               |

| RAA489800A2GNP#AA0                           | 489800           |                                         |                | Tube                              | -40 to +85°C  |

| RAA489800A2GNP#HA0                           | A2GNPA           |                                         |                | Reel, 6k                          |               |

| RTKA489800DE0000BU                           | Evaluation board |                                         |                | •                                 |               |

Notes:

1. See <u>TB347</u> for details about reel specifications.

These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

3. The Moisture Sensitivity Level (MSL) rating is 3. For more information about MSL, see TB363.

Table 1. Key Differences Between Family of Parts

| Part<br>Number | Absolute<br>Overvoltage<br>Protection | Buck-Boost<br>Efficiency<br>Improvement | Pin #23<br>Function | Input/<br>Output<br>Current<br>PROCHOT# | CC/CV<br>Loop<br>ALERT# | 2-FET<br>Buck<br>Only<br>Mode | Forced<br>Buck-Boost<br>and Boost<br>Mode | VSYS Low<br>Shutdown<br>Feature | Default Input<br>Current<br>Limit Setting<br>Trough<br>PROG pin |

|----------------|---------------------------------------|-----------------------------------------|---------------------|-----------------------------------------|-------------------------|-------------------------------|-------------------------------------------|---------------------------------|-----------------------------------------------------------------|

| RAA489800      | Yes                                   | 5%                                      | ALERT#              | No                                      | Yes                     | Yes                           | No                                        | Yes                             | Yes                                                             |

| RAA489801      | Yes                                   | 5%                                      | PROCHOT#            | Yes                                     | No                      | Yes                           | Yes                                       | No                              | Yes                                                             |

| ISL95338       | No                                    | N/A                                     | PROCHOT#            | Yes                                     | No                      | No                            | Yes                                       | No                              | No                                                              |

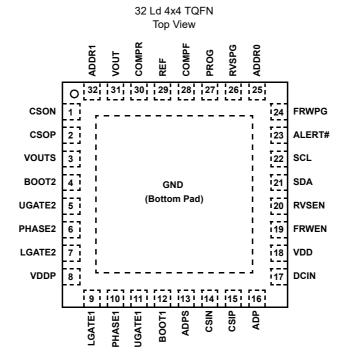

#### 1.4 Pin Configuration

# 1.5 Pin Descriptions

| Pin Number | Pin Name                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                               |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bottom Pad | Pad         GND         Signal common to the IC. Unless otherwise stated, signals are referenced to the GND pin. GNI           be used as the thermal pad for heat dissipation.         Signal common to the IC. Unless otherwise stated, signals are referenced to the GND pin. GNI |                                                                                                                                                                                                                                                                                                                                           |  |

| 1          | CSON                                                                                                                                                                                                                                                                                 | Forward V <sub>OUT</sub> current sense negative input. Connect to the VOUT current resistor negative input. Place a 0.1µF ceramic capacitor between CSOP and CSON to provide differential mode filtering.                                                                                                                                 |  |

| 2          | CSOP                                                                                                                                                                                                                                                                                 | Forward V <sub>OUT</sub> current sense positive input. Connect to the VOUT current resistor positive input. Place a 0.1µF ceramic capacitor between CSOP and CSON to provide differential mode filtering.                                                                                                                                 |  |

| 3          | VOUTS                                                                                                                                                                                                                                                                                | Forward VSYS feedback voltage. Use an optional resistor divider externally to configure forward VSYS voltage.                                                                                                                                                                                                                             |  |

| 4          | BOOT2                                                                                                                                                                                                                                                                                | High-side MOSFET Q4 gate driver supply. Connect an MLCC capacitor across the BOOT2 pin and the PHASE2 pin. The boot capacitor is charged through an internal boot diode connected from the VDDP pin to the BOOT2 pin when the PHASE2 pin drops below VDDP minus the voltage drop across the internal boot diode.                          |  |

| 5          | UGATE2                                                                                                                                                                                                                                                                               | High-side MOSFET Q4 gate drive.                                                                                                                                                                                                                                                                                                           |  |

| 6          | PHASE2                                                                                                                                                                                                                                                                               | Current return path for the high-side MOSFET Q4 gate drive. Connect this pin to the node consisting of the high-side MOSFET Q4 source, the low-side MOSFET Q3 drain, and the inductor output terminal.                                                                                                                                    |  |

| 7          | LGATE2                                                                                                                                                                                                                                                                               | Low-side MOSFET Q3 gate drive.                                                                                                                                                                                                                                                                                                            |  |

| 8          | VDDP                                                                                                                                                                                                                                                                                 | Power supply to the gate drivers. Connect to the VDD pin through a $4.7\Omega$ resistor and connect a $2.2\mu$ F ceramic capacitor to GND. The effective capacitance at 5V must be at least $0.4\mu$ F after derating.                                                                                                                    |  |

| 9          | LGATE1                                                                                                                                                                                                                                                                               | Low-side MOSFET Q2 gate drive.                                                                                                                                                                                                                                                                                                            |  |

| 10         | PHASE1                                                                                                                                                                                                                                                                               | Current return path for the high-side MOSFET Q1 gate drive. Connect this pin to the node consisting of the high-side MOSFET Q1 source, the low-side MOSFET Q2 drain, and the input terminal of the inductor.                                                                                                                              |  |

| 11         | UGATE1                                                                                                                                                                                                                                                                               | High-side MOSFET Q1 gate drive.                                                                                                                                                                                                                                                                                                           |  |

| 12         | BOOT1                                                                                                                                                                                                                                                                                | High-side MOSFET Q1 gate driver supply. Connect an MLCC capacitor across the BOOT1 pin and the PHASE1 pin. The boot capacitor is charged through an internal boot diode connected from the VDDP pin to the BOOT1 pin when the PHASE1 pin drops below VDDP minus the voltage drop across the internal boot diode.                          |  |

| 13         | ADPS                                                                                                                                                                                                                                                                                 | Reverse output voltage feedback. Use a resistor divider externally to configure the reverse output voltage.                                                                                                                                                                                                                               |  |

| 14         | CSIN                                                                                                                                                                                                                                                                                 | ADP current sense negative input.                                                                                                                                                                                                                                                                                                         |  |

| 15         | CSIP                                                                                                                                                                                                                                                                                 | ADP current sense positive input. The modulator also uses this for sensing input voltage in Forward mode and output voltage in Reverse mode.                                                                                                                                                                                              |  |

| 16         | ADP                                                                                                                                                                                                                                                                                  | Senses ADP voltage. Forward mode can be enabled when the ADP voltage is higher than 4.1V.<br>The ADP pin is also one of the two internal low power LDO inputs.                                                                                                                                                                            |  |

| 17         | DCIN                                                                                                                                                                                                                                                                                 | Internal LDO input providing power to the IC. Connect a diode OR from the ADP and system outputs. Connect a $4.7\mu$ F ceramic capacitor to GND. The effective capacitance at 20V must be at least $0.4\mu$ F after derating.                                                                                                             |  |

| 18         | VDD                                                                                                                                                                                                                                                                                  | Internal LDO output that provides the bias power for the internal analog and digital circuit. Connect a 2.2 $\mu$ F ceramic capacitor to GND. The effective capacitance at 5V must be at least 0.4 $\mu$ F after derating. If V <sub>DD</sub> is pulled below 2.7V, the RAA489800 resets all the SMBus registers to their default values. |  |

| 19         | FRWEN                                                                                                                                                                                                                                                                                | Forward mode enable, analog signal input. Forward mode is valid if the FRWEN pin voltage is greater than 0.6V.                                                                                                                                                                                                                            |  |

| 20         | RVSEN                                                                                                                                                                                                                                                                                | Reverse mode enable, digital signal input. Reverse mode is valid if the signal is "1" (logic high), otherwise, Reverse mode is disabled.                                                                                                                                                                                                  |  |

| 21         | SDA                                                                                                                                                                                                                                                                                  | SMBus data I/O. Connect to the data line from the host controller. Connect a 10k pull-up resistor according to the SMBus specification.                                                                                                                                                                                                   |  |

| 22         | SCL                                                                                                                                                                                                                                                                                  | SMBus clock I/O. Connect to the clock line from the host controller. Connect a 10k pull-up resistor according to the SMBus specification.                                                                                                                                                                                                 |  |

| 23         | ALERT#                                                                                                                                                                                                                                                                               | Open-drain output. If WOC, OV, UV, OTP, or ADPOV faults are detected, ALERT# is pulled low. Clear ALERT# with Control4<1>. If ALERT# is asserted, <u>Table 9 on page 26</u> shows which fault information bits are set. Configure ALERT# behavior with Control2<10:9>, Control4<7>, and Control4<1>.                                      |  |

| 24         | FRWPG                                                                                                                                                                                                                                                                                | Open-drain output. Indicator output to indicate the forward modulator is enabled and in regulation.                                                                                                                                                                                                                                       |  |

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                     |  |  |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 25         | ADDR0    | Address setting pin for the IC. The IC address is set by the ADDR0 and ADDR1 logic voltage levels.                                                                                                                                                                                                                                              |  |  |

| 26         | RVSPG    | Open-drain output. Indicator output to indicate the reverse modulator is enabled and in regulation.                                                                                                                                                                                                                                             |  |  |

| 27         | PROG     | A resistor from the PROG pin to GND sets the default forward system output voltage.                                                                                                                                                                                                                                                             |  |  |

| 28         | COMPF    | Forward mode error amplifier output. Connect a compensation network externally from COMPF to GND.                                                                                                                                                                                                                                               |  |  |

| 29         | REF      | Output voltage soft-start reference. It also sets the slew rate for output voltage changes. A ceramic capacitor from REF to GND is set to the desired soft-start time. The forward output voltage (VOUTS) reference soft-start time is set in Forward mode. The reverse output voltage (ADPS) reference soft-start time is set in Reverse mode. |  |  |

| 30         | COMPR    | Reverse mode error amplifier output. Connect a compensation network externally from COMPR to GND.                                                                                                                                                                                                                                               |  |  |

| 31         | VOUT     | Forward V <sub>OUT</sub> sense voltage for modulator and PHASE 2 zero-current comparator.                                                                                                                                                                                                                                                       |  |  |

| 32         | ADDR1    | Address setting pin for the IC. The IC address is set by the ADDR0 and ADDR1 logic voltage levels.                                                                                                                                                                                                                                              |  |  |

# 2. Specifications

### 2.1 Absolute Maximum Ratings

| Parameter                                       | Minimum         | Maximum      | Unit |  |

|-------------------------------------------------|-----------------|--------------|------|--|

| CSIP, CSIN, ADPS, ADP, DCIN                     | -0.3            | +28          | V    |  |

| CSIP                                            | -0.3            | ADP + 2      | V    |  |

| PHASE1                                          | GND - 0.3       | +28          | V    |  |

| PHASE1                                          | GND - 2 (<20ns) | +28          | V    |  |

| UGATE1                                          | PHASE1 - 0.3    | BOOT1 + 0.3  | V    |  |

| PHASE2                                          | GND - 0.3       | +28          | V    |  |

| PHASE2                                          | GND - 2 (<20ns) | +28          | V    |  |

| UGATE2                                          | PHASE2 - 0.3    | BOOT2 + 0.3  | V    |  |

| LGATE1, LGATE2                                  | GND - 0.3       | VDDP + 0.3   | V    |  |

| LGATE1, LGATE2                                  | GND - 2 (<20ns) | VDDP + 0.3   | V    |  |

| VOUT, VOUTS, CSOP, CSON                         | -0.3            | +24          | V    |  |

| VDD, VDDP                                       | -0.3            | +6.5         | V    |  |

| BOOT1                                           | GND - 0.3       | PHASE1 + 6.5 | V    |  |

| BOOT2                                           | GND - 0.3       | PHASE2 + 6.5 | V    |  |

| BOOT1 - PHASE1, BOOT2 - PHASE2                  | -0.3            | +6.5         | V    |  |

| COMPR, COMPF, REF, PROG                         | -0.3            | VDD + 0.3    | V    |  |

| RVSEN, FRWEN, ADDR0, ADDR1                      | -0.3            | +6.5         | V    |  |

| FRWPG, ALERT#, RVSPG                            | -0.3            | +6.5         | V    |  |

| SCL, SDA                                        | -0.3            | +6.5         | V    |  |

| CSIP-CSIN, CSOP-CSON                            | -0.3            | +0.3         | V    |  |

| RVSEN, FRWEN, SDA, SCL, FRWPG, RVSPG, ALERT#    |                 | 2            | mA   |  |

| ESD Rating                                      |                 | Rating       |      |  |

| Human Body Model (Tested per JS-001-2017)       |                 | 2            |      |  |

| Charged Device Model (Tested per JS-002-2014)   |                 | 750          |      |  |

| Latch-Up (Tested per JESD78E; Class 2, Level A) |                 | mA           |      |  |

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

### 2.2 Thermal Information

| Thermal Resistance (Typical)                     | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|--------------------------------------------------|------------------------|------------------------|

| 32 Ld TQFN Package ( <u>Notes 4</u> , <u>5</u> ) | 37                     | 2                      |

Notes:

4. θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See <u>TB379</u>.

5. For  $\theta_{JC},$  the case temperature location is the center of the ceramic on the package underside.

| Parameter                                    | Minimum | Maximum          | Unit |

|----------------------------------------------|---------|------------------|------|

| Junction Temperature Range (T <sub>J</sub> ) | -10     | +125             | °C   |

| Storage Temperature Range (T <sub>S</sub> )  | -65     | +150             | °C   |

| Pb-Free Reflow Profile                       |         | See <u>TB493</u> | •    |

### 2.3 Recommended Operation Conditions

| Parameter                      | Minimum | Maximum | Unit |

|--------------------------------|---------|---------|------|

| ADP Input Voltage              | 4       | 23      | V    |

| V <sub>OUT</sub> Input Voltage | 4       | 21      | V    |

### 2.4 Electrical Specifications

Operating conditions: ADP = CSIP = CSIN = 20V, VOUTS = VOUT = CSOP = CSON = 8V, unless otherwise noted. Boldface limits apply across the ambient temperature range, -40°C to +100°C unless otherwise specified.

| Parameter                                                 | Symbol          | Test Conditions                                                            | Min<br>( <u>Note 6</u> ) | Тур   | Max<br>( <u>Note 6</u> ) | Unit |

|-----------------------------------------------------------|-----------------|----------------------------------------------------------------------------|--------------------------|-------|--------------------------|------|

| UVLO/ACOK                                                 | ł               |                                                                            | ļ                        | ļ     | 1                        | 1    |

| VADP UVLO Rising                                          | VADP_UVLO_r     |                                                                            | 3.9                      | 4.2   | 4.55                     | V    |

| VADP UVLO Hysteresis                                      | VADP_UVLO_h     |                                                                            |                          | 530   |                          | mV   |

| V <sub>OUT</sub> UVLO Rising                              | VOUT_UVLO_r     |                                                                            | 3.9                      | 4.2   | 4.55                     | V    |

| V <sub>OUT</sub> UVLO Hysteresis                          | VOUT_UVLO_h     |                                                                            |                          | 300   |                          | mV   |

| VDDA 2P7 Rising, SMBus Active (Note 7)                    | VDD_2P7_r       |                                                                            | 2.5                      | 2.7   | 2.9                      | V    |

| VDDA 2P7 POR Hysteresis<br>( <u>Note 7</u> )              | VDD_2P7_h       |                                                                            |                          | 150   |                          | mV   |

| VDDA 3P8 POR Rising, Modulator,<br>and Gate Driver Active | VDD_3P8_r       |                                                                            | 3.6                      | 3.8   | 3.9                      | V    |

| V <sub>DD</sub> 3P8 Hysteresis                            | VDD_3P8_h       |                                                                            |                          | 150   |                          | mV   |

| FRWEN Rising                                              | FRWEN_r         |                                                                            | 0.48                     | 0.625 | 0.77                     | V    |

| FRWEN Hysteresis                                          | FRWEN_h         |                                                                            |                          | 20    |                          | mV   |

| Bias Current                                              | •               | •                                                                          | •                        |       | •                        |      |

| Forward Supply Current, Disable State                     |                 | ADP, ADPS CSIN, CSIP, VDDP, DCIN = 5V,<br>FWREN = High, Control4<6> = High |                          | 120   | 200                      | μA   |

| Reverse Supply Current, Disable<br>State                  |                 | V <sub>OUT</sub> , VOUTS CSON, CSOP, VDDP,<br>DCIN = 5V, RVSEN = Low       |                          | 70    | 120                      | μA   |

| Forward Supply Current, Enable State                      |                 | ADP, ADPS CSIN, CSIP, DCIN = 20V,<br>FWREN = High                          |                          | 3000  | 3350                     | μA   |

| Reverse Supply Current, Enable State                      |                 | VOUT, VOUTS CSON, CSOP, DCIN = 20V,<br>RVSEN = High                        |                          | 3000  | 3350                     | μA   |

| Forward Supply Current, Enable State                      |                 | DCIN only (does not include gate driver current)                           |                          | 1600  | 1900                     | μA   |

| Reverse Supply Current, Enable<br>State                   |                 | DCIN only (does not include gate driver current)                           |                          | 1500  | 1700                     | μA   |

| Linear Regulator                                          |                 | •                                                                          |                          |       |                          |      |

| VDDA Output Voltage                                       | V <sub>DD</sub> | 6V < V <sub>ADP</sub> < 23V, no load                                       | 4.5                      | 5.1   | 5.5                      | V    |

| VDDA Dropout Voltage                                      | VDD_dp          | 30mA, V <sub>DCIN</sub> = 4V                                               |                          | 100   |                          | mV   |

| VDD Overcurrent Threshold                                 | VDD_OC          |                                                                            | 90                       | 135   | 175                      | mA   |

#### RAA489800

| Operating conditions: ADP = CSIP = CSIN = 20V, VOUTS = VOUT = CSOP = CSON = 8V, unless otherwise noted. Boldface limits apply |

|-------------------------------------------------------------------------------------------------------------------------------|

| across the ambient temperature range, -40°C to +100°C unless otherwise specified. (Continued)                                 |

| Parameter                                     | Symbol              | Test Conditions              | Min<br>( <u>Note 6</u> ) | Тур | Max<br>( <u>Note 6</u> ) | Unit |

|-----------------------------------------------|---------------------|------------------------------|--------------------------|-----|--------------------------|------|

| ADP Current Regulation, R <sub>ADP</sub> = 20 | mΩ                  |                              |                          |     |                          | l    |

| Input Current Accuracy                        |                     | CSIP - CSIN  = 80mV          |                          | 4   |                          | Α    |

|                                               |                     |                              | -3                       |     | +3                       | %    |

|                                               |                     | CSIP - CSIN  = 40mV          |                          | 2   |                          | Α    |

|                                               |                     |                              | -4                       |     | +4                       | %    |

|                                               |                     | CSIP - CSIN  = 10mV          |                          | 0.5 |                          | Α    |

|                                               |                     |                              | -10                      |     | +10                      | %    |

| Voltage Regulation                            |                     |                              |                          |     |                          | l    |

| Output Voltage Accuracy Forward               |                     | Measured at VOUTS, 5V and up | -1                       |     | +1                       | %    |

| (-10°C to +100°C)                             |                     | Measured at VOUTS, 4V to 5V  | -1.5                     |     | +1.5                     | %    |

| Output Voltage Accuracy Reverse               |                     | Measured at ADPS, 5V and up  | -2                       |     | +2                       | %    |

| (-10°C to +100°C)                             |                     | Measured at ADPS, 4V to 5V   | -2.5                     |     | +2.5                     | %    |

| Output Voltage Accuracy Forward               |                     | Measured at VOUTS, 5V and up | -1.5                     |     | +1.5                     | %    |

| (-40°C to +85°C)                              |                     | Measured at VOUTS, 4V to 5V  | -2                       |     | +2                       | %    |

| Output Voltage Accuracy Reverse               |                     | Measured at ADPS, 5V and up  | -2.5                     |     | +2.5                     | %    |

| (-40°C to +85°C)                              |                     | Measured at ADPS, 4V to 5V   | -3.5                     |     | +3.5                     | %    |

| Minimum Input Voltage Accuracy                |                     | Measured at ADPS             | -3                       |     | +3                       | V    |

| VOUT Current Regulation, Rs2 = 10             | mΩ                  |                              |                          |     |                          |      |

| V <sub>OUT</sub> Current Accuracy             |                     | CSOP - CSON  = 60mV          |                          | 6   |                          | А    |

|                                               |                     |                              | -3                       |     | +3                       | %    |

|                                               |                     | CSOP - CSON  = 20mV          |                          | 2   |                          | А    |

|                                               |                     |                              | -5                       |     | +5                       | %    |

|                                               |                     | CSOP - CSON  = 10mV          |                          | 1   |                          | А    |

|                                               |                     |                              | -10                      |     | +10                      | %    |

|                                               |                     | CSOP - CSON  = 5mV           |                          | 0.5 |                          | А    |

|                                               |                     |                              | -20                      |     | +20                      | %    |

| ADP Current-Sense Amplifier, R <sub>ADP</sub> | s = 20mΩ            |                              |                          |     |                          |      |

| CSIP/CSIN Input Voltage Range                 | V <sub>CSIP/N</sub> |                              | 0                        |     | 27                       | V    |

| RVSEN                                         |                     |                              |                          |     |                          | l    |

| High-Level Input Voltage                      |                     |                              | 0.9                      |     |                          | V    |

| Low-Level Input Voltage                       |                     |                              |                          |     | 0.35                     | V    |

| ALERT#, RVSPG, FWRPG                          |                     |                              | 1                        |     | 1                        | L    |

| Output Sinking Current                        |                     | Pin at 0.4V                  | 15                       | 40  | 65                       | mA   |

| Leakage Current                               |                     |                              |                          |     | 1                        | μA   |

| ALERT#                                        |                     |                              | 1                        |     | 1                        | l    |

| ALERT# Debounce Time ( <u>Note 7</u> )        |                     | ALERT# Debounce register     | -15                      |     | 15                       | %    |

| ,                                             |                     | -                            | 1                        |     | 1                        | L    |

#### RAA489800

| Operating conditions: ADP = CSIP = CSIN = 20V, VOUTS = VOUT = CSOP = CSON = 8V, unless otherwise noted. Boldface limits apply |

|-------------------------------------------------------------------------------------------------------------------------------|

| across the ambient temperature range, -40°C to +100°C unless otherwise specified. (Continued)                                 |

| Parameter                                     | Symbol           | Test Conditions                                                        | Min<br>( <u>Note 6</u> ) | Тур   | Max<br>( <u>Note 6</u> ) | Unit |

|-----------------------------------------------|------------------|------------------------------------------------------------------------|--------------------------|-------|--------------------------|------|

| Protection                                    |                  |                                                                        |                          |       |                          |      |

| ADP Overvoltage Rising Threshold              |                  | Forward mode                                                           | 25.5                     | 26.4  | 27.5                     | V    |

| VSYS Absolute Overvoltage Rising<br>Threshold |                  |                                                                        | 22.5                     | 23.5  | 24                       | V    |

| VSYS Absolute Overvoltage<br>Hysteresis       |                  |                                                                        |                          | 0.65  |                          | V    |

| VOUTS Overvoltage Rising<br>Threshold         |                  | Forward mode VOUTS - 12xREF                                            | 0.85                     | 1.1   | 1.45                     | V    |

| VOUTS Overvoltage Hysteresis                  |                  |                                                                        |                          | 0.55  |                          | V    |

| ADPS Overvoltage Rising<br>Threshold          |                  | Reverse mode ADPS - 12xREF                                             | 0.9                      | 1.2   | 1.5                      | V    |

| ADPS Overvoltage Hysteresis                   |                  |                                                                        |                          | 0.6   |                          | V    |

| Over Current Warning Threshold                |                  | Forward Mode at 4A                                                     | 90                       |       | 110                      | %    |

| VSYS Low Voltage Shutdown                     |                  | Control0<4> = 1, Control0<3> = 0                                       | 2.8                      | 3     | 3.3                      | V    |

| Threshold                                     |                  | Control0<4> = 1, Control0<3> = 1                                       | 3.1                      | 3.3   | 3.6                      | V    |

| VOUTS Undervoltage Falling<br>Threshold       |                  | Forward mode VOUTS - 12xREF                                            | -1.15                    | -0.85 | -0.55                    | V    |

| VOUTS Undervoltage Hysteresis                 |                  |                                                                        |                          | 0.6   |                          | V    |

| ADPS Undervoltage Falling<br>Threshold        |                  | Reverse mode ADPS - 12xREF                                             | -1.55                    | -1.2  | -0.85                    | V    |

| ADPS Undervoltage Hysteresis                  |                  |                                                                        |                          | 0.4   |                          | V    |

| Over-Temperature Threshold ( <u>Note 7</u> )  |                  |                                                                        | 140                      | 150   | 160                      | °C   |

| Oscillator                                    |                  | · ·                                                                    |                          |       | •                        |      |

| Oscillator Frequency, Digital Core<br>Only    |                  |                                                                        | 0.85                     | 1     | 1.15                     | MHz  |

| Digital Debounce Time Accuracy                |                  | PV Debounce and UV Debounce for<br>FWRPG and RVSPG delay               | -15                      |       | 15                       | %    |

| Miscellaneous                                 |                  | - <b>·</b>                                                             |                          |       |                          |      |

| Switching Frequency Accuracy                  |                  | All programmed f <sub>SW</sub> settings, CCM, and no period stretching | -15                      |       | 15                       | %    |

| ADP Discharge Current                         |                  | ADP = 5V                                                               |                          | 22    |                          | mA   |

| V <sub>OUT</sub> Discharge Current            |                  | V <sub>OUT</sub> = 5V                                                  |                          | 22    |                          | mA   |

| REF Pin Source Current                        |                  | Control1 <3> = 0                                                       | 1                        | 1.8   | 2.9                      | μA   |

| REF Pin Sink Current                          |                  | Control1 <3> = 0                                                       | 1.2                      | 2     | 3                        | μA   |

| REF Pin Fast Sink Current                     |                  | Control1 <3> = 1                                                       |                          | 2     |                          | μA   |

| REF Pin Fast Source Current                   |                  | Control1 <3> = 1                                                       |                          | 20    |                          | μA   |

| SMBus                                         |                  |                                                                        |                          |       |                          |      |

| SDA/SCL Input Low Voltage                     |                  |                                                                        |                          |       | 0.7                      | V    |

| SDA/SCL Input High Voltage                    |                  |                                                                        | 1.5                      |       |                          | V    |

| SDA/SCL Input Bias Current                    |                  |                                                                        |                          |       | 1                        | μA   |

| SDA, Output Sink Current (Note 7)             |                  | SDA = 0.4V                                                             | 4                        |       |                          | mA   |

| SMBus Frequency                               | f <sub>SMB</sub> |                                                                        | 10                       |       | 400                      | kHz  |

| Parameter                   | Symbol                  | Test Conditions        | Min<br>( <u>Note 6</u> ) | Тур | Max<br>( <u>Note 6</u> ) | Unit |

|-----------------------------|-------------------------|------------------------|--------------------------|-----|--------------------------|------|

| Gate Driver                 |                         | •                      |                          |     | •                        |      |

| UGATE1 Pull-Up Resistance   | UG1 <sub>RPU</sub>      | 100mA source current   |                          | 800 | 1200                     | mΩ   |

| UGATE1 Source Current       | UG1 <sub>SRC</sub>      | UGATE1 - PHASE1 = 2.5V | 1.3                      | 2   |                          | А    |

| UGATE1 Pull-Down Resistance | UG1 <sub>RPD</sub>      | 100mA sink current     |                          | 350 | 475                      | mΩ   |

| UGATE1 Sink Current         | UG1 <sub>SNK</sub>      | UGATE1 - PHASE1 = 2.5V | 1.9                      | 2.8 |                          | А    |

| LGATE1 Pull-Up Resistance   | LG1 <sub>RPU</sub>      | 100mA source current   |                          | 800 | 1200                     | mΩ   |

| LGATE1 Source Current       | LG1 <sub>SRC</sub>      | LGATE1 - GND = 2.5V    | 1.3                      | 2   |                          | А    |

| LGATE1 Pull-Down Resistance | LG1 <sub>RPD</sub>      | 100mA sink current     |                          | 300 | 450                      | mΩ   |

| LGATE1 Sink Current         | LG1 <sub>SNK</sub>      | LGATE1 - GND = 2.5V    | 2.3                      | 3.5 |                          | Α    |

| LGATE2 Pull-Up Resistance   | LG2 <sub>RPU</sub>      | 100mA source current   |                          | 800 | 1200                     | mΩ   |

| LGATE2 Source Current       | LG2 <sub>SRC</sub>      | LGATE2 - GND = 2.5V    | 1.3                      | 2   |                          | А    |

| LGATE2 Pull-Down Resistance | LG2 <sub>RPD</sub>      | 100mA sink current     |                          | 300 | 450                      | mΩ   |

| LGATE2 Sink Current         | LG2 <sub>SNK</sub>      | LGATE2 - GND = 2.5V    | 2.3                      | 3.5 |                          | А    |

| UGATE2 Pull-Up Resistance   | UG2 <sub>RPU</sub>      | 100mA source current   |                          | 800 | 1200                     | mΩ   |

| UGATE2 Source Current       | UG2 <sub>SRC</sub>      | UGATE2 - PHASE2 = 2.5V | 1.3                      | 2   |                          | А    |

| UGATE2 Pull-Down Resistance | UG2 <sub>RPD</sub>      | 100mA sink current     |                          | 300 | 450                      | mΩ   |

| UGATE2 Sink Current         | UG2 <sub>SNK</sub>      | UGATE2 - PHASE2 = 2.5V | 2.3                      | 3.5 |                          | А    |

| UGATE1 to LGATE1 Dead Time  | t <sub>UG1LG1DEAD</sub> |                        | 10                       | 20  | 40                       | ns   |

| LGATE1 to UGATE1 Dead Time  | t <sub>LG1UG1DEAD</sub> |                        | 10                       | 20  | 40                       | ns   |

| LGATE2 to UGATE2 Dead Time  | t <sub>LG2UG2DEAD</sub> |                        | 10                       | 20  | 40                       | ns   |

| UGATE2 to LGATE2 Dead Time  | t <sub>UG2LG2DEAD</sub> |                        | 10                       | 20  | 40                       | ns   |

Operating conditions: ADP = CSIP = CSIN = 20V, VOUTS = VOUT = CSOP = CSON = 8V, unless otherwise noted. Boldface limits apply across the ambient temperature range, -40°C to +100°C unless otherwise specified. (Continued)

#### Notes:

6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

7. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

### 2.5 SMBus Timing Specification

| Parameters                          | Symbol              | Test Conditions                                                                                 | Min<br>( <u>Note 6</u> ) | Тур | Max<br>( <u>Note 6</u> ) | Unit |

|-------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| SMBus Frequency                     | f <sub>SMB</sub>    |                                                                                                 | 10                       |     | 400                      | kHz  |

| Bus-Free Time                       | t <sub>BUF</sub>    |                                                                                                 | 4.7                      |     |                          | μs   |

| Start Condition Hold Time from SCL  | t <sub>HD:STA</sub> |                                                                                                 | 4                        |     |                          | μs   |

| Start Condition Setup Time from SCL | t <sub>SU:STA</sub> |                                                                                                 | 4.7                      |     |                          | μs   |

| Stop Condition Setup Time from SCL  | t <sub>SU:STO</sub> |                                                                                                 | 4                        |     |                          | μs   |

| SDA Hold Time from SCL              | t <sub>HD:DAT</sub> |                                                                                                 | 300                      |     |                          | ns   |

| SDA Setup Time from SCL             | t <sub>SU:DAT</sub> |                                                                                                 | 250                      |     |                          | ns   |

| SCL Low Period                      | t <sub>LOW</sub>    |                                                                                                 | 4.7                      |     |                          | μs   |

| SCL High Period                     | t <sub>HIGH</sub>   |                                                                                                 | 4                        |     |                          | μs   |

| SMBus Inactivity Timeout            |                     | Maximum charging period without an SMBus<br>Write to MaxSystemVoltage or ADPCurrent<br>register |                          | 175 |                          | s    |

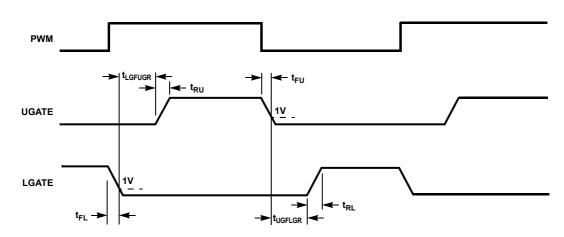

Figure 4. Gate Driver Timing Diagram

#### **Typical Performance Curves** 3.

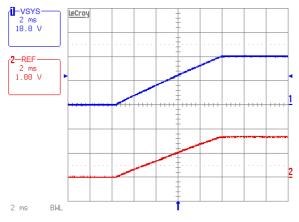

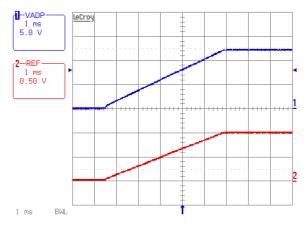

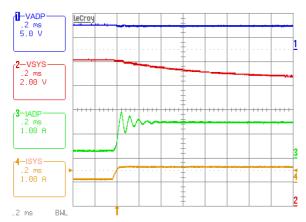

Figure 5. Forward Mode Soft-Start, 12V<sub>ADP</sub>, 20V<sub>SYS</sub>

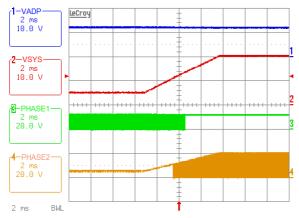

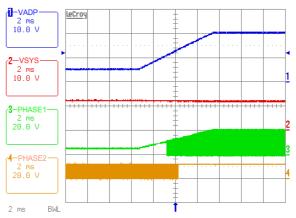

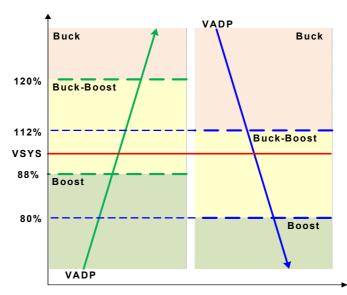

Figure 7. V<sub>SYS</sub> Voltage Ramps Up in Forward Mode, Buck -> Buck-Boost -> Boost Operation Mode Transition

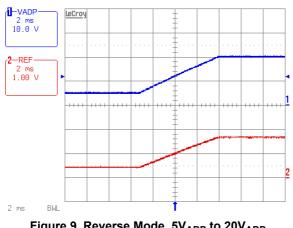

Figure 9. Reverse Mode, 5V<sub>ADP</sub> to 20V<sub>ADP</sub>

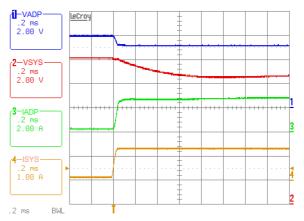

Figure 6. Reverse Mode, Soft-Start, 12V<sub>ADP</sub>, 5V<sub>SYS</sub>

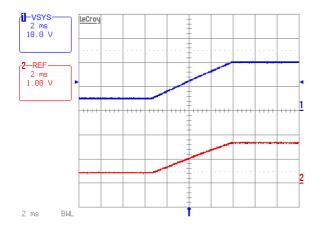

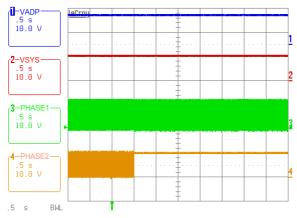

Figure 8. ADP Voltage Ramps Up in Reverse Mode, Buck -> Buck-Boost -> Boost Operation Mode Transition

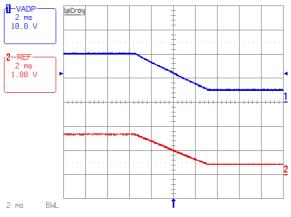

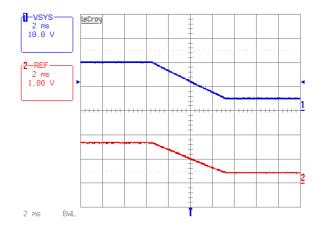

Figure 10. Reverse Mode, 20V<sub>ADP</sub> to 5V<sub>ADP</sub>

Figure 11. Forward Mode, 5V<sub>SYS</sub> to 20V<sub>SYS</sub>

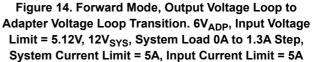

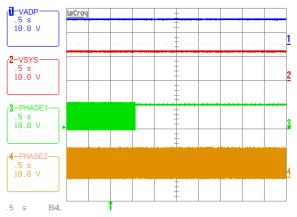

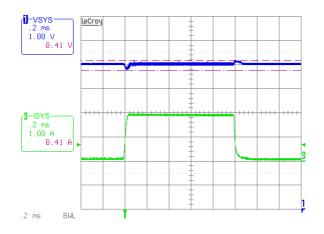

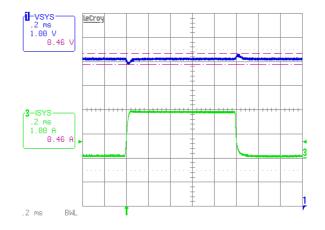

Figure 13. Forward Mode, Output Voltage Loop to ADP Current Loop Transition. 5V<sub>ADP</sub>, 12V<sub>SYS</sub>, System Load 0A to 0.65A Step, ADP Current Limit = 1.5A

Figure 15. Forward Mode, Force Buck-Boost Mode to Buck Mode. 12V<sub>ADP</sub>, 10.1V<sub>SYS</sub>

Figure 12. Forward Mode, 20V<sub>SYS</sub> to 5V<sub>SYS</sub>

Figure 16. Reverse Mode, Force Buck-Boost Mode to Buck Mode. 10.1V<sub>ADP</sub>, 12V<sub>SYS</sub>

Figure 17. Forward Mode, 5V<sub>ADP</sub>, 12V<sub>SYS</sub>, 0-2A Transient Load

Figure 18. Reverse Mode, 20V<sub>ADP</sub>, 12V<sub>SYS</sub>, 0-2A Transient Load

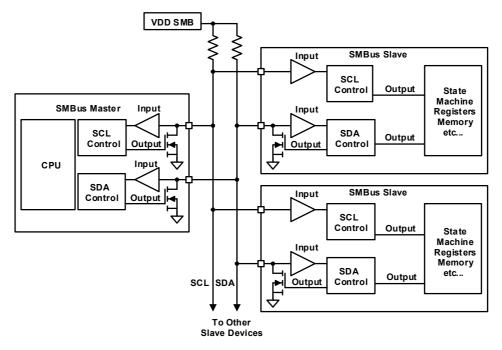

### 4. General SMBus Architecture

Figure 19. General SMBus Architecture

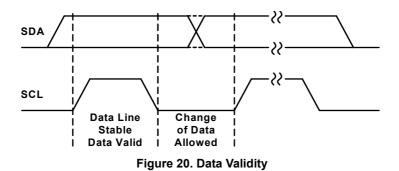

### 4.1 Data Validity

The data on the SDA line must be stable during the HIGH period of the SCL, unless generating a START or STOP condition. The HIGH or LOW state of the data line can change only when the clock signal on the SCL line is LOW. See <u>Figure 20</u>.

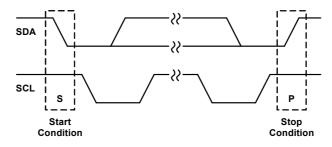

### 4.2 START and STOP Conditions

As Figure 21 shows, the START condition is a HIGH to LOW transition of the SDA line while SCL is HIGH.

The STOP condition is a LOW to HIGH transition on the SDA line while SCL is HIGH. A STOP condition must be sent before each START condition.

Figure 21. Start and Stop Waveforms

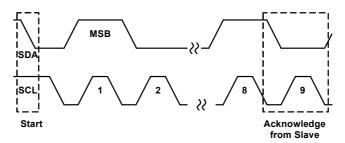

#### 4.3 Acknowledge

Each address and data transmission uses nine clock pulses. The ninth pulse is the acknowledge bit (ACK). After the start condition, the master sends seven slave address bits and an R/W bit during the next eight clock pulses. During the ninth clock pulse, the device that recognizes its own address holds the data line low to acknowledge (see <u>Figure 22</u>). Both the master and the slave use the ACK bit to acknowledge receipt of register addresses and data.

Figure 22. Acknowledge on the SMBus

### 4.4 SMBus Transactions

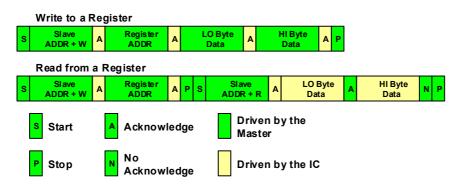

All transactions start with a control byte sent from the SMBus master device. The control byte begins with a START condition, followed by seven bits of slave address (see <u>Table 2</u>), and the R/W bit. The R/W bit is "0" for a WRITE or "1" for a READ. If any slave device on the SMBus recognizes its address, it acknowledges by pulling the Serial Data (SDA) line low for the last clock cycle in the control byte. If no slave exists at that address or it is not ready to communicate, the data line is "1", indicating a Not Acknowledge condition.

After the control byte is sent and the RAA489800 acknowledges it, the second byte sent by the master must be a register address byte such as 0x14 for the SystemCurrentLimit register. The register address byte tells the RAA489800 which register the master writes or reads. See <u>Tables 3</u> for more information about the registers. After the RAA489800 receives a register address byte, it responds with an ACK.

#### 4.5 Byte Format

Every byte put on the SDA line must be eight bits long and must be followed by an ACK bit. Data is transferred with the Most Significant Bit (MSB) first and the Least Significant Bit (LSB) last. The LO BYTE data is transferred before the HI BYTE data. For example, when writing 0x41A0, 0xA0 is written first and 0x41 is written second.

Figure 23. SMBus Read and Write Protocol

### 4.6 SMBus and I<sup>2</sup>C Compatibility

The RAA489800 SMBus minimum input logic high voltage is 1.5V, so it is compatible with I<sup>2</sup>C with pull-up power supplies higher than 1.5V.

The RAA489800 SMBus registers are 16 bits, so it is compatible with 16 bits  $I^2C$  or 8 bits  $I^2C$  with auto-increment capability. The chip does not acknowledge SMBus communication unless either ADP or VOUT is higher than 4.1V.

# 5. RAA489800 SMBus Commands

The RAA489800 receives control inputs from the SMBus interface after V<sub>DD</sub> 2.7V Power-On Reset (POR). The serial interface complies with the System Management Bus Specification, which can be downloaded from <u>www.smbus.org</u>. The RAA489800 uses the SMBus Read-word and Write-word protocols (see <u>Figure 23</u>) to communicate with the host system. The RAA489800 is an SMBus slave device and does not initiate communication on the bus. The RAA489800 address is programmable through the ADDR0 and ADDR1 voltage levels (see <u>Table 2</u>) to support multiple RAA489800s sharing a common SMBus. Connect the ADDR0 and ADDR1 pins to either ground or VDD.

Bits 1 and 2 are for the ADDR0 and ADDR1 pins, respectively. A "1" means the pin voltage is high, while a "0" means the pin voltage is low. From Bits 3 to 7, the value is fixed as 10010. The address is latched at the rising  $V_{DD}$  2.7V POR threshold.

| ADDR0 | ADDR1 | Read/Write | Binary Address | Hex Address |

|-------|-------|------------|----------------|-------------|

| 0     | 0     | 1          | 1001,0001      | 0x91H       |

| 0     | 0     | 0          | 1001,0000      | 0x90H       |

| 0     | 1     | 1          | 1001,0101      | 0x95H       |

| 0     | 1     | 0          | 1001,0100      | 0x94H       |

| 1     | 0     | 1          | 1001,0011      | 0x93H       |

| 1     | 0     | 0          | 1001,0010      | 0x92H       |

| 1     | 1     | 1          | 1001,0111      | 0x97H       |

| 1     | 1     | 0          | 1001,0110      | 0x96H       |

#### Table 2. Address Table

The data (SDA) and clock (SCL) pins have Schmitt-trigger inputs that can accommodate slow edges. Choose pull-up resistors for SDA and SCL to achieve rise times according to the SMBus specifications.

The information in this datasheet is based on current-sensing resistors  $Rs1 = 20m\Omega$  and  $Rs2 = 10m\Omega$ , unless otherwise specified.

| Register Names           | Register<br>Address | Read/<br>Write | Number<br>of Bits | Description                                                                                                                                                                                                    | Default            |

|--------------------------|---------------------|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| SystemCurrentLimit       | 0x14                | R/W            | 11                | [12:2]11-bit, LSB size 4mA, total range 6080mA, with 10m $\Omega$ Rs1.<br>This is output current in Forward mode and input current in<br>Reverse mode. Gain is 0.5x in reverse direction. See <u>Table 4</u> . | 1.5A               |

| ForwardRegulatingVoltage | 0x15                | R/W            | 12                | [14:3]12-bit, LSB size 12mV. See PROG Table 21.                                                                                                                                                                | 5.004V             |

|                          |                     |                |                   |                                                                                                                                                                                                                | 9.000V             |

|                          |                     |                |                   |                                                                                                                                                                                                                | 12.000V            |

|                          |                     |                |                   |                                                                                                                                                                                                                | 15.000V            |

|                          |                     |                |                   |                                                                                                                                                                                                                | 20.004V            |

| Control0                 | 0x39                | R/W            | 16                | Configures various options. See <u>Table 10</u> .                                                                                                                                                              | 0x0000h            |

| Information1             | 0x3A                | R              | 16                | Indicates various status. See <u>Table 18</u> .                                                                                                                                                                | 0x0000h            |

| Control1                 | 0x3C                | R/W            | 16                | Configures various options. See <u>Table 11</u> .                                                                                                                                                              | 0x0000h            |

| Control2                 | 0x3D                | R/W            | 16                | Configures various options. See <u>Table 12</u> .                                                                                                                                                              | 0x0000h            |

| ForwardInputCurrent      | 0x3F                | R/W            | 11                | [12:2]11-bit, LSB size 4mA, total range 6080mA, with 20m $\Omega$ Rs1. See Table 6.                                                                                                                            | Set by<br>PROG pin |

| ReverseRegulatingVoltage | 0x49                | R/W            | 12                | [14:3] 12-bit, LSB size 12mV<br>Reverse mode regulating voltage reference. See <u>Table 15</u> .                                                                                                               | 5.004V             |

| ReverseOutputCurrent     | 0x4A                | R/W            | 6                 | [12:7] 6-bit, LSB size 128mA, total range 4.096A<br>Reverse mode maximum current limit. See <u>Table 16</u> .                                                                                                  | 0.512A             |

#### Table 3.Register Summary

| Register Names    | Register<br>Address | Read/<br>Write | Number<br>of Bits | Description                                                                                        | Default |

|-------------------|---------------------|----------------|-------------------|----------------------------------------------------------------------------------------------------|---------|

| InputVoltageLimit | 0x4B                | R/W            | 6                 | [13:8] 6-bit, LSB size 512mV<br>Forward low $V_{IN}$ loop voltage reference. See <u>Table 17</u> . | 4.096V  |

| Control3          | 0x4C                | R/W            | 16                | Configures various options. See <u>Table 13</u> .                                                  | 0x0000h |

| Information2      | 0x4D                | R              | 16                | Indicates various statuses. See <u>Table 19</u> .                                                  | 0x0000h |

| Control4          | 0x4E                | R/W            | 8                 | [7:0] 8-bit, configures various options. See <u>Tables 14</u> .                                    | 0x00h   |

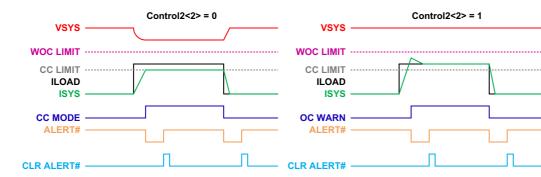

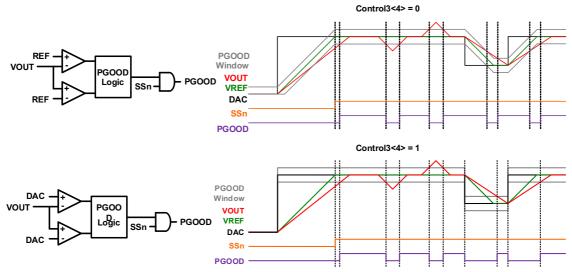

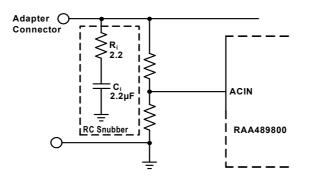

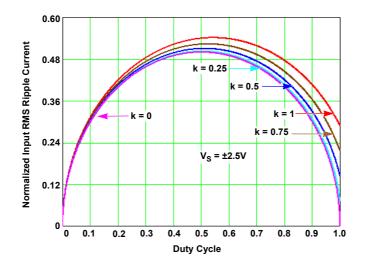

| ManufacturerID    | 0xFE                | R              | 8                 | Manufacturer's ID register.                                                                        | 0x49h   |