#### RC310xxB

VersaClock 7 Programmable Jitter Attenuator Family

#### Description

The RC310xxB are high-performance programmable jitter attenuators with network synchronization capabilities. The devices support JEDEC JESD204B/C for converter synchronization, and SyncE for network-based synchronization.

The RC310xxB are ideal for driving converter circuits in wire-line infrastructure, data center equipment, and instrumentation applications.

#### **Applications**

- Switches / Routers

- Synchronous Ethernet (SyncE) equipment

- Telecom Time Slave Clock (T-TSC) equipment

- Jitter attenuation for 10 / 25 / 40 / 100 / 200 / 400

Gbps Ethernet PHYs or Switches

- Small Cell for 4.5G and 5G

#### **Features**

- 169fs RMS phase jitter at 156.25MHz (typ.)

- PCIe<sup>®</sup> Gen7 Common Clock jitter: 8fs RMS (typ.)

- Compliant with ITU-T G.8262 and G.8262.1 for synchronous Ethernet Equipment Clock (EEC/eEEC)

- Jitter attenuation with programmable loop bandwidth from 0.1Hz to 12kHz

- 1kHz to 650MHz LVDS/LP-HCSL outputs

- 1kHz to 200MHz LVCMOS outputs

- Simple AC-coupling to LVPECL and CML

- Integrated  $100\Omega$  and  $85\Omega$  LP-HCSL terminations

- JESD204B/C support on differential or singleended outputs with DC-coupling or AC-coupling

- Up to four single-ended or two differential clock inputs; one crystal/TCXO/OCXO input

- 1MHz I<sup>2</sup>C, 400kHz SMBus or 20MHz SPI support

- Configuration via factory-programmed One-Time Programmable (OTP) memory, serial interface, or external I2C EEPROM

- OTP holds up to four complete or 27 partial configurations

- 1.8V, 2.5V, 3.3V, -40° to +85°C operation

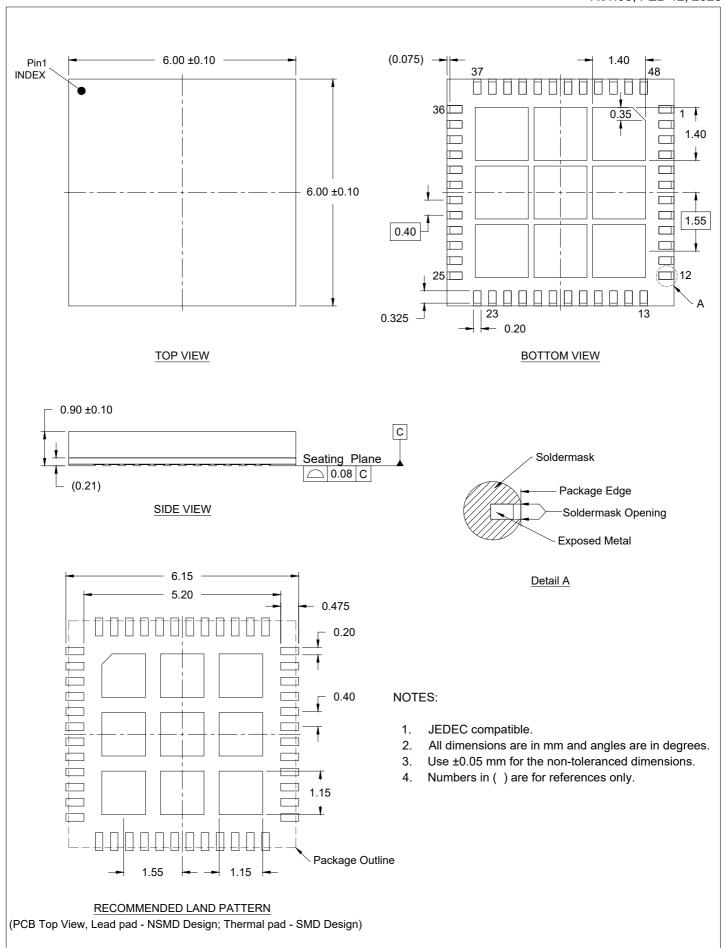

- RC31012B 12 output pairs/24 single-ended outputs

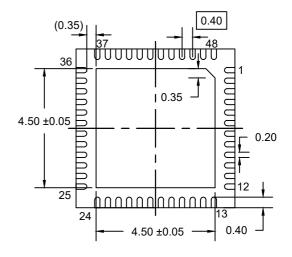

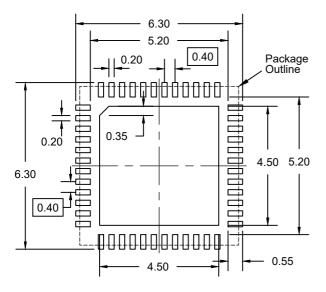

- 6 × 6 mm 48-QFN, integrated crystal option

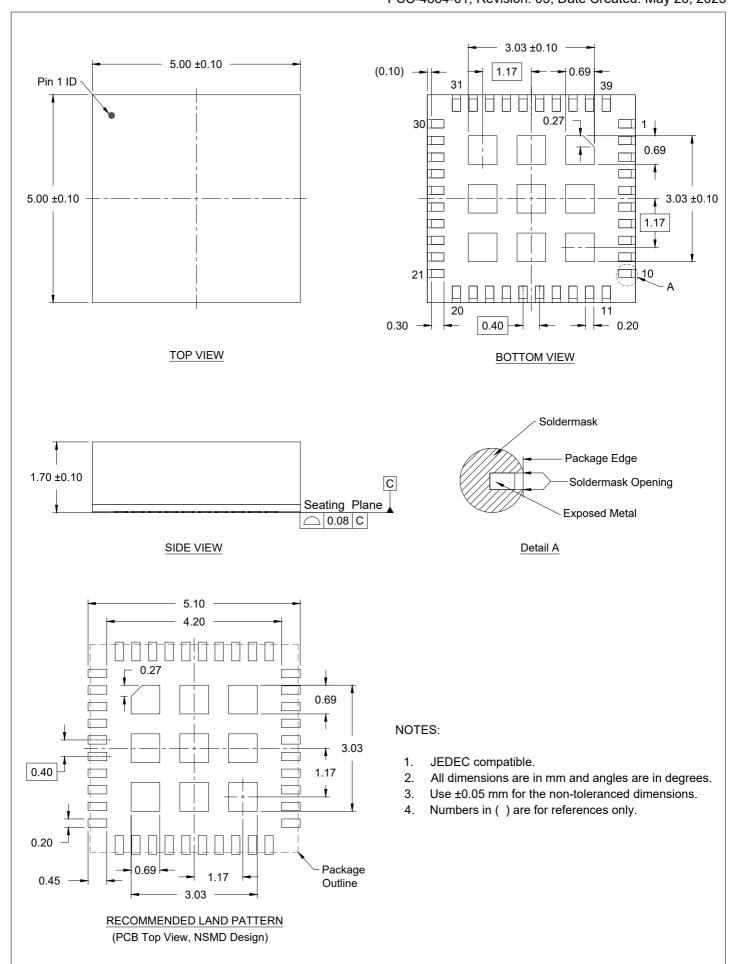

- RC31008B 8 differential/16 single-ended outputs

- 5 × 5 mm 40-QFN, integrated crystal option

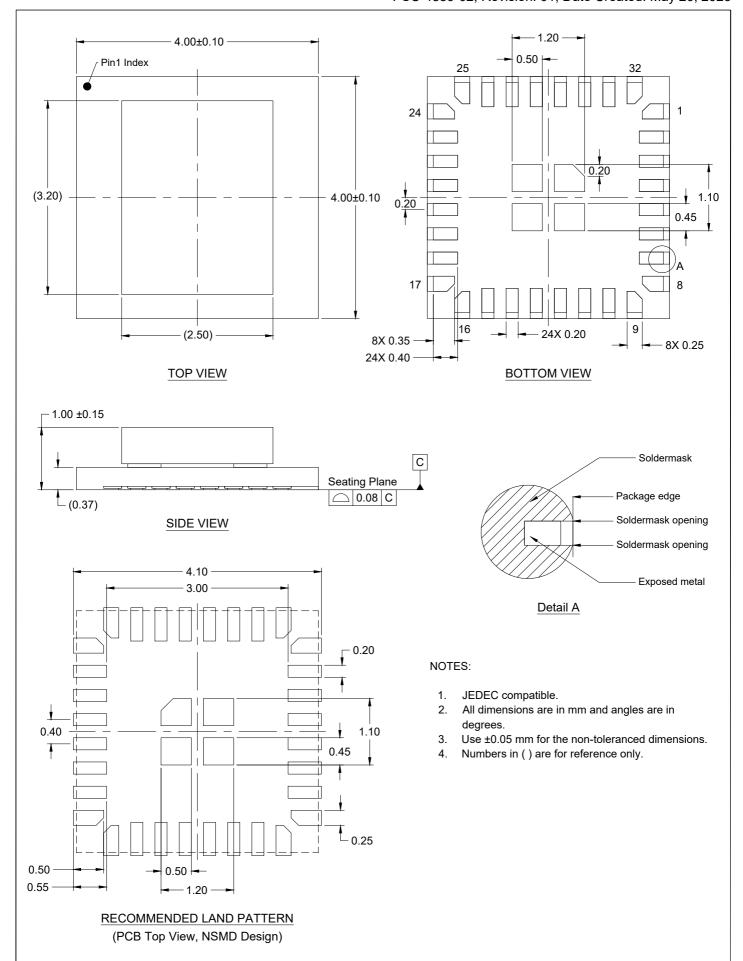

- RC31005B 5 differential/10 single-ended outputs

- 4 × 4 mm 32-LGA with integrated crystal

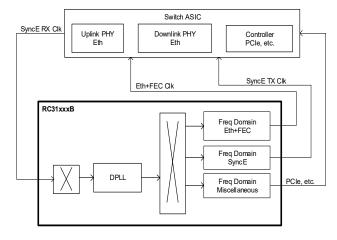

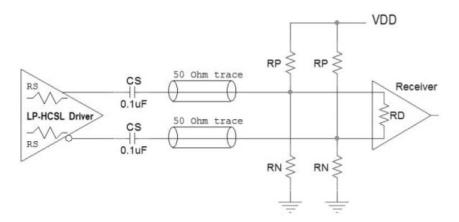

Figure 1. Typical Wire-line Infrastructure Use Case

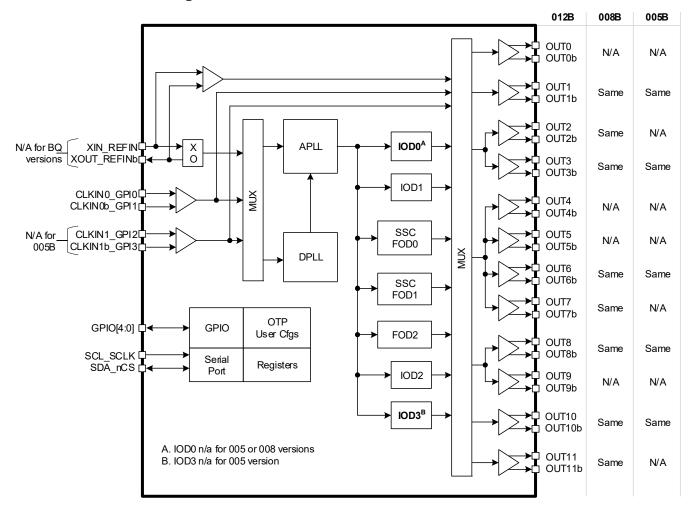

#### **RC310xxB Block Diagram**

Figure 2. RC310xxB Block Diagram

## **Contents**

| 1. | Pin lı | nformation                                       | . 8 |

|----|--------|--------------------------------------------------|-----|

|    | 1.1    | Pin Assignments – RCxxx12B (Top View)            | . 8 |

|    | 1.2    | Pin Descriptions – RCxxx12B                      |     |

|    | 1.3    | Pin Assignments – RCxxx12BQ (Top View)           | 11  |

|    | 1.4    | Pin Descriptions – RCxxx12BQ                     |     |

|    | 1.5    | Pin Assignments – RCxxx08B (Top View)            | 14  |

|    | 1.6    | Pin Descriptions – RCxxx08B                      | 14  |

|    | 1.7    | Pin Assignments – RCxxx08BQ (Top View)           | 16  |

|    | 1.8    | Pin Descriptions – RCxxx08BQ                     | 16  |

|    | 1.9    | Pin Assignments – RCxxx05BQ (Top View)           | 18  |

|    | 1.10   | Pin Descriptions – RCxxx05BQ                     |     |

|    | 1.11   | Pin Characteristics                              |     |

| 2. | Spec   | ifications                                       | 21  |

|    | 2.1    | Absolute Maximum Ratings                         |     |

|    | 2.2    | Recommended Operating Conditions                 |     |

|    | 2.3    | Electrical Characteristics                       |     |

| 3. |        | tional Description                               |     |

| Э. | 3.1    | Power-Up, Configuration, and Serial Interfaces   |     |

|    | 3.1    | Input Clocks                                     |     |

|    | 3.2    | 3.2.1 Crystal/Reference Input                    |     |

|    |        | 3.2.2 Clock Inputs                               |     |

|    | 3.3    | Clock Input Monitors.                            |     |

|    | 3.4    | APLL                                             |     |

|    | 3.4    | 3.4.1 APLL Lock Detector                         |     |

|    | 3.5    | DPLL                                             |     |

|    | 3.6    | DPLL Reference Selection                         |     |

|    | 3.0    | 3.6.1 Manual Reference Selection                 |     |

|    |        | 3.6.2 Automatic Reference Selection              |     |

|    |        | 3.6.3 Hitless Reference Switching                |     |

|    | 3.7    | DPLL Operating Modes                             |     |

|    | 3.1    | 3.7.1 Free-run                                   |     |

|    |        | 3.7.2 Acquire                                    |     |

|    |        | 3.7.3 Normal                                     |     |

|    |        | 3.7.4 Holdover                                   |     |

|    |        | 3.7.5 Hitless Switch.                            |     |

|    |        | 3.7.6 Write Frequency                            |     |

|    |        | 3.7.7 Manual Mode                                |     |

|    | 3.8    | DPLL Lock Detector                               |     |

|    | 3.9    | Output Dividers                                  |     |

|    | 3.9    | 3.9.1 Integer Output Dividers                    |     |

|    |        | 3.9.2 Fractional Output Dividers                 |     |

|    | 3 10   | Clock Outputs                                    |     |

|    | 5.10   | 3.10.1 Output Types                              |     |

|    |        | 3.10.2 Output Banks                              |     |

|    | _      |                                                  |     |

| 4. |        | cation Information                               |     |

|    | 4.1    | Recommendations for Unused Input and Output Pins | 54  |

#### RC310xxB Datasheet

| 9. | Revi                | Revision History |                                                           |    |  |  |  |  |  |

|----|---------------------|------------------|-----------------------------------------------------------|----|--|--|--|--|--|

| 8. | Orde                | ering Info       | ormation                                                  | 65 |  |  |  |  |  |

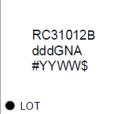

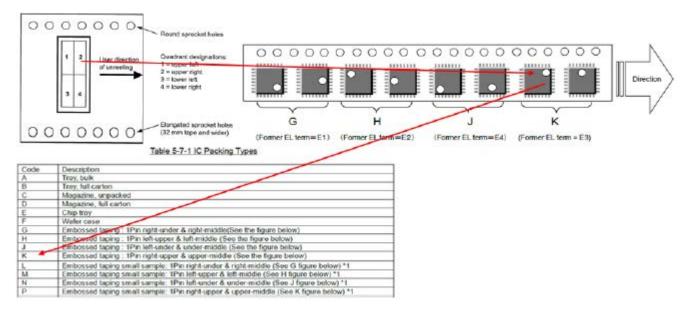

| 7. | Marking Diagrams 63 |                  |                                                           |    |  |  |  |  |  |

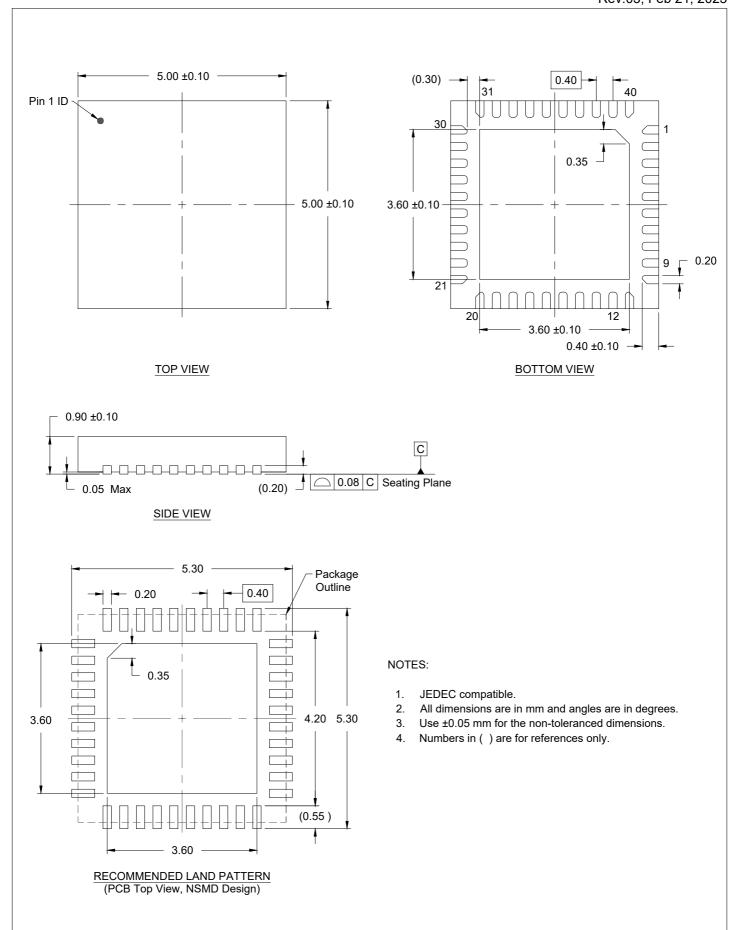

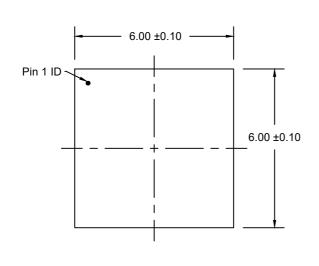

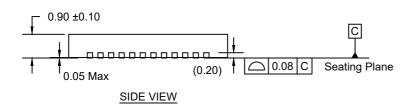

| 6. | Pack                | cage Out         | tline Drawings                                            | 63 |  |  |  |  |  |

|    | 5.2                 | Therma           | al Characteristics                                        | 60 |  |  |  |  |  |

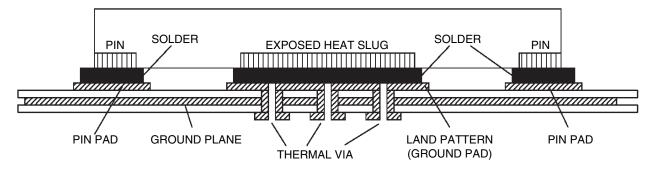

|    | 5.1                 | VFQFP            | PN ePad Thermal Release Path                              | 60 |  |  |  |  |  |

| 5. | Ther                | mal Info         | rmation                                                   | 60 |  |  |  |  |  |

|    |                     | 4.7.1            | Power Sequencing Considerations                           |    |  |  |  |  |  |

|    | 4.7                 |                  | Considerations                                            |    |  |  |  |  |  |

|    | 4.6                 | •                | al I2C Serial EEPROM Recommendations                      |    |  |  |  |  |  |

|    | 4.5                 | -                | Recommendations                                           |    |  |  |  |  |  |

|    |                     | 4.4.2<br>4.4.3   | Direct-Coupled LVDS Termination                           |    |  |  |  |  |  |

|    |                     | 4.4.1            | Direct-Coupled LP-HCSL Termination                        |    |  |  |  |  |  |

|    | 4.4                 |                  | ntial Output Terminations                                 |    |  |  |  |  |  |

|    |                     | 4.3.2            | XTAL Interface in XO Mode, Input Buffer Mode Not Selected |    |  |  |  |  |  |

|    |                     | 4.3.1            | XTAL Interface Set to Input Buffer Mode                   |    |  |  |  |  |  |

|    | 4.3                 |                  | iving the XTAL Interface                                  |    |  |  |  |  |  |

|    | 4.2                 | 4.1.4<br>CLKIN/  | Differential Outputs                                      |    |  |  |  |  |  |

|    |                     | 4.1.3            | LVCMOS Outputs                                            |    |  |  |  |  |  |

|    |                     | 4.1.2            | LVCMOS Control Pins                                       |    |  |  |  |  |  |

|    |                     | 4.1.1            | CLKIN/CLKINb [1:0] Inputs                                 | 54 |  |  |  |  |  |

#### RC310xxB Datasheet

# **Figures**

| Figure 1. Typical Wire-line Infrastructure Use Case                                      | . 1 |

|------------------------------------------------------------------------------------------|-----|

| Figure 2. RC310xxB Block Diagram                                                         | . 2 |

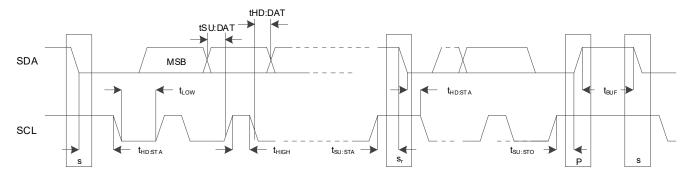

| Figure 3. I2C/SMBus Target Timing Diagram                                                | 45  |

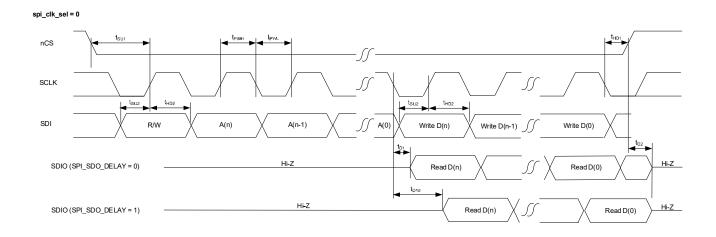

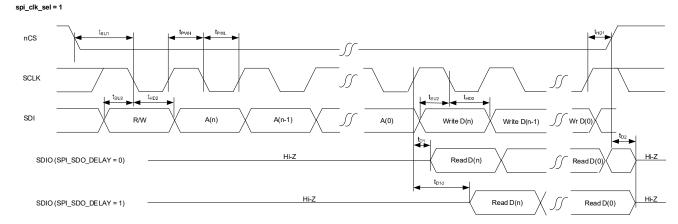

| Figure 4. SPI Bus Timing                                                                 | 47  |

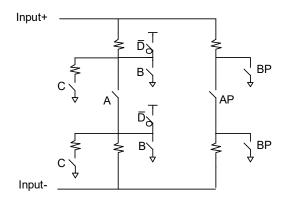

| Figure 5. Programmable Input Buffer Logical Diagram                                      | 54  |

| Figure 6. Input Buffer Behavior by Protocol                                              | 55  |

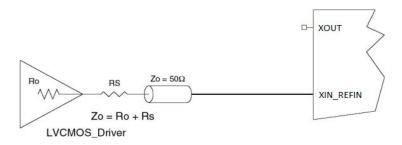

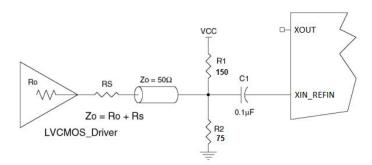

| Figure 7. 1.2V LVCMOS Driver to XTAL Input Interface                                     | 56  |

| Figure 8. LVCMOS Driver to XTAL Input Interface                                          | 56  |

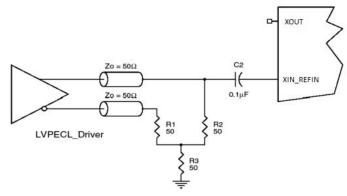

| Figure 9. LVPECL Driver to XTAL Input Interface                                          | 56  |

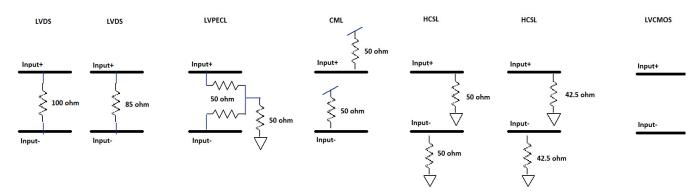

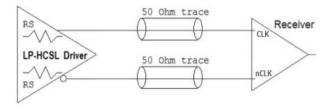

| Figure 10. Standard HCSL Termination                                                     | 57  |

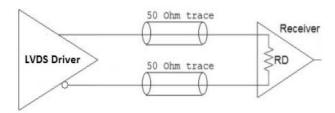

| Figure 11. Standard LVDS Termination                                                     | 57  |

| Figure 12. AC-Coupling Termination                                                       | 58  |

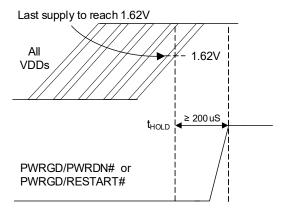

| Figure 13. Power Supply Sequencing Recommendations – Power-Up Using PWRGD/PWRDN# or POR# | 59  |

| Figure 14. P.C. Assembly for Exposed Pad Thermal Release Path – Side View                | 60  |

| Figure 15. Pin 1 Orientation in Tape and Reel Packaging                                  | 64  |

# **Tables**

| Table 1. RCxxx12B Pin Descriptions                                                                 | 8  |

|----------------------------------------------------------------------------------------------------|----|

| Table 2. RCxxx12B Pin Descriptions                                                                 | 11 |

| Table 3. RCxxx08B Pin Descriptions                                                                 | 14 |

| Table 4. RCxxx08BQ Pin Descriptions                                                                | 16 |

| Table 5. RCxxx05BQ Pin Descriptions                                                                | 18 |

| Table 6. Pin Characteristics                                                                       | 20 |

| Table 7. Absolute Maximum Ratings                                                                  | 21 |

| Table 8. Recommended Operating Conditions                                                          | 22 |

| Table 9. PCIe Refclk Phase Jitter, Clock Generator Mode, VDDO = 1.8V/2.5V/3.3V                     | 22 |

| Table 10. PCle Refclk Additive Phase Jitter, Fanout Mode, VDDO = 1.8V/2,5V/3.3V                    | 24 |

| Table 11. Phase Jitter and Phase Noise – 1.8V VDDO                                                 | 25 |

| Table 12. Phase Jitter and Phase Noise – 2.5V VDDO                                                 | 26 |

| Table 13. Phase Jitter and Phase Noise – 3.3V VDDO                                                 | 27 |

| Table 14. Jitter Attenuator and Network Synchronization                                            | 29 |

| Table 15. Clock Input Frequencies                                                                  | 29 |

| Table 16. External Crystal Characteristics                                                         | 29 |

| Table 17. Internal Crystal Characteristics (Q Versions Only)                                       | 30 |

| Table 18. Output Enable/Disable Timing                                                             | 30 |

| Table 19. Output Frequencies and Startup Times                                                     | 31 |

| Table 20. Output-to-Output, Input-to-Output Skew – LP-HCSL Outputs 1.8V/2.5V/3.3V VDDO             | 31 |

| Table 21. Output-to-Output, Input-to-Output Skew – LVDS Outputs 1.8V/2.5V/3.3V VDDO                | 32 |

| Table 22. Output-to-Output, Input-to-Output Skew – LVCMOS Outputs 1.8V/2.5V/3.3V VDDO              | 32 |

| Table 23. Static Phase Offset - Zero Delay Buffer Mode                                             | 33 |

| Table 24. LVCMOS AC/DC Output Characteristics – 1.8V VDDO                                          | 33 |

| Table 25. LVCMOS AC/DC Output Characteristics – 2.5V VDDO                                          | 33 |

| Table 26. LVCMOS AC/DC Output Characteristics – 3.3V VDDO                                          | 34 |

| Table 27. LVDS AC/DC Output Characteristics – 1.8V VDDO                                            | 34 |

| Table 28. LVDS AC/DC Output Characteristics – 2.5V/3.3V VDDO                                       | 35 |

| Table 29. LP-HCSL AC/DC Characteristics, Non-PCIe Frequencies – 1.8V VDDO                          | 36 |

| Table 30. LP-HCSL AC/DC Characteristics, Non-PCIe Frequencies – 2.5V/3.3V VDDO                     | 37 |

| Table 31. LP-HCSL AC/DC Characteristics, 100MHz PCIe – 1.8V VDDO                                   | 38 |

| Table 32. LP-HCSL AC/DC Characteristics, 100MHz PCIe – 2.5V/3.3V VDDO                              | 39 |

| Table 33. 100MHz PCIe Output Clock Accuracy and SSC                                                | 40 |

| Table 34. Spread-Spectrum Programmability                                                          |    |

| Table 35. CLKIN Differential Electrical Characteristics                                            |    |

| Table 36. GPI/GPIO Electrical Characteristics – 1.8V VDDD, VDDR, or VDDX                           | 42 |

| Table 37. GPI/GPIO Electrical Characteristics – 2.5V VDDD, VDDR, or VDDX                           | 43 |

| Table 38. GPI/GPIO Electrical Characteristics – 3.3V VDDD, VDDR, or VDDX                           | 43 |

| Table 39. CMOS GPI/GPIO Common Electrical Characteristics                                          | 43 |

| Table 40. Power Supply Current                                                                     | 44 |

| Table 41. I2C/SMBus Bus DC Electrical Characteristics                                              | 45 |

| Table 42. I2C/SMBus Bus AC Electrical Characteristics                                              | 45 |

| Table 43. SPI Target Interface Electrical Characteristics                                          | 47 |

| Table 44. Power Supply Noise Rejection                                                             |    |

| Table 45. Output Bank Source Mapping                                                               |    |

| Table 46. VDD Pin Assignments for Outputs, Integer Output Dividers, and Fractional Output Dividers |    |

| Table 47. Input Buffer Programming Options for Specific Signaling Protocols                        | 55 |

#### RC310xxB Datasheet

| Table 48. Thermal Characteristics (48-pin with External Crystal) | . 60 |

|------------------------------------------------------------------|------|

| Table 49. Thermal Characteristics (40-pin with External Crystal) | . 61 |

| Table 50. Thermal Characteristics (48-pin with Internal Crystal) | 61   |

| Table 51. Thermal Characteristics (40-pin with Internal Crystal) | . 61 |

| Table 52. Thermal Characteristics (32-pin with Internal Crystal) | . 62 |

| Table 53 Ordering Information                                    | 65   |

#### 1. Pin Information

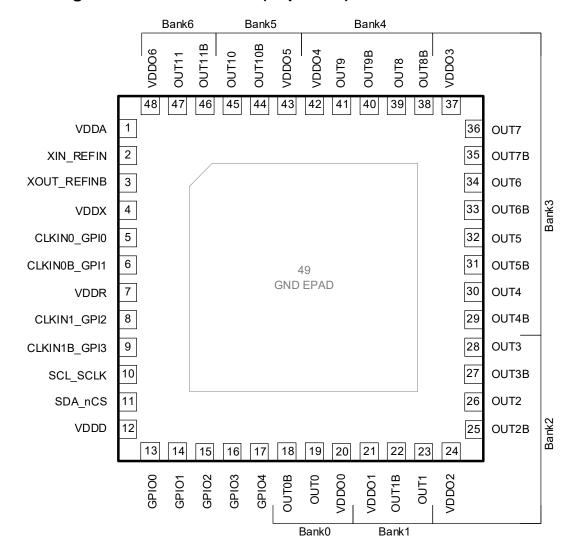

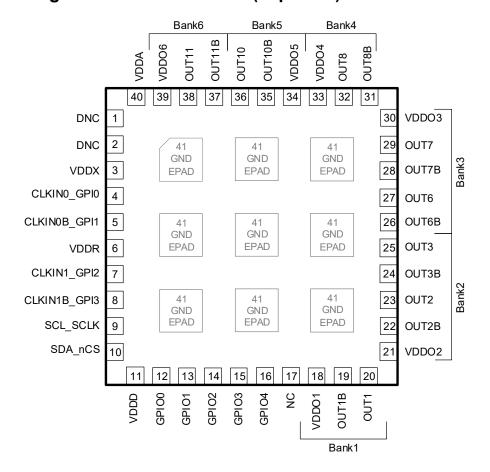

#### 1.1 Pin Assignments – RCxxx12B (Top View)

# 1.2 Pin Descriptions – RCxxx12B

Table 1. RCxxx12B Pin Descriptions

| Number | Name         | Туре  | Description                                                                                                                                                                                    |

|--------|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VDDA         | Power | Analog power supply. SeeTable 8 for supported voltages.                                                                                                                                        |

| 2      | XIN_REFIN    | I     | Crystal Input or differential reference clock positive input / CMOS single-ended reference clock input.                                                                                        |

| 3      | XOUT_REFINb  | I/O   | Crystal Output or differential reference clock negative input.  This pin should be connected to a crystal. If an oscillator is connected to XIN_REFIN, then this pin must be left unconnected. |

| 4      | VDDX         | Power | Crystal oscillator power supply. See Table 8 for supported voltages.                                                                                                                           |

| 5      | CLKIN0_GPI0  | I     | Differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI0.                                                                                 |

| 6      | CLKIN0b_GPI1 | I     | Differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI1.                                                                                 |

Table 1. RCxxx12B Pin Descriptions (Cont.)

| Number | Name         | Туре  | Description                                                                                                                                |

|--------|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | VDDR         | Power | CLKIN (receiver) power supply. See Table 8 for supported voltages.                                                                         |

| 8      | CLKIN1_GPI2  | I     | Differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI2.                             |

| 9      | CLKIN1b_GPI3 | I     | Differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI3.                             |

| 10     | SCL_SCLK     | I     | I2C Mode: I <sup>2</sup> C interface bi-directional clock.  SPI Mode: Serial Clock  This pin is 3.3V tolerant.                             |

| 11     | SDA_nCS      | I     | I2C Mode: I <sup>2</sup> C interface bi-directional data in open-drain mode. SPI Mode: Chip Select (active low) This pin is 3.3V tolerant. |

| 12     | VDDD         | Power | Digital core and GPIO power supply. See Table 8 for supported voltages. When programming the OTP, this supply must be 2.5V or 3.3V.        |

| 13     | GPIO0        | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                       |

| 14     | GPIO1        | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                       |

| 15     | GPIO2        | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                       |

| 16     | GPIO3        | I/O   | General purpose input/output.                                                                                                              |

| 17     | GPIO4        | I/O   | General purpose input/output.                                                                                                              |

| 18     | OUT0b        | 0     | Output Clock 0 negative.                                                                                                                   |

| 19     | OUT0         | 0     | Output Clock 0 positive.                                                                                                                   |

| 20     | VDD00        | Power | Power supply for output bank 0 and IOD 0. See Table 8 for supported voltages.                                                              |

| 21     | VDDO1        | Power | Power supply for output bank 1 and IOD 1. See Table 8 for supported voltages.                                                              |

| 22     | OUT1b        | 0     | Output Clock 1 negative.                                                                                                                   |

| 23     | OUT1         | 0     | Output Clock 1 positive.                                                                                                                   |

| 24     | VDDO2        | Power | Power supply for output bank 2 and FOD 0. See Table 8 for supported voltages.                                                              |

| 25     | OUT2b        | 0     | Output Clock 2 negative.                                                                                                                   |

| 26     | OUT2         | 0     | Output Clock 2 positive.                                                                                                                   |

| 27     | OUT3b        | 0     | Output Clock 3 negative.                                                                                                                   |

| 28     | OUT3         | 0     | Output Clock 3 positive.                                                                                                                   |

| 29     | OUT4b        | 0     | Output Clock 4 negative.                                                                                                                   |

| 30     | OUT4         | 0     | Output Clock 4 positive.                                                                                                                   |

| 31     | OUT5b        | 0     | Output Clock 5 negative.                                                                                                                   |

| 32     | OUT5         | 0     | Output Clock 5 positive.                                                                                                                   |

| 33     | OUT6b        | 0     | Output Clock 6 negative.                                                                                                                   |

| 34     | OUT6         | 0     | Output Clock 6 positive.                                                                                                                   |

| 35     | OUT7b        | 0     | Output Clock 7 negative.                                                                                                                   |

| 36     | OUT7         | 0     | Output Clock 7 positive.                                                                                                                   |

Table 1. RCxxx12B Pin Descriptions (Cont.)

| Number | Name   | Туре  | Description                                                                     |

|--------|--------|-------|---------------------------------------------------------------------------------|

| 37     | VDDO3  | Power | Power supply for output bank 3 and FOD 1. See Table 8 for supported voltages.   |

| 38     | OUT8b  | 0     | Output Clock 8 negative.                                                        |

| 39     | OUT8   | 0     | Output Clock 8 positive.                                                        |

| 40     | OUT9b  | 0     | Output Clock 9 negative.                                                        |

| 41     | OUT9   | 0     | Output Clock 9 positive.                                                        |

| 42     | VDDO4  | Power | Power supply for output bank 4 and FOD 2. See Table 8 for supported voltages.   |

| 43     | VDDO5  | Power | Power supply for output bank 5 and IOD 2. See Table 8 for supported voltages.   |

| 44     | OUT10b | 0     | Output Clock 10 negative.                                                       |

| 45     | OUT10  | 0     | Output Clock 10 positive.                                                       |

| 46     | OUT11b | 0     | Output Clock 11 negative.                                                       |

| 47     | OUT11  | 0     | Output Clock 11 positive.                                                       |

| 48     | VDDO6  | Power | Supply voltage for output bank 6 and IOD 3. See Table 8 for supported voltages. |

| EPAD   | GND    | Power | Ground. ePad must be connected to ground before any VDD is applied.             |

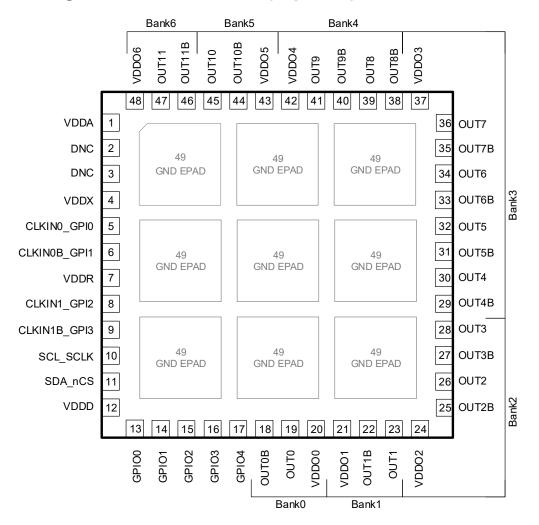

## 1.3 Pin Assignments – RCxxx12BQ (Top View)

#### 1.4 Pin Descriptions - RCxxx12BQ

Table 2. RCxxx12B Pin Descriptions

| Number | Name         | Туре  | Description                                                                                                    |

|--------|--------------|-------|----------------------------------------------------------------------------------------------------------------|

| 1      | VDDA         | Power | Analog power supply. See Table 8 for supported voltages.                                                       |

| 2      | DNC          | N/A   | Do not connect. This pin should have no stubs.                                                                 |

| 3      | DNC          | N/A   | Do not connect. This pin should have no stubs.                                                                 |

| 4      | VDDX         | Power | Crystal oscillator power supply. See Table 8 for supported voltages.                                           |

| 5      | CLKIN0_GPI0  | I     | Differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI0. |

| 6      | CLKIN0b_GPI1 | I     | Differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI1. |

| 7      | VDDR         | Power | CLKIN (receiver) power supply. See Table 8 for supported voltages.                                             |

| 8      | CLKIN1_GPI2  | I     | Differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI2. |

| 9      | CLKIN1b_GPI3 | I     | Differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI3. |

Table 2. RCxxx12B Pin Descriptions (Cont.)

| Number | Name     | Туре  | Description                                                                                                                                |

|--------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 10     | SCL_SCLK | 1     | I2C Mode: I <sup>2</sup> C interface bi-directional clock. SPI Mode: Serial Clock This pin is 3.3V tolerant.                               |

| 11     | SDA_nCS  | 1     | I2C Mode: I <sup>2</sup> C interface bi-directional data in open-drain mode. SPI Mode: Chip Select (active low) This pin is 3.3V tolerant. |

| 12     | VDDD     | Power | Digital core and GPIO power supply. See Table 8 for supported voltages. When programming the OTP, this supply must be 2.5V or 3.3V.        |

| 13     | GPIO0    | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                       |

| 14     | GPIO1    | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                       |

| 15     | GPIO2    | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                       |

| 16     | GPIO3    | I/O   | General purpose input/output.                                                                                                              |

| 17     | GPIO4    | I/O   | General purpose input/output.                                                                                                              |

| 18     | OUT0b    | 0     | Output Clock 0 negative.                                                                                                                   |

| 19     | OUT0     | 0     | Output Clock 0 positive.                                                                                                                   |

| 20     | VDD00    | Power | Power supply for output bank 0 and IOD 0. See Table 8 for supported voltages.                                                              |

| 21     | VDDO1    | Power | Power supply for output bank 1 and IOD 1. See Table 8 for supported voltages.                                                              |

| 22     | OUT1b    | 0     | Output Clock 1 negative.                                                                                                                   |

| 23     | OUT1     | 0     | Output Clock 1 positive.                                                                                                                   |

| 24     | VDDO2    | Power | Power supply for output bank 2 and FOD 0. See Table 8 for supported voltages.                                                              |

| 25     | OUT2b    | 0     | Output Clock 2 negative.                                                                                                                   |

| 26     | OUT2     | 0     | Output Clock 2 positive.                                                                                                                   |

| 27     | OUT3b    | 0     | Output Clock 3 negative.                                                                                                                   |

| 28     | OUT3     | 0     | Output Clock 3 positive.                                                                                                                   |

| 29     | OUT4b    | 0     | Output Clock 4 negative.                                                                                                                   |

| 30     | OUT4     | 0     | Output Clock 4 positive.                                                                                                                   |

| 31     | OUT5b    | 0     | Output Clock 5 negative.                                                                                                                   |

| 32     | OUT5     | 0     | Output Clock 5 positive.                                                                                                                   |

| 33     | OUT6b    | 0     | Output Clock 6 negative.                                                                                                                   |

| 34     | OUT6     | 0     | Output Clock 6 positive.                                                                                                                   |

| 35     | OUT7b    | 0     | Output Clock 7 negative.                                                                                                                   |

| 36     | OUT7     | 0     | Output Clock 7 positive.                                                                                                                   |

| 37     | VDDO3    | Power | Power supply for output bank 3 and FOD 1. See Table 8 for supported voltages.                                                              |

| 38     | OUT8b    | 0     | Output Clock 8 negative.                                                                                                                   |

| 39     | OUT8     | 0     | Output Clock 8 positive.                                                                                                                   |

| 40     | OUT9b    | 0     | Output Clock 9 negative.                                                                                                                   |

#### Table 2. RCxxx12B Pin Descriptions (Cont.)

| Number | Name   | Туре  | Description                                                                     |

|--------|--------|-------|---------------------------------------------------------------------------------|

| 41     | OUT9   | 0     | Output Clock 9 positive.                                                        |

| 42     | VDDO4  | Power | Power supply for output bank 4 and FOD 2. See Table 8 for supported voltages.   |

| 43     | VDDO5  | Power | Power supply for output bank 5 and IOD 2. See Table 8 for supported voltages.   |

| 44     | OUT10b | 0     | Output Clock 10 negative.                                                       |

| 45     | OUT10  | 0     | Output Clock 10 positive.                                                       |

| 46     | OUT11b | 0     | Output Clock 11 negative.                                                       |

| 47     | OUT11  | 0     | Output Clock 11 positive.                                                       |

| 48     | VDDO6  | Power | Supply voltage for output bank 6 and IOD 3. See Table 8 for supported voltages. |

| EPAD   | GND    | Power | Ground. ePad must be connected to ground before any VDD is applied.             |

## 1.5 Pin Assignments – RCxxx08B (Top View)

#### 1.6 Pin Descriptions - RCxxx08B

Table 3. RCxxx08B Pin Descriptions

| Number | Name         | Туре  | Description                                                                                                                                                                                    |

|--------|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | XIN_REFIN    | I     | Crystal Input or differential reference clock positive input / CMOS single-ended reference clock input.                                                                                        |

| 2      | XOUT_REFINb  | I/O   | Crystal Output or differential reference clock negative input.  This pin should be connected to a crystal. If an oscillator is connected to XIN_REFIN, then this pin must be left unconnected. |

| 3      | VDDX         | Power | Crystal oscillator power supply. See Table 8 for supported voltages.                                                                                                                           |

| 4      | CLKIN0_GPI0  | I     | differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI0.                                                                                 |

| 5      | CLKIN0b_GPI1 | I     | differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI1.                                                                                 |

| 6      | VDDR         | Power | CLKIN (receiver) power supply. See Table 8 for supported voltages.                                                                                                                             |

| 7      | CLKIN1_GPI2  | I     | Differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI2.                                                                                 |

| 8      | CLKIN1b_GPI3 | I     | Differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI3.                                                                                 |

| 9      | SCL_SCLK     | I     | I2C Mode: I <sup>2</sup> C interface bi-directional clock.  SPI Mode: Serial Clock  This pin is 3.3V tolerant.                                                                                 |

Table 3. RCxxx08B Pin Descriptions (Cont.)

| Number | Name    | Туре  | Description                                                                                                                                  |

|--------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 10     | SDA_nCS | I/O   | I2C Mode: I <sup>2</sup> C interface bi-directional data in open-drain mode.  SPI Mode: Chip Select (active low)  This pin is 3.3V tolerant. |

| 11     | VDDD    | Power | Digital core and GPIO power supply. See Table 8 for supported voltages. When programming the OTP, this supply must be 2.5V or 3.3V.          |

| 12     | GPIO0   | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                         |

| 13     | GPIO1   | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                         |

| 14     | GPIO2   | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                         |

| 15     | GPIO3   | I/O   | General purpose input/output.                                                                                                                |

| 16     | GPIO4   | I/O   | General purpose input/output.                                                                                                                |

| 17     | NC      | I     | Not connected.                                                                                                                               |

| 18     | VDDO1   | Power | Power supply for output bank 1 and IOD 1. See Table 8 for supported voltages.                                                                |

| 19     | OUT1b   | 0     | Output Clock 1 negative.                                                                                                                     |

| 20     | OUT1    | 0     | Output Clock 1 positive                                                                                                                      |

| 21     | VDDO2   | Power | Power supply for output bank 2 and FOD 0. See Table 8 for supported voltages.                                                                |

| 22     | OUT2b   | 0     | Output Clock 2 negative.                                                                                                                     |

| 23     | OUT2    | 0     | Output Clock 2 positive.                                                                                                                     |

| 24     | OUT3b   | 0     | Output Clock 3 negative.                                                                                                                     |

| 25     | OUT3    | 0     | Output Clock 3 positive.                                                                                                                     |

| 26     | OUT6b   | 0     | Output Clock 6 negative.                                                                                                                     |

| 27     | OUT6    | 0     | Output Clock 6 positive.                                                                                                                     |

| 28     | OUT7b   | 0     | Output Clock 7 negative.                                                                                                                     |

| 29     | OUT7    | 0     | Output Clock 7 positive.                                                                                                                     |

| 30     | VDDO3   | Power | Power supply for output bank 3 and FOD 1. See Table 8 for supported voltages.                                                                |

| 31     | OUT8b   | 0     | Output Clock 8 negative.                                                                                                                     |

| 32     | OUT8    | 0     | Output Clock 8 positive.                                                                                                                     |

| 33     | VDDO4   | Power | Power supply for output bank 4 and FOD 2. See Table 8 for supported voltages.                                                                |

| 34     | VDDO5   | Power | Power supply for output bank 5 and IOD 2. See Table 8 for supported voltages.                                                                |

| 35     | OUT10b  | 0     | Output Clock 10 negative.                                                                                                                    |

| 36     | OUT10   | 0     | Output Clock 10 positive.                                                                                                                    |

| 37     | OUT11b  | 0     | Output Clock 11 negative.                                                                                                                    |

| 38     | OUT11   | 0     | Output Clock 11 positive.                                                                                                                    |

| 39     | VDDO6   | Power | Supply voltage for output bank 6 and IOD 3. See Table 8 for supported voltages.                                                              |

| 40     | VDDA    | Power | Analog power supply. See Table 8 for supported voltages.                                                                                     |

| EPAD   | GND     | Power | Ground. ePad must be connected to ground before any VDD is applied.                                                                          |

#### 1.7 Pin Assignments – RCxxx08BQ (Top View)

#### 1.8 Pin Descriptions - RCxxx08BQ

Table 4. RCxxx08BQ Pin Descriptions

| Number | Name         | Туре  | Description                                                                                                                                  |

|--------|--------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DNC          | N/A   | Do not connect. This pin should have no stubs.                                                                                               |

| 2      | DNC          | N/A   | Do not connect. This pin should have no stubs.                                                                                               |

| 3      | VDDX         | Power | Crystal oscillator power supply. See Table 8 for supported voltages.                                                                         |

| 4      | CLKIN0_GPI0  | I     | Differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI0.                               |

| 5      | CLKIN0b_GPI1 | I     | Differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI1.                               |

| 6      | VDDR         | Power | CLKIN (receiver) power supply. See Table 8 for supported voltages.                                                                           |

| 7      | CLKIN1_GPI2  | I     | Differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI2.                               |

| 8      | CLKIN1b_GPI3 | I     | Differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI3.                               |

| 9      | SCL_SCLK     | I     | I2C Mode: I <sup>2</sup> C interface bi-directional clock. SPI Mode: Serial Clock This pin is 3.3V tolerant.                                 |

| 10     | SDA_nCS      | I/O   | I2C Mode: I <sup>2</sup> C interface bi-directional data in open-drain mode.  SPI Mode: Chip Select (active low)  This pin is 3.3V tolerant. |

Table 4. RCxxx08BQ Pin Descriptions (Cont.)

| Number | Name   | Туре  | Description                                                                                                                         |

|--------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 11     | VDDD   | Power | Digital core and GPIO power supply. See Table 8 for supported voltages. When programming the OTP, this supply must be 2.5V or 3.3V. |

| 12     | GPIO0  | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                |

| 13     | GPIO1  | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                |

| 14     | GPIO2  | I/O   | General purpose input/output.  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                |

| 15     | GPIO3  | I/O   | General purpose input/output.                                                                                                       |

| 16     | GPIO4  | I/O   | General purpose input/output.                                                                                                       |

| 17     | NC     | 1     | Not connected.                                                                                                                      |

| 18     | VDDO1  | Power | Power supply for output bank 1 and IOD 1. See Table 8 for supported voltages.                                                       |

| 19     | OUT1b  | 0     | Output Clock 1 negative.                                                                                                            |

| 20     | OUT1   | 0     | Output Clock 1 positive                                                                                                             |

| 21     | VDDO2  | Power | Power supply for output bank 2 and FOD 0. See Table 8 for supported voltages.                                                       |

| 22     | OUT2b  | 0     | Output Clock 2 negative.                                                                                                            |

| 23     | OUT2   | 0     | Output Clock 2 positive.                                                                                                            |

| 24     | OUT3b  | 0     | Output Clock 3 negative.                                                                                                            |

| 25     | OUT3   | 0     | Output Clock 3 positive.                                                                                                            |

| 26     | OUT6b  | 0     | Output Clock 6 negative.                                                                                                            |

| 27     | OUT6   | 0     | Output Clock 6 positive.                                                                                                            |

| 28     | OUT7b  | 0     | Output Clock 7 negative.                                                                                                            |

| 29     | OUT7   | 0     | Output Clock 7 positive.                                                                                                            |

| 30     | VDDO3  | Power | Power supply for output bank 3 and FOD 1. See Table 8 for supported voltages.                                                       |

| 31     | OUT8b  | 0     | Output Clock 8 negative.                                                                                                            |

| 32     | OUT8   | 0     | Output Clock 8 positive.                                                                                                            |

| 33     | VDDO4  | Power | Power supply for output bank 4 and FOD 2. See Table 8 for supported voltages.                                                       |

| 34     | VDDO5  | Power | Power supply for output bank 5 and IOD 2. See Table 8 for supported voltages.                                                       |

| 35     | OUT10b | 0     | Output Clock 10 negative.                                                                                                           |

| 36     | OUT10  | 0     | Output Clock 10 positive.                                                                                                           |

| 37     | OUT11b | 0     | Output Clock 11 negative.                                                                                                           |

| 38     | OUT11  | 0     | Output Clock 11 positive.                                                                                                           |

| 39     | VDDO6  | Power | Supply voltage for output bank 6 and IOD 3. See Table 8 for supported voltages.                                                     |

| 40     | VDDA   | Power | Analog power supply. See Table 8 for supported voltages.                                                                            |

| EPAD   | GND    | Power | Ground. ePad must be connected to ground before any VDD is applied.                                                                 |

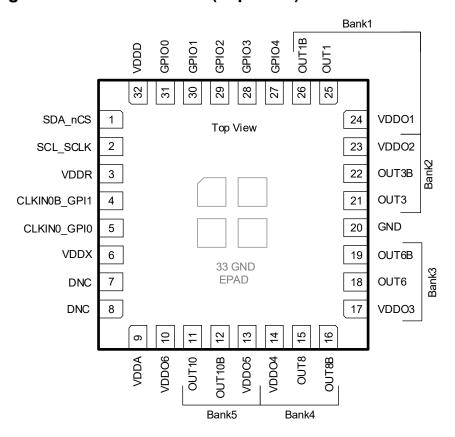

#### 1.9 Pin Assignments – RCxxx05BQ (Top View)

#### 1.10 Pin Descriptions - RCxxx05BQ

Table 5. RCxxx05BQ Pin Descriptions

| Number | Name         | Туре  | Description                                                                                                   |

|--------|--------------|-------|---------------------------------------------------------------------------------------------------------------|

|        |              |       | I2C Mode: I <sup>2</sup> C interface bi-directional data in open-drain mode.                                  |

| 1      | SDA_nCS      | I/O   | SPI Mode: Chip Select (active low)                                                                            |

|        |              |       | This pin is 3.3V tolerant.                                                                                    |

|        |              |       | I2C Mode: I <sup>2</sup> C interface bi-directional clock.                                                    |

| 2      | SCL_SCLK     | I     | SPI Mode: Serial Clock                                                                                        |

|        |              |       | This pin is 3.3V tolerant.                                                                                    |

| 3      | VDDR         | Power | CLKIN (receiver) power supply. See Table 8 for supported voltages.                                            |

| 4      | CLKIN0b_GPI1 | I     | Differential clock negative input / CMOS single-ended reference clock input or general purpose input pin GPI1 |

| 5      | CLKIN0_GPI0  | I     | Differential clock positive input / CMOS single-ended reference clock input or general purpose input pin GPI0 |

| 6      | VDDX         | Power | Crystal oscillator power supply. See Table 8 for supported voltages.                                          |

| 7      | DNC          | NA    | Do not connect. This pin should have no stubs.                                                                |

| 8      | DNC          | NA    | Do not connect. This pin should have no stubs.                                                                |

| 9      | VDDA         | Power | Analog power supply. See Table 8 for supported voltages.                                                      |

| 10     | VDDO6        | Power | Supply voltage for output bank 6 and IOD 3. See Table 8 for supported voltages.                               |

| 11     | OUT10        | 0     | Output Clock 10 positive.                                                                                     |

| 12     | OUT10b       | 0     | Output Clock 10 negative.                                                                                     |

Table 5. RCxxx05BQ Pin Descriptions (Cont.)

| Number | Name  | Туре  | Description                                                                                                                         |  |  |  |

|--------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 13     | VDDO5 | Power | Power supply for output bank 5 and IOD 2. See Table 8 for supported voltages.                                                       |  |  |  |

| 14     | VDDO4 | Power | Power supply for output bank 4 and FOD 2. See Table 8 for supported voltages.                                                       |  |  |  |

| 15     | OUT8  | 0     | Output Clock 8 positive.                                                                                                            |  |  |  |

| 16     | OUT8b | 0     | Output Clock 8 negative.                                                                                                            |  |  |  |

| 17     | VDDO3 | Power | Power supply for output bank 3 and FOD 1. See Table 8 for supported voltages.                                                       |  |  |  |

| 18     | OUT6  | 0     | Output Clock 6 positive.                                                                                                            |  |  |  |

| 19     | OUT6b | 0     | Output Clock 6 negative.                                                                                                            |  |  |  |

| 20     | GND   | Power | Ground                                                                                                                              |  |  |  |

| 21     | OUT3  | 0     | Output Clock 3 positive.                                                                                                            |  |  |  |

| 22     | OUT3b | 0     | Output Clock 3 negative.                                                                                                            |  |  |  |

| 23     | VDDO2 | Power | Power supply for output bank 2 and FOD 0. See Table 8 for supported voltages.                                                       |  |  |  |

| 24     | VDDO1 | Power | Power supply for output bank 1 and IOD 1. See Table 8 for supported voltages.                                                       |  |  |  |

| 25     | OUT1  | 0     | Output Clock 1 positive                                                                                                             |  |  |  |

| 26     | OUT1b | 0     | Output Clock 1 negative.                                                                                                            |  |  |  |

| 27     | GPIO4 | I/O   | General purpose input/output                                                                                                        |  |  |  |

| 28     | GPIO3 | I/O   | General purpose input/output                                                                                                        |  |  |  |

| 29     | GPIO2 | I/O   | General purpose input/output  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                 |  |  |  |

| 30     | GPIO1 | I/O   | General purpose input/output  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                 |  |  |  |

| 31     | GPI00 | I/O   | General purpose input/output  3-level logic input during power-up and CMOS level logic after unless set to 3-level.                 |  |  |  |

| 32     | VDDD  | Power | Digital core and GPIO power supply. See Table 8 for supported voltages. When programming the OTP, this supply must be 2.5V or 3.3V. |  |  |  |

| EPAD   | GND   | Power | Ground. ePad must be connected to ground before any VDD is applied.                                                                 |  |  |  |

#### 1.11 Pin Characteristics

**Table 6. Pin Characteristics**

| Symbol                | Parameter                | Test Conditions                                      | Minimum | Typical | Maximum | Unit         |

|-----------------------|--------------------------|------------------------------------------------------|---------|---------|---------|--------------|

|                       |                          | CLKIN[1:0], CLKIN[1:0]b,<br>GPI[0:3]                 | -       | 2       | -       |              |

|                       |                          | SCL_SCLK, SDA_nCS                                    | -       | 3       | -       |              |

| C <sub>IN</sub>       | Input Capacitance        | XIN_REFIN [1]                                        | -       | 5       | -       | pF           |

|                       |                          | XOUT_REFINb [1]                                      | -       | 4       | -       |              |

|                       |                          | GPIO[0:4]                                            | -       | 5       | -       |              |

| R <sub>PULLUP</sub>   | Input Pull-Up Resistor   | All pins with internal pull up capability            | -       | 52.6    | -       | - kΩ         |

| R <sub>PULLDOWN</sub> | Input Pull-Down Resistor | All pins with internal pull down capability          | -       | 52.6    | -       |              |

|                       | Single-ended LP-HCSL     | $50\Omega$ single-ended (100 $\Omega$ differential). | -       | 51      | -       | 40 to<br>60Ω |

| Z <sub>OUTDC</sub>    | Output Impedance         | 42.5Ω single-ended (85Ω differential).               | -       | 44      | -       | 34 to<br>51Ω |

| -00100                |                          | VDDO = 3.3V                                          | -       | 17.3    | -       |              |

|                       | LVCMOS Output Impedance  | VDDO = 2.5V.                                         | -       | 19.5    | -       | Ω            |

|                       |                          | VDDO = 1.8V                                          | -       | 17.6    | -       |              |

<sup>1.</sup> When used as clock input.

## 2. Specifications

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the RC310xxB at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

## 2.1 Absolute Maximum Ratings

**Table 7. Absolute Maximum Ratings**

| Symbol          | Parameter                             | Conditions                                   | Minimum | Maximum               | Unit |

|-----------------|---------------------------------------|----------------------------------------------|---------|-----------------------|------|

| V <sub>DD</sub> | Supply Voltage with respect to Ground | Any VDD pin                                  | -0.5    | 3.63                  | V    |

|                 |                                       | XIN_REFIN, XOUT_REFINb [2]                   | -0.5    | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IN</sub> | Input Voltage <sup>[1]</sup>          | CLKIN[1:0]_GPI[1:0],<br>CLKIN[1:0]b_GPI[3:2] | -0.5    | V <sub>DD</sub> + 0.3 | V    |

|                 |                                       | GPIO[4:0] used as inputs                     | -0.5    | V <sub>DD</sub> + 0.3 | V    |

|                 |                                       | SCL_SCLK, SDA_nCS                            | -0.5    | 3.63                  | V    |

| I <sub>IN</sub> | Input Current                         | CLKIN[1:0]_GPI[1:0],<br>CLKIN[1:0]b_GPI[3:2] | -       | ±50                   | mA   |

|                 |                                       | OUT[11:0], OUT[11:0]b                        | -       | 30                    | mA   |

|                 | Output Current - Continuous           | GPIO[4:0] used as outputs,<br>SDA_nCS        | -       | 25                    | mA   |

| Гоит            |                                       | OUT[11:0], OUT[11:0]b                        | -       | 60                    | mA   |

|                 | Output Current - Surge                | GPIO[4:0] used as outputs,<br>SDA_nCS        | -       | 50                    | mA   |

| T <sub>J</sub>  | Maximum Junction Temperature          | -                                            | -       | 150                   | °C   |

| T <sub>S</sub>  | Storage Temperature                   | Storage Temperature                          | -65     | 150                   | °C   |

| ESD             | Human Body Model                      | JESD22-A114 (JS-001) Classification          | -       | 2000                  | V    |

| ESD             | Charged Device Model                  | JESD22-C101 Classification                   | -       | 500                   | V    |

<sup>1.</sup> VDD refers to the VDD pin that supplies the particular input. To determine to which VDD pin the specification applies, see Table 46.

<sup>2.</sup> This limit only applies when XIN\_REFIN/XOUT\_REFINb are configured as an "Input Buffer" for use with an external oscillator. No limit is implied when connected directly to a crystal.

#### 2.2 Recommended Operating Conditions

Table 8. Recommended Operating Conditions [1][2]

| Symbol          | Parameter                                                      | Conditions                                                                           | Minimum | Typical | Maximum | Unit |

|-----------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------|---------|---------|---------|------|

| TJ              | Maximum Junction<br>Temperature                                | -                                                                                    | -       | -       | 125     | °C   |

| T <sub>A</sub>  | Ambient Operating temperature                                  | -                                                                                    | -40     | -       | 85      | °C   |

|                 | Supply Voltage with respect to Ground                          | Any VDD pin, 1.8V supply                                                             | 1.71    | 1.8     | 1.89    | V    |

| $V_{DDx}$       |                                                                | Any VDD pin, 2.5V supply                                                             | 2.375   | 2.5     | 2.625   | V    |

|                 |                                                                | Any VDD pin, 3.3V supply                                                             | 3.135   | 3.3     | 3.465   | V    |

| t <sub>PU</sub> | Power-up time for all VDDs to reach minimum specified voltage. | Power ramps must be monotonic. For more considerations, see Application Information. | 0.2     | -       | 5       | ms   |

<sup>1.</sup> All electrical characteristics are specified over Recommended Operating Conditions unless noted otherwise.

#### 2.3 Electrical Characteristics

Table 9. PCle Refclk Phase Jitter, Clock Generator Mode, VDDO = 1.8V/2.5V/3.3V [1][2]

| Symbol                                                                                                                                                                                                             | Parameter                    | Condition                               | Typical | Maximum | PCIe Limit         | Unit   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------|---------|---------|--------------------|--------|

| t <sub>jphPCleG1-CC</sub>                                                                                                                                                                                          | PCIe Gen1 (2.5 GT/s)         |                                         | 1821    | 4450    | 86,000             | fs p-p |

| 4                                                                                                                                                                                                                  | PCIe Gen2 Hi Band (5.0 GT/s) |                                         | 157     | 382     | 3,100              |        |

| tjphPCleG1-CC  tjphPCleG2-CC tjphPCleG3-CC tjphPCleG4-CC tjphPCleG6-CC tjphPCleG7-CC tjphPCleG1-CC tjphPCleG2-CC tjphPCleG3-CC tjphPCleG3-CC tjphPCleG3-CC tjphPCleG3-CC tjphPCleG4-CC tjphPCleG6-CC tjphPCleG6-CC | PCIe Gen2 Lo Band (5.0 GT/s) | Clock Generator Mode                    | 60      | 241     | 3,000              |        |

| t <sub>jphPCleG3-CC</sub>                                                                                                                                                                                          | PCIe Gen3 (8.0 GT/s)         | GT/s) Common Clocked (CC)  Architecture | 51      | 120     | 1,000              |        |

| t <sub>jphPCleG4-CC</sub>                                                                                                                                                                                          | PCIe Gen4 (16.0 GT/s)        |                                         | 51      | 120     | 500 [3]            | fs RMS |

| t <sub>jphPCleG5-CC</sub>                                                                                                                                                                                          | PCIe Gen5 (32.0 GT/s)        | SSC = -0% (off)                         | 19      | 46      | 150 <sup>[4]</sup> | -      |

| t <sub>jphPCleG6-CC</sub>                                                                                                                                                                                          | PCIe Gen6 (64.0 GT/s)        |                                         | 12      | 29      | 100 [5]            |        |

| t <sub>jphPCleG7-CC</sub>                                                                                                                                                                                          | PCIe Gen7 (64.0 GT/s)        |                                         | 8       | 20      | 67 <sup>[6]</sup>  |        |

| t <sub>jphPCleG1-CC</sub>                                                                                                                                                                                          | PCIe Gen1 (2.5 GT/s)         |                                         | 4190    | 6910    | 86,000             | fs p-p |

|                                                                                                                                                                                                                    | PCIe Gen2 Hi Band (5.0 GT/s) | /s)                                     | 371     | 590     | 3,100              |        |

| <sup>l</sup> jphPCleG2-CC                                                                                                                                                                                          | PCIe Gen2 Lo Band (5.0 GT/s) |                                         | 131     | 279     | 3,000              |        |

| t <sub>jphPCleG3-CC</sub>                                                                                                                                                                                          | PCIe Gen3 (8.0 GT/s)         | Clock Generator Mode, CC Architecture   | 123     | 199     | 1,000              |        |

| t <sub>jphPCleG4-CC</sub>                                                                                                                                                                                          | PCIe Gen4 (16.0 GT/s) [7]    | SSC = -0.5%                             | 123     | 199     | 500                | fs RMS |

| t <sub>jphPCleG5-CC</sub>                                                                                                                                                                                          | PCIe Gen5 (32.0 GT/s)        |                                         | 48      | 77      | 150                |        |

| t <sub>jphPCleG6-CC</sub>                                                                                                                                                                                          | PCIe Gen6 (64.0 GT/s)        |                                         | 28      | 47      | 100                |        |

| t <sub>jphPCleG7-CC</sub>                                                                                                                                                                                          | PCIe Gen7 (64.0 GT/s)        |                                         | 20      | 33      | 67                 |        |

<sup>2.</sup> All conditions in this table must be met to guarantee device functionality and performance.

Table 9. PCIe Refclk Phase Jitter, Clock Generator Mode, VDDO = 1.8V/2.5V/3.3V (Cont.)[1][2]

| Symbol                    | Parameter              | Condition                                                                                                     | Typical | Maximum | PCIe Limit | Unit   |

|---------------------------|------------------------|---------------------------------------------------------------------------------------------------------------|---------|---------|------------|--------|

| t <sub>jphPCleG2-IR</sub> | PCIe Gen2 (5.0 GT/s)   |                                                                                                               | 159     | 441     |            |        |

| t <sub>jphPCleG3-IR</sub> | PCIe Gen3 (8.0 GT/s)   | Clock Generator Mode, Independent Reference No Spread (IR-SRNS) Architecture, SSC = 0%  Clock Generator Mode, | 60      | 158     |            |        |

| t <sub>jphPCleG4-IR</sub> | PCIe Gen4 (16.0 GT/s)  |                                                                                                               | 62      | 164     |            |        |

| t <sub>jphPCleG5-IR</sub> | PCIe Gen5 (32.0 GT/s)  | , , ,                                                                                                         | 16      | 41      |            |        |

| t <sub>jphPCleG6-IR</sub> | PCIe Gen6 (64.0 GT/s)  | SSC = 0%                                                                                                      | 12      | 33      |            |        |

| t <sub>jphPCleG7-IR</sub> | PCIe Gen7 (128.0 GT/s) |                                                                                                               | 9       | 23      |            |        |

| t <sub>jphPCleG2-IR</sub> | PCIe Gen2 (5.0 GT/s)   | Clock Generator Mode,                                                                                         | 1322    | 1382    |            |        |

| t <sub>jphPCleG3-IR</sub> | PCIe Gen3 (8.0 GT/s)   |                                                                                                               | 481     | 499     | [8]        | fs RMS |

| t <sub>jphPCleG4-IR</sub> | PCIe Gen4 (16.0 GT/s)  | Separate Spread (IR-SRIS) Architecture,                                                                       | 315     | 342     |            |        |

| t <sub>jphPCleG5-IR</sub> | PCIe Gen5 (32.0 GT/s)  | Clock Generator Mode,                                                                                         | 77      | 128     |            |        |

| t <sub>jphPCleG6-IR</sub> | PCIe Gen6 (64.0 GT/s)  | , ,                                                                                                           | 61      | 66      |            |        |

| t <sub>jphPCleG7-IR</sub> | PCIe Gen7 (128.0 GT/s) | Clock Generator Mode, IR-SRIS Architecture, SSC = -0.15%                                                      | 31      | 36      |            |        |

- 1. The Refclk jitter is measured after applying the filter functions found in the *PCI Express Base Specification 7.0, version 0.7*. For the exact measurement setup, see Test Loads. The worst case results for each data rate are summarized in this table. Equipment noise is removed from all measurements.

- 2. Jitter measurements are made with a capture of at least 100,000 clock cycles captured by a real-time oscilloscope (RTO) with a sample rate of 20GS/s or greater. Broadband oscilloscope noise must be minimized in the measurement. The measured PP jitter is used (no extrapolation) for RTO measurements. Alternately, jitter measurements can be made with a Phase Noise Analyzer (PNA) extending (flat) and integrating and folding the frequency content up to an offset from the carrier frequency of at least 200MHz (at 300MHz absolute frequency) below the Nyquist frequency. For PNA measurements for the 2.5GT/s data rate, the RMS jitter is converted to peak-to-peak jitter using a multiplication factor of 8.83.

- 3. Note that 0.7ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 4. Note that 0.25ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 5. Note that 0.15ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 6. Note that 0.10ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 7. SSC spurs from the fundamental and harmonics are removed up to a cutoff frequency of 2MHz taking care to minimize removal of any non-SSC content

- 8. The *PCI Express Base Specification 7.0, version 0.7* provides the filters necessary to calculate IR jitter values; it does not provide specification limits, therefore, the reference to this footnote. IR values are informative only. A common practice is to split the common clock budget in half. For 16GT/s data rates and above, the user must choose whether to use the output jitter specification, or the input jitter specification, which includes an allocation for the jitter added by the channel. Using 32GT/s, the Refclk output jitter budget is 150fs RMS. One half of the Refclk jitter budget is 106fs RMS. At the clock input, the system must deliver a Refclk with <250fs RMS phase jitter. One half of this value is 177fs RMS. If the clock is placed next to the PCIe device in an IR system, the channel is very short and the user can choose to use this more relaxed value as the jitter limit.

Table 10. PCIe Refclk Additive Phase Jitter, Fanout Mode, VDDO = 1.8V/2,5V/3.3V [1][2]

| Symbol                                                                                                                       | Parameter                         | Condition                                 | Typical | Maximum | PCle Limit [3] | Unit     |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------|---------|---------|----------------|----------|

| t <sub>jphPCleG1-CCadd</sub>                                                                                                 | PCIe Gen1 (2.5 GT/s)              |                                           | 2008    | 3955    | 86,000         | fs p-p   |

|                                                                                                                              | PCIe Gen2 Hi Band (5.0 GT/s)      |                                           | 199     | 361     | 3,100          |          |