# Tsi381<sup>™</sup> PCIe<sup>®</sup> to PCI Bridge Product Brief

# **Features**

### General

- · PCI Express to PCI bridge

- Transparent, Non-transparent, and Opaque modes

- Efficient queuing and buffering for low latency and high throughput

- Compliant with the following specifications:

- PCI Express Base 1.1

- PCI Express PCI/PCI-X Bridge 1.0

- PCI-to-PCI Bridge Architecture 1.2

- PCI Local Bus 3.0

- PCI Bus Power Management Interface 1.2

## **PCI Express**

- x1 lane PCIe Interface

- · Advanced error reporting capability

- · End-to-end CRC check and generation

- Up to four outstanding memory reads

- · ASPM L0 link state power management

- · Legacy interrupt signaling and MSI interrupts

- Hot Plug support

## PCI

- · 32/64-bit addressing and 32-bit data

- Operates at 25, 33, 50, and 66 MHz

- Up to eight outstanding memory reads

- · 3.3V PCI I/Os, 5V tolerant

- Four external PCI masters supported through internal arbiter

- MSI generation and handling using interrupt and GPIO signals

## **Other Features**

- Masquerade mode

- · JTAG IEEE 1149.1, 1149.6 to allow testing of the PCIe Interface

- Four GPIO pins and four interrupt pins that can generate MSIs

- D0, D3 hot, D3 cold power management state support

- 1.2V core power supply

- No power sequencing constraints

- · Packaging:

- 13x13 mm, 144-pin PBGA (10x10 mm option is available; part number Tsi382)

- Pinout and footprint compatible with PLX PEX 8111/8112

- Industrial temperature operating range

- RoHS-compliant package available

## **Device Overview**

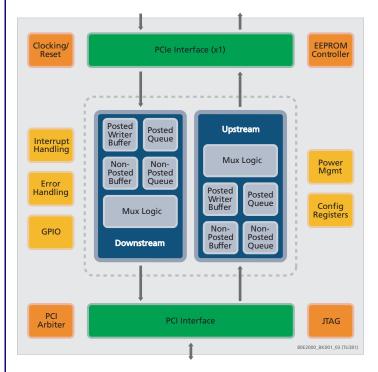

The IDT Tsi381 is a high-performance bus bridge that connects the PCI Express protocol to the PCI bus standard. The Tsi381's PCIe Interface supports a x1 lane PCIe configuration, which enables the bridge to offer exceptional throughput performance of up to 2.5 Gbps per transmit and receive direction.

The device's PCI Interface can operate up to 66 MHz. This interface offers designers extensive flexibility by supporting three types of addressing modes: transparent, opaque, and non-transparent.

#### Simplest, Low-Risk Design

The Tsi381 simplifies board design by using only two power supplies with no power sequencing constraints. Its package is designed to simplify board layout for high reliability and signal integrity. A comprehensive suite of design support resources are also available to aid designers.

Pin compatibility with the PLX PEX8111 and PEX8112 make it easy for designers to migrate current designs to the Tsi381, and thereby bring them to market quickly and with low risk.

#### **Tsi381 Evaluation Board Product Brief**

#### **High Performance**

In addition to low-latency operation and high throughput, the Tsi381 incorporates performance enhancing features, such as short-term caching, that can provide a significant performance boost in many applications.

# Transparent, Non-transparent, and Opaque Bridging

Transparent mode operation is available for efficient, flow through configurations, while non-transparent bridging allows isolation between the Tsi381's PCIe and PCI domains. Non-transparent bridging also enables multi-host systems and is used in applications such as intelligent adapter cards. Opaque mode provides semi-transparent operation for multi-processor configurations and enhanced private device support.

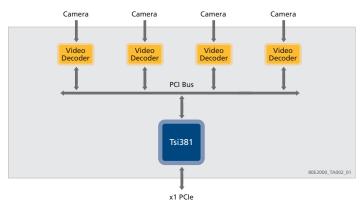

# **Typical Applications**

The Tsi381 is suited to applications that need to bridge PCIe to downstream PCI devices. Its flexibility, high performance, small footprint, and low power consumption, make it ideal for a wide range of applications, including:

- Digital video recorders

- Motherboards (server, SBC, industrial PC)

- PC adapter cards (communications, graphics, imaging, and multimedia)

- · Multifunction printers

- · Line cards and NICs

Figure 2 PC Digital Video Recorder Card Application

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.