## SLG46826-EV Errata Note

## **Abstract**

This document contains the known errata for SLG46826-EV and the recommended workarounds.

## **Contents**

| 1. | Information      | . 1 |

|----|------------------|-----|

| 2. | Errata Summary   | . 1 |

| 3. | Errata Details   | . 2 |

| 4. | Revision History | 10  |

## 1. Information

| Package(s) | 20-pin STQFN: 2 mm x 3 mm x 0.55 mm, 0.4 mm pitch |

|------------|---------------------------------------------------|

|------------|---------------------------------------------------|

## 2. Errata Summary

| Issue #                                                      | Issue Title                                                           |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------|--|

| 1                                                            | Incorrect I2C Reads of the 8-bit Counter Registers                    |  |

| 2                                                            | Non-I2C Compliant ACK Behavior for the NVM and EEPROM Page Erase Byte |  |

| 3                                                            | Leakage from ACMP IN+ to Analog Input Pins                            |  |

| 4 Incorrect 32 mV and 64 mV Hysteresis Operation with ACMPxH |                                                                       |  |

| 5                                                            | Unusable Vref Output in the Range of 32 mV to 192 mV                  |  |

#### 3. Errata Details

## 3.1 Incorrect I<sup>2</sup>C Reads of the 8-bit Counter Registers

#### 3.1.1. Effect

CNT2/DLY2 and CNT4/DLY4

#### 3.1.2. Conditions

The I<sup>2</sup>C latch signal and the clock input occur at about the same time.

#### 3.1.3. Technical Description

Asynchronous interaction between the CNT/DLY clock input and the I<sup>2</sup>C latch signal (generated by an I<sup>2</sup>C read command of the CNT/DLY block's count value) can result in an incorrect I<sup>2</sup>C data read. The CNT/DLY block will count accurately, but the count value transferred into the block's I<sup>2</sup>C read register might be loaded incompletely if the I<sup>2</sup>C latch signal and the clock input occur at about the same time.

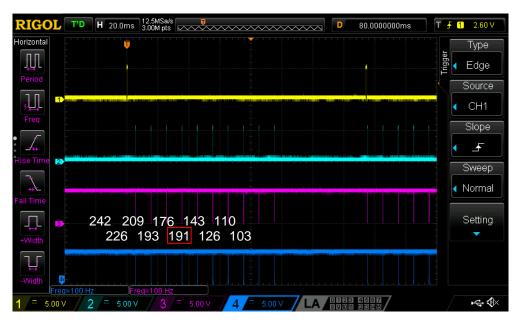

The example data capture below shows ten periodic I<sup>2</sup>C reads of CNT2/DLY2 configured to count down at about 16 clocks per read. The sixth read sample erroneously shows a value greater than that of the fifth. The seventh sample reads as if the previous I<sup>2</sup>C error never occurred - the difference from the fifth sample (176) to the seventh (143) is 33 clocks or 16 clocks + 17 clocks as expected.

Channel 1 (yellow/1st line) - PIN2 (CNT2/DLY2 Out)

Channel 2 (light blue/2nd line) - PIN1 (I2C Read Triggers)

Channel 3 (magenta /3rd line) - PIN8 (I2C SCL)

Channel 3 (dark blue /4th line) - PIN9 (I2C SDA)

Figure 1: Example Data

#### 3.1.4. Workaround

If the possibility of incorrect I<sup>2</sup>C data reads can't be accommodated for by external software checks, one can guarantee proper operation by stopping the CNT/DLY block's clock during I<sup>2</sup>C reads through one of the following methods: by disabling the oscillator block, by reconfiguring the CNT/DLY block's clock source, or by gating an external clock using a LUT (Look Up Table) in the signal matrix. After disabling the CNT/DLY block's clock, the count registers can be read without error. Please note that this workaround will add the I<sup>2</sup>C read and processing time to the counter's overall clock period.

The best workaround depends on the resource constraints of the application. If the oscillator block doesn't clock other logic elements within the design, a matrix output can be used to manually power down the oscillators for the I<sup>2</sup>C read. When the CNT/DLY block's clock source is routed internally from the oscillator block, I<sup>2</sup>C commands can temporarily reconfigure the CNT/DLY block's clock source registers to select "Ext. CLK. (From Matrix)." This action will disable the clock by connecting it to the ground. If the CNT/DLY block is clocked from the signal matrix, the LUT can be used to gate the clock during the I<sup>2</sup>C read.

# 3.2 Non-I<sup>2</sup>C Compliant ACK Behavior for the NVM and EEPROM Page Erase Byte

#### 3.2.1. Effect

**NVM and EEPROM**

#### 3.2.2. Conditions

Erasing the NVM and the EEPROM.

#### 3.2.3. Technical Description

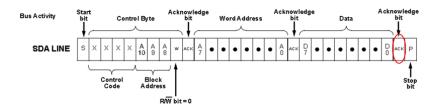

To erase the NVM and the EEPROM, one must perform an I<sup>2</sup>C write to the "Page Erase Byte" located at 0xE3. The ACK bit which follows the "Data" portion of Figure 2 won't comply with standard I<sup>2</sup>C specifications. Please see the ACK bit circled in RED below.

Figure 2: GreenPAK I<sup>2</sup>C Write Frame for Page Erase

The following waveform compares the regular I<sup>2</sup>C ACK behavior (Ref 1 - SCL and Ref 2 - SDA) with the non-compliant ACK behavior (Channel 1 - SCL and Channel 2 - SDA) generated by an I<sup>2</sup>C write to the "Page Erase Byte." During the 9<sup>th</sup> clock cycle, the SLG46827-A does not adhere to the "data hold time" specification by releasing SDA (Channel 2) before the falling edge of the clock pulse on SCL (Channel 1).

Channel 1 (yellow/1st line) - SCL ~ Non-I2C Compliant ACK Behavior (After Data byte)

Channel 2 (light blue/2<sup>nd</sup> line) – SDA ~ Non-I<sup>2</sup>C Compliant ACK Behavior (After Data byte)

Ref 1 (grey/3<sup>rd</sup> line) – SCL ~ Regular I<sup>2</sup>C ACK behavior (Before Data byte) – (5 V/div)

Ref 2 (grey/4<sup>th</sup> line) – SDA ~ Regular I<sup>2</sup>C ACK behavior (Before Data byte) – (5 V/div)

Figure 3: Non-I<sup>2</sup>C Compliant Behavior Oscillogram

Note 1 It should be noted that the NVM and EEPROM erase will execute properly inside the GreenPAK device despite a potential I<sup>2</sup>C NACK. In addition, this behavior only applies to the "Page Erase Byte." All other I<sup>2</sup>C writes won't exhibit this behavior.

On a system level, other I<sup>2</sup>C devices might interpret this non-compliant ACK as an additional STOP and START condition. By definition, a START condition occurs when SCL is HIGH and SDA transitions from HIGH to LOW. A STOP condition occurs when SCL is HIGH and SDA goes from LOW to HIGH. After the 9<sup>th</sup> clock cycle, the MCU should generate the final STOP condition to indicate the end of the transmission to all I<sup>2</sup>C slaves on the bus.

#### 3.2.4. Workaround

No workaround is required for the GreenPAK device as the NVM and EEPROM erase operations will execute properly. For verification, one can perform an I<sup>2</sup>C read of the erased pages. Excluding protected pages, all erased NVM and EEPROM registers should be cleared.

Adjust the MCU's I<sup>2</sup>C firmware to catch and ignore a "NACK" from the GreenPAK device when the "Page Erase Byte" is addressed. In light of the additional STOP and START conditions, the behavior of other I<sup>2</sup>C slaves on the same bus should be evaluated.

## 3.3 Leakage from ACMP IN+ to Analog Input Pins

#### 3.3.1. Effect

IO11/12/13/14, ACMP0/1H, ACMP2/3L

#### 3.3.2. Conditions

Multiple input sources are connected to the ACMP IN+ port simultaneously.

#### 3.3.3. Technical Description

When configured in "Analog IO" mode, IO11/12/13/14 can experience abnormal leakage behavior. This behavior occurs when multiple input sources are simultaneously connected to the ACMP IN+ port. Each of the 4 ACMPs has an input MUX which selects the IN+ source for the comparator. The MUX options are shown in Table 1.

**Table 1: ACMP Input Options**

| ACMP IN+ MUX Options |                        |  |  |

|----------------------|------------------------|--|--|

| ACMP0H               | IO14 Buffered IO14 VDD |  |  |

| ACMP IN+ MUX Options |                                          |  |  |  |  |

|----------------------|------------------------------------------|--|--|--|--|

| ACMP1H               | IO13 Buffered IO13 ACMP0H IN+ source     |  |  |  |  |

| ACMP2L               | IO12 ACMP0H IN+ source ACMP1H IN+ source |  |  |  |  |

| ACMP3L               | IO11 ACMP2L IN+ source Vref0 output      |  |  |  |  |

In the GreenPAK Designer, the input source is selected by the IN+ source dropdown within the ACMP's properties window. When an input source is selected and the ACMP is enabled, an analog switch connects the source to the ACMP's IN+ port. If multiple sources are connected to the ACMP's IN+ port, there will be leakage between the sources.

The IOs shown above can be repurposed as Digital IOs if the ACMPs are disabled or if another input source is selected for the ACMP by the IN+ input MUX. Whenever an IO input mode is configured as an "Analog IO" in accordance with the register definition below, the IO will be connected to the ACMP's IN+ port through an internal switch. This can create a leakage scenario if the ACMP is enabled and connected to another input source.

**Table 2: IO Input Mode Configurations**

| Byte | Register Bit | Signal Function          | Register Bit Definition                                                   |  |  |

|------|--------------|--------------------------|---------------------------------------------------------------------------|--|--|

|      | IO11         |                          |                                                                           |  |  |

|      | 896          | Input Mode Configuration | 00: Digital without Schmitt Trigger                                       |  |  |

| 70   | 897          |                          | 01: Digital with Schmitt Trigger 10: Low Voltage Digital In 11: Analog IO |  |  |

|      | IO12         |                          |                                                                           |  |  |

|      | 904          | Input Mode Configuration | 00: Digital without Schmitt Trigger                                       |  |  |

| 71   | 905          |                          | 01: Digital with Schmitt Trigger 10: Low Voltage Digital In 11: Analog IO |  |  |

|      | IO13         |                          |                                                                           |  |  |

|      | 912          | Input Mode Configuration | 00: Digital without Schmitt Trigger                                       |  |  |

| 72   | 913          |                          | 01: Digital with Schmitt Trigger 10: Low Voltage Digital In 11: Analog IO |  |  |

| IO14 |              |                          |                                                                           |  |  |

|      | 920          |                          | 00: Digital without Schmitt Trigger                                       |  |  |

| 73   | 921          | Input Mode Configuration | 01: Digital with Schmitt Trigger 10: Low Voltage Digital In 11: Analog IO |  |  |

There are 3 standard IO settings that use the "Analog IO" configuration: Analog input/output, Digital input/output (with "Input mode" set to Analog input), and Digital output (with "Output mode" set to 1/2/4x 3-State Output). The first setting is reserved for use with the ACMP, but the other two settings use the "Analog IO" configuration as a high-impedance input. It is important to note that these input modes won't be high impedance if the ACMP is enabled and connected to another input source. When two signals are connected to the ACMP's IN+ source, the voltage level at the ACMP's input depends upon the drive strength of the competing sources.

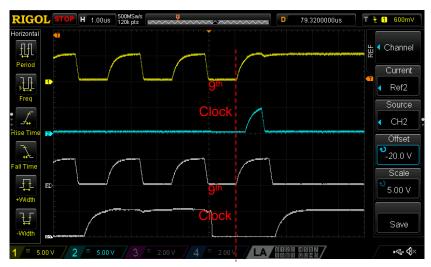

Figure 4 shows the GreenPAK configured with IO14 as a Digital IO with a 1 M $\Omega$  pull-down resistor. Since the OE pin is connected to 0 V, this pin is acting as an "Analog IO." As seen in Table 1, IO14 and V<sub>DD</sub> are both input options for ACMP0H. In this example, IO0 is being used as a digital input to enable and disable the ACMP.

Figure 4: GreenPAK Input Structure Test Schematic

Figure 5 shows that IO14 in analog input mode is pulled HIGH by the V<sub>DD</sub> signal whenever the ACMP is enabled despite having an internal pull-down resistor. This behavior is caused by an internal connection between V<sub>DD</sub> and IO14. Similar behavior can be reproduced when one ACMP's IN+ port is connected to another ACMP's IN+ port.

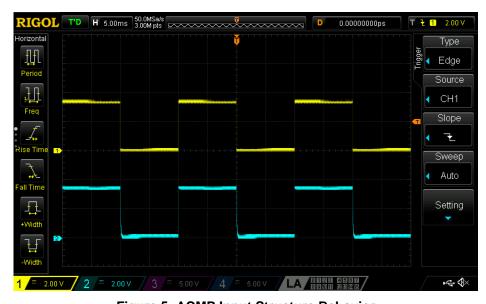

CH1 (Yellow): ACMP PWR UP (IO0)

CH3 (Light Blue): Digital IO w/ Analog Input Mode Configuration (IO14)

Figure 5: ACMP Input Structure Behavior

#### 3.3.4. Workaround

If an ACMP is disabled, the IO associated with that ACMP will operate as expected under any configuration. Please reference Table 1 for more information regarding which IOs are associated with which ACMPs.

When the ACMPs are enabled, it is possible to inadvertently connect multiple ACMP sources together through the input structure. This is possible when the ACMP input is connected to a source other than its analog IO and that IO's input mode is set to "Analog IO".

There is no workaround for this behavior. With this in mind, the IOs should not be used as digital IOs (with "Input mode" set to Analog input) or as digital outputs (with "Output mode" set to 1/2/4x 3-State Output) if the respective ACMP is enabled and connected to another input source.

## 3.4 Incorrect 32 mV and 64 mV Hysteresis Operation with ACMPxH

#### 3.4.1. Effect

ACMP0H and ACMP1H

#### 3.4.2. Conditions

ACMPxH with 32 mV hysteresis, V<sub>DD</sub> = 4.0 V or higher, Vref ranges 0.832 V to 1.024 V, and 1.312 V to 1.44 V.

#### 3.4.3. Technical Description

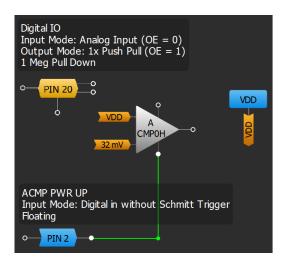

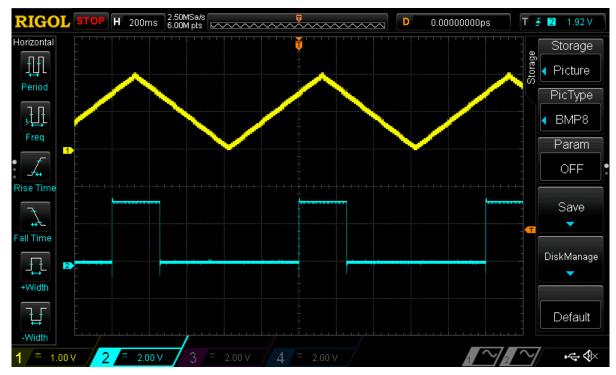

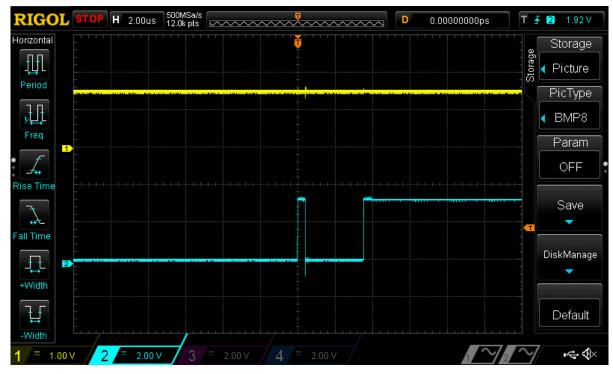

If using ACMPxH with 32 mV hysteresis, ACMPxH output could be glitching when ACMPxH positive input (IN+) is close to the negative input (IN-). It can happen when  $V_{DD}$  = 4.0 V or higher and Vref ranges from 0.832 V to 1.024 V, and 1.312 V to 1.44 V.

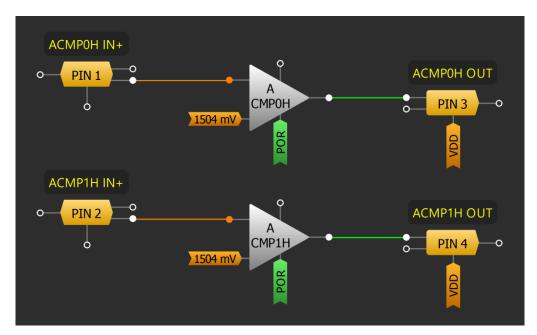

Figure 6: Testing Design

Channel (yellow/top line) - PIN#1 (ACMP0H IN+)

Channel (light blue/top line) - PIN#3 (ACMP0H OUT)

1. Waveform at Vref = 1504 mV, hysteresis is equal to 32 mV.

Figure 7: ACMP Output during Glitching

2. Waveform at Vref = 1504 mV, hysteresis is equal to 32 mV (zoomed rising edge).

Figure 8: Zoomed ACMP Output during Glitching

## 3.4.4. Workaround

- Use the deglitch filter connected to the ACMPxH output.

- Avoid conditions described in paragraph 3.4.2.

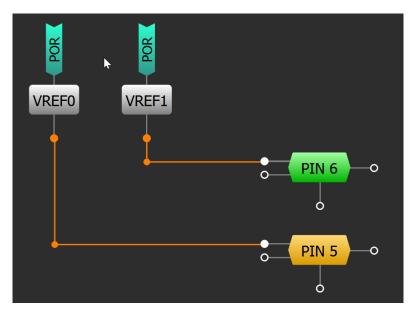

## 3.5 Unusable Vref Output in the Range of 32 mV to 192 mV

#### 3.5.1. Effect

**Both Vref Outputs**

#### 3.5.2. Conditions

Vref output set to any value in the range of 32 mV to 192 mV and connected to the analog input/output PIN.

## 3.5.3. Technical Description

If using Vref output in the range of 32 mV to 192 mV connected to the analog input/output PIN, the Vref accuracy is very low due to the built-in buffer's offset.

Figure 9: Testing Design

## 3.5.4. Workaround

There is no workaround.

## 4. Revision History

| Revision | Date          | Description      |

|----------|---------------|------------------|

| 1.00     | June 11, 2024 | Initial release. |