## **Description**

The 8Axxxx 144BGA EVK is designed to help customers evaluate IDT ClockMatrix devices. This document discusses the following about the EVK:

- Introduces the board and its power supply and jumper settings

- Describes the input and output connectors for normal operation

- Explains how to bring up the board using the Timing Commander software GUI

- Discusses how to configure and program the board to generate standard-compliant frequencies

#### **Kit Contents**

- 8A34xxx 144BGA Evaluation Board

- USB Type A cable

## Requirements

- IDT Timing Commander Software Installed (available at www.idt.com/timingcommander)

- ClockMatrix GUI (available at www.idt.com/clockmatrix)

- USB 2.0 or USB 3.0 interface

- Windows XP SP3 or later

- Processor: Minimum 1GHz

- Memory: Minimum 512MB; recommended 1GB

- Available disk space: Minimum 600MB (1.5GB 64-bit); recommended 1GB (2GB 64-bit)

- Network access during installation if the .NET framework is not currently installed on the system

### 8A3xxxx 144BGA EVK Board

#### **Important Notes**

#### **Disclaimer**

Integrated Device Technology, Inc. and its affiliated companies (herein referred to as "IDT") shall not be liable for any damages arising out of defects resulting from

- (i) delivered hardware or software

- (ii) non-observance of instructions contained in this manual and in any other documentation provided to user, or

- (iii) misuse, abuse, use under abnormal conditions, or alteration by anyone other than IDT.

TO THE EXTENT PERMITTED BY LAW, IDT HEREBY EXPRESSLY DISCLAIMS AND USER EXPRESSLY WAIVES ANY AND ALL WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, INCLUDING, WITHOUT LIMITATION, IMPLIED WARRANTIES OF MERCHANTABILITY AND OF FITNESS FOR A PARTICULAR PURPOSE, STATUTORY WARRANTY OF NON-INFRINGEMENT, AND ANY OTHER WARRANTY THAT MAY ARISE BY REASON OF USAGE OF TRADE, CUSTOM, OR COURSE OF DEALING.

Important Equipment Warning: Ensure the correct connection of all cables. Supplying the board using the wrong polarity could result in damage to the board and/or the equipment. Check that all jumpers have been removed from the board before applying power.

### **Contents**

| 1. | Usa                                                         | ge Guide                                          | 4  |

|----|-------------------------------------------------------------|---------------------------------------------------|----|

|    | 1.1                                                         | Board Overview                                    | 4  |

|    | 1.2                                                         | Board Power Supply                                | 5  |

|    | 1.3                                                         | Voltage Selection Jumpers                         | 5  |

|    | 1.4                                                         | GPIO Switches, LEDs, and Test Points              | 6  |

|    | 1.5                                                         | USB Jack                                          | /  |

|    | 1.6                                                         | Onboard EEPROM                                    | 7  |

| 2. | Working with Timing Commander™ for Programing/Configuration |                                                   |    |

|    | 2.1                                                         | Default Operation                                 | 8  |

|    | 2.2                                                         | Using Timing Commander to Control the Board       | 9  |

|    | 2.3                                                         | Output Terminations and Rework to Take 1PPS Input | 15 |

| 3. | How                                                         | to Upgrade the Firmware                           | 16 |

|    | 3.1                                                         | Upload Firmware to the RAM                        |    |

|    | 3.2                                                         | Upload Firmware into the EEPROM                   | 18 |

|    | 3.3                                                         | Verify the EEPROM Programming                     | 19 |

| 4. | Sche                                                        | ematics                                           | 20 |

| 5. | Orde                                                        | ering Information                                 | 29 |

| 6. | Revi                                                        | sion History                                      | 29 |

# **List of Figures**

| Figure 1.  | Overview of 144BGA ClockMatrix Evaluation Board            | 4  |

|------------|------------------------------------------------------------|----|

| Figure 2.  | Overview of 144BGA ClockMatrix Evaluation Board            | 5  |

| Figure 3.  | GPIO Setting and Status Display Area                       |    |

| Figure 4.  | Board Setting for Default Operation                        | 8  |

| Figure 5.  | Starting Up Timing Commander GUI                           | 9  |

| Figure 6.  | Selecting 8A34001 using Personality File v4.6.             | 10 |

| Figure 7.  | Timing Commander GUI with a Settings File Opened           | 11 |

| Figure 8.  | Setting I <sup>2</sup> C for Connecting the Board with GUI | 12 |

| Figure 9.  | A Green Band appears when a Valid Connection is Made       | 12 |

| Figure 10. | Firmware Version Mismatch Warning Message                  | 13 |

| Figure 11. | Reading Firmware Version                                   | 13 |

| Figure 12. | Read Firmware Version of ClockMatrix Chip                  | 14 |

| Figure 13. | AC Coupling and Terminations for Input Clock               | 15 |

| Figure 14. | Configuring CLK0 as CMOS to Receive a 1PPS Input           | 15 |

| List o     | of Tables                                                  |    |

| Table 1.   | GPIO Settings                                              | 6  |

| Tahla 2    | FEDDOM I/C Connections                                     | 7  |

## 1. Usage Guide

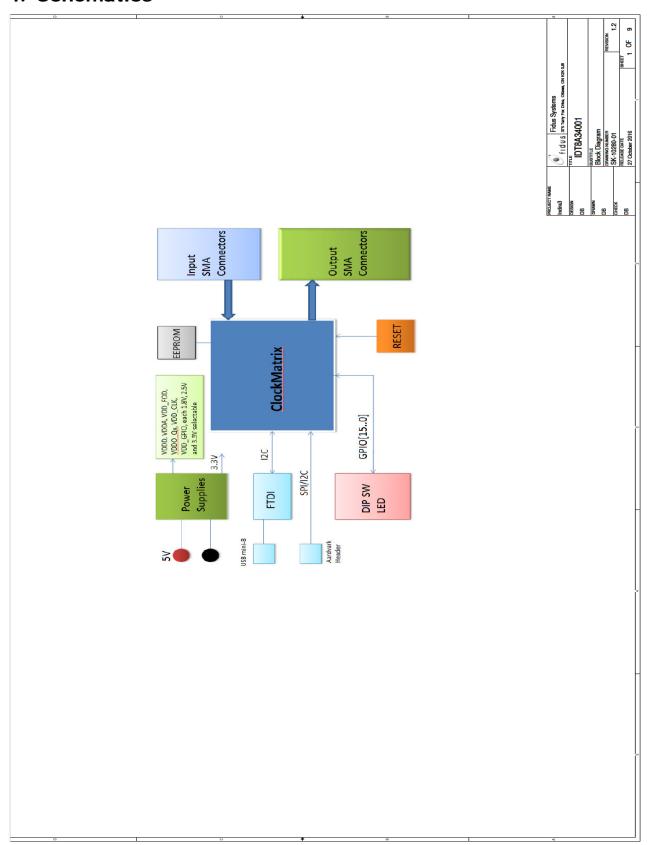

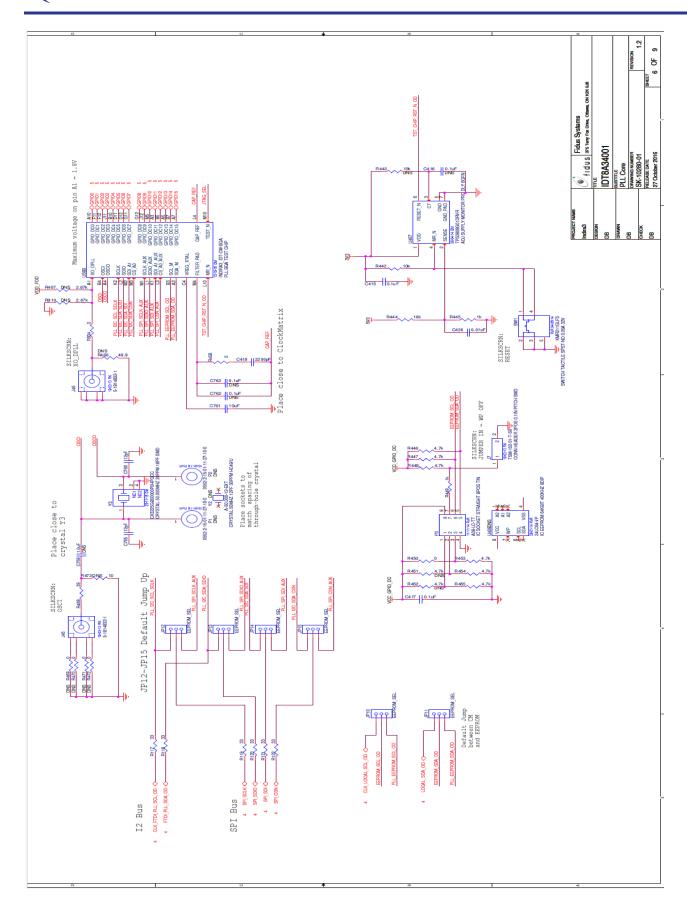

#### 1.1 Board Overview

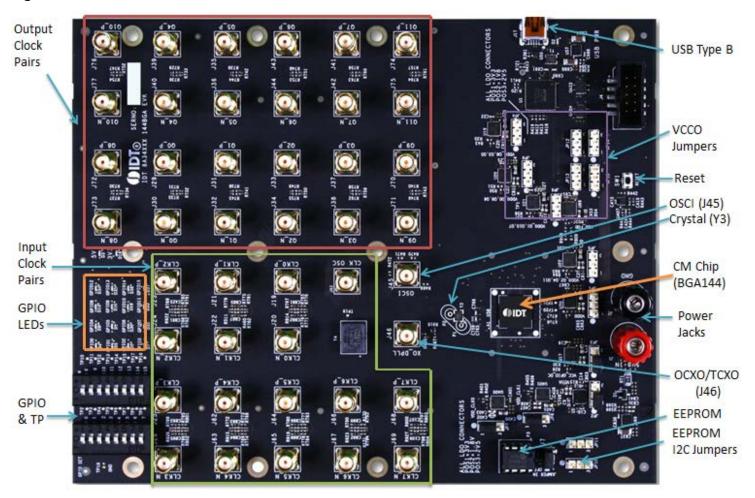

The following diagram identifies various components of the board: input and output SMA connectors, power supply jacks, and some jumper settings necessary for the board operations.

Figure 1. Overview of 144BGA ClockMatrix Evaluation Board

Detailed descriptions of the board are as follows.

- Input SMA Connectors There are eight differential inputs labeled CLK0/nCLK0–CLK7/nCLK7. Each input clock can be configured differentially (LVDS, PECL 2.5V, and PECL 3.3V) or in single-ended format (CMOS).

- Output SMA Connectors There are 12 outputs labeled as Q0/nQ0–Q11/nQ11. Each output clock can be configured differentially (LVDS, LVPECL, or user-defined amplitude), or in single-ended format (LVCMOS in-phase or out-of-phase)

- GPIO switch, LEDs, and test points There are 16 GPIOs available. Each GPIO can be set a "low" or "high" level (if input) or displayed with an LED (if output). Some GPIOs are used to set the chip in a certain working condition on power-up. For more information, see GPIO Switches, LEDs, and Test Points.

- USB connector A USB mini-connector connects the evaluation board to a PC for GUI communications. No power is drawn from the USB connector other than to power the FTDI USB chip.

- VCCO voltage selection jumpers Each output voltage can be individually supplied with 1.8V, 2.5V, or 3.3V. These jumpers are used to select the voltage for the output voltages.

- Reset button A small button is used to reset the board.

- OSCI Input connector An SMA connector, J45, can optionally supply a clock signal to overdrive the crystal.

- OCXO/TCXO reference An SMA connector, J46, can supply a local OCXO/TCXO reference as an optional reference for System DPLL.

- Crystal A crystal of various frequencies must be present for board operations. A 3225 footprint is provided for SMT crystals. For easy plug-in of a canned crystal, two through holes are also available.

- EEPROM An SO-8 socket is provided to hold an EEPROM device of compatible package. EEROM is used to store firmware and customer configuration data, if needed.

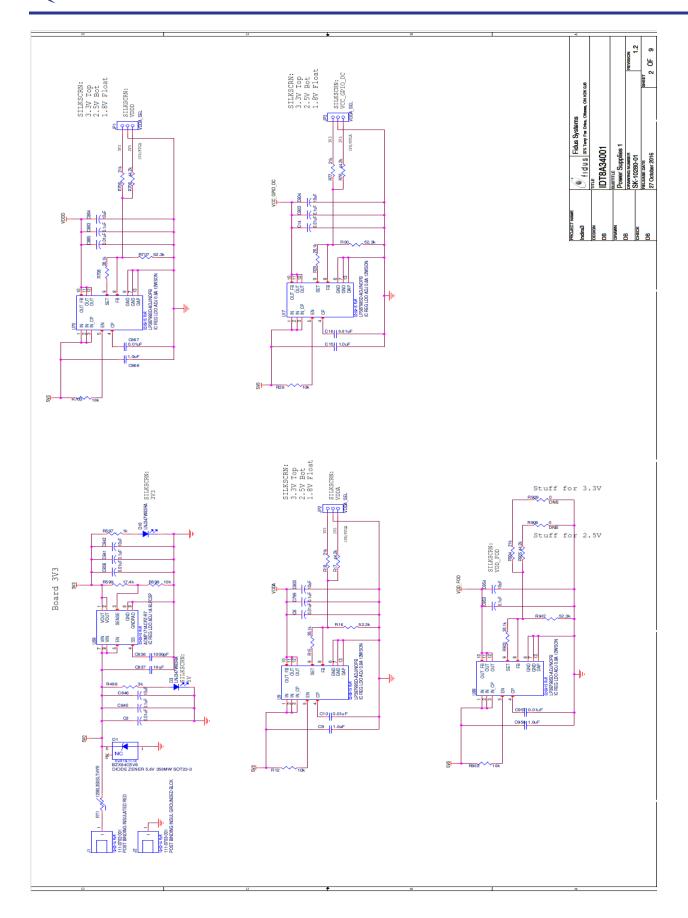

#### 1.2 Board Power Supply

The board uses a single +5V supply for its power supplies. When running the board, set the bench power supply at 5V/2A. The red jack (J1) is positive; the black jack (J2) is the ground.

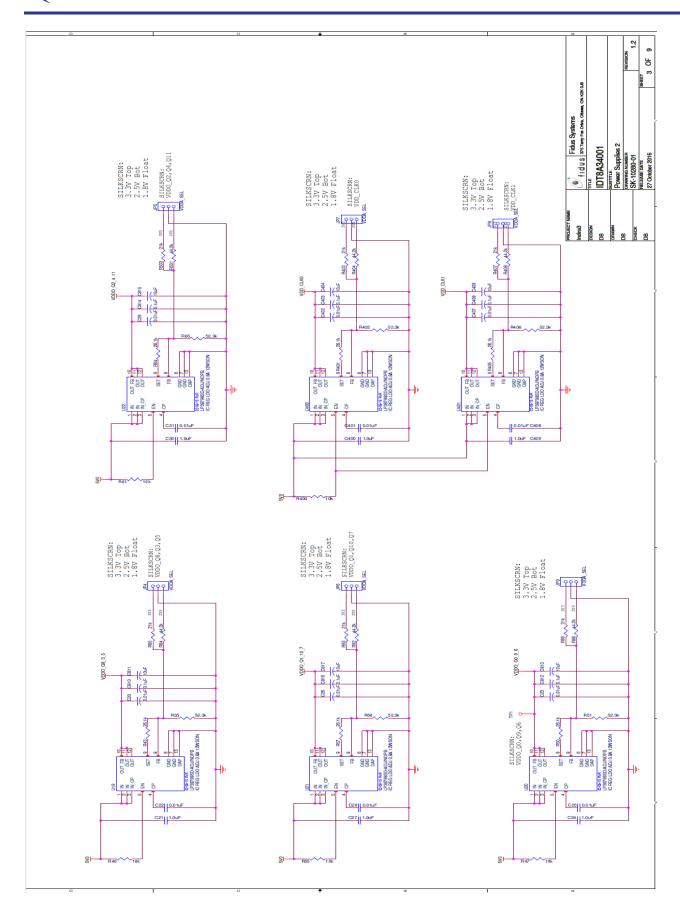

Multiple LDOs are used to generate 3.3V, 2.5V, and 1.8V from the +5V supply.

#### 1.3 Voltage Selection Jumpers

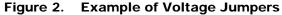

There are nine headers/jumpers to select different voltages for different functional blocks of the chip. Each head is labeled pin 1 and pin 3 – jumping pin 1 and pin 2 will select 3.3V; jumping pin 2 and pin 3 will select 2.5V; no jumper will have 1.8V.

Please see the following example for JP4 and JP9 – JP4 will select 2.5V; JP9 will select 3.3V.

The following list shows which head/jumper is used to select what voltage:

- JP1 VDDD

- JP2 VDDA

- JP3 VCC\_GPIO\_DC

- JP4 VDDO\_Q8\_3\_5

- JP5 VDDO\_Q2\_4\_11

- JP6 VDDO\_1\_10\_7

- JP7 VDD\_CLK0

- JP8 VDD\_CLK1

- JP9 VDDO\_Q0\_9\_6

Important Equipment Warning: VDD\_FOD voltage is selected by resistors R908 and R909. In order to prevent damage to the device, both R908 and R909 should not be stuffed, in which case VDD\_FOD = 1.8V.

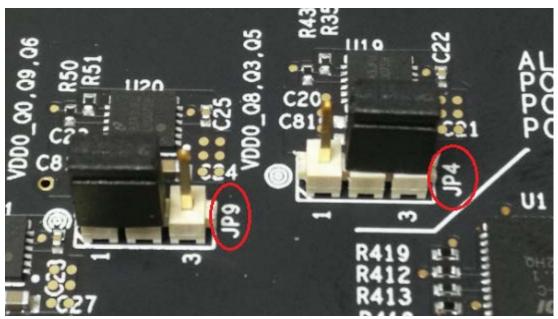

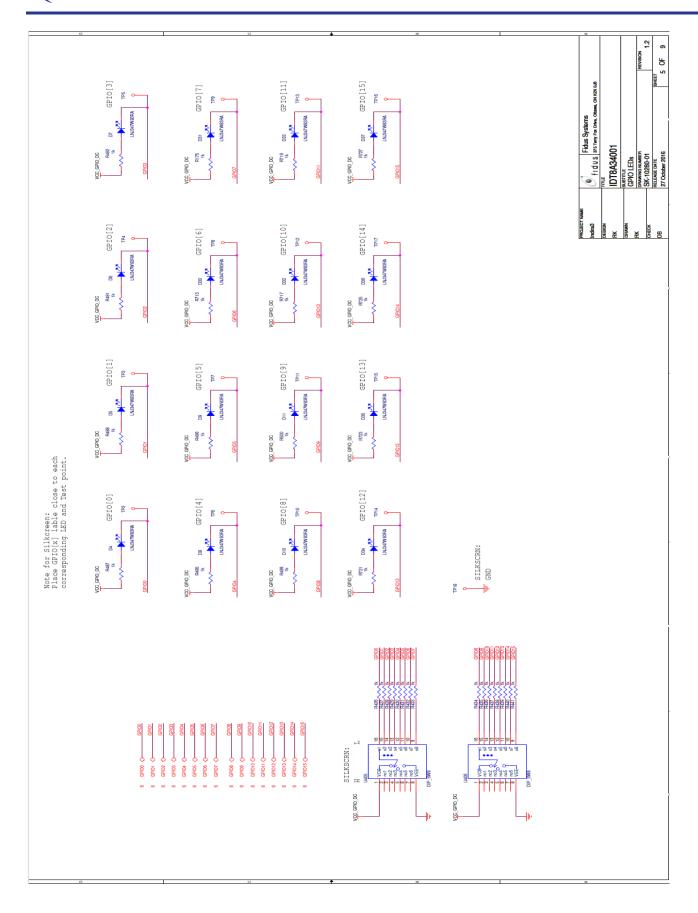

#### 1.4 GPIO Switches, LEDs, and Test Points

Two 8-bit dip switches sets the logic levels for 16 GPIOs. The following table shows the GPIO levels for each setting and the corresponding LED state.

Table 1. GPIO Settings

| Dip Switch Position | GPIO Logic Level                                 | LED                                              |

|---------------------|--------------------------------------------------|--------------------------------------------------|

| Left                | Low                                              | On                                               |

| Center              | High if GPIO is configured as Input              | High if GPIO is configured as Input              |

|                     | High or Low according to the GPIO output setting | High or Low according to the GPIO output setting |

| Right               | High                                             | Off                                              |

Please see the picture and labels in Figure 3.

When the GPIOs are configured as outputs (such as User-Controlled or LOL indicator), the dip switch for the corresponding GPIO should be placed in the center position. The LED will indicate the state of the GPIO.

Figure 3. GPIO Setting and Status Display Area

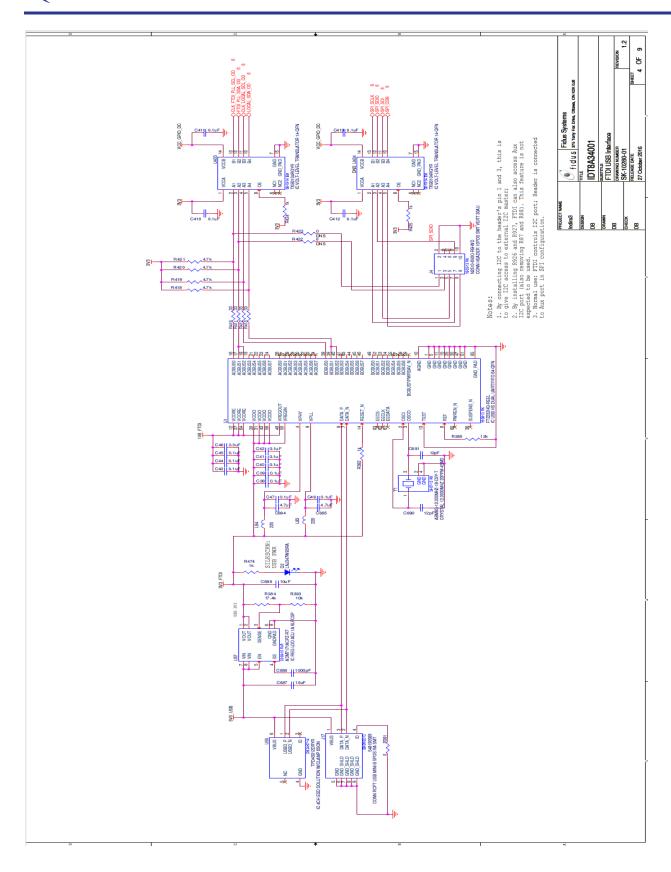

#### 1.5 USB Jack

The board has a USB mini-connector. The other end of the USB cable is a USB Type A connector going to a PC.

#### 1.6 Onboard EEPROM

An onboard EEPROM is used to store device firmware and/or customer's configuration data. There are two headers/jumpers, JP10 and JP11, used to select the I<sup>2</sup>C communication paths for the EEPROM.

Table 2. EEPROM I<sup>2</sup>C Connections

|                              | JP10/JP11        | JP10/JP11          |

|------------------------------|------------------|--------------------|

| Jumper Position              | Both Pin 1 and 2 | Both Pin 2 and 3   |

| EEPROM I <sup>2</sup> C Path | FDTI and EEPROM  | EEPROM and CM Chip |

# 2. Working with Timing Commander™ for Programing/Configuration

The following sections are best cross-referenced with the ClockMatrix GUI Step-by-Step User Guide which is available on www.idt.com.

### 2.1 Default Operation

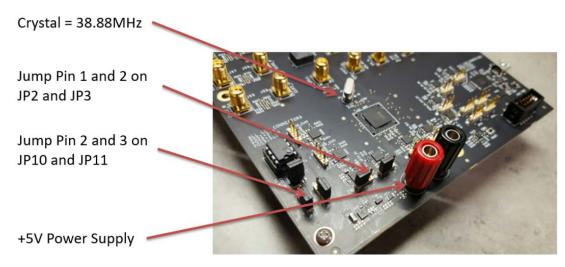

The board can operate off an EEPROM that has stored all information including firmware and a default configuration data. A default operation provides a sanity check on the board before running the board through the IDT Timing Commander. Please set the board in the following default conditions (see Figure 4 for jumper and switch positions).

- Set all the GPIOs to the center position. This will ensure that GPIO8 and GPIO9 are high and that the serial port is configured for I<sup>2</sup>C 1-byte addressing.

- VDDA = 3.3V, VCC\_GPIO\_DC = 3.3V, and VDDO\_Qx = 3.3V

- Crystal frequency = 50MHz

- CLK0 = 25MHz

- EEPROM is connected to ClockMatrix chip through an I<sup>2</sup>C bus by jumping Pin 2 and 3 of JP10 and JP11

With the above default conditions ready, connect the board to the PC using a USB type A to USB mini cable, and power up the board using a single +5V supply. On power-up, the ClockMatrix chip will read its firmware and configuration data from EEPROM and update all registers. When this process is completed, the following frequencies are available:

Q0 = 122.88MHzQ1 = 122.88MHz

Figure 4. Board Setting for Default Operation

Important Equipment Warning: In order to set GPIO8 and GPIO9 to "High", the switches for GPIO8 and GPIO9 must be set either to the "+" (high) position or the center position.

#### 2.2 Using Timing Commander to Control the Board

Once the default operation is successful, complete the following steps to configure and program the ClockMatrix device per your specific application requirements using Timing Commander GUI tools:

- 1. Power up the board and set the main serial port in I<sup>2</sup>C mode by GPIO9 = "high". Set GPIO8 = "High". Connect the board to the PC.

- 2. Start the Timing Commander software. You will see options of "New Setting File" and "Open Setting file". For a new configuration, select "New Setting File".

Figure 5. Starting Up Timing Commander GUI

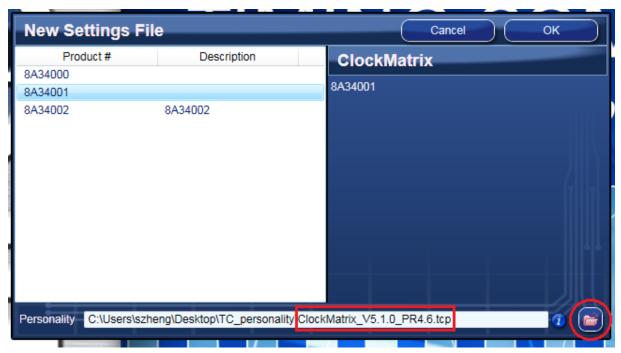

3. After selecting "New Settings File", a device selection window will pop up. In the window, choose the intended device in the list (in this example, 8A34001 is selected). Click the button at the lower right corner of the window (red circle) to browse and select the correct personality file (in this example, personality v4.6 is selected). Click OK.

Figure 6. Selecting 8A34001 using Personality File v4.6

4. The GUI window with the 8A34001 block diagram will open for configurations; or if "Open Settings File" is selected in Step 3, you will be prompted to browse and select an existing .tcs file and the personality file. When the configuration file is open, all configured values will be displayed (see Figure 7).

Figure 7. Timing Commander GUI with a Settings File Opened

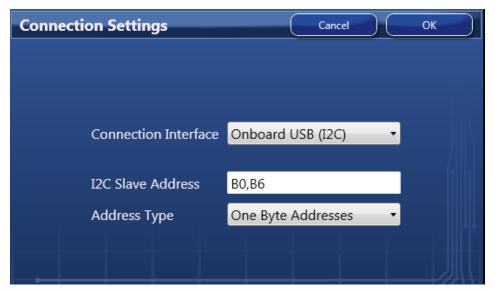

5. In order to connect the board with Timing Commander (PC), click the button (red circle) at the up-right corner of the GUI to set up the communication protocols (see Figure 7).

After I<sup>2</sup>C and one-byte addressing are selected, click OK to close the window.

Figure 8. Setting I<sup>2</sup>C for Connecting the Board with GUI

6. Click on the chip symbol at the upper-right corner to initiate the connection. The connection is valid when a green band appears at the upper-right corner of the window, as shown below.

Figure 9. A Green Band appears when a Valid Connection is Made

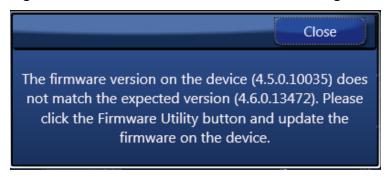

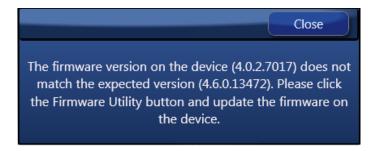

7. If ClockMatrix chip's firmware, or firmware loaded from EEPROM, has a different version from that in the Personality file, a firmware version mismatch warning message will appear. Click "Close" button to close the message window and a connection is made.

Figure 10. Firmware Version Mismatch Warning Message

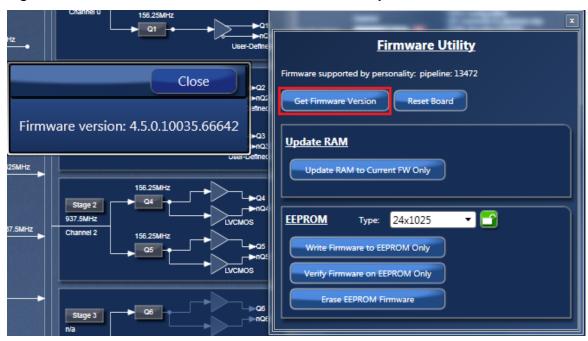

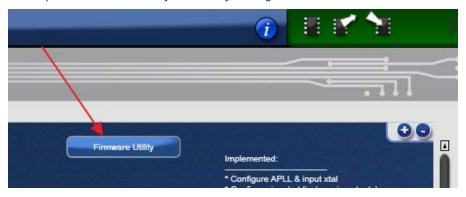

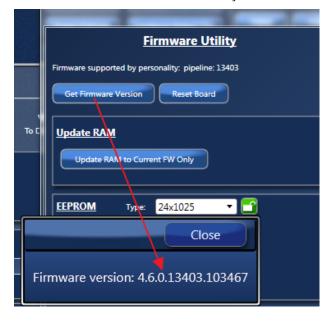

8. Once the connection is made, the firmware version can be read within the GUI. Click the "Firmware Utility" button to bring up the Firmware Utility window, as shown below.

Figure 11. Reading Firmware Version

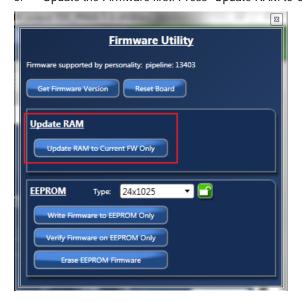

9. Within the Firmware Utility window, click the "Get Firmware Version" button to read the firmware version.

Figure 12. Read Firmware Version of ClockMatrix Chip

10. In the case where the firmware version mismatches each other, a firmware upgrade is necessary to update the chip's firmware. To do so, complete the steps in How to Upgrade the Firmware to update the chip's firmware.

#### 2.3 Output Terminations and Rework to Take 1PPS Input

All outputs are terminated with a  $100\Omega$  resistor across the output pair. This is the recommended termination regardless of the Voffset and Vswing settings. Since the outputs are DC-coupled, they will support a 1PPS output without any need for rework.

Important Equipment Warning: When connecting the outputs to measurement equipment, use a DC-block to ensure that the output operates at its intended V<sub>offset</sub>. Otherwise, the equipment may load the output down and cause degraded performance.

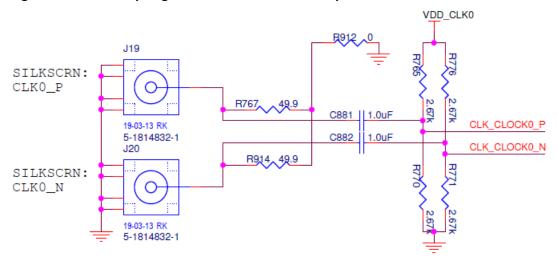

The following rework must be implemented in order to support a 1PPS input clock. All input clocks for this board are ac-coupled and terminated as in the following figure.

Figure 13. AC Coupling and Terminations for Input Clock

For a 1PPS input, a single-ended input with DC-coupling is recommended. As such, the populated AC-coupling capacitor must be removed and the input must be configured as LVCMOS, not differential.

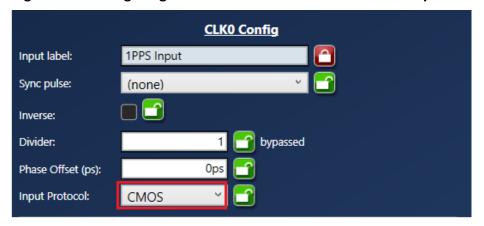

In Figure 13, to make CLK0 supportive of 1PPS input, first configure CLK0 as LVCMOS in Timing Commander (see Figure 14).

Figure 14. Configuring CLK0 as CMOS to Receive a 1PPS Input

2. Once in LVCMOS mode, CLK0\_P and CLK0\_N will be two separate LVCMOS inputs instead of a differential pair. To make CLK0\_P receive a 1PPS input, replace C881 with a 0Ω resistor; and at the same time, remove R765 and R770.

# 3. How to Upgrade the Firmware

# 3.1 Upload Firmware to the RAM

- 1. Connect to the EVK board.

- 2. Power up the board with no EEPROM present. This ensures the firmware is 4.0.2.7017, as displayed in the figure.

- 3. The GUI will indicate that the firmware on the chip does not match the GUI firmware. Press "Close".

4. Open the "Firmware Utility" window by clicking on the button as follows.

5. Update the Firmware first. Press "Update RAM to Current FW Only".

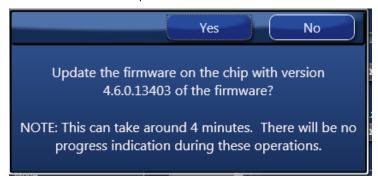

6. In the next window, press "Yes" and wait around 3-4 minutes.

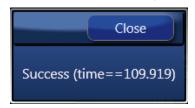

7. Once the firmware is updated, the following window will indicate a successful update. Click "Close".

8. Press "Get Firmware Version" to verify that the RAM was updated correctly, then click "Close".

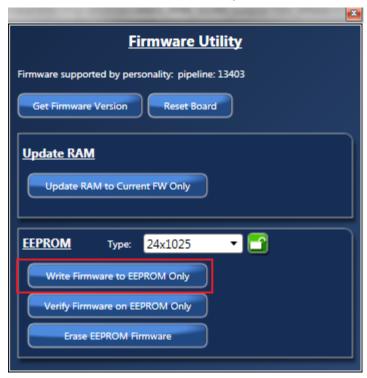

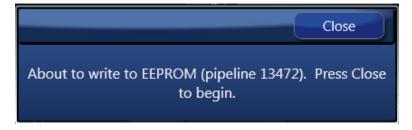

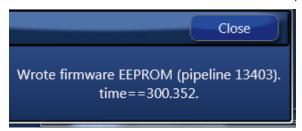

#### 3.2 Upload Firmware into the EEPROM

- 1. Once the firmware has been updated to the chip (steps 1 to 8), install the EEPROM on the EVK board.

- 2. Press "Write Firmware to EEPROM Only".

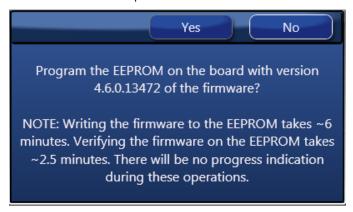

3. In the next window, press "Yes".

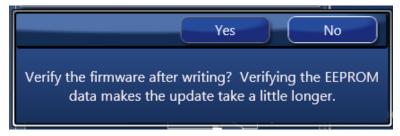

4. When asked to "Verify" the EEPROM, press "No".

5. In the next window, press "Close" to start the EEPROM write.

6. Wait about 5 minutes for the EEPROM write to complete. Click "Close" in the following window.

## 3.3 Verify the EEPROM Programming

- 7. Power cycle the board.

- 8. Disconnect and reconnect to the chip.

- 9. Read back the firmware version to ensure it is correct (see steps 3 to 7).

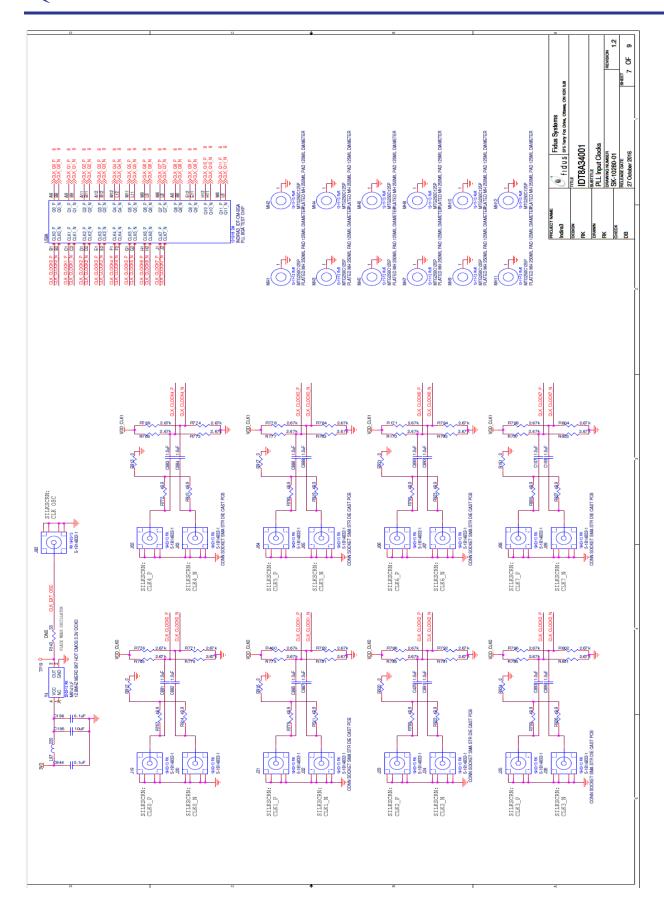

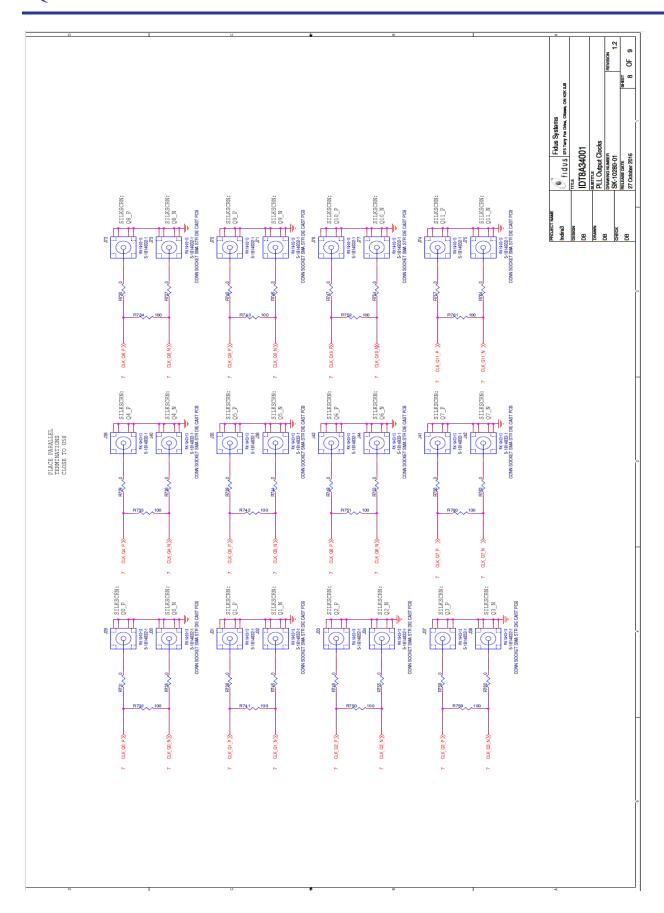

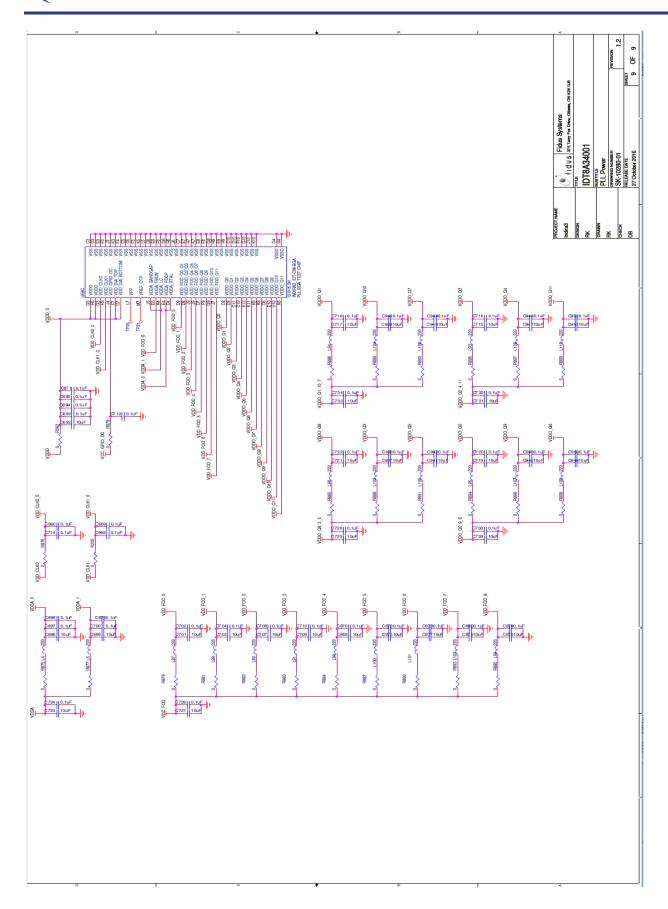

# 4. Schematics

# 5. Ordering Information

| Orderable Part Number | Description                   |

|-----------------------|-------------------------------|

| 8A34001-EVK           | 8A3xxxx 144BGA Evaluation Kit |

# 6. Revision History

| Revision Date    | Description of Change |

|------------------|-----------------------|

| February 6, 2019 | Initial release.      |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.