# In-System Programming Guide

**SLG47004** ISPG-SLG47004

# **Contents**

| Co  | ntents             | 3         |                                                | 2    |  |  |  |

|-----|--------------------|-----------|------------------------------------------------|------|--|--|--|

| Fig | jures.             |           |                                                | 3    |  |  |  |

| Та  | bles               |           |                                                | 3    |  |  |  |

| 1   | Term               | s and De  | finitions                                      | 4    |  |  |  |

| 2   | Intro              | duction   |                                                | 5    |  |  |  |

| 3   | Hard               | ware Req  | uirements                                      | 5    |  |  |  |

|     | 3.1                |           | nd Signals                                     |      |  |  |  |

| 4   | I <sup>2</sup> C S | ignal Spe | ecification                                    | 7    |  |  |  |

|     | 4.1                | Addressi  | ing                                            | 7    |  |  |  |

|     | 4.2 Commands       |           |                                                |      |  |  |  |

|     |                    | 4.2.1     | Write Command                                  | 7    |  |  |  |

|     |                    | 4.2.2     | Verify Command                                 | 8    |  |  |  |

|     |                    | 4.2.3     | Erase Command                                  | 8    |  |  |  |

| 5   | Mem                | ory Spac  | e                                              | . 10 |  |  |  |

|     | 5.1                | Memory    | Map                                            | . 10 |  |  |  |

|     | 5.2                | Pages     |                                                | . 11 |  |  |  |

|     |                    | 5.2.1     | Protection Page                                | . 11 |  |  |  |

|     |                    | 5.2.2     | Service Page                                   | . 13 |  |  |  |

| 6   | Prog               | ramming   | Algorithm for NVM Configuration Register Space | . 14 |  |  |  |

| 7   | Prog               | ramming   | Algorithm for the Emulated EEPROM Space        | . 17 |  |  |  |

| Re  | vision             | History . |                                                | . 19 |  |  |  |

# ISPG-SLG47004

# **SLG47004**

# **Figures**

| Figure 1: STQFN-24 Pin Configuration                                            | . 6<br>. 7<br>. 8<br>. 8 |

|---------------------------------------------------------------------------------|--------------------------|

| Figure 7: I <sup>2</sup> C Address Mapping1                                     |                          |

| Figure 8: Flowchart for Programming NVM without Acknowledge Polling             |                          |

| Figure 9: Flowchart for Programming NVM with Acknowledge Polling                |                          |

| Figure 10: Flowchart for Programming EEPROM without Acknowledge Polling1        |                          |

| Figure 11: Flowchart for Programming Emulated EEPROM with Acknowledge Polling 1 | 18                       |

| Tables                                                                          |                          |

| Table 1: I <sup>2</sup> C Specifications                                        | . 6                      |

| Table 2: ERSR Register Format                                                   |                          |

| Table 3: ERSR Register Bits Function Description                                |                          |

| Table 4: RPR Register Format                                                    |                          |

| Table 5: RPR Register Bits Function Description                                 |                          |

| Table 6: NPR Format                                                             |                          |

| Table 7: NPR Bit Function Description                                           |                          |

| Table 8: WPR Register Format                                                    |                          |

| Table 9: WPR Register Bits Function Description                                 | 12                       |

| Table 10: PRL Register Format                                                   |                          |

| Table 11: PRL Bit Function Description                                          | 13                       |

# 1 Terms and Definitions

ACK Acknowledge Bit

ERSE Erase Enable

ERSR Erase Register

IO Input/Output

IP Intellectual Property

LSB Least Significant Bit

MSB Most Significant Bit

MTP Multi-Time Programmable

NPR Non-Volatile Memory Protection Register

NVM Non-Volatile Memory

PRL Protect Lock Bit

R/W Read/Write

RPR Register Read/Write Protection

SCL I<sup>2</sup>C Clock Input

SDA I<sup>2</sup>C Data Input/Output

WPB Write Protect Block Bits

WPR Write Protection Register

WPRE Write Protect Register Enable

## 2 Introduction

This document describes the in-system programming procedures for the SLG47004.

# 3 Hardware Requirements

# 3.1 Pinout and Signals

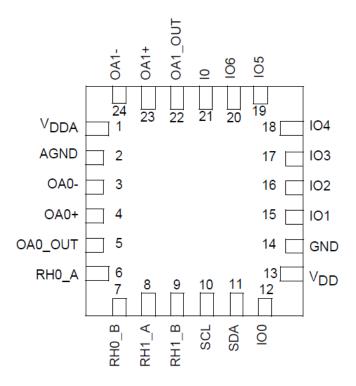

Four pins are required to program the SLG47004: VDD, GND, SCL, and SDA.

The  $V_{DD}$  pin requires a voltage ranging from 2.5 V to 5.5 V for Programming (Write) operations, and 2.4 V to 5.5 V for Verification (Read) operations.

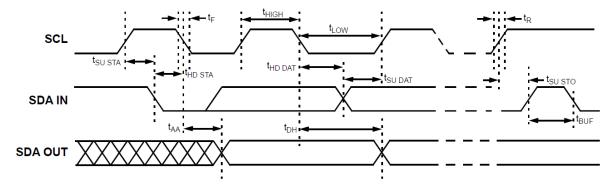

The SCL and SDA pins are defined to be standard I<sup>2</sup>C signaling. I<sup>2</sup>C Fast Mode Plus speed (1 MHz) NVM read and I<sup>2</sup>C Fast Mode speed (400 kHz) NVM write communication is supported for these devices. Refer to Table 1 for the signal timing characteristics of these pins.

Figure 1: STQFN-24 Pin Configuration

Table 1: I<sup>2</sup>C Specifications

|                  |                                                 |                                            | Fa   | st-Mod | de  | Fast | t-Mode | Plus |      |

|------------------|-------------------------------------------------|--------------------------------------------|------|--------|-----|------|--------|------|------|

| Symbol           | Parameter                                       | Condition                                  | Min  | Тур    | Max | Min  | Тур    | Max  | Unit |

| F <sub>SCL</sub> | Clock Frequency, SCL                            | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ |      |        | 400 |      |        | 1000 | kHz  |

| t <sub>LOW</sub> | Clock Pulse Width Low                           | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ | 1300 |        |     | 500  |        |      | ns   |

| thigh            | Clock Pulse Width High                          | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ | 600  |        |     | 260  |        |      | ns   |

| tı               | Input Filter Spike<br>Suppression (SCL,<br>SDA) | V <sub>DD</sub> = 2.4 V to 5.5 V           |      |        | 50  |      |        | 50   | ns   |

| t <sub>AA</sub>  | Clock Low to Data Out<br>Valid                  | V <sub>DD</sub> = 2.4 V to 5.5 V           |      |        | 900 |      |        | 450  | ns   |

| t <sub>BUF</sub> | Bus Free Time between Stop and Start            | V <sub>DD</sub> = 2.4 V to 5.5 V           | 1300 |        |     | 500  |        |      | ns   |

| thd_sta          | Start Hold Time                                 | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ | 600  |        |     | 260  |        |      | ns   |

| tsu_sta          | Start Set-up Time                               | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ | 600  |        |     | 260  |        |      | ns   |

| thd_dat          | Data Hold Time                                  | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ | 0    |        |     | 0    |        |      | ns   |

| tsu_dat          | Data Set-up Time                                | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ | 100  |        |     | 50   |        |      | ns   |

| t <sub>R</sub>   | Inputs Rise Time                                | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ |      |        | 300 |      |        | 120  | ns   |

| t <sub>F</sub>   | Inputs Fall Time                                | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ |      |        | 300 |      |        | 120  | ns   |

| tsu_std          | Stop Set-up Time                                | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ | 600  |        |     | 260  |        |      | ns   |

| t <sub>DH</sub>  | Data Out Hold Time                              | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V}$ | 50   |        |     | 50   |        |      | ns   |

Figure 2: I<sup>2</sup>C General Timing Characteristics

# 4 I<sup>2</sup>C Signal Specification

## 4.1 Addressing

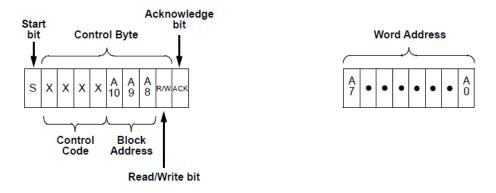

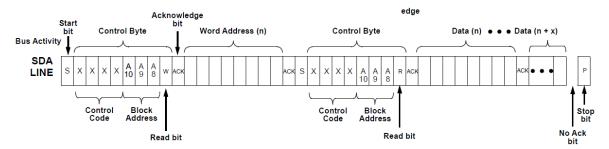

Each command to the I<sup>2</sup>C Serial Communications macrocell begins with a Control Byte. The bits inside this Control Byte are shown in Figure 3.

After the Start bit, the first four bits make up the control code. Each bit in the control code can be sourced independently from registers [1019:1016] or can be defined externally by IO4, IO3, IO2, and IO1. If external GPIO source is selected, the LSB of the control code is defined by the value of IO1, while the MSB is defined by the value of IO4. The address source (either register bit or PIN) for each bit in the control code is defined by registers [1023:1020]. This provides flexibility on the chip level when addressing this device and other devices on the same I<sup>2</sup>C bus. **The default control code is 0001 and is selected by registers [1019:1016]**.

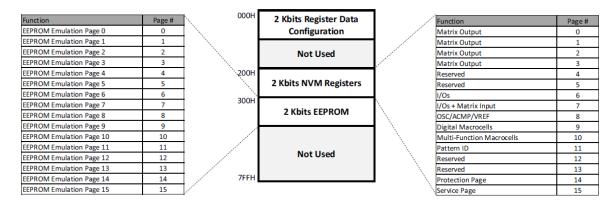

The Block Address is the next three bits (A10, A9, A8), which will define the most significant bits in the addressing of the data to be read or written by the I<sup>2</sup>C command. For the SLG47004, these 3 bits determine whether the I<sup>2</sup>C command accesses the Register Data Configuration, NVM Data Configuration, or EEPROM address spaces, as defined in Figure 6. The last bit in the Control Byte is the R/W bit, which selects whether a read command or write command is requested, with a "1" selecting a Read command and a "0" selecting a Write command.

This Control Byte will be followed by an Acknowledge bit (ACK), which is sent by this device to indicate successful communication of the Control Byte data.

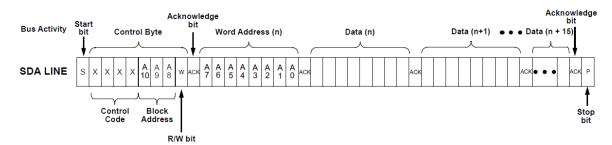

Figure 3: Page Write Command

### 4.2 Commands

#### 4.2.1 Write Command

To program the SLG47004, a 16-byte  $I^2C$  page write command can be sent to configure the MTP memory. Upon receipt of a proper Control Byte and Word Address, the SLG47004 will send an ACK. The device will then be ready to receive page data, which is 16 sequential writes of 8-bit data words. The SLG47004 will respond with an ACK after each data word is received. After all page data is written, the addressing device, such as a Bus Master, must then terminate the write operation with a Stop condition. At that time, the SLG47004 will enter an internal, self-timed write cycle, which will be completed within  $t_{WR} = 20$  ms (max). While the data is being written into the NVM Memory Array, all inputs, outputs, internal logic, and  $I^2C$  access to the Register Data Configuration address space will be operational/valid.

Figure 4: Page Write Command Example

# 4.2.2 Verify Command

The Random Sequential Read command can be used for verification. The command starts with a Control Byte (with R/W bit set to "0", indicating a write command) and a Word Address to set the internal byte address. These bytes are followed by another start bit with the same Control Byte (with R/W bit set to "1", indicating a read command). The start bit in the middle of the command will halt the decoding of a Write command, but will set the internal address counter in preparation for the second half of the command. After the start bit, the Bus Master issues a second Control Byte with the R/W bit set to "1", after which the SLG47004 issues an Acknowledge bit, followed by the requested eight data bits. Once the SLG47004 transmits the first data byte, the Bus Master issues an Acknowledge bit. The Bus Master can continue reading sequential bytes of data by sending additional Acknowledge bits or it can terminate the command with a Stop condition.

Figure 5: Random Sequential Read Command

## 4.2.3 Erase Command

The erase scheme allows a 16-byte page within the MTP memory to be erased by modifying the contents of the Erase Register (ERSR) found at 0xE3. This erase command should be written to the Register Data Configuration address space as defined by Figure 6. In addition, this erase command can be configured to erase a page within either the 2 kbits of NVM or 2 kbits of EEPROM by setting ERSEB4 (register [1820]) in accordance with Table 3. The page can be selected by setting registers [1819:1816] (bits ERSEB0, ERSEB1, ERSEB2, ERSEB3 from Table 3) to match the desired page number shown in Figure 7. When registers [1823:1821] (bits ERSEB0, ERSEB1, ERSEB2 from Table 3) are set to "110" in the ERSR register, the device will start a self-timed erase cycle, which will complete in a maximum of  $t_{ER} = 20 \text{ ms}$  (max).

Table 2: ERSR Register Format

|                           | b7    | b6    | b5    | b4     | b3     | b2     | b1     | b0     |

|---------------------------|-------|-------|-------|--------|--------|--------|--------|--------|

| Page<br>Erase<br>Register | ERSE2 | ERSE1 | ERSE0 | ERSEB4 | ERSEB3 | ERSEB2 | ERSEB1 | ERSEB0 |

**Table 3: ERSR Register Bits Function Description**

| Bit | Name Ty |       | Туре | Description         |

|-----|---------|-------|------|---------------------|

| 7   | ERSE2   | Erase | W    | 000: erase disable; |

| Bit | Na     | me        | Туре | Description                                                            |

|-----|--------|-----------|------|------------------------------------------------------------------------|

| 6   | ERSE1  | Enable    | W    | 110: cause the NVM erase: full NVM (4k bits) erase for                 |

| 5   | ERSE0  |           | W    | ERSCHIP = 1 if DIS_ERSCHIP = 0 or page erase for ERSCHIP = 0.          |

| 4   | ERSEB4 |           | W    |                                                                        |

| 3   | ERSEB3 | Page      | W    | Define the page address, which will be erased:                         |

| 2   | ERSEB2 | Selection | W    | ERSB4 = 0 corresponds to the Upper 2K NVM used for chip configuration; |

| 1   | ERSEB1 | for Erase | W    | ERSB4 = 1 corresponds to the 2-k emulated EEPROM.                      |

| 0   | ERSEB0 |           | W    |                                                                        |

Upon receipt of the proper Device Address and Erase Register Address, the SLG47004 will send an ACK. The device will then be ready to receive Erase Register data. The SLG47004 will respond with another I<sup>2</sup>C ACK after the Erase Register data byte is received. The addressing device, such as a Bus Master, must then terminate the write operation with a Stop condition. At that time, the SLG47004 will enter an internal, self-timed erase cycle, which will be completed within terminate (max 20 ms). While the data is being erased within the MTP memory cells, all inputs, outputs, internal logic, and I<sup>2</sup>C access to the Register Data Configuration address space will be operational/valid. After the erase has taken place, the contents of ERSE bits will be set to "0" automatically.

# 5 Memory Space

# 5.1 Memory Map

In the read and write command structure, there are a total of 11 bits that define the address for the I<sup>2</sup>C command: 3 bits for the Block Address and 8 bits for the Word Address.

As previously described, the Block Address determines which 2 kbits of address space to communicate with. The 2 kbits of Register Data Configuration cells configure the operation of the SLG47004 device. The 2 kbits of NVM Data Configuration correspond to the MTP cells that persist through power down events and are loaded into the Register Data Configuration cells upon power up. The 2 kbits of EEPROM are allocated for application-specific MTP memory storage.

The Word Address defines the specific bytes of data to access within these memory spaces. Figure 7 breaks these 2 kbits of data (256 bytes) into 16-byte pages. Refer to the register map found within the SLG47004's base die datasheet for more information.

| Lowest I <sup>2</sup> C                    | I <sup>2</sup> C E | Block Addı | ress   | Memory Space                        |                              |

|--------------------------------------------|--------------------|------------|--------|-------------------------------------|------------------------------|

| Address = 000h                             | A10 = 0            | A9 = 0     | A8 = 0 | 2 Kbits Register Data Configuration |                              |

|                                            | A10 = 0            | A9 = 0     | A8 = 1 | Not Used                            |                              |

|                                            | A10 = 0            | A9 = 1     | A8 = 0 | 2 Kbits NVM Data Configuration      | 16 pages to configure GPAK   |

|                                            | A10 = 0            | A9 = 1     | A8 = 1 | 2 Kbits EEPROM                      | 16 pages for emulated EEPROM |

| Highest I <sup>2</sup> C<br>Address = 7FFh | A10 = 1            | A9 = X     | A8 = X | Not Used                            |                              |

Figure 6: I<sup>2</sup>C Block Addressing

Figure 7: I<sup>2</sup>C Address Mapping

# 5.2 Pages

The SLG47004 I<sup>2</sup>C registers are separated into 3 address spaces: the SLG47004 Register Data Configuration, the NVM Data Configuration, and the EEPROM. Each of these address spaces contain 2048-bits of register data which equates to 16 pages of 16 bytes of data. The MTP IP limits I<sup>2</sup>C write and erase operations to 16-byte segments defined as pages for both the NVM Data Configuration and the EEPROM address spaces.

# **5.2.1** Protection Page

Page E (#14) contains the protection settings for the SLG47004. Individual registers determine whether the SLG47004's Register Data Configuration, NVM Data Configuration, and EEPROM address spaces can be accessed via I<sup>2</sup>C reads, writes, and erases. The Register Protection (RPR - 0xE0), NVM Protection (NPR - 0xE1), and EEPROM Protection (WPR - 0xE2) bytes can can be locked using the Protection Lock Bit (PRL - 0xE4).

The current configuration of the protection registers can be determined by performing a Random Read command of the desired register with the Block Adress set to "000". Modifying these registers using the Block Address of "000" will change the functionality of the protection scheme, but all configuration changes will be lost after a power cycle or soft reset.

Once the user determines the desired security settings for their project, they can erase and program Page E (#14) with the PRL set HIGH. Refer to section 5.2.1.4 for a description of this procedure. Note that the protection page configuration will not be active until the SLG47004 device is reset and the NVM Data Configuration contents are loaded into the SLG47004 Configuration Registers. This will cause the protection scheme to persist after a power cycle or soft reset.

#### 5.2.1.1 Register Protection (RPR)/Rheostat Protection

The RPR register is located within address 0xE0. This register locks the ability to read, write, and erase the SLG47004's Register Data Configuration. These registers impact the "000" Block Address. In addition, this register locks the ability of the rheostats' program input to erase and program the current rheostat value into Page C (#12) and Page D (#13) of the MTP NVM Data Configuration address space. Refer to Table 4 for the format and Table 5 for the bit function descriptions.

**Table 4: RPR Register Format**

|     | b7 | b6 | b5 | b4     | b3    | b2    | b1    | b0    |

|-----|----|----|----|--------|-------|-------|-------|-------|

| RPR |    |    |    | RH_PRB | RPRB3 | RPRB2 | RPRB1 | RPRB0 |

**Table 5: RPR Register Bits Function Description**

| Bit |            | Name                                | Туре | Description                                                                                                                                                                             |

|-----|------------|-------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | RH_PRB     | RH_PRB                              |      | Program signal from connection matrix is enabled;     Program signal from connection matrix is disabled.                                                                                |

| 3:2 | RPRB [3:2] | 2k Register Write<br>Selection Bits | R/W  | <ul><li>00: 2k register data is unprotected for write;</li><li>01: 2k register data is partly protected for write;</li><li>10: 2k register data is fully protected for write.</li></ul> |

| 1:0 | RPRB [1:0] | 2k Register Read<br>Selection Bits  | R/W  | 00: 2k register data is unprotected for read; 01: 2k register data is partly protected for read; 10: 2k register data is fully protected for read.                                      |

#### 5.2.1.2 **NVM Protection (NPR)**

The NPR register is located within address 0xE1. This register locks the ability to read, write, and erase the NVM Configuration Data. These registers impact the "010" Block Address. Refer to Table 6 for the format and Table 7 for the bit function descriptions.

**Table 6: NPR Format**

|     | b7 | b6 | b5 | b4 | b3 | b2 | b1    | b0    |

|-----|----|----|----|----|----|----|-------|-------|

| NPR |    |    |    |    |    |    | NPRB1 | NPRB0 |

**Table 7: NPR Bit Function Description**

| Bit | N          | Name Type Description                     |     |                                                                                                                                                                                                                                                                                |  |

|-----|------------|-------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1:0 | NPRB [1:0] | 2k NVM<br>Configuration<br>Selection Bits | R/W | 00: 2k NVM Configuration data is unprotected for read and write/erase; 01: 2k NVM Configuration data is fully protected for read; 10: 2k NVM Configuration data is fully protected for write/erase; 11: 2k NVM Configuration data is fully protected for read and write/erase. |  |

#### 5.2.1.3 **EEPROM Protection (WPR)**

The SLG47004 utilizes a software scheme to lock portions of the EEPROM from write and erase operations. The WPR register is located within address 0xE2. This register impacts the "011" Block Address. Refer to Table 8 for the format and Table 9 for the bit function descriptions.

**Table 8: WPR Register Format**

|     | b7 | b6 | b5 | b4 | b3 | b2   | b1   | b0   |

|-----|----|----|----|----|----|------|------|------|

| WPR |    |    |    |    |    | WPRE | WPB1 | WPB0 |

Table 9: WPR Register Bits Function Description

| Bit | Name      |                                     | Туре | Description                                                                                                                                                                                                                  |  |

|-----|-----------|-------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2   | WPRE      | Write Protect<br>Register<br>Enable | R/W  | 0: No Software Write Protection enabled (default); 1: Write Protection is set by the state of WPB [1:0] bits.                                                                                                                |  |

| 1:0 | WPB [1:0] | Write Protect<br>Block Bits         | R/W  | 00: Upper quarter of emulated EEPROM is write protected (default); 01: Upper half of emulated EEPROM is write protected; 10: Upper 3/4 of emulated EEPROM is write protected; 11: Entire emulated EEPROM is write protected. |  |

## 5.2.1.4 Protection Lock Bit (PRL)

The Protect Lock Bit can be used to permanently lock the current state of the RPR, NPR, and WPR protection registers. A logic "0" indicates that these protection registers can be modified, whereas a logic "1" indicates that they have been locked and can no longer be modified. The PRL register bit is located at register [1824] within 0xE4.

This bit blocks I<sup>2</sup>C write access to these protection registers by locking the entire configuration of Page E (#14) within the NVM. To lock these registers, follow the procedure below:

- 1. Read and Store the Rheostat Tolerance Data Stored within 0xE6 to 0xE9 (optional).

- 2. Erase Page E (#14) within the NVM.

- 3. Program Page E (#14) within the NVM using the Desired Protection Settings (splice in the Rheostat Tolerance Data for 0xE6 to 0xE9).

- 4. Issue a Soft Reset using register [984] within 0x7B or Power Cycle the SLG47004 to Load the Protection Settings into the Configuration Registers. Note that the "Soft Reset" Feature is unavailable if the RPR is "Fully Protected for Write" (RPRB [3:2] = "10").

If PRL is HIGH and the NVM is locked for I<sup>2</sup>C writes and erases, this will permanently lock the protection settings.

**Table 10: PRL Register Format**

|     | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

|-----|----|----|----|----|----|----|----|-----|

| PRL |    |    |    |    |    |    |    | PRL |

## **Table 11: PRL Bit Function Description**

| Bit | Name |            | Туре | Description                                |  |  |

|-----|------|------------|------|--------------------------------------------|--|--|

| 0   |      | Protection |      | 0: RPR/WPR/NPR Settings can be Changed;    |  |  |

| U   | PRL  | Lock       | R/W  | 1: RPR/WPR/NPR Settings cannot be Changed. |  |  |

# 5.2.2 Service Page

Page 8 (#8) and page F (#15) are both dedicated service pages within the NVM Data Configuration and SLG47004 Register Data Configuration address spaces. They contain reserved information that is preprogrammed onto the device during final test. The information on these pages can be read via I<sup>2</sup>C, but they cannot be written or erased, since they are locked by Renesas Electronics using the Service Page Lock Bit (register [1944]). As these pages cannot be altered by the user, the programming algorithm skips all I<sup>2</sup>C operation on these pages.

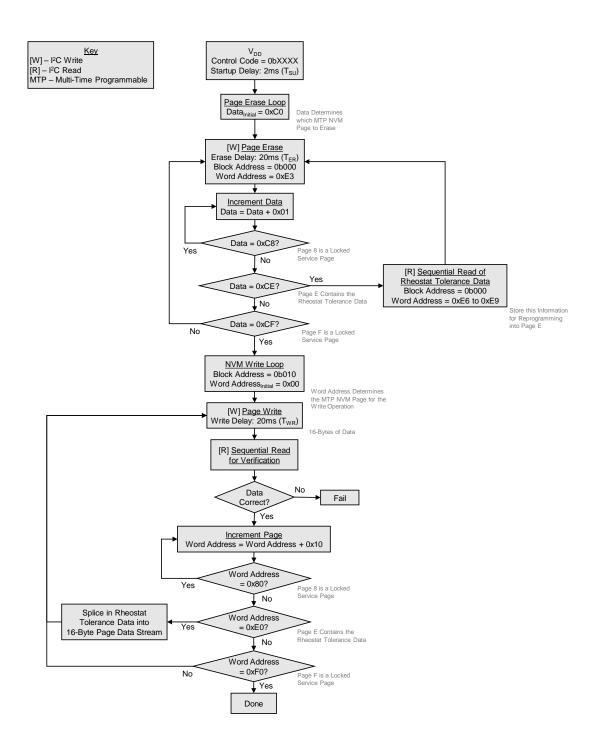

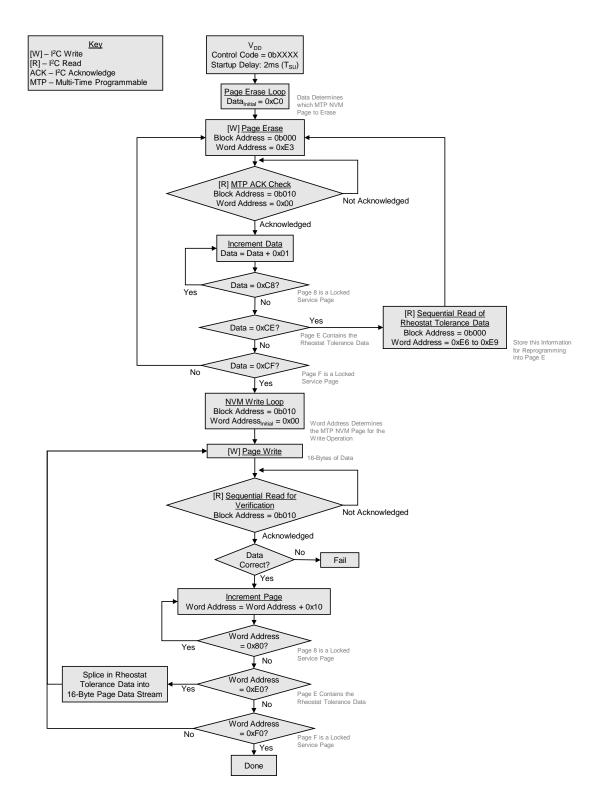

# 6 Programming Algorithm for NVM Configuration Register Space

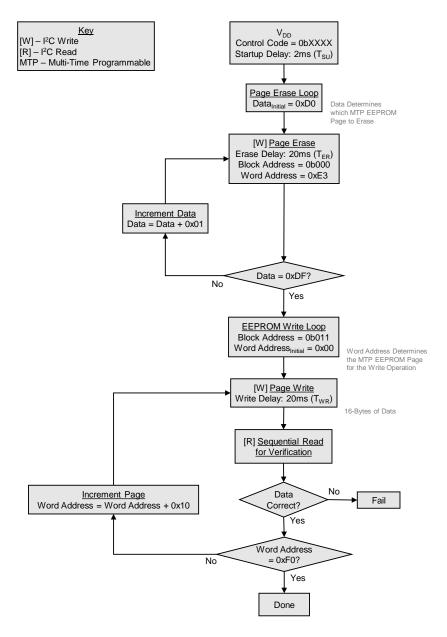

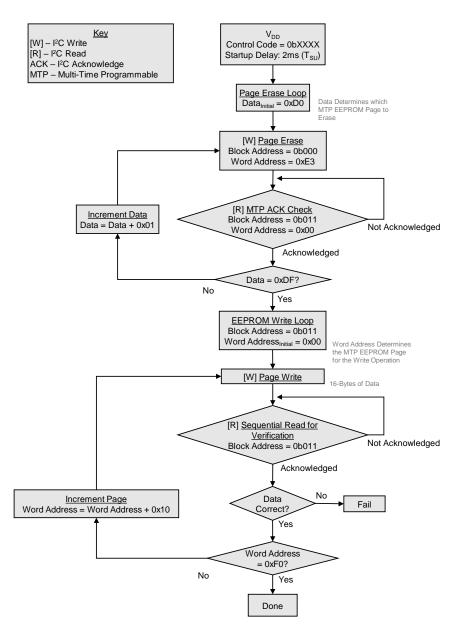

The SLG47004 programming algorithm for the NVM Data Configuration address space consists of a series of sequential I<sup>2</sup>C write and read commands. The MTP IP limits I<sup>2</sup>C programming operations to 16-byte page writes.

Data "1" cannot be re-programmed as data "0" without first being erased. Each byte can only be programmed one time without erasure.

Note 1 The functionality of the device is based upon the SLG47004 Register Data Configuration. The NVM Data Configuration will not be reloaded from the NVM until power is cycled or a reset command is issued.

Special care should be taken when erasing and re-programming Page E (#14). The Rheostat Tolerance Data is stored within this page and should be read so that it can be inserted into the new byte sequence for programming into Page E (#14).

The SLG47004 can be programmed either with or without an acknowledge polling routine. The acknowledge polling routine is implemented to optimize time sensitive applications that would prefer not to wait the fixed maximum write cycle time (twr). This method allows the application to know instantly when the NVM write cycle has completed so a subsequent operation can start.

Figure 8: Flowchart for Programming NVM without Acknowledge Polling

Figure 9: Flowchart for Programming NVM with Acknowledge Polling

# 7 Programming Algorithm for the Emulated EEPROM Space

The SLG47004 programming algorithm for the emulated EEPROM address space consists of a series of sequential I<sup>2</sup>C write and read commands. The MTP IP limits I<sup>2</sup>C programming operations to 16-byte page writes.

Data "1" cannot be re-programmed as data "0" without first being erased. Each byte can only be programmed one time without erasure.

Programming the emulated EEPROM follows a similar flow to that of the NVM with three differences:

- The Emulated EEPROM Block Address is "011" (in contrast with the "010" Block Adress of the NVM Data Configuration address space);

- With emulated EEPROM, all 16 pages are user accessible (no Service or Protection Pages);

- Rheostat Tolerance Data is stored in the NVM and does not require consideration in the EEPROM programming flow.

Figure 10: Flowchart for Programming EEPROM without Acknowledge Polling

Figure 11: Flowchart for Programming Emulated EEPROM with Acknowledge Polling

# **Revision History**

| Revision | Date        | Description        |  |

|----------|-------------|--------------------|--|

| 1.1      | 16-Mar-2022 | Renesas rebranding |  |

| 1.0      | 9-Nov-2020  | Initial version    |  |

## **Status Definitions**

| Status               | Definition                                                                                                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |

## **RoHS Compliance**

Renesas Electronics Corporation's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.