#### ISL73847SLH

Low Dose Rate Test Results of the ISL73847SLH Rad Hard Single/Dual Phase Current Mode PWM Controller

#### Introduction

This report documents the results of low dose rate (LDR) total dose testing of the ISL73847SLH, a synchronous buck controller that can operate as a single or dual phase controller. The testing was conducted to provide an assessment of the total dose hardness of the parts and to determine any bias sensitivity. Parts were irradiated under bias and with all pins grounded at LDR to 100krad(Si) with an anneal. The ISL73847SLH is rated at 75krad(Si) at LDR (0.01rad(Si)/s) and is acceptance tested on a wafer-by-wafer basis to the datasheet limits.

### **Product Description**

The ISL73847SLH is a synchronous buck controller that can operate as a single or dual phase controller. It is intended to work with the ISL71441SLH (half bridge GaN FET driver) to generate point-of-load voltage rails for commercial space applications.

It accepts an input voltage range of 4.5V to 19V with an output switching frequency that is programmable between 250kHz and 1.5MHz with a single external resistor. The output can regulate a voltage upwards of 600mV and is limited on the top end by the minimum off-time and selected switching frequency.

The wide input voltage range makes it a suitable power supply option for a high current FPGA core and other general purpose power solutions. The ISL73847SLH uses current mode modulation, which simplifies loop compensation and provides excellent power supply rejection. Additionally, the output is remotely sensed to compensate for any voltage drop in the load conditions. All of this put together results in a robust power supply solution that requires minimal components while achieving high power density.

The ISL73847SLH also features a tri-level output that provides excellent protection against faults by driving a mid-scale voltage to signal the power stage to enter a Hi-Z condition.

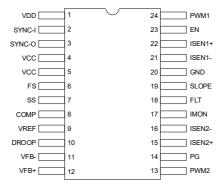

The ISL73847SLH is available in a 24 Ld hermetically sealed Ceramic Dual Flatpack (CDFP) package or in die form. The package and pinout configuration for the ISL73847SLH is shown in Figure 1 and the pin descriptions are shown in Table 1.

Figure 1. Pinout Configuration

**Table 1. Pin Descriptions**

| Pin<br>Number | Pin Name | Description                                                                                                                                                                                                                                                                                                       |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VDD      | The power supply input to the IC. The voltage range on this pin is 4.5V to 19V.                                                                                                                                                                                                                                   |

| 2             | SYNC-I   | This pin is an input that accepts 2x the required output switching frequency (regardless of single or dual phase). Internally the IC divides the clock down to get two clocks 180° from each other for each phase.  Note: This pin has an internal pull down, leave it floating if SYNC function is not required. |

#### **Table 1. Pin Descriptions**

| Pin<br>Number         | Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3                     | SYNC-O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | This pin can output either 1x or 2x the output switching frequency depending on the loading present on the pin during power up (before soft-start). When outputting 1x, the SYNC-O is 180° out of phase with phase 1 clock. The 2x SYNC-O output is in phase with the SYNC-I. $100k\Omega$ to VCC: SYNC-O outputs 1x output switching frequency. $100k\Omega$ to GND: SYNC-O outputs 2x output switching frequency.                                      |  |  |  |  |  |  |

| 4                     | VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Output of internal LDO for analog circuity, short this pin to pin 5.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 5                     | VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tput of internal LDO for analog circuity, short this pin to pin 4.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 6                     | This pin sets the frequency for the internal oscillator between 1MHz and 3MHz. This sets the MHz and 1.5MHz for each phase.  When FS is tied to VCC, the oscillator switching frequency (f <sub>OSC</sub> ) is 1MHz, a resistor between adjusts the frequency between 1MHz and 3 MHz. If SYNC-I is being used to sync to an extern set to a frequency 15% less than the external clock.  Equation 2 in the datasheet can be used to find what resistor is required for a given frequency |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 7                     | SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | This is the soft-start pin, connect a ceramic capacitor from SS to GND to set the soft-start ramp. The soft-start time is adjustable between 2ms and 200ms. Equation 18 in the datasheet shows the relationship between the soft-start capacitor and soft-start time.                                                                                                                                                                                    |  |  |  |  |  |  |

| 8                     | COMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Output of error amplifier, connect a resistor and capacitor to ground for compensation adjustment.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 9                     | VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Output for the internal voltage reference. Insert a resistor between VREF and DROOP to enable droop regulation.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 10 DROOP output can b |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This pin is a current mirrored version of the output of the current sense amp output (sum of both phases). This output can be tied to the VREF pin through a resistor to enable droop regulation. The voltage created by the mirrored current and the resistor between VREF and DROOP sets the droop level.                                                                                                                                              |  |  |  |  |  |  |

| 11                    | VFB-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | This pin is the negative input for differential voltage feedback.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 12                    | VFB+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | This pin is the positive input for differential voltage feedback.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 13                    | PWM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | This pin is the PWM output for the secondary phase. Requires 100kΩ to GND.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 14                    | PG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | This pin is the power good indicator. It is an open-drain output, limit the sink current through this pin to below 7.2mA.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 15                    | ISEN2+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | This pin is the positive input for the secondary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 16                    | ISEN2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | This pin is the negative input for the secondary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 17                    | IMON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | This pin outputs the summed outputs of the current sense amplifiers for telemetry purposes.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 18                    | FLT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | This pin sequences the startup between the ISL73847SLH and the ISL73041SEH. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  A logic low on this pin indicates that either the ISL73847SLH or ISL73041SEH has encountered a fault or is not ready to start switching. A logic high indicates that there is no faults for either device. |  |  |  |  |  |  |

| 19                    | SLOPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of $25\Omega k$ to $100\Omega k$ to adjust slope compensation.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 20                    | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | This is the ground reference for the ISL73847SLH. This pin is tied to the package seal ring (lid)                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 21                    | ISEN1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 22                    | ISEN1+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | This pin is the positive input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 23                    | EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | This pin is the chip enable for the ISL73847SLH.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 24                    | PWM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | This pin is the PWM output for the primary phase. Requires $100k\Omega$ to GND.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

## **ISL73847SLH LDR Total Dose Test Report**

# **Contents**

| 1. | Test I                      | Test Description                          |    |  |  |  |  |

|----|-----------------------------|-------------------------------------------|----|--|--|--|--|

|    | 1.1                         | Irradiation Facilities                    | 4  |  |  |  |  |

|    | 1.2                         | Test Fixturing                            | 4  |  |  |  |  |

|    | 1.3                         | Characterization Equipment and Procedures | 4  |  |  |  |  |

|    | 1.4                         | Experimental Matrix                       | 4  |  |  |  |  |

|    | 1.5                         | Downpoints                                | 5  |  |  |  |  |

|    | Test I                      | Test Results                              |    |  |  |  |  |

|    | 2.1                         | Attributes Data                           | 5  |  |  |  |  |

|    | 2.2                         | Key Parameter Variables Data              | 5  |  |  |  |  |

| 3. | . Discussion and Conclusion |                                           |    |  |  |  |  |

| 4. | Revision History            |                                           |    |  |  |  |  |

| Δ. | Repo                        | rted Parameters                           | 43 |  |  |  |  |

## 1. Test Description

#### 1.1 Irradiation Facilities

LDR testing was performed at 0.01rad(Si)/s using the Renesas Palm Bay Hopewell Designs N40 panoramic irradiator. PbAl spectrum hardening filters were used to shield the test board and devices under test against low energy secondary gamma radiation. Half of the samples were biased, and half had all pins grounded during irradiation.

## 1.2 Test Fixturing

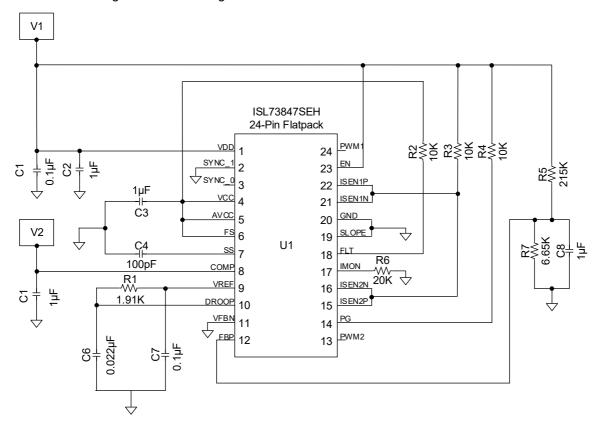

Figure 2 shows the configuration and voltages used for biased irradiation.

Note: VCC1 = V1 = 20V; VCC2 = V2 = 1.5V

Figure 2. TID Bias Schematic and Bias Voltages

# 1.3 Characterization Equipment and Procedures

All electrical testing was performed at room temperature outside the irradiator, using production automated test equipment (ATE) with data-logging at each down-point.

# 1.4 Experimental Matrix

Irradiation was performed in accordance with the guidelines of MIL-STD-883 Test Method 1019. The experimental matrix consisted of 12 samples irradiated at LDR under bias and 12 samples irradiated at LDR with all pins grounded. All parts were also subjected to a 168 hour, 100°C biased anneal. Three control units were used. The ISL73847SLH samples were from wafer lot V6C763/4/5.

## 1.5 Downpoints

Downpoints for the LDR tests were 0, 10, 20, 30, 40, 50, 60, 75, 100krad(Si), and Post-Anneal (PA).

#### 2. Test Results

#### 2.1 Attributes Data

LDR testing of the ISL73847SLH is complete. All tested parameters passed the datasheet limits up to the guaranteed dose of 75krad(Si). Two biased units failed parametric testing at 100krad(Si) and three biased units failed parametric testing after Post-Anneal but remained fully functional. Table 2 summarizes the results.

**Dose Rate** Pass<sup>[1]</sup> Bias Sample Size **Downpoint** Fail (rad(Si)/s) Pre-irradiation 12 0-10krad(Si) 12 0 20krad(Si) 12 0 30krad(Si) 12 0 0 40krad(Si) 12 Biased 0.01 12 (Figure 2 50krad(Si) 12 0 60krad(Si) 12 0 0 75krad(Si) 12 100krad(Si) 10 2 Post-Anneal 9 3 Pre-irradiation 12 n 10krad(Si) 12 0 20krad(Si) 0 12 30krad(Si) 0 12 40krad(Si) 12 0 0.01 Grounded 12 50krad(Si) 0 12 60krad(Si) 0 12 75krad(Si) 12 0 100krad(Si) 12 n Post-Anneal 12 0

**Table 2. Total Dose Test Attributes Data**

## 2.2 Key Parameter Variables Data

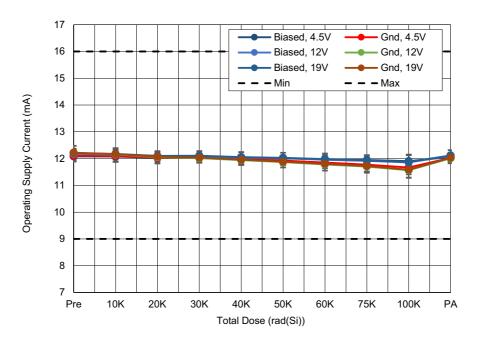

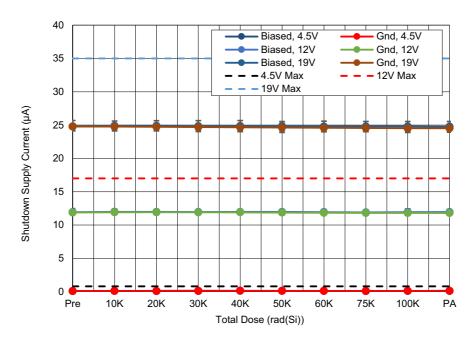

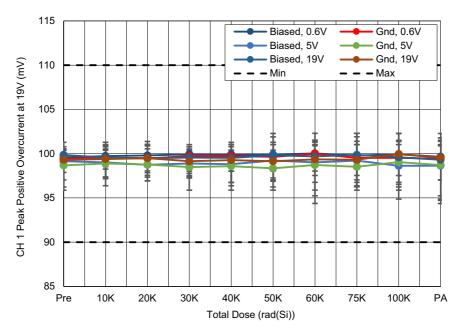

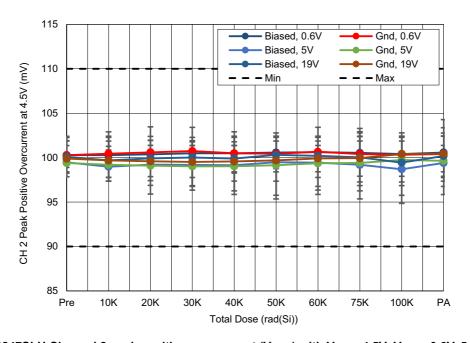

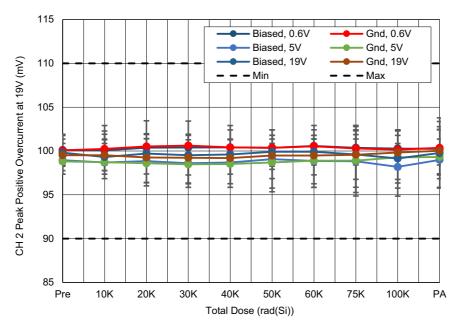

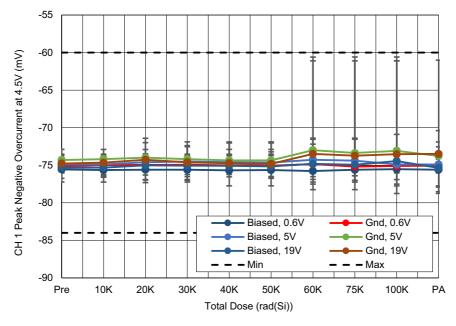

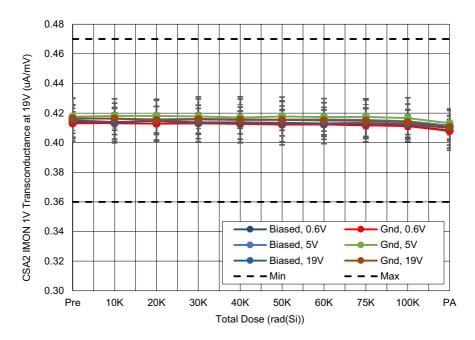

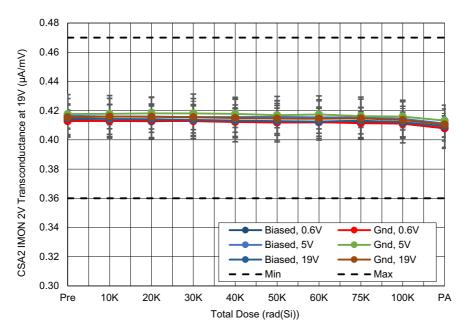

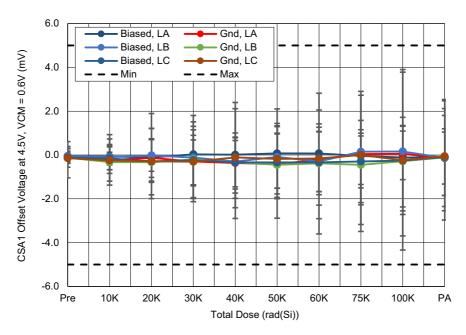

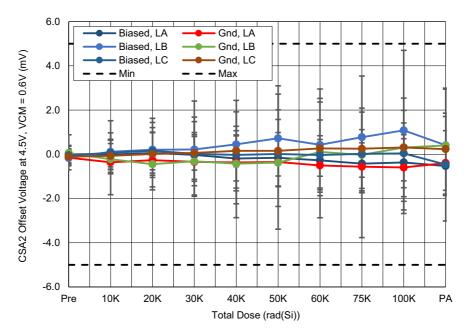

The plots in Figure 3 through Figure 75 illustrate the LDR response of the selected parameters shown in Table 3 in the Appendix. The plots show the average tested values of the parameters as a function of total dose for each of the irradiation conditions, biased and grounded, plus a 168 hour 100°C anneal. That downpoint is shown as PA (Post-Anneal) on the graphs. The plots also include error bars at each downpoint, representing the minimum and maximum measured values of the samples, although in some plots the error bars might not be visible because of their values compared to the scale of the graph.

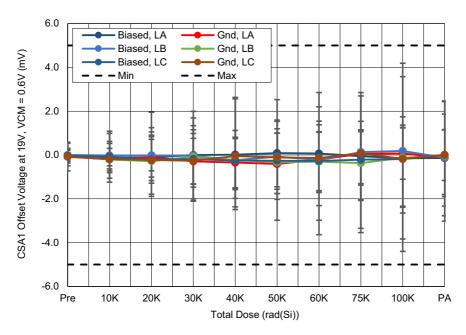

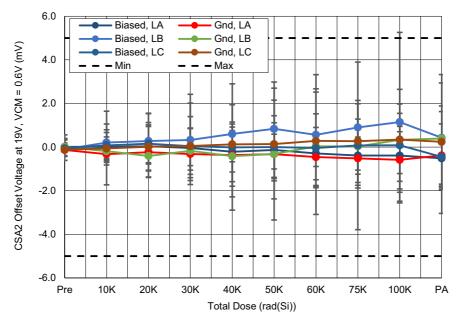

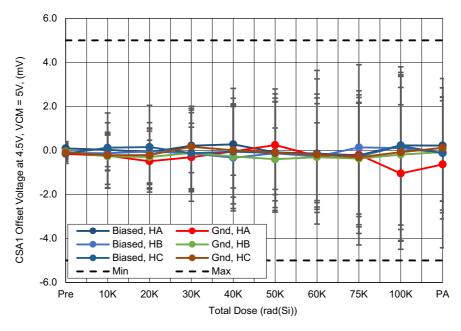

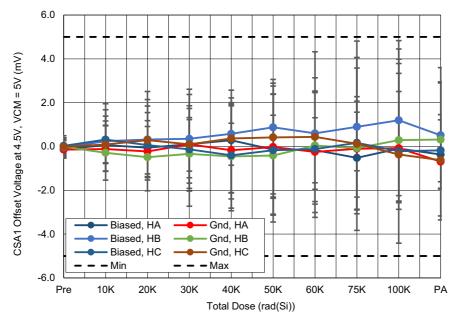

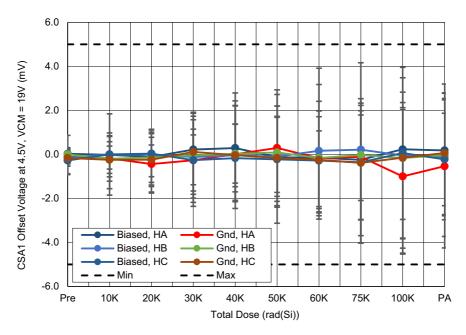

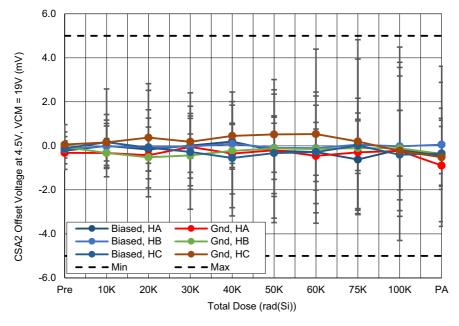

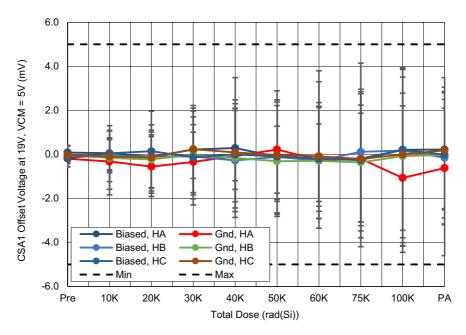

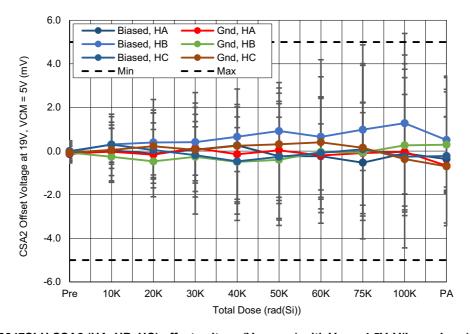

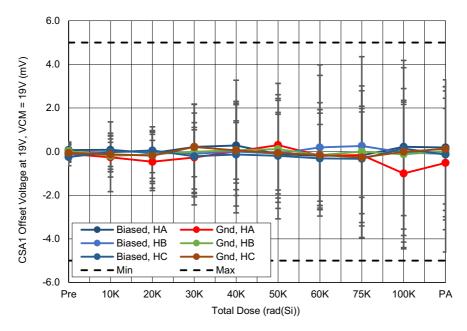

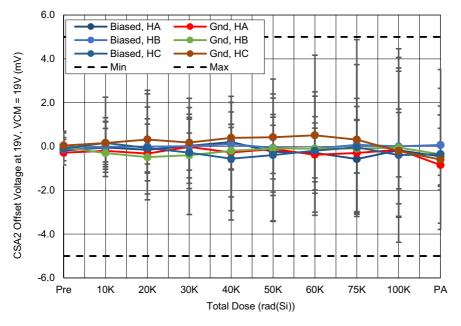

Each Current Sense Amp on the ISL73847SLH has triple redundancy for improved SEE tolerance and therefore has three current-sense measurements. These are shown as LA, LB, LC (Low Side) in Figure 39 through Figure 42 and HA, HB, HC (High Side) in Figure 43 through Figure 50.

<sup>1.</sup> A Pass indicates a sample that passes all datasheet limits.

The irradiated parts passed all parameters up to the TID acceptance level of 75krad(Si); however, there were two units that were logged as parametric failures at the final TID characterization exposure level of 100krad(Si). One of those parts, along with two other parts, also failed parametric testing after the anneal. These results are shown in Fig. 9, Fig. 10, Fig. 42, and Fig. 48. They are further examined in Discussion and Conclusion.

Figure 3. ISL73847SLH operating supply current ( $I_{DDO}$ ) at  $V_{DD}$  = 4.5V, 12V and 19V; EN = 3.3V;  $f_{SW}$  = 500kHz and  $C_L$ =100pF, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 9mA minimum and 16mA maximum.

Figure 4. ISL73847SLH shutdown supply current ( $I_{DDSD}$ ) at  $V_{DD}$  = 4.5V, 12V and 19V; EN = GND, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 35 $\mu$ A maximum.

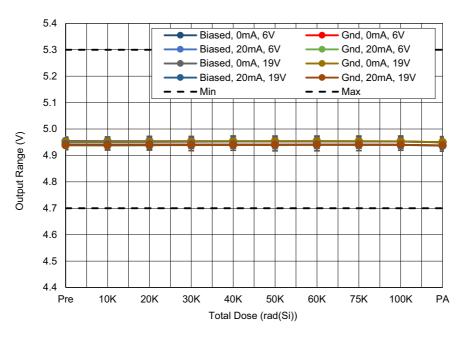

Figure 5. ISL73847SLH LDO output voltage range ( $V_{CC}$ ) at  $V_{DD}$  = 6V and 19V;  $I_{OUT}$  = 0mA and 20mA, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 4.7V minimum and 5.3V maximum.

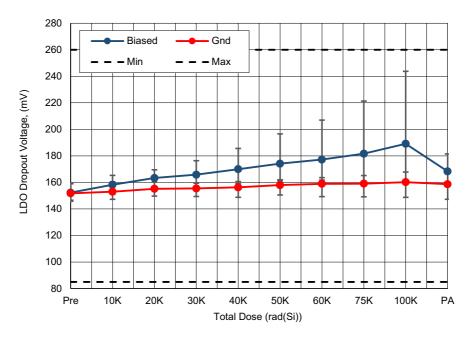

Figure 6. ISL73847SLH LDO dropout voltage (VCC $_{DO}$ ) at  $V_{DD}$  = 4.5V;  $I_{OUT}$  = 50mA, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 85mV minimum and 250mV maximum.

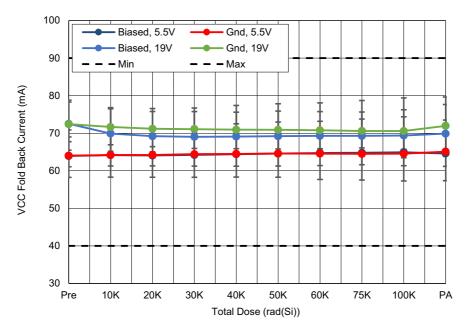

Figure 7. ISL73847SLH VCC foldback current ( $I_{CC-SC}$ ) at  $V_{DD}$  = 5.5V and 19V;  $V_{CC}$  = 0V; EN = 1.6V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 40mA minimum and 90mA maximum.

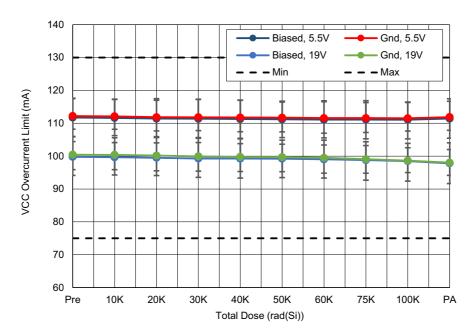

Figure 8. ISL73847SLH VCC overcurrent limit ( $I_{CC-CL}$ ) at  $V_{DD}$  = 5.5V and 19V;  $V_{CC}$  = 4.5V; EN = 1.6V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 75mA minimum and 130mA maximum.

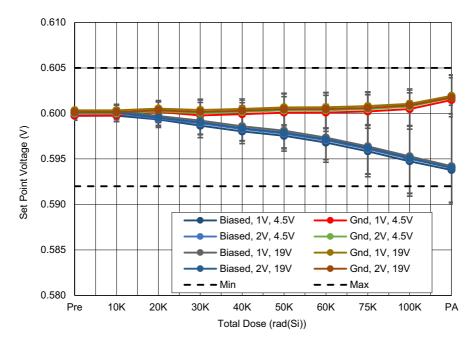

Figure 9. ISL73847SLH set point voltage ( $V_{FB+}$ ), at  $V_{DD}$  = 4.5V and 19V;  $V_{REF}$  =  $V_{DROOP}$  = 1V and 2V;  $V_{SEN1}$  =  $V_{SEN2}$  = 0mV, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.597V minimum and 0.604V maximum.

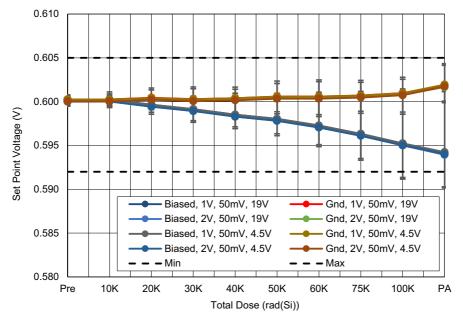

Figure 10. ISL73847SLH set point voltage ( $V_{FB+}$ ) at  $V_{DD}$  = 4.5V and 19V;  $V_{REF}$  =  $V_{DROOP}$  = 1V and 2V;  $V_{SEN1}$  =  $V_{SEN2}$  = 50mV, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.597V minimum and 0.604V maximum.

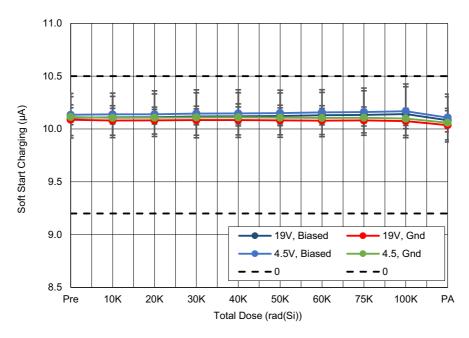

Figure 11. ISL73847SLH soft-start sourcing current (I<sub>SOFTSTART</sub>) at VDD = 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 9.2µA minimum and 10.5µA maximum.

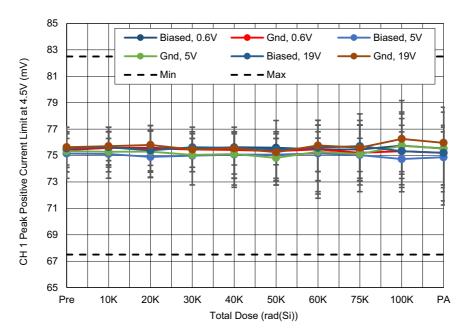

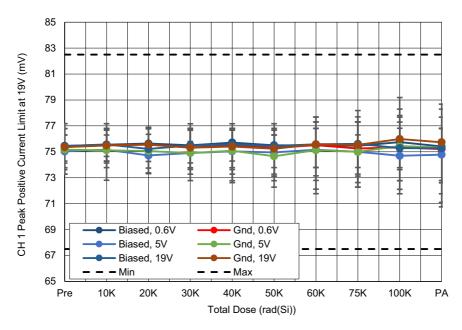

Figure 12. ISL73847SLH Channel 1 peak positive current limit ( $V_{PCL}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 67.5mV minimum and 82.5mV maximum.

Figure 13. ISL73847SLH Channel 1 peak positive current limit ( $V_{PCL}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 67.5mV minimum and 82.5mV maximum.

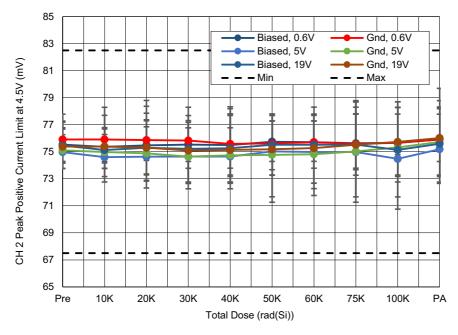

Figure 14. ISL73847SLH Channel 2 peak positive current limit ( $V_{PCL}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 67.5mV minimum and 82.5mV maximum.

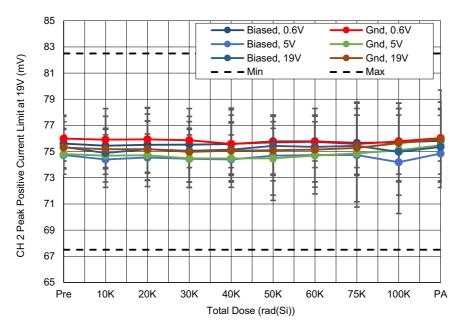

Figure 15. ISL73847SLH Channel 2 peak positive current limit ( $V_{PCL}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 67.5mV minimum and 82.5mV maximum.

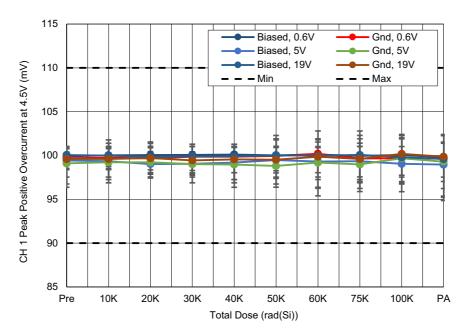

Figure 16. ISL73847SLH Channel 1 peak positive overcurrent ( $V_{POC}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90mV minimum and 110mV maximum.

Figure 17. ISL73847SLH Channel 1 peak positive overcurrent ( $V_{POC}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90mV minimum and 110mV maximum.

Figure 18. ISL73847SLH Channel 2 peak positive overcurrent ( $V_{POC}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90mV minimum and 110mV maximum.

Figure 19. ISL73847SLH Channel 2 peak positive overcurrent ( $V_{POC}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90mV minimum and 110mV maximum.

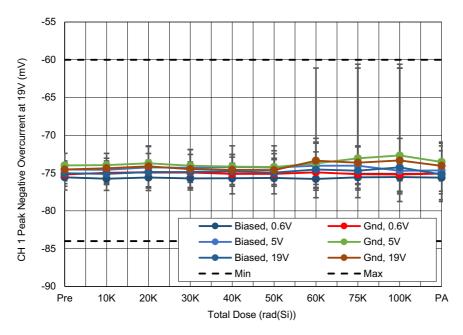

Figure 20. ISL73847SLH Channel 1 peak negative overcurrent ( $V_{NOC}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -84mV minimum and -60mV maximum.

Figure 21. ISL73847SLH Channel 1 peak negative overcurrent ( $V_{NOC}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -84mV minimum and -60mV maximum.

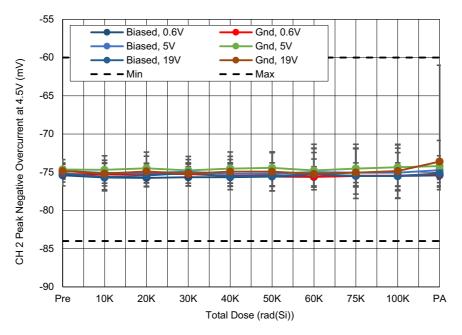

Figure 22. ISL73847SLH Channel 2 peak negative overcurrent ( $V_{NOC}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -84mV minimum and -60mV maximum.

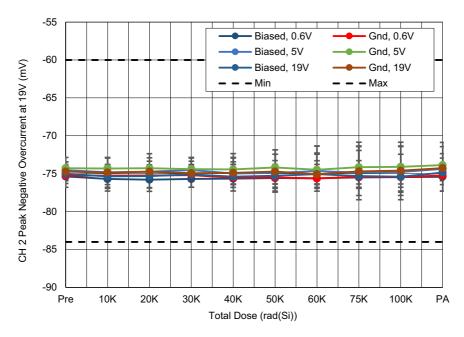

Figure 23. ISL73847SLH Channel 2 peak negative overcurrent ( $V_{NOC}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -84mV minimum and -60mV maximum.

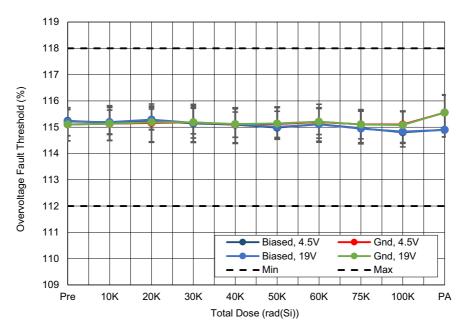

Figure 24. ISL73847SLH overvoltage fault threshold ( $V_{FB,\,OV}$ ) with  $V_{DD}$  = 4.5V and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 112% minimum and 118% maximum.

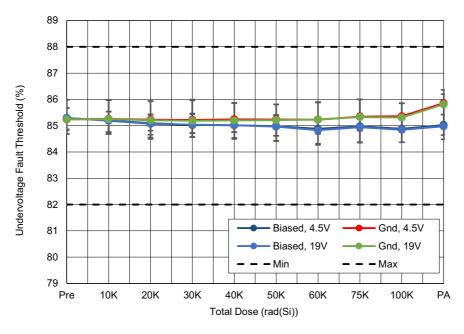

Figure 25. ISL73847SLH undervoltage fault threshold ( $V_{FB,\,UV}$ ) with  $V_{DD}$  = 4.5V and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 82% minimum and 88% maximum.

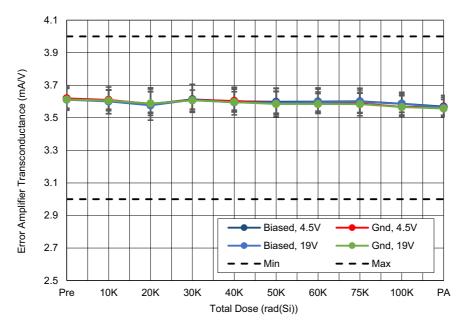

Figure 26. ISL73847SLH error amplifier transconductance ( $g_{m-EA}$ ) with  $V_{DD}$  = 4.5V and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 3mA/V minimum and 4mA/V maximum.

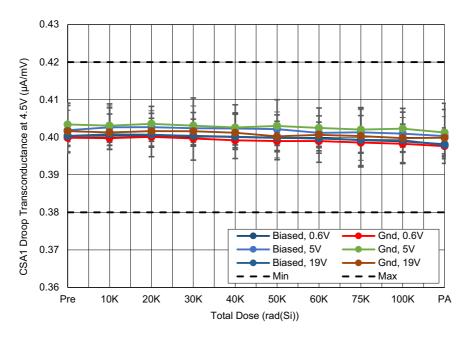

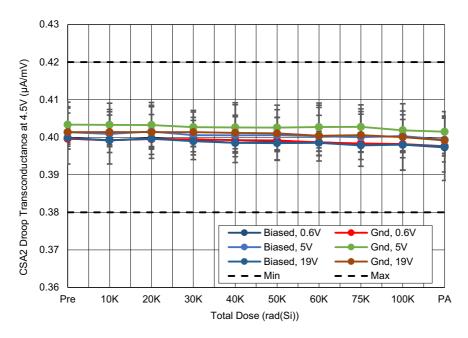

Figure 27. ISL73847SLH CSA1 droop transconductance ( $g_{m(CSA, DRP)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+}, I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.38 $\mu$ A/mV minimum and 0.42 $\mu$ A/mV maximum.

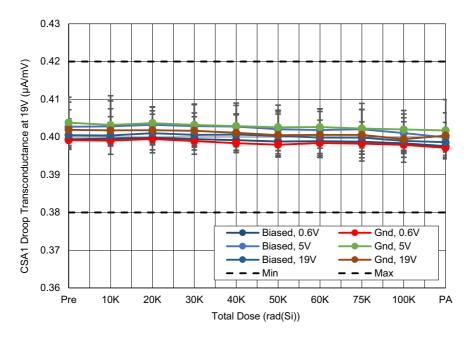

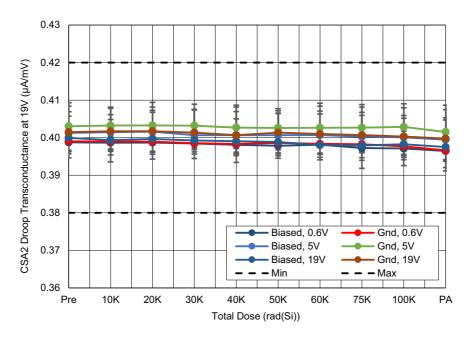

Figure 28. ISL73847SLH CSA1 droop transconductance ( $g_{m(CSA,DRP)}$ ) with  $V_{DD}$  = 19V;  $V(I_{SEN+},I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.38 $\mu$ A/mV minimum and 0.42 $\mu$ A/mV maximum.

Figure 29. ISL73847SLH CSA2 droop transconductance ( $g_{m(CSA,DRP)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+},I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.38 $\mu$ A/mV minimum and 0.42 $\mu$ A/mV maximum.

Figure 30. ISL73847SLH CSA2 droop transconductance ( $g_{m(CSA,DRP)}$ ) with  $V_{DD}$  = 19V;  $V(I_{SEN+},I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.38 $\mu$ A/mV minimum and 0.42 $\mu$ A/mV maximum.

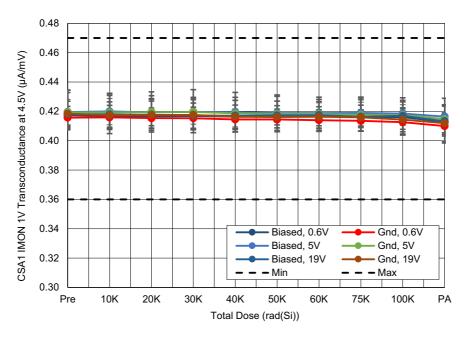

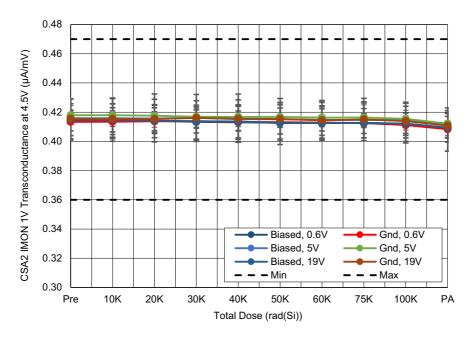

Figure 31. ISL73847SLH CSA1 IMON 1V transconductance ( $g_{m(CSA, IMON)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+}, I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.36 $\mu$ A/mV minimum and 0.47 $\mu$ A/mV maximum.

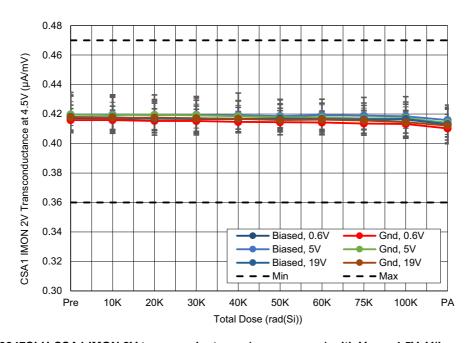

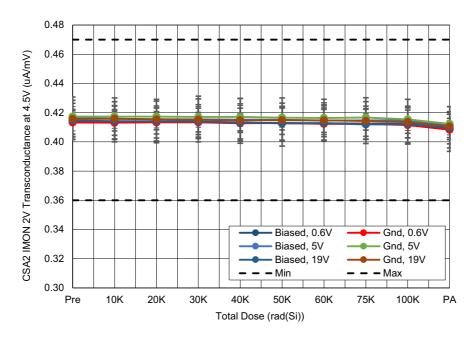

Figure 32. ISL73847SLH CSA1 IMON 2V transconductance ( $g_{m(CSA, IMON)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+}, I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.36 $\mu$ A/mV minimum and 0.47 $\mu$ A/mV maximum.

Figure 33. ISL73847SLH CSA2 IMON 1V transconductance  $(g_{m(CSA, IMON)})$  with  $V_{DD} = 4.5V$ ;  $V_{(ISEN+,SEN-)} = 10$ mV and 50mV,  $V_{CM} = 0.6V$ , 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are  $0.36\mu\text{A/mV}$  minimum and  $0.47\mu\text{A/mV}$  maximum.

Figure 34. ISL73847SLH CSA2 IMON 2V transconductance ( $g_{m(CSA, IMON)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+}, I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.36 $\mu$ A/mV minimum and 0.47 $\mu$ A/mV maximum.

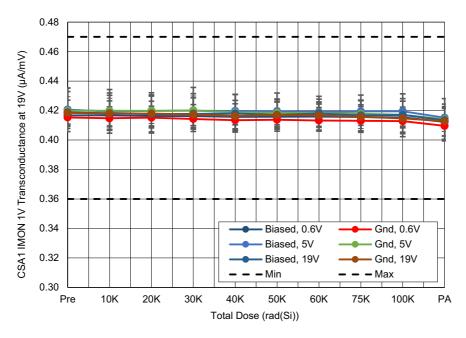

Figure 35. ISL73847SLH CSA1 IMON 1V transconductance  $(g_{m(CSA, IMON)})$  with  $V_{DD}$  = 19V;  $V(I_{SEN+}, I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.36µA/mV minimum and 0.47µA/mV maximum.

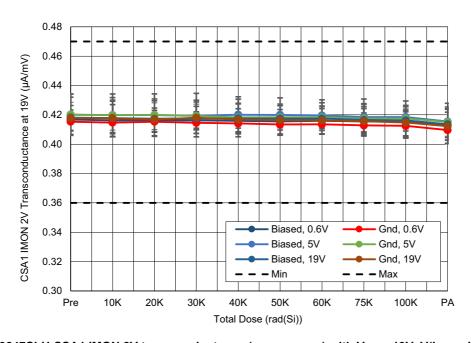

Figure 36. ISL73847SLH CSA1 IMON 2V transconductance ( $g_{m(CSA,IMON)}$ ) with  $V_{DD}$  = 19V;  $V(I_{SEN+},I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.36 $\mu$ A/mV minimum and 0.47 $\mu$ A/mV maximum.

Figure 37. ISL73847SLH CSA2 IMON 1V transconductance ( $g_{m(CSA,IMON)}$ ) with  $V_{DD}$  = 19V;  $V(I_{SEN+},I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.36 $\mu$ A/mV minimum and 0.47 $\mu$ A/mV maximum.

Figure 38. ISL73847SLH CSA2 IMON 2V transconductance ( $g_{m(CSA,IMON)}$ ) with  $V_{DD}$  = 19V;  $V(I_{SEN+},I_{SEN-})$  = 10mV and 50mV,  $V_{CM}$  = 0.6V, 5.0V, and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.36 $\mu$ A/mV minimum and 0.47 $\mu$ A/mV maximum.

Figure 39. ISL73847SLH CSA1 (LA, LB, LC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 0.6V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 40. ISL73847SLH CSA2 (LA, LB, LC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 0.6V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 41. ISL73847SLH CSA1 (LA, LB, LC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 19V;  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 0.6V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 42. ISL73847SLH CSA2 (LA, LB, LC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 19V;  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 0.6V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 43. ISL73847SLH CSA1 (HA, HB, HC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 5V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 44. ISL73847SLH CSA2 (HA, HB, HC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 4.5V;  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 5V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 45. ISL73847SLH CSA1 (HA, HB, HC) offset voltage  $(V_{OS(CSA)})$  with  $V_{DD}$  = 19V;  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 5V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 46. ISL73847SLH CSA2 (HA, HB, HC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 19V;  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 5V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 47. ISL73847SLH CSA1 (HA, HB, HC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 4.5V,  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 48. ISL73847SLH CSA2 (HA, HB, HC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 4.5V,  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 49. ISL73847SLH CSA1 (HA, HB, HC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 19V,  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

Figure 50. ISL73847SLH CSA2 (HA, HB, HC) offset voltage ( $V_{OS(CSA)}$ ) with  $V_{DD}$  = 19V,  $V(I_{SEN+}, I_{SEN-})$  = 0mV,  $V_{CM}$  = 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -4.5mV minimum and 4.5mV maximum.

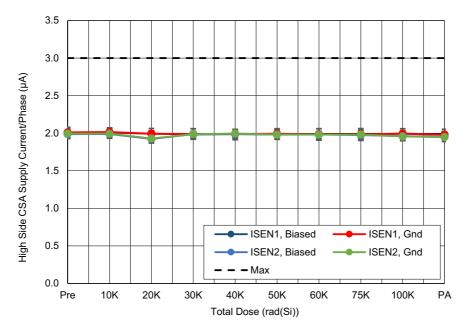

Figure 51. ISL73847SLH high-side CSA supply current per phase ( $I_{CSA}$ ) with  $V_{DD}$  = 19V, EN = 3.3V,  $V_{CM}$  = 2.7V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 3µA maximum.

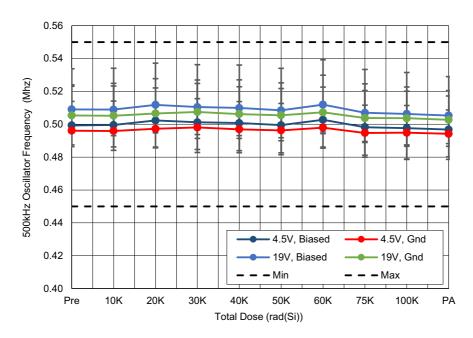

Figure 52. ISL73847SLH frequency range for 500kHz Oscillator ( $f_{OSC-0.5M}$ ) with  $V_{DD}$  = 4.5V and 19V;  $R_{FS}$  = 205k $\Omega$ ; EN = 3.3V;  $R_{SYNC-O}$  = 100k $\Omega$  to GND, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.45MHz minimum and 0.55MHz maximum.

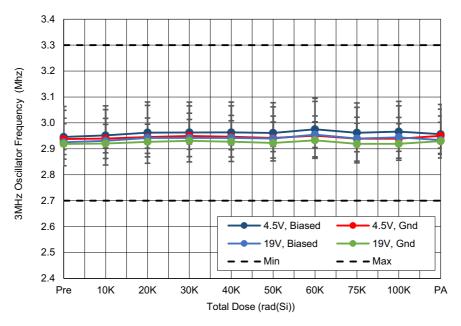

Figure 53. ISL73847SLH frequency range for 3MHz Oscillator ( $f_{OSC-3M}$ ) with  $V_{DD}$  = 4.5V and 19V;  $R_{FS}$  = 16.7k $\Omega$ ; EN = 3.3V;  $R_{SYNC-O}$  = 100k $\Omega$  to GND, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 2.7MHz minimum and 3.3MHz maximum.

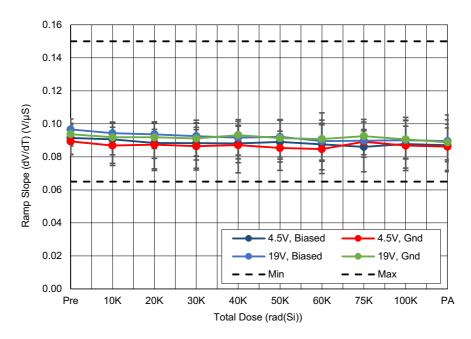

Figure 54. ISL73847SLH slope generator ramp slope ( $V_{RAMP-SLOPE}$ ) with  $V_{DD}$  = 4.5V and 19V;  $f_{SW}$  = 500kHz;  $V_{SLOPE}$  = 0.4V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.065V/µs minimum and 0.15V/µs maximum.

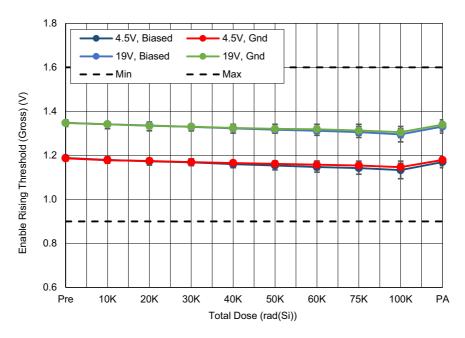

Figure 55. ISL73847SLH rising enable threshold (Gross) ( $V_{IH-EN-G}$ ) with  $V_{DD}$  = 4.5V and 19V; FS =  $V_{CC}$ , as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.9V minimum and 1.6V maximum.

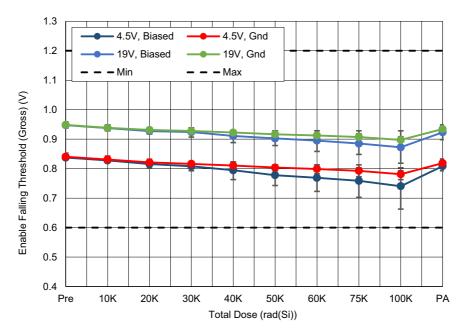

Figure 56. ISL73847SLH falling enable threshold (Gross) ( $V_{IL-EN-G}$ ) with  $V_{DD}$  = 4.5V and 19V; FS =  $V_{CC}$ , as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.6V minimum and 1.2V maximum.

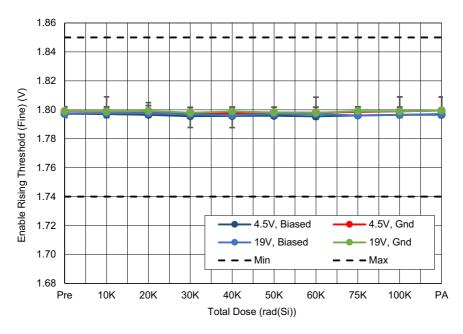

Figure 57. ISL73847SLH rising enable threshold (Fine) ( $V_{IH-EN-F}$ ) with  $V_{DD}$  = 4.5V and 19V; FS =  $V_{CC}$ , as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 1.74V minimum and 1.85V maximum.

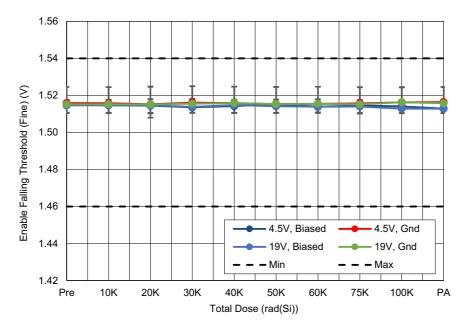

Figure 58. ISL73847SLH falling enable threshold (Fine) ( $V_{IL-EN-F}$ ) with  $V_{DD}$  = 4.5V and 19V; FS =  $V_{CC}$ , as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 1.46V minimum and 1.54V maximum.

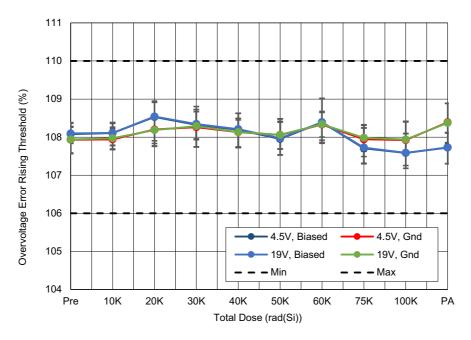

Figure 59. ISL73847SLH overvoltage error threshold rising ( $V_{OVH}$ ) with  $V_{DD}$  = 4.5V and 19V; EN = 3.3V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 106% minimum and 110% maximum.

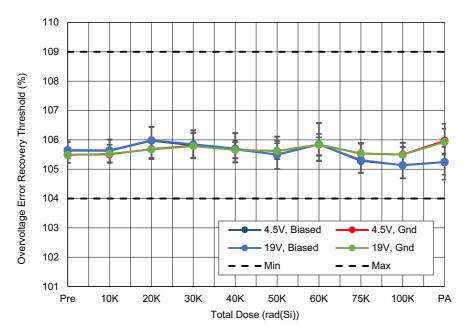

Figure 60. ISL73847SLH overvoltage error threshold recovery ( $V_{OVL}$ ) with  $V_{DD}$  = 4.5V and 19V; EN = 3.3V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 104% minimum and 109% maximum.

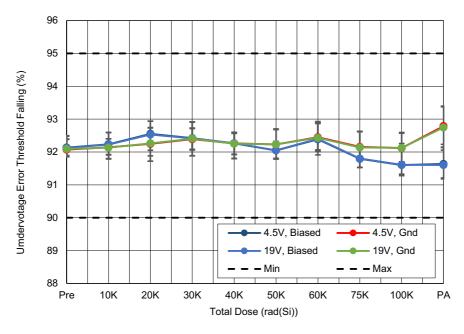

Figure 61. ISL73847SLH undervoltage error threshold ( $V_{UVL}$ ) with  $V_{DD}$  = 4.5V and 19V; EN = 3.3V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90% minimum and 94% maximum.

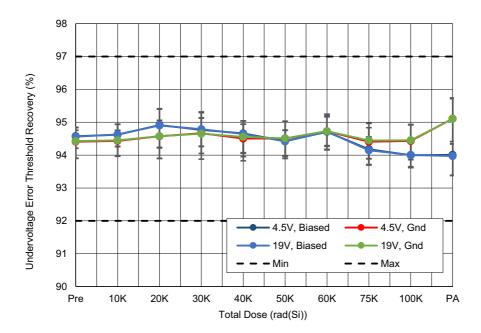

Figure 62. ISL73847SLH undervoltage error threshold recovery ( $V_{UVH}$ ) with  $V_{DD}$  = 4.5V and 19V; EN = 3.3V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 92% minimum and 96% maximum.

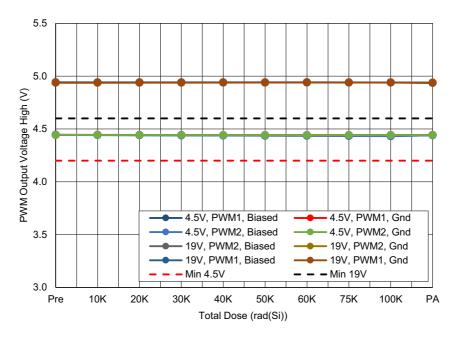

Figure 63. ISL73847SLH PWM output voltage high ( $V_{OH}$ ) with  $V_{DD}$  = 4.5V and 19V;  $I_{PWM}$  = -500 $\mu$ A as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 4V minimum for  $V_{DD}$  = 4.5V and 4.5V minimum for  $V_{DD}$  = 19V.

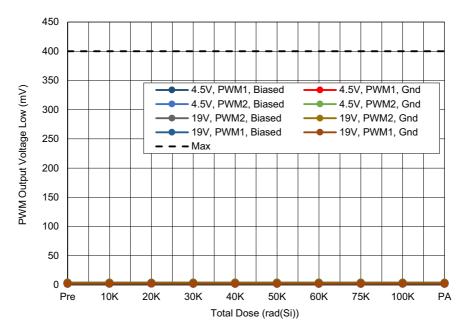

Figure 64. ISL73847SLH PWM output voltage low ( $V_{OL}$ ) with  $V_{DD}$  = 4.5V and 19V;  $I_{PWM}$  = +500 $\mu$ A as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 400mV maximum.

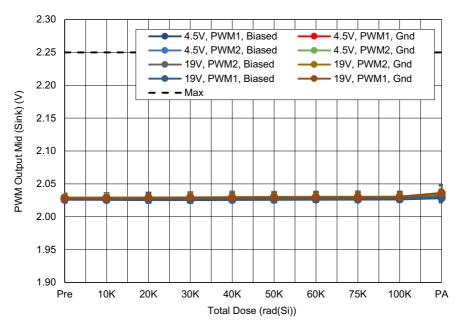

Figure 65. ISL73847SLH PWM output voltage mid sink ( $V_{OZ}$ ) with  $V_{DD}$  = 4.5V and 19V;  $I_{PWM}$  = -100 $\mu$ A, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 2.3V maximum.

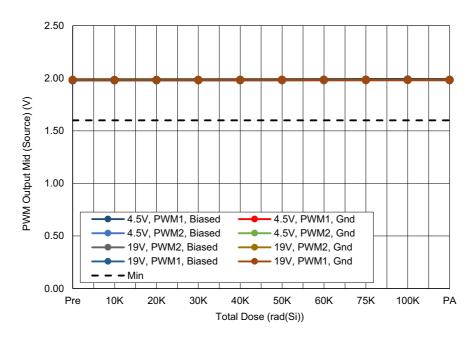

Figure 66. ISL73847SLH PWM output voltage mid source ( $V_{OZ}$ ) with  $V_{DD}$  = 4.5V and 19V;  $I_{PWM}$  = +100 $\mu$ A, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 1.8V minimum.

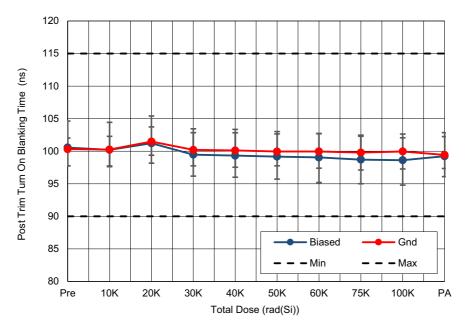

Figure 67. ISL73847SLH post trim turn on blanking time (t<sub>MINONBLK</sub>) as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90ns minimum and 115ns maximum.

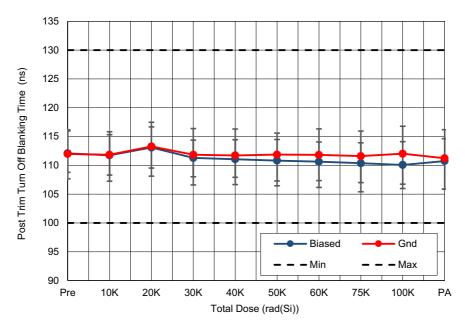

Figure 68. ISL73847SLH post trim turn off blanking time (t<sub>MINOFFBLK</sub>) as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 100ns minimum and 130ns maximum.

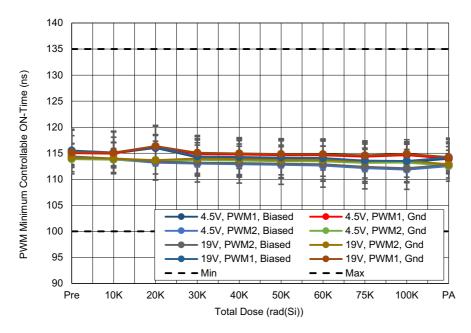

Figure 69. ISL73847SLH PWM minimum controllable ON-time ( $t_{MINCTRLON}$ ) with  $V_{DD}$  = 4.5V and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 100ns minimum and 135ns maximum.

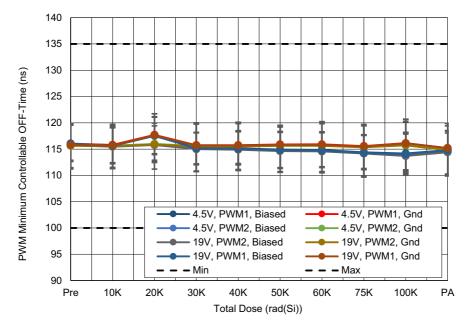

Figure 70. ISL73847SLH PWM minimum controllable OFF-time ( $t_{MINCTRLOFF}$ ) with  $V_{DD}$  = 4.5V and 19V, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 100ns minimum and 135ns maximum.

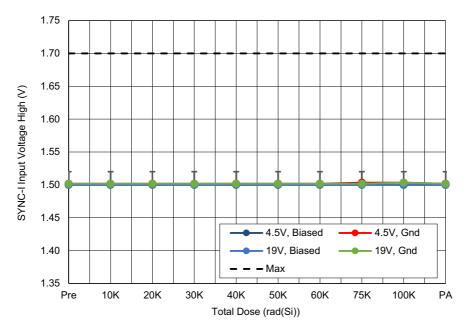

Figure 71. ISL73847SLH SYNC-I input voltage high ( $V_{SYNCH}$ ) with  $V_{DD}$  = 4.5V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 1.7V maximum.

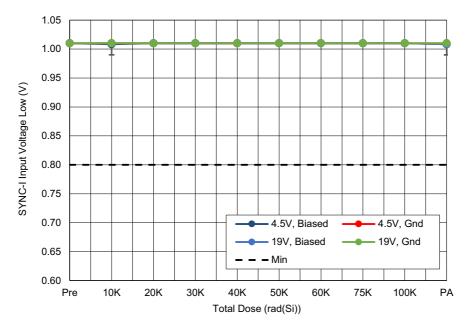

Figure 72. ISL73847SLH SYNC-I input voltage low ( $V_{SYNCL}$ ) with  $V_{DD}$  = 4.5V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 0.8V minimum.

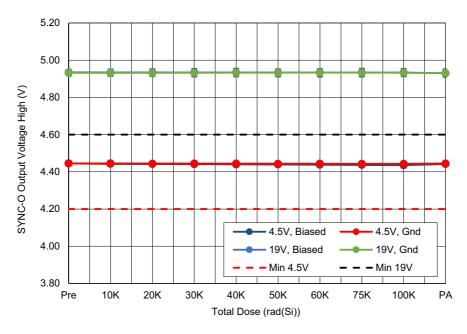

Figure 73. ISL73847SLH SYNC-O output voltage high ( $V_{SYNC-OH}$ ) with  $V_{DD}$  = 4.5V and 19V;  $I_{SYNC-O}$  = -500 $\mu$ A, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 4.2V minimum for  $V_{DD}$  = 4.5V and 4.6V minimum for  $V_{DD}$  = 19V.

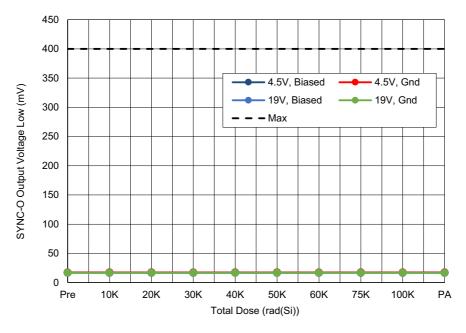

Figure 74. ISL73847SLH SYNC-O output voltage low ( $V_{SYNC-OL}$ ) with  $V_{DD}$  = 4.5V and 19V;  $I_{SYNC-O}$  = +500 $\mu$ A, as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 400mV maximum.

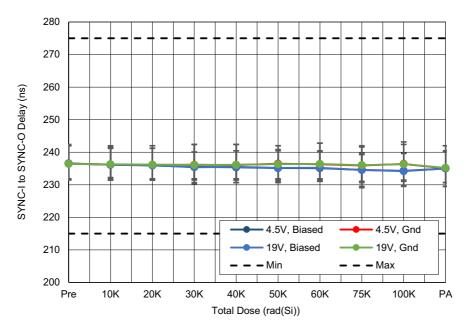

Figure 75. ISL73847SLH SYNC-I to SYNC-O delay ( $t_{SYNC-DLY}$ ) with  $V_{DD}$  = 4.5V and 19V as a function of LDR irradiation and anneal for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 215ns minimum and 275ns maximum.

### 3. Discussion and Conclusion

The results of the LDR total dose testing of critical, selected parameters of the ISL73847SLH synchronous buck controller have been reported. Attributes Data summarizes the attributes data for the test and Key Parameter Variables Data provides plots of the total dose response for the selected parameters.

All tested datasheet parameters passed at all downpoints up to and including the datasheet guaranteed level of 75krad(Si). However, as can be seen in Figure 9 and Figure 10 (Set Point Voltage) at 100krad(Si), one biased unit (SN 5) marginally failed the minimum limit of 0.592 for all four tests. That same unit and two other biased units (SN 7 and SN 12) also slightly failed the post-anneal measurement for those same parametric tests. This characterization also showed a slight sensitivity between biased and grounded parts. The biased measurements and grounded measurements were similar after annealing.

Unit 12 also marginally failed the Offset Voltage maximum limit of 5mV at 100krad(Si) as shown in Figure 42 and Figure 48. None of these marginal parametric failures affected the functionality of the parts.

In conclusion, the ISL73847SLH synchronous buck controller passes all datasheet limits to 75krad(Si) LDR.

# 4. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.00     | Jan 13, 2025 | Initial release. |

# A. Reported Parameters

Table 3 below lists the datasheet parameters that are considered indicative of part performance. These parameters are plotted in Figure 3 through Figure 75. All limits are taken from the ISL73847SLH datasheet, which may also have more details on test conditions.

Table 3. Datasheet Total Dose Parameters (T<sub>A</sub> = 25°C)

| Fig. | Parameter                           | Symbol                                                                                                         | Conditions                                                                                                           | Low<br>Limit | High<br>Limit | Unit  |

|------|-------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------|---------------|-------|

| 3    | Operating Supply Current            | I <sub>DDO</sub>                                                                                               | $V_{DD}$ = 4.5V, 12V, 19V, EN = 3.3V, $f_{SW}$ = 500kHz, $C_L$ = 100pF                                               | 9            | 16            | mA    |

|      |                                     |                                                                                                                | V <sub>DD</sub> = 4.5V, EN = GND                                                                                     | -            | 0.80          | μA    |

| 4    | Shutdown Supply Current             | I <sub>DDSD</sub>                                                                                              | V <sub>DD</sub> = 12V, EN = GND                                                                                      | -            | 17            | μA    |

|      |                                     |                                                                                                                | V <sub>DD</sub> = 19V, EN = GND                                                                                      | -            | 35            | μΑ    |

| 5    | Output Voltage Range                | VCC                                                                                                            | V <sub>DD</sub> = 6V, 19V, I <sub>OUT</sub> = 0mA, 20mA                                                              | 4.7          | 5.3           | V     |

| 6    | Dropout Voltage                     | VCC <sub>DO</sub>                                                                                              | V <sub>DD</sub> = 4.5V, I <sub>OUT</sub> = 50mA                                                                      | 85           | 260           | mV    |

| 7    | V <sub>CC</sub> Foldback Current    | I <sub>CC-SC</sub>                                                                                             | V <sub>DD</sub> = 5.5V, 19V, V <sub>CC</sub> = 0V, EN = 1.6V                                                         | 40           | 90            | mA    |

| 8    | V <sub>CC</sub> Overcurrent Limit   | I <sub>CC-CL</sub>                                                                                             | V <sub>DD</sub> = 5.5V, 19V, V <sub>CC</sub> = 4.5V, EN = 1.6V                                                       | 75           | 130           | mA    |

| 9    | Valta a Oct Daint                   |                                                                                                                | V <sub>REF</sub> = V <sub>DROOP</sub> , V <sub>SEN1</sub> = V <sub>SEN2</sub> = 0mV                                  | 0.500        | 0.005         | .,    |

| 10   | - Voltage Set Point                 | $V_{FB+}$                                                                                                      | V <sub>REF</sub> = V <sub>DROOP</sub> , V <sub>SEN1</sub> = V <sub>SEN2</sub> = 50mV                                 | 0.592        | 0.605         | V     |

| 11   | Soft-Start Sourcing<br>Current      | I <sub>SOFTSTART</sub>                                                                                         | V <sub>DD</sub> = 19V                                                                                                | 9.2          | 10.5          | μA    |

| 12   | Peak Positive Current               | Channel 1) $V_{DD} = 19V; V_{CM} = 0.6V, 5.0V, 19V$ Positive Current $V_{DD} = 4.5V; V_{CM} = 0.6V, 5.0V, 19V$ | V <sub>DD</sub> = 4.5V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                            |              | 82.5          | mV    |

| 13   | Limit (Channel 1)                   |                                                                                                                | V <sub>DD</sub> = 19V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                             | 67.5         |               |       |

| 14   | Peak Positive Current               |                                                                                                                | V <sub>DD</sub> = 4.5V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                            |              |               |       |

| 15   | Limit (Channel 2)                   |                                                                                                                | V <sub>DD</sub> = 19V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                             |              |               |       |

| 16   | Peak Positive Overcurrent           |                                                                                                                | V <sub>DD</sub> = 4.5V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                            |              | 110           | >/    |

| 17   | (Channel 1)                         | V <sub>POC</sub>                                                                                               | V <sub>DD</sub> = 19V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                             | 90           |               |       |

| 18   | Peak Positive Overcurrent           |                                                                                                                | V <sub>DD</sub> = 4.5V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                            |              |               | mV    |

| 19   | (Channel 2)                         |                                                                                                                | V <sub>DD</sub> = 19V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                             |              |               |       |

| 20   | Peak Negative                       |                                                                                                                | V <sub>DD</sub> = 4.5V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                            | -84          |               | mV    |

| 21   | Overcurrent (Channel 1)             |                                                                                                                | V <sub>DD</sub> = 19V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                             |              |               |       |

| 22   | Peak Negative                       | $V_{NOC}$                                                                                                      | V <sub>DD</sub> = 4.5V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                            |              | -60           |       |

| 23   | Overcurrent (Channel 2)             |                                                                                                                | V <sub>DD</sub> = 19V; V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                             |              |               |       |

| 24   | Overvoltage Threshold               | V <sub>(FB, OV)</sub>                                                                                          | V <sub>DD</sub> = 4.5V, 19V                                                                                          | 112          | 118           | %     |

| 25   | Undervoltage Threshold              | V <sub>(FB, UV)</sub>                                                                                          | V <sub>DD</sub> = 4.5V, 19V                                                                                          | 82           | 88            | %     |

| 26   | Error Amplifier<br>Transconductance | g <sub>m-EA</sub>                                                                                              | V <sub>DD</sub> = 4.5V, 19V                                                                                          | 3            | 4             | mA/V  |

| 27   | Droop Transconductance              |                                                                                                                | V <sub>DD</sub> = 4.5V; V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 10mV, 50mV,<br>V <sub>CM</sub> = 0.6V, 5.0V, 19V | - 0.38       | 0.42          |       |

| 28   | (CSA1)                              |                                                                                                                | V <sub>DD</sub> = 19V; V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 10mV, 50mV,<br>V <sub>CM</sub> = 0.6V, 5.0V, 19V  |              |               | μA/mV |

| 29   | Droop Transconductance (CSA2)       | 9m(CSA, DRP)                                                                                                   | V <sub>DD</sub> = 4.5V; V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 10mV, 50mV,<br>V <sub>CM</sub> = 0.6V, 5.0V, 19V |              |               |       |

| 30   |                                     |                                                                                                                | V <sub>DD</sub> = 19V; V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 10mV, 50mV,<br>V <sub>CM</sub> = 0.6V, 5.0V, 19V  |              |               |       |

Table 3. Datasheet Total Dose Parameters ( $T_A = 25^{\circ}C$ )

| Fig. | Parameter                                                 | Symbol                     | Conditions                                                                                    | Low<br>Limit | High<br>Limit | Unit  |

|------|-----------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------|--------------|---------------|-------|

| 31   | IMON Transconductance (CSA1, 1V)                          |                            |                                                                                               |              |               |       |

| 32   | IMON Transconductance<br>(CSA1, 2V)                       |                            | V <sub>DD</sub> = 4.5V; V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 10mV, 50mV,               | 0.36         | 0.47          | μA/mV |

| 33   | IMON Transconductance (CSA2, 1V)                          | 9 <sub>m(CSA, IMON)</sub>  | V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                             |              |               |       |

| 34   | IMON Transconductance<br>(CSA2, 2V)                       |                            |                                                                                               |              |               |       |

| 35   | IMON Transconductance (CSA1, 1V)                          |                            |                                                                                               |              |               | μA/mV |

| 36   | IMON Transconductance<br>(CSA1, 2V)                       |                            | V <sub>DD</sub> = 19V; V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 10mV, 50mV,                | 0.26         |               |       |

| 37   | IMON Transconductance<br>(CSA2, 1V)                       | 9 <sub>m(CSA, IMON)</sub>  | V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                             | 0.36         | 0.47          |       |

| 38   | IMON Transconductance<br>(CSA2, 2V)                       |                            |                                                                                               |              |               |       |

| 39   | Offset Voltage (CSA1)                                     |                            | V = 4 EV V()           = 0.007                                                                |              |               |       |

| 40   | Offset Voltage (CSA2)                                     | V <sub>OS(CSA)</sub>       | $V_{DD} = 4.5V$ , $V(I_{SEN+}, I_{SEN-}) = 0$ mV, $V_{CM} = 0.6V$                             | _            | _             | mV    |

| 41   | Offset Voltage (CSA1)                                     | (Low Side)                 | 400.000                                                                                       | -5           | 5             |       |

| 42   | Offset Voltage (CSA2)                                     | -                          | $V_{DD} = 19V, V(I_{SEN+}, I_{SEN-}) = 0mV, V_{CM} = 0.6V$                                    |              |               |       |

| 43   | Offset Voltage (CSA1)                                     |                            |                                                                                               |              | 5             | mV    |

| 44   | Offset Voltage (CSA2)                                     | -                          | $V_{DD} = 4.5V, V(I_{SEN+}, I_{SEN-}) = 0mV, V_{CM} = 5V$                                     | -5           |               |       |

| 45   | Offset Voltage (CSA1)                                     | -                          | $V_{DD} = 19V$ , $V(I_{SEN+}, I_{SEN-}) = 0$ mV, $V_{CM} = 5V$                                |              |               |       |

| 46   | Offset Voltage (CSA2)                                     | V <sub>OS(CSA)</sub> (High |                                                                                               |              |               |       |

| 47   | Offset Voltage (CSA1)                                     | Side)                      |                                                                                               |              |               |       |

| 48   | Offset Voltage (CSA2)                                     | -                          | $V_{DD} = 4.5V$ , $V(I_{SEN+}, I_{SEN-}) = 0$ mV, $V_{CM} = 19$ V                             |              |               |       |

| 49   | Offset Voltage (CSA1)                                     |                            | V <sub>DD</sub> = 19V, V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 0mV, V <sub>CM</sub> = 19V |              |               |       |

| 50   | Offset Voltage (CSA2)                                     | -                          |                                                                                               |              |               |       |

| 51   | HS CSA Supply Current per Phase (Current into ISENx- pin) | I <sub>CSA</sub>           | V <sub>DD</sub> = 19V; EN = 3.3V; V <sub>CM</sub> = 2.7V                                      | -            | 3             | μА    |

| 52   | Oscillator Frequency                                      | f <sub>OSC-0.5M</sub>      | $V_{DD}$ = 4.5V, 19V, $R_{FS}$ = 205kΩ, EN = 3.3V, $R_{SYNC-O}$ = 100kΩ to GND                | 0.45         | 0.55          | MHz   |

| 53   | Range                                                     | f <sub>OSC-3M</sub>        | $V_{DD}$ = 4.5V, 19V, $R_{FS}$ = 16.7kΩ, EN = 3.3V, $R_{SYNC-O}$ =100kΩ to GND                | 2.70         | 3.30          | MHz   |

| 54   | Ramp Slope                                                | V <sub>RAMP-SLOPE</sub>    | V <sub>DD</sub> = 4.5V, 19V, f <sub>SW</sub> = 500kHz, V <sub>SLOPE</sub> = 0.4V              | 0.06         | 0.15          | V/µs  |

| 55   | Rising Enable Threshold (Gross)                           | V <sub>IH-EN-G</sub>       | V <sub>DD</sub> = 4.5V, 19V, FS = V <sub>CC</sub>                                             | 0.9          | 1.6           | ٧     |

| 56   | Falling Enable Threshold (Gross)                          | V <sub>IL-EN-G</sub>       | V <sub>DD</sub> = 4.5V, 19V, FS = V <sub>CC</sub>                                             | 0.6          | 1.2           | V     |

| 57   | Rising Enable Threshold (Fine)                            | V <sub>IH-EN-F</sub>       | V <sub>DD</sub> = 4.5V, 19V, FS = V <sub>CC</sub>                                             | 1.74         | 1.85          | V     |

| 58   | Falling Enable Threshold (Fine)                           | V <sub>IL-EN-F</sub>       | V <sub>DD</sub> = 4.5V, 19V, FS = V <sub>CC</sub>                                             | 1.46         | 1.54          | V     |

| 59   | Overvoltage Error<br>Threshold                            | V <sub>OVH</sub>           | V <sub>DD</sub> = 4.5V, 19V, EN = 3.3V                                                        | 106          | 110           | %     |

| 60   | Overvoltage Error<br>Threshold Recovery                   | V <sub>OVL</sub>           | V <sub>DD</sub> = 4.5V, 19V, EN = 3.3V                                                        | 104          | 109           | %     |

Table 3. Datasheet Total Dose Parameters ( $T_A = 25^{\circ}C$ )