## 4RCD0124KC0

DDR4 Register Command Address Buffer with Parity

# **Description**

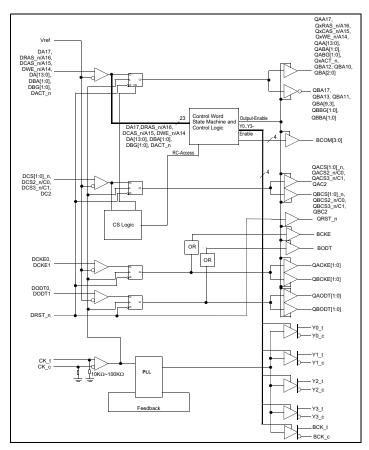

The 4RCD0124KC0 is a 32-bit 1:2 register command, address buffer with parity, and is designed for 1.2V VDD operation.

All inputs are pseudo-differential with an external or internal voltage reference. All outputs are full-swing CMOS drivers optimized to drive single-terminated  $25\Omega$  to  $50\Omega$  traces in DDR4 RDIMM and LRDIMM applications. The clock outputs Yn\_t and Yn\_c and control net outputs QxCKEn, QxCSn, and QxODTn can be driven with a different strength to compensate for different DIMM net topologies. By disabling unused outputs the power consumption is reduced.

The 4RCD0124KC0 operates from a differential clock (CK\_t and CK\_c). Inputs are registered at the crossing of CK\_t going HIGH, and CK\_c going LOW. The input signals can be either re-driven to the outputs or can be used to access device internal control registers when certain input conditions are met.

### **Features**

- Pinout optimized DDR4 RDIMM PCB layout

- DDR4-1600/1866/2133/2400

- Supports CKE Power Down operation modes

- Support Quad Chip Select Operation

- · Direct Dual CS Mode

- · Direct QuadCS Mode

- · Encoded QuadCS Mode

- Provides access to internal control words for configuring the device features and adapting in different RDIMM and system applications

- Compliant to JEDEC DDR4RCD01 Spec rev 1.0

- Available in 253-ball Dual-Pitch (0.50mm/0.65mm),

15 x 20 grid, Rectangular Ball Grid Array Package

# **Applications**

Servers with DIMM data rates up to 2400

Figure 1. Block Diagram

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.