# Application Note 8-bit SISO, SIPO, PISO, PIPO Shift Registers

# **AN-CM-303**

#### Abstract

This application note shows how to implement various 8-bit shift registers within the GreenPAK IC. Serial in serial out, Serial in parallel out, Parallel in serial out, and Parallel in parallel out shift registers have been designed in the examples.

The application note comes complete with a design file which can be found in the Reference section.

## Contents

| Ab  | stract                    | . 1 |

|-----|---------------------------|-----|

| Со  | ntents                    | . 2 |

| Fig | jures                     | 2   |

| Та  | bles                      | 2   |

| 1   | Terms and Definitions     | 3   |

| 2   | References                | 3   |

| 3   | Introduction              | 4   |

| 4   | SISO Shift Register       |     |

| 5   | SIPO Shift Register       | 5   |

| 6   | PISO Shift Register       | 8   |

| 7   | PIPO Shift Register1      | 10  |

| 8   | GreenPAK Cost Advantage 1 | 12  |

| 9   | Conclusions1              | 12  |

| Re  | vision History            | 13  |

# **Figures**

| Figure 1: 8-bit Serial In Serial Out Shift Register                       | 4  |

|---------------------------------------------------------------------------|----|

| Figure 2: Timing Diagram of 8-bit Serial In Serial Out Shift Register     | 5  |

| Figure 3: 8-bit Serial In Parallel Out Shift Register                     | 6  |

| Figure 4: Timing Diagram of 8-bit Serial In Parallel Out Shift Register   | 7  |

| Figure 5: 8-bit Parallel In Serial Out Shift Register                     | 8  |

| Figure 6: Timing Diagram of 8-bit Parallel In Serial Out Shift Register   | 9  |

| Figure 7: 8-bit Parallel In Parallel Out Shift Register                   | 10 |

| Figure 8: Timing Diagram of 8-bit Parallel In Parallel Out Shift Register | 11 |

## **Tables**

| Table 1: Comparison of Other ICs Available in Market | 12 |

|------------------------------------------------------|----|

|------------------------------------------------------|----|

| -  |     |       |    |     |  |

|----|-----|-------|----|-----|--|

| Δr | n   | icati | on | Not |  |

|    | יאי | Jouri |    |     |  |

#### **1** Terms and Definitions

| DFF  | D-Flipflop                   |

|------|------------------------------|

| GPIO | General purpose input/output |

| PIPO | Parallel in parallel out     |

| PISO | Parallel in serial out       |

| SIPO | Serial in parallel out       |

| SISO | Serial in serial out         |

#### 2 References

For related documents and software, please visit:

#### GreenPAK<sup>™</sup> Programmable Mixed-Signal Products | Renesas

Download our free GreenPAK<sup>™</sup> Designer software [1] to open the .gp files [1] and view the proposed circuit design. Use the GreenPAK development tools [2] to freeze the design into your own customized IC in a matter of minutes. Find out more in a complete library of application notes [3] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] Go Configure<sup>™</sup> Software Hub | Renesas

- [2] AN-CM-303, 8-bit SISO, SIPO, PISO, PIPO Shift Registers.gp, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

- [5] SLG46533, Datasheet

## 3 Introduction

Registers are sequential circuits made with flipflops to store and transfer binary information. Shift registers are primarily made with D flipflops in a daisy chain structure. These flipflops can each store one bit of binary information, all of which are controlled by a shared input clock. DFF's can read and store the value of the input signal at every rising edge of the clock. This property of the DFF can be used to build various registers. Different forms of registers like SISO, SIPO, PISO, PIPO are differentiated by the way data is loaded and retrieved.

The implementation shown in this application note consists of 8-bit shift registers which are designed with GreenPAK SLG46533 IC [5]. The number of bits in a shift register corresponds to the number of flipflops present; in this design eight DFFs are used.

## 4 SISO Shift Register

SISO is one of the most basic forms of the shift registers. The data is loaded serially and retrieved serially. The output of the first DFF is fed into the input of the next DFF at each clock cycle, eventually reaching the last DFF / Output. This Shift register output is delayed from the input. The shift register shifts, or streams, one-bit data per clock cycle.

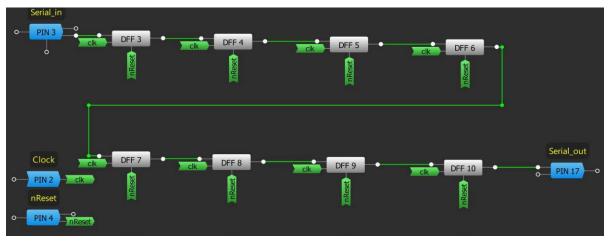

Figure 1: 8-bit Serial In Serial Out Shift Register

As shown in the design above, DFF3 is fed with the input data bits serially and the output is taken from DFF10 serially. All the DFFs share the same clock. nReset is set high to ensure that all DFF's are enabled for normal operation.

The timing diagram shown below has clock and input data stream as first and second waveforms. The rest of the waveforms show how the output of each DFF shifts serially. If we consider the first 8 input bits which are 10011010, we can clearly observe that these 8 bits appear one after another by the 8th rising edge clock at the output of DFF10

One of the main applications of the SISO register is to act as a delay element. The delay can be controlled by the number of stages in the register and the frequency of the clock. In the design below the clock is at 1kHz, so the delay that is observed is 7 ms.

| A  |       | 41.0.0 | Mate |

|----|-------|--------|------|

| Ар | piica | ποη    | Note |

**Revision 1.0**

| [P] dk                     | +2 ms                                                                                                           | <br>+4 ms | <u> </u> | ims<br>I i | +8                                      |        |                                 | ) ms<br>I I | +12 m |

|----------------------------|-----------------------------------------------------------------------------------------------------------------|-----------|----------|------------|-----------------------------------------|--------|---------------------------------|-------------|-------|

| High -                     |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] PIN 3 -> OUT<br>High - |                                                                                                                 | <br>      |          |            |                                         |        |                                 |             |       |

| Low                        |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] DFF 3 -> Q<br>High -   |                                                                                                                 | <br>      |          |            |                                         |        |                                 |             |       |

| Low -                      |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] DFF 4 -> Q<br>High –   |                                                                                                                 |           |          |            |                                         | ****** |                                 |             |       |

| Low -                      |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] DF∓ 5 -> Q<br>High ¬   | sonara a constructiva de la constru |           |          |            |                                         |        | municipation and an an an and a |             |       |

| Low -                      |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] DFF 6 -> Q<br>High ¬   |                                                                                                                 |           |          |            | \$1000000000000000000000000000000000000 |        |                                 |             |       |

| Low                        |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] DFF 7 -> Q<br>High →   |                                                                                                                 | <br>      |          |            |                                         |        |                                 |             | -     |

| Low -                      |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] DFF 8 -> Q<br>High →   |                                                                                                                 | <br>      |          |            |                                         |        |                                 |             |       |

|                            |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] DFF 9 -> Q<br>High     |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| Low -                      |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| [P] DFF 10 -> Q<br>High    |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| Low                        |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| 4.0 V<br>3.0 V<br>2.0 V    |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

| 1.0V<br>0.0V<br>1.0V       |                                                                                                                 |           |          |            |                                         |        |                                 |             |       |

Figure 2: Timing Diagram of 8-bit Serial In Serial Out Shift Register

## 5 SIPO Shift Register

In this type of shift register, the data is sent serially and retrieved in parallel. All the DFF's are clocked by the same clock and nReset is used to ensure that all the DFF's are enabled for normal operation. The data is fed serially into DFF3. All the parallel outputs are from the outputs of the DFF that are present in the shift register. The output of each intermediate DFF is fed as input to the next DFF. All 8 input serial bits will be available at the parallel outputs after 8 rising edges of the clock.

| Appl | lication | Note |  |

|------|----------|------|--|

|      | louion   |      |  |

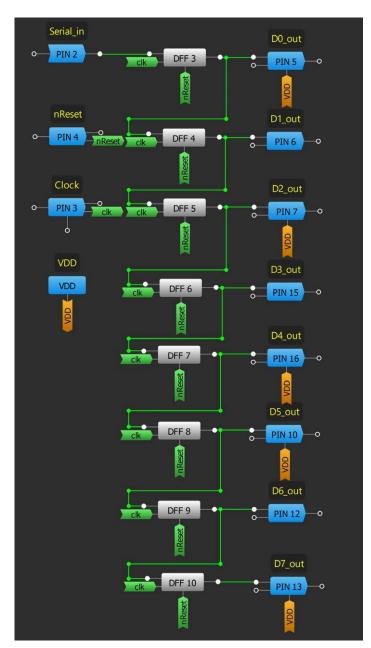

Figure 3: 8-bit Serial In Parallel Out Shift Register

The timing diagram of the SIPO shift register is shown in Fig 4. It has a clock and Serial Data-in as the first two waveforms, and all other waveforms are the outputs of the DFF's. It can be observed that after the 8<sup>th</sup> rising edge of the clock, the entire input data bits are visible at the output of each DFF.

The first bit which is transmitted serially is observed at the last DFF's output. The main application of the SIPO shift register is data conversion in many digital applications. Sometimes the SIPO shift register is connected to the output of a microprocessor when more GPIO pins are required. In the above design, the clock frequency is 1 kHz and the time taken to convert the 8 serial bits to parallel bits is 8 ms.

**Application Note**

**Revision 1.0**

Figure 4: Timing Diagram of 8-bit Serial In Parallel Out Shift Register

**Application Note**

Revision 1.0

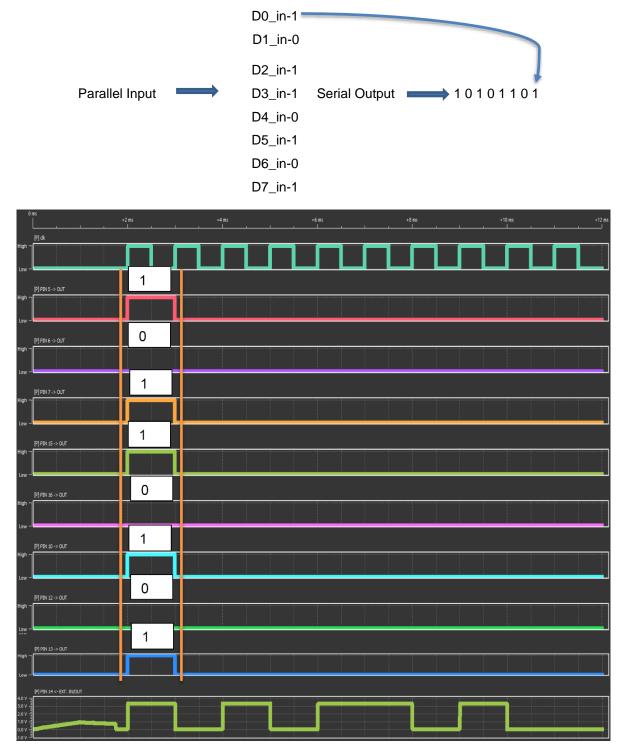

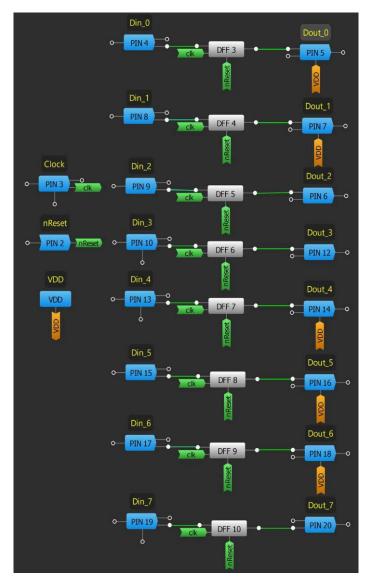

#### 6 PISO Shift Register

The PISO shift register is the converse of the SIPO shift register. The inputs are presented simultaneously in parallel, and the output is retrieved serially. The data is taken out one bit per clock cycle. The main point to note in this shift register is that a clock is not required to load the data in the shift register, whereas a clock is required to unload the data.

Similar to the other shift registers, all the DFF's are clocked by the same clock and have the nReset set high for normal operation. 2-bit lookup tables provided in the IC are used as OR gates to provide parallel input to the DFF's as well as transmit the output of one DFF as the input to the next DFF. The output is retrieved serially from the output of DFF10.

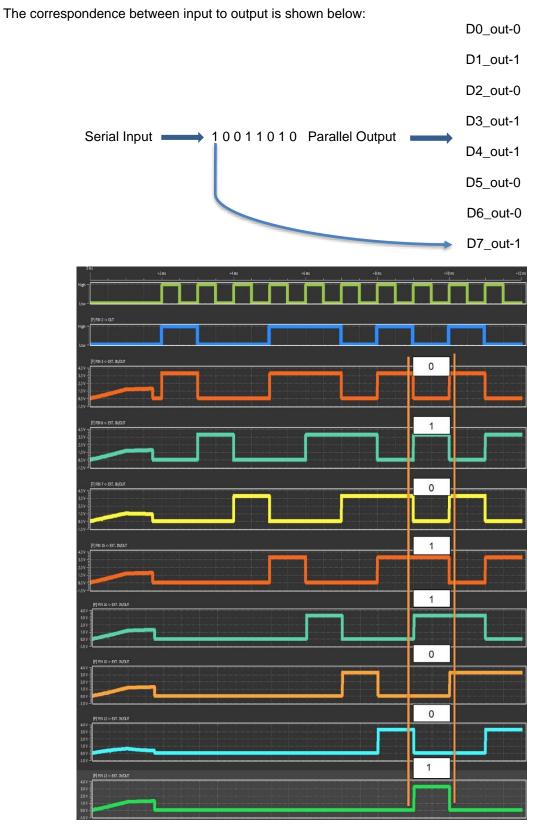

Figure 5: 8-bit Parallel In Serial Out Shift Register

This type of shift register is typically used for data conversion from parallel to serial. All the parallel bits with the data are serially transmitted to the single input of a microprocessor which helps in using fewer input pins of the microprocessor.

The timing diagram shown in Fig. 6 depicts the clock and all parallel inputs, highlighted between two vertical orange lines. The last waveform is the serial data out which shows how all the parallel inputs are converted into a serial bitstream.

### AN-CM-303

#### 8-bit SISO, SIPO, PISO, PIPO Shift Registers

The way how inputs correspond to output is shown below.

Figure 6: Timing Diagram of 8-bit Parallel In Serial Out Shift Register

| ۸m | nling | tion | Noto |

|----|-------|------|------|

| rμ | μποσ  |      | Note |

**Revision 1.0**

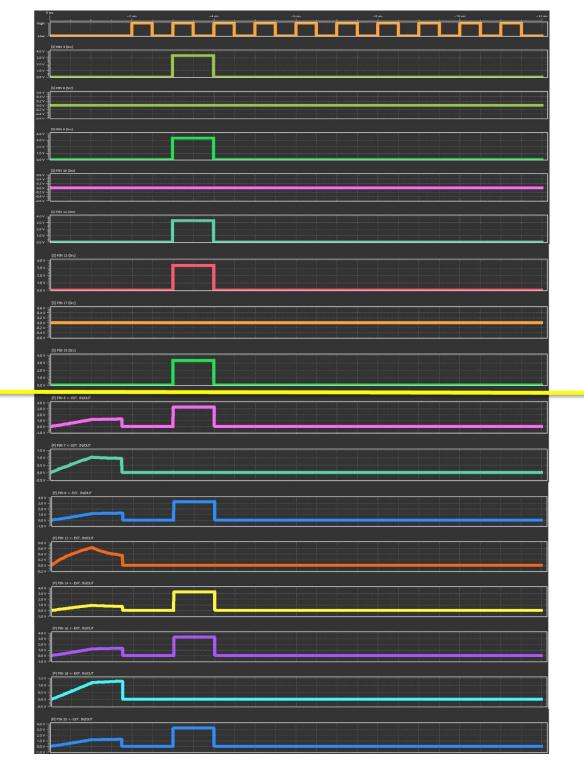

## 7 PIPO Shift Register

This shift register is the converse of the SISO shift register. The input data is given and retrieved in parallel. The output changes with respect to the input within the same clock cycle. Similar to the PISO shift register, a clock is not required to load data into the flipflops, but to latch and transfer out. Hence a PIPO shift register can be used as a temporary storage device, though in practice other GreenPAK capabilities are often included within the design. Whenever new data output is required, a rising edge clock presents the DFF content to the output. One note about this shift register is that there is no connection between individual DFFs. Similar to other shift registers, the same clock and nReset are applied to all the DFF's.

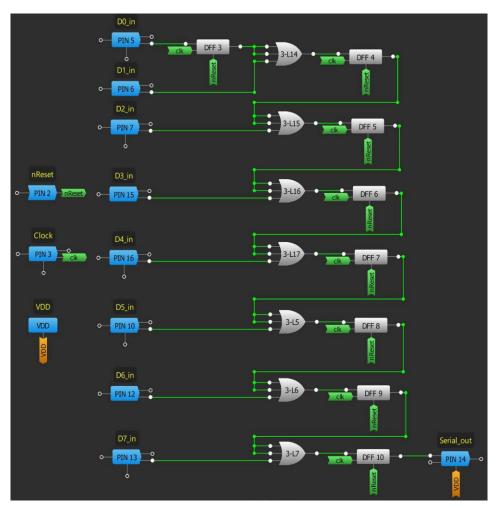

Figure 7: 8-bit Parallel In Parallel Out Shift Register

The timing diagram of the PIPO shift register is shown in Fig. 8. As all the inputs and outputs are loaded and unloaded separately, it results in a large number of waveforms to show. The yellow highlighted line in the waveforms separates the input and the output. All the top waveforms are inputs and the bottom waveforms are outputs. It's clearly visible from the waveforms that the loaded data can be retrieved with a single clock pulse.

| A   | the extreme | Mate |

|-----|-------------|------|

| ADD | lication    | Note |

|     |             |      |

**Revision 1.0**

Figure 8: Timing Diagram of 8-bit Parallel In Parallel Out Shift Register

| App | lication | Note |

|-----|----------|------|

**Revision 1.0**

#### 8 GreenPAK Cost Advantage

The GreenPAK SLG46533 IC is a very versatile Programmable Mixed-Signal ASIC. Many applications have been implemented with this IC. Table 1 shows some of the competing IC's that are available in the market for shift register applications.

#### Table 1: Comparison of Other ICs Available in Market

| IC           | Quantity | Price   | Package/Size                    |

|--------------|----------|---------|---------------------------------|

| TPIC6C596PWR | 1        | \$ 1.10 | TSSOP (16)<br>5.00 mm × 4.40 mm |

| MM74HC595MX  | 1        | \$ 0.58 | TSSOP (16)<br>5.00 mm x 4.40 mm |

| SN74HC595    | 1        | \$ 0.95 | TSSOP (16)<br>5.00 mm × 4.40 mm |

**Note 1** All the prices of the ICs are referred from Digi-Key on 08-05-2020.

GreenPAK SLG46533 IC is of size 2.00 mm x 3.00 mm and costs less than \$ 0.50. It is clearly visible that the GreenPAK IC is one of the best solutions that are available in the market. Moreover, the user has control over the configuration of the IC in GreenPAK, which increases its value.

#### 9 Conclusions

Shift registers are an integral part of any digital system. In this application note, four types of shift registers, SISO, SIPO, PISO, PIPO have been configured within the GreenPAK SLG46533 IC. The 8-bit shift registers in this application note form a viable alternative to other shift registers available on the market. The GreenPAK SLG46533 IC has the advantage of low PCB area footprint, more circuitry available, and lower cost.

# **Revision History**

| Revision | Date        | Description      |

|----------|-------------|------------------|

| 1.0      | 11-Sep-2020 | Initial version. |

**Application Note**

**Revision 1.0**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.