# Application Note DC Power Line Communication AN-CM-318

## Abstract

This application note presents a low cost, low power, capacitor-coupled, DC power-line communication system based on the GreenPAK SLG46108 device.

This application note comes complete with design files which can be found in the references section.

# Contents

| Ab  | stract                | 1 |

|-----|-----------------------|---|

| Со  | ntents                | 2 |

| Fig | jures                 | 2 |

| 1   | Terms and Definitions | 3 |

| 2   | References            | 3 |

| 3   | Introduction          | 4 |

| 4   | TX/RX Operation       | 4 |

| 5   | Circuit Analysis      |   |

| 6   | GreenPAK Design       | 6 |

|     | 6.1 Pin Configuration | 7 |

|     | 6.2 Modulation        | 7 |

|     | 6.3 Demodulation      | 7 |

| 7   | Application Schematic | 8 |

| 8   | Measurements          | 9 |

| 9   | Conclusion1           | 2 |

| Re  | vision History1       | 3 |

# **Figures**

| 4<br>5<br>5 |

|-------------|

| 3           |

| •           |

| 3           |

| 7           |

| 3           |

| 9           |

| 9           |

| )           |

| )           |

| 1           |

| 1           |

| 2           |

|             |

## **1** Terms and Definitions

PLCPower Line CommunicationLUTLook Up Table

#### 2 References

For related documents and software, please visit:

https://www.dialog-semiconductor.com/configurable-mixed-signal.

Download our free GreenPAK Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to modify the design into your own customized IC in a matter of minutes. Find out more in a complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] GreenPAK Designer Software, Software Download and User Guide

- [2] AN-CM-318 Power Line Communication.gp, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

- [5] SLG46108, Datasheet

Author: James Li

This article was originally published on Power Electronics News.

**Application Note**

**Revision 1.0**

# 3 Introduction

This application note presents a method to use a DC power line for data communication while simultaneously providing power without interruption. This is accomplished via RLC coupling circuits together with GreenPAK IC's providing modulation (TX) and demodulation (RX).

## 4 TX/RX Operation

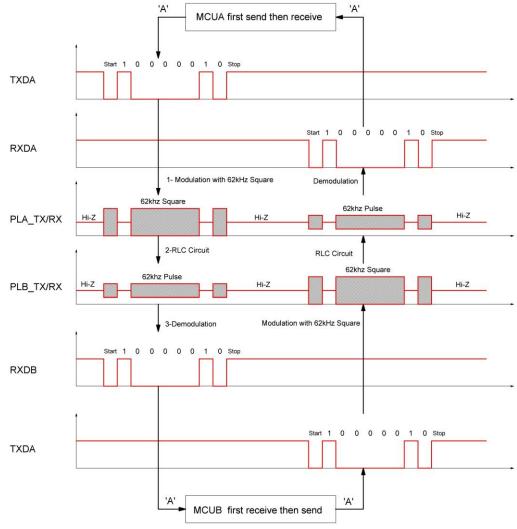

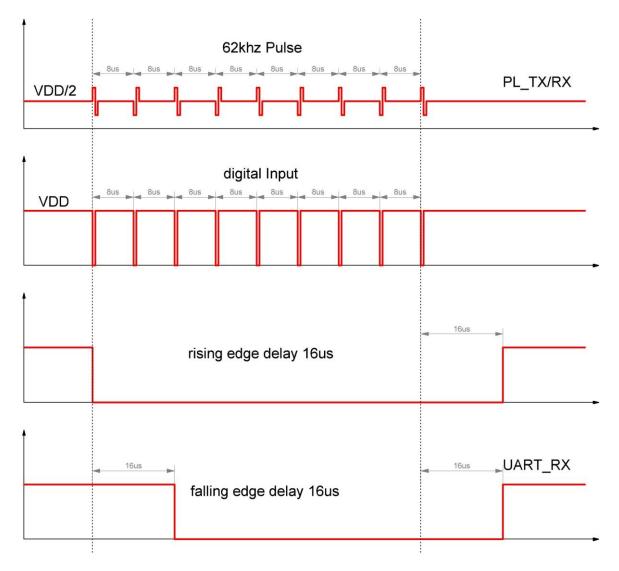

The communication signal on this power line is On-Off Key (OOK) modulated. GreenPAK IC's perform the OOK modulation / demodulation of UART digital signals using of 62kHz carriers generated from within the GreenPAK IC's. Figure 1 shows UART communication between side A and B. TXD\_ and RXD\_ are the digital UART signals as seen by the system MCU's at each end; PL\_TX/RX are the signals coupled to/from the power line.

Figure 1: Operation Timing Diagram

## 5 Circuit Analysis

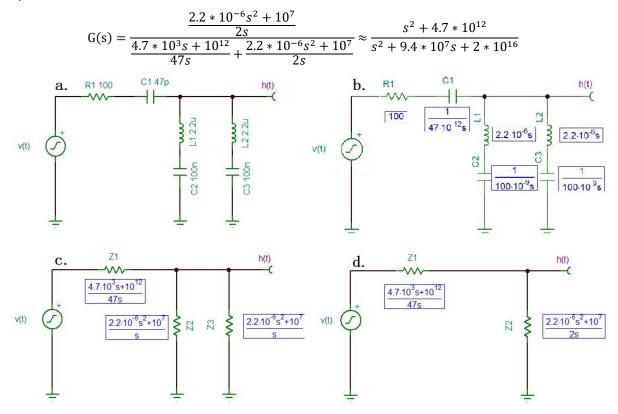

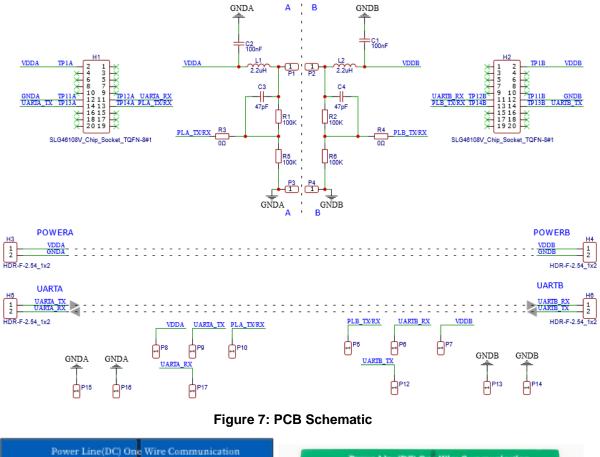

The RLC coupling circuit is shown in Figure 7. The analysis is of the circuit under non-ideal (rising edge equals 10ns) step signal. The s-domain model of the non-ideal step signal can be obtained by Laplace transform of the time domain expression.

| Application Note Revisi | on 1.0 06-Sept-2021 |

|-------------------------|---------------------|

|-------------------------|---------------------|

$$\mathbf{v}(t) = \frac{5}{t_r} * t * [\mathbf{u}(t) - \mathbf{u}(t - t_r)] + 5 * \mathbf{u}(t - t_r) \xrightarrow{Laplace} \mathbf{V}(s) = \frac{5}{t_r} * \frac{1}{s^2} * (1 - e^{-t_r s})$$

The s-domain model of the circuit obtained by replacing the circuit components with its s-domain model and simplify(a>b>c>d). This process is shown in Figure 2. R1 represents the output impedance of GPIO.

Figure 2: RLC Circuit Simplification in s-Domain

Multiply the mode of the circuit with the input signal to get the response function in s-domain:

$$H(s) = V(s) * G(s) = \frac{5}{10 * 10^{-9}} * \frac{1}{s^2} * (1 - e^{-10 \times 10^{-9}s}) * \frac{s^2 + 4.7 \times 10^{12}}{s^2 + 9.4 \times 10^7 s + 2 \times 10^{16}}$$

The response in time domain can be obtained by performing the inverse Laplace transform of the function:

$$h(t) = \begin{cases} 3.76 * e^{-4.7 * 10^7 t} \sin(1.33 * 10^8 t), & 0 \le t \le 10 * 10^{-9} \\ 6.3 * e^{-4.7 * 10^7 t} \sin(1.33 * 10^8 t + 68.3^\circ), & t > 10 * 10^{-9} \end{cases}$$

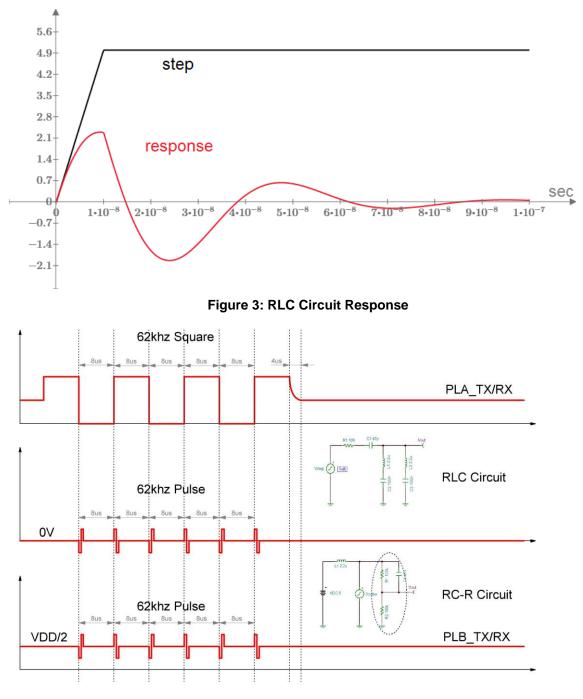

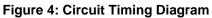

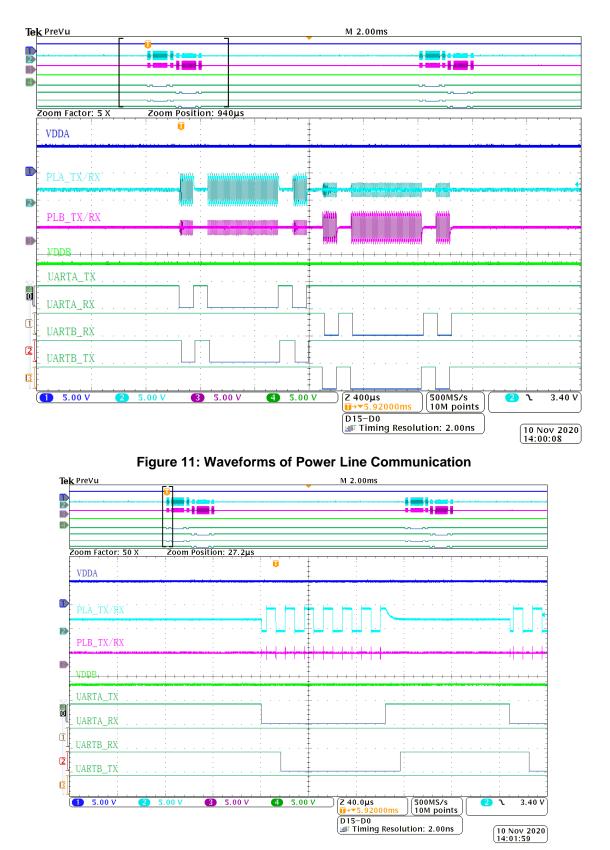

The response curve is shown in Figure 3. The rising and falling edges of PL\_TX are converted into pulses. Figure 4 summarizes the impact of the circuit. In order to prevent the PL\_RX PIN from receiving a negative voltage, the pulse is DC biased to VDD/2 by the RC-R circuit.

| Δ | n | nl | ica         | tic | n | N | ote |

|---|---|----|-------------|-----|---|---|-----|

|   | μ | рι | <b>i</b> ca | uc  |   |   | ULE |

**Revision 1.0**

## 6 GreenPAK Design

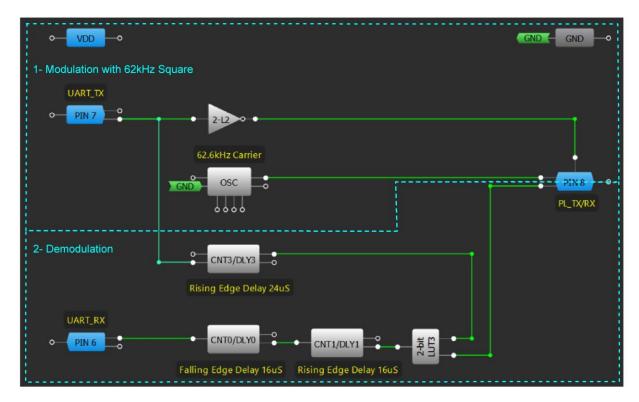

The GreenPAK-SLG46108V developed in GreenPAK Designer is shown in Figure 5.

| Application Note | Revision 1.0 |

|------------------|--------------|

|                  |              |

Figure 5: SLG46108 GreenPAK Design

#### 6.1 **Pin Configuration**

The PIN7(UART\_TX) is used to receive the serial port signal. After being modulated, it is sent to the power line through the PIN8 (PL\_TX/RX). PIN7(UART\_TX) is set as digital input without Schmitt trigger with pull up resistor.

The signal received from PL\_TX/RX is demodulated and output to PIN6(UART\_RX), PIN6 is set as digital output push-pull.

PIN8(PL\_TX/RX) is configured as a digital input/output. When PIN7(UART\_TX) is a low level, PL\_TX/RX is in output mode, otherwise its input mode.

#### 6.2 Modulation

This design is for a 9600bps baud-rate, so the carrier frequency needs to be greater than 48kHz. We configure OSC power mode to force power on, OSC frequency to 2Mhz/8, output0 second divider by 4 to get a 62.6kHz carrier.

As shown in Figure 1, when UART\_TX is a low level, PL\_TX/RX outputs the carrier. When UART\_TX is a high level, PL\_TX/RX is in a high-impedance input state.

#### 6.3 Demodulation

After PL\_TX/RX stops outputting the carrier and re-biased to VDD/2 by the RC-R circuit, we start to demodulate the signal input by PL\_TX/RX. The time required to re-bias to VDD/2 can be measured by an Oscilloscope. We set DLY3 to rising edge delay 24us which is greater than the measured time, 2-bit LUT3 sets to high when DLY3 inputs low.

| Application Note | Revision 1.0 | 06-Sept-2021 |  |

|------------------|--------------|--------------|--|

|                  |              |              |  |

As shown in Figure 6, PL\_TX/RX receives the signal from the power line and converts it into a digital pulse, then is demodulated by DLY1(rising edge delay 16us). In order to ensure that the low-level time after demodulation is equal to before modulation, delay the demodulated signal by DLY0(falling edge delay 16us).

Since the bias voltage of PL\_TX/RX is VDD/2, when PL\_TX/RX is in digital input mode, the device will consume approximately 70uA of extra current.

#### Figure 6: Demodulation

## 7 Application Schematic

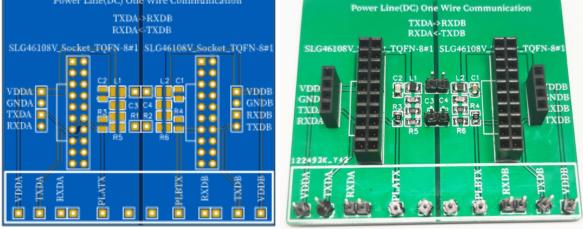

Figure 7 depicts the schematic of the power line interface on a PCB with SLG46108 sockets. Figure 8 shows the picture of the PCB with its prototype. Two IC sockets will plug directly into the 2x10 female socket like Figure 9.

|    |      |       | -    |      |

|----|------|-------|------|------|

| Δn | nlia | catio | nn M | lote |

|    |      | Jui   |      | 10LC |

**Revision 1.0**

Figure 8: PCB with Prototype

#### 8 Measurements

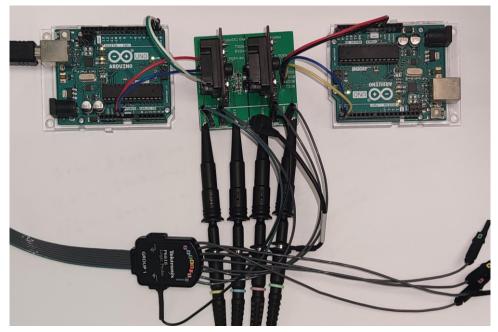

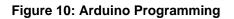

The board was tested with two Arduino boards as shown in Figure 9, Arduino A power by USB, Arduino B power by the power line. Figure 10 shows the Arduino programming used in the test. Arduino A sends a character 'A' every 10ms, Arduino B returns the received character. Figure 11 shows the waveform obtained in the test. Figure 12 shows the detail of the signal sent by PLA\_TX/RX. Figure 13 shows the detail of the pulse received by PLB\_TX/RX.

| Application Note | Revision 1.0 | 06-Sept-2021 |

|------------------|--------------|--------------|

|                  |              |              |

Figure 9: Testing with Arduino

```

//Arduino B Program

//Arduino A Program.

int inByte = 0;

void setup()

void setup()

{

// start serial port at 9600 bps:

Serial.begin(9600);

Serial.begin(9600);

while (!Serial) {}

while (!Serial) {}

}

void loop()

if (Serial.available() > 0)

void loop()

{

//send the received byte

//send 'A' every 10mS

inByte = Serial.read();

Serial.write('A');

Serial.write(inByte);

delay(10);

}

```

Figure 12: The detail of the signal sent by PLA\_TX/RX

**Application Note**

**Revision 1.0**

Figure 13: The detail of the signal received by PLB\_TX/RX

#### 9 Conclusion

This application note presents how to implement a low cost, low power, DC power line communication based on GreenPAK and capacitive coupling. Compared with other solutions, the main advantage of GreenPAK is that the communication method or content can be modified as needed. For example, you can easily modify the carrier frequency to suit the required communication baud rate. In addition, you can use the DFF inside the GreenPAK IC to form parallel-to-serial components, directly serialize the IO state and transmit it to the power line without the involvement of the MCU. The GreenPAK which includes ACMPs can easily transmit the battery level information into the power line.

| -   |          |      |

|-----|----------|------|

| App | lication | Note |

|     |          |      |

# **Revision History**

| Revision | Date        | Description      |

|----------|-------------|------------------|

| 1.0      | 6-Sept-2021 | Initial version. |

**Application Note**

**Revision 1.0**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.