### F1485 - Multi-Carriers with Wider IBW

This document provides information for the F1485 under the operation of multi-carrier signals with instantaneous bandwidths (IBW) of up to 400MHz at the 3300MHz to 4200MHz frequency range. Within this document are the updated BOM table, measured ACLR with DPD performance at  $f_0 = 3.55$ GHz for 1-Carrier-100MHz signal, 2-Carrier-100MHz signal with IBW = 200MHz and 400MHz, and the RF performance plots with the updated BOM.

### Contents

| Evaluation Kit Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.   | Introduction                                                                           | 2 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------|---|

| 4. Bill of Materials  5. Measured RF Performance with Updated BOM  6. Revision History  Figure S  Figure 1. ACLR of F1485 MB with Optimized BOM (f <sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 200MHz)  Figure 2. ACLR of F1485 MB with Optimized BOM (f <sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 400MHz)  Figure 3. Application Circuit Electrical Schematic  Figure 4. Gain                                                                               | 2.   | Measured ACLR Results                                                                  | 2 |

| 5. Measured RF Performance with Updated BOM  6. Revision History  Figures  Figure 1. ACLR of F1485 MB with Optimized BOM (fo = 3.55GHz, 2C-100MHz, IBW = 200MHz)  Figure 2. ACLR of F1485 MB with Optimized BOM (fo = 3.55GHz, 2C-100MHz, IBW = 400MHz)  Figure 3. Application Circuit Electrical Schematic  Figure 4. Gain.  Figure 5. Reverse Isolation.  Figure 6. Input Return Loss  Figure 7. Output Return Loss  Figure 8. OIP3.  Figure 9. OP1dB. | 3.   | Evaluation Kit Schematic                                                               | 4 |

| Figures  Figure 1. ACLR of F1485 MB with Optimized BOM (f <sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 200MHz)                                                                                                                                                                                                                                                                                                                                               | 4.   | Bill of Materials                                                                      | 5 |

| Figure 1. ACLR of F1485 MB with Optimized BOM (f <sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 200MHz)                                                                                                                                                                                                                                                                                                                                                        | 5.   | Measured RF Performance with Updated BOM                                               | 6 |

| Figure 1. ACLR of F1485 MB with Optimized BOM (f <sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 200MHz)                                                                                                                                                                                                                                                                                                                                                        | 6.   | Revision History                                                                       | 7 |

| Figure 1. ACLR of F1485 MB with Optimized BOM (f <sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 200MHz)                                                                                                                                                                                                                                                                                                                                                        |      |                                                                                        |   |

| Figure 2. ACLR of F1485 MB with Optimized BOM (f <sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 400MHz)                                                                                                                                                                                                                                                                                                                                                        | Fig  | gures                                                                                  |   |

| Figure 3. Application Circuit Electrical Schematic  Figure 4. Gain  Figure 5. Reverse Isolation  Figure 6. Input Return Loss  Figure 7. Output Return Loss  Figure 8. OIP3  Figure 9. OP1dB                                                                                                                                                                                                                                                              |      |                                                                                        |   |

| Figure 4. Gain                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figu | re 2. ACLR of F1485 MB with Optimized BOM ( $f_0 = 3.55$ GHz, 2C-100MHz, IBW = 400MHz) | 3 |

| Figure 4. Gain                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figu | re 3. Application Circuit Electrical Schematic                                         | 4 |

| Figure 5. Reverse Isolation  Figure 6. Input Return Loss  Figure 7. Output Return Loss  Figure 8. OIP3  Figure 9. OP1dB                                                                                                                                                                                                                                                                                                                                  |      |                                                                                        |   |

| Figure 6. Input Return Loss                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                                                                        |   |

| Figure 8. OIP3Figure 9. OP1dB                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                                                                                        |   |

| Figure 9. OP1dB                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figu | re 7. Output Return Loss                                                               | 6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figu | re 8. OIP3                                                                             | 6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figu | re 9. OP1dB                                                                            | 6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _    |                                                                                        |   |

### 1. Introduction

In 5G wireless communication systems, wider radio instantaneous bandwidth (IBW) allows for more efficient use of available spectrum. Higher bandwidth allows for faster data transfer and increased capacity. Taking the 5G 3.6GHz frequency band as an example, the IBW has increased from 100MHz to 200MHz, and now up to 400MHz. Driven by the increase in IBW requirements, the F1485 Evaluation Kit BOM is optimized for better ACLR with DPD performance for 2-Carrier-100MHz with IBW = 200MHz and 400MHz. The updated BOM significantly improves the Video Bandwidth of the F1485 resulting in enhanced ACLR with DPD performance for high IBW signals.

## 2. Measured ACLR Results

Table 1 shows the measured ACLR with DPD performance for 1-Carrier-100MHz and 2-Carrier-100MHz with IBW = 200MHz and 400MHz.

Table 1. Measured ACLR Results of F1485 MB with Optimized BOM

|                                   |                                                                | Pout  | ACLR with DPD [1] |                 | ACLR without DPD |                 |

|-----------------------------------|----------------------------------------------------------------|-------|-------------------|-----------------|------------------|-----------------|

| вом                               | Signal case                                                    | (dBm) | ACLR_L<br>(dBc)   | ACLR_R<br>(dBc) | ACLR_L<br>(dBc)  | ACLR_R<br>(dBc) |

|                                   | f <sub>0</sub> = 3.55GHz,1C-100MHz,<br>IBW = 100MHz, PAR = 8dB | 15    | -63               | -63             | -43.2            | -38.6           |

| F1485 Optimized<br>BOM in Table 2 | f <sub>0</sub> = 3.55GHz, 2C-100MHz<br>IBW = 200MHz, PAR = 8dB | 15    | -59.5             | -59.1           | -38.9            | -37.8           |

|                                   | f <sub>0</sub> = 3.55GHz, 2C-100MHz<br>IBW = 400MHz, PAR = 8dB | 15    | -56.2             | -57.8           | -37.9            | -41.3           |

<sup>1.</sup> ACLR with DPD is tested with AMD ZCU208 platform. ACLR values may vary with different DPD algorithms and test setup.

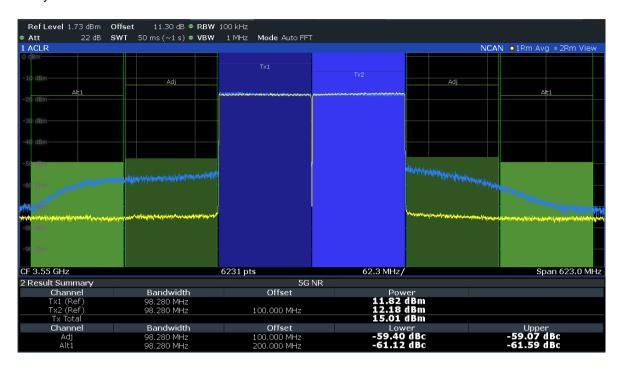

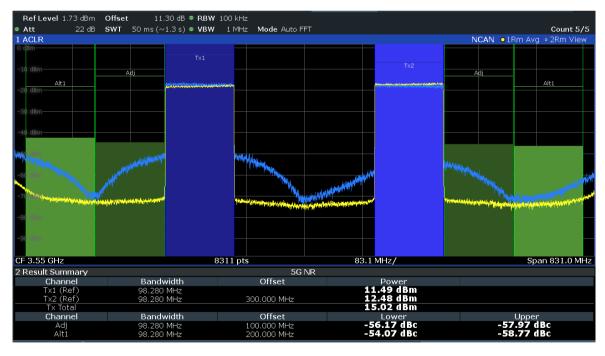

Figure 1 and Figure 2 show the ACLR at  $f_0$  = 3.55GHz for 2-Carrier-100MHz with IBW = 200MHz and 400MHz, respectively.

Figure 1. ACLR of F1485 MB with Optimized BOM (f<sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 200MHz)

Figure 2. ACLR of F1485 MB with Optimized BOM (f<sub>0</sub> = 3.55GHz, 2C-100MHz, IBW = 400MHz)

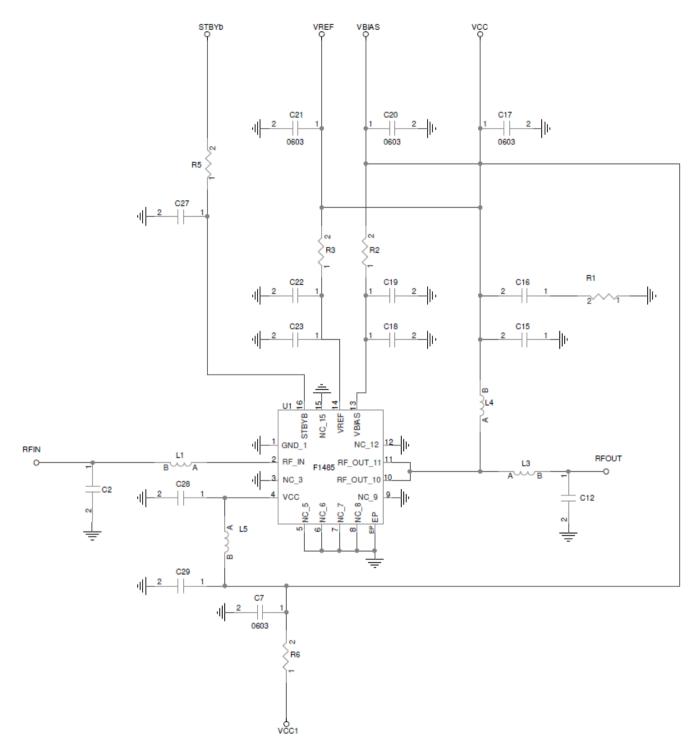

# 3. Evaluation Kit Schematic

Figure 3. Application Circuit Electrical Schematic

## 4. Bill of Materials

Table 2. Application Circuit Bill of Material (BOM) for VBW Enhancement

| Part Reference                    | Qty | Description                                     | Manufacturer Part # | Manufacturer |

|-----------------------------------|-----|-------------------------------------------------|---------------------|--------------|

| C7, C20, C21 3 47                 |     | 47μF ±20%, 6.3V, X5R Ceramic Capacitor (0603)   | GRM188R60J476ME15D  | MURATA       |

| C15                               | 1   | 15pF ±5%, 50V, C0G Ceramic Capacitor (0402)     | GRM1555C1H150JA     | MURATA       |

| C29                               | 1   | 100pF ±5%, 50V, C0G Ceramic Capacitor (0402)    | GRM1555C1H101JA     | MURATA       |

| C16                               | 1   | 10μF ±10%, 10V, X7R Ceramic Capacitor (0603)    | GRM188Z71A106MA73   | MURATA       |

| C18, C19, C22,<br>C23, C27, C17 6 |     | DNP                                             | -                   | -            |

| C28                               | 1   | 1μF ±10%, 16V, X6S Ceramic Capacitor (0402)     | GRM155C81C105KE11   | MURATA       |

| C2                                | 1   | 18nH Chip Inductor (0402)                       | LQP15MN18NG02D      | MURATA       |

| C12                               | 1   | 1.2pF ±0.1pF, 50V, C0G Ceramic Capacitor (0402) | GRM1555C1H1R2WA     | MURATA       |

| L3                                | 1   | 5.1pF ±0.1pF, 50V, C0G Ceramic Capacitor (0402) | GRM1555C1H5R1WA     | MURATA       |

| L4                                | 1   | 2.2nH ±0.3nH, 300mA Chip Inductor (0402)        | L-07C2N2SV6S        | JOHANSON     |

| L1, L5, R1, R2, R5,<br>R6, R8     |     | 0Ω Resistors (0402)                             | ERJ-2GE0R00X        | PANASONIC    |

| R3 1                              |     | 69.8Ω ±1%, 1/10W, Resistor (0402)               | ERJ-2RKF69R8X       | PANASONIC    |

| Module 1                          |     | F1485                                           | -                   | Renesas      |

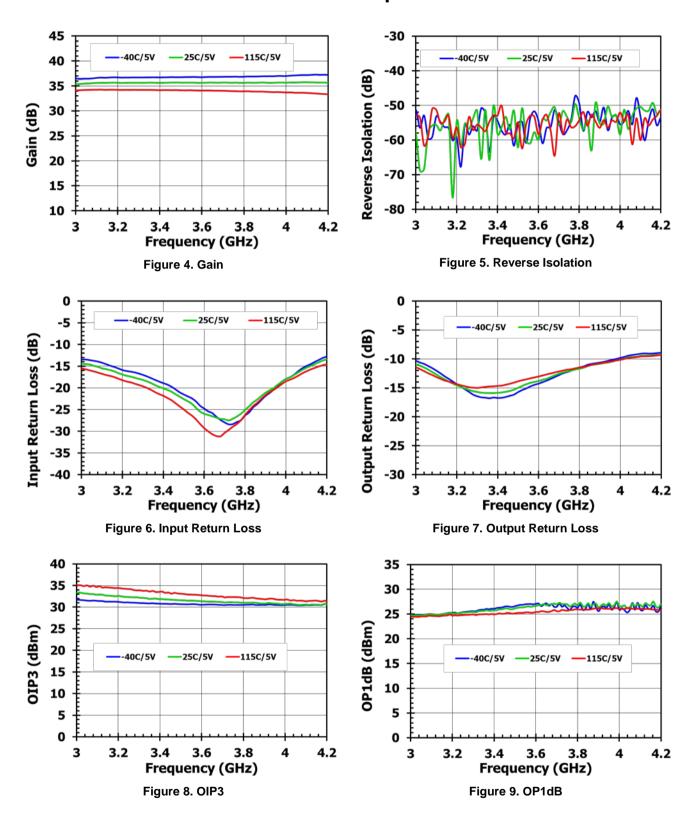

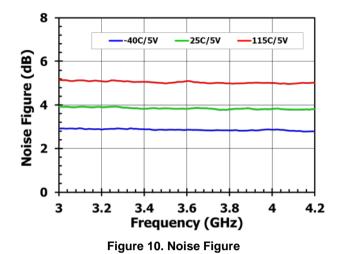

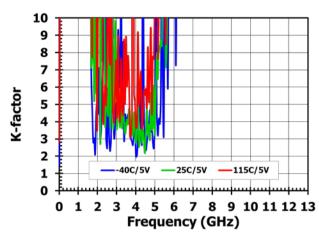

## 5. Measured RF Performance with Updated BOM

Figure 11. K-factor

# 6. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.00     | Aug 11, 2023 | Initial release. |

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.