### RAA225019 I<sup>2</sup>C Sequence and Timing Guidelines

### 1. Introduction

The following are recommended guidelines that customers must follow to ensure the RAA225019 operates robustly and without issues:

## 2. I<sup>2</sup>C Ready Sequence

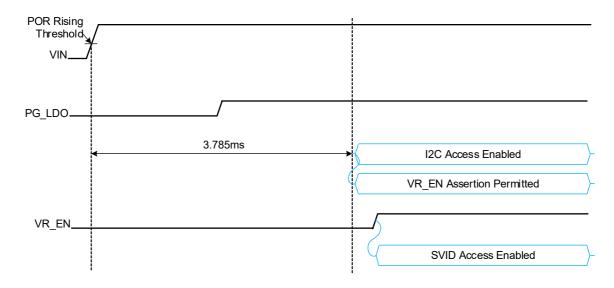

The I<sup>2</sup>C interface goes through a preparation stage after VIN rises above the Power-On Reset (POR) rising threshold. On the LNL-MX platform, multiple units support various rails, and each unit requires a different configuration before it can support full operation. For these rails, it is crucial to ensure that I<sup>2</sup>C write operations are accessible and that all write commands are acknowledged before the VR\_EN signal is asserted. I<sup>2</sup>C communication becomes available after the I2C\_ready time (V<sub>IN</sub>POR to I<sup>2</sup>C Timing) as in the datasheet EC table. Figure 2 shows the timing diagram. When PIN and AVIN are above the POR rising threshold, the internal bandgap and LDO are activated. The startup state machine runs, and the settings on each of the three PROG pins are read sequentially. The RAA225019 cannot guarantee package recognition until the I<sup>2</sup>C addresses are configured by the PROGx pins. To ensure that the proper configuration is loaded into each rail, the I<sup>2</sup>C ready enable timing must be adhered to for all rails. After the I<sup>2</sup>C enable timing is completed (V<sub>IN</sub>POR to I<sup>2</sup>C Timing), the I<sup>2</sup>C bus is ready for communication.

| V <sub>IN</sub> POR to I <sup>2</sup> C Timing <sup>[4]</sup> | - | PIN > POR rising to I2C Communication start                   | - |   | 3.785 | ms |

|---------------------------------------------------------------|---|---------------------------------------------------------------|---|---|-------|----|

|                                                               |   | PIN > POR rising to SDA release                               | - | - | 700   | μs |

| V <sub>IN</sub> POR to EN Ready <sup>[4]</sup>                | - | PIN > POR rising to<br>VR_EN1/VR_EN2/EN3/EN_LDO going<br>high | - | - | 3.865 | ms |

Figure 1. Datasheet Electrical Specification Table Snapshot

Figure 2. Startup Timing Diagram

The I2C\_Data line (SDA) is pulled low before the RAA225019 VIN POR. Typically, the Embedded Controller (EC) begins sending configuration commands only after all PRIM rails to the SoC have been supplied. Since the RAA225019 is a system Power Management Integrated Circuit (PMIC), it supplies some of these PRIM rails. As a result, a few of the ROP rails are enabled with default One-Time Programmable (OTP) settings. If the customer follows this architecture, I<sup>2</sup>C communication for the register configuration commences only after the RAA225019 POR sequence is completed and some rails have been enabled. To confirm this, either gate EC programming until the Power-Good signal of VnnAON is asserted or verify the sequence in the actual system.

Other system implementation recommendations include:

- Characterize PMIC\_VIN discharge at pre-regulator disable, and/or implement a discharging circuit.

- Use a separate I<sup>2</sup>C bus line for the PMIC compared to other devices (such as charger, pre-regulator).

- Configure the charger before enabling the pre-regulator or after the PMIC\_VIN POR is reached if the I<sup>2</sup>C bus of the charger is shared with the PMIC.

- Align EC configuration for the PMIC's V<sub>IN</sub>POR to I<sup>2</sup>C Timing after the PMIC reaches Vin\_POR.

# 3. Revision History

| Revision | Date        | Description      |

|----------|-------------|------------------|

| 1.00     | Nov 7, 2024 | Initial release. |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.