# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

# ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# **コードレス電話,携帯無線機用** 1.8 ~ 5.5 √**電圧** 80 MHz ~ 550 MHz**デュアル**PLL**周波数シンセサイザ**LSI μPD3140GS**の使い方と応用**

# 目 次

| 1  | . はじめ          | E                                     | 3  |

|----|----------------|---------------------------------------|----|

| 2  | . 製品概          | 要                                     | 3  |

| 3  | . 製品特          | 徵                                     | 4  |

|    | 3.1            | μ PD3140GSの特徴                         | 4  |

|    | 3.2            | μ PD3140GSの応用システム例                    | 4  |

| 4  | . 回路構          | 成と端子接続,機能                             | 5  |

|    | 4.1            | 回路構成                                  | 5  |

|    | 4.2            | 端子機能                                  | 7  |

| 5  | . 製品フ          | ァミリ一覧と主な仕様                            | 9  |

| 6  | . PLL <b>制</b> | <b>御データの設定方法</b>                      | 10 |

|    | 6.1            | スワロ・カウンタ,メイン・カウンタ,リファレンス・カウンタの分周数の計算式 | 10 |

|    | 6.2            | 制御データの入力方法                            | 10 |

|    | 6.3            | シリアル・データの入力タイミング                      | 11 |

|    | 6.4            | シリアル・データにより制御できる内容                    | 12 |

|    |                | シフト・レジスタのデータ・フォーマット                   |    |

| 7  | . 位相比          | 較器の出力波形とロック判定出力                       | 19 |

|    | 7.1            | ロック判定出力動作について                         |    |

|    | 7.2            | 位相比較器出力およびロック判定出力のモニタ方法               |    |

| 8  | . テスト          | モードの設定方法                              | 20 |

|    | 8.1            | テストモードとは                              | 20 |

|    | 8.2            | テストモードの設定方法とモニタ内容                     | 20 |

| 9  | . 基本特          | 性                                     | 21 |

|    | 9.1            | シングル動作 / デュアル動作時の電源電流                 | 21 |

|    | 9.2            | プリスケーラ部の入力感度特性                        | 22 |

|    | 9.3            | 基準発振器の発振特性                            | 24 |

| 10 | . 応用回          | 路例とその特性                               | 25 |

|    | 10. 1          | 応用回路の構成                               | 25 |

|    | 10. 2          | 未使用端子の処理方法                            | 28 |

|    | 10.3           | ループ・フィルタの設計                           | 29 |

|    |                | PLLブロック・パラメータの計算                      |    |

|    | 10.5           | PLLループ・パラメータの決定とロックアップ・タイム短縮モードの理論    | 33 |

|    |                |                                       | 38 |

|    |                |                                       |    |

| 10.7 ループ・フィルタの調整とシリアル・テータの設定例 |      |

|-------------------------------|------|

| 11.おわりに                       | . 45 |

| 付録(1)応用評価基板の使用法               | . 46 |

| (2)μ PD3140GS用データ発生プログラムの使用法  | . 49 |

| (3)システム応用例ブロック図               | . 54 |

| (4)μ PD3140GSトラブル・シューティング     | . 55 |

# 本製品使用上の注意事項

- (1) 静電気等の過大入力にご注意願います。

- (2) Vcc端子にはバイパス・コンデンサを挿入してください。

- (3)ループ・フィルタ定数はご使用のVCO等にあわせて設定願います。

- (4) グラウンドパターンは極力広くしてください。

- (5)電源投入後は必ずシリアル・データを転送ください(データ転送前のLSIの動作は不安定なため)。

- (6)チャージポンプ・スイッチによるロックアップ・タイム短縮モードを使用する場合,基本フィルタは自動切り替え時にループゲインが大きく変動しないような回路定数にしてください。

- (7)オプション・データを含むシリアル・データはご使用のシステムに合わせて設定願います。

本書は本製品の一般的なアプリケーションの概要をご紹介するものです。掲載の応用回路および回路定数 はあくまで一例であり、量産設計を対象とするものではございません。

特に,PLL周波数シンセサイザの諸特性はご使用になるVCOの特性および基板パターンにより大きく変化します。したがいまして,本書を参考にして実際にご使用になるVCOの特性等ご計画のシステムにあわせて,回路定数およびシリアル・データの設定をお願いします。

#### 1.はじめに

コードレス電話は1987年秋の市場開放以来,その利便性から急速なテンポで普及しており,'92年は500万台程度の需要となっています。このうち,親機(ベースセット)から半径約100mの交信距離をもつアナログ小電力タイプが90%以上を占めます。また電話機全体に占める割合も,'88年がわずか10%(台数ベース)だったのに対し'90年は約50%に達し,さらに'92年は60%近い構成比になっています。

このように,親機(ベースセット)と子機(ハンドセット)の間を電波で結ぶコードレス電話の登場により,電話機市場においても高周波デバイスが必要になりました。

特にアナログ小電力タイプの場合,チャネル数89 ch (通話用:87 ch,制御用:2 ch),チャネル間隔12.5 kHzのマルチチャネル・アクセス (MCA: Multi Channel Access)方式を採用しているため,選局部に使用するPLL周波数シンセサイザLSIが無線部の特性を決定するキーデバイスになります。

当社では,コードレス電話用デュアルPLL周波数シンセサイザLSIとして µ PD2843GS,2844BGS,2844BGS(1)の計 3 品種を製品化しました。

そしてその上位製品として80 MHz ~ 550 MHzの汎用デュアルPLL周波数シンセサイザLSI  $\mu$  PD3140GSを開発,製品化しました。

以下にその概要を紹介します。

#### 2.製品概要

μ PD3140GSは,高周波送受信システムの周波数シンセサイザ用に80 MHz ~ 550 MHz動作のプリスケーラとPLLをそれぞれ 2 回路内蔵したLSIです。それぞれ 2 回路持つことにより,アナログコードレス電話等の送信用周波数と受信用周波数をそれぞれ別のPLLで構成することができ,スプリアスの影響を受けない安定したシンセサイザを構成できます。

さらに,待ち受けモード(数百m秒~数秒に1回,電話の着信を調べるモード)に対応するため,電源ON時にマイコンからのデータにより両側のPLLを独立にON/OFF制御して動作電流を低く抑えるパワーセーブ機能を備えていること,アクティブ・フィルタ構成用のトランジスタを内蔵することにより,実装面積,部品点数の低減ができることなど多くの特徴を有した製品です。

また本LSIは,最新の高速動作Bi-CMOSプロセスを用い,従来製品に比べさらに低電圧動作,低消費電流を実現しています。

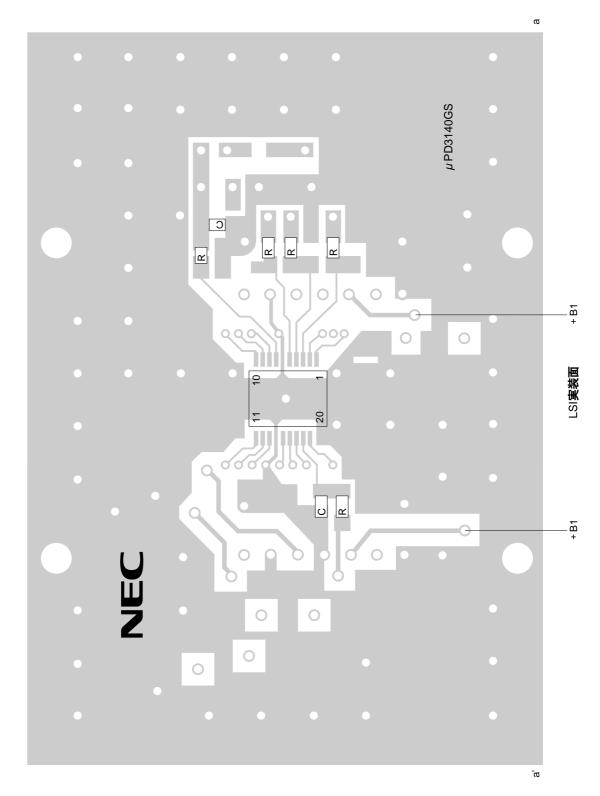

パッケージはセットの小形化が可能な20ピン・プラスチック・SSOP (シュリンクSOP)です。図2 - 1に外形写真を示します。

図2-1 外形写真

### 3.製品特徵

#### 3.1 µPD3140GSの特徴

( 1 )  $f_T$  = 13 GHz高速動作Bi-CMOSプロセスの採用により,低電圧化を実現。

Vcc = 1.8 V ~ 5.5 Vで動作します。

(2)動作周波数fin = 80 MHz ~ 550 MHz (PLL ch1, ch2共通)

日本のアナログコードレス電話の他、アマチュア無線等の幅広い用途に使用できます。

- (3)高速基準発振回路を内蔵し、バッファ出力端子により外部出力が可能。基準発振周波数fref = 30 MHz MAX. X'tal発振器を共用するようなアプリケーションに対応できます。

- (4)パワーセーブ機能により2つのプリスケーラを独立にON/OFF制御が可能。

- (5)低消費電流 ・デュアル (両ch)動作時: lcc OP2 = 4.3 mA TYP.@Vcc = 1.8 V

- ・シングル ( 片側 ) 動作時 : Icc OP1 = 2.7 mA TYP.@Vcc = 1.8 V

- ・両chOFF時 : Icc PS = 10 μ A MAX. @Vcc = 1.8 V

- (6) チャージポンプ・スイッチ制御機能によりロックアップ・タイム短縮が可能 ロックアップ・タイム9 ms@fstep = 12.5 kHz , 1 MHzスイング

- (7)ロック感度切り替え機能を内蔵

リファレンスに対する入力信号パルスの許容時間差を4段階で設定可能:150 ns ~ 5 μs)。

- (8) µ PD2844とピンおよびカウンタ・データがコンパチブル (オプションデータは異なります)。

- (9)20ピンSSOPパッケージにより高密度・面実装が可能。

- (10)同一カウンタデータ入力時の動作変動がない。

μ PD2844まで採用していたデータリセット方式を改善することにより , 幅広い用途に対応できるようになりました。

#### **3.2** μPD3140GS**の応用システム例**

- ・小電力アナログ・コードレス電話

- ・特定小電力トランシーバ

- ・VHF帯無線機(アマチュア無線等)

- ・RFリモコン

- ・CT1/CT2コードレス電話(てい倍方式)

- · PHS (2nd PLL)

- ・アナログ / ディジタル・セルラ (2nd PLL)

# 4.回路構成と端子接続,機能

#### 4.1 回路構成

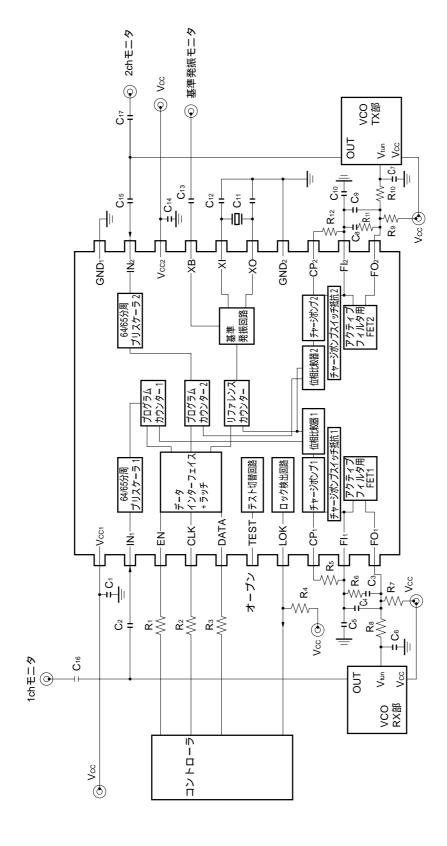

μ PD3140GSの内部等価ブロック図を図4 - 1 に示します。

GND<sub>1</sub> 20 V<sub>CC1</sub> 64/65分周プリスケーラ 1 64/65分周プリスケーラ 2 IN<sub>2</sub> 19  $IN_1$ プログラム カウンタ 1 (メイン+ スワロ) 18 3 - EN Vcc2 データ プログラム カウンタ 2 (メイン+スワロ) インタフェース CLK ΧB 17 + ラッチ - DATA ΧI 16 リファレンス 基準 カウンタ 発振回路 テスト切り替え回路 - TEST -XΩ 15 LOK ロック検出回路 GND<sub>2</sub> 14 位相比較器1 位相比較器2 チャージポンプ2 チャージポンプ 1 CP<sub>1</sub> -CP<sub>2</sub> 13 チャージポンプスイッチ抵抗 1 チャージポンプスイッチ抵抗 2 12 9 - FI₁  $Fl_2$ アクティブ・ フィルタ 用FET 1 アクティブ・ フィルタ 用FET 2 10 FO<sub>1</sub> FO<sub>2</sub> 11

**図4-1** μPD3140GS内部ブロック図(端子接続はTop View)

#### (1) VCO信号入力部とNカウンタ(パルス・スワロ式カウンタ)

1/64,1/65分周の2モジュラス・プリスケーラ,6ビットのスワロ・カウンタ(0~63)および11ビットのメイン・カウンタ(64~2047)をそれぞれ2組で構成しています。

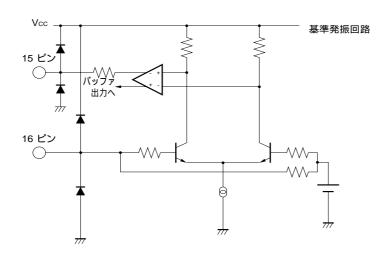

#### (2)リファレンス周波数発生部

基準発振器(外付け水晶による発振回路)と13ビットのリファレンス・カウンタ(64~4096)で構成しています。本リファレンス・カウンタはPLL 1ch, 2ch共通のリファレンス信号を発生させます。

# (3) データ設定部

3 線式シリアルバス・インタフェース回路, 19ビットのシフト・レジスタおよびデータ・ラッチ回路で構成しています。

#### (4)位相比較部

位相比較回路,チャージ・ポンプ,アクティブ・フィルタ用FET各2組およびロック検出回路1つで構成しています。

チャージ・ポンプ出力はマイコンからのデータ設定により極性の切り替えが可能です。この極性は使用するVCO の極性およびフィルタの形式によって決定します。

ロック判定出力は、パワーセーブ機能による片ch動作時は動作しているPLLがロックするのを判定します。両方動作しているときは両方ともロックしたときにロック判定します

アクティブ・フィルタ用のFETは,オープン・ドレインタイプのMOS FETです。

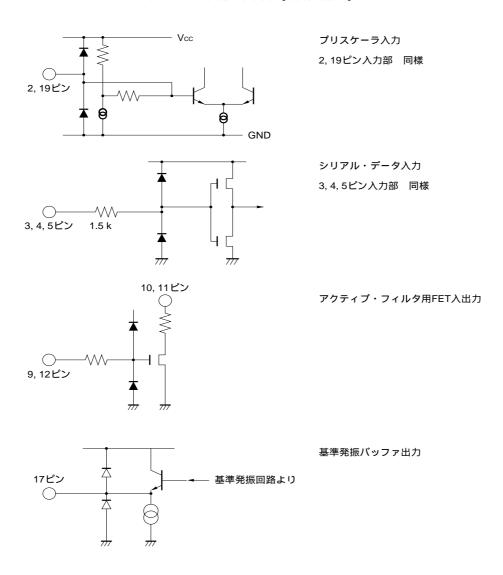

# 4.2 端子機能

各端子の機能説明を表 4 - 1 に示します。また各端子部分の内部等価回路を図 4 - 4 に示します。  $\mu$  PD3140GSは 従来品  $\mu$  PD2844BGS , 2844BGS (1) とオプション設定の内容が増えただけでカウンタデータと外形はコンパチブルです。

表4-1 端子機能の説明

| 端子番号 | 端子名称             | 説明                                                 |

|------|------------------|----------------------------------------------------|

| 1    | Vcc1             | アナログ系,プリスケーラの電源端子(PLL 1ch,2ch共通)                   |

| 2    | IN <sub>1</sub>  | 64/65分周プリスケーラ入力,C結合入力する。 IN₁:PLL 1ch側              |

| 19   | IN <sub>2</sub>  | IN₂:PLL 2ch側                                       |

| 3    | EN               | データのロード・イネーブル入力端子                                  |

| 4    | CLK              | データのクロック入力端子                                       |

| 5    | DATA             | データ入力端子                                            |

| 6    | TEST             | テスト端子(実使用時にはGNDへ接地する。 <b>8.テストモードの設定方法</b> を参照)    |

| 7    | LOK              | ロック判定出力端子(オープン・ドレイン)                               |

|      |                  | パワーセーブ機能による片ch動作時は,動作しているPLLがロックしているのを判定する。両方動作してい |

|      |                  | るときは,両方ともロックしたときにロック判定する。ロック時Low(Sink)出力           |

| 8    | CP <sub>1</sub>  | チャージポンプ出力端子 CP1:PLL 1ch側                           |

| 13   | CP <sub>2</sub>  | CP <sub>2</sub> : PLL 2ch側                         |

| 9    | FI₁              | アクティブ・フィルタ用MOS FET                                 |

| 12   | Fl <sub>2</sub>  | ゲート入力端子                                            |

|      |                  | チャージポンプスイッチ抵抗の出力を兼ねています。                           |

|      |                  | FI₁: PLL 1ch側  FO \ 次段VCOへ                         |

|      |                  | Fl <sub>2</sub> : PLL 2ch側                         |

| 10   | FO <sub>1</sub>  | アクティブ・フィルタ用MOS FET 前段CPより FI                       |

| 11   | FO <sub>2</sub>  | ドレイン入力端子                                           |

|      |                  | FO1 : PLL 1ch側                                     |

|      |                  | FO <sub>2</sub> : PLL 2ch側                         |

|      |                  | パッシブ・フィルタを使用する場合オープン                               |

| 14   | GND <sub>2</sub> | PLLディジタル系のGND端子(PLL 1ch , 2ch共通)                   |

| 15   | XO               | 基準発振回路の入出力端子(リファレンス用:PLL 1ch,2ch │<br>│            |

|      |                  |                                                    |

| 16   | XI               | たとえばX'-talを外付けして発振を行う。 XI                          |

|      |                  | TCXOから16ピンへC結合による入力も可能 XO 土 XO イン                  |

|      |                  | (VIN = 0.2 VP-P ~ 1.0 VP-P , fmax = 30.0 MHz ) IC内 |

| 17   | XB               | 基準発振パッファ出力端子<br>基準発振<br>AMPより<br>次2ndMIX段などへ       |

|      |                  |                                                    |

|      |                  |                                                    |

| 18   | Vcc2             | PLLディジタル系の電源端子(PLL 1ch , 2ch共通)                    |

| 20   | GND <sub>1</sub> | アナログ系 , プリスケーラのGND端子 ( PLL 1ch , 2ch共通 )           |

|      | GINDI            | ファロノボ,フリスソープのGND姉丁(FLL IGII,2GII共理)                |

# 図4-2 内部等価回路(各端子部分)

# 5.製品ファミリ一覧と主な仕様

表 5 - 1 に当社のコードレス電話用デュアルPLL周波数シンセサイザLSIの主な仕様一覧を示します。本製品は従来の  $\mu$  PD2840GSから2844BGS (1) より大幅に高機能化しており、さまざまなアプリケーションに対応できます。

表5-1 コードレス電話用デュアルPLL周波数シンセサイザLSI従来品との比較

| 項目         | 品名<br>項目 |               | μ PD2842GS      | μ PD2843GS     | μ PD2844GS<br>μ PD2844BGS | μ PD2844GS(1)<br>μ PD2844BGS(1) | μ PD3140GS  |  |

|------------|----------|---------------|-----------------|----------------|---------------------------|---------------------------------|-------------|--|

| リファレンス用デ   | ィバイダ     | 固定            |                 | 可変             | 可変 (4                     | ~ 8192 )                        | 可変(64~4094) |  |

|            |          | ( 10          | 24)             | (2~4096)       | 注)2の                      | 倍数のみ                            | 注)2の倍数のみ    |  |

| チャージポンプ出   | 力形態      | 電流出力方式        |                 |                | 電流出力方式                    |                                 | 電流出力        |  |

|            |          | 電流値を外付け       | <b>が抵抗により制</b>  | (              | プログラマブル                   | •)                              | 電圧出力        |  |

|            |          | 御でき , ロック     | アップタイム          |                |                           |                                 | (プログラマブル)   |  |

|            |          | をコントロール       | ノできる。           |                |                           |                                 |             |  |

| チャージポンプ    | 進み       | HIGH          | LOW             |                | 極性均                       | 刀り替え可能                          |             |  |

| 出力位相極性     | 遅れ       | LOW           | HIGH            |                | (プロ                       | グラマブル )                         |             |  |

|            | 一 致      | ハイ・インピーダンス    | ハイ・インピーダンス      |                |                           |                                 |             |  |

| ループ・フィルタ   | 構成       | ・パッシフ         | <b>ブ</b> メイン    | • 7            | ・アクティブ                    |                                 |             |  |

| (チャージポンプ   | 構成 )     | ・アクティ         | <sup>,</sup> ブ可 | .,             | (ッシブ可                     |                                 | ・パッシブいずれも可  |  |

|            |          |               |                 |                |                           |                                 | (ただし共用不可)   |  |

| ループ・フィルタ用  | MOSFET   | なし(外作         | 付が要)            | あり (内蔵)        |                           |                                 |             |  |

| (アクティブ・フィ) | ルタ用 )    |               |                 | (オープン・ドレインタイプ) |                           |                                 |             |  |

| 基準発振バッファと  | 出力       | なし (必要な場合外付け) |                 |                |                           |                                 | 内蔵          |  |

| ロックアップ・タイ  | ム短縮用     |               |                 | なし             |                           |                                 | 内蔵          |  |

| チャージポンプス~  | イッチ      |               |                 |                |                           |                                 |             |  |

| ロック感度データは  | 切り替え     |               | なし ( 500 ns固定 ) |                |                           |                                 |             |  |

| データイン・リセ   | ット方式     |               | NO              |                |                           |                                 |             |  |

|            |          |               |                 |                |                           |                                 | 同一カウンタデータ入  |  |

|            |          |               |                 |                |                           |                                 | 力による動作変動なし  |  |

| 電源電圧       |          |               | 2.2 ~           | 5.5 V          |                           | 2.0 ~ 5.5 V                     | 1.8 ~ 5.5 V |  |

| パッケージ      |          | 20년           | ンSOP (300ミ      | ル)             | 20                        | 0ピンSSOP (30                     | 00ミル)       |  |

$\mu$  PD2844BGS/BGS (1) は  $\mu$  PD2844GS/GS (1) の品質向上品であり,特性上は同等です。

μPD3140GSの電気的特性および外形図については最新データ・シートをご覧ください。

μ PD2840GS ~ 2444BGS (1) は保守化傾向のため, μ PD3140GSを推奨します。

#### 6.PLL制御データの設定方法

#### 6.1 Nカウンタ,リファレンス・カウンタの分周数の計算式

外部に接続するVCOの発振周波数と基準発振周波数に対する各カウンタの分周比は,次の関係式に従って設定してください。

$$\frac{\text{fvco}}{N} = \frac{\text{fref}}{R} = \text{fstep} \qquad \dots (1)$$

fvco: VCOの発振周波数(2,19ピンへの入力周波数)

fref : 基準発振周波数 (水晶振動子の発振周波数)

fstep :ステップ周波数 (比較周波数)

R : リファレンス・カウンタの設定値(リファレンス・カウンタの設定参照p.14)

N : Nカウンタ(VCO入力側カウンタ)の設定値(Nカウンタの設定参照p.13)

#### 6.2 制御データの入力方法

制御データの入力は,データ端子(5ピン),クロック端子(4ピン),イネーブル端子(3ピン)の3線式シリアル・バス・インタフェースで行います。

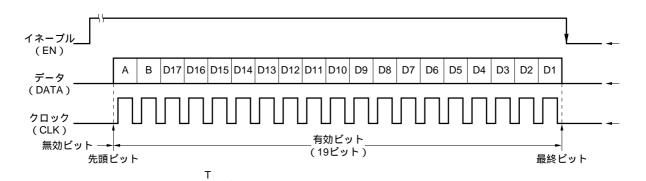

データ端子に,バイナリコードによるシリアルデータを入力します。本データのシフト・レジスタへの読み込みは,クロック端子に入力するクロック信号の立ち下がりで行い,イネーブル信号が"High"レベルの時,データ入力をLSI内に受けつけ,データ切り替えビット(2ビット)によりラッチ選択し,イネーブル信号の立ち下がりでLSI内に受けつけ最新の19ビット分がラッチされます。1回のラッチでLSI内に受けつけた19ビット分以前のデータはダミーデータと見なされ無効となります。イネーブル信号が"Low"レベルの間は,データ,クロック信号ともに受けつけません。

注意 電源 ( Vcc/Vpp ) 投入後は,必ずデータを転送してください。データ転送前のLSIの出力状態は,不定となっていますのでご注意願います (データ転送前のICの動作状態はロット,条件等により異なるため)。

図6-1 制御データの概念図

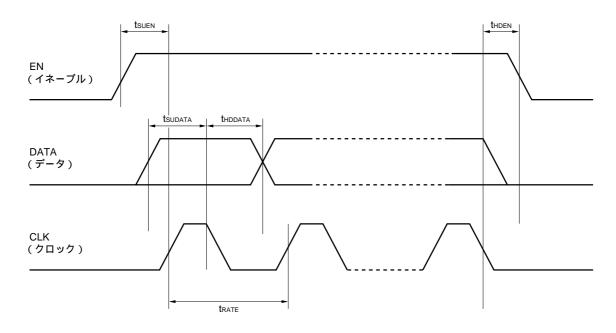

# 6.3 シリアル・データの入力タイミング

図6-2に,入力信号のタイミングを示します。

図6-2 シリアル・データの入力信号のタイミング

| 項目           | 電気的特性          |

|--------------|----------------|

| ENセットアップ時間   | tsuen 500 ns   |

| ENホールド時間     | thden 500 ns   |

| DATAセットアップ時間 | tsudata 100 ns |

| DATAホールド時間   | thddata 100 ns |

| CLKV         | 1μs trate 1s   |

# 6.4 シリアル・データにより制御できる内容

シリアル・データの入力により,次の項目をそれぞれ単独で制御できます。データラッチの選択は,データ切り替えビットで行います。

送信側のNカウンタの分周比

受信側のNカウンタの分周比

リファレンス・カウンタの分周比

オプション・データ設定(9項目)

# 6.5 シフト・レジスタのデータ・フォーマット

図6-3 シフト・レジスタの基本ビット構成

| <b>最</b> |   |   |     |     |     |     |     | 最後の | ビット | . — |    |    |    |    |    |    |    |    |    |

|----------|---|---|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|

| A        | 4 | В | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

#### (1)データ切り替えビットの設定

先頭ビットとその次のビットの計 2 ビット (A, B) でラッチ選択します。

表6-1 データ切り替えビットの構成と内容

| ビット | ∼構成 | 内容                    |  |  |  |  |  |

|-----|-----|-----------------------|--|--|--|--|--|

| Α   | В   | P) 台                  |  |  |  |  |  |

| 0   | 0   | 2 ピン入力側Nカウンタの分周比データ設定 |  |  |  |  |  |

| 0   | 1   | 19ピン入力側Nカウンタの分周比データ設定 |  |  |  |  |  |

| 1   | 0   | オプション・データ設定           |  |  |  |  |  |

| 1   | 1   | リファレンス・カウンタの分周比データ設定  |  |  |  |  |  |

<sup>&</sup>quot; 0 " = Low , " 1 " = High

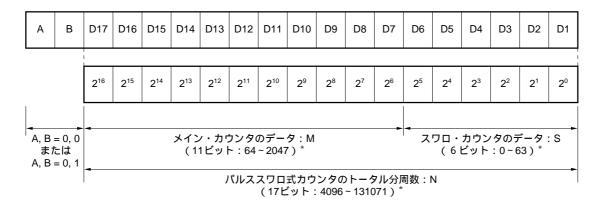

# (2) Nカウンタのデータの設定

2 モジュラス・プリスケーラ,スワロ・カウンタおよびメイン・カウンタから構成されるパルススワロ方式のNカウンタのトータル分周数Nは下記のように表されます。本方式は連続する分周数を得ることができ,またその分周数を単純にバイナリ・コードに変換して設定できるメリットがあります。

$$N = S (P+1) + P (M-S) = PM+S$$

=  $64 \times M + S$

ここでメイン・カウンタの分周数は

$$M = (D17 \times 2^{10}) + (D16 \times 2^{9}) + (D15 \times 2^{8}) + (D14 \times 2^{7}) + (D13 \times 2^{6}) + (D12 \times 2^{5}) + (D11 \times 2^{4}) + (D10 \times 2^{3}) + (D9 \times 2^{2}) + (D8 \times 2^{1}) + (D7 \times 2^{0})$$

スワロ・カウンタの分周数は

$$S = (D6 \times 2^5) + (D5 \times 2^4) + (D4 \times 2^3) + (D3 \times 2^2) + (D2 \times 2^1) + (D1 \times 2^0)$$

したがってパルススワロ式カウンタのトータル分周数Nは下記のようになります。

$$\begin{split} N &= 64 \times \left\{ \text{ } \left( \text{ } \text{D}17 \times 2^{10} \right) + \left( \text{D}16 \times 2^{9} \right) + \left( \text{D}15 \times 2^{8} \right) + \left( \text{D}14 \times 2^{7} \right) + \left( \text{D}13 \times 2^{6} \right) + \left( \text{D}12 \times 2^{5} \right) \right. \\ &\quad + \left( \text{D}11 \times 2^{4} \right) + \left( \text{D}10 \times 2^{3} \right) + \left( \text{D}9 \times 2^{2} \right) + \left( \text{D}8 \times 2^{1} \right) + \left( \text{D}7 \times 2^{0} \right) \right. \right\} + \left( \text{D}6 \times 2^{5} \right) + \left( \text{D}5 \times 2^{4} \right) \\ &\quad + \left( \text{D}4 \times 2^{3} \right) + \left( \text{D}3 \times 2^{2} \right) + \left( \text{D}2 \times 2^{1} \right) + \left( \text{D}1 \times 2^{0} \right) \\ N &= \left( \text{D}17 \times 2^{16} \right) + \left( \text{D}16 \times 2^{15} \right) + \left( \text{D}15 \times 2^{14} \right) + \left( \text{D}14 \times 2^{13} \right) + \left( \text{D}13 \times 2^{12} \right) + \left( \text{D}12 \times 2^{11} \right) \\ &\quad + \left( \text{D}11 \times 2^{10} \right) + \left( \text{D}10 \times 2^{9} \right) + \left( \text{D}9 \times 2^{8} \right) + \left( \text{D}8 \times 2^{7} \right) + \left( \text{D}7 \times 2^{6} \right) + \left( \text{D}6 \times 2^{5} \right) + \left( \text{D}5 \times 2^{4} \right) \\ &\quad + \left( \text{D}4 \times 2^{3} \right) + \left( \text{D}3 \times 2^{2} \right) + \left( \text{D}2 \times 2^{1} \right) + \left( \text{D}1 \times 2^{0} \right) \end{split}$$

連続可変範囲 = 4096 ~ 131071 (D13 ~ D17データのいずれかは1に設定)

このようにパルススワロ式カウンタのためトータル分周数を単純にバイナリ・コードに変換すれば良いわけです。

図6-4 Nカウンタの分周数設定ビット構成 (パルススワロ式カウンタのトータル分周数の設定)

\*( )内は(カウンタビット数:連続可変範囲)

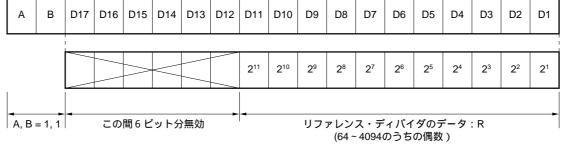

#### (3)リファレンス・カウンタのデータ設定

リファレンス・カウンタもプログラマブルになっていますので,基準発振周波数および比較周波数を使用するシステムに合わせて設定できます。分周数Rは次の計算式に基づいて,バイナリ・コードに変換します。

図6-5 リファレンス・カウンタの分周数設定ビット構成

**備考** 第1番目と第2番目のクロックでA,Bのデータが読み込まれ,第9番目以降のクロックでD11以降の リファレンス・カウンタのデータが読み込まれます。

注意 D12~D17のデータは,いかなるデータでも無効になります。この場合,クロック信号は入力しておいてください(クロック信号によってこの無効の6ビット分をカウントするため)。

# リファレンス側分周数:R

- $R = R' \times 2 = \{ (D11 \times 2^{10}) + (D10 \times 2^{9}) + (D9 \times 2^{8}) + (D8 \times 2^{7}) + (D7 \times 2^{6}) + (D6 \times 2^{5}) + (D5 \times 2^{4}) + (D4 \times 2^{3}) + (D3 \times 2^{2}) + (D2 \times 2^{1}) + (D1 \times 2^{0}) \} \times 2$

- = D11 x 2<sup>11</sup> + D10 x 2<sup>10</sup> + D9 x 2<sup>9</sup> + D8 x 2<sup>8</sup> + D7 x 2<sup>7</sup> + D6 x 2<sup>6</sup> + D5 x 2<sup>5</sup> + D4 x 2<sup>4</sup> + D3 x 2<sup>3</sup> + D2 x 2<sup>2</sup> + D1 x 2<sup>1</sup> 設定範囲 = 64 ~ 4094 (連続する偶数の設定が可能)

表6-2 リファレンス・ディバイダの分周数とそれに対するバイナリ・コード

| 基準発振      | 八田粉(D) | D44 | D40 | D9 | D8 | D7 | DC | DE | D4 | Do | D2 | D1 |

|-----------|--------|-----|-----|----|----|----|----|----|----|----|----|----|

| 周波数       | 分周数(R) | D11 | D10 | D9 | סט | יט | D6 | D5 | D4 | D3 | D2 | וט |

| 12.8 MHz  | 4004   | 0   | 4   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| の場合       | 1024   | 0   | '   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 21.25 MHz | 1700   | 0   | 4   | 4  | 0  | 4  | 0  | 4  | 0  | 0  | 4  | 0  |

| の場合       | 1700   | 0   | I   | I  | 0  | ı  | 0  | I  | 0  | U  | -  | 0  |

備考 上記分周数は,比較周波数を12.5 kHzとした場合

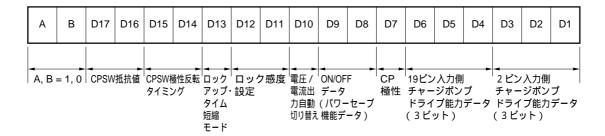

# (4)オプション・データ設定について

オプション・データ設定ではPLL特性 / 動作の制御のためのデータ設定を行います。本設定は (A,B)=(1,0) にすればデータ入力可能です。以下の項目を設定します。

PLL1ch側チャージポンプドライブ能力(D1~D3)

PLL2ch側チャージポンプドライブ能力(D4~D6)

両チャネル共通チャージポンプ出力極性(D7)

パワーセーブ機能: 2つのチャネルのプリスケーラON/OFF(D8, D9)

チャージポンプ電圧/電流出力自動切り替え(D10)

ロック感度設定:比較信号パルスの許容時間差の設定(D11, D12)

チャージポンプ・スイッチ制御(D13(ただしD10=1の場合))

チャージポンプ・スイッチ抵抗出力の極性反転タイミング(D14, D15)

チャージポンプ・スイッチ抵抗値(D16,D17)

オプション・データ設定のビット構成は図のようになります。

図6-6 オプション・データ設定のビット構成

D1~D6:チャージポンプ (CP)・ドライブ能力設定

| D3   | D2   | D1   |    | CP・ドラ     | イブ能力          |

|------|------|------|----|-----------|---------------|

| (D6) | (D5) | (D4) | 能力 | 出力電流(Icp) | 出力換算抵抗( Rcp ) |

| 0    | 0    | 0    | 小  | 10 µ A    | 100 k         |

| 0    | 0    | 1    |    | 30 µ A    | 33 k          |

| 0    | 1    | 0    | ÷  | 100 µ A   | 10 k          |

| 0    | 1    | 1    | ÷  | 130 µ A   | 7.7 k         |

| 1    | 0    | 0    | ÷  | 300 µ A   | 3.3 k         |

| 1    | 0    | 1    | :  | 330 µ A   | 3 k           |

| 1    | 1    | 0    | i  | 400 µ A   | 2.5 k         |

| 1    | 1    | 1    | 大  | 電圧出力      | 500           |

補足1 出力換算抵抗値はVcc = 2 V時の数値。

換算式

$$Rcp = \frac{Vo}{Icp}$$

$$= \frac{Vcc}{2 \times Icp}$$

**補足2** D1~D3:PLL1chデータ

D4~D6:PLL2chデータ

#### D7: **チャージポンプ極性切り替え(PLL** 1ch, 2ch共通)

|    |       |      | _ 15 1 | -          | •          |

|----|-------|------|--------|------------|------------|

| D7 | チャージポ | 基準   | 信号に対す  | フィルタ形式     |            |

| וט | ンプ極性  | 進み位相 | 遅れ位相   | — 致        | フィルラ カカタエレ |

| 0  | 正     | Low  | High   | ハイ・インピーダンス | パッシブ・フィルタ  |

| 1  | 負     | High | Low    | ハイ・インピーダンス | アクティブ・フィルタ |

アクティブ・フィルタかパッ シブ・フィルタかによりCP 極性を設定してください。

D8 ~ D9: プリスケーラの動作設定 (パワーセーブ機能)

| D8 | D9 | PLL 1ch側 | PLL 2ch側 | 基準発振器<br>+ バッファ | 動作状態    |

|----|----|----------|----------|-----------------|---------|

| 0  | 0  | OFF      | OFF      | OFF             | 両ch OFF |

| 0  | 1  | OFF      | ON       | ON              | シングル動作  |

| 1  | 0  | ON       | OFF      | ON              |         |

| 1  | 1  | ON       | ON       | ON              | デュアル動作  |

プリスケーラをOFFしたチャネルのチャージポンプ出力は強制的にハイ・インピーダンスとなり、PLLループを組んだまま電源電流のセーブができます。このときPLLディジタル系回路は常時ONとなっています。よって両chのプリスケーラをOFFしていても、シリアルデータを書き換えることができます(シングルPLLとしての使用法は28ページをご覧ください)。

- 注意1.ONになっているプリスケーラに規定のレベルおよび周波数の入力信号がされていない場合,あやまった出力がされますのでご注意ください。

- 2.パワーセーブ状態では,同調電圧がロック時の値からループフィルタのリーク電流分だけずれる場合がありますのでご注意ください。

D11,12:ロック感度設定 (PLL 1ch, 2ch共通)

| D11 | D12 | ロック感度設定 |

|-----|-----|---------|

| 0   | 0   | 5.0 µs  |

| 1   | 0   | 1.5 µs  |

| 0   | 1   | 500 ns  |

| 1   | 1   | 150 ns  |

リファレンスに対する入力信号パルスの許容時間差

ロック感度設定は,基準発振信号を基に比較されるVCOからの入力信号のパルスの許容時間差を設定するものです。この設定はLSI内部のロック検出回路の許容時間差を制御し,許容時間差内に入った場合ロックと判定し,ICがロック時の動作に切り替わります。電圧出力から電流出力へはこの感度設定により自動的に切り替わるわけです。通常,許容時間差が小さい方がロックアップ・タイムが短縮できます。通常500 ns ぐらいがよいでしょう。

ただし、被変調VCOをPLL制御する場合、定常ループ時に許容時間差が小さすぎるとロックはずれ等が起こる際は許容時間差を大きくしてください。

D10:チャージポンプ出力自動切り替え(電圧/電流出力切り替えモード):PLL 1ch, 2ch共通

| D10 | ドライプ能力設定<br>D1~3 | LOCK状態 | PLL 1ch側 |

|-----|------------------|--------|----------|

| 0   | 111以外            | UNLOCK | 電流出力     |

|     | 111以外            | LOCK   | 電流出力     |

| 1   | 111以外            | UNLOCK | 電圧出力     |

|     | 111以外            | LOCK   | 電流出力     |

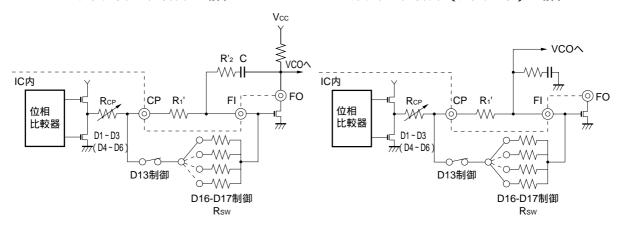

ドライブ能力設定D4~6の場合はPLL2ch側 出力は各chのCP端子から行われます。 D13~17: チャージポンプ・スイッチ (CPSW) 動作設定 (ロックアップ・タイム短縮モード): PLL 1ch, PLL 2ch共通

電圧出力時のFI端子によるCPSW出力とCP端子による出力のスイッチ切り替えです。

図6-7 チャージポンプ部の構造とループ・フィルタ

アクティブ・フィルタの場合

パッシブ・フィルタ (ラグリード) の場合

| D10 | D13 | CPSW動作 |

|-----|-----|--------|

| 1   | 1   | ON     |

| '   | 0   | OFF    |

| 0   | 1   | OFF    |

| "   | 0   | OFF    |

| D14 | D15 | CPSW抵抗出力の極 |  |

|-----|-----|------------|--|

| D14 |     | 性反転回数      |  |

| 0   | 0   | 反転1回       |  |

| 0   | 1   | 反転2回       |  |

| 1   | 0   | 反転4回       |  |

| 1   | 1   | 反転8回       |  |

| D16 | D17 | CPSW抵抗值:Rsw |  |

|-----|-----|-------------|--|

|     |     | (MOS:ON抵抗)  |  |

| 0   | 0   | 150         |  |

| 0   | 1   | 500         |  |

| 1   | 0   | 1.5 k       |  |

| 1   | 1   | 5.0 k       |  |

ロックアップ・タイム短縮モードでFI端子によるCPSW抵抗出力からCP端子による出力への切り替えは CPSW抵抗出力極性反転タイミングにより設定された反転回数が終了したのちに自動的に行われます。

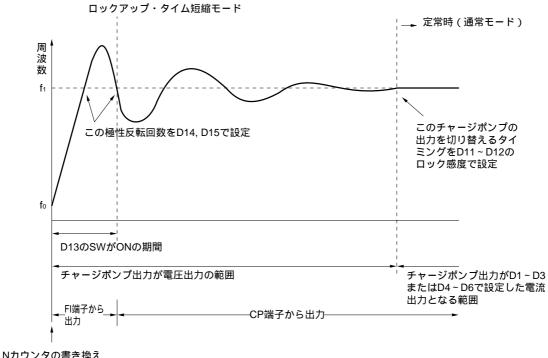

# 図 6 - 8 D10とD13を1に設定した場合のPLL制御動作

Nカウンタ・データを書き換えたチャネルのPLLは各モードが下記の要領で自動的に切り替わります。

Nカウンタの書き換え

備考 ・カウンタデータを書き換えないチャネルのPLLは通常モードのままです。

・各ロックアップ・タイム短縮モードの理論説明は37ページをご覧ください。

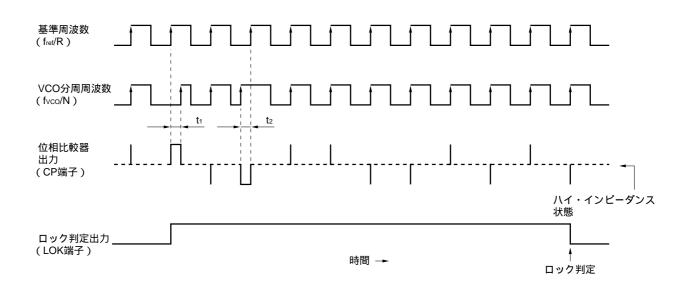

### 7.位相比較器の出力波形とロック判定出力

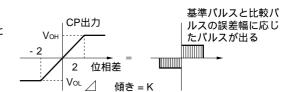

図7-1 位相比較器の出力波形とロック判定出力の関係

#### 7.1 ロック判定出力動作について

図7 - 1 にチャージ・ポンプの極性が正(切り替えビットが"0")の時の位相比較器の出力波形とロック判定出力の関係を示します。

ロック判定出力は動作しているPLLのパルス時間差trおよびteが,ロック感度設定した許容時間差以下になった状態で8周期以上連続したときに"Low"になり,ロック判定します。ただし,デュアル動作で使用している場合,片側のPLLがロックしただけではロック判定しませんので注意してください。

チャージ・ポンプの極性が負(切り替えビットが"1")の時は,位相比較器の出力極性が反転します。

#### 7.2 位相比較器出力およびロック判定出力のモニタ方法

#### 位相比較器出力波形のモニタ (CP端子)

CP端子と接続しているFI端子をプルアップ抵抗等により0.5 x Vccに固定するとCP出力のH, Lおよびハイ・インピーダンスがより明確にモニタできます。実使用時はとりはずしてください。

#### ロック判定出力のモニタ (LOK端子)

LOK端子はオープンドレインのためプルアップ抵抗によりある電圧に固定するとH, Lが明確にモニタできます。

#### 8. テストモードの設定方法

#### 8.1 テストモードとは

テストモードは2つのプリスケーラとPLLロジックの大きく分けて3つのブロックの動作をそれぞれモニタするためのモードです。本モードはICの評価時のテストに用いるものであり、実際のPLL動作時には使用しないモードです。

#### 8.2 テストモードの設定方法とモニタ内容

テストモードの設定はディジタル電源Vcc2を他電源より1.5 V以上で印加することにより行います。たとえば他電源がVcc = 2 Vの時Vcc2 = 4 Vにするとテストモードに移行します。テストモードにはプロックに分けて3つのモードがあります。

#### テストモード1

・1chプリスケーラ出力をテスト端子でモニタできます。 1chプリスケーラ - IN1端子入力信号の65分周の信号がTEST端子に出力されます。

#### テストモード2

・2chプリスケーラ出力をテスト端子でモニタできます。 2chプリスケーラ - IN2端子入力信号の65分周の信号がTEST端子に出力されます。

#### テストモード3

・PLLロジック回路のモニタを行います。本モードにより強制的にロックがかかっているときの動作を行い、3つの回路評価が可能となります。

チャージポンプ回路 - 強制的にハイ・インピーダンス状態になり,リーク測定等が可能 チャージポンプ・スイッチ回路 - CLK端子に16カウント以上の信号入力でCP-FI端子間のSWがON OFF (OPEN)となる。

ロック検出回路 - CLK端子に16カウント以上の信号入力でロック端子がON(L)

テストモードの設定と内容をまとめると表8-1のようになります。

テストモード条件設定 ブロック名 CLK端子 TEST端子 他モニタ端子 設定モード | EN端子 | DATA端子 1chプリスケーラ 1chプリスケーラ出力 テストモード1 Н 2chプリスケーラ テストモード2 2chプリスケーラ出力 チャージポンプ回路 テストモード3 Н CP端子:ハイ・インピーダンス測定 チャージポンプ・スイッチ回路 | テストモード3 Н CP-FI端子間スイッチ制御 Н ロック検出回路 テストモード3 Н Н ロック端子制御

表8-1 テストモード一覧表

# 9.基本特性

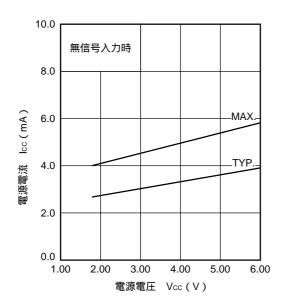

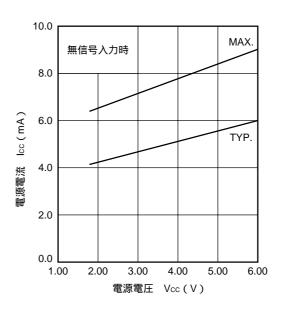

# 9.1 シングル動作/デュアル動作時の電源電流

図9-1,9-2にオプションデータのプリスケーラ動作設定によりPLLをシングル動作およびデュアル動作させたときの電源電圧 - 電源電流特性を示します。電源電流TYP品とMAX品はそれぞれ電源電圧と直線的な関係にあります。また測定回路を図9-3に示します。

図9-1 シングル動作時の電源電圧 - 電源電流特性 図9-2 デュアル動作時の電源電圧 - 電源電流特性

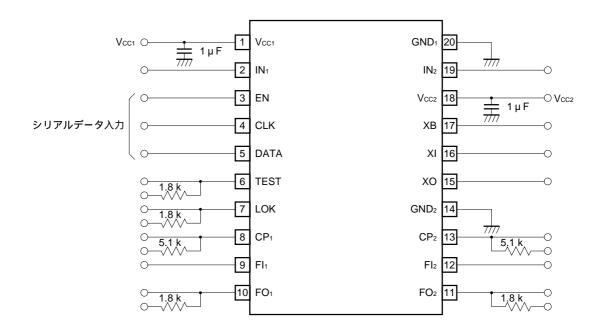

図9-3 電源電流測定回路

電源電流の測定方法は下記の要領で行います。

電源をVcc1, Vcc2に印加する(Vcc1, Vcc2, GND1, GND2およびEN, CLK, DATA以外はオープンにする)。

シリアルデータを入力する(特にオプションデータD8, D9によりプリスケーラの動作設定を行う)。 電源電流を測定する。

特にシリアルデータを入力しないとICの動作状態は不定のままとなり、電流は希望の消費をしないため正しい測定ができませんので注意してください。

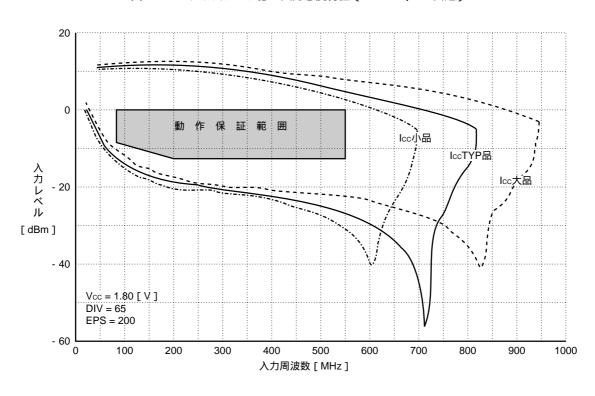

#### 9.2 プリスケーラ部の入力感度特性

図9 - 4にプリスケーラ部の入力感度特性曲線を示します。Pin = - 12 ~ 0 dBmの入力レベルで日本のアナログコードレス電話の1stローカルに使用する200 MHz ~ 550 MHzの範囲での動作を保証しています。またPin = - 8 ~ 0 dBm の入力レベルで80 MHz ~ 200 MHzの動作を保証しており,各種VHF帯の無線システムへの応用が可能です。また各種携帯電話の2ndローカルへの使用も可能です。

図9-4 プリスケーラ部の入力感度特性 (PLL1ch, 2ch共通)

図9-5 プリスケーラ入力感度特性測定回路

プリスケーラ入力感度特性測定回路を図 8 - 5 に示します。測定方法は下記の要領でテストモード 1 , 2 により行います。

電源をVcc1, Vcc2に印加する。

シリアルデータを入力する(オプションデータによりデュアル動作を設定する)。

ICをテストモードに設定する(Vcc2=Vcc1 + 2 Vにする)。

TESTピンにより 2 モジュラスプリスケーラの分周出力をモニタすることが可能となる。このときPLL1ch , 2chのプリスケーラ出力の切り替えは 3 ピンと 5 ピンのデータにより行うことによりテストモード 1 , 2 の切り替えで可能となる。

| EN ( 3 ピン ) 入力 | DATA ( 5 ピン ) 入力 | TEST (6ピン) |  |

|----------------|------------------|------------|--|

| Н              | L                | 1chの出力     |  |

| L              | Н                | 2chの出力     |  |

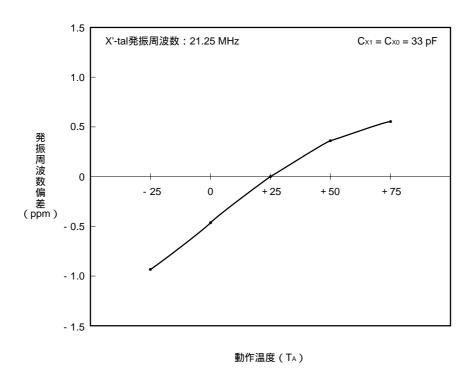

# 9.3 基準発振器の発振特性

TCXOを使用せずに,X'-tal(水晶振動子)を外付けしてLSI内部の発振回路を使用した場合の基準発振器の温度変化に対する発振周波数特性を図9 - 6に示します。

図9-6 X-tal使用時における内部基準発振器の発振周波数特性

実使用時,X'-tal発振回路の外付け容量値はご使用のX'-talの特性に合わせて決定してください。

# 10. 応用回路例とその特性

# 10.1 応用回路の構成

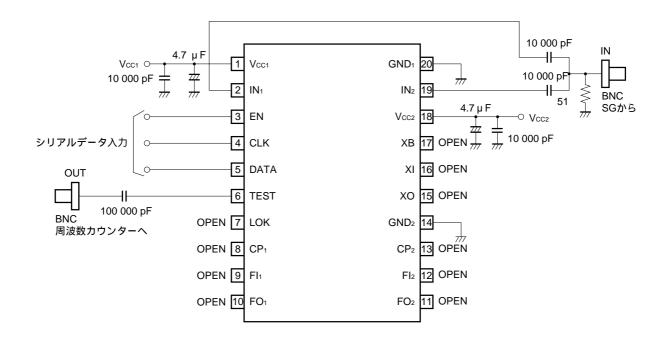

図10 - 1 に当社にて評価した応用回路の構成を,表10 - 1 に使用部品リストを示します。

# 表10 - 1 µPD3140GS**応用回路部品リスト例**

# (1)チップ部品

| 記号  | 使用部品     |  |  |

|-----|----------|--|--|

| C1  | 1 000 pF |  |  |

| C2  | 100 pF   |  |  |

| C3  | 39 nF    |  |  |

| C4  | 1 000 pF |  |  |

| C5  | 1 000 pF |  |  |

| C6  | 1 000 pF |  |  |

| C7  | 1 000 pF |  |  |

| C8  | 39 nF    |  |  |

| C9  | 1 000 pF |  |  |

| C10 | 1 000 pF |  |  |

| C11 | 33 pF    |  |  |

| C12 | 33 pF    |  |  |

| 記号  | 使用部品     |  |  |

|-----|----------|--|--|

| C13 | 1 000 pF |  |  |

| C14 | 1 000 pF |  |  |

| C15 | 100 pF   |  |  |

| C16 | 1 000 pF |  |  |

| C17 | 1 000 pF |  |  |

| 記号  | 使用部品  |  |  |

|-----|-------|--|--|

| R1  | 1.2 k |  |  |

| R2  | 1.2 k |  |  |

| R3  | 1.2 k |  |  |

| R4  | 100 k |  |  |

| R5  | 10 k  |  |  |

| R6  | 22 k  |  |  |

| R7  | 10 k  |  |  |

| R8  | 33 k  |  |  |

| R9  | 10 k  |  |  |

| R10 | 33 k  |  |  |

| R11 | 22 k  |  |  |

| R12 | 10 k  |  |  |

# (2)その他

| 記号    | 使 用 部 品                 |  |  |  |

|-------|-------------------------|--|--|--|

| VCO   | VK-9H ( 京セラ殿製 )         |  |  |  |

| X'tal | PW-2J 21.25 MHz(東京電波殿製) |  |  |  |

VCOの周波数関係は,国内アナログコードレス電話の子機および親機の場合を想定しています。したがって,VCOの発振周波数は表10 - 2に示す359 MHz / 254 MHzまたは276 MHz / 380 MHzにて評価しました。

基準発振器には,一般的に使用する21.25 MHzまたは12.8 MHzのX'talを用いています。

ループ・フィルタは , LSI内部のMOS FETを使用したアクティブ・フィルタで構成しています。 各外付け部品の機能を以下に示します。

C1, C17: 電源ラインのバイパス用コンデンサ

C2, C18: VCO1, VCO2の発振信号入力のためのカップリング用コンデンサ(DCカット)

C<sub>19</sub>, C<sub>20</sub>: VCO1, VCO2の発振信号モニタ用カップリング用コンデンサ

R1, R2, R3: データラインの電圧調整用抵抗

C16: 基準発振バッファ出力のカップリング用コンデンサ

$R_5 + R_6 + C_6 + C_7 + R_8 + C_8 + C_9$   $R_{12} + R_{11} + C_{11} + C_{12} + R_{10} + C_{13} + C_{10}$  : ループ・フィルタ構成用抵抗およびコンデンサ

R7, R9: ループ・フィルタ構成用MOS FETのバイアス供給用抵抗

C<sub>14</sub> , C<sub>15</sub> : X'tal発振器用コンデンサ

R4:LOK判定出力モニタ用プルアップ抵抗(応用評価時に使用)

VCOは子機用の京セラ殿製VK-9Hと親機用のVK-9Bを使用しています。

主な仕様を表10 - 2 に示します。

表10 - 2 VCO**の主な仕様**

| 品名         | VK-9H                                           |             | VK-9H VK-9B           |                |

|------------|-------------------------------------------------|-------------|-----------------------|----------------|

| 項目         | TX ch                                           | RX ch       | TX ch                 | RX ch          |

| 電源電圧       | 3.0 V , 3.5                                     | 5 V , 4.0 V | 3.5 V , 4.0 V , 4.5 V |                |

| 消費電流       |                                                 | 10 m/       | АТур.                 |                |

| 発振周波数      | fo = 254.4 MHz fo = 359.2 MHz                   |             | fo = 380.8 MHz        | fo = 276.2 MHz |

| 制御電圧       | 電源電圧による                                         |             |                       |                |

| 制御感度       | 2.0 ± 0.5 MHz/V ( Vcc ± 0.5 V時 )                |             |                       |                |

| 出力レベル      | - 5 dBm以上                                       |             |                       |                |

| C/N        | 70 dBTyp.(OFFSET.12.5 kHz,8 kHzB.W)             |             |                       |                |

| S/N        | 46 dB以上(Signal:1 kHz1.75 kHz.dav.0.3~ 3 kHzB.W) |             |                       |                |

| 変調感度       | 3.5 ± 1.0 kHz ( 60 mVrms時 )                     |             |                       |                |

| スプリアスレスポンス | - 15 dB以下                                       |             |                       |                |

| 出力インピーダンス  | 規定なし                                            |             |                       |                |

| 適用         | 日本小電力コードレス電話                                    |             |                       |                |

# 10.2 未使用端子の処理方法

以下のように使用しない端子がある場合の処理方法を場合ごとに分けて説明します。

# XB**端子を使用しない場合**

XB オープン

# パッシブ・フィルタ時のFO端子

FO オープン

FI チャージポンプ・スイッチ抵抗出力端子として使用

#### シングルPLLとして使用する場合

- · IN GND

- ・CP オープン

- · FI GND

- · FO GND

(オプションデータD8, D9にて使用しない側のchはOFFにしてください。)

# リファレンス周波数としてTCXOを使用する場合

- XI TCXOから入力

- XO オープンまたはRF接地(コンデンサ30 pF程度)

# 10.3 ループ・フィルタの設計

#### (1)設計式

K : 位相比較器の変換利得 (V/rad)

K√ : VCOの変換利得(感度)(rad/V・sec)

K : ループゲイン (K=K ・K√)

n:自然角周波数

: ダンピング・ファクタ

t : ロックアップ・タイム

K<sub>F</sub> : ループ・フィルタの利得

N:Nカウンタの分周数

R : リファレンス・カウンタの分周数

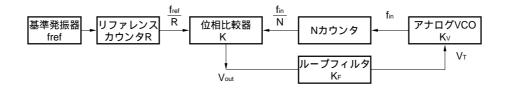

ループ・フィルタは、位相比較器・チャージポンプからの出力の高周波成分を除去して同調電圧をVCOに与え、かつPLLのループ特性を決定する重要なブロックです(図10 - 2)。そこでこのブロックを設計するにあたっては、PLLの入出力特性が良好に得られるように定数を設定する必要があります。

#### 図10 - 2 PLLプロック図(ディジタルアナログ混成PLLによる周波数シンセサイザの場合)

PLLの入力と出力の関係を求めます。入力と出力は各々時間の関数で表されますが、PLLは帰還ループであるため、そのままで関係を表すのは微積分方程式で記述され、複雑になります。ここで入力、出力をそれぞれラプラス変換に置き換えると、その2式の関係は伝達方程式で簡単に表されます。この関係式を変形し、ループ・フィルタを構成する定数をループ安定度や各デバイス特性により表現します。ループ安定度には自然角周波数、ダンピング・ファクタがあり、これらの設定によりロックアップ・タイムが決定します。デバイス特性には位相比較器とVCOの変換利得およびNカウンタの分周数があげられます。

ループの入出力特性を伝達方程式で表します。入力を i(S), 出力を o(S)とすると,

$$H(s) = \frac{o(s)}{i(s)} = \frac{K \cdot Kv(s) \cdot K_F(s)}{1 + \frac{K \cdot Kv(s) \cdot K_F(s)}{N}}$$

.....(1)

Kv, Krは時間の関数なのでラプラス変換すると,

$$K_{V(S)} = \frac{K_{V}}{S}$$

.....(2)

ここで 1・ 2はループ・フィルタの時定数を表します。

よって, 伝達方程式は,

$$H(s) = \frac{O(s)}{I(s)} = \frac{I(s)}{I(s)} = \frac{I(s)}{I(s)} = \frac{I(s)}{I(s)} + I(s) = \frac{I(s)}{I(s)} = \frac{I(s)}{I(s)}$$

PLLのループ特性としてインディシャル応答および閉ループ周波数特性があげられます。これらの特性を決定するパラメータとして自然角周波数 n, ダンピング・ファクタ があります。

そこで入出力伝達方程式を n, にて表します。

良好な入出力特性が得られるように, n, を設定することにより,所望の特性を満たすループ・フィルタの時定数 1, 2が求められます。それではフィルタの形式ごとに計算式を求めていきます。

アクティブ・ラグリード・フィルタの場合, 伝達方程式は

$$H(s) = \frac{o(s)}{i(s)} = \frac{N(1+2s)}{\frac{S^2}{n^2} + \frac{2s}{n} + 1}$$

.....(5)

この場合 n, は次のようになります。

ここで 1= CR1, 2= CR2であるから

また一般的に

$$c = (5 \sim 10)$$

n .....(10)

ただし,

パッシブ・ラグ・フィルタの場合は伝達方程式は、

$$H(s) = \frac{o(s)}{i(s)} = \frac{N}{\frac{S^2}{n^2} + \frac{2}{n} + 1}$$

.....(12)

ただし

ここで = CRであるから

$$R = \frac{K \cdot K_V}{N \cdot n^2 C}$$

$$= \frac{1}{2 \cdot n^2 \cdot C^2} \qquad (15)$$

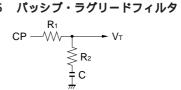

パッシブ・ラグ・リード・フィルタの場合は、

$$H(s) = \frac{o(s)}{i(s)} = \frac{N(1 + 2s)}{\frac{S^2}{n^2} + \frac{2s}{n} + 1}$$

.....(16)

ただし

$$n = \sqrt{\frac{K \cdot K_V}{N(1 + 2)}} \qquad .....(17)$$

ここで 1= CR1, 2= CR2であるから

$$R_1 + R_2 = \frac{K \cdot K_V}{N n^2 C} \qquad .....(19)$$

ちなみに, それぞれについて解くと

$$R_1 = \frac{K \cdot K_V}{N_{n^2}C} + \frac{N_{n^2} - 2 \cdot K \cdot K_V}{K \cdot K_V \cdot n^2C} \qquad ....(20)$$

ループ・フィルタの形式と定数の計算式をまとめると下記のようになります。

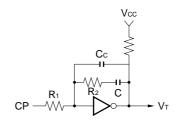

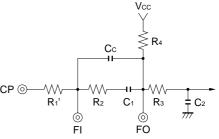

# アクティブ・ラグリードフィルタの定数の計算式 — 図10 - 3 アクティブ・ラグリードフィルタ

$$R_1 = \frac{K \cdot K_V}{N \cdot n^2 C}$$

$$R_2 = \frac{2}{nC}$$

$$C_C = \frac{1}{R_2 \cdot (5 \sim 10) \cdot n}$$

# – パッシブ・ラグフィルタの定数の計算式 –

$$R_1 = \frac{K \cdot K_V}{N \cdot n^2 C}$$

$$= \frac{1}{2 \cdot n^2 \cdot {}^2 C}$$

図10-4 パッシブ・ラグフィルタ

ちなみに各特性式はフィルタの形式に関わらず次のように求められます。

$$K = \frac{V_{OH} - V_{OL}}{2} \times \frac{1}{2}$$

$$K_{V} = \frac{f}{V} \times 2$$

$$N = \frac{f_{VCO}}{f_{ref}/R}$$

使用する位相比較器,VCOによりK、,Kv,Nが決まるため,ロックアップタイムを基準として,PLLのルー プ安定度を左右する , nを設定すると,計算によりループ・フィルタの定数が求められます。

#### 10.4 PLLプロック・パラメータの計算

#### ・位相比較器の変換利得

$$K = \frac{V_{OH} - V_{OL}}{2} \times \frac{1}{2} (V/rad) \qquad .....(22)$$

ここで出力電圧 Vон , VoLは特に規格化していません。式 (22)でVoH - VoLの値は一般に

で与えられます。ここでVcc=2Vの場合のK を計算すると

$$K = \frac{2-0}{2} \times \frac{1}{2} = 0.159 \text{ (V/rad)}$$

図10-6 位相比較器出力について

#### ・VCO**の感度**

$$Kv = \frac{f_{\text{max}} - f_{\text{min}}}{V_{\text{max}} - V_{\text{min}}} \times 2 \quad (\text{rad/V} \cdot \text{sec}) \qquad .....(23)$$

表9-2に示したVCOの仕様一覧より,

$$K_{V(IX)} = \frac{254.9625 - 253.8625}{3 - 1} \times 2 = 3.46 \times 10^{6} \text{ (rad/V \cdot sec)}$$

$$K_{V(RX)} = \frac{359.6125 - 358.5125}{3 - 1} \times 2 = 3.46 \times 10^{6} \text{ (rad/V \cdot sec)}$$

# ・全体の分周比

$$N = \frac{f_{VCO}}{f_{ref}/R} \qquad .....(24)$$

$$U = \int_{0}^{\infty} \int_{0}^{\infty} dt dt$$

$$N_{\text{max.}} = N_{\text{TX}} = \frac{359.6125 \text{ (MHz)}}{12.5 \text{ (kHz)}} = 28769$$

$$N_{\text{min.}} = N_{\text{RX}} = \frac{253.8625 \text{ (MHz)}}{12.5 \text{ (kHz)}} = 20309$$

----- K , K∨ , Nの決定 -----

K = 0.159 (V/rad)

$K_V = 3.46 \times 10^6 \text{ ( rad/V \cdot sec )}$

$N_{max} = 28769$

$N_{min} = 20309$

#### 10.5 PLLループ・パラメータの決定とロックアップ・タイム短縮モード理論

ループ安定度を決める上で重要なことは下記の3つです。

ループ系が安定なこと

ロックアップ・タイムが小さいこと

ロック時の系の雑音が少ないこと

についてはダンピング・ファクタ を大きくすると系は安定になります。

はインディシャル応答特性から安定に落ちつく ntを小さくすればよい。ここで nを大きく取ればtは小さくできます。

は位相比較角周波数を nより小さくする方向に定数を決定するか, を小さくして周波数特性の広域減衰特性を 大きくすることにより可能になります。

しかしながら,前記 , を同時に満足させることは特性的に相反します。そこで希望項目の着目によってそれぞれ定数の決定を行います。

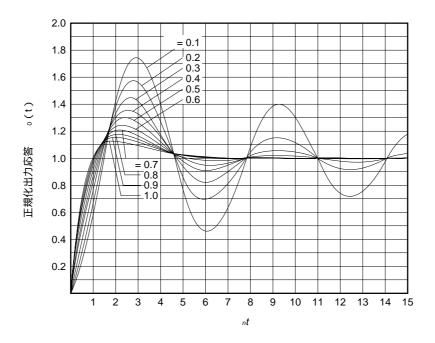

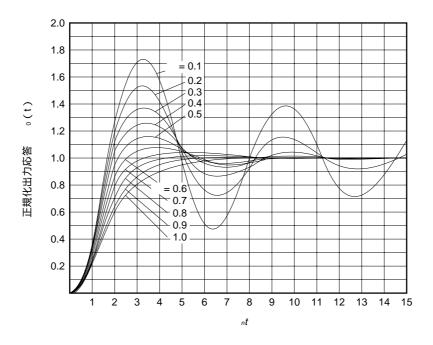

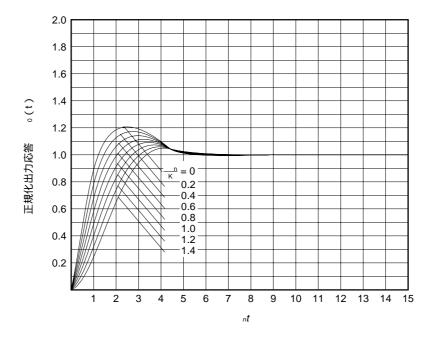

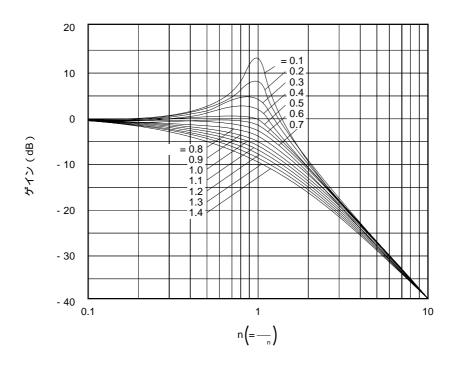

, nを設定するためのループ特性のグラフを示します。図10 - 6 にPLLシステムの過渡応答を,図10 - 7 に閉ループ周波数特性を示します。図10 - 6 の縦軸は正規化出力応答,横軸は ntです。

# 図10 - 7 PLLシステムにおけるループの過渡応答

# (a) アクティブ (ラグリード) フィルタの場合

# (b) パッシブ・ラグフィルタの場合

# (c)パッシブ・ラグリード・フィルタの場合( = 0.7時)

図10 - 8 PLLシステムにおける閉ループ波数特性

## (a) アクティブ (ラグリード) フィルタの場合 (パッシブ・ラグリード・フィルタで n/K=0の場合)

## (b) パッシブ・ラグフィルタの場合 (パッシブ・ラグリード・フィルタで n/K=2 の場合)

## ロックアップ・タイム短縮モードの理論説明

本LSIではロックアップ・タイムを短縮する手段としてループ・フィルタの抵抗値を変化させることによりVCOの同調電圧端子へのドライブ電流を変化させ、ダンピング・ファクタをPLLの状況に応じて切り替える方法を採用しています。ループフィルタの抵抗値を変化させる方法としては チャージポンプ出力を電圧出力と電流出力と切り替えて、内部シリアル抵抗分を制御する , チャージポンプスイッチによりパラレルに用意した小抵抗と ,外付けのフィルタの抵抗とのパスを切り替えて制御する ,の2通りの方法を組み合わせることにより実現しています。各切り替えのタイミングは内部のロック検出回路での位相状態の感知等により ,ループ状態に応じてフィルタ抵抗値が自動的に制御されます。抵抗値と関係のある可変パラメータとしてダンピング・ファクタがループ状況に応じた値に自動的に切り替わり ,ロックアップ・タイムの短縮が実現可能となる訳です。

式で表すと下記のようにまとめられます。

#### 各モードと時定数の関係

オプション・データ設定により各モード時はチャージポンプの出力抵抗R₁が下記のように変化し, とともにループ特性が使用状況に応じて自動的に切り替わる。

通常モード時R1 = R1' + RCP : R1大CP端子からの電圧出力時R1 = R1' : R1中チャージポンプ・スイッチ抵抗出力時R1 = Rsw : R1小

#### 各モードとPLLパラメータの関係

使用状況によってダンピングファクタ: を切り替えることができます。この切り替えはCP端子からの電圧出力時のダンピング・ファクタが0.9~1.1になるループ・フィルタを構成すれば,オプション・データによるLSI内部へのチャージポンプ・スイッチ抵抗出力の極性反転タイミングの設定およびロック検出回路へのロック感度設定に応じて自動的に切り替えることが可能になります。

通常モード時 = 0.3 ~ 0.5程度 (高C/N,低カットオフ周波数)

CP端子からの電圧出力時 = 0.9 ~ 1.1

(隣接チャネルへの周波数変更に使用)

チャージポンプ・スイッチ抵抗出力時 =3~

(間欠動作立ち上げ時等に使用)

表10-3 ロックアップモードとパラメータの変化

| モード     | СР出力                | R <sub>1</sub> | n |       | t      | 収束   | ループノイズ |

|---------|---------------------|----------------|---|-------|--------|------|--------|

| ロックアップ・ | チャージポンプ・スイッチ抵抗によるパ  | 小              | 大 | 大     | 小さくなる  | しない* | 大      |

| タイム短縮   | スを通った電圧出力(FI端子より出力) |                |   | 3以上   |        |      |        |

| 出力切り替え  | CP端子からの電圧出力         | 中              | 中 | 0.9   | 比較的小さく | する方向 | 中      |

|         |                     |                |   | ~ 1.1 | なる     |      |        |

| 通常モード   | CP端子からの電流出力         | 大              | 小 | 0.3   | 従来と同じ  | 一定   | 小      |

|         |                     |                |   | ~ 0.5 |        |      |        |

<sup>\*</sup>チャージポンプ・スイッチ抵抗出力の極性反転により強制的に収束方向に向かわせる。

これらの図10 - 7 , 10 - 8 より , ループ全体の系が安定に向かうためには , を大きくすれば良いことが分かりま すが,逆に帯域外信号( / n>1)の減衰量が小さくなり,ループ内のノイズが増加することを示しています。また 帯域外信号の減衰量を大きくし,C/Nをよくするには, を小さくすれば良いのですが,ループが安定するまでの nt が大きくなりますので,ロック・アップ時間が長くなることを示しています。以上のことから本LSIではループの状態 により が変化する方式をとっています。

C/Nを重視する通常モードでは,0.3程度が最適です。

また出力応答は通常0.9~1.1程度になった時点で安定すると判断できます。

フィルタのR1はCP端子による電圧出力時の をもとに計算すればよいので = 0.9とおきます。この場合 nt = 4.5 で収束すると考えます。

ここで, CP端子による電圧 電流切り替え出力でのロックアップ時間を設計目標よりt = 20 msとすると n = 225に なります。

#### 10.6 アクティブ・フィルタの計算例

# フィルタ定数の計算 アクティブ・ラグリードフィルタの場合 図10-9 アクティブ・ラグリードフィルタ

C<sub>1</sub> = 39 nFに設定すると,式(8)より

$$R_{1}'(TX) = \frac{K \cdot K_{V(TX)}}{n^{2} \cdot N_{TX} \cdot C_{1}} = \frac{0.159 \times 3.46 \times 10^{6}}{(225)^{2} \times 28769 \times 39 \times 10^{-9}}$$

$$= 9.7 \text{ k}$$

$$R_{1}'(RX) = \frac{K \cdot K_{V(RX)}}{n^{2} \cdot N_{RX} \cdot C_{1}} = \frac{0.159 \times 3.46 \times 10^{6}}{(225)^{2} \times 20309 \times 39 \times 10^{-9}}$$

$$= 13.7 \text{ k}$$

$$CP \odot W$$

$$R_{1}' R_{2} C_{1}$$

$$R_{3} T_{2}$$

また式(9)より

$$R_2 = \frac{2}{n \cdot C_1} = \frac{2 \times 0.9}{225 \times 39 \times 10^{-9}}$$

$$= 205 \,k$$

次に式(10)より

$$c = (5 \sim 10)$$

$n = (5 \sim 10) \times 225$

= 1 125 \sim 2 250

したがって式(11)より

Cc =

$$\frac{1}{R_2 \cdot c} = \frac{1}{205 \times 10^3 \times (1125 \sim 2250)}$$

= 2 200 pF ~ 4 300 pF

#### — フィルタ定数の算出結果 —

$$R_{1}{}^{\prime}\left( \tau x\right) =9.7\;k\qquad \text{, }R_{1}{}^{\prime}\left( \mathsf{R}x\right) =13.7\;k$$

$Cc = 2200 pF \sim 4300 pF$

$C_1 = 39 \text{ nF}$

#### 10.7 ループフィルタの調整とシリアルデータの設定例

#### (1) ロックアップ・タイム短縮モードを実現するループフィルタの設計例

#### 設計手順

電圧/電流出力切り替えモードの設計:ループフィルタの回路形式と定数の決定

まずループフィルタの回路形式を決定します。その後にチャージポンプのドライブ設定で電圧出力(データ:111)にし,ロックアップ・タイムが最小になるようにループ・フィルタの定数を設定します。

ちなみにフィルタ定数の設計をロックアップタイム重視のPLLパラメータで算出し(理想状態の時定数の 決定)、実際のボード上のVCO波形をスペアナでモニタしながら最適化すると良いでしょう。

通常モードの設定:シリアル・データによるオプション設定

チャージポンプのドライブ設定で電流出力 (データ:000~110)で通常時のC/Nが最適となるように電流を設定します。このときC/Nがとれない場合再度回路定数の見直しをします。

#### 使用時

電圧出力から電流出力への切り替え:シリアルデータによるオプション設定

チャージポンプ出力自動切り替え"D10"のデータで"1"にすれば,アンロック時電圧出力,ロック後電流出力(このときドライブ設定はの設定)に自動的に切り替わるため,ロックアップ・タイムを短縮しながらと高C/Nが実現できます。

#### (2) ロックアップ・タイム短縮モードの使用法:シリアルデータによるオプション設定

ロックアップ・タイム短縮モードとは:電圧/電流出力切り替えを行うときにさらにロックアップ・タイムを 短縮するモードです。たとえば,間欠動作時の立ち上がり時にロックアップ・タイム短縮モードを使います。

#### 設定手順

D10 = 1, D13 = 1のとき, チャージポンプ極性反転 (D14/D15) のビットが "1" のときと "0" のときのチャージポンプSW抵抗 (D16/D17) をそれぞれ設定します。

#### 使用手順

間欠動作の立ち上がり時 "D13"のデータで"1"にすれば,チューニング電圧が収束するに従いチャージポンプ・スイッチ抵抗出力 CP端子電圧出力 電流出力に自動的に切り替わる訳です。

このときチャージポンプ・スイッチ出力時とCP端子電圧出力時にループゲインの変動が大きいと収束しない場合がありますので注意してください。この場合改善のためにはR1'は10k ~30k に設定するとよいでしょう。

実際に応用回路で用いたアクティブ・フィルタの定数 (表10 - 1の使用部品リスト参照)は,前記の計算による算出結果をもとに,実際によりC/N特性,ロックアップ・タイム特性を評価し,カット・アンド・トライを重ね次のように決定しました。

- 調整後のフィルタの定数(最終決定値)--

$R_1' = 10 \; k$  ,  $R_2 = 22 \; k$

Cc = 1000 pF ,  $C_1 = 39 nF$

$R_3 = 33 k$  ,  $R_4 = 10 k$

$C_2 = 1000 pF$

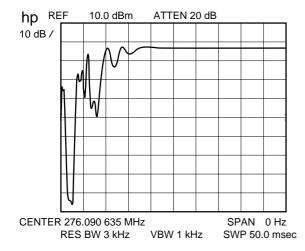

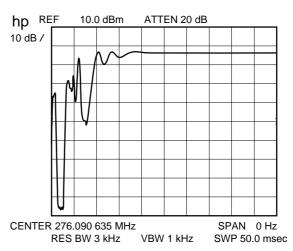

## 10.8 PLL動作時のロックアップ・タイム特性とキャリア特性

C/N = 70 dB以上 (@12.5 kHz離調),チャージポンプ・スイッチを用いたロックアップ・タイム短縮モードにおける最小ロックアップ・タイム = 9 msであり,良好な結果が得られています。

PLL-ICの電源電圧によりチャージポンプ出力(CP端子からの出力)のインピーダンスが変化しますので,オプション設定データの内容を使用条件に合わせて最適化してください。

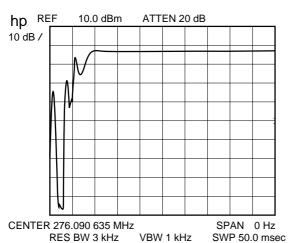

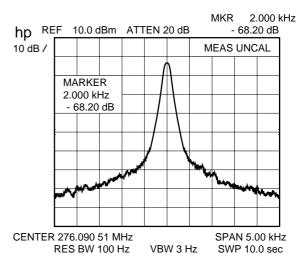

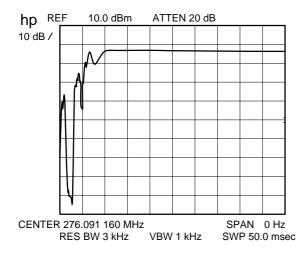

## 図10 - 10 応用評価データ VK-9B受信側VCOのPLL特性 (276 MHz) - 応用回路例 (25~27ページ参照) による

## (1) Vcc = 2.5 Vの場合

ロックアップタイム特性 (チャージポンプ・スイッチによるロックアップ・タイム短縮モード設定時) 275.5625 MHz 276.6625 MHz可変

Rsw = 1.5 k

Rsw = 500

オプション設定データ内容

チャージポンブ・ドライブ電流 : 400 μA ロック感度 : 150 ns

チャージポンプ・スイッチ抵抗出力

極性反転回数: 4 回ステップ周波数: 12.5 kHz

チャージポンプ・スイッチ抵抗値を変化 (5.0 k , 1.5 k , 500 )

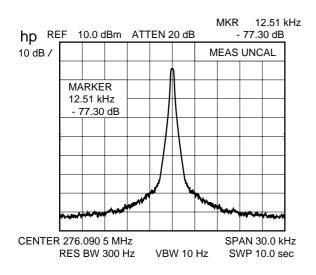

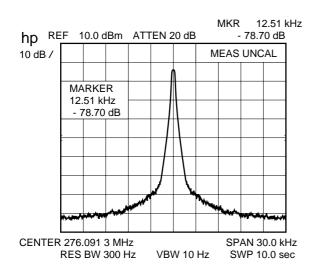

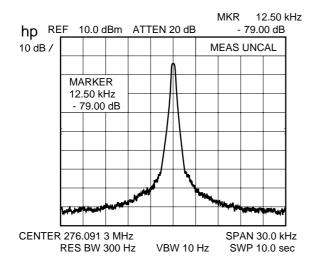

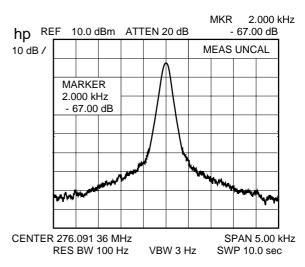

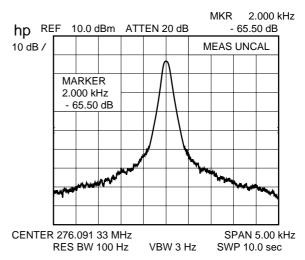

## (2) Vcc = 2.5 V, スペクトル特性

## スペクトル特性1

条件:  $Vcc = 2 v \cdot CP = 100 \mu A$

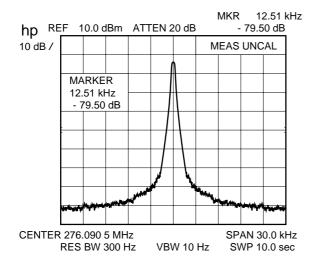

#### スペクトル特性3

条件:  $Vcc = 2 \vee \cdot CP = 400 \mu A$

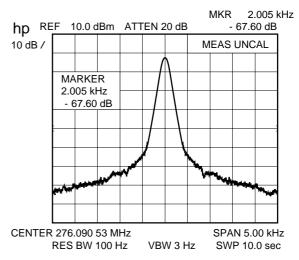

## スペクトル特性2

条件:  $Vcc = 2 \lor \cdot CP = 100 \mu A$ (SPAN = 5 KHz)

#### スペクトル特性4

条件:  $Vcc = 2 \lor \cdot CP = 400 \mu A$ (SPAN = 5 KHz)

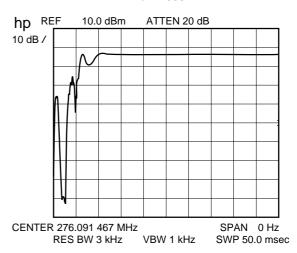

## (3) Vcc = 5.0 Vの場合

ロックアップタイム特性 (チャージポンプ・スイッチによるロックアップ・タイム短縮モード設定時) 257.5625 MHz 276.6625 MHz可変

Rsw = 500

Rsw = 150

オプション設定データ内容

チャージポンブ・ドライブ電流 : 400 μA ロック感度 : 150 ns

チャージポンプ・スイッチ抵抗出力

極性反転回数 : 8 回ステップ周波数 : 12.5 kHz

チャージポンプ・スイッチ抵抗値を変化 (1.5 k ,500 ,150 )

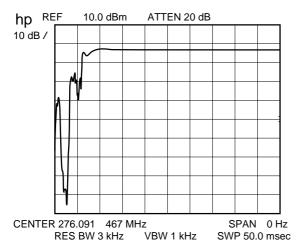

## (4) Vcc = 5.0 V, スペクトル特性

## スペクトル特性1

条件:  $Vcc = 5 \vee \cdot CP = 100 \mu A$

## スペクトル特性3

条件:  $Vcc = 5 \vee \cdot CP = 400 \mu A$

## スペクトル特性2

条件:  $Vcc = 5 \text{ v} \cdot CP = 100 \ \mu A$ (SPAN = 5 KHz)

## スペクトル特性4

条件:  $V_{CC} = 5 \vee \cdot CP = 400 \mu A$ (SPAN = 5 KHz)

## 11. おわりに

以上,コードレス電話,携帯無線機用80 MHz ~ 550 MHz用デュアルPLL周波数シンセサイザLSI,  $\mu$  PD3140GSの使い方と応用についてご紹介しました。

今後の商品展開として,アナログ・セルラ電話用デュアルPLL周波数シンセサイザLSIおよびディジタルセルラ対応 の高速ロックアップPLLおよび各種ディジタル移動体通信機に対応した製品を計画していきます。

**補足** μ PD3140GSのご評価用ツールとして「応用評価用基板」と「データ発生プログラム」がございます。 付録にてその取扱い説明を行います。

## 付録 (1)応用評価基板の使用法

#### 1.1 測定装置

電源,スペクトラム・アナライザ,データ発生用パソコン(ディスクトップなど),シグナル・ジェネレータ(水晶振動子またはTCXOを用いる場合は不要),オシロスコープ

#### 1.2 基板に部品を実装

μPD3140GS基板に「応用回路例とその特性」等を参考にして外付け回路を設計し,抵抗や容量等を実装します。 μPD2844GS基板を使用する場合は以下の変更をお願いします。

|     | μΡΙ    | D2844GS  | μ PD3140GS |  |  |  |

|-----|--------|----------|------------|--|--|--|

| 175 | ゚ン     | $V_{DD}$ | 基準発振バッファ出力 |  |  |  |

| 18년 | ژ<br>ک | PS       | Vcc2       |  |  |  |

|     |        |          |            |  |  |  |

#### 1.3 測定準備

- ・VCO波形をスペクトラムアナライザでモニタします。

- ・ロックアップタイム測定は,正確にはスペクトラム・アナライザのゼロスパンモードによりVCOのキャリアの立ち上がりをモニタすることにより行います。

- ・オーバ・シュートを見る場合はVCOのV<sub>t</sub>の部分をストレージ・オシロスコープでモニタしてそのチューニング電圧の波形を観察します。

#### 1.4 回路定数およびオプション設定の調整

- ・ロックアップタイムは電圧/電流出力切り替えモード時のループ・フィルタの回路定数を最適化願います。さら に短縮する場合はチャージポンプ・スイッチ抵抗出力の設定をお願いします。

- ・C/Nの調整はチャージポンプ・ドライブ電流の最適化をお願いします。

## 1.5 備考

NEC製データ発生用プログラムを使用する場合は次項を参照願います。

## (2) μ PD3140GS**用データ発生プログラムの使用法**

#### . 必要なもの

PC98シリーズのパソコン注1

プリンタケーブル

プログラムの入ったディスク (μPD3140GSデータ発生プログラム: Ver3) <sup>注2</sup>

- **注1**.パソコンによっては出力伝送速度が異なってしまう場合がありますのでご注意ください(例えばノートタイプ。この場合™をご参照ください)。

- 2.本プログラムを用いてICを評価する場合, Ver 3 以前のものは表示画面とデータ内容が異なっている場合がありますのでご確認ください(メニュー画面にVer 3 の表示のないものはVer 3 以前のものです)。

## . プログラムのパッケージ内容

IO.SYS

MSDOS.SYS

COMMAND.COM

PRINT.SYS

**CONFIG.SYS**

AUTOEXEC.BAT

N88BASIC.LIB

D3140S.EXE プログラム本体

D3140S.DEF 前回の設定状態のセーブファイル

#### . プログラムの起動方法

ディスクをドライブにいれてリセットすると自動的に立ち上がります。

ハードディスク等で使うときはCONFIG.SYSにPRINT.SYSを設定し,N88BASIC.LIB,D3140.EXE,D3140.DEFを同じディレクトリに入れて,D3140.EXEを入れたディレクトリでD3140と打ちます。

## . プログラムの操作方法

#### 基本操作

キーでメニューを移動します。

トップメニュー上でSPACEキーを押すと現在設定されている状態を出力します(同じ設定でICを替えて測定するときに使用)。

HELPキーで現在設定されている状態を表示します(設定状態の確認に使用)。

メニュー項目の選択はリターンキーで行います。

#### トップメニュー項目

#### 動作切り替え

ICの動作状態を任意に替えることができます。 キーでPLL1またはPLL2を選択し,スペースキーによってON,OFFを切り替えます。なお,スペースキーで切り替えるごとにオプションのみデータが出力されます。

#### CP設定

チャージポンプに関する設定を行います。選択するとサブメニューが表示されます。メインメニューに戻るには「終了」を選択するか,スペースキーまたはSTOPキーを押します。メニューの内容についてはCPメニューを参照ください。

#### ロック感度

ロック判定をするときの感度を設定します。表示されている4種類の中から キーで選択しリターンキーを押します。

#### 周波数設定

リファレンス, PLL1, PLL2の周波数の設定を行います。選択するとサブメニューが表示されます。メインメニューに戻るには「終了」を選択するか,スペースキーまたはSTOPキーを押します。メニューの内容については周波数設定メニューを参照ください。

#### トリガ

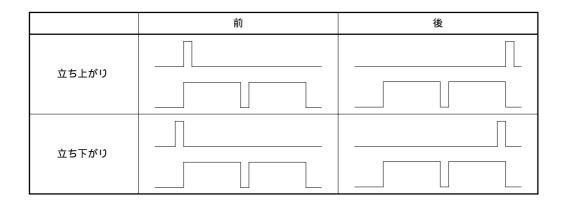

トリガに関する設定を行います。これらはすべて キーで選択しリターンキーを押します。まずトリガ 位置を選択します。「前」はデータの出力前にトリガを出し、「後」はデータの出力後にトリガを出します。次にトリガ動作を選択します。 は立ち上がり動作 , は立ち下がり動作を表します。最後にPLLのデータの順番を選択します。これはPLL1とPLL2のどちらを先に出力するかを選択します。

#### 終了

プログラムを終了する。

#### CPメニュー

#### 極性切り替え

チャージポンプの極性を切り替えます。

#### ドライブ

チャージポンプのドライブ電流を選択します。表示されている8種類の中から キーで選択しリターンキーを押します。

CP制御(チャージポンプの電圧/電流出力自動切り替え)

チャージポンプ電流の自動制御を行うかを選択します。 キーで選択しリターンキーを押します。 高速CP(ロックアップ・タイム短縮モード)

チャージポンプ・スイッチを使用するかを選択します。 キーで選択しリターンキーを押します。 SW制御(チャージポンプ・スイッチ抵抗出力の極性反転回数)

チャージポンプとフィルタ用トランジスタ間の抵抗を切り放すタイミングを選択します。表示されている 8種類の中から キーで選択しリターンキーを押します。1回目とはチャージポンプが1回反転したら 切り放すことを意味しています。

抵抗設定 (チャージポンプ・スイッチ抵抗値)

チャージポンプとフィルタ用トランジスタ間の抵抗値を設定します。表示されている8種類の中から キーで選択しリターンキーを押します。 終了

トップメニューに戻ります。

なお選択すると直ちにオプションデータのみ出力されます。

#### 周波数設定メニュー

REF

リファレンスの周波数(分周数)を設定します。単位はMHzで入力します。

PLL1

PLL1の周波数 (分周数)を設定します。周波数で設定時の単位はMHzで入力します。またチャネル設定時は 1 から89です。 (チャネルは国内小電力アナログコードレス電話に対応)

PII 2

PLL2の周波数(分周数)を設定します。周波数で設定時の単位はMHzで入力します。またチャネル設定時は1から89です。

設定方法

PLL1, PLL2をチャネルで設定するか,周波数で設定するかを選択します。 キーで選択しリターンキーを押します。チャネルを選択した場合は親機用か子機用かを選択します。

オプション(国内小電力アナログコードレス電話以外の周波数での評価を行う場合)

PLL1, PLL2のチャネル1の周波数およびステップ周波数を設定します。単位はステップ周波数はkHzで,他はMHzで入力します。

終了

トップメニューに戻ります。

なお選択するとただちに変更したデータのみ出力されます。

## . ハードの構成

ハードはパソコンにプリンタケーブルをつけその先に以下のものを付けます。

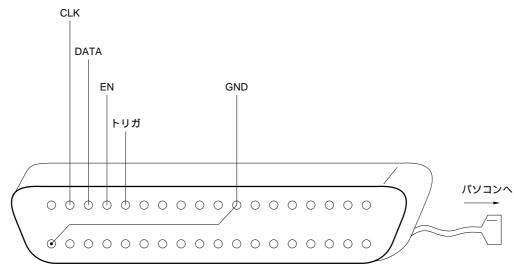

36ピンアンフェノールのメスに下図のように配線します。そして 2 ピンをCLKに , 3 ピンをDATAに 4 ピンをENにつなぎます。また11ピンと19ピンをつなぎ , そことGND (ICのGNDと共通)をつなぎます。 5 ピンはトリガとして使用できます。

プリンタケーブル外観

## . トリガ

トリガとENの関係は下図のようになっています。

## WI. プリンタ出力の伝送速度の調整

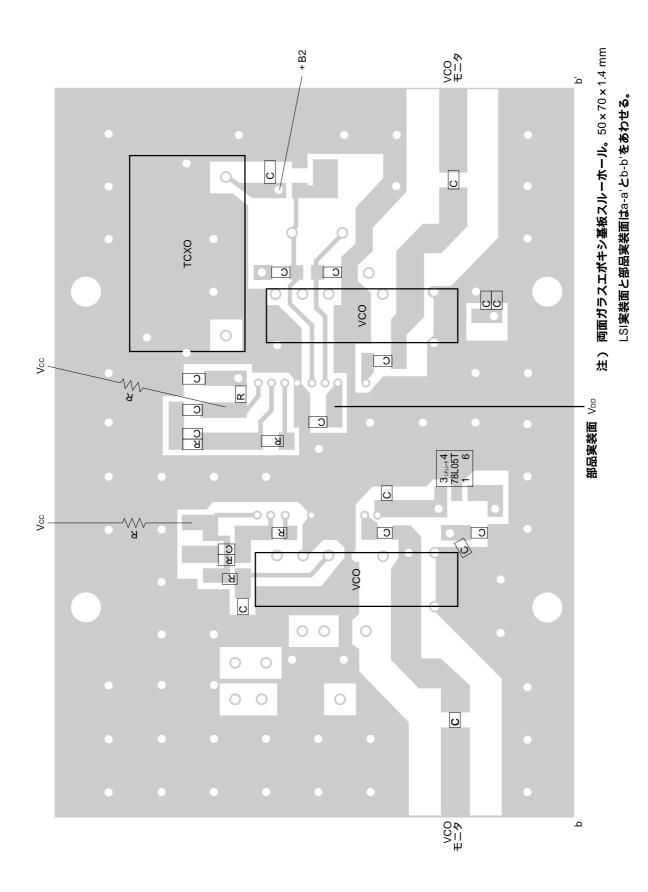

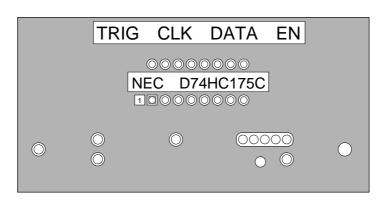

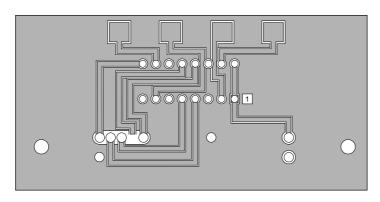

ノート・パソコンなど最近のパソコンではプリンタ出力の伝送速度が速いため , NEC製QUAD D-TYPE FLIP-FLOP・IC  $\mu$  PD74HC175Cを用いた変換回路により伝送速度を調整すれば , 本プログラムを修正することなく評価に使用できます。図にその変換ボードのプリント・パターンを示します (  $\mu$  PD74HC175Cの使用についてはそのデータシートをご参照ください ) 。

## 図 プリンタ出力 伝送速度変換用ポードのプリント・パターン

IC実装面

裏 面

**注** 39×68×1.6 mmガラスエポキシ基板に 両面銅パターニング半田メッキ 裏面はa-a'とb-b'をあわせる。

### 使用法

- (1) IC実装面に μ PD74HC175Cと36ピン・アンフェノール・オスのコネクタを差し込み,裏面で半田付けします。

- (2)IC実装面に表示しているTRIG, CLK, DATA, ENは裏面の四角パターンと対応しています。この四角のパターンにICに接続するデータライン用ケーブルを半田付けします。

- (3)36ピン・アンフェノールのオスとメスをつなげればプリンタ出力の伝送速度はPLLをコントロール可能な速度となります。

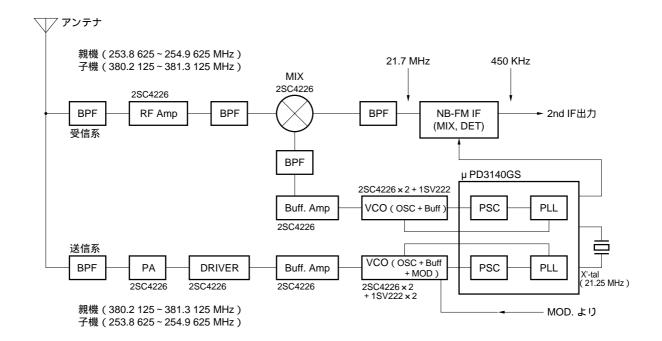

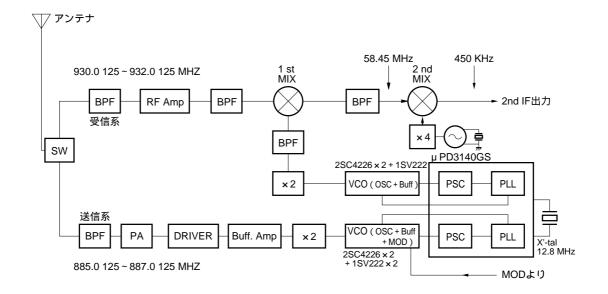

## (3)システム応用例プロック図

## 国内小電力アナログ・コードレス電話システム・ブロック図例

## CT1+アナログ・コードレス電話システム・プロック図例

# **(4)** μ PD3140GS トラブル・シューティング

1. μ PD3140GS量産品のロット番号と製品仕様の相違点を表 1 に示します。

表1 ロット番号と製品仕様の相違点

| ロット番号  | 製品レベル   | 主 な 規 格                     |

|--------|---------|-----------------------------|

| 末尾A~C  | DSサンプル品 | 温度範囲 - 20~ +75 。量産品と回路相違有。  |

| 415D以降 | 量産品     | 最終FIX回路。温度範囲 - 35~ +85 に拡大。 |

| 428D以降 | 量産品     | FI端子リーク規格の追加。               |

| 526D以降 | 量産品     | ロック動作選別追加。                  |

2. 主な動作不具合と使用上の注意事項について表2にまとめます。

表 2 動作不具合と使用上の注意

| 現象              | 問 題         | 外付けループフィルタの調整      | フィルタ以外の調整        |

|-----------------|-------------|--------------------|------------------|

| 高温動作で誤動作        | ループゲインが高すぎる | 直列抵抗値を上げて自然周波      | オプションデータによりチャージポ |

|                 |             | 数を下げる              | ンプ・ドライブ電流を下げる    |

| 低温動作で誤動作        | ループゲインが低すぎる | 直列抵抗値を下げて自然周波      | オプションデータによりチャージポ |

|                 |             | 数を上げる              | ンプ・ドライブ電流を上げる    |

| チャージポンプ・スイッチが切  | 切り替え時のループゲイ | 直列抵抗値を10 k~30 k にす |                  |

| り替わらない          | ン変動が大きい     | <b>వ</b>           |                  |

| 電圧 電流出力切り替えでロッ  | 電圧出力時のダンピング | 電圧出力時 = 0.9~1.1とし, |                  |

| クアップ・タイムが短縮されな  | ファクタ が小さすぎる | 電流出力時 = 0.3~0.5程度に |                  |

| LI              |             | する                 |                  |

| 被変調VCOでロックがはずれる | ロック感度が狭すぎる  |                    | オプションデータによりロック感度 |

|                 |             |                    | 設定値を広くする         |

| フィルタ定数を最適化してもキ  | 電源から低周波ノイズが |                    | 電源ラインをの低周波インピーダン |

| ャリアの数百Hz近傍にスプリア | 乗る          |                    | スを下げる(GNDベタまたは低周 |

| スが発生する          |             |                    | 波用バイパス・コンデンサを挿入) |

## 参考資料

アプリケーションノート μ PD2843GS, μ PD2844BGS, 2844BGS(1)の使い方と応用 資料番号IEA-722

技術資料 PLLを使った周波数シンセサイザ回路の基礎 資料番号IEB-550

データシート μ PD3140GS 資料番号P10957JJ2V0DS00

## その他参考資料

| 資 料 名               | 資料番号            |  |  |

|---------------------|-----------------|--|--|

| NEC半導体デバイスの信頼性品質管理  | IEM-5069        |  |  |

| NEC半導体デバイスの品質水準     | IEI-620         |  |  |

| 半導体デバイス実装マニュアル      | C10535JJ7V0IF00 |  |  |

| 半導体デバイス パッケージ・マニュアル | IEI-635         |  |  |

| 半導体デバイスの品質保証ガイド     | MEI-603         |  |  |

| 半導体総合セレクションガイド      | X10678JJDV0SG00 |  |  |

(メ モ)

本資料に掲載の応用回路および回路定数は、例示的に示したものであり、量産設計を対象とするものではありません。

文書による当社の承諾なしに本資料の転載複製を禁じます。

本資料に記載された製品の使用もしくは本資料に記載の情報の使用に際して,当社は当社もしくは第三者の知的所有権その他の権利に対する保証または実施権の許諾を行うものではありません。上記使用に起因する第三者所有の権利にかかわる問題が発生した場合,当社はその責を負うものではありませんのでご了承ください。

M4A 94.11

# --- お問い合わせは ,最寄りのNECへ -----

## 【営業関係お問い合わせ先】

## 【本資料に関する技術お問い合わせ先】

| 半導体ソリューション技術本部<br>超高周波・光デバイス技術部 | 〒210 川崎市幸区塚越三丁目484番地            | 川崎  | (044)548-8881 |                                            |  |

|---------------------------------|---------------------------------|-----|---------------|--------------------------------------------|--|

| 半導体販売技術本部東日本販売技術部               | 〒108-01 東京都港区芝五丁目7番1号(NEC本社ビル)  | 東京  | (03)3798-9619 | 半導体<br>インフォメーション センター                      |  |

| 半導体販売技術本部中 部 販 売 技 術 部          | 〒460 名古屋市中区錦一丁目17番1号(NEC中部ピル)   | 名古屋 | (052)222-2125 | FAX( <b>044)548-7900</b><br>(FAXにてお願い致します) |  |

| 半導体販売技術本部<br>西日本販売技術部           | 〒540 大阪市中央区城見一丁目 4番24号(NEC関西ビル) | 大 阪 | (06) 945-3383 |                                            |  |