# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# RENESAS

# HD404374/HD404384/HD404389/ HD404082/HD404084 シリーズ

A/D コンバータ内蔵、低電圧動作 AS マイコン

RJJ03B0049-0500H Rev.5.00 2003.09.11

#### 概要

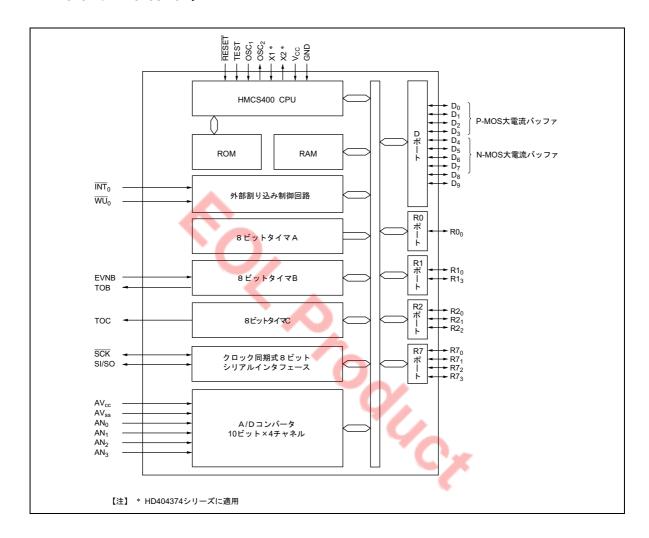

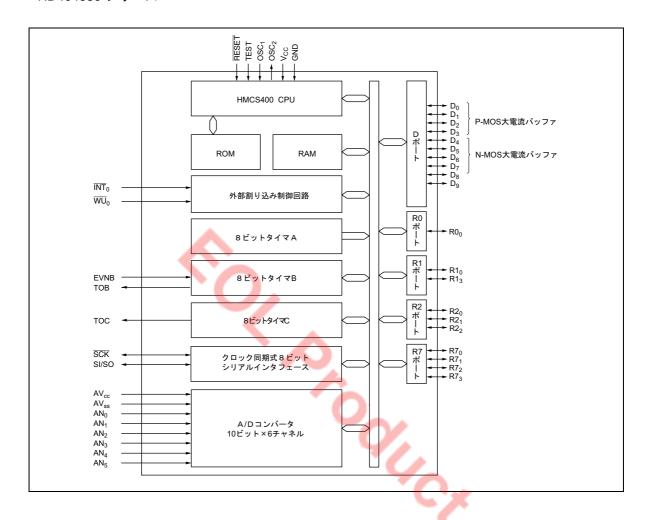

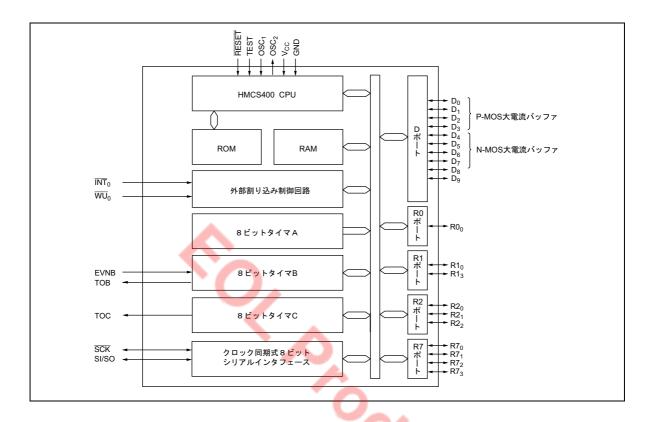

HD404374 シリーズ、HD404384 シリーズ、HD404389 シリーズは、10 ビット A/D コンバータ、シリアルインタフェース、および大電流入出力端子を持っており、バッテリーチャージャーなど高分解能の A/D 変換制御が必要なアプリケーションに適した低電圧動作 4 ビットシングルチップマイコンです。

HD404082/HD404084 シリーズは、HD404384 シリーズの下位品種であり、ソフトウェアの下位互換が可能な低電圧動作 4 ビットシングルチップマイコンです。

HD404374 シリーズは、時計用 32.768kHz サブ発振子を付けることにより、時計のカウントアップが行え、 豊富な低消費電力モードにより、消費電流の低減が図れます。

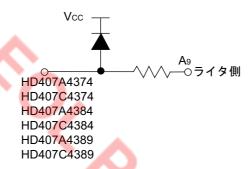

HD407A4374、HD407A4384、HD407A4389、HD407C4374、HD407C4384、HD407C4389 は PROM を内蔵した ZTAT®マイコンです。システムの開発期間を飛躍的に短縮し、デバッグから量産までをスムーズに立ち上げることができます(PROM のプログラム仕様は 27256 タイプと同様です)。

#### 特長

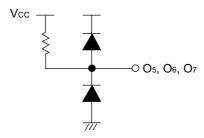

● 入出力端子 20本

大電流入出力端子 (ソース 10mA max) 4 本 大電流入出力端子 (シンク 15mA max) 4 本

アナログ入力兼用端子 4本(HD404374/HD404384/HD404389 シリーズ)

- タイマ/カウンタ 16 ビットタイマ 1本 (8 ビットタイマ 2本としても使用可能)8 ビットタイマ 1本

- タイマ出力 2本 (PWM 出力可能)

- イベント入力 1本 (エッジプログラマブル)

- 8ビットクロック同期式シリアルインタフェース 1本

ZTAT®: Zero Turn Around Time ZTAT®は(株)ルネサステクノロジの登録商標です。

#### HD404374/HD404384/HD404389/HD404082/HD404084 シリーズ

● A/D コンバータ 10 ビット×4 チャネル (HD404374/HD404384 シリーズ)

10 ビット×6 チャネル (HD404389 シリーズ)

なし (HD404082/HD404084 シリーズ)

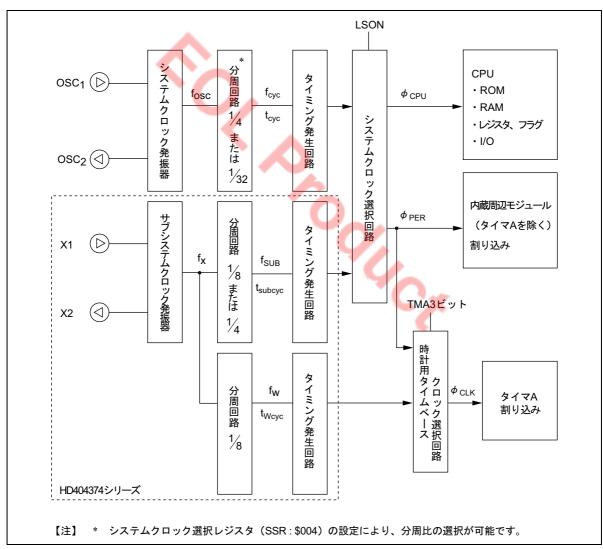

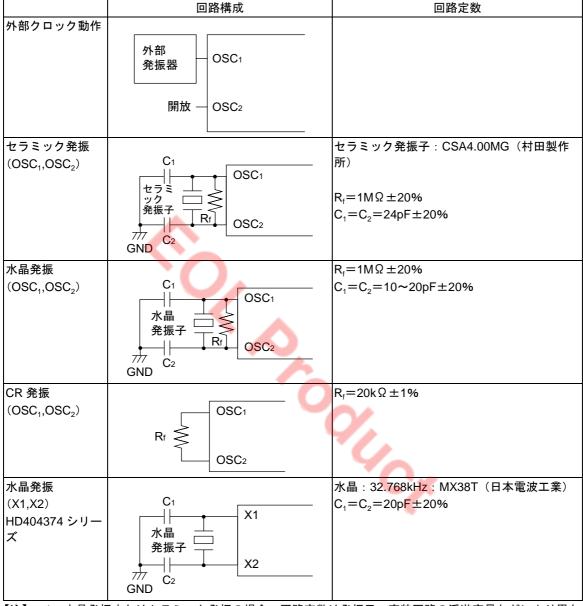

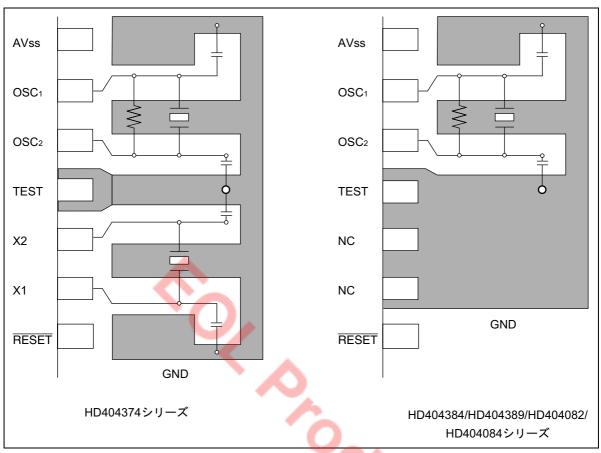

• 発振器内蔵

HD404374 シリーズ

メインクロック (セラミック発振子、水晶発振子、CR 発振、または外部クロック動作可能)

サブクロック (32.768kHz 水晶発振子)

HD404384/HD404389/HD404082/HD404084 シリーズ

メインクロック (セラミック発振子、水晶発振子、CR発振、または外部クロック動作可能)

● 割り込み

外部 2本

内部 5本 (HD404374/HD404384/HD404389 シリーズ)

4本 (HD404082/HD404084 シリーズ)

- サブルーチンスタック 割り込み含め最大 16 レベル

- 低消費電力モード

HD404374 シリーズ 4

HD404384/HD404389/HD404082/HD404084 シリーズ

- HD404384/HD404389/HD404082/HD404084 シリー∧ 2モジュールスタンバイ (タイマ、シリアル、A/D コンバータ)

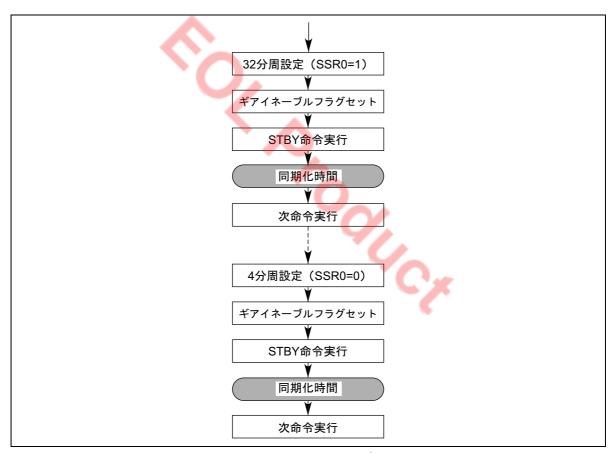

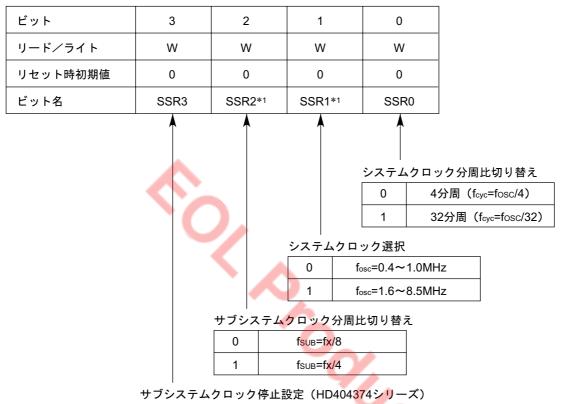

- システムクロック分周ソフトウェア切り替え (1/4 または 1/32)

- ストップモードからの復帰入力 1本

- 命令実行時間

最小 0.89 μs(f<sub>OSC</sub>=4.5MHz、1/4 分周)

最小 0.47 μs(f<sub>OSC</sub>=8.5MHz、1/4 分周)

動作電圧

$Vcc = 1.8V \sim 5.5V$

$Vcc = 2.0V \sim 5.5V (ZTAT^{\circ})$

#### 【使用上の注意】

(1) マスク ROM 版および ZTAT®版は、データシートに記載しております電気的特性の基準値を十分満足することを確認しております。しかし、製造プロセスの違い、内部の配線パターン等の違いにより、特性上の実力値や動作マージン、ノイズマージン等は異なります。つきましては、いずれの製品におかれましても同等の実機システム評価試験を行い、動作のご確認をお願いいたします。

QUA

(2) 電源投入後、メモリレジスタ、データエリア、スタックエリアの値は不定です。初期化の 上ご使用ください。

## 製品ラインアップ

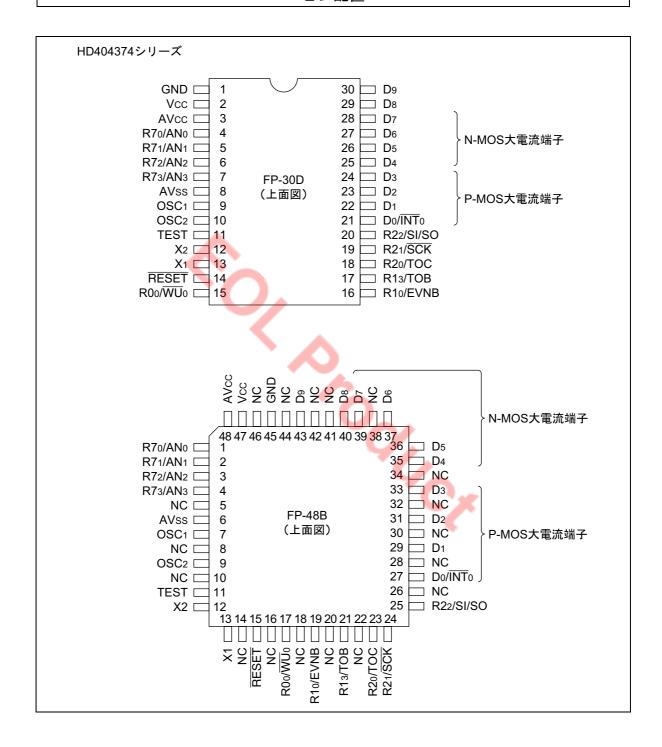

#### HD404374 シリーズ

| 区分      | 製品名        | 型名           | ROM (ワード) | RAM(ディジット) | パッケージ                                  |

|---------|------------|--------------|-----------|------------|----------------------------------------|

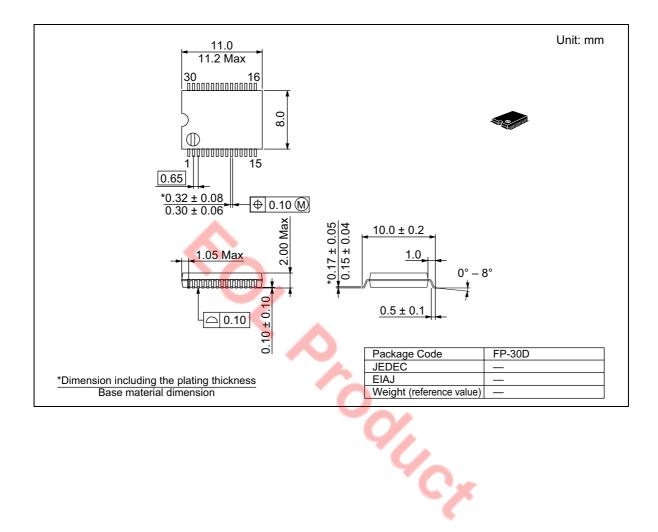

| マスク ROM | HD404372   | HD404372FT   | 2,048     | 512        | 30 ピンプラスチック SSOP(FP-30D)               |

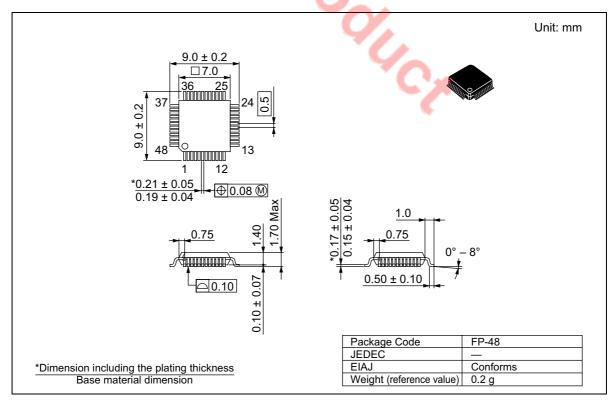

|         |            | HD404372H    |           |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HD40A4372  | HD40A4372FT  |           |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD40A4372H   |           |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HD40C4372  | HD40C4372FT  |           |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD40C4372H   |           |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HD404374   | HD404374FT   | 4,096     |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD404374H    |           |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HCD404374  | HCD404374    |           |            | チップ* <sup>2</sup>                      |

|         | HD40A4374  | HD40A4374FT  |           |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD40A4374H   |           |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HD40C4374  | HD40C4374FT  |           |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD40C4374H   |           |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HCD40C4374 | HCD40C4374   |           |            | チップ* <sup>2</sup>                      |

| ZTAT®   | HD407A4374 | HD407A4374FT | 4,096     |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         | HD40C4374  | HD407C4374FT |           |            | 30 ピンプラスチック SSOP(FP-30D)               |

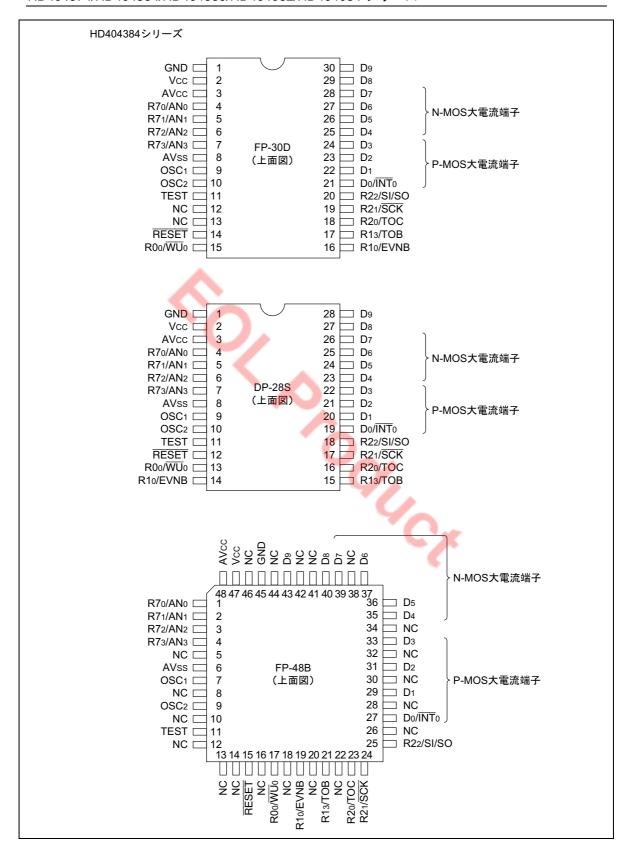

## HD404384 シリーズ

| 区分      | 製品名        | 型名          | ROM (ワード) | RAM | (ディジット) | パッケージ                                  |

|---------|------------|-------------|-----------|-----|---------|----------------------------------------|

| マスク ROM | HD404382   | HD404382FT  | 2,048     |     | 512     | 30 ピンプラスチック SSOP(FP-30D)               |

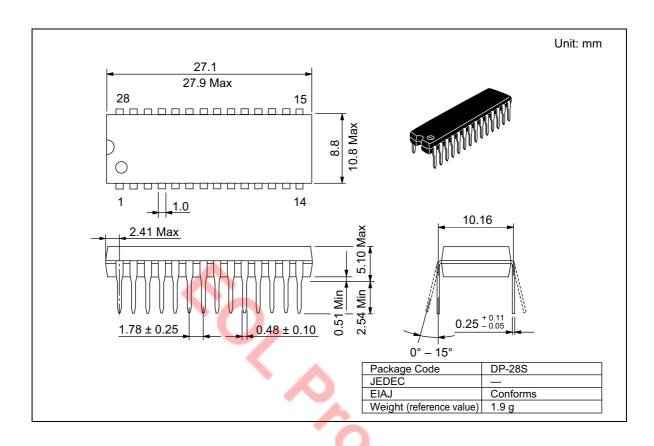

|         |            | HD404382S   |           |     | 7/,     | 28 ピンプラスチック DILP(DP-28S)               |

|         |            | HD404382H   |           |     |         | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HD40A4382  | HD40A4382FT |           |     | • (     | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD40A4382S  |           |     |         | 28 ピンプラスチック DILP(DP-28S)               |

|         |            | HD40A4382H  |           |     |         | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HD40C4382  | HD40C4382FT |           |     |         | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD40C4382S  |           |     |         | 28 ピンプラスチック DILP(DP-28S)               |

|         |            | HD40C4382H  |           |     |         | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HD404384   | HD404384FT  | 4,096     |     |         | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD404384S   |           |     |         | 28 ピンプラスチック DILP(DP-28S)               |

|         |            | HD404384H   |           |     |         | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HCD404384  | HCD404384   |           |     |         | チップ* <sup>2</sup>                      |

|         | HD40A4384  | HD40A4384FT |           |     |         | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD40A4384S  |           |     |         | 28 ピンプラスチック DILP(DP-28S)               |

|         |            | HD40A4384H  |           |     |         | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HD40C4384  | HD40C4384FT |           |     |         | 30 ピンプラスチック SSOP(FP-30D)               |

|         |            | HD40C4384S  |           |     |         | 28 ピンプラスチック DILP(DP-28S)               |

|         |            | HD40C4384H  |           |     |         | 48 ピンプラスチック LQFP(FP-48B)* <sup>1</sup> |

|         | HCD40C4384 | HCD40C4384  |           |     |         | チップ* <sup>2</sup>                      |

| 区分    | 製品名        | 型名           | ROM (ワード) | RAM(ディジット) | パッケージ                    |

|-------|------------|--------------|-----------|------------|--------------------------|

| ZTAT® | HD407A4384 | HD407A4384FT | 4,096     | 512        | 30 ピンプラスチック SSOP(FP-30D) |

|       |            | HD407A4384S  |           |            | 28 ピンプラスチック DILP(DP-28S) |

|       | HD407C4384 | HD407C4384FT |           |            | 30 ピンプラスチック SSOP(FP-30D) |

|       |            | HD407C4384S  |           |            | 28 ピンプラスチック DILP(DP-28S) |

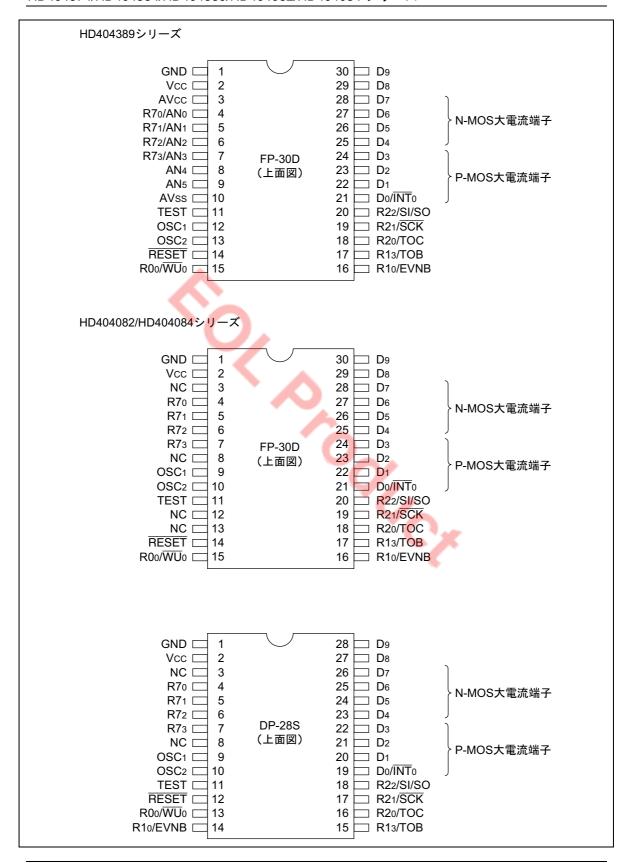

## HD404389 シリーズ

| 区分      | 製品名        | 型名           | ROM (ワード) | RAM(ディジット) | パッケージ                    |

|---------|------------|--------------|-----------|------------|--------------------------|

| マスク ROM | HD404388   | HD404388FT   | 8,192     | 512        | 30 ピンプラスチック SSOP(FP-30D) |

|         | HD40A4388  | HD40A4388FT  |           |            | 30 ピンプラスチック SSOP(FP-30D) |

|         | HD40C4388  | HD40C4388FT  |           |            | 30 ピンプラスチック SSOP(FP-30D) |

|         | HD404389   | HD404389FT   | 16,384    |            | 30 ピンプラスチック SSOP(FP-30D) |

|         | HD40A4389  | HD40A4389FT  |           |            | 30 ピンプラスチック SSOP(FP-30D) |

|         | HD40C4389  | HD40C4389FT  |           |            | 30 ピンプラスチック SSOP(FP-30D) |

| ZTAT®   | HD407A4389 | HD407A4389FT | 16,384    |            | 30 ピンプラスチック SSOP(FP-30D) |

|         | HD407C4389 | HD407C4389FT |           |            | 30 ピンプラスチック SSOP(FP-30D) |

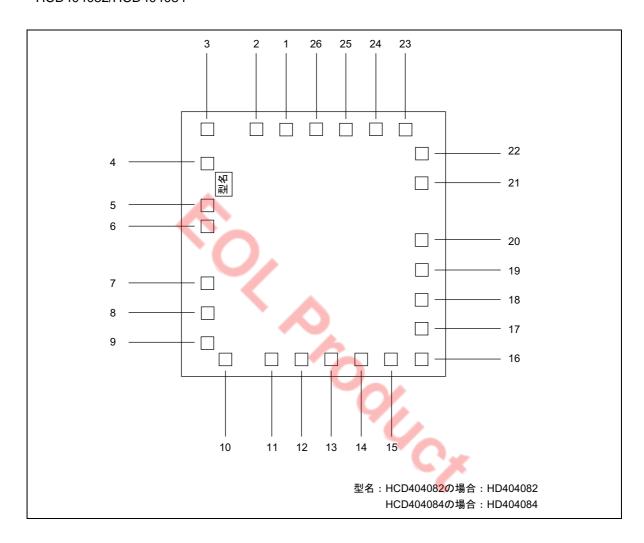

## HD404082 シリーズ

| 区分      | 製品名         | 型名          | ROM (ワード)          | RAM(ディジット) | パッケージ                                  |

|---------|-------------|-------------|--------------------|------------|----------------------------------------|

| マスク ROM | HD404081    | HD404081FT  | 1,024              | 128        | 30 ピンプラスチック SSOP(FP-30D)               |

|         |             | HD404081S   | ·                  | A.         | 28 ピンプラスチック DILP(DP-28S)               |

|         |             | HD404081H   |                    |            | 48 ピンプラスチック LQFP(FP-48B)*²             |

|         | HD40A4081   | HD40A4081FT |                    |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |             | HD40A4081S  |                    |            | 28 ピンプラスチック DILP(DP-28S)               |

|         |             | HD40A4081H  |                    |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>2</sup> |

|         | HD40C4081   | HD40C4081FT |                    |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |             | HD40C4081S  |                    |            | 28 ピンプラスチック DILP (DP-28S)              |

|         |             | HD40C4081H  |                    |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>2</sup> |

|         | HD404082    | HD404082FT  | 2,048              |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |             | HD404082S   |                    |            | 28 ピンプラスチック DILP(DP-28S)               |

|         |             | HD404082H   |                    |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>2</sup> |

|         | HCD404082   | HCD404082   |                    |            | チップ * <sup>4</sup>                     |

|         | HD40A4082   | HD40A4082FT |                    |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |             | HD40A4082S  |                    |            | 28 ピンプラスチック DILP(DP-28S)               |

|         |             | HD40A4082H  |                    |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>2</sup> |

|         | HD40C4082   | HD40C4082FT |                    |            | 30 ピンプラスチック SSOP(FP-30D)               |

|         |             | HD40C4082S  |                    |            | 28 ピンプラスチック DILP(DP-28S)               |

|         |             | HD40C4082H  |                    |            | 48 ピンプラスチック LQFP(FP-48B)* <sup>2</sup> |

|         | HCD40C4082  | HCD40C4082  |                    |            | チップ * <sup>4</sup>                     |

| ZTAT®   | HD404384 シリ | Jーズの ZTAT®  | を使用 * <sup>3</sup> |            |                                        |

#### HD404084 シリーズ

| 区分      | 製品名         | 型名          | ROM (ワード)               | RAM(ディジット) | パッケージ                    |

|---------|-------------|-------------|-------------------------|------------|--------------------------|

| マスク ROM | HD404084    | HD404084FT  | 4,096                   | 256        | 30 ピンプラスチック SSOP(FP-30D) |

|         |             | HD404084S   |                         |            | 28 ピンプラスチック DILP(DP-28S) |

|         | HCD404084   | HCD404084   |                         |            | チップ *4                   |

|         | HD40A4084   | HD40A4084FT |                         |            | 30 ピンプラスチック SSOP(FP-30D) |

|         |             | HD40A4084S  |                         |            | 28 ピンプラスチック DILP(DP-28S) |

|         | HD40C4084   | HD40C4084FT |                         |            | 30 ピンプラスチック SSOP(FD-30D) |

|         |             | HD40C4084S  |                         |            | 28 ピンプラスチック DILP(DP-28S) |

|         | HCD40C4084  | HCD40C4084  |                         |            | チップ * <sup>4</sup>       |

| ZTAT®   | HD404384 シリ | ノーズの ZTAT®  | ・<br>を使用 * <sup>3</sup> |            |                          |

- 【注】 \*1 FP-48B は、下記の制約があります。

- (1) マスク ROM 版のみの展開。デバック等は他のパッケージの ZTAT®での対応となります。 ▲

- (2) WSは、<mark>量産先</mark>頭での対応となります。

- \*2 計画中

- \*3 ZTAT®でのチップ出荷は対応していません。

- \*4 チップ出荷の場合、出荷仕様がパッケージ品と異なりますので必ず、弊社営業担当にご確認ください。

NOON CX

# 機能一覧

|                                         | 製品名            | HD404372                   | HD404374                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | HD404382                                | HD404384                                                                                                                                                         | HD404388                     | HD404389                                           | HD404081               | HD404082               | HCD404082      | HD404084               | HCD404084  |

|-----------------------------------------|----------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------|------------------------|------------------------|----------------|------------------------|------------|

|                                         |                | HD40A4372<br>HD40C4372     | HD40A4374<br>HD40C4374<br>HD407A4374<br>HD407C4374                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | HD40A4382<br>HD40C4382                  | HD40A4384<br>HD40C4384<br>HD407A4384<br>HD407C4384                                                                                                               | HD40A4388<br>HD40C4388       | HD40A4389<br>HD40C4389<br>HD407A4389<br>HD407C4389 | HD40A4081<br>HD40C4081 | HD40A4082<br>HD40C4082 | HCD40C4082     | HD40A4084<br>HD40C4084 | HCD40C4084 |

| ROM (7- F)                              | ا<br>ب         | 2,048                      | 4,096<br>ZTAT®I≴PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2,048                                   | 4,096<br>ZTAT®I≴PROM                                                                                                                                             | 8,192                        | 16,384<br>ZTAT®I‡PROM                              | 1,024                  | 2,048                  | 2,048          | 4,096                  | 4,096      |

| RAM (ディジット)                             | イジット)          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | 512                                                                                                                                                              |                              |                                                    |                        |                        | 128            |                        |            |

| <u>Q</u>                                |                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | 20本 (max)                                          |                        |                        |                |                        |            |

| 大雅                                      | 大電流入出力<br>端子   |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | 4                                                                                                                                                                | 本(Source 10m                 | 4本(Source 10mA max)、4本(Sink 15mA max)              | ink 15mA max)          |                        |                |                        |            |

| ア.                                      | アナログ入力<br>兼用端子 |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | 4本                                                                                                                                                               |                              |                                                    |                        |                        | I              |                        |            |

| タイマ/カウンタ                                | カウンタ           |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | 3★                                                 |                        |                        |                |                        |            |

| Ý,                                      | タイマ出力          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  | 24                           | 2本 (PWM出力可能)                                       |                        |                        |                |                        |            |

| ÷                                       | イベント入力         |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  | #                            | 1本 (エッジ選択可能)                                       |                        |                        |                |                        |            |

| シリアルインタフェース                             | ۲<br>ا         |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  | 1 <del>↑</del> (8            | 1本(8ビットクロック周期式)                                    | <b>蜀</b> 式)            |                        |                |                        |            |

| A/Dコンバータ                                | 1-4            |                            | 10ビット×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ビット×4チャネル                               |                                                                                                                                                                  | 10ビット、                       | 10ビット×6チャネル                                        |                        |                        | ı              |                        |            |

| 割り込み                                    | 外部             |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | 2本                                                 |                        |                        |                |                        |            |

| 要因                                      | 岳              |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | 5本                                                                                                                                                               |                              | 4                                                  |                        |                        | 4本             |                        |            |

| 低消費電力モード                                | カモード           |                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |                                                                                                                                                                  |                              |                                                    | 2                      |                        |                |                        |            |

| K                                       | ストップモード        |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | 0                                                  | 4                      |                        |                |                        |            |

| <u>ו</u> ים                             |                |                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |                                                                                                                                                                  |                              | ,                                                  | 1                      |                        |                |                        |            |

| <del>'</del> '   :                      | スタンハイモート       |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | 0                                                  |                        |                        |                |                        |            |

| <u>+</u> +                              | サフアクティフ<br>モード |                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |                                                                                                                                                                  |                              |                                                    | I                      |                        |                |                        |            |

| トジューアルないジャ                              | ۷ 、            |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | 0                                                  |                        |                        |                |                        |            |

| ハント・カロッカ                                | 7 0            |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | C                                                  |                        |                        |                |                        |            |

| - ノベノムノロック - 分割ソフト切り替え                  | ノロンノト切り替え      |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | )                                                  |                        |                        |                |                        |            |

| メイン・                                    | メイン セラミック発振    |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | 0                                                  |                        |                        |                |                        |            |

| 発振器 7                                   | 水晶発振           |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                  |                              | 0                                                  |                        |                        |                |                        |            |

|                                         | CR発振           | O (HD40C437;<br>HD40C4084  | O (HD40C4372, HD40C4374, HD407C4374, HD40C4382, HD40C4384, HD407C4384, HD40C4388, HD40C4389, HD407C4389, HD40C4081, HD40C4082, HCD40C4082, HD40C4082, HD40C4088, HD40C4389, HD40C4389, HD40C4389, HD40C4088, HD40C4389, HD40C4088, HD40 | ID407C4374、HI                           | 040C4382, HD400                                                                                                                                                  | 24384、HD407C                 | 4384、HD40C438                                      | 8, HD40C4389,          | HD407C4389、F           | нD40С4081, НБ₄ | 40C4082, HCD4(         | 0C4082,    |