#### ISL71148SLH

Radiation Hardened 8-Channel 14-Bit 900/480ksps SAR ADC

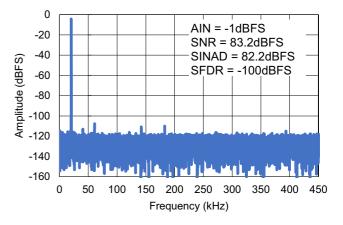

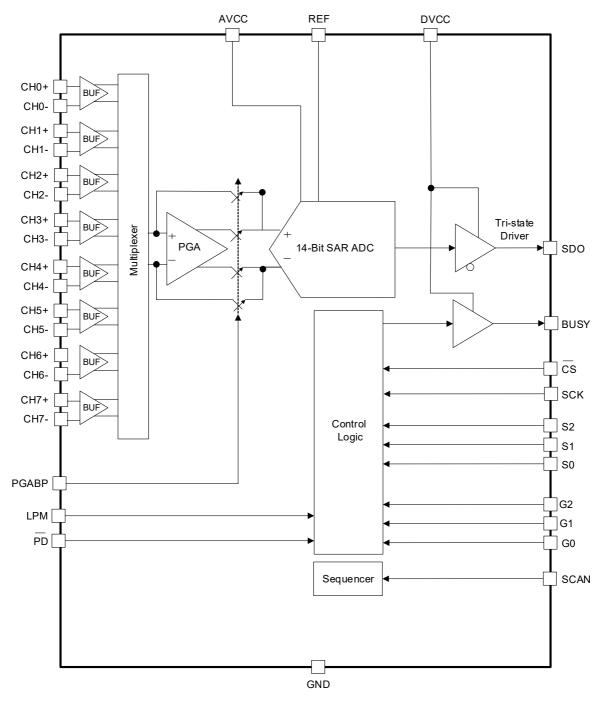

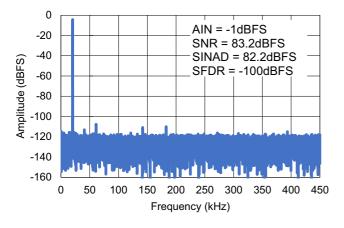

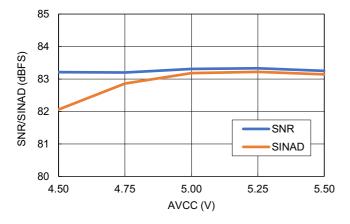

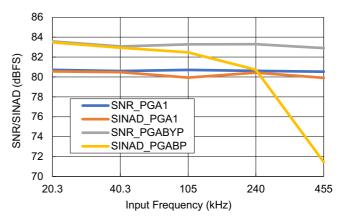

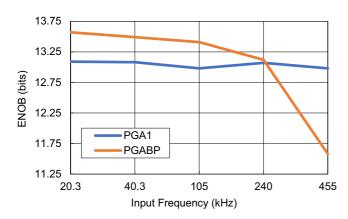

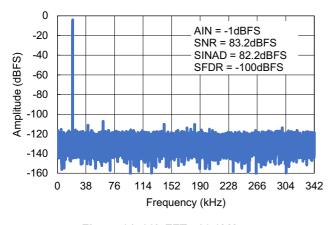

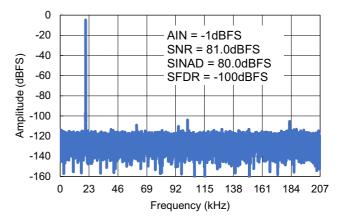

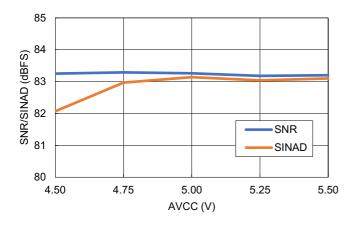

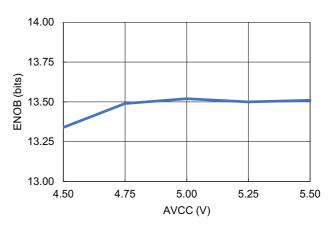

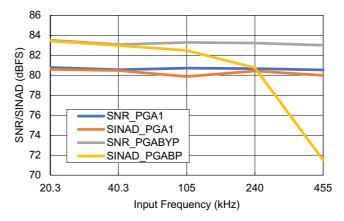

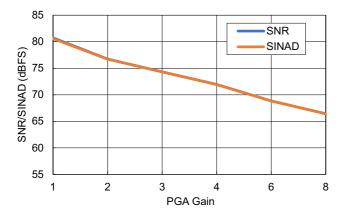

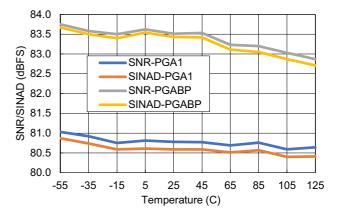

The ISL71148SLH is a radiation hardened 8-channel high precision 14-bit, 900/480ksps SAR Analog-to-Digital Converter (ADC). The ADC core is preceded by eight fully differential analog input channels, a buffered 8-to-1 multiplexer, and a PGA (Programmable Gain Amplifier). The device features a peak SNR of 83.2dBFS when operating at 900ksps. With the PGA enabled, sampling rates up to 480ksps are supported. The PGA can be bypassed to increase the sample rate to 900ksps.

The product features 900/480ksps throughput with no data latency, excellent linearity, and dynamic accuracy. The ISL71148SLH offers a high-speed SPI-compatible serial interface that supports logic ranging from 2.2V to 3.6V using a separate digital I/O supply pin.

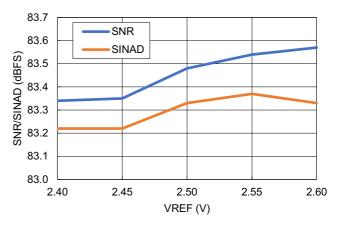

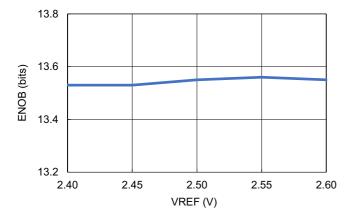

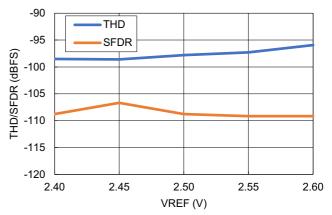

The ISL71148SLH offers a separate low-power mode (LPM) pin that reduces power dissipation at lower sample rates. An external reference with a supported input range of 2.4V to 2.6V determines the analog input signal range.

The ISL71148SLH is available in a 48-lead Thin Quad Flat-Pack (TQFP) space plastic.

#### Applications

- · Precision signal processing

- · Propulsion, payload systems

- · High-end industrial

- · Engine control

- · Down-hole drilling

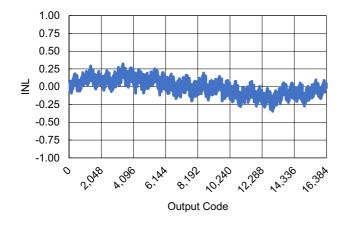

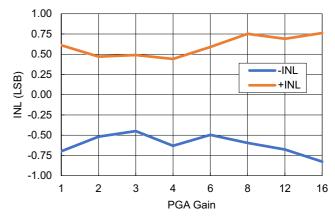

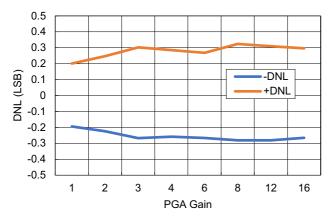

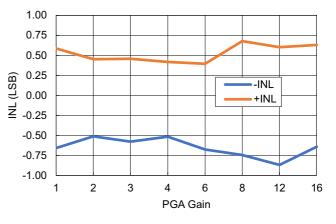

Figure 1. INL vs Output Code

#### **Features**

- Qualified to Renesas Rad Hard Plastic Production and QCI Flow (R34ZZ0006EU)

- All screening and QCI is in accordance with SAE AS6294/1 and NASA PEMS-INST-001.

- 8 Buffered Differential Analog Input Channels with Multiplexer

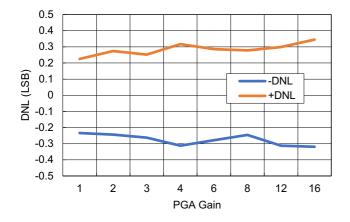

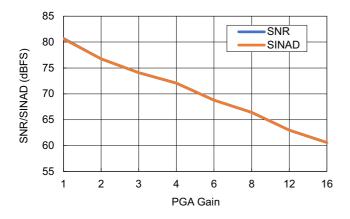

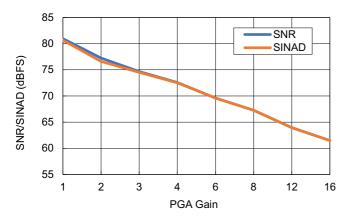

- Bypassable PGA with selectable gain (1 ≤ G ≤ 16)

- Fully Differential Bipolar Operation

- Channel Scan Sequencer

- Full throughput rate with no data latency

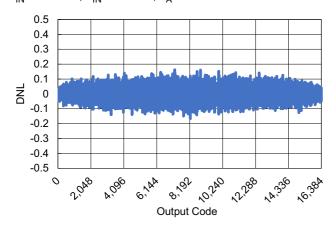

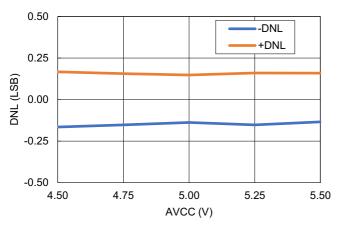

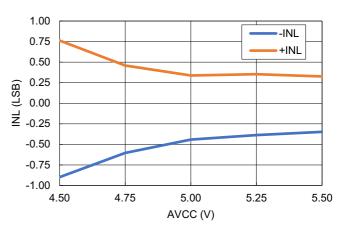

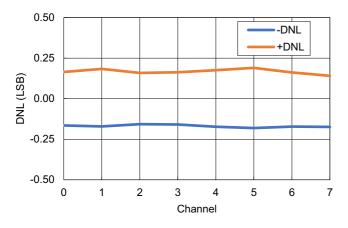

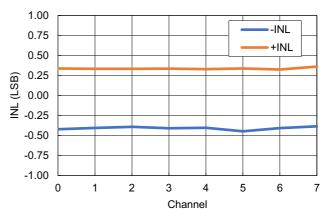

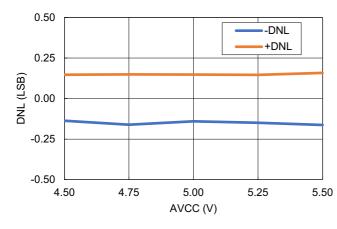

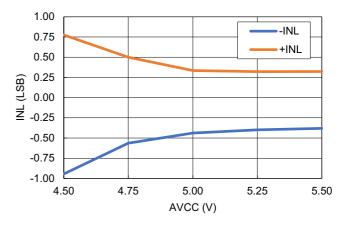

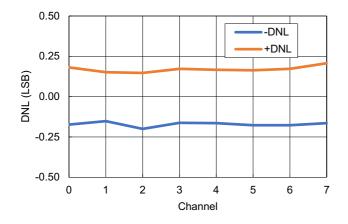

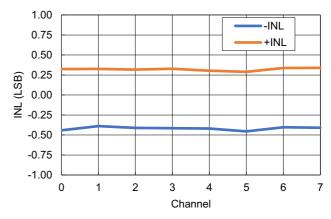

- Excellent linearity: ±0.2 LSB DNL, ±0.4 LSB INL

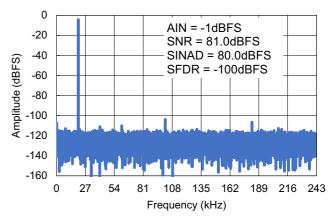

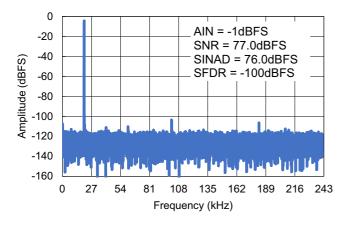

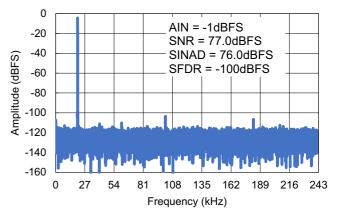

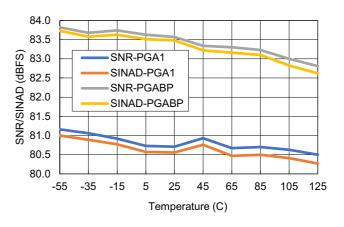

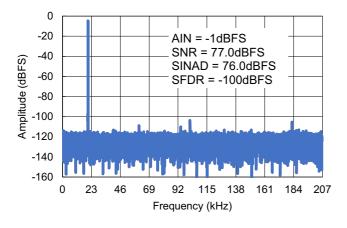

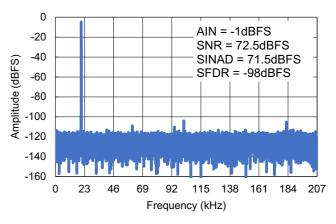

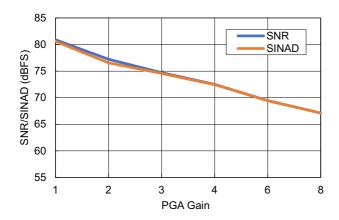

- Low noise: 83.2dBFS (PGA bypassed), 77dBFS SNR (PGA Gain = 2)

- 5V AV<sub>CC</sub> supply and 2.5V/3.3V DV<sub>CC</sub> supply

- Analog input impedance: >1GΩ, <5pF</li>

- Wide 50MHz -3dB input bandwidth

- Low power mode operation at lower sample rates

- High speed SPI-compatible serial I/O

- Full military temperature range operation

T<sub>Δ</sub> = -55°C to +125°C

- TID Rad Hard Assurance (RHA) testing

- LDR (≤10mrad(Si)/s): 75krad(Si)

- SEE Characterization

- No DSEE for AV<sub>CC</sub> = 6.2V, DV<sub>CC</sub> = 4.6V, and V<sub>RFF</sub> = 3.6V at 86MeV•cm<sup>2</sup>/mg

- SEFI <3.1µm<sup>2</sup> at 86MeV•cm<sup>2</sup>/mg

Figure 2. FFT - 20.3kHz

# **Contents**

| 1. | Overview     |                                             |    |  |  |  |  |  |

|----|--------------|---------------------------------------------|----|--|--|--|--|--|

|    | 1.1          | Typical Application Schematic               |    |  |  |  |  |  |

|    | 1.2          | Functional Block Diagram                    | 5  |  |  |  |  |  |

| 2. | Pin Ir       | nformation                                  | 6  |  |  |  |  |  |

|    | 2.1          | Pin Assignments                             | 6  |  |  |  |  |  |

|    | 2.2          | Pin Descriptions                            | 6  |  |  |  |  |  |

| 3. | Spec         | ifications                                  | 9  |  |  |  |  |  |

|    | 3.1          | Absolute Maximum Ratings                    | 9  |  |  |  |  |  |

|    | 3.2          | Recommended Operating Conditions            |    |  |  |  |  |  |

|    | 3.3          | Thermal Information                         | 9  |  |  |  |  |  |

|    | 3.4          | Electrical Specifications                   | 10 |  |  |  |  |  |

|    |              | 3.4.1 Normal Operating Mode                 | 10 |  |  |  |  |  |

|    |              | 3.4.2 Low Power Mode                        | 11 |  |  |  |  |  |

|    |              | 3.4.3 Channel Input Specifications          | 13 |  |  |  |  |  |

|    |              | 3.4.4 I/O Specifications                    | 14 |  |  |  |  |  |

|    |              | 3.4.5 Operation Burn-In Deltas              |    |  |  |  |  |  |

|    | 3.5          | Timing Specifications                       |    |  |  |  |  |  |

|    |              | 3.5.1 Normal Operating Mode                 |    |  |  |  |  |  |

|    |              | 3.5.2 Low Power Mode                        |    |  |  |  |  |  |

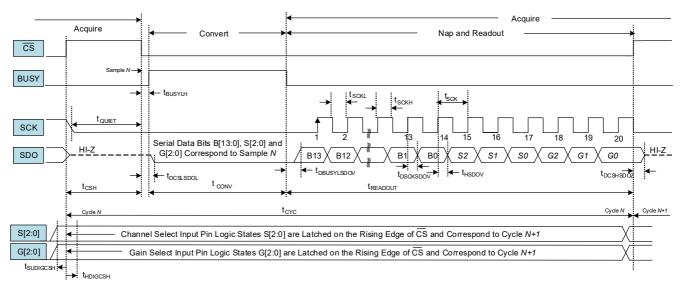

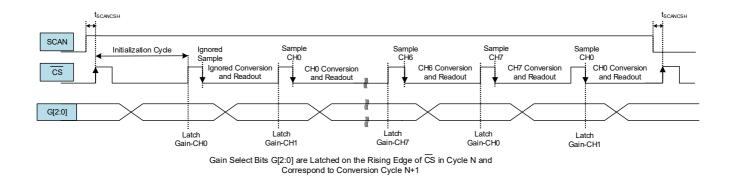

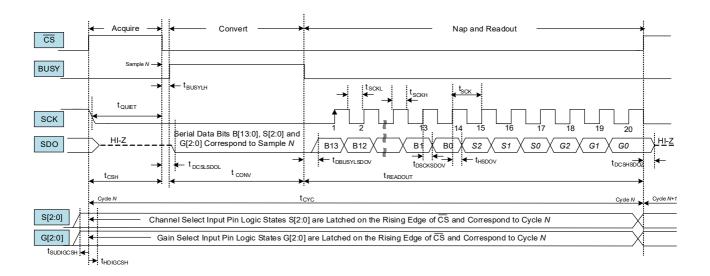

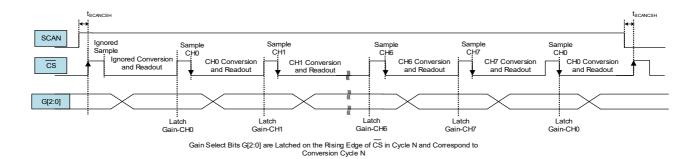

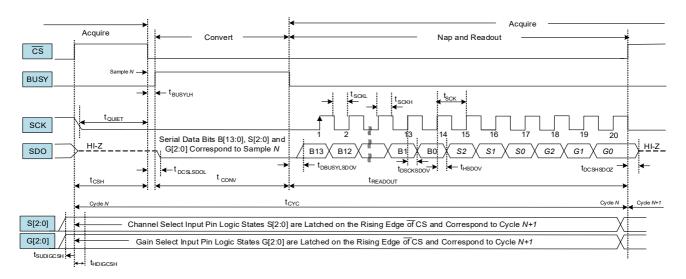

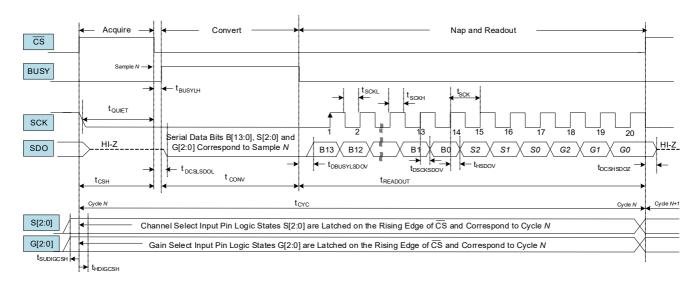

|    | 3.6          | Timing Diagrams                             | 17 |  |  |  |  |  |

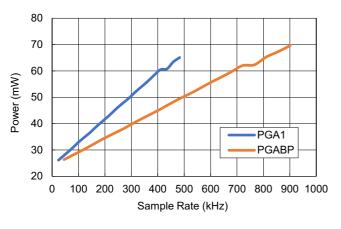

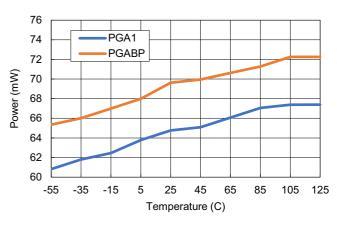

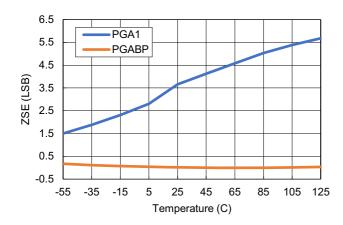

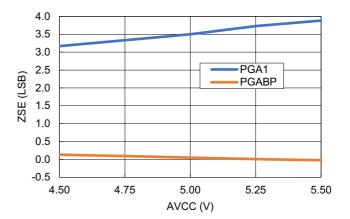

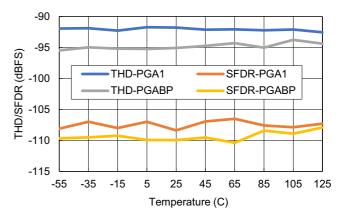

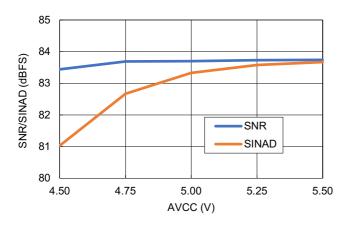

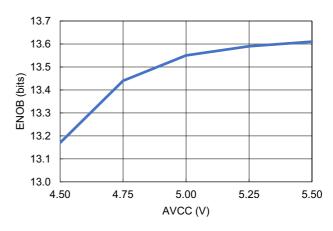

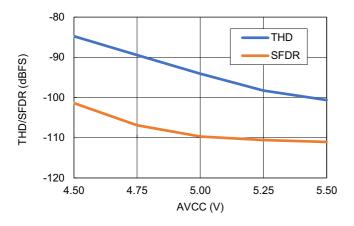

| 4. | Typic        | al Performance Curves                       | 19 |  |  |  |  |  |

|    | 4.1          | Normal Operation                            | 19 |  |  |  |  |  |

|    | 4.2          | Low Power Mode                              | 26 |  |  |  |  |  |

|    | 4.3          | Single Ended Operation - Normal Mode        | 33 |  |  |  |  |  |

|    | 4.4          | Single Ended Operation - Low Power Mode     | 35 |  |  |  |  |  |

| 5. | Appli        | cations Information                         | 37 |  |  |  |  |  |

|    | 5.1          | Overview                                    | 37 |  |  |  |  |  |

|    | 5.2          | Serial Interface and BUSY                   | 38 |  |  |  |  |  |

|    | 5.3          | Operational Phases and Timing               | 38 |  |  |  |  |  |

|    |              | 5.3.1 Normal Operation Mode Timing          | 39 |  |  |  |  |  |

|    |              | 5.3.2 Low Power Mode Timing                 | 40 |  |  |  |  |  |

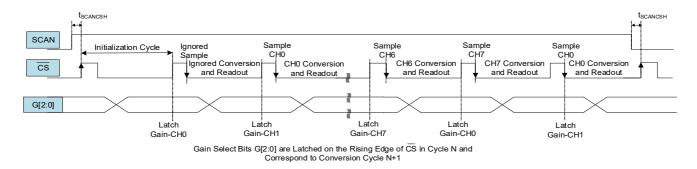

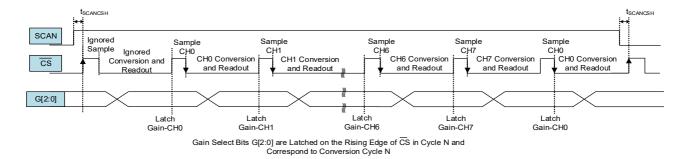

|    |              | 5.3.3 Gain and Channel Select Bits Timing   | 42 |  |  |  |  |  |

|    |              | 5.3.4 PGA Gain and Analog Input Range       | 42 |  |  |  |  |  |

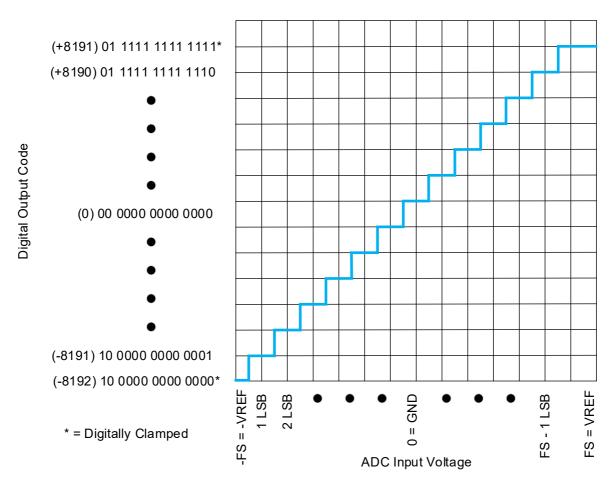

|    |              | 5.3.5 Digital Clamping and Full Scale Range | 43 |  |  |  |  |  |

|    |              | 5.3.6 Input Channel Sequencer (SCAN Mode)   |    |  |  |  |  |  |

|    | 5.4          | Convert Start (CS) Pin                      |    |  |  |  |  |  |

|    | 5.5          | Power-Down (PD) Pin                         |    |  |  |  |  |  |

|    | 5.6          | Reference Input (REF) Pin                   |    |  |  |  |  |  |

|    | 5.7          | PGA Bypass (PGABP) Pin                      |    |  |  |  |  |  |

|    | 5.8          | ±(CH0 - CH7) Input Pins                     |    |  |  |  |  |  |

|    | 5.9          | Low Power Mode (LPM) Pin                    |    |  |  |  |  |  |

|    | 5.10         | SCAN Pin                                    |    |  |  |  |  |  |

|    | 5.11         | Channel Selection (S2, S1, and S0) Pins     |    |  |  |  |  |  |

|    | 5.12         | Gain Selection (G2, G1, and G0) Pins        |    |  |  |  |  |  |

|    | 5.13         | Transfer Function                           |    |  |  |  |  |  |

|    | 5 1 <i>1</i> | Power Supply Sequencing                     | 48 |  |  |  |  |  |

#### ISL71148SLH Datasheet

|    | - 4F                 | 0-1-1-0   | avina On austina                       | 40   |  |  |  |

|----|----------------------|-----------|----------------------------------------|------|--|--|--|

|    |                      |           | aring Operation                        |      |  |  |  |

|    | 5.16                 | Configu   | ration Examples                        | . 49 |  |  |  |

|    |                      | 5.16.1    | Normal Mode, PGA Gain                  | . 49 |  |  |  |

|    |                      | 5.16.2    | Normal Mode, PGA Bypassed              | . 50 |  |  |  |

|    |                      | 5.16.3    | Low Power Mode, PGA Enabled            | . 50 |  |  |  |

|    |                      | 5.16.4    | Low Power Mode, PGA Bypassed           | . 50 |  |  |  |

|    |                      | 5.16.5    | Single-Ended Operation                 | . 50 |  |  |  |

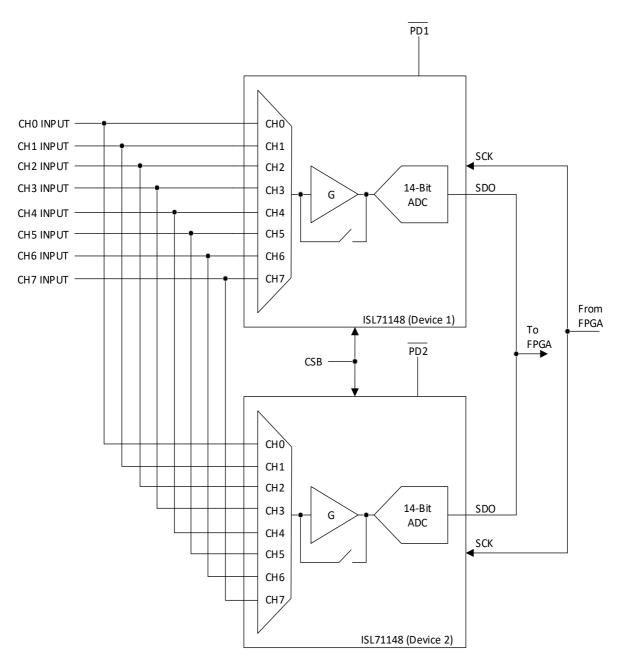

|    |                      | 5.16.6    | Dual Footprint ISL73148SEH/ISL71148SLH | . 51 |  |  |  |

| 6. | Die a                | nd Asse   | mbly Characteristics                   | . 52 |  |  |  |

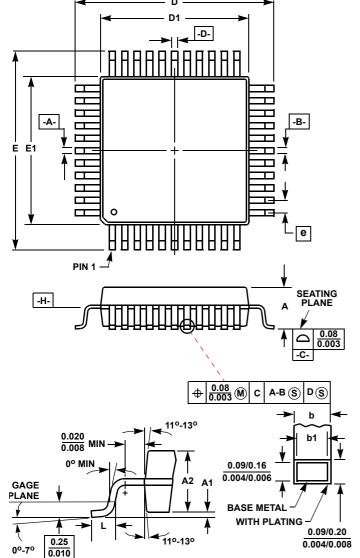

| 7. | Pack                 | age Outl  | ine Drawing                            | . 53 |  |  |  |

| 8. | Ordering Information |           |                                        |      |  |  |  |

| 9. | Revis                | sion Hist | orv                                    | . 54 |  |  |  |

## 1. Overview

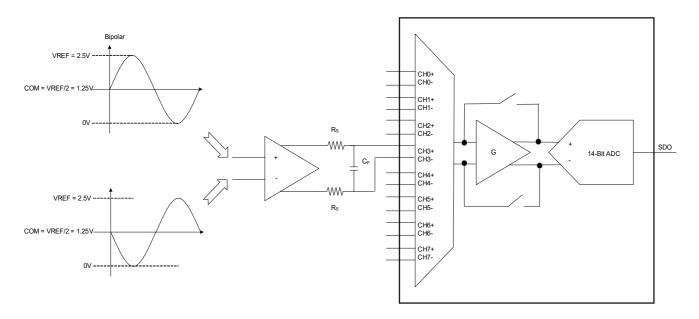

# 1.1 Typical Application Schematic

Figure 3. Typical Application Example Circuit

# 1.2 Functional Block Diagram

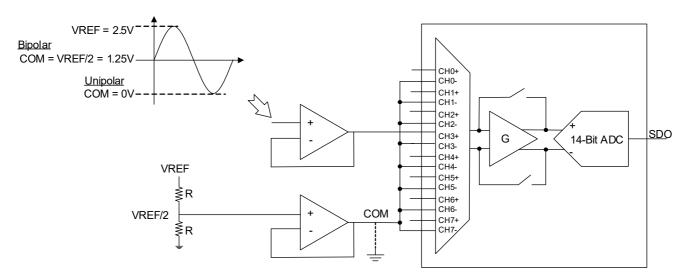

Figure 4. Block Diagram

## 2. Pin Information

# 2.1 Pin Assignments

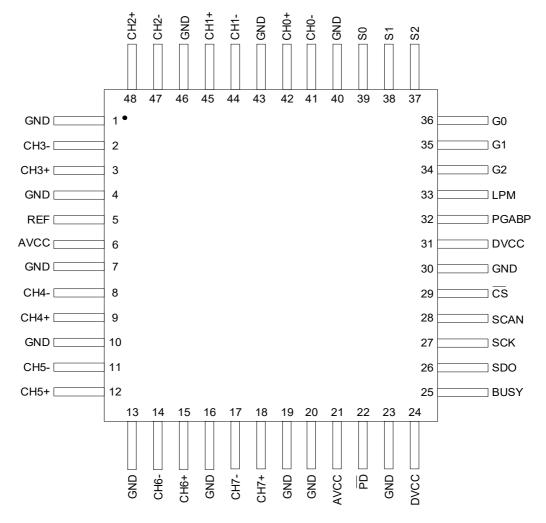

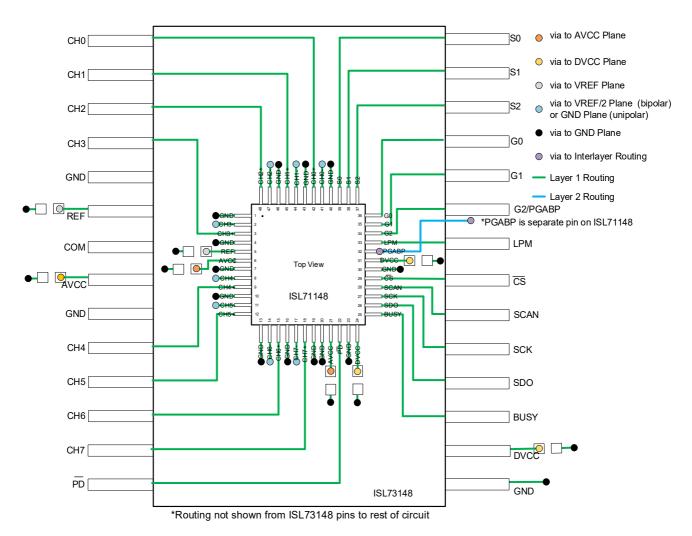

Figure 5. Pin Assignments - Top View

# 2.2 Pin Descriptions

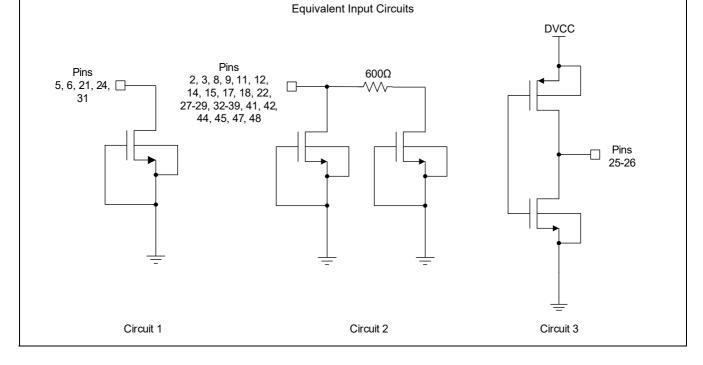

| Pin Number                                               | Pin Name | ESD<br>Circuit | Description                                                                                                                                                                                                                        |

|----------------------------------------------------------|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 7, 10,<br>13, 16, 19,<br>20, 23, 30,<br>40, 43, 46 | GND      | -              | Analog and digital supply ground. Tie directly to the PCB ground plane (GND).                                                                                                                                                      |

| 6,21 AVCC                                                |          | 1              | Analog supply. The supply range is 4.5V to 5.5V. Bypass this pin to GND with a $10\mu F$ ceramic capacitor.                                                                                                                        |

| 5                                                        | REF      | 1              | Reference Input. The input range of REF is 2.4V to 2.6V. The voltage at the REF pin ( $V_{REF}$ ) defines the input range of each Analog Input Channel as 0V to $V_{REF}$ . Bypass REF to GND with a 10 $\mu$ F ceramic capacitor. |

| Pin Number | Pin Name      | ESD<br>Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2          | CH3-          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3          | CH3+          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8          | CH4-          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9          | CH4+          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11         | CH5-          | 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12         | CH5+          | 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14         | CH6-          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15         | CH6+          | 1              | Analog Input Channel Pairs. CH0± to CH7± are eight fully differential input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17         | CH7-          | 2              | channel pairs. Each Analog Input Channel pin can be driven within the voltage range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18         |               |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 41         | CH0-          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 42         | CH0+          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 44         | CH1-          | 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 45         | CH1+          | _              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 47         | CH2-          | _              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 48         | CH2+          | _              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22         | ₽D            | 2              | Power-Down Low Input. When this input is logic low, the chip is powered down. If this occurs during a conversion, the conversion is halted, and the SDO pin is placed in Hi-Z. DV <sub>CC</sub> determines logic levels. This pin has an internal 500kOhm pull-up resistor to DVCC.                                                                                                                                                                                                                                                                                                                                                                                            |

| 24, 31     | DVCC          | 1              | Digital I/O supply. The voltage range on this pin is 2.2V to 3.6V. DV $_{CC}$ is nominally set to the same supply voltage as the host interface (2.5V or 3.3V). Bypass DVCC to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 25         | BUSY          | 3              | Busy output. A logic high indicates a conversion is in progress. The BUSY indicator returns low following the completion of a conversion. DV <sub>CC</sub> determines logic levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26         | SDO           | 3              | Serial data output. The current conversion result is serially shifted on this pin on the rising edges of SCK, from MSB first to LSB last. The data stream comprises 14 bits of conversion data followed by the channel select and gain select bits corresponding to the conversion result. DV <sub>CC</sub> determines logic levels.                                                                                                                                                                                                                                                                                                                                           |

| 27         | SCK           | 2              | Serial data clock input. When $\overline{\text{CS}}$ is low, and the BUSY indicator is low, the conversion result is shifted out on SDO on the rising edges of SCK, with the Most Significant Bit (MSB) first to the Least Significant Bit (LSB) last. D <sub>VCC</sub> determines logic levels. SCK should be held low when it is not being asserted.                                                                                                                                                                                                                                                                                                                         |

| 28         | SCAN          | 2              | Channel scan input. When this input is logic-high, the internal sequencer controls the channel selected. CH0 is the first channel selected following the rising edge of SCAN. Each subsequent channel is selected on each new rising edge of $\overline{\text{CS}}$ . DV <sub>CC</sub> determines logic levels.                                                                                                                                                                                                                                                                                                                                                                |

| 29         | <del>CS</del> | 2              | Convert Start Low input. A falling edge on this input completes the sampling process and starts a new conversion. The conversion is timed using an internal oscillator. The device automatically powers down following the conversion process. The logic state of the $\overline{CS}$ pin controls the state of the SDO pin. A logic high on the $\overline{CS}$ pin disables the SDO pin driver, and the SDO pin impedance is Hi-Z. A logic low on the $\overline{CS}$ pin enables the SDO driver (unless $\overline{PD}$ is low) and allows data to be read out following a conversion. Hold this pin low at power-up and when in power-down or when the device is inactive. |

| Pin Number | Pin Name                                                                                                                            | ESD<br>Circuit | Description                                                                                                                                                                                                                                                                                                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32         | PGABP                                                                                                                               | 2              | PGA bypass mode input. When this input is logic high, the PGA is bypassed, and the input buffer/multiplexer directly drives the ADC. The maximum throughput rate is increased to 900ksps. DV <sub>CC</sub> determines logic levels.                                                                                                                                     |

| 33         | controlled by the CS pin logic state held high. The ADC is automated a down between conversions to reduce power consumption for low |                | Low power mode input. When this input is logic high, the acquisition time is directly controlled by the $\overline{\text{CS}}$ pin logic state held high. The ADC is automatically powered down between conversions to reduce power consumption for lower sample rates. This pin is a device configuration pin and should not be switched dynamically during operation. |

| 34         | G2                                                                                                                                  |                | Logic Inputs. These three pins program the gain of the PGA. The G2, G1, and G0                                                                                                                                                                                                                                                                                          |

| 35         | G1                                                                                                                                  | 2              | logic inputs are latched internally on the rising edge of CS. DV <sub>CC</sub> determines logic                                                                                                                                                                                                                                                                         |

| 36         | G0                                                                                                                                  |                | levels.                                                                                                                                                                                                                                                                                                                                                                 |

| 37         | S2                                                                                                                                  |                | Channel selection logic inputs. These three pins select the input channel passed                                                                                                                                                                                                                                                                                        |

| 38         | S1                                                                                                                                  | 2              | through the input multiplexer to the PGA (or ADC if the PGA is bypassed). The S2, S1, and S0 logic inputs are latched internally on the rising edge of $\overline{\text{CS}}$ . DV <sub>CC</sub>                                                                                                                                                                        |

| 39         | S0                                                                                                                                  |                | determines logic levels.                                                                                                                                                                                                                                                                                                                                                |

# 3. Specifications

## 3.1 Absolute Maximum Ratings

**Caution**: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                                                     | Min  | Max                      | Unit |

|-------------------------------------------------------------------------------|------|--------------------------|------|

| Supply Voltage (AVCC to GND)                                                  | -0.3 | 6.5                      | V    |

| Supply Voltage (AVCC to GND) <sup>[1]</sup>                                   | -0.3 | 6.2                      | V    |

| Supply Voltage (DVCC to GND)                                                  | -0.3 | 4.6                      | V    |

| Supply Voltage (DVCC to GND) <sup>[1]</sup>                                   | -0.3 | 4.6                      | V    |

| Reference Input Voltage (REF to GND)                                          | -0.3 | 3.6                      | V    |

| Reference Input Voltage (REF to GND) <sup>[1]</sup>                           | -0.3 | 3.6                      | V    |

| (CH0:7+, CH0:7- to GND) Voltage                                               | -0.3 | (V <sub>REF</sub> + 0.3) | V    |

| Digital Input Voltage (PD, CS, SCK, S2, S1, S0, G2, G1, G0, SCAN, LPM, PGABP) | -0.3 | (DV <sub>CC</sub> + 0.3) | V    |

| Maximum Junction Temperature                                                  | -    | +150                     | °C   |

| Storage Temperature Range                                                     | -65  | +150                     | °C   |

| Human Body Model (Tested per MIL-STD-883 TM3015.7)                            | -    | 2.5                      | kV   |

| Charged Device Model (Tested per JS-002-2022)                                 | -    | 750                      | V    |

<sup>1.</sup> Tested in a heavy ion (Au) environment at LET = 86Mev•cm<sup>2</sup>/mg at 125°C.

# 3.2 Recommended Operating Conditions

| Parameter                                          | Min | Max              | Unit |

|----------------------------------------------------|-----|------------------|------|

| Temperature                                        | -55 | +125             | °C   |

| Analog Supply Voltage, A <sub>VCC</sub>            | 4.5 | 5.5              | V    |

| Digital Supply Voltage, D <sub>VCC</sub>           | 2.2 | 3.6              | V    |

| Reference Input Voltage, V <sub>REF</sub>          | 2.4 | 2.6              | V    |

| Analog Input Differential Voltage, A <sub>IN</sub> | 0   | V <sub>REF</sub> | V    |

#### 3.3 Thermal Information

| Parameter          | Package    | Symbol                         | Conditions          | Typical<br>Value | Unit |

|--------------------|------------|--------------------------------|---------------------|------------------|------|

| Thermal Resistance | 48 LD TQFP | θ <sub>JA</sub> [1]            | Junction to ambient | 48               | °C/W |

| Thermal Nesistance | 40 LD TQTF | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case    | 11               | °C/W |

<sup>1.</sup>  $\theta_{JA}$  is measured in free air with the component on high-effective thermal conductivity test board. See TB379.

<sup>2.</sup> For  $\theta_{\text{JC}},$  the case temperature location is the center of package top.

## 3.4 Electrical Specifications

## 3.4.1 Normal Operating Mode

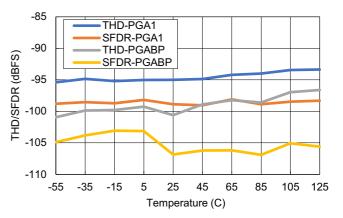

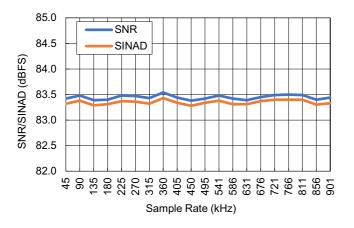

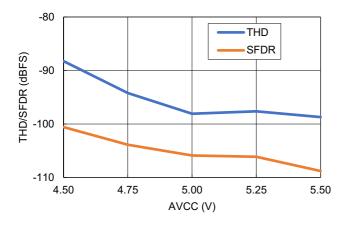

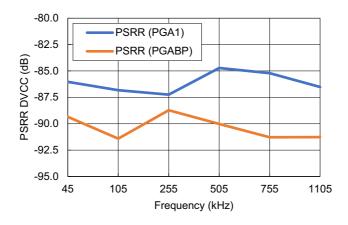

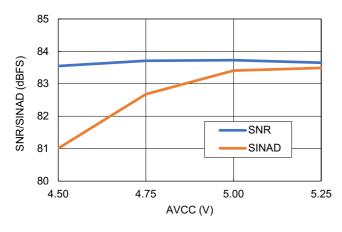

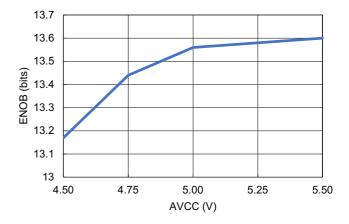

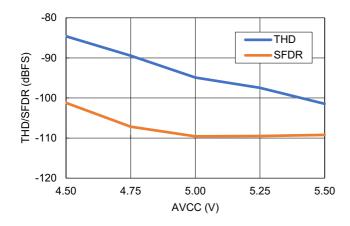

$AV_{CC}$  = 5.0V;  $DV_{CC}$  = 2.5V, REF = 2.5V, GND = 0V, PGA Bypassed, LPM = 0V,  $f_{SAMP}$  = 900.901ksps,  $F_{IN}$  = 20.3kHz,  $A_{IN}$  = -1dBFS;  $T_A$  = 25°C, unless otherwise noted. **Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.**

| Parameter                                 | Symbol | Test Conditions                                                             | Min  | Typ <sup>[1]</sup> | Max | Unit               |

|-------------------------------------------|--------|-----------------------------------------------------------------------------|------|--------------------|-----|--------------------|

| Converter Characteristics                 | l .    |                                                                             |      | l .                | I   |                    |

| Resolution                                | -      | -                                                                           | 14   | -                  | -   | bits               |

| No Missing Codes                          | -      | -                                                                           | 14   | -                  | -   | bits               |

| Transition Noise                          | -      | RMS noise, 14-bit LSB                                                       | -    | 0.29               | -   | LSB <sub>RMS</sub> |

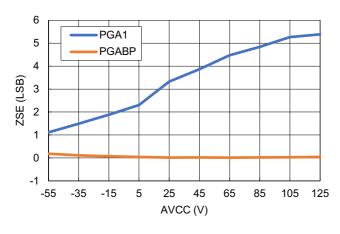

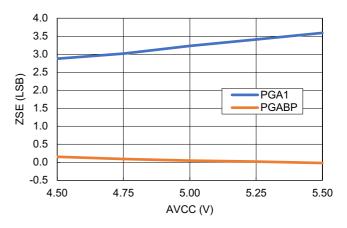

| Zero-Scale Error                          | ZSE    | Measured with input set to V <sub>REF</sub> /2.                             | -4   | ±0.1               | 4   | LSB                |

| Zero-Scale Error Drift                    | ZSED   | Measured with input set to V <sub>REF</sub> /2.                             | -    | ±0.001             | -   | LSB/°C             |

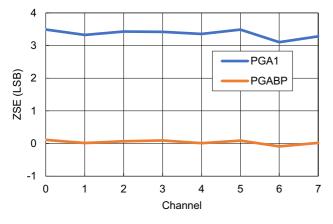

| Zero-Scale Error Match                    | ZSEM   | Measured with input set to V <sub>REF</sub> /2.                             | -4   | ±0.5               | 4   | LSB                |

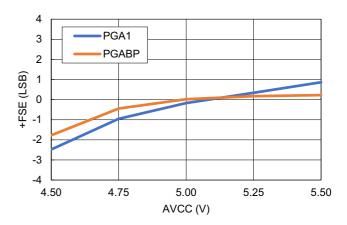

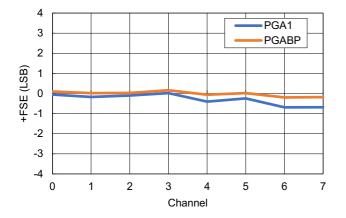

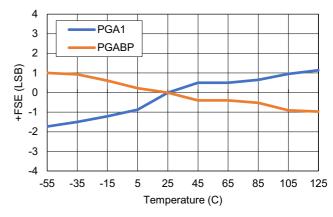

| Positive Full-Scale Error                 | +FSE   | Measured with input connected to V <sub>REF</sub>                           | -7   | ±0.1               | 7   | LSB                |

| Positive Full-Scale Error Drift           | +FSED  | Measured with input connected to V <sub>REF</sub>                           | -    | ±0.003             | -   | LSB/°C             |

| Positive Full-Scale Error Match           | +FSEM  | Measured with input connected to V <sub>REF</sub>                           | -4   | ±1                 | 4   | LSB                |

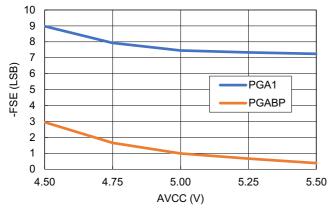

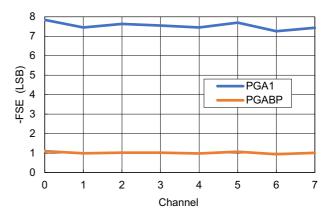

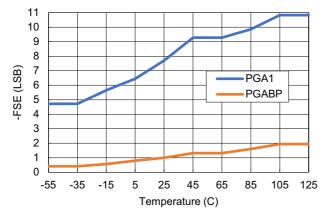

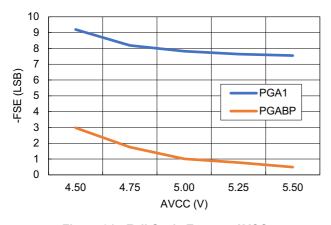

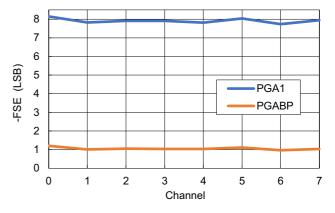

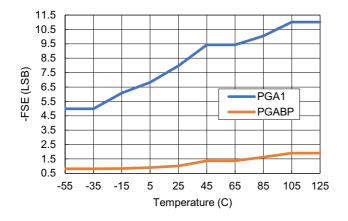

| Negative Full-Scale Error                 | -FSE   | Measured with input connected to GND                                        | -7   | ±1                 | 7   | LSB                |

| Negative Full-Scale Error Drift           | -FSED  | Measured with input connected to GND                                        | -    | ±0.014             | -   | LSB/°C             |

| Negative Full-Scale Error<br>Match        | -FSEM  | Measured with input connected to GND                                        | -4   | ±1                 | 4   | LSB                |

| Integral Non-Linearity <sup>[2]</sup>     | INL    | Measured with full-scale input signal.                                      | -1   | ±0.4               | 1   | LSB                |

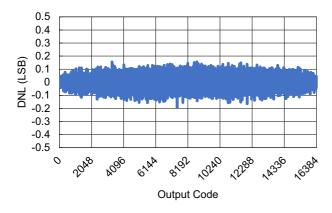

| Differential Non-Linearity <sup>[2]</sup> | DNL    | Measured with full-scale input signal.                                      | -0.5 | ±0.2               | 0.5 | LSB                |

| Dynamic Accuracy                          |        |                                                                             |      | ľ                  | l   |                    |

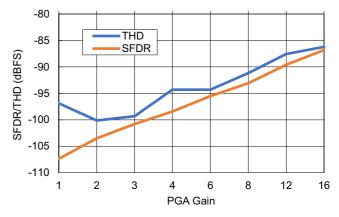

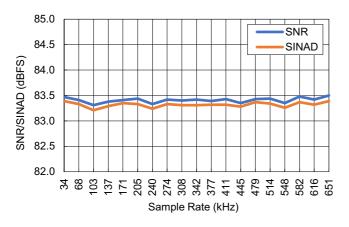

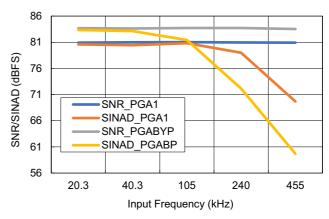

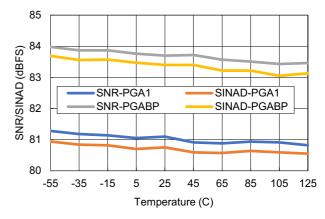

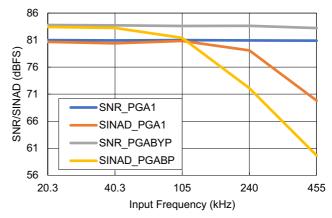

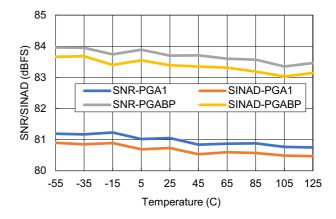

|                                           | SNR    | PGA Bypassed                                                                | 82   | 83.2               | -   |                    |

| Signal-to-Noise Ratio                     |        | PGA Gain = 2, f <sub>SAMP</sub> = 483.092ksps                               | 76   | 77                 | -   | dBFS               |

|                                           |        | PGA Gain = 16, f <sub>SAMP</sub> = 483.092ksps,<br>A <sub>IN</sub> = -3dBFS | 59.5 | 62                 | -   |                    |

|                                           |        | PGA Bypassed                                                                | 81   | 82.2               | -   |                    |

| Signal-to-Noise + Distortion              | SINAD  | PGA Gain = 2, f <sub>SAMP</sub> = 483.092ksps                               | 75   | 76                 | -   | dBFS               |

| Ratio                                     |        | PGA Gain = 16, f <sub>SAMP</sub> = 483.092ksps,<br>A <sub>IN</sub> = -3dBFS | 58.5 | 61                 | -   |                    |

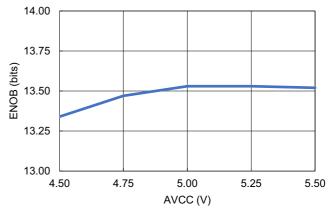

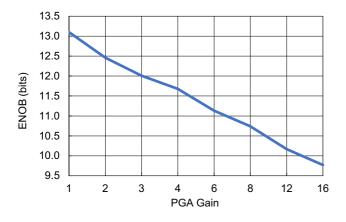

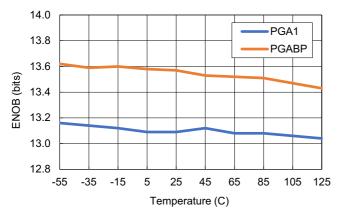

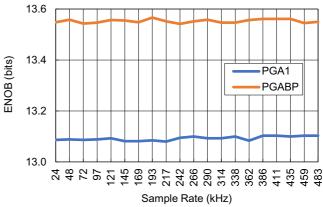

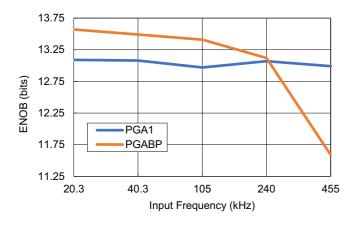

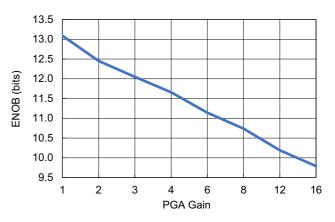

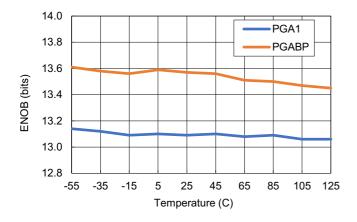

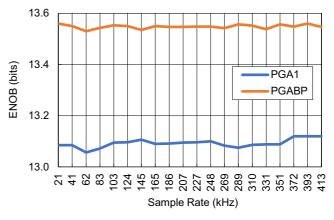

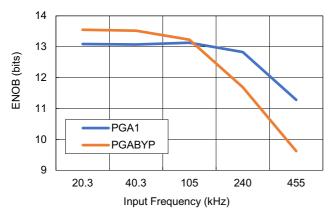

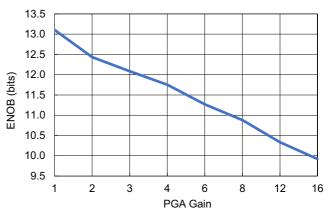

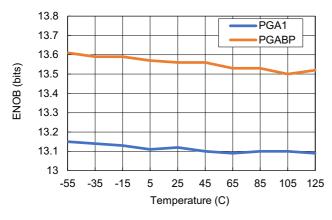

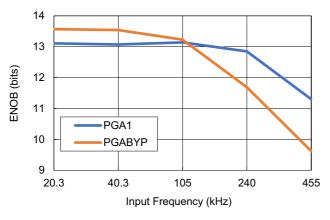

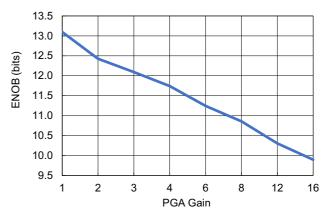

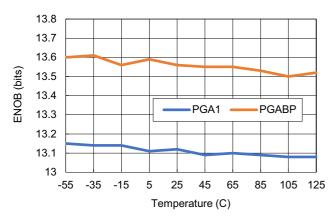

|                                           |        | PGA Bypassed                                                                | 13.1 | 13.5               | -   |                    |

| Effective Number of Bits                  | ENOB   | PGA Gain = 2, f <sub>SAMP</sub> = 483.092ksps                               | 12.1 | 12.5               | -   | bits               |

| Zilosare Hambsi et Bile                   | LIVOD  | PGA Gain = 16, f <sub>SAMP</sub> = 483.092ksps,<br>A <sub>IN</sub> = -3dBFS | 9.4  | 9.8                | -   | טונס               |

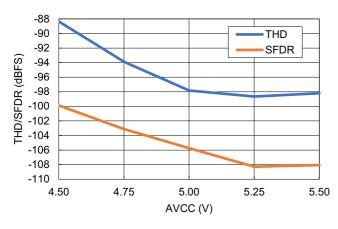

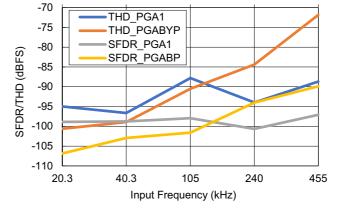

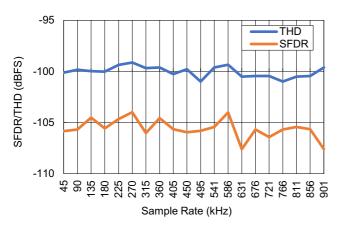

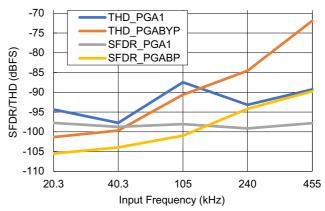

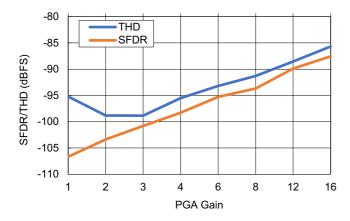

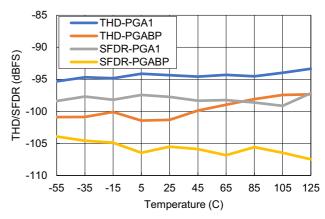

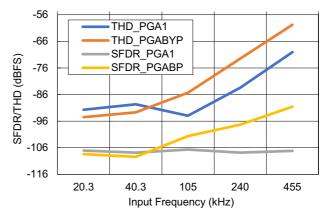

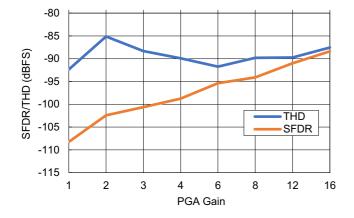

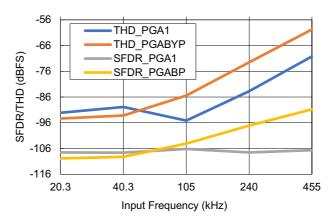

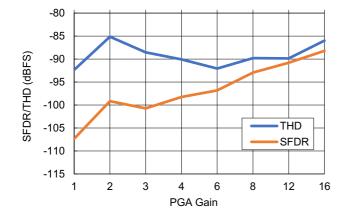

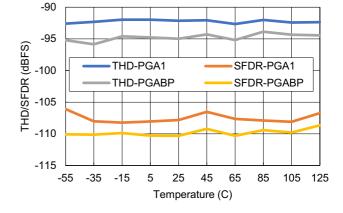

|                                           |        | PGA Bypassed                                                                | 85   | 95                 | -   |                    |

| Total Harmonic Distortion                 | THD    | PGA Gain = 2, f <sub>SAMP</sub> = 483.092ksps                               | 85   | 95                 | -   | dBFS               |

| 3.5.5.                                    | ואט    | PGA Gain = 16, f <sub>SAMP</sub> = 483.092ksps,<br>A <sub>IN</sub> = -3dBFS | 80   | 85                 | -   |                    |

$AV_{CC} = 5.0V$ ;  $DV_{CC} = 2.5V$ , REF = 2.5V, GND = 0V, PGA Bypassed, LPM = 0V,  $f_{SAMP} = 900.901$ ksps,  $F_{IN} = 20.3$ kHz,  $A_{IN} = -1$ dBFS;  $T_A = 25^{\circ}$ C, unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.

| Parameter                            | Symbol               | Test Conditions                                                             | Min | Typ <sup>[1]</sup> | Max  | Unit              |  |

|--------------------------------------|----------------------|-----------------------------------------------------------------------------|-----|--------------------|------|-------------------|--|

|                                      |                      | PGA Bypassed                                                                | 90  | 100                | -    |                   |  |

| Spurious Free Dynamic Range          | SFDR                 | PGA Gain = 2, f <sub>SAMP</sub> = 483.092ksps                               | 90  | 100                | -    | dBFS              |  |

|                                      |                      | PGA Gain = 16, f <sub>SAMP</sub> = 483.092ksps,<br>A <sub>IN</sub> = -3dBFS | -   | 90                 | -    |                   |  |

| Channel-to-Channel Isolation         | -                    | Full-scale signal applied to one channel, other channels connected to GND   | -   | -100               | -    | dB                |  |

| Input Bandwidth                      | -                    | Source impedance = 50Ω, -3dB point                                          | -   | 50                 | -    | MHz               |  |

| Aperture Delay                       | t <sub>AD</sub>      | CS falling edge to sample edge                                              | -   | 2.5                | -    | ns                |  |

| Aperture Jitter                      | t <sub>AJITTER</sub> | -                                                                           | -   | 500                | -    | fs <sub>RMS</sub> |  |

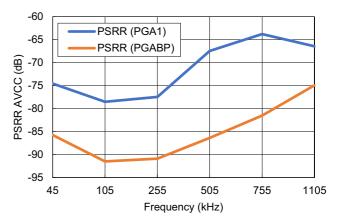

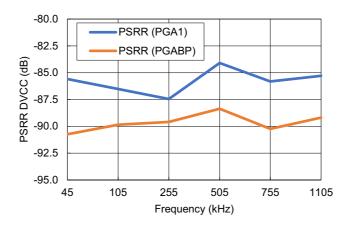

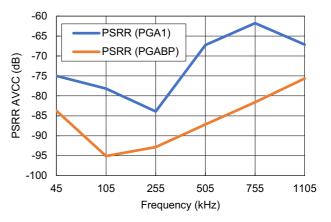

| Power Supply Characteristics         | (AVCC, DV            | CC)                                                                         |     |                    |      |                   |  |

| Analog Supply Voltage                | AV <sub>CC</sub>     | -                                                                           | 4.5 | -                  | 5.5  | V                 |  |

| Analog Cupply Current Active         |                      | Active, PGA enabled, f <sub>SAMP</sub> = 483.092ksps                        | -   | 17.6               | 20.5 | mA                |  |

| Analog Supply Current - Active       | I <sub>AVCC</sub>    | Active, PGA bypassed, f <sub>SAMP</sub> = 900.901ksps                       | -   | 20                 | 23   | mA                |  |

| Analas Cumulu Cumunt Statio          | I <sub>Static</sub>  | PGA enabled. CS held Low                                                    | -   | 10.5               | 13   | mA                |  |

| Analog Supply Current - Static       |                      | PGA bypassed. CS held Low                                                   | -   | 6                  | 9    | mA                |  |

| Analog Supply Current - Sleep        | I <sub>SLAVCC</sub>  | PD held Low                                                                 | -   | 20                 | -    | μA                |  |

| Digital Supply Voltage               | DV <sub>CC</sub>     | -                                                                           | 2.2 | -                  | 3.6  | V                 |  |

| Digital Complex Company Active       |                      | PGA enabled. f <sub>SCK</sub> = 50MHz                                       | -   | 346                | 600  | μA                |  |

| Digital Supply Current - Active      | I <sub>DVCC</sub>    | PGA bypassed. f <sub>SCK</sub> = 50MHz                                      | -   | 512                | 700  | μA                |  |

| District Committee Committee Charles |                      | PGA enabled. CS held Low.                                                   | -   | 100                | 120  | μA                |  |

| Digital Supply Current - Static      | I <sub>STDVCC</sub>  | PGA bypassed. CS held Low.                                                  | -   | 70                 | 90   | μA                |  |

| Digital Supply Current - Sleep       | I <sub>SLDVCC</sub>  | PD held Low                                                                 | -   | 6                  | -    | μA                |  |

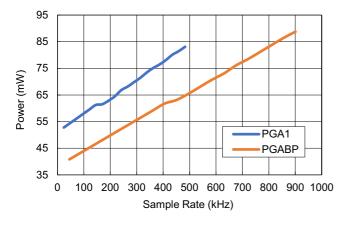

|                                      | P <sub>ACTIVE</sub>  | PGA enabled, f <sub>SAMP</sub> = 483.092ksps                                | -   | 89                 | 104  | mW                |  |

|                                      | P <sub>ACTIVE</sub>  | PGA bypassed, f <sub>SAMP</sub> = 900.091ksps                               | -   | 101                | 117  | mW                |  |

| P <sub>D</sub>                       | P <sub>STATIC</sub>  | PGA enabled, CS held Low                                                    | -   | 53                 | 70   | mW                |  |

|                                      | P <sub>STATIC</sub>  | PGA bypassed, CS held Low.                                                  | -   | 30                 | 50   | mW                |  |

|                                      | P <sub>SLEEP</sub>   | PD held Low                                                                 | -   | 115                | -    | μW                |  |

<sup>1.</sup> Typical values are not guaranteed.

#### 3.4.2 Low Power Mode

$AV_{CC} = 5.0V$ ;  $DV_{CC} = 2.5V$ , REF = 2.5V, GND = 0V, PGA Bypassed, LPM = 2.5V,  $f_{SAMP} = 684.932$ ksps,  $F_{IN} = 20.3$ kHz,  $A_{IN} = -1$ dBFS;  $T_A = 25$ °C, unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.

| Parameter                 | Symbol | Test Conditions | Min | Typ <sup>[1]</sup> | Max | Unit |  |  |

|---------------------------|--------|-----------------|-----|--------------------|-----|------|--|--|

| Converter Characteristics |        |                 |     |                    |     |      |  |  |

| Resolution                | -      | -               | 14  | -                  | -   | bits |  |  |

| No Missing Codes          | -      | -               | 14  | -                  | -   | bits |  |  |

<sup>2.</sup> Characterized on all channels, production tested on Channel 0 only.

$AV_{CC}$  = 5.0V;  $DV_{CC}$  = 2.5V, REF = 2.5V, GND = 0V, PGA Bypassed, LPM = 2.5V,  $f_{SAMP}$  = 684.932ksps,  $F_{IN}$  = 20.3kHz,  $A_{IN}$  = -1dBFS;  $T_A$  = 25°C, unless otherwise noted. **Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.**

| Parameter                                 | Symbol               | Test Conditions                                                             | Min  | Typ <sup>[1]</sup> | Max | Unit               |

|-------------------------------------------|----------------------|-----------------------------------------------------------------------------|------|--------------------|-----|--------------------|

| Transition Noise                          | -                    | RMS noise, 14-bit LSB                                                       | -    | 0.29               | -   | LSB <sub>RMS</sub> |

| Zero-Scale Error                          | ZSE                  | Measured with input set to V <sub>REF</sub> /2.                             | -4   | ±0.1               | 4   | LSB                |

| Zero-Scale Error Drift                    | ZSED                 | Measured with input set to V <sub>REF</sub> /2.                             | -    | ±0.001             | -   | LSB/°C             |

| Zero-Scale Error Match                    | ZSEM                 | Measured with input set to V <sub>REF</sub> /2.                             | -4   | ±0.5               | 4   | LSB                |

| Positive Full-Scale Error                 | +FSE                 | Measured with input connected to V <sub>REF</sub>                           | -7   | ±0.1               | 7   | LSB                |

| Positive Full-Scale Error Drift           | +FSED                | Measured with input connected to V <sub>REF</sub>                           | -    | ±0.003             | -   | LSB/°C             |

| Positive Full-Scale Error Match           | +FSEM                | Measured with input connected to V <sub>REF</sub>                           | -4   | ±1                 | 4   | LSB                |

| Negative Full-Scale Error                 | -FSE                 | Measured with input connected to GND                                        | -7   | ±1                 | 7   | LSB                |

| Negative Full-Scale Error Drift           | -FSED                | Measured with input connected to GND                                        | -    | ±0.014             | -   | LSB/°C             |

| Negative Full-Scale Error Match           | -FSEM                | Measured with input connected to GND                                        | -4   | ±1                 | 4   | LSB                |

| Integral Non-Linearity <sup>[2]</sup>     | INL                  | Measured with full scale input signal.                                      | -1   | ±0.4               | 1   | LSB                |

| Differential Non-Linearity <sup>[2]</sup> | DNL                  | Measured with full scale input signal.                                      | -0.5 | ±0.2               | 0.5 | LSB                |

| Dynamic Accuracy                          | 1                    |                                                                             |      | l.                 |     |                    |

|                                           |                      | PGA Bypassed                                                                | 82   | 83.2               | -   |                    |

| Signal-to-Noise Ratio                     | SNR                  | PGA Gain = 2, f <sub>SAMP</sub> = 413.223ksps                               | 76   | 77                 | -   | dBFS               |

| - G                                       |                      | PGA Gain = 16, f <sub>SAMP</sub> = 413.223ksps,<br>A <sub>IN</sub> = -3dBFS | 59.5 | 62                 | -   |                    |

|                                           | SINAD                | PGA Bypassed                                                                | 81   | 82.2               | -   |                    |

| Signal-to-Noise + Distortion Ratio        |                      | PGA Gain = 2, f <sub>SAMP</sub> = 413.223ksps                               | 75   | 76                 | -   | dBFS               |

|                                           |                      | PGA Gain = 16, f <sub>SAMP</sub> = 413.223ksps,<br>A <sub>IN</sub> = -3dBFS | 58.5 | 61                 | -   |                    |

|                                           |                      | PGA Bypassed                                                                | 13.1 | 13.5               | -   |                    |

| Effective Number of Bits                  | ENOB                 | PGA Gain = 2, f <sub>SAMP</sub> = 413.223ksps                               | 12.1 | 12.5               | -   | bits               |

|                                           |                      | PGA Gain = 16, f <sub>SAMP</sub> = 413.223ksps,<br>A <sub>IN</sub> = -3dBFS | 9.4  | 9.8                | -   |                    |

|                                           |                      | PGA Bypassed                                                                | 85   | 95                 | -   |                    |

| Total Harmonic Distortion                 | THD                  | PGA Gain = 2, f <sub>SAMP</sub> = 413.223ksps                               | 85   | 95                 | -   | dBFS               |

|                                           |                      | PGA Gain = 16, f <sub>SAMP</sub> = 413.223ksps,<br>A <sub>IN</sub> = -3dBFS | 80   | 85                 | -   | , עטו              |

|                                           |                      | PGA Bypassed                                                                | 90   | 100                | -   |                    |

| Spurious Free Dynamic Range               | SFDR                 | PGA Gain = 2, f <sub>SAMP</sub> = 413.223ksps                               | 90   | 100                | -   | dBFS               |

|                                           |                      | PGA Gain = 16, f <sub>SAMP</sub> = 413.223ksps,<br>A <sub>IN</sub> = -3dBFS | -    | 90                 | -   | ubra               |

| Channel-to-Channel Isolation              | -                    | Full-scale signal applied to one channel, other channels connected to GND   | -    | -100               | -   | dB                 |

| Input Bandwidth                           | -                    | Source impedance = $50\Omega$ , -3dB point                                  | -    | 50                 | -   | MHz                |

| Aperture Delay                            | t <sub>AD</sub>      | CS falling edge to sample edge                                              | -    | 2.5                | -   | ns                 |

| Aperture Jitter                           | t <sub>AJITTER</sub> | -                                                                           | -    | 500                | -   | fs <sub>RMS</sub>  |

$AV_{CC}$  = 5.0V;  $DV_{CC}$  = 2.5V, REF = 2.5V, GND = 0V, PGA Bypassed, LPM = 2.5V,  $f_{SAMP}$  = 684.932ksps,  $F_{IN}$  = 20.3kHz,  $A_{IN}$  = -1dBFS;  $T_A$  = 25°C, unless otherwise noted. **Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.**

| Parameter                                 | Symbol              | Test Conditions                                      | Min | Typ <sup>[1]</sup> | Max  | Unit |  |

|-------------------------------------------|---------------------|------------------------------------------------------|-----|--------------------|------|------|--|

| Power Supply Characteristics (AVCC, DVCC) |                     |                                                      |     |                    |      |      |  |

| Analog Supply Voltage                     | AV <sub>CC</sub>    | -                                                    | 4.5 | -                  | 5.5  | V    |  |

| A                                         | 1                   | Active, PGA enabled, f <sub>SAMP</sub> = 413.223ksps | -   | 13.9               | 16.9 | mA   |  |

| Analog Supply Current - Active            | IAVCC               | Active, PGA bypassed, f <sub>SAMP</sub> = 670ksps    | -   | 15.8               | 17.5 | mA   |  |

| Analog Supply Current - Static            | 1                   | PGA enabled. CS held Low                             | -   | 6                  | 7.5  | mA   |  |

| Analog Supply Current - Static            | I <sub>Static</sub> | PGA bypassed. CS held Low.                           | -   | 6                  | 7.5  | mA   |  |

| Analog Supply Current - Sleep             | I <sub>SLAVCC</sub> | PD held Low                                          | -   | 20                 | -    | μΑ   |  |

| Digital Supply Voltage                    | DV <sub>CC</sub>    | -                                                    | 2.2 | -                  | 3.6  | V    |  |

| Digital Supply Current Active             | I <sub>DVCC</sub>   | PGA enabled. f <sub>SCK</sub> = 50MHz                | -   | 346                | 600  | μΑ   |  |

| Digital Supply Current - Active           |                     | PGA bypassed. f <sub>SCK</sub> = 50MHz               | -   | 512                | 700  | μΑ   |  |

| Digital Cumply Current Statio             | I <sub>STDVCC</sub> | PGA enabled. CS held Low                             | -   | 92                 | 140  | μΑ   |  |

| Digital Supply Current - Static           |                     | PGA bypassed. CS held Low                            | -   | 64                 | 120  | μΑ   |  |

| Digital Supply Current - Sleep            | I <sub>SLDVCC</sub> | PD held Low                                          | -   | 6                  | -    | μΑ   |  |

|                                           | P <sub>ACTIVE</sub> | PGA enabled, f <sub>SAMP</sub> = 413.223ksps         | -   | 70                 | 86   | mW   |  |

| $P_{D}$                                   | P <sub>ACTIVE</sub> | PGA bypassed, f <sub>SAMP</sub> = 684.932ksps        | -   | 80                 | 89   | mW   |  |

|                                           | P <sub>STATIC</sub> | PGA enabled, CS held Low                             | -   | 30                 | 40   | mW   |  |

|                                           | P <sub>STATIC</sub> | PGA bypassed, CS held Low                            | -   | 30                 | 40   | mW   |  |

|                                           | P <sub>SLEEP</sub>  | PD held Low                                          | -   | 115                | -    | μW   |  |

<sup>1.</sup> Typical values are not guaranteed.

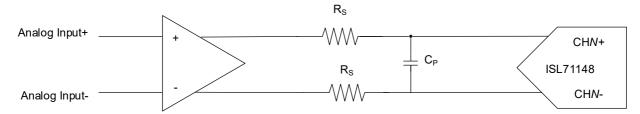

### 3.4.3 Channel Input Specifications

$AV_{CC}$  = 5.0V;  $DV_{CC}$  = 2.5V, REF = 2.5V, GND = 0V,  $T_A$  = 25°C,  $F_{IN}$  = 20.3kHz, unless otherwise noted. **Boldface limits apply across** the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.

| Parameter                                                       | Symbol           | Test Conditions                    | Min                       | Typ <sup>[1]</sup>  | Max                       | Unit |  |  |

|-----------------------------------------------------------------|------------------|------------------------------------|---------------------------|---------------------|---------------------------|------|--|--|

| Channel Input Characteristics (CH0 to CH7)                      |                  |                                    |                           |                     |                           |      |  |  |

| Absolute Input Range (CH0+ to CH7+ to GND, CH0- to CH7- to GND) | -                | Recommended Operating<br>Condition | -0.1                      | -                   | V <sub>REF</sub> + 0.1    | V    |  |  |

| Input Differential Range<br>(CHn+ - CHn-)                       | -                | -                                  | -V <sub>REF</sub> /GAIN   | -                   | V <sub>REF</sub> /GAIN    | V    |  |  |

| Common Mode Input Range ½×(CHn+ + CHn-)                         | -                | -                                  | V <sub>REF</sub> /2 - 0.1 | V <sub>REF</sub> /2 | V <sub>REF</sub> /2 + 0.1 | V    |  |  |

| Input Common Mode Rejection Ratio                               | -                | -                                  | -                         | 90                  | -                         | dB   |  |  |

| Input Leakage Current                                           | IA <sub>IN</sub> | -                                  | -1                        |                     | 1                         | μA   |  |  |

| Input Capacitance                                               | C <sub>IN</sub>  | -                                  | -                         | 4                   | -                         | pF   |  |  |

| Input Resistance                                                | R <sub>IN</sub>  | -                                  | -                         | 1                   | -                         | GΩ   |  |  |

<sup>2.</sup> Characterized on all channels, production tested on Channel 0 only.

$AV_{CC}$  = 5.0V;  $DV_{CC}$  = 2.5V, REF = 2.5V, GND = 0V,  $T_A$  = 25°C,  $F_{IN}$  = 20.3kHz, unless otherwise noted. **Boldface limits apply across** the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter         | Symbol | Test Conditions        | Min   | Typ <sup>[1]</sup> | Max  | Unit |

|-------------------|--------|------------------------|-------|--------------------|------|------|

| PGA Gain Accuracy |        | Gain = 1, G2:G0 = 000  | -0.45 | -0.2               | 0.15 | %    |

|                   |        | Gain = 2, G2:G0 = 001  | -0.45 | -0.2               | 0.15 | %    |

|                   |        | Gain = 3, G2:G0 = 010  | -0.45 | -0.2               | 0.15 | %    |

|                   |        | Gain = 4, G2:G0 = 011  | -0.45 | -0.2               | 0.15 | %    |

|                   | _      | Gain = 6, G2:G0 = 100  | -0.8  | -0.3               | 0.35 | %    |

|                   |        | Gain = 8, G2:G0 = 101  | -0.8  | -0.4               | 0.35 | %    |

|                   |        | Gain = 12, G2:G0 = 110 | -1    | -0.5               | 0.2  | %    |

|                   |        | Gain = 16, G2:G0 = 111 | -1    | -0.7               | 0.2  | %    |

<sup>1.</sup> Typical values are not guaranteed.

#### 3.4.4 I/O Specifications

$AV_{CC} = 5.0V$ ;  $DV_{CC} = 2.5V$ , REF = 2.5V, GND = 0V,  $T_A = 25^{\circ}C$ , unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.

| Parameter                                              | Symbol             | Test Conditions                                 | Min                    | Typ <sup>[1]</sup> | Max                  | Unit |

|--------------------------------------------------------|--------------------|-------------------------------------------------|------------------------|--------------------|----------------------|------|

| Digital Inputs and Outputs (PD                         | , CS, SCK, I       | BUSY, SDO, LPM, PGABP, S2, S1, S0               | , G2, G1, G0)          |                    | 1                    |      |

| High Level Input                                       | V <sub>IH</sub>    | -                                               | 0.8×DV <sub>CC</sub>   | -                  | -                    | V    |

| Low Level Input                                        | V <sub>IL</sub>    | -                                               | -                      | -                  | 0.2×DV <sub>CC</sub> | V    |

| Input Current (CS, SCK, PGABP, S2, S1, S0, G2, G1, G0) | I <sub>IN</sub>    | V <sub>IN</sub> = 0V to DV <sub>CC</sub>        | -1                     | -                  | 1                    | μA   |

| Input Capacitance                                      | C <sub>IN</sub>    | -                                               | -                      | 5                  | -                    | pF   |

| High Level Output                                      | V <sub>OH</sub>    | $DV_{CC}$ - Output, $I_O = -500\mu A$           | DV <sub>CC</sub> - 0.2 | -                  | -                    | V    |

| Low Level Output                                       | V <sub>OL</sub>    | I <sub>O</sub> = 500μA                          | -                      | -                  | 0.2                  | V    |

| Output Source Current                                  | I <sub>SRC</sub>   | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>       |                        | -10                |                      | mA   |

| Output Sink Current                                    | I <sub>SNK</sub>   | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>       |                        | 10                 |                      | mA   |

| Hi-Z Output Leakage Current                            | I <sub>OZ</sub>    | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>       | -1                     |                    | 1                    | μΑ   |

| PD Input Resistance                                    | R <sub>INPDL</sub> | Internal pull-up resistance to D <sub>VCC</sub> | 375                    | 475                | 600                  | kΩ   |

| LPM Input Resistance                                   | R <sub>INLPM</sub> | Internal pull-down resistance to GND            | 375                    | 475                | 600                  | kΩ   |

| Reference Input Characteristic                         | s (REF)            |                                                 |                        |                    | •                    | •    |

| REF Input Voltage Range                                | $V_{REF}$          | -                                               | 2.4                    | 2.5                | 2.6                  | V    |

| REF Input Current                                      | I <sub>REF</sub>   | -                                               | -                      | 150                | 200                  | μΑ   |

<sup>1.</sup> Typical values are not guaranteed.

#### 3.4.5 Operation Burn-In Deltas

$AV_{CC}$  = 5.0V;  $DV_{CC}$  = 2.5V, REF = 2.5V, GND = 0V, PGA Bypassed, LPM = 0V (Normal Mode) and LPM =  $DV_{CC}$  (Low Power Mode),  $f_{SAMP}$  = 900.901ksps (Normal Mode) and 684.932ksps (Low Power Mode),  $F_{IN}$  = 20.3kHz,  $A_{IN}$  = -1dBFS,  $T_A$  = +25°C, S2, S1, and S0 = 0V (Channel 0 selected); unless otherwise noted.

| Parameter                | Symbol | Test Conditions                       | Min  | Max | Unit |

|--------------------------|--------|---------------------------------------|------|-----|------|

| Integral Non-Linearity   | INL    | Measured with full scale input signal | -0.5 | 0.5 | LSB  |

| Signal to Noise Ratio    | SNR    | F <sub>IN</sub> = 20.3kHz             | -1   | 1   | dBFS |

| Effective Number of Bits | ENOB   | F <sub>IN</sub> = 20.3kHz             | -0.2 | 0.2 | bits |

## 3.5 Timing Specifications

#### 3.5.1 Normal Operating Mode

$AV_{CC}$  = 4.5V to 5.5V;  $DV_{CC}$  = 2.2V to 3.6V, REF = 2.5V, GND = 0V, PGA Bypassed, LPM = 0V,  $f_{SAMP}$  = 900.901ksps,  $A_{IN}$  = -1dBFS;  $T_A$  = 25°C, unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.

| Parameter                            | Symbol                  | Test Conditions                              | Min | Typ <sup>[1]</sup> | Max     | Unit |

|--------------------------------------|-------------------------|----------------------------------------------|-----|--------------------|---------|------|

| Maximum Sampling Frequency           | f                       | PGA Bypassed                                 | -   | -                  | 900.901 | kHz  |

|                                      | f <sub>SAMP</sub>       | PGA Enabled                                  | -   | -                  |         | kHz  |

|                                      |                         | BUSY Output High Time, PGA<br>Bypassed       | -   | -                  | 660     | ns   |

| Conversion Time                      | t <sub>CONV</sub>       | BUSY Output High Time, PGA<br>Enabled        | -   | -                  | 1550    | ns   |

| CS High Time                         | t <sub>CSH</sub>        | -                                            | 150 | -                  | -       | ns   |

| SCK Held Low to CS↓                  | t <sub>QUIET</sub>      | -                                            | 150 | -                  | -       | ns   |

| CS↓ to BUSY↑                         | t <sub>BUSYLH</sub>     | PGA enabled, C <sub>L</sub> = 10pF           | -   | -                  | 100     | ns   |

| CS↓ to BUSY↑                         | t <sub>BUSYLH</sub>     | PGA bypassed, C <sub>L</sub> = 10pF          | -   | -                  | 30      | ns   |

| SCK Period                           | t <sub>sck</sub>        | -                                            | 20  | -                  | -       | ns   |

| SCK High Time                        | tscкн                   | -                                            | 8   | -                  | -       | ns   |

| SCK Low Time                         | t <sub>SCKL</sub>       | -                                            | 8   | -                  | -       | ns   |

| SDO Data Valid Delay from BUSY↓      | t <sub>DBUSYLSDOV</sub> | C <sub>L</sub> = 10pF                        | -   | -                  | 0       | ns   |

| SDO Data Valid Delay from SCK↑       | t <sub>DSCKSDOV</sub>   | C <sub>L</sub> = 10pF                        | -   | -                  | 20      | ns   |

| SDO Data Valid Hold Time from SCK↑   | t <sub>HSDOV</sub>      | C <sub>L</sub> = 10pF                        | 7   | -                  | -       | ns   |

| SDO Bus Acquisition Time from CS↓    | t <sub>DCSLSDOL</sub>   | C <sub>L</sub> = 10pF                        | -   | -                  | 25      | ns   |

| SDO Bus Relinquish Time after CS↑    | t <sub>DCSHSDOZ</sub>   | C <sub>L</sub> = 10pF                        |     | -                  | 25      | ns   |

| G2:0, S2:0 to <del>CS</del> ↑        | t <sub>SUDIGCSH</sub>   | Setup time for gain and channel select bits. | 5   | -                  | -       | ns   |

| G2:0, S2:0 from CS↑                  | t <sub>HDIGCSH</sub>    | Hold time for gain and channel select bits.  | 25  | -                  | -       | ns   |

| SCAN to CS↑                          | t <sub>SCANCSH</sub>    | Setup time for SCAN input.                   | 20  | -                  | -       | ns   |

| Wake-Up time from Power-Down<br>Mode | t <sub>WAKE</sub>       | Time to wait after PD↑ to first sample       | -   | 15                 | 25      | μs   |

<sup>1.</sup> Typical values are not guaranteed.

#### 3.5.2 Low Power Mode

$AV_{CC}$  = 4.5V to 5.5V;  $DV_{CC}$  = 2.2V to 3.6V, REF = 2.5V, GND = 0V, PGA Bypassed, LPM =2.5V,  $f_{SAMP}$  = 684.932ksps,  $A_{IN}$  = -1dBFS;  $T_A$  = 25°C, unless otherwise noted. **Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.**

| Parameter                                        | Symbol                  | Test Conditions                              | Min | Typ <sup>[1]</sup> | Max     | Unit |

|--------------------------------------------------|-------------------------|----------------------------------------------|-----|--------------------|---------|------|

| Maximum Campling Fraguency                       | f                       | PGA Bypassed                                 | -   | -                  | 684.932 | kHz  |

| Maximum Sampling Frequency                       | f <sub>SAMP</sub>       | PGA Enabled                                  | -   | -                  | 413.223 | kHz  |

|                                                  | +                       | BUSY Output High Time,<br>PGA Bypassed       | -   | -                  | 660     | ns   |

| Conversion Time                                  | t <sub>CONV</sub>       | BUSY Output High Time,<br>PGA Enabled        | -   | -                  | 1550    | ns   |

| CS High Time                                     | t <sub>CSH</sub>        | -                                            | 500 | -                  | -       | ns   |

| SCK Held Low to CS↓                              | t <sub>QUIET</sub>      | -                                            | 500 | -                  | -       | ns   |

| <br>CS↓ to BUSY↑                                 |                         | C <sub>L</sub> = 10pF, PGA enabled.          | -   | -                  | 100     | ns   |

| C3 to B031                                       | t <sub>BUSYLH</sub>     | C <sub>L</sub> = 10pF, PGA bypassed.         | -   | -                  | 30      | ns   |

| SCK Period                                       | t <sub>SCK</sub>        | -                                            | 20  | -                  | -       | ns   |

| SCK High Time                                    | t <sub>SCKH</sub>       | -                                            | 8   | -                  | -       | ns   |

| SCK Low Time                                     | t <sub>SCKL</sub>       | -                                            | 8   | -                  | -       | ns   |

| SDO Data Valid Delay from BUSY↓                  | t <sub>DBUSYLSDOV</sub> | C <sub>L</sub> = 10pF                        | -   | -                  | 0       | ns   |

| SDO Data Valid Delay from SCK↑                   | t <sub>DSCKSDOV</sub>   | C <sub>L</sub> = 10pF                        | -   | -                  | 20      | ns   |

| SDO Data Valid Hold Time from SCK↑               | t <sub>HSDOV</sub>      | C <sub>L</sub> = 10pF                        | 7   | -                  | -       | ns   |

| SDO Bus Acquisition Time from CS↓                | t <sub>DCSLSDOL</sub>   | C <sub>L</sub> = 10pF                        | -   | -                  | 25      | ns   |

| SDO Bus Relinquish Time after CS↑                | t <sub>DCSHSDOZ</sub>   | C <sub>L</sub> = 10pF                        | -   | -                  | 25      | ns   |

| G2:0, S2:0 to <del>CS</del> ↑                    | t <sub>SUDIGCSH</sub>   | Setup time for gain and channel select bits. | 15  | -                  | -       | ns   |

| G2:0, S2:0 from <del>CS</del> ↑                  | t <sub>HDIGCSH</sub>    | Hold time for gain and channel select bits.  | 10  | -                  | -       | ns   |

| SCAN to CS↑                                      | t <sub>SCAN</sub>       | Setup time for SCAN input.                   | 20  | -                  | -       | ns   |

| Wake-Up time from Power-Down Mode <sup>[2]</sup> | t <sub>WAKE</sub>       | Time to wait after PD↑ to first sample       | -   | 15                 | 25      | μs   |

<sup>1.</sup> Typical values are not guaranteed.

<sup>2.</sup> Production tested in normal mode.

## 3.6 Timing Diagrams

Note: Bits S2, S1, S0, G2, G1, and G0 are optional and not required. For maximum sample rate, do not provide additional clocks for these bits.

Figure 6. Operational Timing Diagram - Normal Operation

Figure 7. SCAN Timing Diagram - Normal Mode

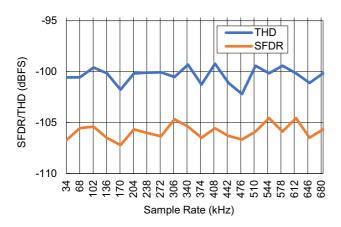

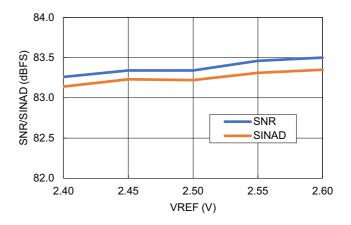

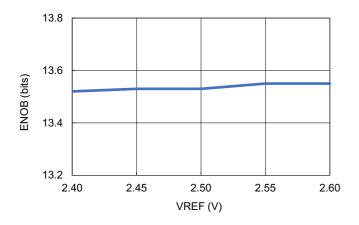

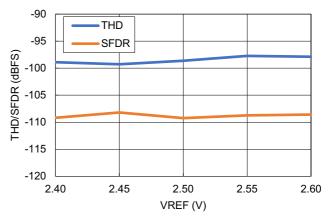

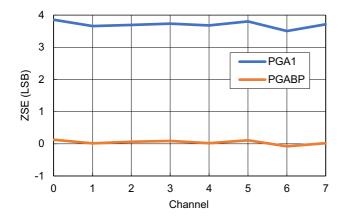

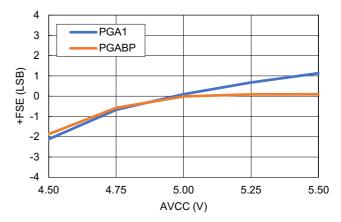

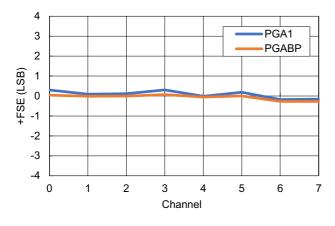

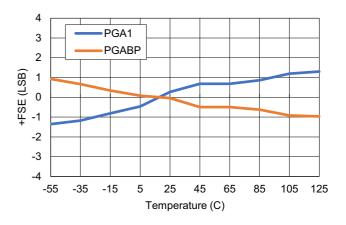

Note: Bits S2, S1, S0, G2, G1, and G0 are optional and not required. For maximum sample rate, do not provide additional clocks for these bits.