# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

# ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# M3727GM6/M8-XXXSP/FP M37272E8SP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER and ON-SCREEN DISPLAY CONTROLLER

RJJ03B0138-0100Z Rev.1.00 2001.04.01

#### 1. 概要

$M3727GM6/M8-XXXSP/FPは、シリコンゲートCMOSプロセスを採用したシングルチップマイクロコンピュータです。OSD、データスライサ、<math>I^2C$ -BUSインタフェースなどを備えていますので、クローズドキャプションデコーダ内蔵TVの選局システムに最適です。

M37272E8SP/FP は、電気的書き込み可能な PROM を内蔵していること以外はM3727GM6/M8-XXXSP/FPと同等の機能を有しています。また M3727GM6-XXXSP/FP, M3727GM8-XXXSP/FP の相違点は ROM, RAM 容量のみですので特に断らないかぎり M3727GM6-XXXSP/FP として説明します。

#### 2. 特 長

● 基本機械語命令 71

● メモリ容量

ROM 24K バイト(M3727GM6-XXXSP/FP)

32K バイト(M3727GM8-XXXSP/FP, M37272E8SP/FP)

RAM 1024 バイト(M3727GM6-XXXSP/FP, M37272E8SP/FP)

1152 バイト(M3727GM8-XXXSP/FP, M37272E8SP/FP)

| 1152 バイト(M3727GM8-XXXSP/FP, M37272E8SP/FP)      |

|-------------------------------------------------|

| ( ROM 訂正メモリを含む)                                 |

| ● 命令実行時間 ( 最短命令、8MHz 時 ) 0.5 µ s ( 最小 )         |

| ● 単一電源 5V ± 10%                                 |

| ● サブルーチンネスティング 最大 128 レベル                       |

| ●割り込み 17 要因 16 ベクタ                              |

| ●8 ビットタイマ6本                                     |

| ● プログラマブル入出力                                    |

| (ポート P0, P1, P2, P30, P31)26本                   |

| ● 入力ポート ( ポート P50, P51 )2 本                     |

| ● 出力ポート ( ポート P52 ~ P55 )                       |

| ● LED 駆動ポート 4 本                                 |

| ● シリアル I/O 8 ビット× 1本                            |

| ● マルチマスタ I <sup>2</sup> C-BUS インタフェース 1 本(2 系統) |

| ● A-D 比較器 ( 分解能 6 ビット ) 6 チャネル                  |

| ● PWM 出力回路8 ビット× 6 本                            |

| ●消費電力                                           |

| 高速モード時 137.5mW                                  |

(電源電圧 5.5V、発振周波数 32kHz 時)

● クローズドキャプションデータスライサ

ライサ ON 時)

● ROM 訂正機能 ....... 2ベクタ

(電源電圧 5.5V、発振周波数 8MHz, OSD 表示, データス

低速モード時 ...... 0.33mW

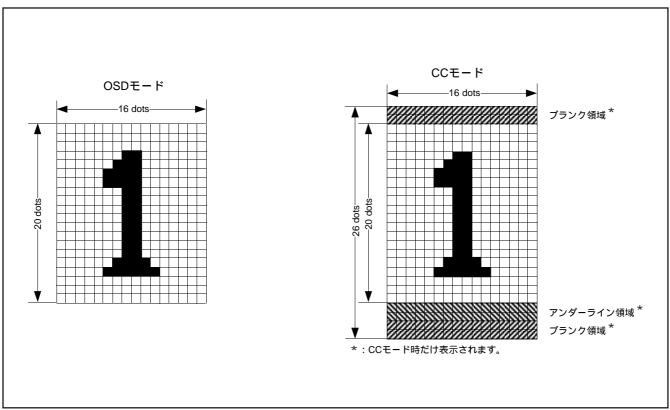

#### ● OSD 機能

表示文字数 32 文字 × 2 行

(ソフトウエアによって3行以上の表示可能)

文字種類 254種類

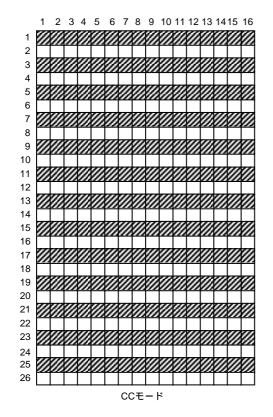

文字表示領域 CC モード:16 x 26 ドット

OSD モード:16 × 20 ドット

文字サイズ CC モード:1種類

OSD モード:8 種類

文字色種類 8種類(R,G,B)

着色単位 文字、文字背景、ラスター 表示位置 水平 128 段階 / 垂直 512 段階

アトリビュート CC モード: スムーズイタリック、アンダーライン、

フラッシュ、オートソリット<sup>\*</sup> スペ ース

OSD モード:フチドリ

スムーズ Roll-up ウインドウ機能

#### 3. 応 用

クローズドキャプションデコーダ内蔵 TV

# 【目次】

| 1. | 忧    | <b>娄</b>               | 1  |

|----|------|------------------------|----|

| 2. | 特    | 長                      | 1  |

| 3. | 応    | 用                      | 1  |

| 4. | ピン   | 接続図                    | 3  |

| 5. | ブロ   | ック図                    | 4  |

| 6. | 性能   | 概要                     | 5  |

| 7. | 端子   | の機能説明                  | 7  |

| 8. | 機能   | ブロック動作説明               | 11 |

|    | 8.1  | 中央演算処理装置 ( CPU )       | 11 |

|    | 8.2  | メモリ                    | 12 |

|    | 8.3  | 割り込み                   | 17 |

|    | 8.4  | タイマ                    | 22 |

|    | 8.5  | シリアル I/O               | 26 |

|    | 8.6  | マルチマスタ I2C-BUS インタフェース | 29 |

|    | 8.7  | PWM 出力回路               | 43 |

|    | 8.8  | A-D 比較器                | 47 |

|    | 8.9  | ROM 訂正機能               | 49 |

|    | 8.10 | データスライサ                | 50 |

|    | 8.11 | OSD 機能                 | 61 |

|    |      | 8.11.1 表示位置            | 66 |

|    |      | 8.11.2 ドットサイズ          | 70 |

|    |      | 8.11.3 OSD用クロック        | 71 |

|    |      | 8.11.4 フィールド判別表示       | 72 |

|    |      | 8.11.5 OSD用メモリ         | 74 |

|    |      | 8.11.6 文字色             | 78 |

|    |      | 8.11.7 文字背景色           | 78 |

|    |      | 8.11.8 OUT1, OUT2 信号   | 79 |

|    |      | 8.11.9 アトリビュート         | 80 |

|    |      | 8.11.10 多行表示           | 85 |

|    |      | 8.11.11 オートソリッドスペース機能  | 86 |

|    |      | 8.11.12 ウインドウ機能        | 87 |

|    |      | 8.11.13 OSD 出力端子制御     | 89 |

|    |      | 8.11.14 ラスター着色         | 90 |

|    | 8.12 | 暴走検出機能                 | 92 |

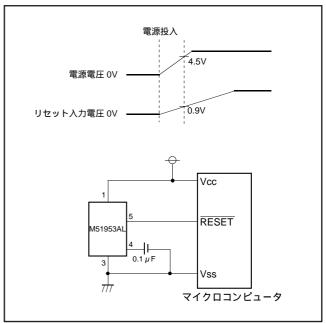

|    | 8.13 | リセット回路                 | 93 |

|    | 8.14 | クロック発生回路               | 94 |

|    |      | OSD 用発振回路              |    |

|    | 8.16 | オートクリア回路               | 97 |

|    | 8.17 | アドレッシングモード             | 97 |

|    | 8 18 | <b>継</b> 械語命今一瞥表       | 97 |

| 9.  | 使用上の注意事項                            | . 97 |

|-----|-------------------------------------|------|

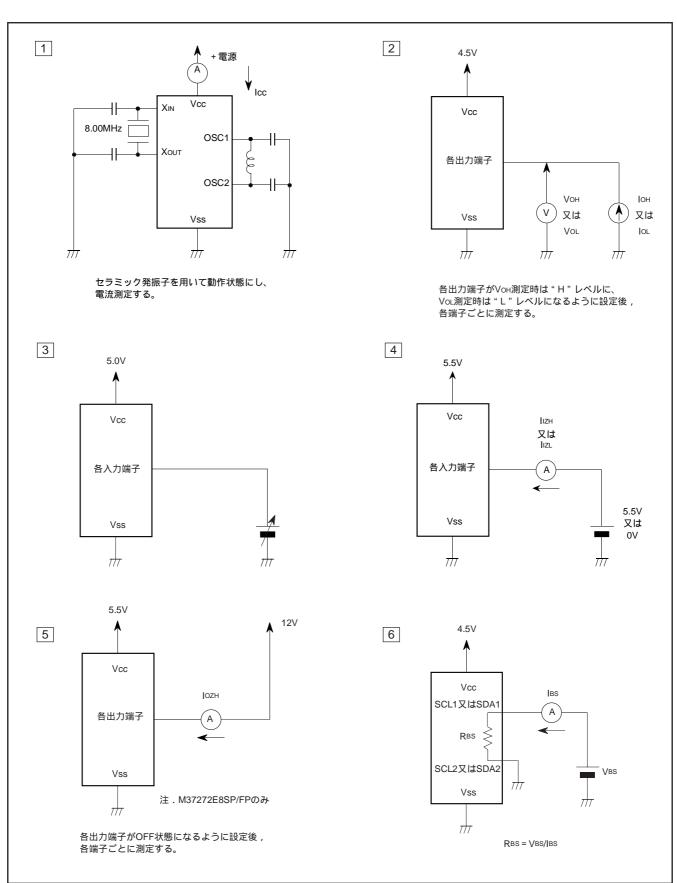

| 10. | 絶対最大定格                              | . 98 |

| 11. | 推奨動作条件                              | . 98 |

| 12. | 電気的特性                               | . 99 |

| 13. | A-D 比較特性                            | 101  |

| 14. | マルチマスタ I <sup>2</sup> C-BUS バスライン特性 | 101  |

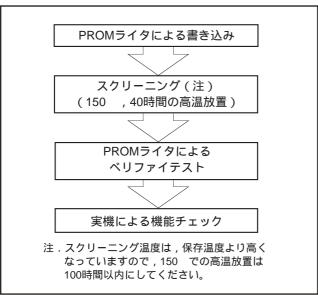

| 15. | PROM 書き込み方法                         | 102  |

| 16. | マスク発注時の提出資料                         | 103  |

| 17. | ワンタイム PROM 版 M37272E8SP/FP マーキング図   | 104  |

| 18. | 付録                                  | 105  |

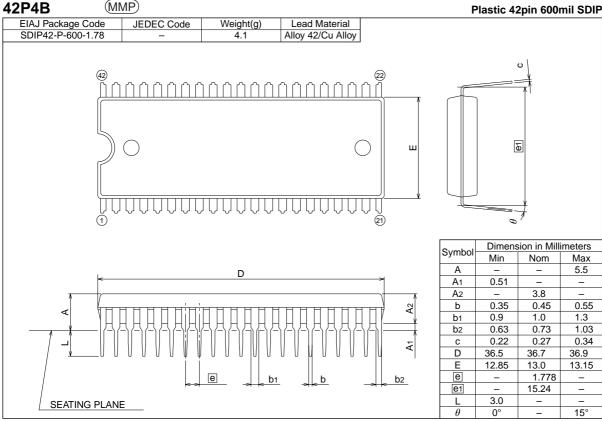

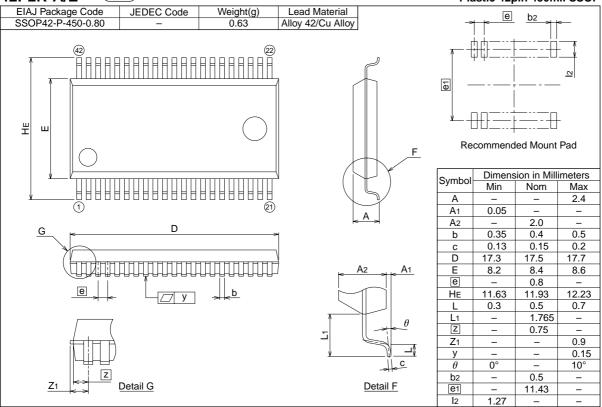

| 19. | パッケージ外形寸法図                          | 129  |

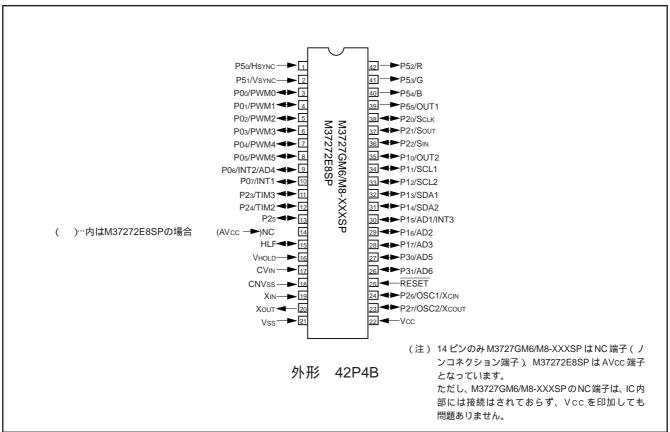

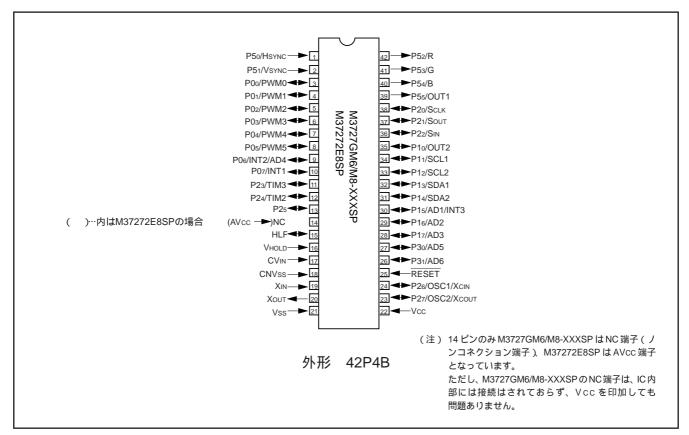

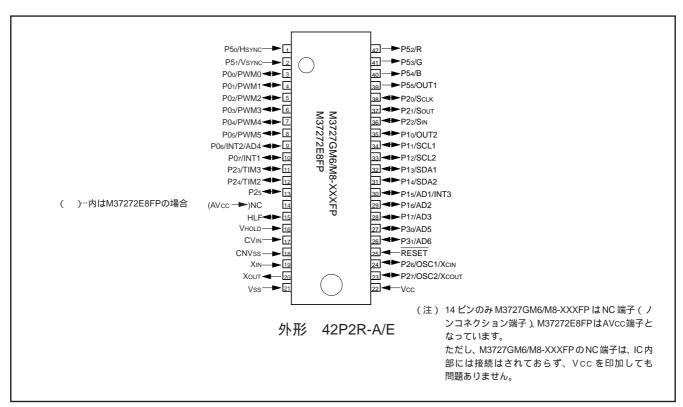

#### 4. ピン接続図

図 4.1 ピン接続図 (1)(上面図)

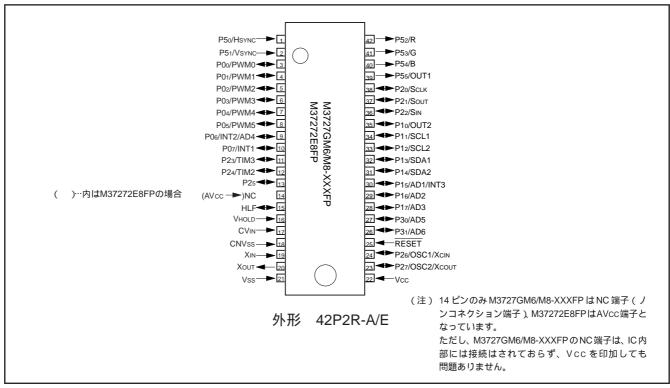

図 4.2 ピン接続図 (2)(上面図)

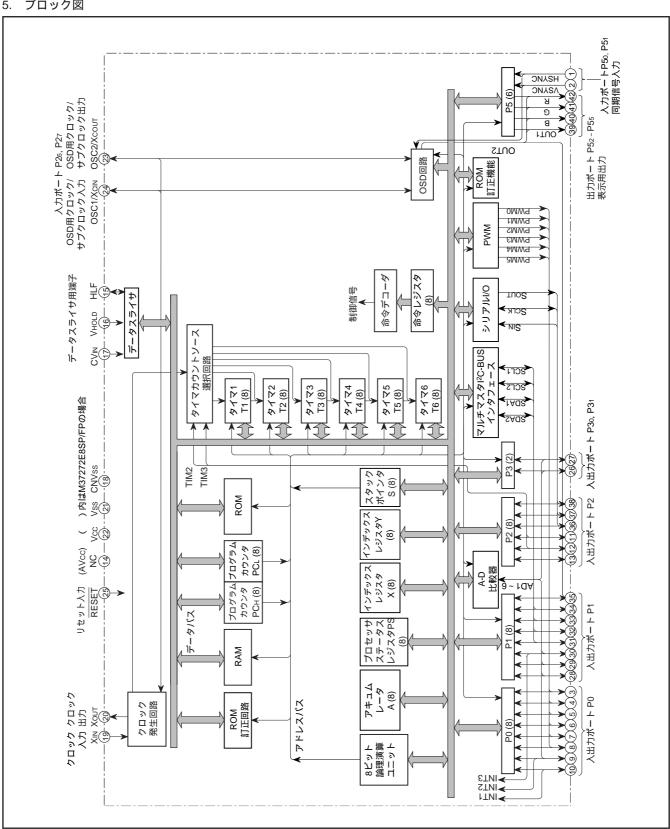

#### ブロック図

M3727G のブロック図 図 5.1

# 6. 性能概要

# 表 6.1 性能概要

| 項目                         |           |                   |                      | 性能                                                                                                                                              |  |

|----------------------------|-----------|-------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 基本命令数                      | 基本命令数     |                   |                      | 71                                                                                                                                              |  |

| 命令実行時間                     |           |                   |                      | 0.5 μ s ( 最短命令 , 発振周波数 8 MHz 時 )                                                                                                                |  |

| クロック周波数                    |           |                   |                      | 8MHz ( 最大)                                                                                                                                      |  |

|                            | ROM       | M3727GM6-XXXSP/FP |                      | 24K バイト                                                                                                                                         |  |

|                            |           | M3727GM8-XXXS     | P/FP, M37272E8SP/FP  | 32K バイト                                                                                                                                         |  |

| <br>  メモリ容量                | RAM       | M3727GM6-XXX      | SP/FP                | 1024 バイト(ROM 訂正メモリを含む)                                                                                                                          |  |

| グロリ谷里                      |           | M3727GM8-XXXS     | SP/FP, M37272E8SP/FP | 1152 バイト(ROM 訂正メモリを含む)                                                                                                                          |  |

|                            | OSD       | ROM               |                      | 10K バイト                                                                                                                                         |  |

|                            | OSD       | RAM               |                      | 128バイト                                                                                                                                          |  |

|                            | P0        |                   | 入出力                  | 8 ビット× 1(Nチャネルオープンドレイン出力形式, PWM 出力, INT<br>入力, A-D 入力と兼用)                                                                                       |  |

|                            | P10 ~ P17 |                   | 入出力                  | 8 ビット× 1(P1 は CMOS 入出力形式,ただし P11 ~ P14 はマルチマスタ $I^2$ C-BUS インタフェースとして使用時,N チャネルオープンドレイン出力形式,OSD 出力,A-D 入力,INT 入力,マルチマスタ $I^2$ C-BUS インタフェースと兼用) |  |

| 入出力ポート                     | P20 ~     | P27               | 入出力                  | 8 ビット×1 (P2 は CMOS 入出力形式, ただし P20, P21 はシリアル出力として使用時, N チャネルオープンドレイン出力形式,シリアル入出力,タイマ用外部クロック入力,OSDクロック入出力,サブクロック入出力と兼用)                          |  |

|                            | P30, P31  |                   | 入出力                  | 2 ビット×1(CMOS 入出力又は N チャネルオープンドレイン出力<br>形式, A-D 入力と兼用)                                                                                           |  |

|                            | P50, F    | P51               | 入 力                  | 2 ビット×1 (OSD 入力と兼用)                                                                                                                             |  |

|                            | P52 ~     | P55               | 出力                   | 4 ビット×1(CMOS 出力形式,OSD 出力と兼用)                                                                                                                    |  |

| シリアル 1/0                   |           |                   |                      | 8ビット×1本                                                                                                                                         |  |

| マルチマスタ I <sup>2</sup> C-BI | JS インタ    | フフェース             |                      | 1本(2系統)                                                                                                                                         |  |

| A-D 比較器                    |           |                   |                      | 6チャネル (分解能 6 ビット)                                                                                                                               |  |

| PWM 出力回路                   |           |                   |                      | 8ビット×6本                                                                                                                                         |  |

| タイマ                        |           |                   |                      | 8ビット×6本                                                                                                                                         |  |

| ROM 訂正機能                   |           |                   |                      | 2ベクタ                                                                                                                                            |  |

| サブルーチンネステ                  | ィング       |                   |                      | 最大 128 レベル                                                                                                                                      |  |

|                            |           |                   |                      | < 17 要因 >                                                                                                                                       |  |

| 割り込み                       |           |                   |                      | INT外部割り込み×3,内部タイマ割り込み×6,シリアルI/O割り込み                                                                                                             |  |

|                            |           |                   |                      | x 1, OSD 割り込みx 1, マルチマスタ I <sup>2</sup> C-BUS インタフェース割り<br>込みx 1, データスライサ割り込みx 1, f(XIN)/4096 割り込みx 1,                                          |  |

|                            |           |                   |                      | VSYNC 割り込み×1, BRK 命令割り込み×1, リセット×1                                                                                                              |  |

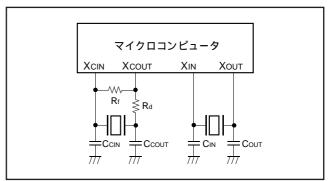

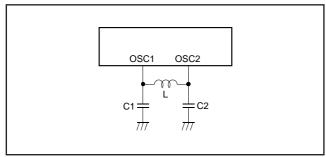

| クロック発生回路                   |           |                   |                      | 2回路内蔵(セラミック共振子,又は水晶発振子外付け)                                                                                                                      |  |

| データスライサ                    |           |                   |                      | 内蔵                                                                                                                                              |  |

#### 表 6.2 性能概要(つづき)

|                               |            |                           |                   |              | 性能                                                                                   |

|-------------------------------|------------|---------------------------|-------------------|--------------|--------------------------------------------------------------------------------------|

|                               |            | 表示文艺                      | 字数                |              | 32文字×2行                                                                              |

|                               |            | ドット                       | 構成                |              | CC モード: 16 × 26 ドット(文字表示領域は16 × 20 ドット)                                              |

|                               |            |                           |                   |              | OSD モード: 16 × 20 ドット                                                                 |

|                               |            | 文字種                       | 類                 |              | 254 種類                                                                               |

| OSD 機能                        |            | 文字サ                       | イズ                |              | CC モード:1種類                                                                           |

|                               |            |                           |                   |              | OSD モード:8種類                                                                          |

|                               |            | キャラクタフォント着色               |                   |              | 1 画面 8 種類 (文字単位)                                                                     |

|                               |            | 表示位置                      | Ĕ                 |              | 水平:128段階、垂直:512段階                                                                    |

| 電源電圧                          |            |                           |                   |              | 5V ± 10%                                                                             |

| 消費電力                          | 消費電力 高速モード |                           | E-ド時 OSD ON データ   |              | 137.5mW 標準(発振周波数 f(XIN) = 8MHz , fosc = 27MHz)<br>< 165mW 標準> < >内はM37272E8SP/FP の場合 |

|                               |            |                           | OSD OFF           | データスライサOFF   | 55mW 標準 ( 発振周波数 f(XIN) = 8MHz )<br>< 82.5mW 標準 > 〈 >内は M37272E8SP/FP の場合             |

|                               | 低速モ・       | 低速モード時 OSD OFF データスライサOFI |                   |              | 0.33mW 標準(発振周波数 f(XCIN) = 32kHz, f(XIN)=停止)                                          |

| ストップモード時                      |            |                           | 诗                 |              | 0.055mW 最大                                                                           |

| 動作周囲温度                        |            |                           |                   |              | - 10 ~ 70                                                                            |

| 素子構造                          |            |                           |                   |              | CMOS シリコンゲート                                                                         |

| パッケージ                         | •          |                           | M3727GM6/M8-XXXSP | , M37272E8SP | 42 ピンプラスチックモールド SDIP                                                                 |

| M3727GM6/M8-XXXFP, M37272E8FP |            |                           |                   | , M37272E8FP | 42 ピンプラスチックモールド SSOP                                                                 |

# 7. 端子の機能説明

# 表 7.1 端子の機能説明

| 端子名                    | 名 称                         | 入出力 | 機能                                                                                                  |

|------------------------|-----------------------------|-----|-----------------------------------------------------------------------------------------------------|

| Vcc, (AVcc)            | 電源入力                        |     | Vcc, (AVcc) に5V ± 10% (標準), Vss に 0V を印加します。                                                        |

| Vss                    |                             |     | ( )内はM37272E8SP/FPのみ                                                                                |

| CNVss                  | CNVss                       |     | Vss に接続してください。                                                                                      |

| RESET                  | リセット入力                      | 入力  | リセット入力端子で , リセットするには 2 μ s 以上必要です。                                                                  |

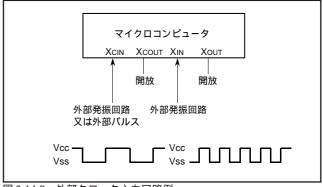

| XIN                    | クロック入力                      | 入力  | メインクロック発生回路の入出力端子です。クロック発生回路を内蔵しており発振周波数の設定は<br>セラミック共振子又は水晶発振子を XIN と XOUT の間に接続して行います。 外部クロック入力を利 |

| Хоит                   | クロック出力                      | 出力  | 用する場合はクロック発振源を XIN 端子に接続し, XOUT 端子を開放してください。                                                        |

| P00/PWM0 ~             | 入出力ポート P0                   | 入出力 | ポート P0 は8 ビットの入出力ポートです。入出力方向レジスタを持っており,各ビットごとに入                                                     |

| P05/PWM5,              |                             |     | 力端子にするか出力端子にするかをプログラムできます。リセット時には入力モードになります。                                                        |

| P06/INT2/AD4           |                             |     | 出力形式は N チャネルオープンドレイン出力です。( 注 1 )                                                                    |

| P07/INT1               | PWM 出力                      | 出力  | P00 ~ P05 端子は,それぞれ PWM 出力端子 PWM0 ~ PWM5 と共用です。出力形式は N チャネルオープンドレイン出力です。                             |

|                        | 外部割り込み入力                    | 入力  | P06,P07 端子は,それぞれ INT 外部割り込み入力端子 INT2,INT1 と共用です。                                                    |

|                        | アナログ入力                      | 入力  | P06 端子は,アナログ入力端子 AD4 と共用です。                                                                         |

| P10/OUT2,<br>P11/SCL1, | 入出力ポート P1                   | 入出力 | ポート P1 は 8 ビットの入出力ポートでポート P0 とほぼ同等の機能を有しています。出力形式は CMOS 出力です。(注 1)                                  |

| P12/SCL2,              | OSD 出力                      | 出力  | P10 端子は,OSD 出力端子 OUT2 と共用です。出力形式は CMOS 出力です。                                                        |

| P13/SDA1,              | マルチマスタ I <sup>2</sup> C-BUS | 入出力 | P11 ~ P14端子は , マルチマスタI <sup>2</sup> C-BUSインタフェース使用時 , それぞれ SCL1 , SCL2 , SDA1 ,                     |

| P14/SDA2,              | インタフェース                     |     | SDA2 と共用です。出力形式は N チャネルオープンドレイン出力です。                                                                |

| P15/AD1/INT3,          | アナログ入力                      | 入力  | P10 , P15 ~ P17 端子は , それぞれアナログ入力端子 AD8 , AD1 ~ AD3 と共用です。                                           |

| P16/AD2,               | 外部割り込み                      | 入力  | P15 端子は,INT 外部割り込み入力端子 INT3 と共用です。                                                                  |

| P17/AD3                | 入力                          |     |                                                                                                     |

| P20/SCLK,              | 入出力ポート P2                   | 入出力 | ポート P2 は 8 ビットの入出力ポートでポート P0 とほぼ同等の機能を有しています。出力形式は                                                  |

| P21/SOUT,              |                             |     | CMOS 出力です。(注1)                                                                                      |

| P22/SIN,               | シリアル 1/0                    | 入出力 | P20 端子は,シリアル I/O 同期クロック入出力端子 Sclк と共用です。出力形式は N チャネル                                                |

| P23/TIM3,              | 同期クロック入出力                   |     | オープンドレイン出力です。                                                                                       |

| P24/TIM2,              | シリアル 1/0                    | 出力  | P21 端子は,シリアル I/O データ出力端子 SOUT と共用です。シリアル I/O 使用時、出力形式は                                              |

| P25,                   | データ出力                       |     | N チャネルオープンドレイン出力です。                                                                                 |

| P26/OSC1/              | シリアル 1/0                    | 入力  | P22 端子は , シリアル I/O データ入力端子 SIN と共用です。                                                               |

| XCIN,                  | データ入力                       |     |                                                                                                     |

| P27/OSC2/              | タイマ用外部                      | 入力  | P23, P24端子は, それぞれタイマ用外部クロック入力端子 TIM3, TIM2 と共用です。                                                   |

| Хсоит                  | クロック入力                      |     |                                                                                                     |

|                        | OSD 用クロック<br>入力             | 入力  | P26 端子は,OSD 用クロック入力端子 OSC1 と共用です。(注2)                                                               |

|                        | OSD 用クロック<br>出力             | 出力  | P27 端子は,OSD 用クロック入力端子 OSC2 と共用です。出力形式は、CMOS 出力です。(注2)                                               |

|                        | サブクロック<br>入力                | 入力  | P26 端子は,サブクロック入力端子 XCIN と共用です。(注2)                                                                  |

|                        | サブクロック<br>出力                | 出力  | P27 端子は,サブクロック入力端子 Хсоит と共用です。出力形式は、CMOS 出力です。                                                     |

#### 表 7.2 端子の機能説明(つづき)

| 端子名        | 名 称      | 入出力 | 機能                                                                |

|------------|----------|-----|-------------------------------------------------------------------|

| P30/AD5,   | 入出力ポートP3 | 入出力 | ポート P30, P31 は 2 ビットの入出力ポートです。ポート P0 とほぼ同等の機能を有しています。             |

| P31/AD6,   |          |     | 出力形式は、CMOS出力,又はNチャネルオープンドレイン出力のどちらかを選択できます。                       |

|            |          |     | (注1、3)                                                            |

|            | アナログ入力   | 入力  | P30, P31 端子は, それぞれアナログ入力端子 AD5, AD6 と共用です。                        |

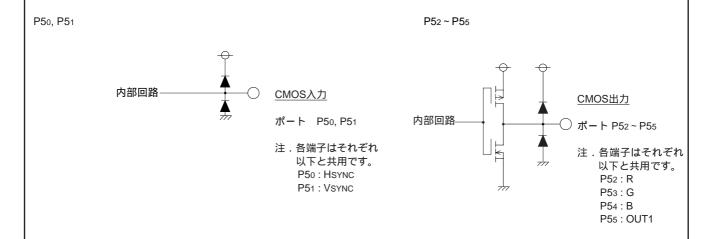

| P50/HSYNC, | 入力ポート P5 | 入力  | ポート P5 は2 ビットの入力ポートです。                                            |

| P51/VSYNC  | 水平同期信号   | 入力  | P50 端子は,OSD 用の水平同期信号入力端子 HSYNC と共用です。                             |

|            | 垂直同期信号   | 入力  | P51 端子は,OSD 用の垂直同期信号入力端子 VSYNC です。                                |

| P52/R,     | 出力ポート P5 | 出力  | P52 ~ P55 端子は , 4 ビットの出力ポートです。出力形式は CMOS 出力です。                    |

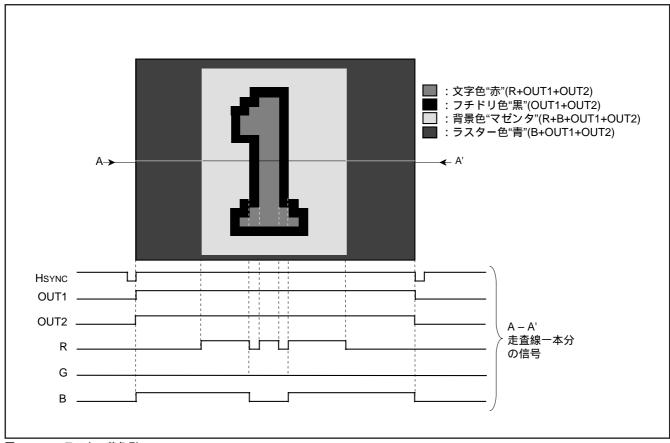

| P53/G,     | OSD 出力   | 出力  | P52~ P55 端子は , それぞれ OSD 出力端子 R , G , B , OUT1 と共用です。出力形式は CMOS 出力 |

| P54/B,     |          |     | です。                                                               |

| P55/OUT1   |          |     |                                                                   |

| CVIN       | データスライサ  | 入力  | コンデンサを介してコンポジットビデオ信号を入力してください。                                    |

| VHOLD      | 入出力      | 入力  | VHOLD と VSS の間にコンデンサを接続してください。                                    |

| HLF        |          | 入出力 | HLF と Vss の間にコンデンサと抵抗からなるフィルタを接続してください。                           |

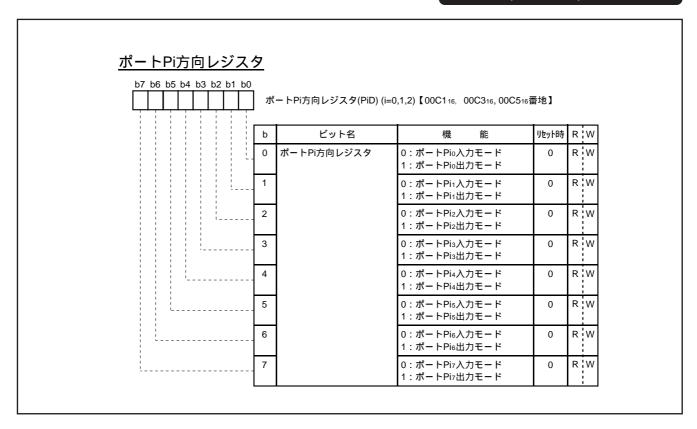

- 注1. ポートPi(i=0~3)はポートPi方向レジスタを持っており,入力として使用するか,出力として使用するか,ビット単位にプログラムできます。方向レジスタが"1"にプログラムされている端子は出力端子となります。"0"の場合は入力端子となります。出力端子としてプログラムされている端子に書き込んだデータはポートのラッチに書き込まれ,それがそのまま出力端子に出力されます。出力端子としてプログラムされている端子から読み込んだ場合は,出力端子の内容が読み込まれるのではなく,ポートのラッチの内容が読み込まれます。したがって発光ダイオードなどを直接駆動したため,出力"L"電圧が上がっていても以前に出力した値を正しく読むことができます。入力端子としてプログラムされている端子はフローティングとなり,端子の値を読み込むことができます。書き込んだ場合はポートのラッチに書き込まれるだけで端子はフローティングのままです。

- 2. 入出力ポートとの切り替えは,ラスターカラーレジスタ及び OSD コントロールレジスタで行います。また,P26, P27 を OSD 用のクロック入出力端子として使用する場合,ポート P2 方向レジスタの対応するビットを"0"(入力モード)にしてください。

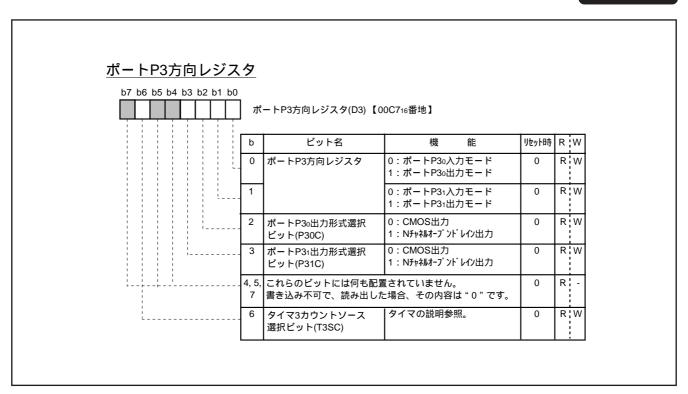

- 3. 出力形式の切り替えは , ポート P3方向レジスタのビット 2 , 3 で行います。" 0 " のときは , CMOS 出力 , " 1 " のときは N チャネルオープンドレイン出力になります。

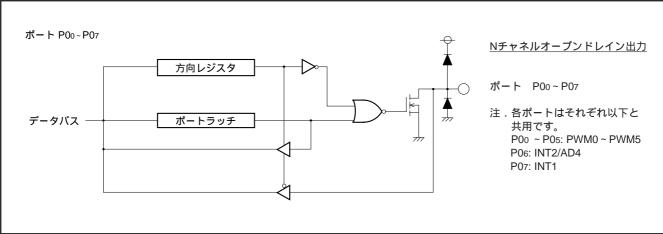

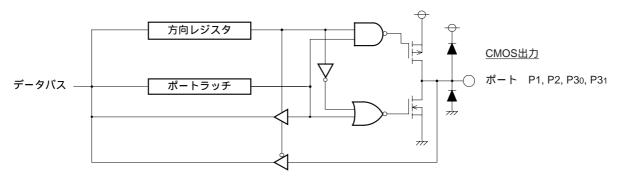

図 7.1 入出力端子のブロック図 (1)

#### ポート P1, P2, P30, P31

#### 注1. 各ポートはそれぞれ以下と共用です。

P10: OUT2 P20: SCLK P11: SCL1 P21: SOUT P12: SCL2 P22: SIN P13: SDA1 P23: TIM3 P14: SDA2 P24: TIM2 P15: AD1/INT3 P30: AD5 P16: AD2 P31: AD6 P17: AD3

- 2. ポートP30, P31の出力形式は、CMOS出力、又はNチャネルオープンドレイン出力のどちらかを選択できます。( Nチャネルオープ ンドレイン出力の場合は、P00~P07と同じです。)

- 3.ポートP11~P14は、マルチマスタI<sup>2</sup>C-BUSインタフェースとして使用時、Nチャネルオープンドレイン出力となります。(Nチャネ ルオープンドレイン出力の場合は、P00~P07と同じです。)

- 4.ポートP20, P21は、シリアル出力として使用時、Nチャネルオープンドレイン出力となります。( Nチャネルオープンドレイン出力 の場合は、P00~P07と同じです。)

図 7.2 入出力端子のブロック図(2)

#### 8. 機能ブロック動作説明

#### 8.1 中央演算処理装置(CPU)

本マイクロコンピュータは、740 ファミリ共通の CPU を 持っています。

各命令の動作については740ファミリアドレッシングモード及び機械語命令一覧表、又はMELPS 740 PROGRAM-MING MANUAL を参照ください。

品種に依存する命令については以下のとおりです。

- ・FST, SLW 命令はありません。

- ・MUL, DIV 命令が使用可能です。

- ・WIT命令が使用可能です。

- ・STP命令が使用可能です。

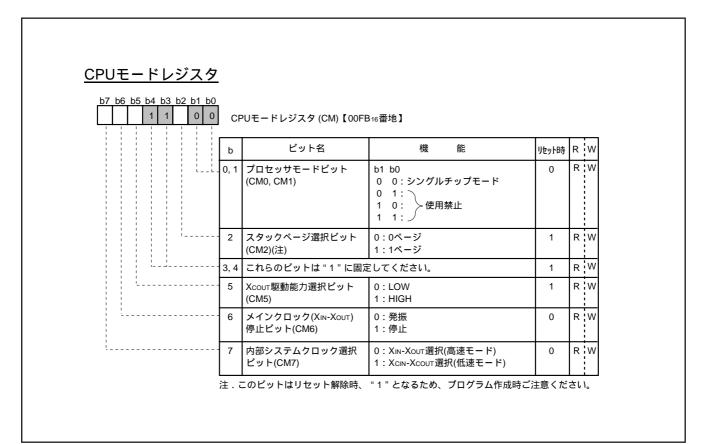

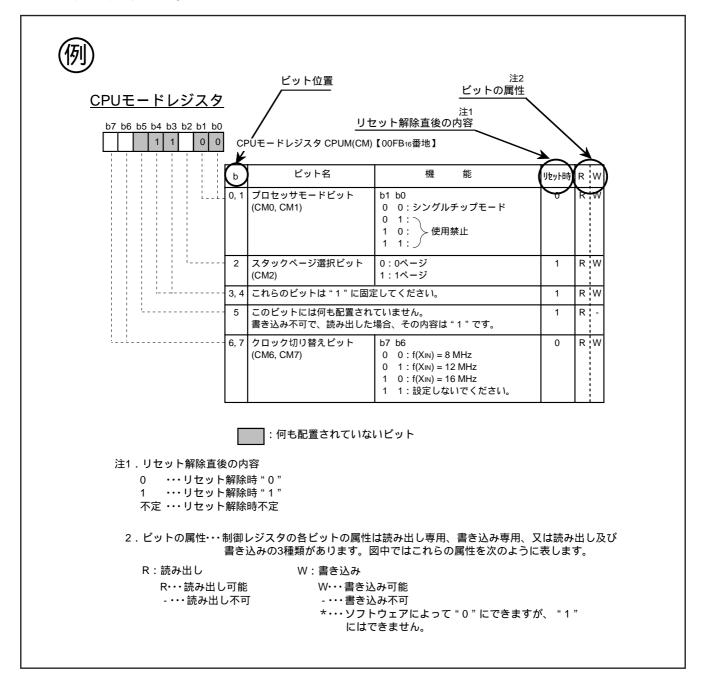

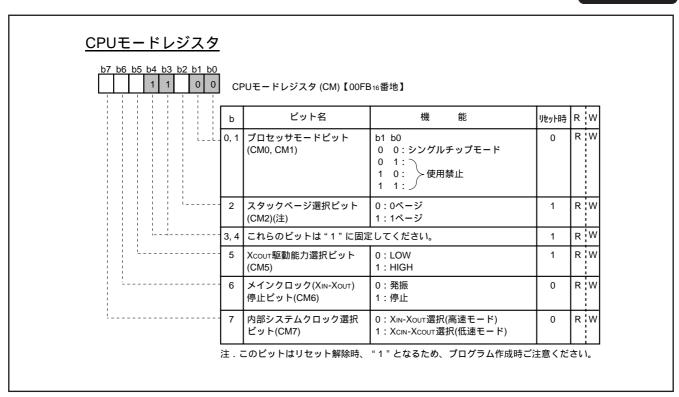

#### 8.1.1 CPU モードレジスタ

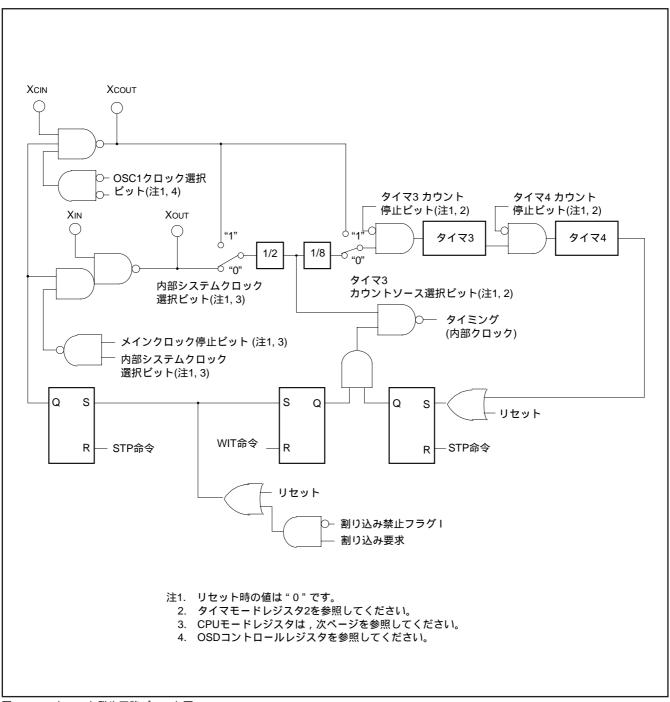

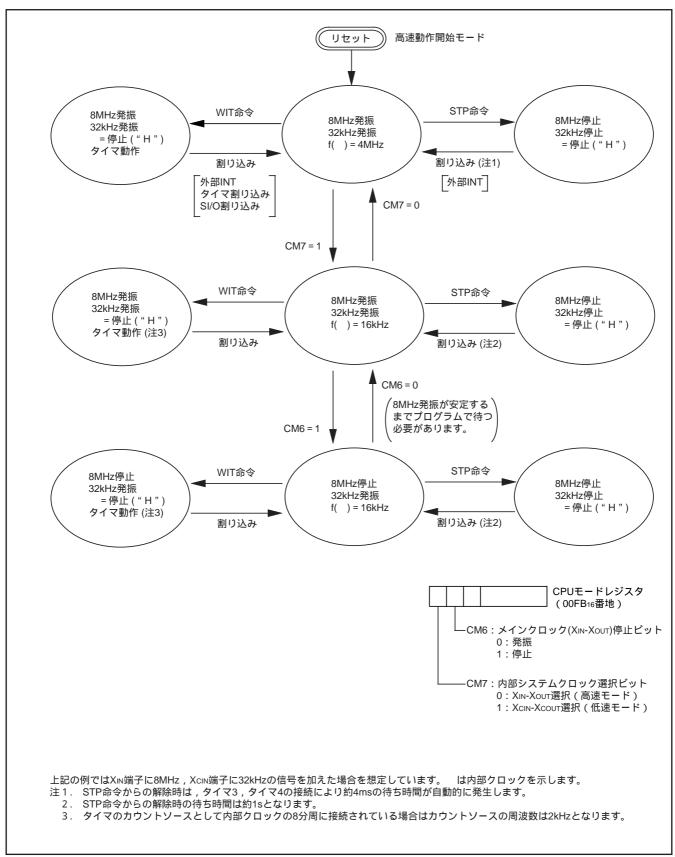

CPUモードレジスタには、スタックページの選択ビットやチップの内部システムクロックの選択ビットなどが割り当てられています。

このレジスタは00FB16番地に配置されています。

図 8.1.1 CPU モードレジスタ

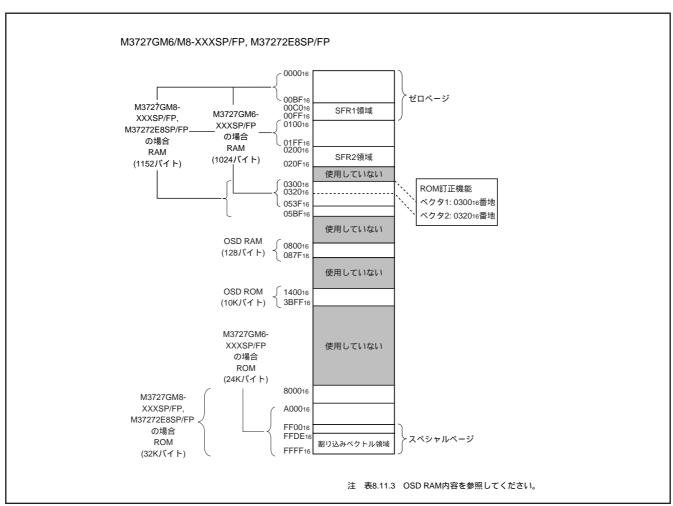

#### 8.2 メモリ

#### 8.2.1 SFR 領域

ゼロページ内にあり、入出力ポート、タイマなどの制御 レジスタが配置されています。

#### 8.2.2 RAM

データ格納、サブルーチン呼び出し及び割り込み時の スタックなどに使用します。

#### 8.2.3 ROM

ユーザプログラムや割り込みベクトルなどを格納します。

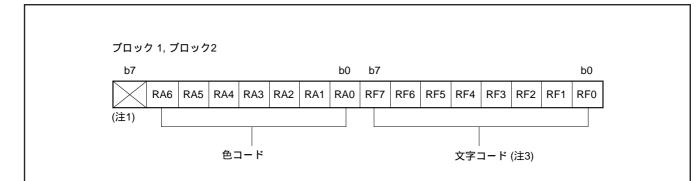

#### 8.2.4 OSD RAM

CRTに表示する文字コード、文字色などの指定データを格納します。

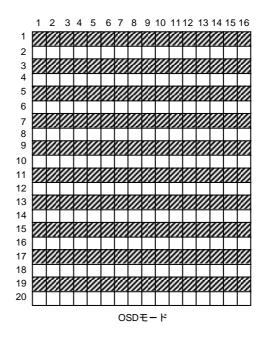

#### 8.2.5 OSD ROM

CRT に表示する文字データを格納します。

#### 8.2.6 割り込みベクトル領域

リセット及び割り込みのベクトル番地格納領域です。

#### 8.2.7 ゼロページ

ゼロページアドレッシングモードを使用することにより 2語でアクセスできる領域です。

#### 8.2.8 スペシャルページ

スペシャルページアドレッシングモードを使用することにより2語でアクセスできる領域です。

#### 8.2.9 ROM 訂正用ベクタ

ROM 訂正用のプログラム飛び先番地として使用します。

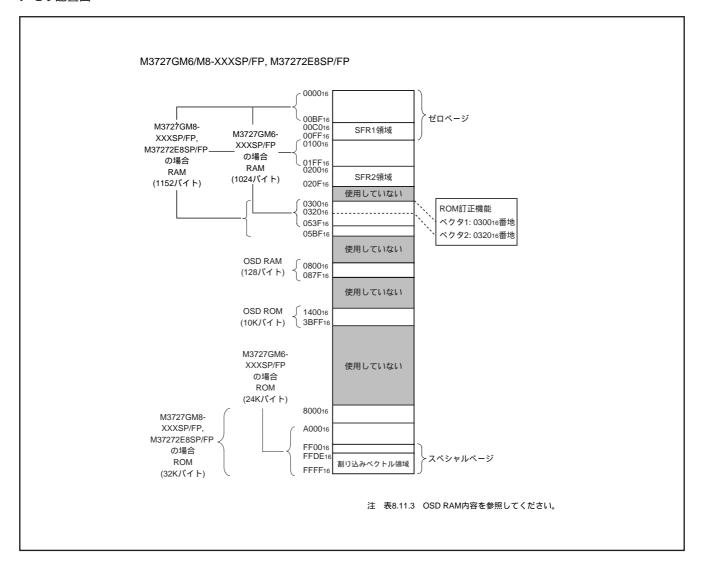

図 8.2.1 メモリ配置図 (M3727GM6/M8-XXXSP/FP, M37272E8SP/FP)

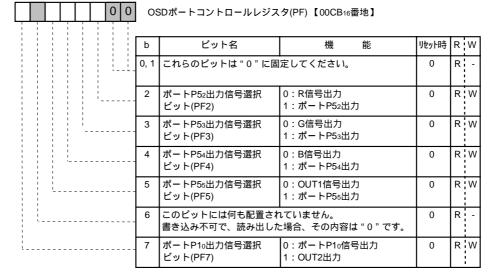

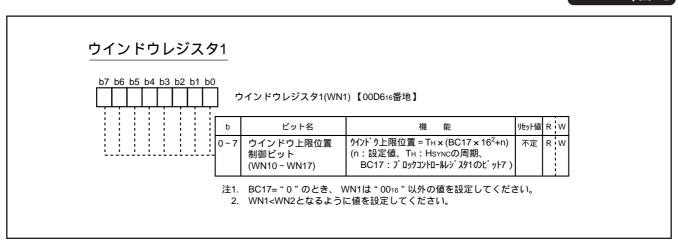

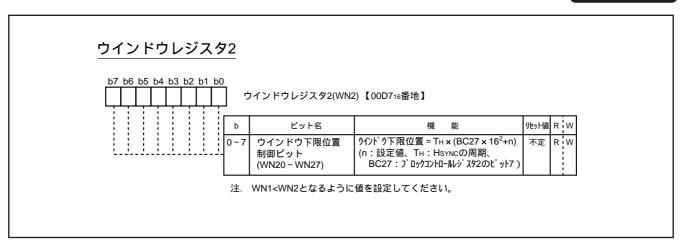

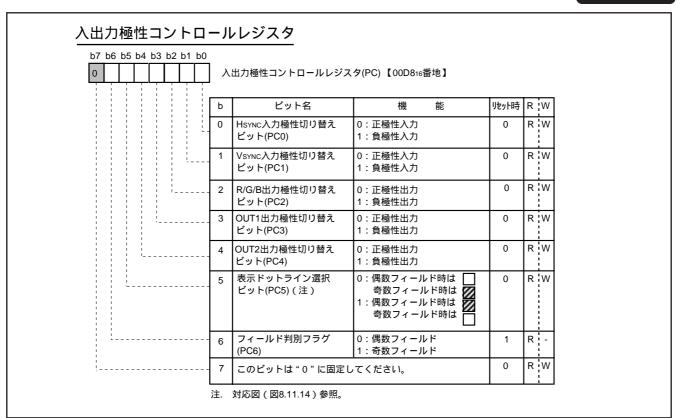

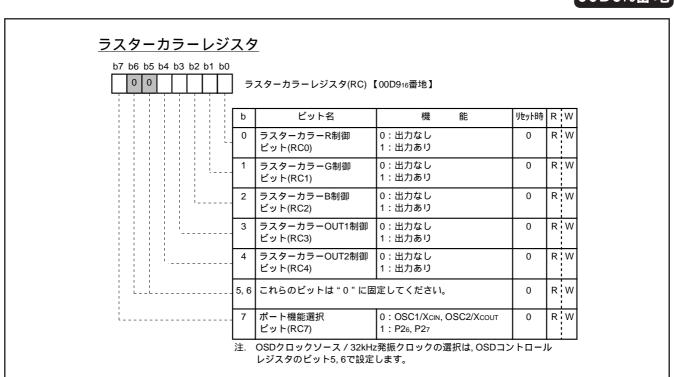

#### SFR1領域(C016~DF16番地) <リセット直後の状態> < ビット配置図 > 0 : リセット直後は " 0 " : ファンクションビットあり 1:リセット直後は"1" : ファンクションビットなし ?:リセット直後は不定 0 : "0"に固定してください。 ("1"を書き込まないでください。) 1 : "1"に固定してください。 ("0"を書き込まないでください。) 番地 レジスタ名 ビット配置図 リセット直後の状態 b0 b7 h7 b0 C0<sub>16</sub> ポートP0(P0) ? 0016 C1<sub>16</sub> ポートP0方向レジスタ(D0) C216 ポートP1(P1) ? 0016 C316 ポートP1方向レジスタ(D1) ? C4<sub>16</sub> ポートP2(P2) 0016 C5<sub>16</sub> ポートP2方向レジスタ(D2) P31 P30 0 0 0 0 0 ? C6<sub>16</sub> ポートP3(P3) P31CP30CP31DP30D C7<sub>16</sub> ポートP3方向レジスタ(D3) T3SC 0016 C8<sub>16</sub> C9<sub>16</sub> ? ? CA<sub>16</sub> ポートP<sub>5</sub>(P<sub>5</sub>) PF5 PF4 PF3 PF2 0 0 0016 PF7 CB<sub>16</sub> OSDポートコントロールレジスタ(PF) CC<sub>16</sub> 0016 0016 ? CD<sub>16</sub> CDL27CDL26CDL25CDL24CDL23CDL22CDL21CDL20 ? CE<sub>16</sub> キャプションデータレジスタ3(CD3) ? CF16 キャプションデータレジスタ4(CD4) CDH27CDH26CDH25CDH24CDH23CDH22CDH21CDH20 OC6 OC5 OC4 OC3 OC2 OC1 OC0 0016 D016 OSDコントロールレジスタ(OC) HP6 HP5 HP4 HP3 HP2 HP1 HP0 0016 D1<sub>16</sub> 水平位置レジスタ(HP) BC17 BC16 BC15 BC14 BC13 BC12 BC11 BC10 D216 ブロックコントロールレジスタ1(BC1) BC27 BC26 BC25 BC24 BC23 BC22 BC21 BC20 ? D3<sub>16</sub> ブロックコントロールレジスタ2(BC2) VP17 VP16 VP15 VP14 VP13 VP12 VP11 VP10 ? D416 垂直位置レジスタ1(VP1) ? VP27 VP26 VP25 VP24 VP23 VP22 VP21 VP20 D5<sub>16</sub> 垂直位置レジスタ2(VP2) ? WN17WN16WN15WN14WN13WN12WN11WN10 D616 ウインドウレジスタ1(WN1) WN27WN26WN25WN24WN23WN22WN21WN20 ? D716 ウインドウレジスタ2(WN2) PC6 PC5 PC4 PC3 PC2 PC1 PC0 4016 D816 入出力極性コントロールレジスタ(PC) 0 RC4 RC3 RC2 RC1 RC0 RC7 0 0016 D916 ラスタカラーレジスタ(RC) ? DA16 ? DB16 INT3 INT2 INT1 0016 DC16 割り込み入力極性レジスタ(RE) 0016 0016 DD<sub>16</sub> 0016 DE<sub>16</sub> 0016 0016 DF<sub>16</sub> ?

図8.2.2 SFR (スペシャルファンクションレジスタ) 1メモリマップ (1)

#### SFR1領域(E016~FF16番地) < ビット配置図 > <リセット直後の状態> 0 : リセット直後は " 0 " ファンクションビットあり 1: リセット直後は " 1 " : ファンクションビットなし | ? |: リセット直後は不定 0 : "0"に固定してください。 ("1"を書き込まないでください。) 1 : "1"に固定してください。 ("0"を書き込まないでください。) レジスタ名 ビット配置図 リセット直後の状態 番地 b0 b7 b7 b0 0 0 DSC12DSC11DSC10 EO<sub>16</sub> データスライサ制御レジスタ1(DSC1) 0016 0 E1<sub>16</sub> データスライサ制御レジスタ2(DSC2) DSC25DSC24DSC23 DSC20 ? 0 | ? ? 0 0 E216 キャプ ションデータレシ スタ1(CD1) CDL17 CDL16 CDL15 CDL14 CDL13 CDL12 CDL11 CDL10 0016 E316 キャプ ションデ ータレシ スタ2(CD2) CDH17CDH16CDH15CDH14CDH13CDH12CDH11CDH10 0016 CRD7CRD6CRD5CRD4CRD3 E416 クロックランイン検出レシ・スタ(CRD) 0016 DPS7 DPS6 DPS5 DPS4 DPS3 0 E5<sub>16</sub> データクロック位置レシ・スタ(DPS) 1 0 0916 CPS7 CPS6 CPS5 CPS4 CPS3 CPS2 CPS1 CPS0 0 0 E616 キャプション位置レジスタ(CPS) 0 0 | 0 0 E7<sub>16</sub> データスライサテストレジスタ2 0016 E816 データスライサテストレジスタ1 0016 HC5 HC4 HC3 HC2 HC1 HC0 0016 E916 同期信号カウンタレジスタ(HC) ? EA16 シリアルI/Oレジスタ(SIO) 0016 EB<sub>16</sub> シリアルI/Oモードレジスタ(SM) 0 SM6 SM5 0 SM3 SM2 SM1 SM0 ? 0 EC<sub>16</sub> AD制御レジスタ1(AD1) ADC14 ADC12ADC11ADC10 0 | 0 | 0 0 | 0 | 0 ADC25ADC24ADC23ADC22ADC21ADC20 0016 ED<sub>16</sub> AD制御レジスタ2(AD2) EE16 タイマ5(T5) 0716 FF<sub>16</sub> EF16 タイマ6(T6) F016 タイマ1(T1) FF<sub>16</sub> 0716 F1<sub>16</sub> タイマ2(T2) FF<sub>16</sub> F216 タイマ3(T3) 0716 F316 タイマ4(T4) F416 タイマモードレジスタ1(TM1) TM17 TM16 TM15 TM14 TM13 TM12 TM11 TM10 0016 TM27 TM26 TM25 TM24 TM23 TM22 TM21 TM20 F516 タイマモードレジスタ2(TM2) 0016 D7 D6 D5 D4 D3 D2 D1 D0 ? F616 I<sup>2</sup>Cデータシフトレジスタ(S0) SAD6 SAD5 SAD4 SAD2 SAD1 SAD0 RBW 0016 $F7_{16}$ $I^2$ Cアドレスレジスタ(S0D) SAD3 MST TRX BB PIN AL AAS ADO LRB 0 0 0 1 | 0 0 | 0 | F816 I<sup>2</sup>Cステータスレジスタ(S1) 10BIT BSEL1 BSEL0 ALS ESO BC2 BC1 BC0 0016 F916 I<sup>2</sup>Cコントロールレジスタ(S1D) CCR4|CCR3|CCR2|CCR1|CCR0 0016 FA16 I<sup>2</sup>Cクロックコントロールレシ・スタ(S2) BIT MODE CM2 3C<sub>16</sub> CM7 CM6 CM5 0 FB<sub>16</sub> CPUモードレジスタ(CPUM) 0016 |IN3R|VSCR|OSDR|TM4R|TM3R|TM2R|TM1F FC<sub>16</sub> 割り込み要求レジスタ1(IREQ1) 0 TM56R IICR IN2R CKR S1R DSR IN1R 0016 FD16 割り込み要求レジスタ2(IREQ2) FE<sub>16</sub> 割り込み制御レジスタ1(ICON1) IN3EVSCEOSDETM4ETM3ETM2ETM1E 0016 FF16 割り込み制御レジスタ2(ICON2) TM56CTM56E IICE IN2E CKE S1E DSE IN1E 0016

図8.2.3 SFR(スペシャルファンクションレジスタ)1メモリマップ(2)

#### SFR2領域(20016~20F16番地) <リセット直後の状態> <ビット配置図> \_\_\_: }ファンクションビットあり 0: リセット直後は "0" 1: リセット直後は"1" : ファンクションビットなし ?:リセット直後は不定 0 : "0"に固定してください。 ("1"を書き込まないでください。) 1 : "1"に固定してください。 ("0"を書き込まないでください。) レジスタ名 ビット配置図 リセット直後の状態 番地 b7 b0 b7 b0 200<sub>16</sub> PWM0レジスタ(PWM0) ? ? 201<sub>16</sub> PWM1レジスタ(PWM1) ? 20216 PWM2レジスタ(PWM2) ? 203<sub>16</sub> PWM3レジスタ(PWM3) 204<sub>16</sub> PWM4レジスタ(PWM4) ? 205<sub>16</sub> PWM5レジスタ(PWM5) 20616 0016 ? 0016 ? 20716 PM13 PM10 0 208<sub>16</sub> PWMモードレジスタ1(PM1) 0 M22 M21 M20 PM25 0016 209<sub>16</sub> PWMモードレジスタ2(PM2) 0016 20A<sub>16</sub> ROM訂正アドレス1(上位) 0016 20B<sub>16</sub> ROM訂正アドレス1(下位) 20C<sub>16</sub> ROM訂正アドレス2(上位) 0016 0016 20D<sub>16</sub> ROM訂正アドレス2(下位) RCR1 RCR0 0016 20E<sub>16</sub> ROM訂正許可レジスタ(RCR) ? 20F<sub>16</sub>

図8.2.4 SFR(スペシャルファンクションレジスタ)2メモリマップ

| <                  | 〈ビット配置図 >                                   | <リセット直後の状態>        |

|--------------------|---------------------------------------------|--------------------|

|                    | : }ファンクションビットあり                             | 0 : リセット直後は " 0 "  |

|                    | [ 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     | 1 : リセット直後は " 1 "  |

|                    | : ファンクションビットなし                              | ?: リセット直後は不定       |

|                    | 0 : "0"に固定してください。<br>("1"を書き込まないでください       | l <sub>o</sub> )   |

|                    | 1 : " 1 " に固定してください。<br>(" 0 " を書き込まないでください | ١, )               |

| レジスタ名              | ビット配置図<br>b7 b0                             | リセット直後の状態<br>b7 b0 |

| プロセッサステータスレジスタ(PS) | N V T B D I Z C                             | ? ? ? ? ? 1 ? ?    |

| プログラムカウンタ(РСн)     |                                             | FFFF16番地の内容        |

|                    |                                             | FFFE16番地の内容        |

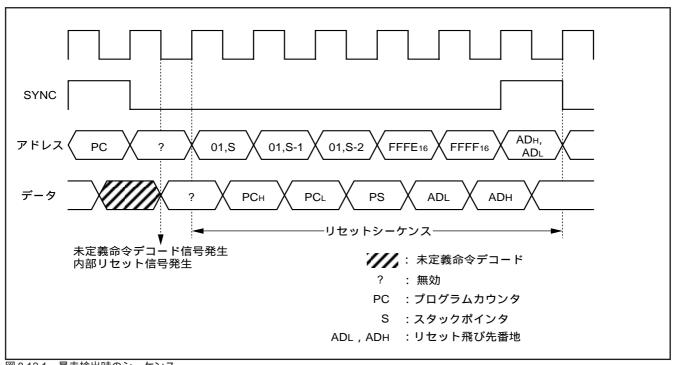

図 8.2.5 プロセッサステータスレジスタとプログラムカウンタのリセット時の内部状態

#### 8.3 割り込み

割り込みはベクトル割り込みで、外部4要因、内部11要因、 ソフトウエア1要因、及びリセットの17の要因から発生する ことが可能です。表 8.3.1 にベクトルテーブルと優先順位を 示します。リセットは割り込みと同じような動作をしますの で、この表中に入れておきます。

#### 割り込みを受け付けると、

プログラムカウンタとプロセッサステータスレジスタが 自動的にスタックへ待避されます。

割り込み禁止フラグ Iが"1"に、割り込み要求ビットが "0"になります。

ベクトル番地に格納されている飛び先番地がプログラム カウンタに入ります

リセットは何ものによっても禁止されることはありません。 これら以外の割り込みは割り込み禁止フラグ I が " 1 " のと き、受け付けられません。

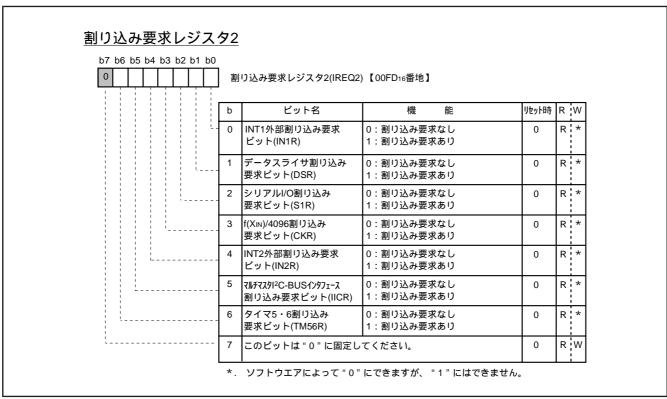

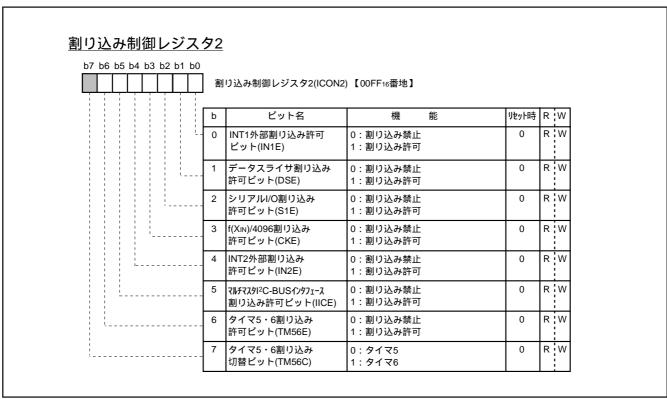

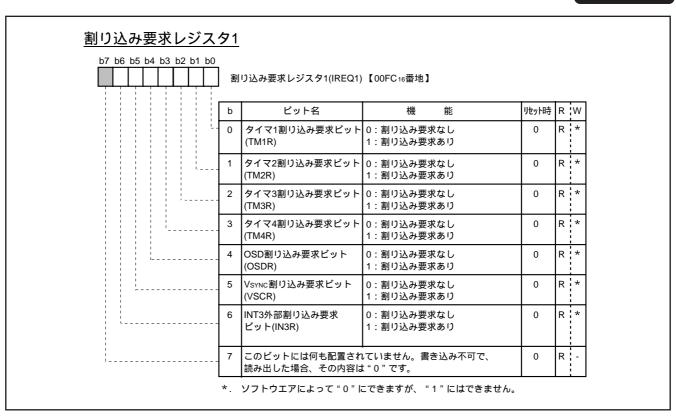

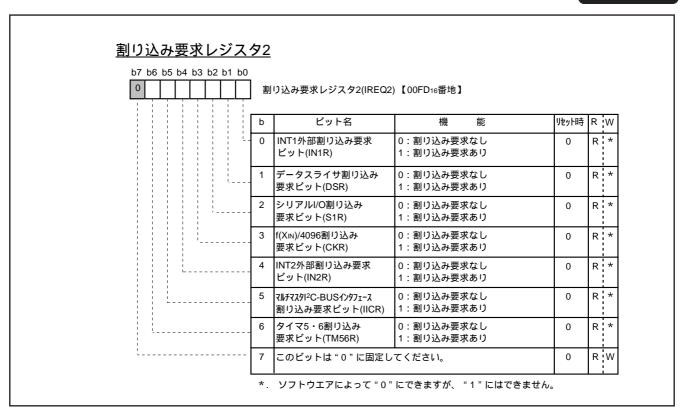

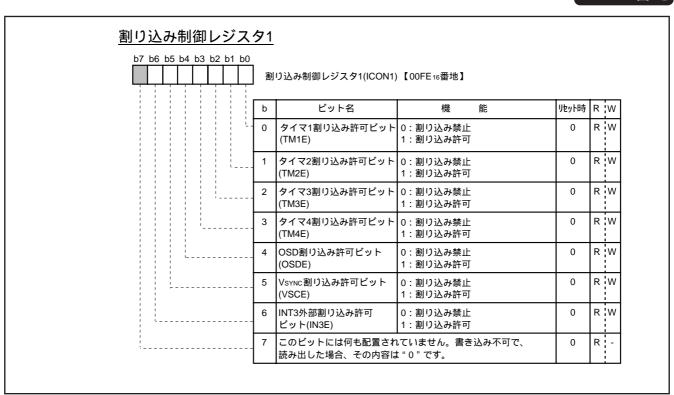

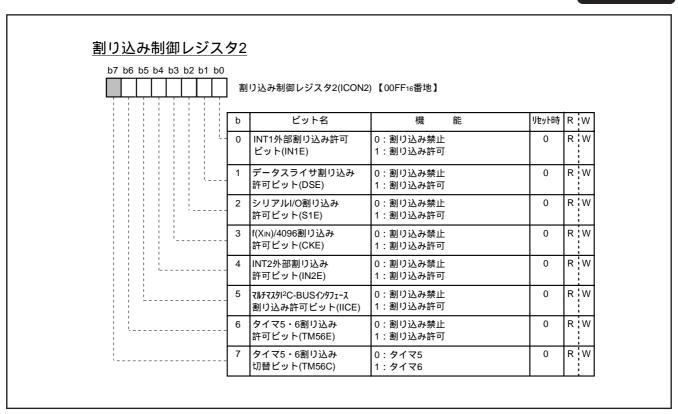

BRK 命令割り込みを除く各割り込みは、割り込み要求 ビットと割り込み許可ビットを持っています。割り込み要求 ビットは割り込み要求レジスタ1,2、割り込み許可ビットは 割り込み制御レジスタ1,2の各ビットに割り当てられていま す。割り込み関係レジスタを図8.3.2~図8.3.6に示します。

リセットと BRK 命令割り込みを除いた割り込みは、割り 込み許可ビットが"1"、割り込み要求ビットが"1"、かつ割 リ込み禁止フラグ Iが"0"のとき、受け付けられます。割り 込み要求ビットはプログラムで"0"にできますが、"1"

にはできません。割り込み許可ビットはプログラムで"0"又 は"1"にできます。

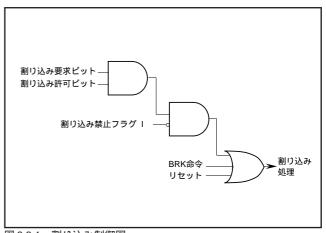

リセットは、割り込み優先順位中、最優先のノンマスカブ ル割り込みとして処理されます。図8.3.1 に割り込み制御図 を示します。

#### 8.3.1 割り込み要因

#### (1) VSYNC, OSD 割り込み

VSYNC割り込みは、垂直同期信号に同期した割り込み要求 です。

OSD 割り込みは、CRT への文字ブロック表示終了後に発 生する割り込みです。

#### (2) INT1 ~ INT3 外部割り込み

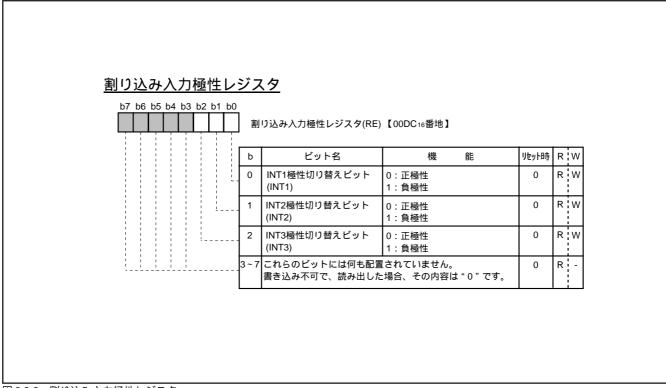

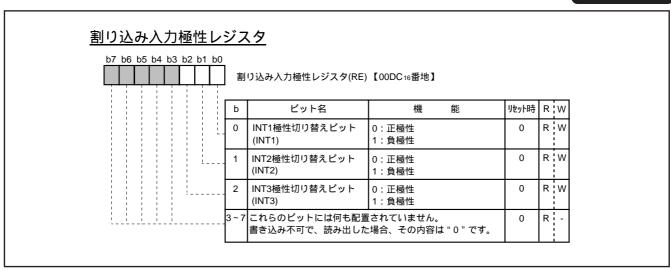

外部割り込み入力で、各端子のレベルが"L"から"H"、 又は"H"から"L"に変化するのを検出して割り込み要求を 発生します。入力極性は、割り込み入力極性レジスタ (00DC16番地)のビット0~ビット2によって選択されます。 これらのビットが"0"の場合"L"から"H"の変化、"1"の 場合"H"から"L"の変化が検出されます。ただし、リセッ ト時は"0"になります。

#### (3)タイマ1~4割り込み

タイマ1~4のオーバフローにより割り込みが発生します。

| 主 0 2 1 | 割り込みベク | トロ.来抽 | レ原生順位    |

|---------|--------|-------|----------|

| 衣 8.3.1 | 刮り込みハン | トル留地  | △1愛 元順1仏 |

| 優先 | 如小头,而口                                     | ベクトル番地 |                    | /# +*               |  |

|----|--------------------------------------------|--------|--------------------|---------------------|--|

| 順位 | 割り込み要因                                     | 上位     | 下位                 | 備考                  |  |

| 1  | リセット                                       | FFFF16 | FFFE16             | ノンマスカブル             |  |

| 2  | OSD割り込み                                    | FFFD16 | FFFC16             |                     |  |

| 3  | INT1 外部割り込み                                | FFFB16 | FFFA16             | 極性プログラマブル           |  |

| 4  | データスライサ割り込み                                | FFF916 | FFF816             |                     |  |

| 5  | シリアル I/O 割り込み                              | FFF716 | FFF616             |                     |  |

| 6  | タイマ4割り込み                                   | FFF516 | FFF416             |                     |  |

| 7  | f(XIN)/4096割り込み                            | FFF316 | FFF216             |                     |  |

| 8  | Vsync 割り込み                                 | FFF116 | FFF016             |                     |  |

| 9  | タイマ3割り込み                                   | FFEF16 | FFEE16             |                     |  |

| 10 | タイマ 2 割り込み                                 | FFED16 | FFEC16             |                     |  |

| 11 | タイマ 1 割り込み                                 | FFEB16 | FFEA <sub>16</sub> |                     |  |

| 12 | INT3 外部割り込み                                | FFE916 | FFE816             | 極性プログラマブル           |  |

| 13 | INT2 外部割り込み                                | FFE716 | FFE616             | 極性プログラマブル           |  |

| 14 | マルチマスタ l <sup>2</sup> C-BUS<br>インタフェース割り込み | FFE516 | FFE416             |                     |  |

| 15 | タイマ5・6割り込み                                 | FFE316 | FFE216             | ソフトウエアによる要因の切り換え(注) |  |

| 16 | BRK命令割り込み                                  | FFDF16 | FFDE16             | ノンマスカブル             |  |

注. プログラムの途中で要因切り換えを行うと不要な割り込みが発生します。そのため、要因の設定はプログラムの初期設定時に行ってくだ さい。

#### (4)シリアルI/O割り込み

クロック同期形シリアル I/O からの割り込み要求です。

#### (5) f(XIN)/4096 割り込み

f(XIN)の4096分周で割り込みが発生します。ただし、PWM モードレジスタ1のビット0を"0"に設定してください。

### (6) データスライサ割り込み

データスライスの終了時に割り込みが発生します。

# (7) マルチマスタ $I^2$ C-BUS インタフェース割り込み マルチマスタ $I^2$ C-BUS インタフェースに関する割り込み 要求です。

#### (8) タイマ5・6割り込み

タイマ5,6のオーバフローにより割り込みが発生します。 優先順位は同じで、ソフトウエアによって切り替えます。

# (9) BRK 命令割り込み

優先順位が最下位のソフトウエア割り込みで、対応した 割り込み許可ビットを持たず、割り込み禁止フラグ の影響 を受けません (ノンマスカブル)。

図8.3.1 割り込み制御図

#### 割り込み要求レジスタ1 b7 b6 b5 b4 b3 b2 b1 b0 割り込み要求レジスタ1(IREQ1) 【00FC16番地】 b ビット名 リセット時 IR W R¦\* タイマ1割り込み要求ビット 0:割り込み要求なし 0 (TM1R) 1:割り込み要求あり タイマ2割り込み要求ビット 0:割り込み要求なし R: 1:割り込み要求あり R : タイマ3割り込み要求ビット 0:割り込み要求なし (TM3R) 1:割り込み要求あり タイマ4割り込み要求ビット R 0:割り込み要求なし (TM4R) 1:割り込み要求あり OSD割り込み要求ビット R;\* 0:割り込み要求なし (OSDR) 1:割り込み要求あり R : \* Vsync割り込み要求ビット 0:割り込み要求なし 1:割り込み要求あり (VSCR) R¦\* INT3外部割り込み要求 0:割り込み要求なし ビット(IN3R) 1:割り込み要求あり このビットには何も配置されていません。書き込み不可で、 R 読み出した場合、その内容は"0"です。 \*. ソフトウエアによって"0"にできますが、"1"にはできません。

図 8.3.2 割り込み要求レジスタ 1

図8.3.3 割り込み要求レジスタ2

#### 割り込み制御レジスタ1 b7 b6 b5 b4 b3 b2 b1 b0 割り込み制御レジスタ1(ICON1)【00FE16番地】 機 能 ルット時 R ¦W ビット名 R W タイマ1割り込み許可ビット 0:割り込み禁止 1:割り込み許可 R W タイマ2割り込み許可ビット 0:割り込み禁止 1:割り込み許可 タイマ3割り込み許可ビット 0:割り込み禁止 R W 1:割り込み許可 タイマ4割り込み許可ビット 0:割り込み禁止 R¦W 1:割り込み許可 OSD割り込み許可ビット 0:割り込み禁止 R W 1:割り込み許可 Vsync割り込み許可ビット R W 0:割り込み禁止 1:割り込み許可 R¦W INT3外部割り込み許可 0:割り込み禁止 0 ビット(IN3E) 1:割り込み許可 このビットには何も配置されていません。書き込み不可で、 R¦-0 読み出した場合、その内容は"0"です。

図8.3.4 割り込み制御レジスタ1

図 8.3.5 割り込み要求レジスタ 2

図8.3.6 割り込み入力極性レジスタ

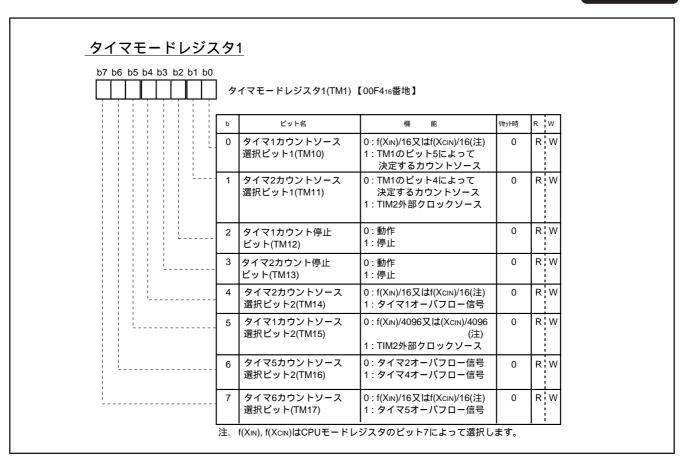

#### 8.4 タイマ

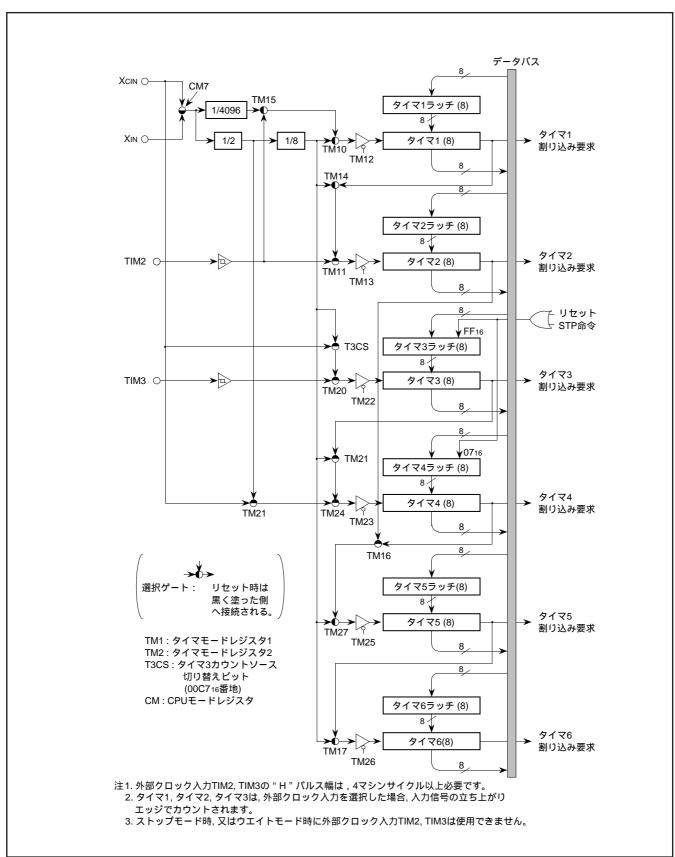

タイマは、タイマ1、タイマ2、タイマ3、タイマ4、タイマ5、タイマ6の6本あります。いずれもタイマラッチ付き8ビットタイマです。図8.4.3にタイマのブロック図を示します。

タイマ1~6は、すべてダウンカウント動作で分周比は 1/(n+1)です。これらのタイマは、タイマラッチ(00F016~00F316:タイマ1~タイマ4、00EE16,00EF16:タイマ5、タイマ6)に値を書き込むことで同時にタイマにも値が設定されます。

タイマへの設定直後からカウントソースの入力によって nn16-1 , nn16-2 , ... , 0116 , 0016 とダウンカウントし、タイマの値が 0016 となった次のカウントソース入力でオーバフローが起こり割り込み要求が発生します。

以下にそれぞれのタイマについて説明します。

#### 8.4.1 タイマ1

タイマ1のカウントソースは次のいずれかを選択できます。

- ・f(XIN)/16 又はf(XCIN)/16

- ・f(XIN)/4096 又はf(XCIN)/4096

- ・TIM2端子からの外部クロック

タイマモードレジスタ1(00F416番地)のビット5及びビット0の2ビットを用いていずれか一つを選択します。

また、f(XIN),f(XCIN)はCPUモードレジスタのビット7によって選択します。

タイマ1オーバフローによりタイマ1割り込み要求が発生します。

#### 8.4.2 タイマ2

タイマ2のカウントソースは次のいずれかを選択できます。

- ・f(XIN)/16 又はf(XCIN)/16

- ・タイマ1のオーバフロー信号

- ・TIM2 端子からの外部クロック

タイマモードレジスタ1(00F416番地)のビット4、ビット1の2ビットを用いてこの3種類から一つを選択します。また、f(XIN),f(XCIN)はCPUモードレジスタのビット7によって選択します。カウントソースをタイマ1のオーバフロー信号とすることで、タイマ1を8ビットプリスケーラとして用いることができます。

タイマ2オーバフローによりタイマ2割り込み要求が発生します。

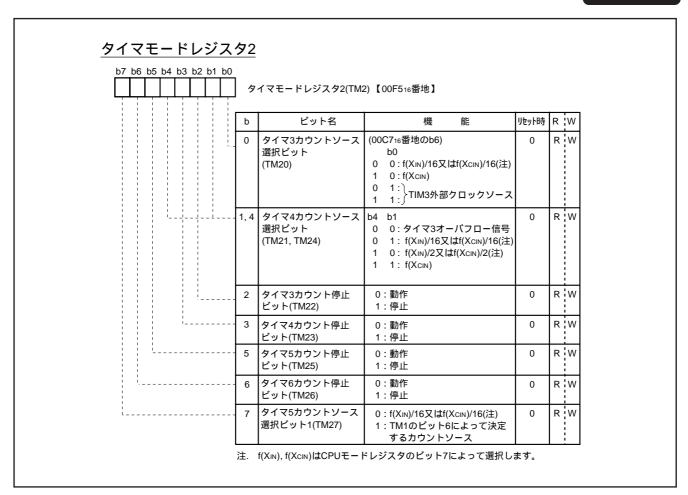

#### 8.4.3 タイマ3

タイマ3のカウントソースは次のいずれかを選択できます。

- ・f(XIN)/16 又はf(XCIN)/16

- f(XCIN)

- ・TIM3 端子からの外部クロック

タイマモードレジスタ2(00F516番地)のビット0,00C716番地のビット6の2ビットを用いてこの3種類から一つを選択します。また、f(XIN),f(XCIN)はCPUモードレジスタのビット7によって選択します。

タイマ3オーバフローによりタイマ3割り込み要求が発生します。

#### 8.4.4 タイマ4

タイマ 4 のカウントソースは次のいずれかを選択できま す。

- ・f(XIN)/16 又はf(XCIN)/16

- ・f(XIN)/2 又はf(XCIN)/2

- f(Xcin)

- ・タイマ3のオーバフロー信号

タイマモードレジスタ2(00F516番地)のビット4、及びビット1の2ビットを用いてこの4種類から一つを選択します。また、f(XIN), f(XCIN)はCPUモードレジスタのビット7によって選択します。カウントソースをタイマ3のオーバフロー信号とすることで、タイマ3を8ビットのプリスケーラとして用いることができます。

タイマ4オーバフローによりタイマ4割り込み要求が発生します。

#### 8.4.5 タイマ5

タイマ 5 のカウントソースは次のいずれかを選択できま す。

- ・f(XIN)/16 又はf(XCIN)/16

- ・タイマ2のオーバフロー信号

- ・タイマ4のオーバフロー信号

タイマモードレジスタ (00F416番地)のビット6、タイマモードレジスタ (00F516番地)のビット7の2ビットを用いてこの3種類から一つを選択します。カウントソースをタイマ2又はタイマ4のオーバフロー信号とすることで、タイマ2又はタイマ4を8ビットのプリスケーラとして用いることができます。f(XIN),f(XCIN)はCPUモードレジスタのビット7によって選択します。

タイマ5オーバフローによりタイマ5割り込み要求が発生 します。 8.4.6 タイマ 6

タイマ 6 のカウントソースは次のいずれかを選択できます。

- ・f(XIN)/16 又はf(XCIN)/16

- ・タイマ5のオーバフロー信号

タイマモードレジスタ1(00F416番地)のビット7を用いてこの2種類から一つを選択します。また、f(XIN), f(XCIN)はCPUモードレジスタのビット7によって選択します。カウントソースをタイマ5のオーバフロー信号とすることでタイマ5を8ビットのプリスケーラとして用いることができます。

タイマ6オーバフローによりタイマ6割り込み要求が発生します。

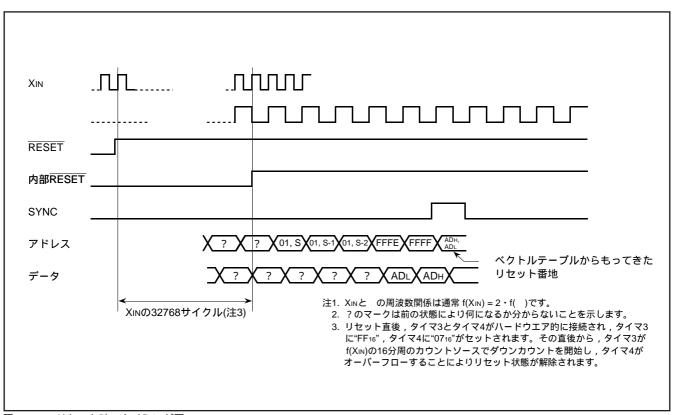

リセット時、タイマ3、タイマ4はハードウエア的に接続され、タイマ3に "FF16"、タイマ4に "0716"がセットされます。そして、タイマ3のカウントソースとしてf(XIN) \*/16が選択されます。この状態でのタイマ4オーバフローによって内部リセットが解除され、同時に内部クロックが供給されます。

STP 命令実行時、タイマ3、タイマ4はハードウエア的に接続され、タイマ3に"FF16"、タイマ4に"0716"がセットされますが、タイマ3のカウントソースとしてf(XIN)\*/16は選択されません。したがって、STP 命令を実行する前に、ソフトウエアによってタイマモードレジスタ2(00F516番地)のビット0及び00C716番地のビット6を"0"にしてください(タイマ3のカウントソースとしてf(XIN)\*/16を選択する)。この状態でのタイマ4オーバフローによってSTP状態が解除され、同時に内部クロックが供給されます。

以上の処理により、安定したクロックのもとでプログラムが開始されます。

\*: CPU モードレジスタのビット 7 (CM7)が "1" の場合は、 f(XIN)が f(XCIN)となります。

タイマに関連するレジスタのビット構成を図 8.4.1、図 8.4.2 に示します。

#### タイマモードレジスタ1 b7 b6 b5 b4 b3 b2 b1 b0 タイマモードレジスタ1(TM1)【00F416番地】 R !W ビット名 ルット時 タイマ1カウントソース 0: f(XIN)/16又はf(XCIN)/16(注) R¦W 0 選択ビット1(TM10) 1: TM1のビット5によって 決定するカウントソース R W タイマ2カウントソース 0: TM1のビット4によって 選択ビット1(TM11) 決定するカウントソース 1: TIM2外部クロックソース タイマ1カウント停止 0:動作 R¦W ビット(TM12) 1:停止 0 R; W 0:動作 タイマ2カウント停止 ビット(TM13) タイマ2カウントソース 0: f(XIN)/16又はf(XCIN)/16(注) R W 0 選択ビット2(TM14) 1:タイマ1オーバフロー信号 タイマ1カウントソース 0: f(Xin)/4096又は(Xcin)/4096 0 R¦W 選択ビット2(TM15) (注) 1 : TIM2外部クロックソース タイマ5カウントソース 0: タイマ2オーバフロー信号 R¦W 選択ビット2(TM16) 1: タイマ4オーバフロー信号 0: f(Xin)/16又はf(Xcin)/16(注) R W タイマ6カウントソース 0 選択ビット(TM17) 1: タイマ5オーバフロー信号 注. f(XIN), f(XCIN)はCPUモードレジスタのビット7によって選択します。

図 8.4.1 タイマモードレジスタ 1

#### タイマモードレジスタ2 b7 b6 b5 b4 b3 b2 b1 b0 タイマモードレジスタ2(TM2) 【00F516番地】 ビット名 Jセット時 R W タイマ3カウントソース (00C7<sub>16</sub>番地のb6) RW 0 選択ビット 0 0: f(Xin)/16又はf(Xcin)/16(注) (TM20) 1 0: f(Xcin) 0 1: TIM3外部クロックソース 1, 4 タイマ4カウントソース b4 b1 R W 0:タイマ3オーバフロー信号 選択ビット 0 (TM21, TM24) 0 1: f(Xin)/16又はf(Xcin)/16(注) 1 0: f(X<sub>IN</sub>)/2又はf(X<sub>CIN</sub>)/2(注) 1 1: f(Xcin) タイマ3カウント停止 0:動作 R W ビット(TM22) 1:停止 タイマ4カウント停止 0 R¦W 0:動作 ビット(TM23) 1:停止 タイマ5カウント停止 RW 0:動作 1:停止 ビット(TM25) タイマ6カウント停止 0:動作 RW 0 ビット(TM26) 1:停止 タイマ5カウントソース R W 0: f(Xin)/16又はf(Xcin)/16(注) 選択ビット1(TM27) 1:TM1のビット6によって決定 するカウントソース 注. f(XIN), f(XCIN)はCPUモードレジスタのビット7によって選択します。

図8.4.2 タイマモードレジスタ2

図8.4.3 タイマブロック図

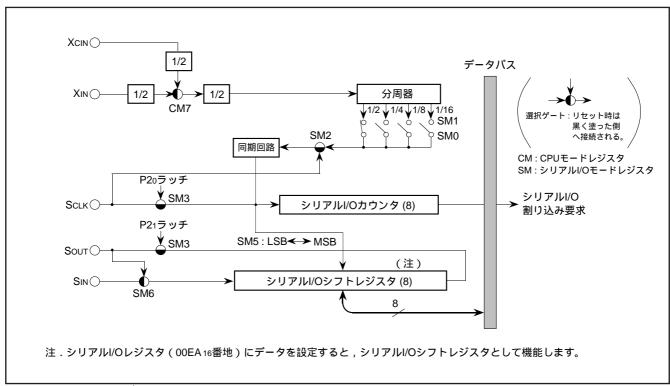

#### 8.5 シリアル1/0

本マイクロコンピュータは、クロック同期形で8ビットデータを直列に受信、又は送信できるシリアルI/Oを1本内蔵しています。

図 8.5.1 にシリアル I/O のブロック図を示します。同期クロック入出力端子(SCLK) データ出力端子(SOUT) データ入力端子(SIN)はポート P20~ P22 と共用しています。

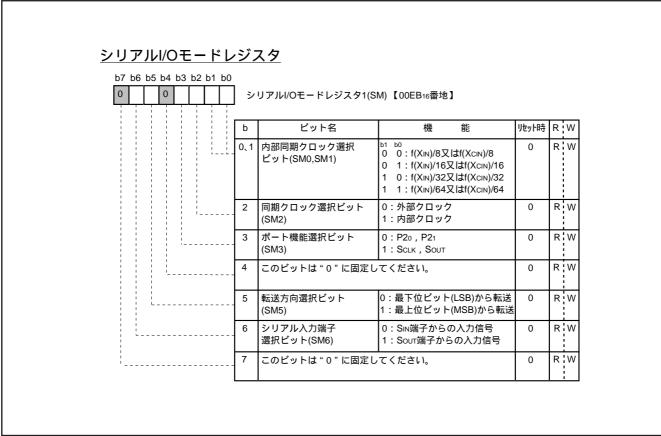

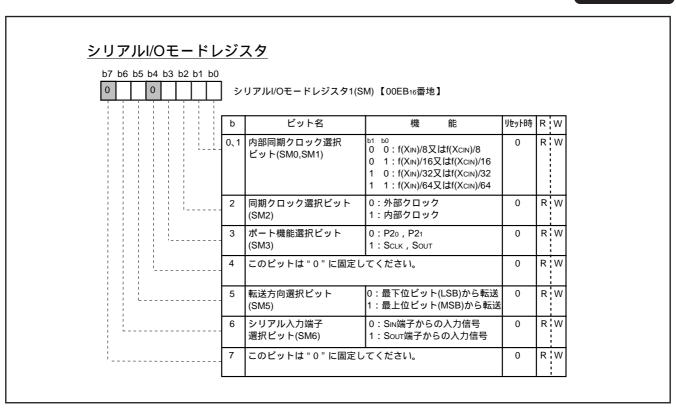

シリアル I/O モードレジスタ(00EB16番地)のビット2で同期クロックを内部から供給するか、外部(SCLK端子)から供給するかを選択します。内部クロックの場合ビット1とビット0でf(XIN)又はf(XCIN)の8分周、16分周、32分周、64分周のいずれかを選択します。シリアルI/O用端子として使用する場合、ポートP2方向レジスタ(00C516番地)のSIN端子に対応するビットを入力側"0")に設定してください。

次にシリアルI/Oの動作について説明します。クロック源として内部クロックを選択するか、外部クロックを選択するかで動作が異なります。

図 8.5.1 シリアル I/O のブロック図

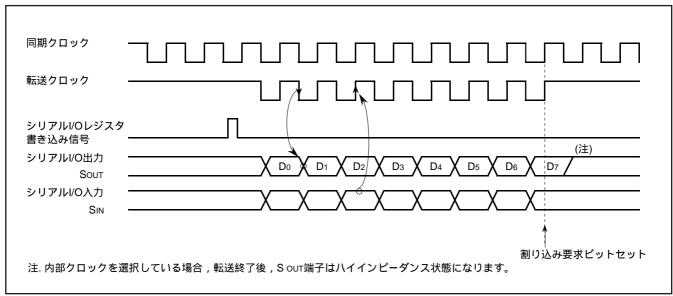

まず、内部クロックを選択した場合について説明します。シリアルI/Oレジスタ(00EA16番地)への書き込みサイクル中に、シリアルI/Oカウンタが"7"にセットされ、シリアルI/Oレジスタの転送クロックは強制的に"H"になります。書き込みサイクル終了後転送クロックの立ち下がりのたびに、SOUT端子からデータが出力されます。転送を最下位ビットから行うか、最上位ビットから行うかは、シリアルI/Oモードレジスタのビット5で選択します。また、受信時にはSIN端子から転送クロックの立ち上がりのたびにデータが取り込まれると同時に、シリアルI/Oレジスタの内容が1ビットずつシフトされます。

転送クロックを8回カウントするとシリアルI/Oカウンタは"0"となり、転送クロックは"H"の状態で停止し、割り込み要求ビットが"1"になります。

クロック源として外部クロックを選択した場合は転送クロックを8回カウントすると割り込み要求ビットは"1"になりますが、転送動作は禁止されませんので外部でクロックを制御してください。外部クロックはデューティサイクル50%で500kHz以下のクロックを使用してください。

図 8.5.2 にタイミングを示します。転送に外部クロックを用いる場合は、シリアルI/Oカウンタの初期化を行う際に外部クロックが"H"になっている必要があります。内部クロックと外部クロックを切り替えて使用する場合、転送を行っていないときに切り替えてください。また切り替えた後に必ずシリアルI/Oカウンタの初期化を行ってください。

- 注1. ビット処理命令(SEB命令, CLB命令)などによるシリアル I/O レジスタへの書き込みによっても,シリアルI/Oカウンタ がセットされるため,プログラム作成上注意が必要です。

- 2. 同期クロックとして外部クロックを選択した場合,転送クロックの入力レベルが"H"のときに,シリアルI/Oレジスタへ送信データを書き込んでください。

図 8.5.2 シリアル I/O タイミング

図 8.5.3 シリアル I/O モードレジスタ

####

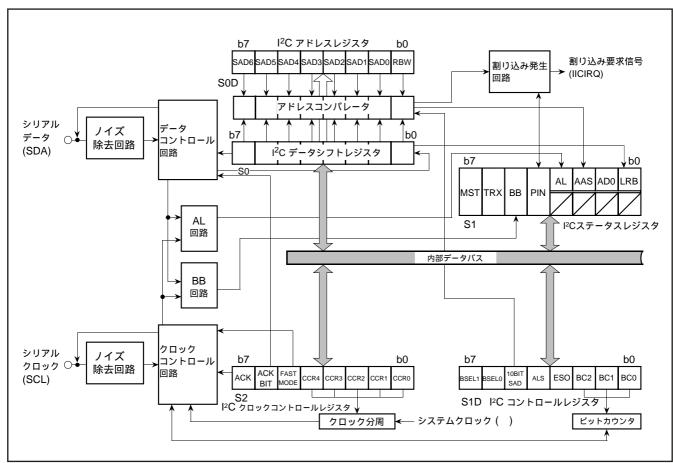

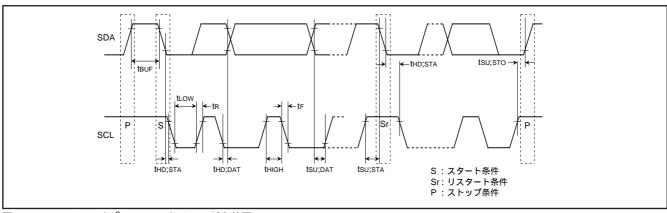

マルチマスタI<sup>2</sup>C-BUSインタフェースは、フィリップス社 I<sup>2</sup>C-BUSのデータ転送フォーマットに基づいてシリアル通信 を行う回路です。アービトレーション・ロストの検出機能、シンクロニアス機能を有しており、マルチマスタのシリアル 通信に対応できます。

図 8.6.1 にマルチマスタ  $I^2$ C-BUS インタフェースのブロック図、表 8.6.1 にマルチマスタ  $I^2$ C-BUS インタフェース機能を示します。

このマルチマスタ $I^2$ C-BUSインタフェースは、 $I^2$ Cアドレスレジスタ、 $I^2$ Cデータシフトレジスタ、 $I^2$ Cクロックコントロールレジスタ、 $I^2$ Cコントロールレジスタ、 $I^2$ Cステータスレジスタとその他の制御回路により構成されています。

表 8.6.1 マルチマスタ I<sup>2</sup>C-BUS インタフェース機能

| 項 目         | 機能                                                                                                       |

|-------------|----------------------------------------------------------------------------------------------------------|

| フォーマット      | フィリップス社 I <sup>2</sup> C-BUS 規格準拠<br>10 ビットアドレッシングフォーマット<br>7 ビットアドレッシングフォーマット<br>高速クロックモード<br>標準クロックモード |

| 通信モード       | フィリップス社 I <sup>2</sup> C-BUS 規格準拠<br>マスタ送信<br>マスタ受信<br>スレーブ送信<br>スレーブ受信                                  |

| SCL クロック周波数 | 16.1kHz ~ 400kHz ,( = 4 MHz)                                                                             |

- : システムクロック = f(XIN)/2

- 注. I<sup>2</sup>C-BUSインタフェースとポート(SCL1 SCL2 SDA1 SDA2) の接続を制御する機能 (I<sup>2</sup>C コントロールレジスタ [00F916 番地]のビット 6 , ビット 7 )の使用に起因する第三者の特許権その他の権利侵害については , 当社はその責任は負いません。

図 8.6.1 マルチマスタ I<sup>2</sup>C-BUS インタフェースのブロック図

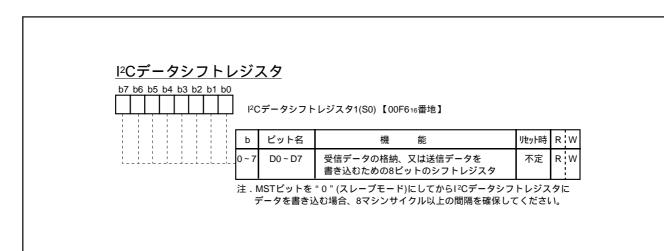

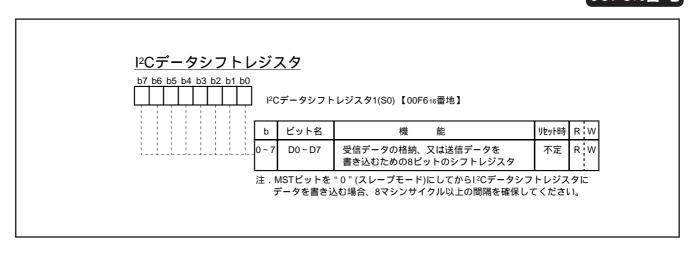

#### 8.6.1 I<sup>2</sup>C データシフトレジスタ

I<sup>2</sup>Cデータシフトレジスタ(S0:00F616番地)は、受信デー タの格納、又は送信データを書き込むための8ビットのシフ トレジスタです。

送信データをこのレジスタに書き込むと、SCLクロックに 同期してビット7から外部へ転送されます。そして、1ビッ トのデータが出力されるたびに、このレジスタの内容は左へ 1 ビットシフトされます。データ受信時は、SCL クロックに 同期してこのレジスタのビット0からデータが入力されま す。そして、1 ビットのデータが入力されるたびに、このレ ジスタの内容は左へ1ビットシフトされます。

I<sup>2</sup>C データシフトレジスタは、I<sup>2</sup>C コントロールレジスタ (00F916番地)のESOビットが"1"のときのみ書き込みが 可能です。I<sup>2</sup>C データシフトレジスタへの書き込み命令に よってビットカウンタがリセットされます。ESO ビットが " 1 ", I<sup>2</sup>C ステータスレジスタ ( 00F816 番地 ) の MST ビット が"1"のとき、I2Cデータシフトレジスタの書き込み命令 により、SCL が出力されます。I<sup>2</sup>C データシフトレジスタの 読み出しは、ESO ビットの値にかかわらずいつでも可能で す。

注. MST ビットを"0"(スレーブモード)にしてから I<sup>2</sup>C データ シフトレジスタにデータを書き込む場合,8マシンサイクル以 上の間隔を確保してください。

図 8.6.2 I<sup>2</sup>C データシフトレジスタ

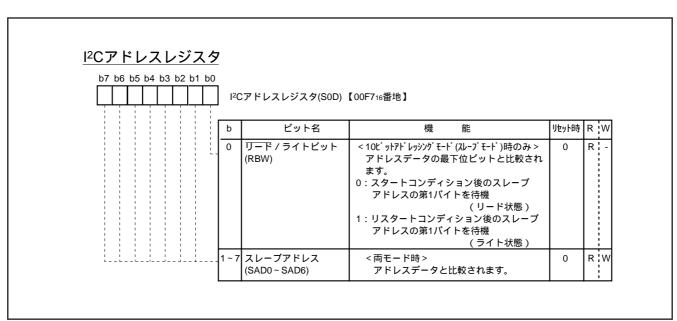

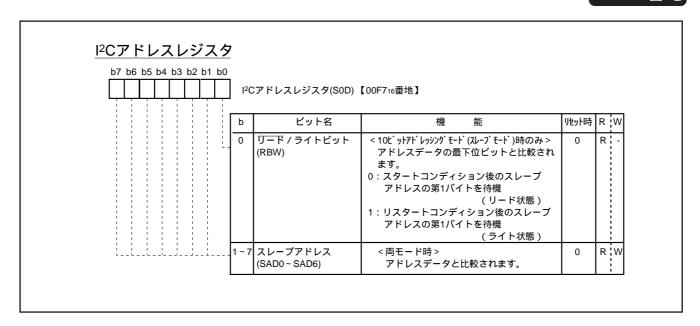

#### 8.6.2 I<sup>2</sup>C アドレスレジスタ

I<sup>2</sup>C アドレスレジスタ (00F716番地)は7 ビットのスレー ブアドレスと 1 ビットの リード/ライトビットにより構成さ れます。アドレッシングモード時は、このレジスタに書き込 まれたスレーブアドレスと、スタートコンディションを検出 した直後に受信するアドレスデータとを比較します。

#### (1) $\vec{U}$ $\vec{V}$ $\vec{V}$

7 ビットアドレッシングモード時には、アドレス比較の際 に使用されません。10ビットアドレッシングモード時には、 受信した1バイト目のアドレスデータとI<sup>2</sup>Cアドレスレジス タの内容 (SAD6 ~ SAD0 + RBW) が比較されます。

RBW ビットはストップコンディションを検出すると、自 動的に"0"になります。

(2)ビット1~ビット7:スレーブアドレス(SAD0~SAD6) スレーブアドレスを格納するビットです。 7 ビットアド レッシングモード、10ビットアドレッシングモードにかかわ らず、マスタから送信されるアドレスデータとこれらのビッ トの内容が比較されます。

図 8.6.3 I<sup>2</sup>C アドレスレジスタ

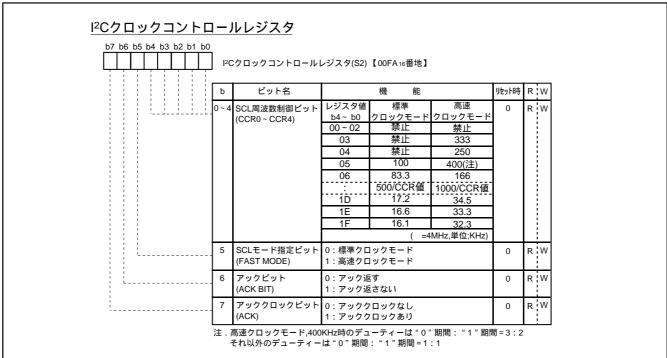

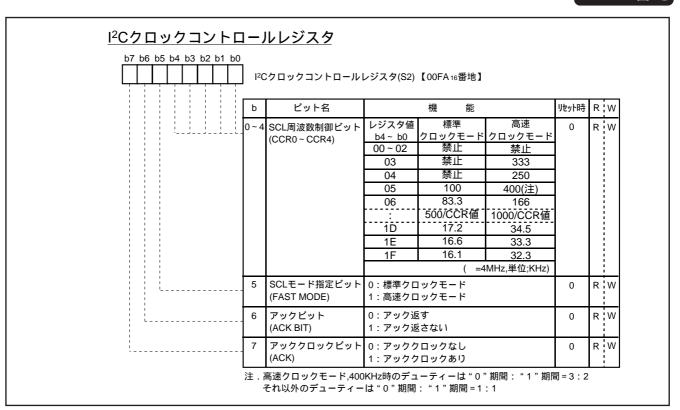

8.6.3  $I^{2}C$  クロックコントロールレジスタ

$I^{2}C$  クロックコントロールレジスタ (00FA16 番地) はアックの制御、SCL モード、SCL の周波数を設定するレジスタです。

(1) ビット 0 ~ ビット 4: SCL 周波数制御ビット (CCR0 ~ CCR4)

SCL 周波数を制御するビットです。

(2) ビット 5: SCL モード指定ビット (FAST MODE ) SCL モードを指定するビットです。" 0 " の場合、標準クロックモードになります。" 1 " の場合、高速クロックモードになります。

#### (3) ビット6: アックビット(ACK BIT)

アッククロック\*発生時のSDAの状態を設定します。"0"の場合はアックを返すモードとなり、アッククロック発生時に SDA を"L"にします。"1"の場合はアックを返さないモードとなり、アッククロック発生時に SDA を"H"の状態に保持します。

ただし、ACK BIT = "0"の状態で、アドレスデータを受信するとき、スレープアドレスとアドレスデータが一致した場合は自動的に SDA を"L"にします(アックを返します)。 スレープアドレスとアドレスデータが一致しなかった場合は自動的に SDA を"H"にします(アックを返しません)。

\*アッククロック:確認応答用のクロック

#### (4) ビット7: アッククロックビット (ACK)

データ転送の確認応答であるアクノリッジメントのモードを指定するビットです。"0"の場合、アッククロックなしモードになり、データ転送後にアッククロックは発生しません。"1"の場合はアッククロックありのモードになり、1バイトのデータ転送が完了するたびに、マスタはアッククロックを発生します。アドレスデータ、制御データを送信するデバイスは、アッククロック発生時にSDAを解放し("H"の状態にする)、データを受信するデバイスが発生させるアックビットを受信します。

注. I<sup>2</sup>Cクロックコントロールレジスタの書き込みを転送途中で行わないでください。転送途中に書き込みを行うとI<sup>2</sup>Cクロックジェネレータがリセットされ,データが正常に転送できません。

図 8.6.4 I<sup>2</sup>C クロックコントロールレジスタ

#### 8.6.4 I<sup>2</sup>C コントロールレジスタ

$I^{2}C$  コントロールレジスタ ( 00F916 番地 ) はデータ通信 フォーマットの制御を行うレジスタです。

#### (1)ビット0~ビット2:ビットカウンタ(BC0~BC2)

次に転送されるデータ1バイト分のビット数を決定する ビットです。割り込み要求信号は、これらのビットで指定さ れたビット数の転送完了直後に発生します。

スタートコンディションを受信すると、これらのビットは "0002"になり、アドレスデータは必ず8ビットで送受信されます。

# (2)ビット3:I<sup>2</sup>C インタフェース使用許可ビット(ESO)

マルチマスタ  $I^2$ C-BUS インタフェースの使用を許可する ビットです。"0"の場合使用禁止状態で、SDA 及び SCL は ハイインピーダンスになります。"1"の場合、使用許可と なります。

ESO = "0"のとき、次のように処理されます。

- ・ I<sup>2</sup>C ステータスレジスタ ( 00F816 番地 ) の PIN = " 1", BB = " 0", AL = " 0"に設定される。

- ・ I<sup>2</sup>C データシフトレジスタ (00F616 番地) への書き込みは 禁止される。

#### (3)ビット4:データフォーマット選択ビット(ALS)

スレープアドレスの認識を行うか否かを決定するビットです。"0"の場合はアドレッシングフォーマットとなり、アドレスデータを認識します。そして、スレープアドレスとアドレスデータとを比較して一致した場合、又はジェネラルコール(「8.6.5 I<sup>2</sup>Cステータスレジスタ」のビット1参照)を受信したときのみ転送処理が行えます。"1"の場合はフリーデータフォーマットとなり、スレープアドレスを認識しません。

# (4) ビット5: アドレッシングフォーマット選択ビット (10BIT SAD)

スレーブのアドレス指定フォーマットを選択するビットです。"0"の場合は7ビットアドレッシングフォーマットとなり、I<sup>2</sup>Cアドレスレジスタ(00F716番地)の上位7ビット(スレーブアドレス)のみアドレスデータと比較されます。"1"の場合には10ビットアドレッシングフォーマットとなり、I<sup>2</sup>Cアドレスレジスタの全ビットがアドレスデータと比較されます。

(5) ビット6、ビット7: I<sup>2</sup>C-BUS インタフェースとポート の接続制御ビット(BSEL0, BSEL1)

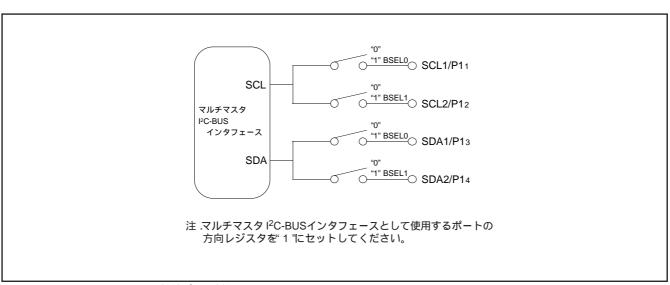

マルチマスタ $I^2$ C-BUSインタフェースのSCL ,SDA とポートの接続を制御するビットです(図 8.6.5 参照),

図 8.6.5 BSEL0 , BSEL1 による接続ポート制御

#### I<sup>2</sup>Cコントロールレジスタ b7 b6 b5 b4 b3 b2 b1 b0 I<sup>2</sup>Cコントロールレジスタ(S1D) 【00F916番地】 R¦W b ビット名 機 能 ルット時 b2 b1 b0 0 0 0 :8 ビットカウンタ R W (送/受信ビット数) 0 0 1:7 (BC0 ~ BC2) 0 1 0:6 0 1 1:5 0 0:4 1 0 1:3 1 1 0:2 1 1 1:1 3 I<sup>2</sup>C-BUSインタフェース 0:使用禁止 R W 0 使用許可ビット(ESO) 1:使用許可 データフォーマット選択ビット 0 : アドレッシングフォーマット 4 0 R W 1 : フリーデータフォーマット 5 アドレッシングフォーマット 0 : 7ビットアドレッシングフォーマット RW 0 選択ビット(10BIT SAD) 1 : 10ビットアドレシングフォーマット b7 b6 接続ポート I<sup>2</sup>C-BUSインタフェースと (注) RW 0 0 0:なし ポートの接続制御ビット 0 1: SCL1,SDA1 (BSEL0,BSEL1) 1 0: SCL2,SDA2 1 1: SCL1,SDA1,SCL2,SDA2

図 8.6.6 I<sup>2</sup>C コントロールレジスタ

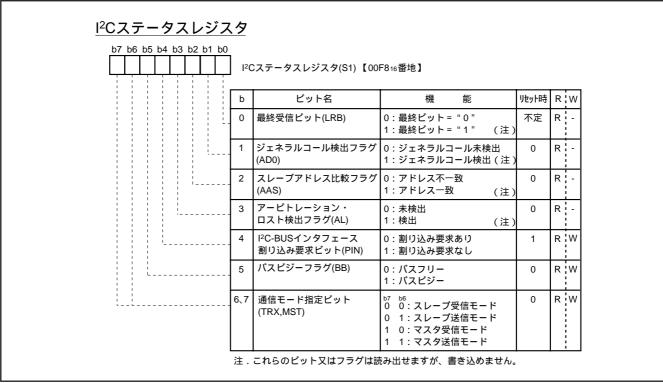

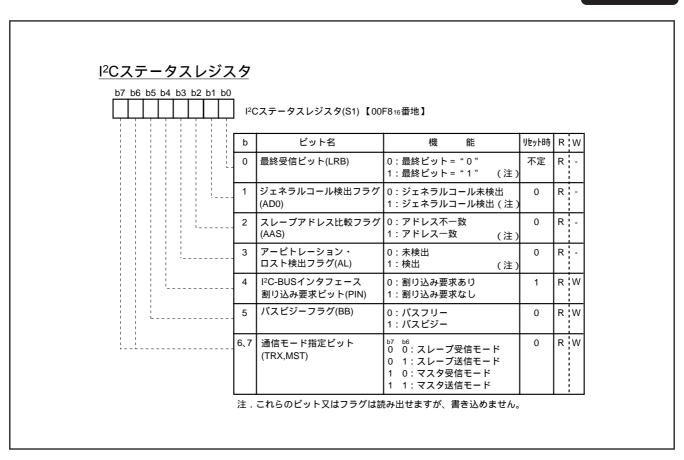

# 8.6.5 I<sup>2</sup>C ステータスレジスタ

1<sup>2</sup>C ステータスレジスタ (00F816 番地)は I<sup>2</sup>C-BUS インタフェースの状態を制御するレジスタです。下位 4 ビットは読み出し専用で、上位 4 ビットは読み出し/書き込み可能です。

# (1) ビット 0: 最終受信ビット (LRB)

受信したデータの最終ビットの値を格納するビットで、アックの受信確認に使用可能です。アッククロック発生時に、アックが返ってきた場合、LRBビットは"0"になります。アックが返らなかった場合は"1"になります。アックモードでない場合は受信データの最終ビットの値が入力されます。I<sup>2</sup>Cデータシフトレジスタ(00F616番地)に書き込み命令を実行すると"1"から"0"になります。

# (2) ビット1: ジェネラルコール検出フラグ(AD0)

アドレスデータがすべて"0"であるジェネラルコール<sup>1</sup>をスレープモード時に受信したときに"1"になります。マスタデバイスがジェネラルコールを発信することにより、ジェネラルコール後の制御データはすべてのスレーブデバイスに受信されます。AD0ビットはストップコンディション、スタートコンディションの検出により"0"になります。

\* ジェネラルコール:マスタが全スレーブにジェネラルコー ルアドレス " 0016 " を送信すること。

# (3) ビット 2: スレーブアドレス比較フラグ (AAS) アドレスデータの比較結果を示すフラグです。

スレーブ受信モード時、7ビットアドレッシングフォーマットでは、以下のいずれかの条件で、"1"になります。

- ・スタートコンディション発生直後のアドレスデータが I<sup>2</sup>Cアドレスレジスタ(00F716番地)に格納されている 上位7ビットのスレープアドレスと一致した場合

- ・ジェネラルコールを受信した場合

スレープ受信モード時、10 ビットアドレッシングフォーマットでは、以下の条件で"1"になります。

・アドレスデータとI<sup>2</sup>Cアドレスレジスタ(スレーブアドレス、及びRBWビットで構成される8ビット)とを比較し、1バイト目が一致した場合

このビットは $I^2$ C データシフトレジスタ (00F616番地)に書き込み命令を行うことにより"1"から"0"になります。

(4) ビット3:アービトレーションロスト\*検出フラグ(AL) マスタ送信モード時、SDAがマイコン以外の装置によって "L"レベルにされた場合、アービトレーションを失ったと判 定し、このビットは"1"になります。同時にTRX ビットは"0"になるため、アービトレーションを失ったバイトの送信が完了した直後に、MSTビットが"0"になります。スレーブアドレス送信中にアービトレーションを失った場合、TRX ビットが"0"になり、受信モードとなります。そのため、別のマスタデバイスにより送信される自分自身のスレーブアドレスを受信し、認識することが可能になります。

\*アービトレーションロスト:マスタとしての通信が不許可となった状態。

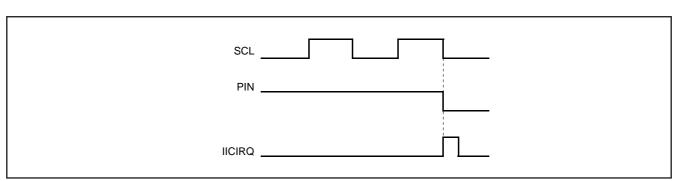

# (5)ビット4: I<sup>2</sup>C-BUS インタフェース割り込み要求ビット (PIN)

割り込み要求信号を発生させるビットです。 1 バイトのデータ通信完了ごとに、PIN ビットは"1"から"0"になります。同時に CPU へ割り込み要求信号が発生します。PIN ビットは内部クロックの最終クロック(アッククロックを含む)の立ち下がりに同期して"0"になり、割り込み要求信号はPINビットの立ち下がりに同期して発生します。スレーブ時は、ストップコンディションを検出すると、PIN ビットの立ち下がりに関係なく、マルチマスタ I<sup>2</sup>C-BUS インタフェース割り込み要求ビット(IR)は"0"から"1"(要求あり)になります。PIN ビットが"0"のときは SCL は"0"に保たれクロックの発生は禁止されます。図 8.6.8 に割り込み要求信号の発生タイミングを示します。

以下のいずれかの条件でPIN ビットが"1"になります。

- ・PIN ビットへの "1" 書き込み

- ・I<sup>2</sup>C データシフトレジスタ (00F616 番地) への書き込み命 令の実行(注)

- ・ESO ビットが"0"のとき

- ・リセット時

- 注. これらのレジスタへの書き込み命令実行後、PIN ビットが"1"になるまで8BCLK サイクル以上要します。

PIN ビットが"0"になる条件を以下に示します。

- ・1 バイトのデータ送信完了直後(アービトレーションロストを検出した場合を含む)

- ・1 バイトのデータ受信完了直後

- ・スレーブ受信の際、ALS = 0 で、スレーブアドレス又は ジェネラルコールアドレス受信完了直後

- ・スレーブ受信の際、ALS = 1 で、アドレスデータ受信完了 直後

# (6) ビット5:バスビジーフラグ(BB)

バスシステムの使用状態を示すビットです。"0"の場合、このバスシステムは使用されておらず、スタートコンディションを発生させることが可能です。"1"の場合、このバスシステムは使用されており、スタートコンディションの発生はスタートコンディション重複防止機能(注)によって禁止されます。

このフラグはマスタ送信時のみ、ソフトウエアによる書き込みが可能です。マスタ送信以外のモードでは、スタートコンディションの検出により"1"になり、ストップコンディションの検出により"0"になります。また、 $I^2C$ コントロールレジスタ(00F916番地)のESOビットが"0"の場合、及びリセット時にはBBフラグは"0"に保持されます。

(7) ビット6:通信モード指定ビット(転送方向指定ビット: TRX)

データ通信の転送方向を決定するビットです。"0"の場合、受信モードとなり、送信デバイスのデータを受信します。"1"の場合、送信モードとなり、SCL上に発生するクロックに同期してSDA上にアドレスデータ、制御データを出力します。

$I^2C$  コントロールレジスタ ( 00F916 番地 ) の ALS ビットが " 0 " でスレーブの場合、マスタから送信されたアドレス データの最下位ビット ( R/W ビット ) が " 1 "のときは TRX ビットは " 1 " ( 送信 ) になります。 ALS ビットが " 0 " で R/W ビットが " 0 " のときは TRX ビットは " 0 " ( 受信 ) になります。

以下のいずれかの条件でTRX ビットが"0"になります。

- ・アービトレーションロストを検出した場合

- ・ストップコンディションを検出した場合

- ・スタートコンディション重複防止機能(注)によりスタートコンディション発生を禁止された場合

- ・MST = "0"で、スタートコンディションを検出した場合

- ・MST = "0"で、アックが返ってこなかったことを検出した場合

- ・リセット時

(8) ビット7: 通信モード指定ビット(マスタ/スレーブ指定 ビット: MST)

データ通信を行う際のマスタ/スレーブを指定するビットです。"0"の場合、スレーブとなり、マスタが生成するスタートコンディション、ストップコンディションを受信し、マスタが発生させるクロックに同期してデータ通信を行います。"1"の場合、マスタとなり、スタートコンディション、ストップコンディションを生成します。また、データ通信に必要なクロックを SCL 上に発生させます。

以下のいずれかの条件でMSTビットが"0"になります。

- ・アービトレーションロストを検出した場合、1 バイトデータ送信終了直後

- ・ストップコンディションを検出した場合

- ・スタートコンディション重複防止機能(注)によりスター トコンディション発生を禁止された場合

- ・リセット時

- 注:スタートコンディション重複防止機能は,以下の条件が成立している場合に,スタートコンディションの発生,ビットカウンタのリセット,及びSCLの出力を禁止する機能です。

- ・別のマスタデバイスによるスタートコンディションが成立

図 8.6.7 I<sup>2</sup>C ステータスレジスタ

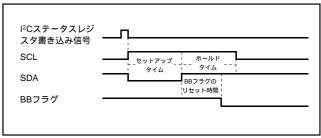

図8.6.8 割り込み要求信号の発生タイミング

## 8.6.6 スタートコンディション発生方法

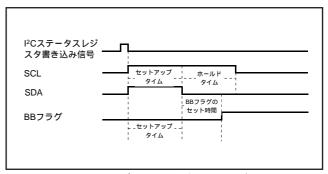

I<sup>2</sup>C コントロールレジスタ ( 00F916 番地 ) の ESO ビットが " 1 "の状態で、I<sup>2</sup>C ステータスレジスタ ( 00F816 番地 ) に書き込み命令を行い MST , TRX , BB ビットを " 1 "にするとスタートコンディションが発生します。その後、ビットカウンタが " 0002 "になり 1 バイト分の SCL が出力されます。スタートコンディションの発生及びBB ビットセットタイミングは、標準クロックモードと高速クロックモードで異なります。図 8.6.9 のスタートコンディション発生タイミング図と表 8.6.2 のスタートコンディション、ストップコンディション発生タイミング表を参照してください。

図 8.6.9 スタートコンディション発生タイミング図

# 8.6.7 ストップコンディションの発生方法

I<sup>2</sup>C コントロールレジスタ(00F916 番地)の ESO ビットが "1"の状態でI<sup>2</sup>C ステータスレジスタ(00F816 番地)へ書き 込み命令を行い MST = 1, TRX = 1, BB = 0 にすると、ストップコンディションが発生します。ストップコンディションの発生及び BB フラグのリセットタイミングは、標準クロックモードと高速クロックモードで異なります。図8.6.10のストップコンディション発生タイミング図と表 8.6.2のスタートコンディション、ストップコンディション発生タイミング表を参照してください。

図8.6.10 ストップコンディション発生タイミング図

表8.6.2 スタートコンディション,ストップコンディション発生タ イミング表

| 項目                 | 標準クロックモード       | 高速クロックモード           |  |

|--------------------|-----------------|---------------------|--|

| セットアップ時間           | 5.0 μ s         | 2.5 μ s             |  |

| スタートコンディション )      | (20サイクル)        | (10 サイクル)           |  |

| セットアップ時間           | 4.25 μ s        | 1.75 μ s            |  |

| ストップコンディション)       | (17 サイクル)       | (7サイクル)             |  |

| ホールド時間             | 5.0 μs (20サイクル) | 2.5 μ s ( 10 サイクル ) |  |

| BB フラグセット / リセット時間 | 3.0 μs (12サイクル) | 1.5 μ s ( 6 サイクル )  |  |

\_\_\_\_\_\_\_注. = 4 MHz 時の絶対時間 ,( ) 内は のサイクル数

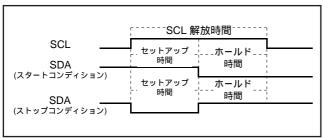

### 8.6.8 スタート/ストップコンディション検出条件

スタート/ストップコンディションを検出する条件を図8.6.11 と表8.6.3 に示します。表8.6.3 の3条件を満たす場合のみスタート/ストップコンディションを検出できます。

注. スレーブ (MST = 0) 時にストップコンディションを検出すると, CPU に対して割り込み要求信号 IICIRQ を発生します。

図 8.6.11 スタートコンディション,ストップコンデション検出の タイミング図

## 表8.6.3 スタートコンディション ストップコンディション検出条件

| 標準クロックモード                   | 高速クロックモード                  |

|-----------------------------|----------------------------|

| 6.5 μs(26サイクル) < SCL解放時間    | 1.0 μs( 4 サイクル ) < SCL解放時間 |

| 3.25 μs (13サイクル) < セットアップ時間 | 0.5 μ s(2 サイクル) < セットアップ時間 |

| 3.25 μ s( 13サイクル ) < ホールド時間 | 0.5 μ s( 2 サイクル ) < ホールド時間 |

注. = 4 MHz 時の絶対時間,( )内は のサイクル数

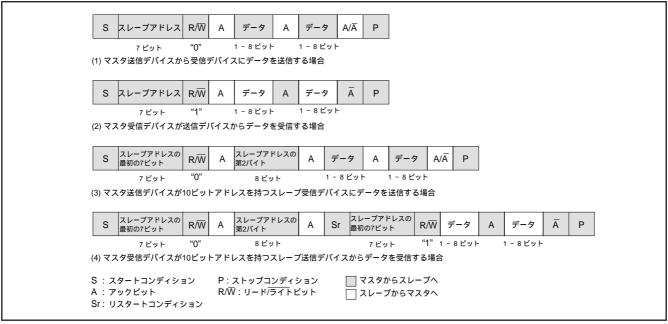

### 8.6.9 アドレスデータ通信

アドレスデータ通信のフォーマットには、7 ビットアドレッシングフォーマットと10 ビットアドレッシングフォーマットがあります。それぞれのアドレス通信フォーマットについての、対応方法を説明します。

## (1) 7 ビットアドレッシングフォーマット

7 ビットアドレッシングフォーマットに対応するために、I<sup>2</sup>C コントロールレジスタ(00F916番地)の10BIT SAD ビットを"0"にしてください。マスタから送信された最初の7 ビットのアドレスデータと、I<sup>2</sup>C アドレスレジスタ(00F716番地)に格納された上位7 ビットのスレープアドレスを比較します。この比較時には、I<sup>2</sup>C アドレスレジスタ(00F716番地)のRBW ビットのアドレス比較は行われません。7 ビットアドレッシングフォーマット時のデータ伝送フォーマットは図8.6.12の(1),(2)を参照してください。

# (2) 10 ビットアドレッシングフォーマット

10 ビットアドレッシングフォーマットに対応するために、I<sup>2</sup>C コントロールレジスタ ( 00F916 番地 ) の 10BIT SAD ビットを" 1"にしてください。マスタから送信された 1 バイト目のアドレスデータと、I<sup>2</sup>C アドレスレジスタ ( 00F716 番地 ) に格納されたスレーブアドレス 7 ビットがアドレス比較されます。この比較時には、I<sup>2</sup>C アドレスレジスタ ( 00F716 番地 ) の RBW ビットと、マスタから送信されるアドレスデータの最終ビット(R/W ビット)が、アドレス比較されます。10 ビットアドレッシングモード時には、アドレスデータの最終ビットである R/W ビットは制御データの通信方向を指定するだけでなく、アドレスデータのビットとして処理されます。

1バイト目のアドレスデータとスレーブアドレスが一致した場合には、I<sup>2</sup>Cステータスレジスタ (00F816番地)の AAS ビットが"1"にセットされます。2バイト目のアドレスデータは、I<sup>2</sup>Cデータシフトレジスタ (00F616番地)に格納した後、ソフトウエアで2バイト目のアドレスデータとスレーブアドレスのアドレス比較を行ってください。2バイトのアドレスデータとスレーブアドレスが一致した場合には、I<sup>2</sup>Cアドレスレジスタ (00F716番地)の RBW ビットをソフトウエアで"1"にしてください。この処理により、リスタートコンディション検出後に受信する7ビットのスレーブアドレス及びR/WのデータとI<sup>2</sup>Cアドレスレジスタ (00F716番地)の値を一致させることができます。10ビットアドレッシングフォーマット時のデータ伝送フォーマットは図8.6.12の(3),(4)を参照してください。

### 8.6.10 マスタ送信例

標準クロックモード、SCL 周波数 100kHz、アックを返す モードの場合のマスタ送信例を以下に示します。

I<sup>2</sup>C アドレスレジスタ (00F716 番地)の上位 7 ビットにスレーブアドレス、RBW ビットに"0"を設定します。

$I^2$ Cクロックコントロールレジスタ( 00FA16番地 )に" 8516 " を設定することによって、アックを返すモード、SCL = 100kHz にします。

I<sup>2</sup>C ステータスレジスタ (00F816 番地 ) に " 1016 " を設定し、SCL を " H " レベルに保持します。

I<sup>2</sup>C コントロールレジスタ ( 00F916 番地 ) に " 4816 " を設定することによって、通信許可状態にします。

$I^{2}$ C データシフトレジスタ ( 00F616 番地 ) の上位 7 ビット に送信先のアドレスデータを設定します。また、最下位 ビットは " 0 " にします。

I<sup>2</sup>C ステータスレジスタ (00F816 番地) に "F016"を設定することによって、スタートコンディションを発生させます。このとき、1 バイト分のSCL とアッククロックは自動的に発生します。

I<sup>2</sup>C データシフトレジスタ (00F616番地)に送信データを 設定します。このとき、SCL とアッククロックは自動的に 発生します。

複数バイトの制御データを送信する場合、 を繰り返します。

アックが返らなかった場合又は送信が終了した場合は、I<sup>2</sup>C ステータスレジスタ(00F816番地)に"D016"を設定することのよってストップコンディションを発生させます。

### 8.6.11 スレーブ受信例

高速クロックモード、SCL周波数400kHz、アックなしモード、アドレッシングフォーマットの場合のスレーブ受信例を以下に示します。

I<sup>2</sup>C アドレスレジスタ (00F716 番地)の上位 7 ビットにスレープアドレス、RBW ビットに "0"を設定します。

$I^2$ Cクロックコントロールレジスタ( 00FA16番地 )に" 2516 " を設定することによって、アックなしモード、SCL = 400kHz にします。

I<sup>2</sup>C ステータスレジスタ (00F816 番地)に "1016"を設定し SCL を "H"レベルに保持します。

I<sup>2</sup>C コントロールレジスタ (00F916 番地) に "4816"を設定することによって、通信許可状態にします。

スタートコンディションを受信すると、アドレス比較されます。

- <送信されたアドレスがすべて"0"の場合(ジュネラルコール)> I<sup>2</sup>C ステータスレジスタ(00F816番地)の AD0= "1"に設定され、割り込み要求信号が発生します。

- <送信されたアドレスが、で設定したアドレスと一致した場合> I<sup>2</sup>C ステータスレジスタ(00F816 番地)の AAS="1"に設定され、割り込み要求信号が発生します。

- <上記以外の場合>

I<sup>2</sup>Cステータスレジスタ(00F816番地)のAD0="0"、AAS= "0"に設定され、割り込み要求信号は発生しません。

$I^{2}$ C データシフトレジスタ(00F616 番地)にダミーデータを設定します。

複数バイトの制御データを受信する場合、 を繰り返します。

ストップコンディションを検出すると通信が終了します。

図 8.6.12 アドレスデータ通信フォーマット

8.6.12 マルチマスタ  $I^2$ C-BUS インタフェースの注意事項 (1) リード・モディファイ・ライト命令の使用について

SEB, CLBなどのリード・モディファイ・ライト命令をマルチマスタI<sup>2</sup>C-BUSインタフェースの各レジスタに使う場合の注意事項は以下のとおりです。

- ・I<sup>2</sup>C データシフトレジスタ(SO)転送中にリード・モディファイ・ライト命令を使用すると、意図しない値になることがあります。

- ・I<sup>2</sup>C アドレスレジスタ (SOD) ストップコンディション検出時にリード・モディファイ・ ライト命令を使用すると、意図しない値になることがあり

ます。

上記のタイミングでリード/ライトビット(RBW)が、ハードウエアによって変化するためです。

- ・I<sup>2</sup>C ステータスレジスタ (S1) すべてのビットはハードウエアによって変化しますので、 リード・モディファイ・ライト命令を使用しないでください。

- ・I<sup>2</sup>C コントロールレジスタ(S1D) スタートコンディション検出時及びバイト転送完了時に

スタートコンティション検出時及びハイト転送元了時に リード・モディファイ・ライト命令を使用すると、意図し ない値になることがあります。

上記のタイミングでビットカウンタ(BC0~BC2)が、ハードウエアによって変化するためです。

・I<sup>2</sup>C クロックコントロールレジスタ (S2) リード・モディファイ・ライト命令は使用可能です。 (2) マルチマスタで使用する場合のスタートコンディション 発生手順について

手順例(発生手順の必要条件は 以降に記します。)

:

LDA ~ (スレーブアドレス値の取り出し)

SEI (割り込みの禁止)

BBS 5,S1,BUSBUSY (BB フラグ確認及び分岐処理)

**BUSFREE**:

STA S0 (スレーブアドレス値の書き込み) LDM #\$F0,S1 (スタートコンディション発生のトリカ)

CLI (割り込みの許可)

.

**BUSBUSY:**

CLI (割り込みの許可)

:

I<sup>2</sup>Cデータシフトレジスタへのスレーブアドレス値の書き 込みには、STA、STXあるいはSTYのゼロページアドレッ シング命令を必ず使用してください。

スタートコンディション発生のトリガの設定はLDM命令を必ず使用してください。

前記 のスレーブアドレス値の書き込みと のスタートコンディション発生のトリガの設定は、手順例のとおり必ず連続して実行するようにしてください。

BBフラグの確認、スレーブアドレス値の書き込み、スタートコンディション発生のトリガ、以上3つの処理ステップの間は必ず割り込みを禁止にしてください。

BBフラグがバスビジーである場合は、ただちに割り込み を許可にしてください。

# (3) リスタートコンディション発生手順について

手順例(発生手順の必要条件は 以降に記します。)

PINビットが"0"のとき、以下の手順を実行してください。

:

LDM #\$00,S1 (スレーブ受信モードにする)

LDA ~ (スレーブアドレス値の取り出し)

SEI (割り込みの禁止)

STA SO (スレーブアドレス値の書き込み)

LDM #\$F0,S1 (リスタートコンディション発生のトリガ)

CLI (割り込みの許可)

.

PIN ビットが " 0 " の状態で、スレーブ受信モードにしてください。PIN ビットには" 1 "を書き込まないでください。 BB ビットへの書き込みに " 0 " 又は " 1 " の指定はありません。

TRX ビットが"0"になり、SDA 端子が解放されます。 I<sup>2</sup>Cデータシフトレジスタへのスレープアドレス値の書き 込みによって、SCL 端子が解放されます。書き込みには、STA,STX,STY のゼロページアドレッシング命令を必ず使用してください。

リスタートコンディション発生のトリガの設定はLDM命令を必ず使用してください。

前記の のスレーブアドレス値の書き込みと のリスタートコンディション発生のトリガの設定は手順例のとおり必ず連続して実行するようにしてください。

スレーブアドレス値の書き込み、リスタートコンディション発生のトリガ、以上2つの処理ステップの間は必ず割り込みを禁止にしてください。

(4) ストップコンディション発生手順について

手順例(発生手順の必要条件は 以降に記します。)

:

SEI (割り込みの禁止)

LDM #\$C0,S1 (マスタ送信モードにする)

NOP (NOPを設定)

LDM #\$D0,S1 (ストップコンディション発生のトリガ)

CLI (割り込みの許可)

:

マスタ送信モード設定時、PINビットに"0"を書き込んでください。

マスタ送信モード設定後、NOP命令を実行してください。 また、マスタ送信モード設定後10マシンサイクル以内に、 ストップコンディション発生のトリガを設定してください。

マスタ送信モードの設定からストップコンディション発生 のトリガの処理ステップの間は必ず割り込みを禁止にして ください。

# (5) I<sup>2</sup>C ステータスレジスタへの書き込みについて

同時にPINビットを"0"から"1"、MSTビット及びTRXビットを"1"から"0"にする命令実行をしないでください。SCL端子が解放されて、約1マシンサイクル後にSDA端子が解放される状態になることがあります。PINビットが"1"の時に、MSTビット及びTRXビットを"1"から"0"にする命令実行をしても、同様の状態になることがあります。

# (6) ストップコンディション発生後の処理について

マスタとしてストップコンディションを発生させた後、バスビジーフラグ BB が " 0 " になるまでの間、I<sup>2</sup>C データシフトレジスタ S0 及び I<sup>2</sup>C ステータスレジスタ S1 に書き込みを行わないで下さい。ストップコンディション波形が正常に発生されないことがあります。上記レジスタに対する読み出しは問題ありません。

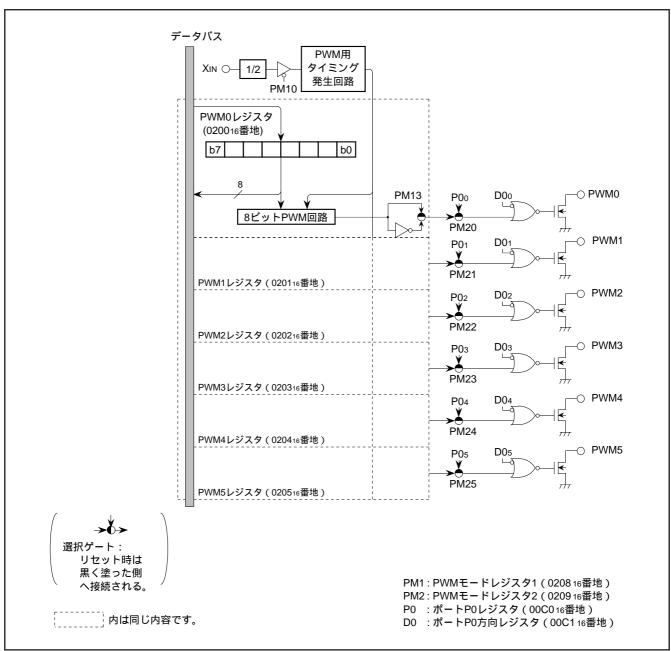

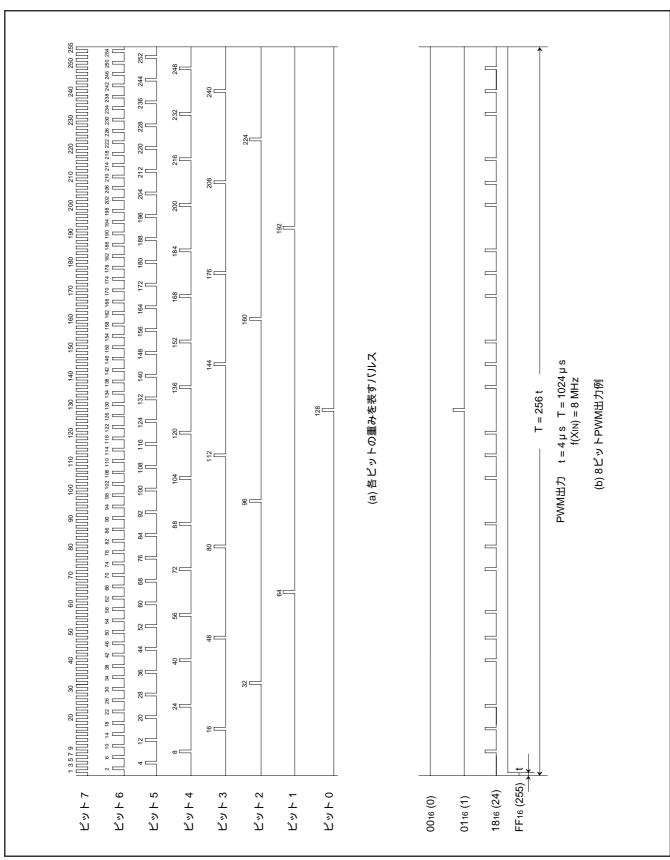

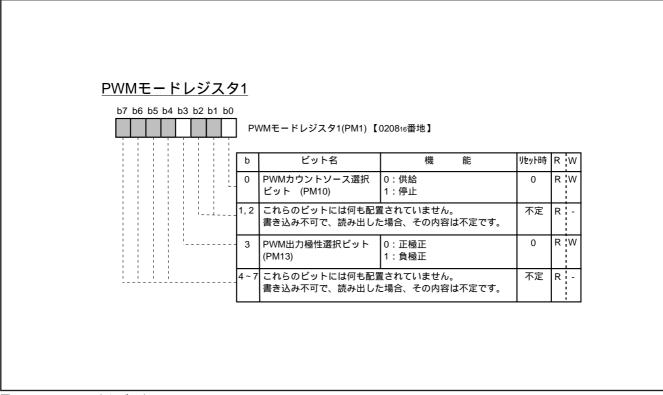

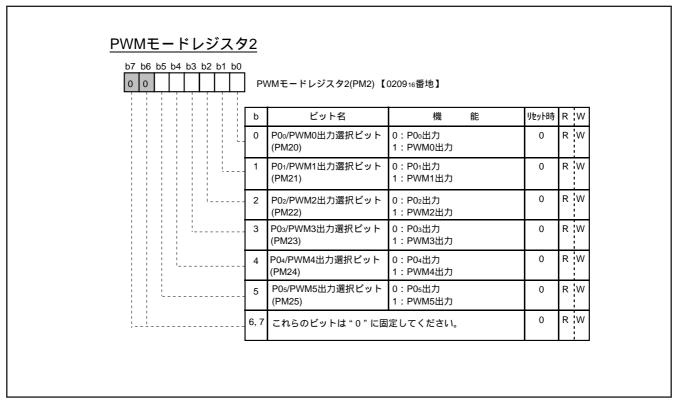

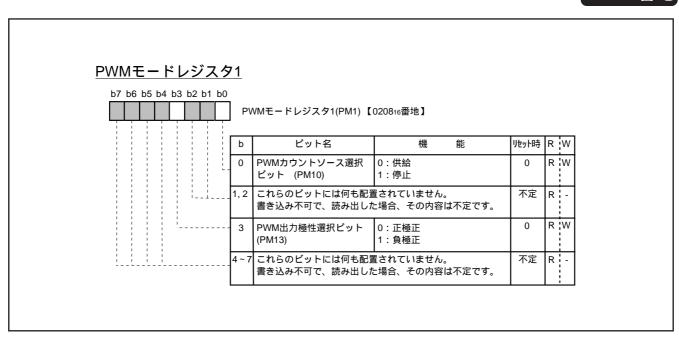

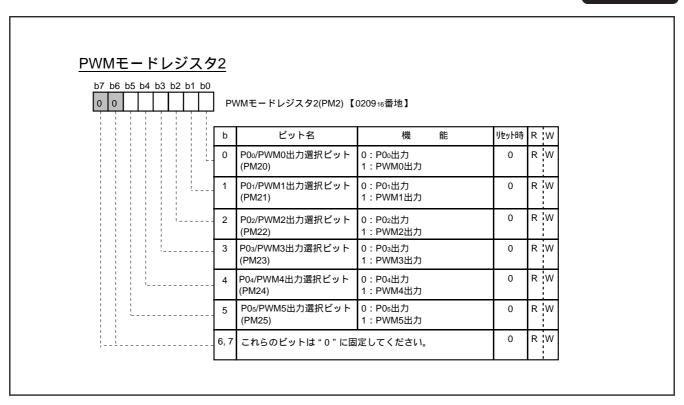

# 8.7 PWM 出力回路

本マイクロコンピュータは、8ビットPWMを6本(PWM0 ~ PWM5) 備えています。PWM0 ~ PWM5 は同じ回路構成で、8ビットの分解能を持ち、最小分解ビット幅4 $\mu$ s、繰り返し周期1024 $\mu$ sです(f(XIN) = 8MHz の場合)。

図8.7.1 に PWM のブロック図を示します。 PWM のタイミング発生回路はf(XIN)を2分周した信号を基本として、PWM0 ~ PWM5 の各制御信号を供給します。

# 8.7.1 データの設定

PWM0~PWM5を出力する場合には、出力データ8ビットをPWMi レジスタ(iは0~5,020016~020516番地)に設定します。

#### 8.7.2 レジスタから PWM 回路への転送

PWM レジスタから PWM 回路へのデータ転送は、レジスタへのデータ書き込みが行われた時点で実行されます。

PWM 出力端子から出力される信号は、このレジスタの内容に対応したものです。

### 8.7.3 PWM の動作

次に動作について説明します。

まず、PWMモードレジスタ1(020816番地)のビット0を "0"にクリアし(リセット時は"0") PWMカウントソース を供給します。

PWM0~PWM5はポートP00~P05と出力端子が共用です。ポートP0方向レジスタの対応ビットを"1"にし、出力モードにします。PWMモードレジスタ1(020816番地)のビット3で出力極性を選択します。そして、PWMモードレジスタ2(020916番地)のビット5~ビット0を"1"にし、ポートをPWM出力にします。

上記のレジスタを設定することによって PWM 出力端子から PWM 出力が行われます。

図8.7.2 に PWM のタイミング図を示します。 $2^8 = 256$  区間を1周期 T とします。回路内部では1周期の間に、各ビットの重みを表すビット0からビット7までの8種類のパルスが出力されます(図8.7.2(a)参照)、PWM は PWM レジスタのビット0~ビット7のパルスの和を取った波形を出力します。図8.7.2(b)にいくつかの例を示します。図のように PWM レジスタの内容を変えることにより、"H"の区間が 0/256~255/256 までの 256 通りの出力を選ぶことができます(全区間 "H"出力はできません)。

# 8.7.4 リセット後の出力

リセット時には、ポート P00 ~ P05 は、ハイインピーダンス状態ですが、PWM レジスタ及び PWM 回路の内容は不定です。リセット解除後、PWMレジスタを設定するまで、PWM出力の内容は不定ですので注意が必要です。

図 8.7.1 PWM 回路ブロック図

図 8.7.2 PWM タイミング図

図 8.7.3 PWM モードレジスタ 1

図 8.7.4 PWM モードレジスタ 2

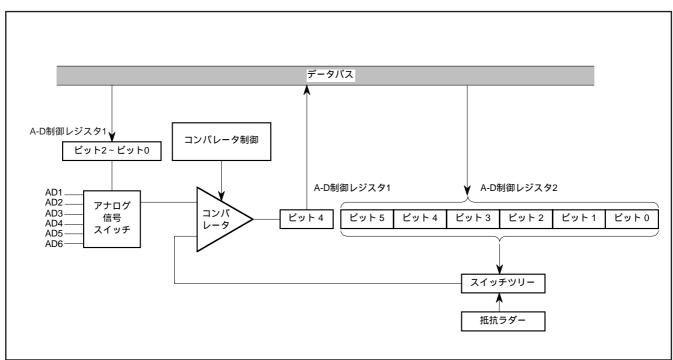

# 8.8 A-D 比較器

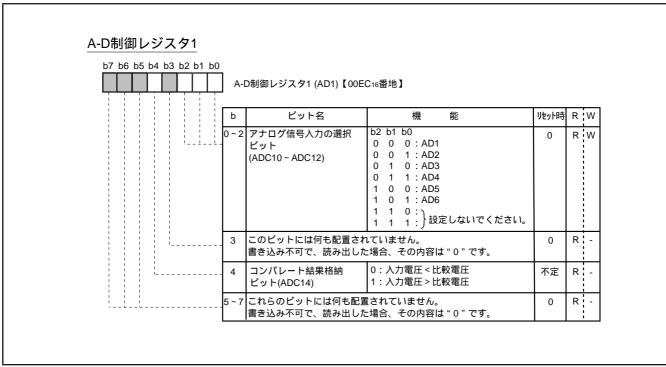

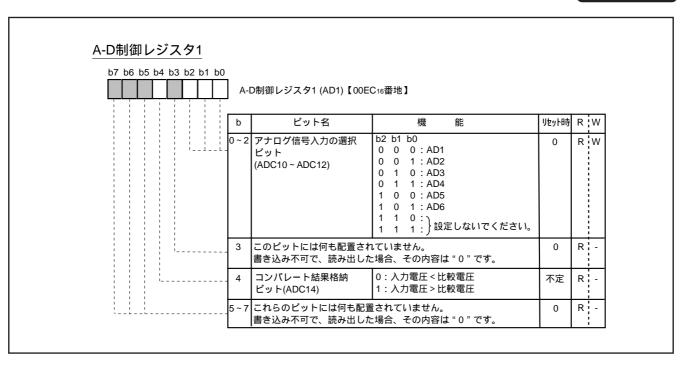

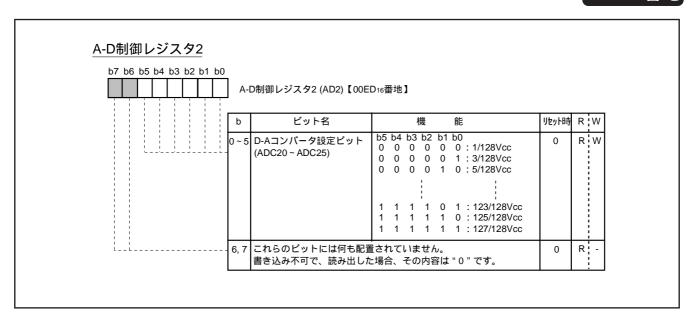

A-D比較器は、抵抗ストリング方式の6ビットD-A変換器 とコンパレータから構成されています。図8.8.1にA-D比較 器のブロック図を示します。

A-D制御レジスタ2(00ED16番地)下位6ビットによって D-A 変換の比較電圧 Vref が設定されます。

また、アナログ入力電圧と比較電圧 Vref との比較結果は、A-D制御レジスタ1(00EC16番地)のビット4に格納されます。

A-D比較動作を行うためには、アナログ入力端子に対応する方向レジスタのビットを"0"にして、ポートをアナログ入力端子として使用できる状態にします。まず、A-D制御レジスタ1のビット0~ビット2にアナログ入力端子を選択するデータを書き込みます。その後、A-D制御レジスタ2のビット0~ビット5に比較したいVrefに対応するデジタル値を書き込みます。このA-D制御レジスタ2の書き込み動作により、直ちに電圧比較が開始され、16マシンサイクル後(NOP命令×8)に完了します。

図 8.8.1 A-D 比較器ブロック図

図 8.8.2 A-D 制御レジスタ 1

図 8.8.3 A-D 制御レジスタ 2

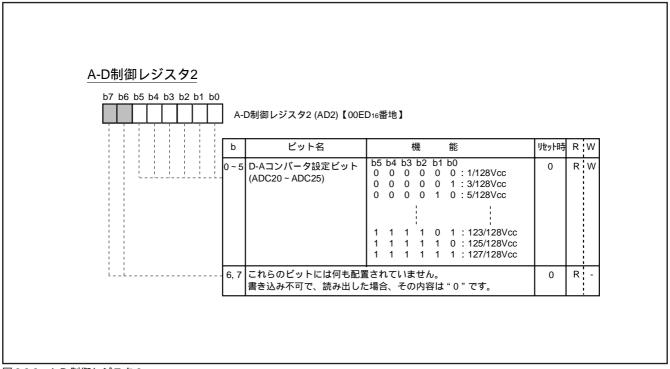

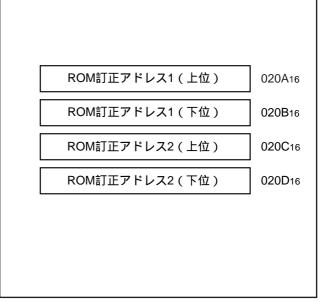

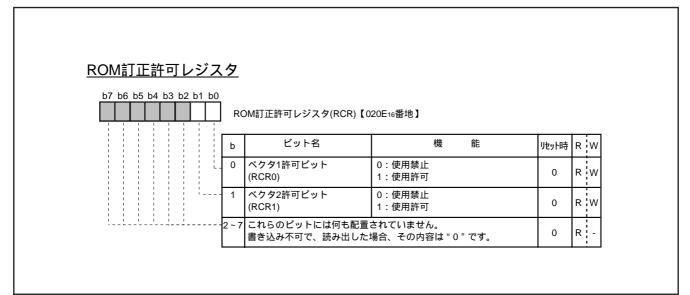

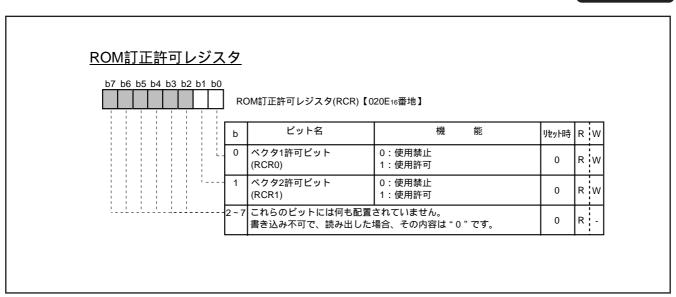

# 8.9 ROM 訂正機能

ROM内のプログラムデータを訂正することができます。 訂正できるアドレスは2箇所までで、RAM領域内のROM訂 正用メモリに訂正プログラムを格納します。ROM訂正用ベ クタは2ベクタあります。

ベクタ1:030016番地ベクタ2:032016番地

訂正する ROM データのアドレスを ROM 訂正アドレスレジスタに設定します。プログラムカウンタの値が設定したアドレスの値に一致すると、ROM 訂正ベクタを先頭に格納した訂正プログラムへと分岐します。訂正プログラムからメインプログラムへの復帰のためには、訂正プログラムの最後にJMP命令のオペコード及びオペランド(計3バイト)が必要です。

ROM訂正機能はROM訂正許可レジスタによって制御されます。

- 注1. ROM訂正アドレスは,各命令の先頭アドレス(オペコードのアドレス)を指定してください。

- 2. 訂正プログラムからメインプログラムへの復帰は JMP 命令 (計 3 バイト) で行ってください。

- 3. ベクタ1,ベクタ2に同一のROM訂正アドレスを設定 しないでください。

図 8.9.1 ROM 訂正アドレスレジスタ

図 8.9.2 ROM 訂正許可レジスタ

# 8.10 データスライサ

本マイクロコンピュータは、クローズドキャプションデコーダ(以下 CCD と称す)に対応するためのデータスライサ機能を内蔵しています。本機能によってコンポジットビデオ信号の垂直帰線消去期間中に重畳されたキャプションデータを取り出すことができます。CVIN 端子には、シンクチップを負極性にするコンポジットビデオ信号を入力します。

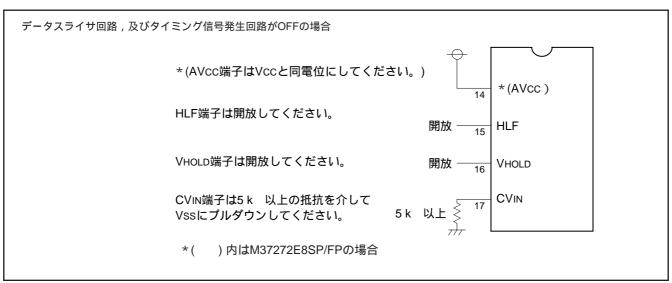

データスライサ機能を使用しない場合は、データスライサ制御レジスタ1(00E016番地)のビット0を"0"に設定することによって、データスライサ回路及びタイミング信号発生回路をOFFすることができます。これらの設定によって、電源電流を抑えることができます。

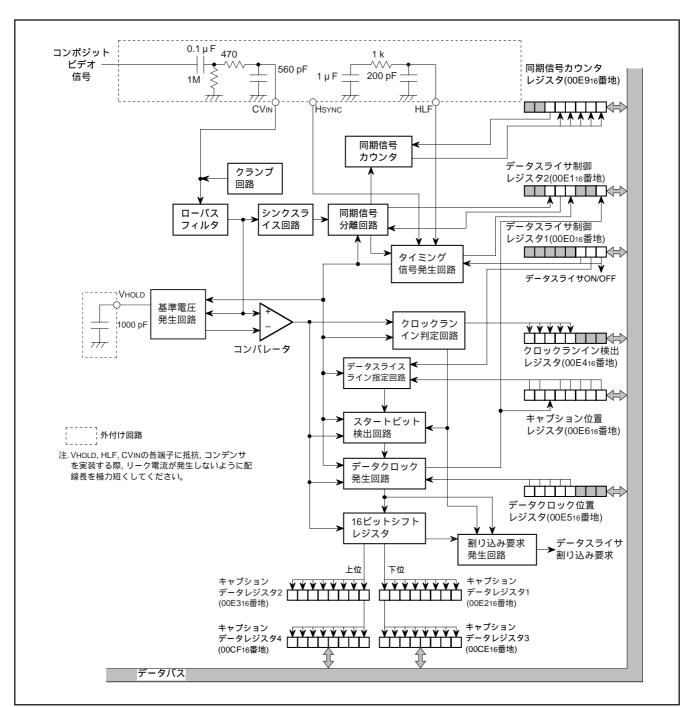

図 8.10.1 データスライサブロック図

8.10.1 データスライサを使用しない場合の注意事項 データスライサ制御レジスタ1(00E016番地)のビット0 が"0"の場合、図8.10.2のように端子を処理してください。

図 8.10.2 データスライサ回路,及びタイミング信号発生回路 OFF の場合の,データスライサ入出力端子の処理方法

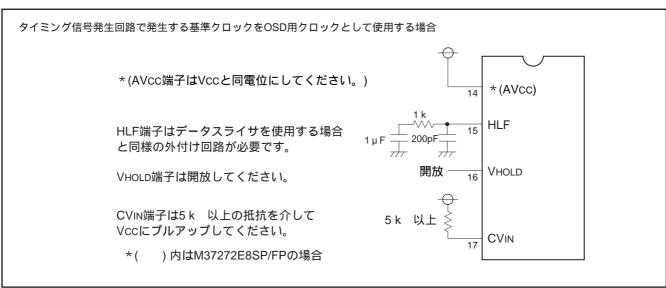

データスライサ制御レジスタ1(00E016番地)のビット0、2の両方が"1"の場合、図8.10.3のように端子を処理してください。

図 8.10.3 タイミング信号発生回路 ON の場合の,データスライサ入出力端子の処理方法

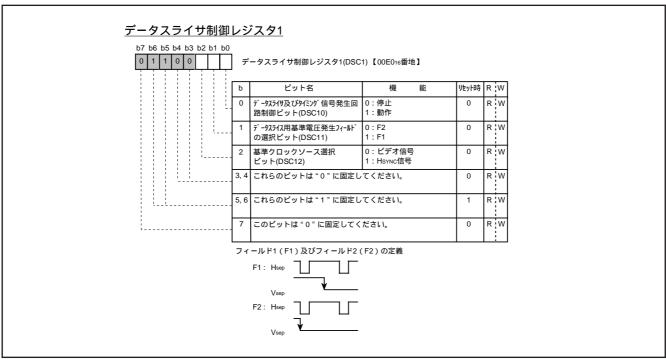

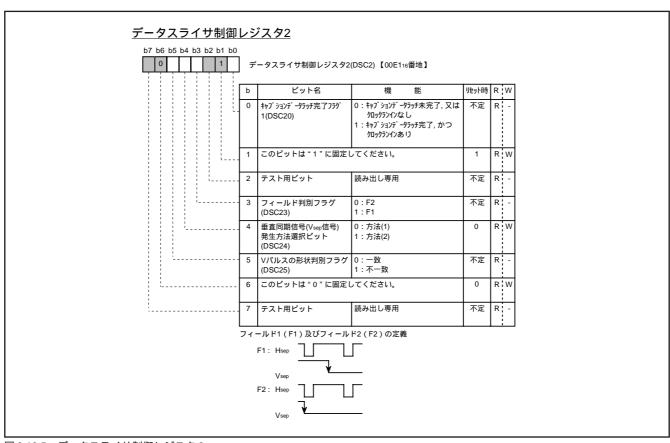

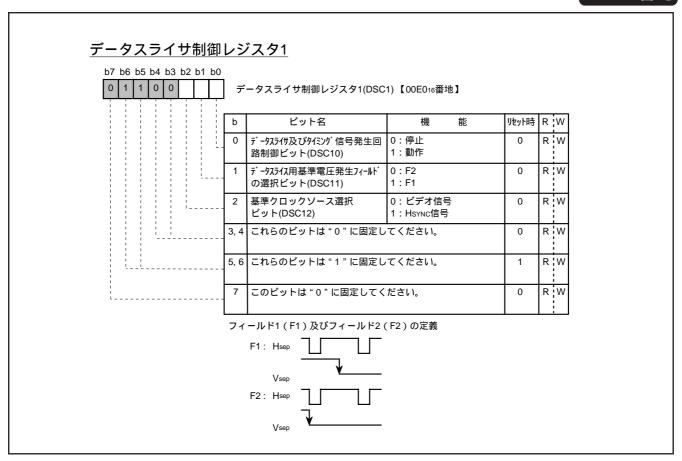

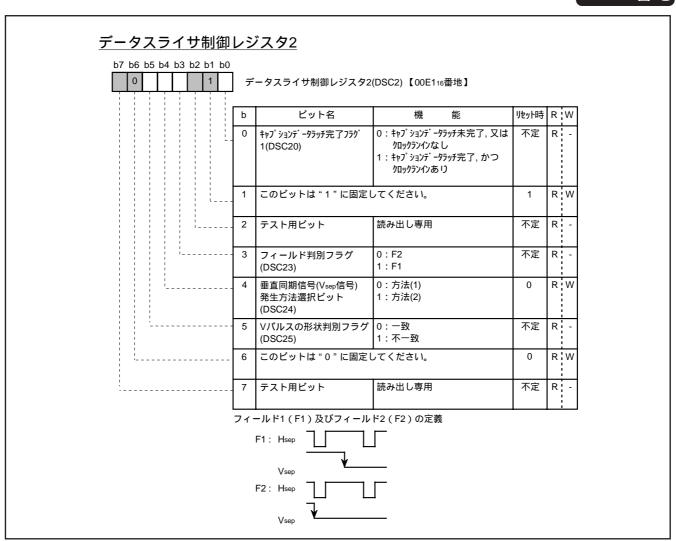

図 8.10.4、図 8.10.5 にデータスライサ制御レジスタを示します。

図 8.10.4 データスライサ制御レジスタ 1

図 8.10.5 データスライサ制御レジスタ 2

### 8.10.2 クランプ回路・ローパスフィルタ

CVIN 端子から入力されたコンポジットビデオ信号は、クランプ回路でシンクチップ部分を基準にしてクランプされます。ローパスフィルタはクランプされたコンポジットビデオ信号のノイズを減衰します。コンポジットビデオ信号が入力される CVIN 端子は、外部でのコンデンサ  $(0.1\ \mu\ F)$  結合が必要です。また CVIN 端子は、数  $100k \sim 1\ M$  程度の抵抗でプルダウンしてください。さらに CVIN 端子に抵抗及びコンデンサで簡単なローパスフィルタ回路を外付けすることを推奨します(図 8.10.1 参照)。

# 8.10.3 シンクスライス回路

ローパスフィルタの出力信号からコンポジットシンク信号 を取り出します。

# 8.10.4 同期信号分離回路

シンクスライス回路で取り出されたコンポジットシンク 信号から水平同期信号と垂直同期信号を分離します。

# (1)水平同期信号 (Hsep)

コンポジットシンク信号の立ち下がりエッジでワンショットの水平同期信号 Hsep を発生します。

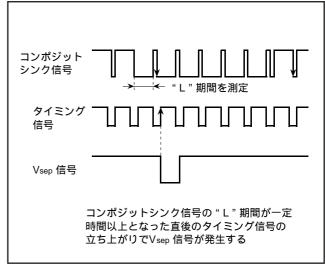

### (2)垂直同期信号 (Vsep)

Vsep信号の発生方法は、データスライサ制御レジスタ 2 (00E116 番地)のビット 4 を用いて、次の 2 種類から選択することができます。

- ・方法 1 コンポジットシンク信号の "L"レベル幅を測定し、一定時間以上であれば、その "L"レベル直後のタイミング信号の立ち上がりに同期して Vsep 信号を発生します。

- ・方法 2 コンポジットシンク信号の "L"レベル幅を測定し、一定時間以上であれば、その "L"レベル直後のタイミング信号の "L"レベル期間中に、コンポジットシンク信号の立ち下がりがあるかを検出します。立ち下がりがある場合は、タイミング信号の立ち上がりに同期して Vsep信号を発生します(図8.10.6 参照)。

発生タイミングを図8.10.6 に示します。図中のタイミング 信号はタイミング発生回路が出力する基準クロックをもとに 発生されます。

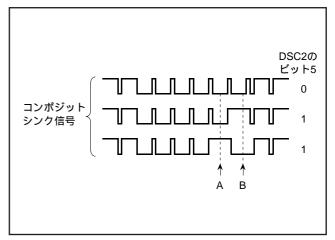

データスライサ制御レジスタ2のビット5を読み出すことによって、コンポジットシンク信号のVパルス部分の形状が判別できます。図8.10.7のようにA,Bのレベルが一致していれば"0"、不一致であれば"1"になります。

図 8.10.6 Vsep 発生タイミング (方法 2)

# 8.10.5 タイミング信号発生回路

タイミング信号発生回路は水平同期信号周波数の832倍の基準クロックを発生します。また、基準クロック、水平同期信号、及び垂直同期信号をもとに各種タイミング信号を発生します。タイミング信号発生回路はデータスライサ制御レジスタ1(00E016番地)のビット0を"1"に設定することによって動作します。

基準クロックはデータスライサの他に OSD 機能の表示用 クロックとしても使用できます。また、コンポジットシンク 信号のかわりにHSYNC信号をカウントソースとすることもできます。ただし、HSYNC信号を選択した場合はデータスライサを使用できません。基準クロックのカウントソースはデータスライサ制御レジスタ 1 (00E016番地)のビット 2 で選択できます。

HLF端子は、図8.10.1に示す様に抵抗とコンデンサを接続してください。また、リーク電流が発生しないように配線長をできる限り短くしてください。

注. データスライサ及びタイミング信号発生回路を動作させてから 基準クロックが安定するまで数 10ms 程度の時間が必要です。 この期間,各種タイミング信号,Hsep信号,Vsep信号は不定 となりますので,プログラム作成の際は,安定時間を考慮して ください。

図 8.10.7 Vパルス形状の判別

### 8.10.6 データスライスライン指定回路

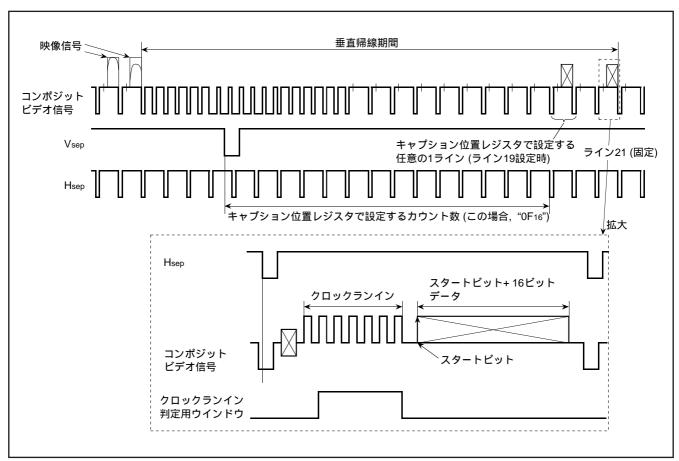

# (1) データスライスラインの指定

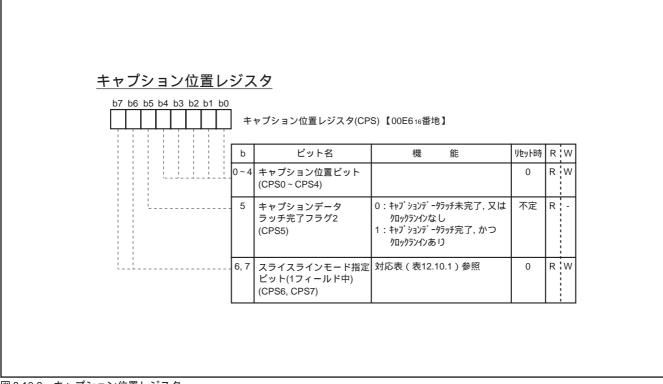

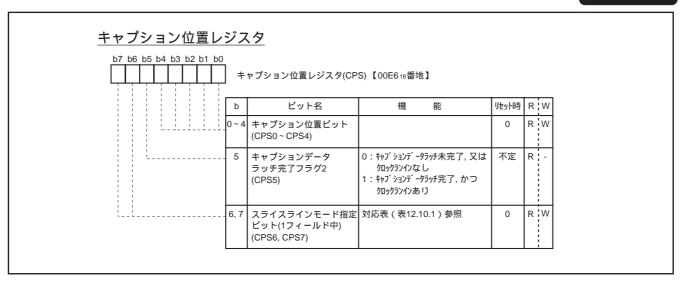

キャプションデータが重畳されるラインを決定します。 1フィールド中のライン21(固定)と任意の1ラインの計 2ライン/1フィールド、F1/F2の両フィールドのデー タスライスが可能です。各設定はキャプション位置レジ スタ(00E616番地)で行います(表8.10.1参照)。

Vsep の立ち下がりでカウンタをリセットし、Hsep の本数をカウントします。カウンタの値とキャプション位置レジスタのビット 4 ~ ビット 0 の設定値とが一致したHsep に対してデータスライスを行います。

キャプション位置レジスタには"0016"~"1F16"の値が設定できます(任意の1ラインのみの設定時)。図8.10.8に垂直帰線期間中の信号を示します。キャプション位置レジスタを図8.10.9に示します。

### (2) スライス電圧を設定するラインの指定

どのラインのクロックランインに対して、スライス用の基準電圧(スライス電圧)を発生するかを表 8.10.1 に示します。スライス電圧を発生させるフィールドの指定はデータスライサ制御レジスタ1のビット1で設定します。1フィールド中のスライス電圧発生ラインは、キャプション位置レジスタのビット7、6で設定します(表8.10.1参照)。

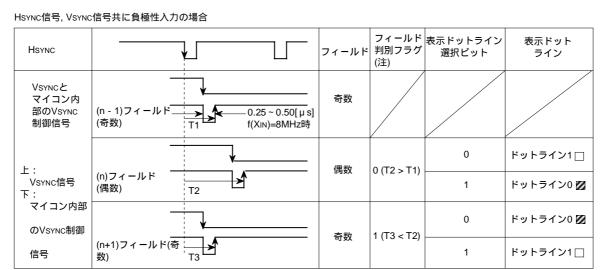

# (3) フィールドの判別

データスライサ制御レジスタ2のビット3によって、フィールド判別フラグを読み出すことができます。このフラグはVsepの立ち下がりのタイミングで変化します。

図8.10.8 垂直帰線期間中の信号

図 8.10.9 キャプション位置レジスタ

表 8.10.1 データスライスラインの指定

| CPS  |      |                                                                               |                                                                          |  |

|------|------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| ビット7 | ビット6 | データスライスするフィールド・ライン                                                            | スライス電圧発生フィールド・ライン                                                        |  |

| 0    | 0    | ・F1/F2両フィールド<br>・ライン 21 と CPS のビット 4 ~ 0 で指定される 1 ライ<br>ン ( 計 2 ライン ) ( 注 2 ) | ・DSC1 のビット 1 で指定されるフィールド・ライン 21 (計 1 ライン)                                |  |

| 0    | 1    | ・F1/F2両フィールド<br>・CPS のビット4 ~ 0 で指定される1ライン<br>(計1ライン)(注3)                      | ・DSC1 のビット1 で指定されるフィールド<br>・CPS のビット4 ~ 0 で指定される1ライン<br>(計1ライン)(注3)      |  |

| 1    | 0    | ・F1/F2両フィールド<br>・ライン 21 (計 1 ライン )                                            | ・DSC1 のビット 1 で指定されるフィールド<br>・ライン 21 (計 1 ライン)                            |  |

| 1    | 1    | ・F1/F2両フィールド<br>・ライン 21 と CPS のビット 4 ~ 0 で指定される 1 ライン (計 2 ライン )(注 2)         | ・DSC1 のビット1 で指定されるフィールド<br>・ライン 21 と CPS のビット4 ~ 0 で指定される1ライン(計2ライン)(注2) |  |

注 1. DSC1: データスライサ制御レジスタ1

CPS:キャプション位置レジスタ

- 2. CPSのビット4~0には"0016"~"1016"の値を設定してください。 3. CPSのビット4~0には"0016"~"1F16"の値を設定してください。

### 8.10.7 基準電圧発生回路・コンパレータ

クランプ回路によってクランプされたコンポジットビデオ 信号は基準電圧発生回路、及びコンパレータに入力されま す。

# (1) 基準電圧発生回路

データスライスライン指定回路で指定されたラインにおけるクロックランインの振幅を用いて基準電圧(スライス電圧)を発生します。VHOLD端子とVSS間にコンデンサを接続してください。また、リーク電流が発生しないように配線長をできる限り短くしてください。

### (2) コンパレータ

コンポジットビデオ信号の電圧と基準電圧発生回路によって発生した電圧(基準電圧)を比較し、コンポジットビデオ信号をデジタル値に変換します。

### 8.10.8 スタートビット検出回路

データスライスライン指定回路で決定したラインにおいて スタートビットを検出します。スタートビットの判定は以下 のようになります。

タイミング信号が出力する基準クロックを 13 分周したサンプリングクロックを生成します。

そのサンプリングクロックを用いてクロックランインパル スを検出します。

パルス検出後、サンプリングクロックでコンパレータ出力からスタートビットパターンを検出します。

# 8.10.9 クロックランイン判定回路

コンポジットビデオ信号中のウインドウ中でパルス数をカウントすることによってクロックランインであることを判定します。

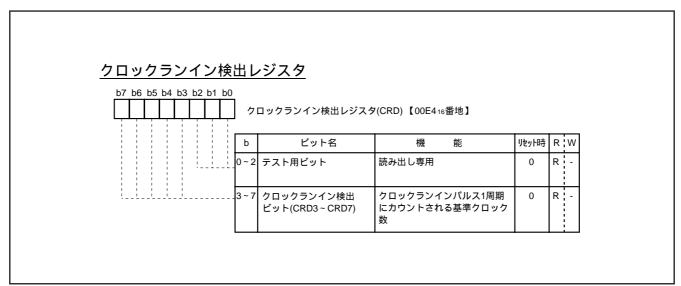

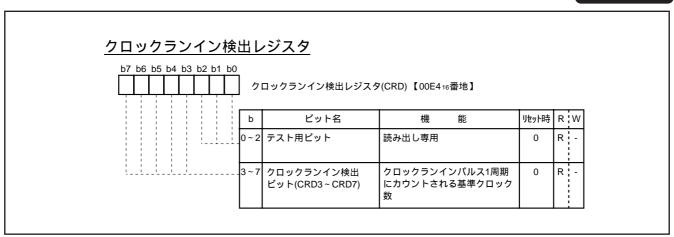

また、クロックランインパルス1周期にカウントされる基準クロック数はクロックランイン検出レジスタ(00E416番地)のビット7~ビット3に格納されます。これらのビットはデータスライサ割り込み(「8.10.12割り込み要求発生回路」)の発生後に読み出してください。

クロックランイン検出レジスタを図8.10.10に示します。

図 8.10.10 クロックランイン検出レジスタ

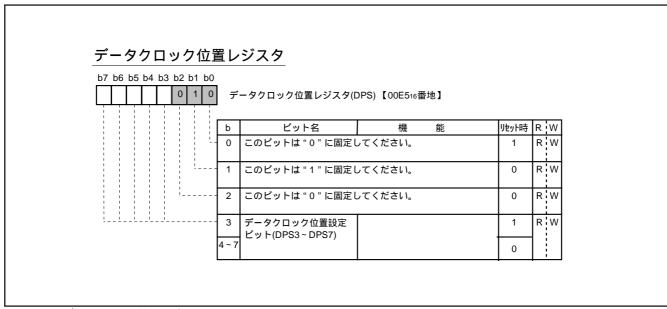

# 8.10.10 データクロック発生回路

データクロック発生回路は、スタートビット検出回路で検出されたスタートビットに同期したデータクロックを発生します。データクロックはキャプションデータを16ビットシフトレジスタへ格納するためのクロックです。16ビットのデータが16ビットシフトレジスタへ格納され、かつクロックランイン判定回路でクロックランインありと判定された場合、キャプションデータラッチ完了フラグがセットされます。この完了フラグは垂直同期信号(Vsep)の立ち下がりで"0"にリセットされます。

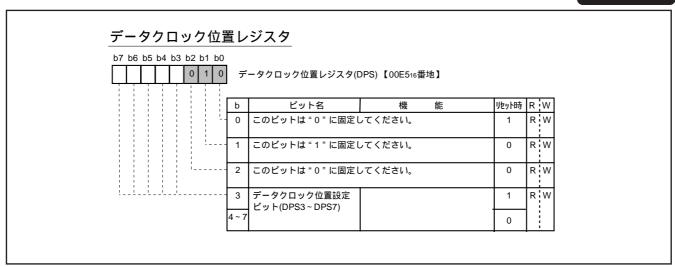

図8.10.11 データクロック位置レジスタ

# 8.10.11 16 ビットシフトレジスタ

コンパレータでデジタル値に変換されたキャプションデータは、データクロックに同期して16ビットシフトレジスタに格納されます。格納されたキャプションデータの上位8ビットは、キャプションデータレジスタ2(00E316番地)/キャプションデータレジスタ4(00CF16番地),下位8ビットはキャプションデータレジスタ1(00E216番地)/キャプションデータレジスタ1(00E216番地)/キャプションデータレジスタ3(00CE16番地)を読み出すことによってデータ内容を得ることができます。またこれらのレジスタはVsepの立ち下がりで"0"にリセットされます。キャプションデータレジスタ1~4はデータスライサ割り込み(「8.10.12割り込み要求発生回路」)発生後に読み出してください。

### 8.10.12 割り込み要求発生回路

キャプション位置レジスタ(00E616番地)のビット7、ビット6の組み合わせによって表8.10.3に示すように割り込み要求が発生します。キャプションデータレジスタ1~4の内容、及びクロックランイン検出レジスタのビット7~3の内容は、データスライサ割り込み要求発生後に読み出してください。

表 8.10.2 キャプションデータラッチ完了フラグ,及び16 ビットシフトレジスタ内容

| _ スライスラインの設定モード |      | キャプションデータラッチ完了フラグの内容            |                                 | 16 ビットシフトレジスタの内容                              |                                               |

|-----------------|------|---------------------------------|---------------------------------|-----------------------------------------------|-----------------------------------------------|

| CPS             |      | 完了フラグ 1                         | 完了フラグ2                          | キャプションデータ                                     | キャプションデータ                                     |

| ビット7            | ビット6 | (DSC2のビット0)                     | (CPSのビット5)                      | レジスタ 1, 2                                     | レジスタ 3, 4                                     |

| 0               | 0    | ライン21                           | CPS のビット 4 ~ 0 で<br>指定される 1 ライン | ライン 21 の 16 ビット<br>データ                        | CPS のビット 4 ~ 0 で<br>指定される 1 ラインの<br>16 ビットデータ |

| 0               | 1    | CPS のビット 4 ~ 0 で<br>指定される 1 ライン | 無効                              | CPS のビット 4 ~ 0 で<br>指定される 1 ラインの<br>16 ビットデータ | 無効                                            |

| 1               | 0    | ライン 21                          | 無効                              | ライン 21 の 16 ビット<br>データ                        | 無効                                            |

| 1               | 1    | ライン21                           | CPS のビット 4 ~ 0 で<br>指定される 1 ライン | ライン 21 の 16 ビット<br>データ                        | CPS のビット4~0で<br>指定される1ラインの<br>16ビットデータ        |

CPS: キャプション位置レジスタ DSC2: データスライサ制御レジスタ 2

表 8.10.3 割り込み要求発生要因

| キャプション位置レジスタ |      | データスライスライン終了時割り込み要求           |

|--------------|------|-------------------------------|

| ビット7         | ビット6 | ライン 21 スライス後                  |

| 0            | 0    |                               |

| 0            | 1    | キャプション位置レジスタビット4~0で指定される1ライン後 |

| 1            | 0    | ライン 21 スライス後                  |

| 1            | 1    | ライン 21 スライス後                  |

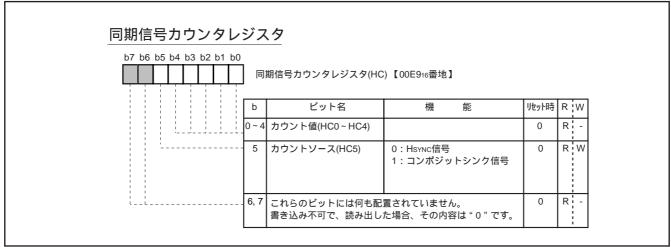

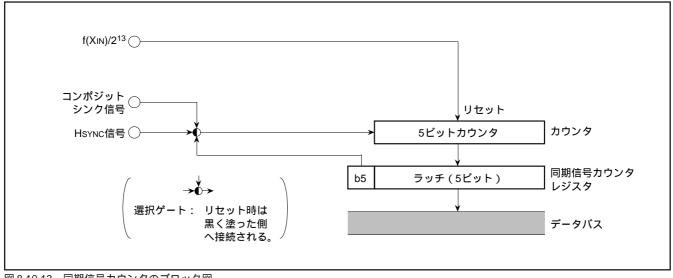

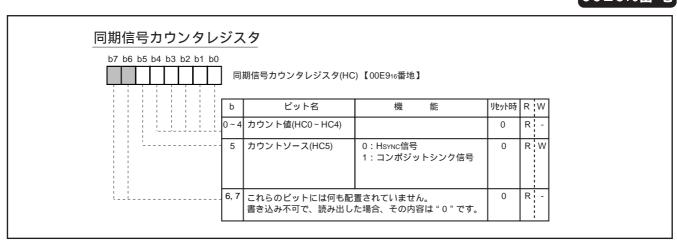

### 8.10.13 同期信号カウンタ

合は、"1F16"がラッチに格納されます。

同期信号カウンタは、データスライサ回路で映像信号から 取り出されたコンポジットシンク信号、又はHSYNC端子から 入力されたHSYNCをカウントソースとしてカウントします。 f(XIN)/213で生成される一定時間(T時間)のカウント値が、 5 ビットのラッチに格納されます。このためラッチの値は T時間周期で変化します。カウント値が "1F16"を越えた場

ラッチの値は、同期信号カウンタレジスタ(00E916番地) を読み出すことによって得ることができます。カウントソー スは、同期信号カウンタレジスタのビット5によって選択 します。

同期信号カウンタは、PWMモードレジスタ1(020816番地) のビット0を"0"に設定した状態で使用してください。

図8.10.12に同期信号カウンタレジスタを、図8.10.13に同 期信号カウンタのブロック図を示します。

図 8.10.12 同期信号カウンタレジスタ

図 8.10.13 同期信号カウンタのブロック図

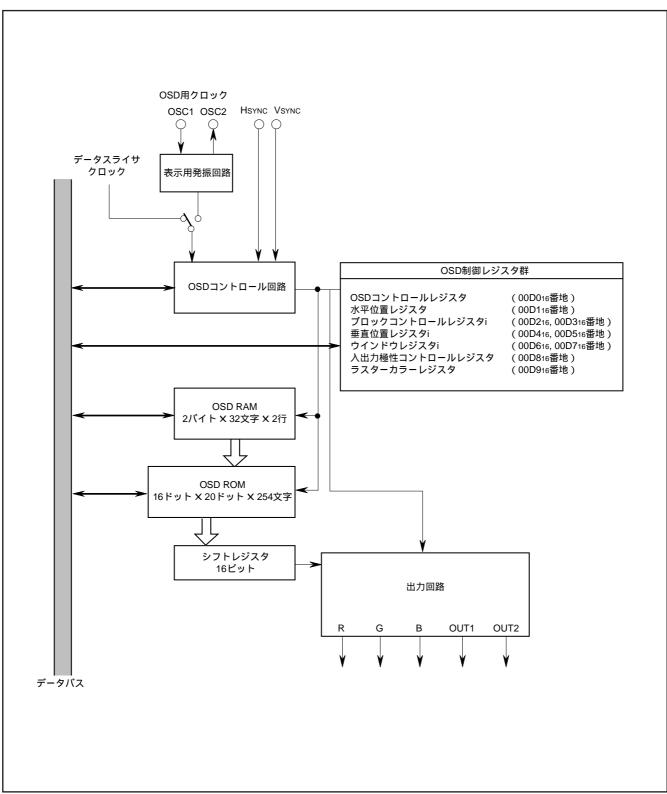

# 8.11 OSD 機能

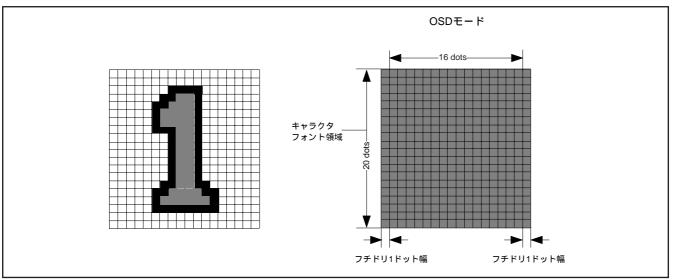

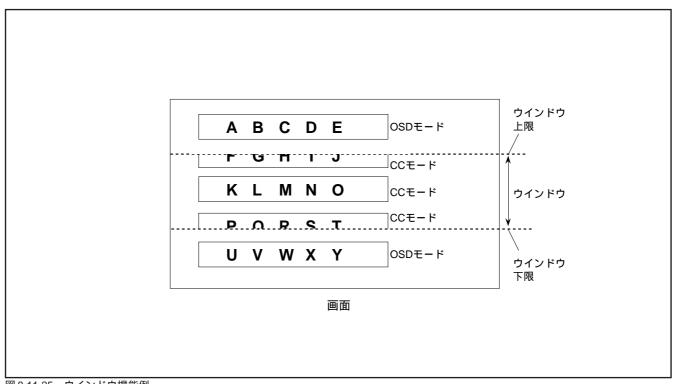

OSD 機能の概要を表 8.11.1 に示します。本マイクロコンピュータは 32 文字  $\times 2$  行の OSD 回路を内蔵しています。また、2 つの表示モードを備えており、ブロックコントロールレジスタ i (i = 1, 2) によって、ブロック単位に 2 つの表示モードが選択できます。

各表示の特長を以下に示します。

表 8.11.1 各表示モードの特長

| 項目          |        | 表示モード                         |                                  |  |

|-------------|--------|-------------------------------|----------------------------------|--|

|             |        | CCモード<br>(クローズドキャプションモード)     | OSDモード<br>(オンスクリーンディスプレイモード)     |  |

| 表示文字数       |        | 32文字×2行                       |                                  |  |

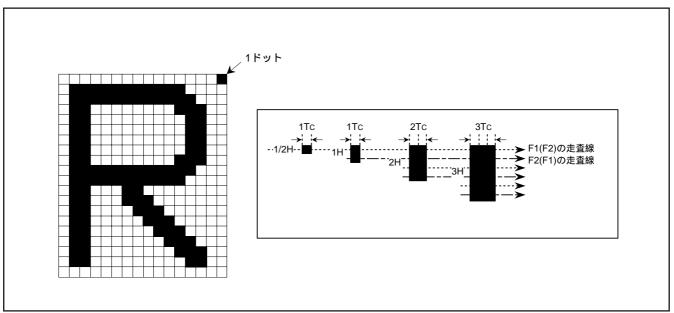

| ドット構成       |        | 16×26ドット(文字表示領域は16×20ドット)     | 16×20ドット                         |  |

| 文字種類        |        | 254種類                         |                                  |  |

| 文字サイズ       |        | 1種類                           | 8種類                              |  |

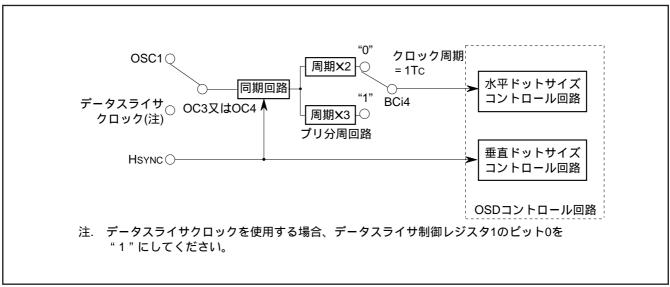

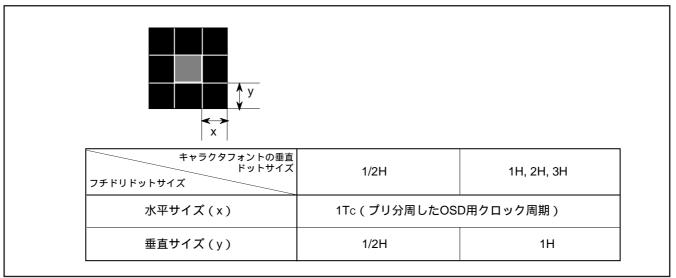

|             | プリ分周比  | 2倍 ( 固定 )                     | 2倍, 3倍                           |  |

|             | ドットサイズ | 1Tc × 1/2H                    | 1Tc×1/2H, 1Tc×1H, 2Tc×2H, 3Tc×3H |  |

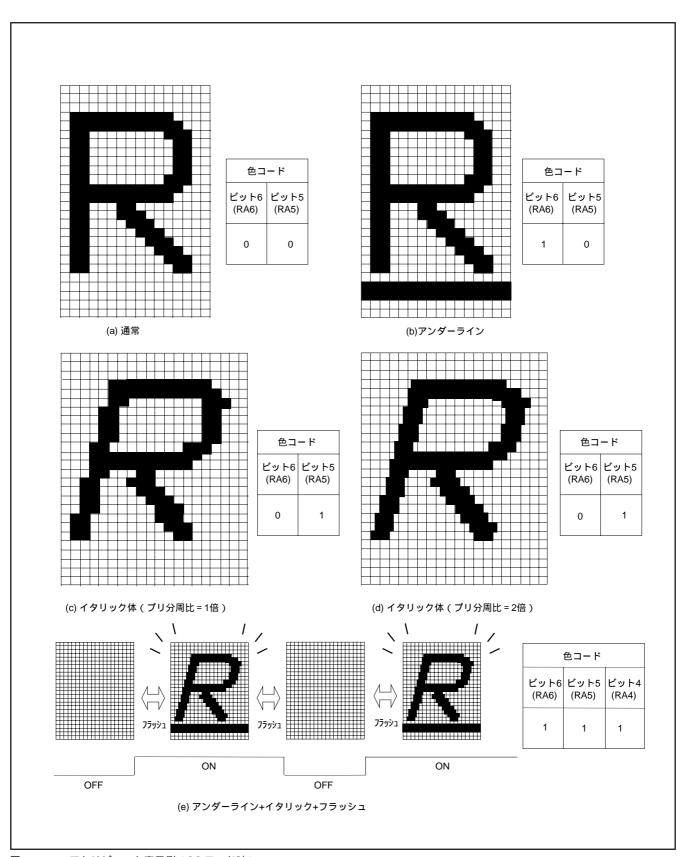

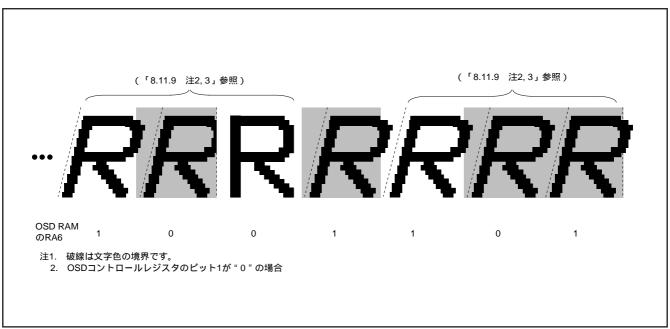

| アトリビュート     |        | スムーズイタリック, アンダーライン, フラッシュ(点滅) | フチドリ(黒)                          |  |

| キャラクタフォント着色 |        | 1画面8種類(文字単位)                  |                                  |  |

| 文字背景着色      |        |                               | 1画面8種類(文字単位)                     |  |

| OSD出力       |        | R, G, B                       |                                  |  |

| ラスター着色      |        | 可能(画面単位)                      |                                  |  |

| 他機能         |        | オートソリッドスペース機能<br>ウインドウ機能      |                                  |  |

| 表示位置        |        | 水平:128段階、垂直:512段階             |                                  |  |

| 拡張表示 (多行表示) |        | 可能                            |                                  |  |

注.文字サイズはドットサイズとプリ分周比によって指定します。「(2)ドットサイズ」を参照してください。

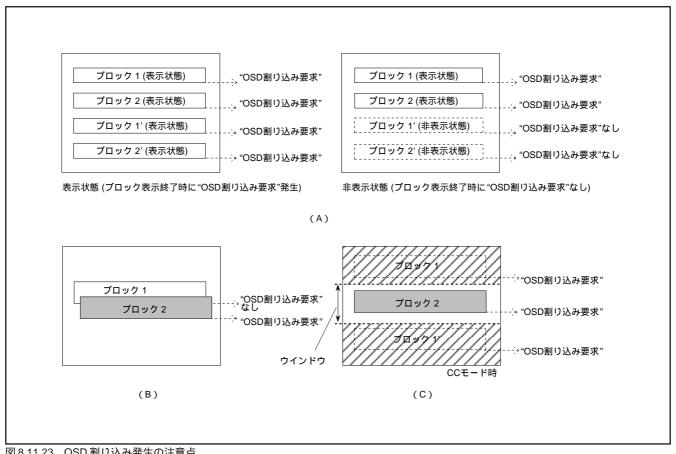

OSD回路には拡張表示モードがあり、1 行表示するごとに割り込みをかけ、ソフトウエアで表示の終了したブロックのデータを書き替えることにより、3 行以上の多行表示を行うことができます。

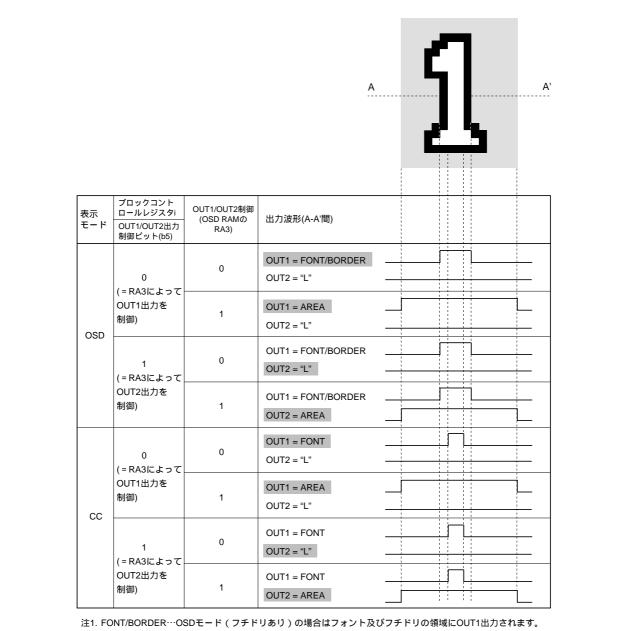

図 8.11.1 に OSD 用文字表示領域を、図 8.11.2 に OSD 回路 のブロック図を示します。また、図 8.11.3 に OSD コントロールレジスタを、図 8.11.4 にブロックコントロールレジスタ i を示します。

図 8.11.1 OSD 用文字表示領域

図 8.11.2 OSD 回路ブロック図

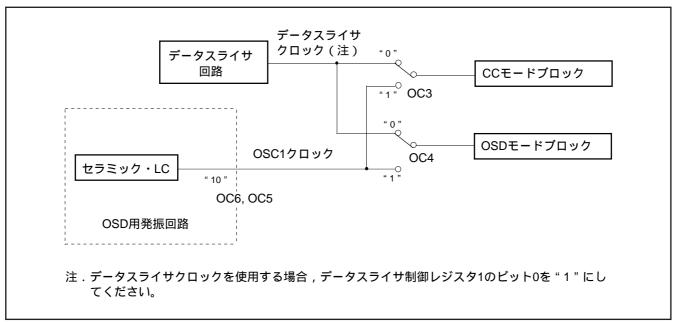

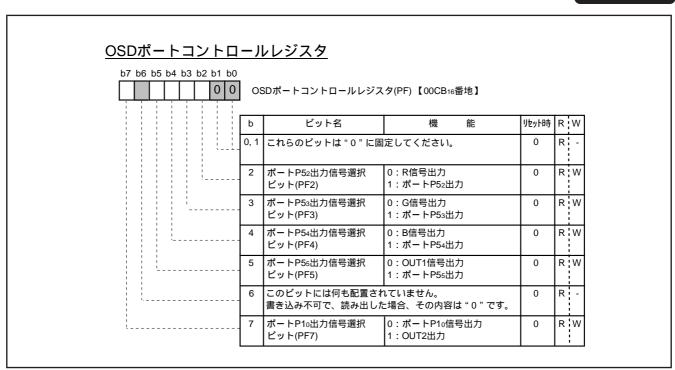

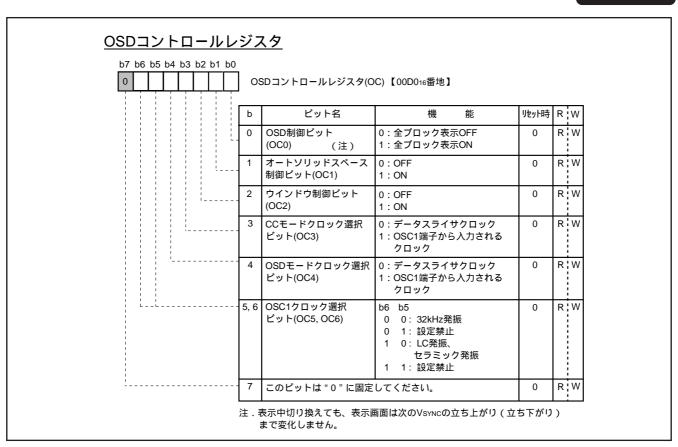

#### OSDコントロールレジスタ b7 b6 b5 b4 b3 b2 b1 b0 0 OSDコントロールレジスタ(OC) 【00D016番地】 リセット時 R W ビット名 能 b R¦W OSD制御ビット 0:全ブロック表示OFF 0 0 (注) 1:全ブロック表示ON オートソリッドスペース 0: OFF R¦W 0 制御ビット(OC1) ウインドウ制御ビット R W 0: OFF 0 (OC2) 1: ON RW CCモードクロック選択 0:データスライサクロック 0 1: OSC1端子から入力される ビット(OC3) クロック ┃OSDモードクロック選択 ┃0:データスライサクロック 0 R¦W 1:OSC1端子から入力される ビット(OC4) クロック 5,6 OSC1クロック選択 b6 b5 0 R¦W ビット(OC5, OC6) 0 0:32kHz発振 0 1: 設定禁止 1 0: LC発振、 セラミック発振 1 1: 設定禁止 このビットは"0"に固定してください。 0 R W 注.表示中切り換えても、表示画面は次のVsyncの立ち上がり(立ち下がり)

まで変化しません。

図 8.11.3 OSD コントロールレジスタ

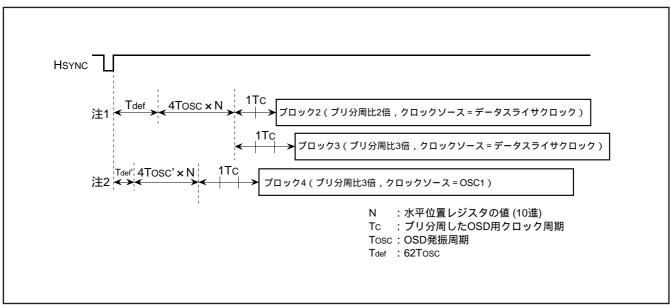

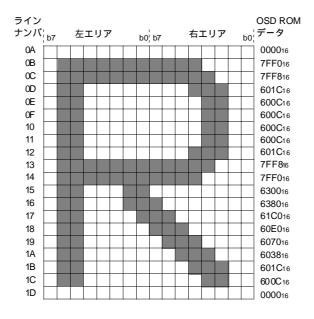

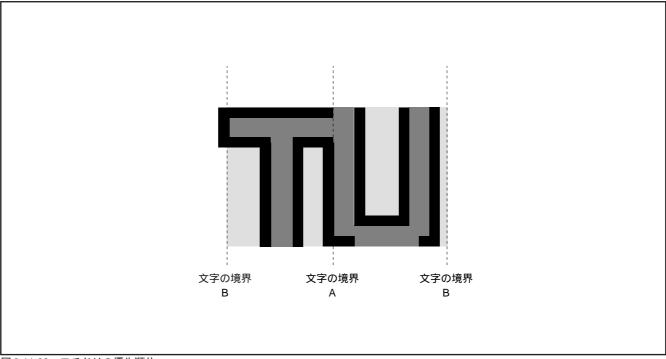

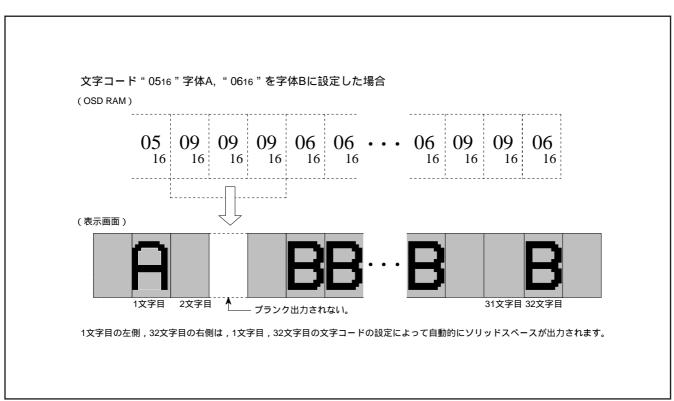

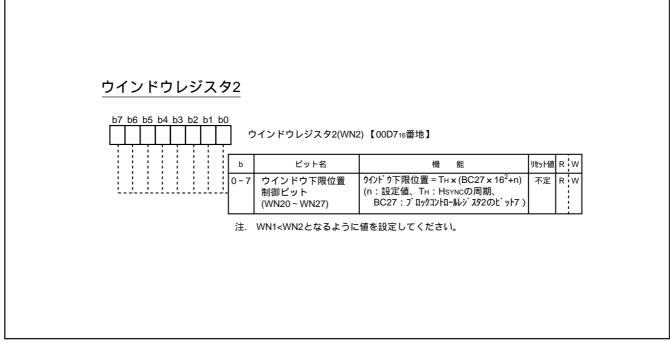

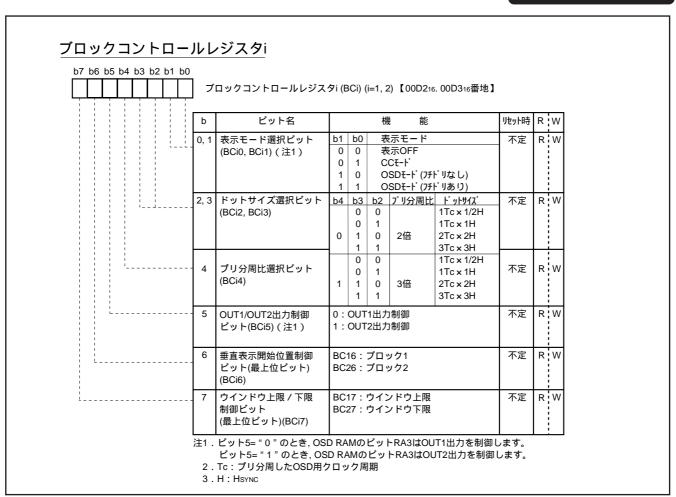

#### ブロックコントロールレジスタi b7 b6 b5 b4 b3 b2 b1 b0 ブロックコントロールレジスタi (BCi) (i=1, 2) 【00D216. 00D316番地】 ビット名 ルット時 R W 0, 1 表示モード選択ビット b1 b0 表示モード 不定 R¦W (BCi0, BCi1) (注1) 0 0 表示OFF 0 1 CCE-F OSDモ-ド(フチドリなし) 0 1 OSDモード(フチドリあり) 1 1 ドットサイズ選択ビット R W 2, 3 b4 b3 b2 プリ分周比 ドットサイズ 不定 1Tc x 1/2H (BCi2, BCi3) 0 0 1Tc x 1H 2Tc × 2H 0 1 0 2倍 3Tc × 3H 0 0 1Tc x 1/2H プリ分周比選択ビット R¦W 不定 1Tc x 1H 0 (BCi4) 1 Ω 3倍 2Tc×2H 1 1 1 $3Tc \times 3H$ 0:OUT1出力制御 RW 不定 OUT1/OUT2出力制御 ビット(BCi5) (注1) 1:OUT2出力制御 BC16: ブロック1 R W 垂直表示開始位置制御 不定 ビット(最上位ビット) BC26: ブロック2 (BCi6) ウインドウ上限 / 下限 BC17: ウインドウ上限 不定 R W 制御ビット BC27:ウインドウ下限 (最上位ビット)(BCi7) 注1. ビット5= "0"のとき, OSD RAMのビットRA3はOUT1出力を制御します。 ビット5= "1"のとき, OSD RAMのビットRA3はOUT2出力を制御します。 2. Tc: プリ分周したOSD用クロック周期 3 . H : Hsync

図8.11.4 ブロックコントロールレジスタi

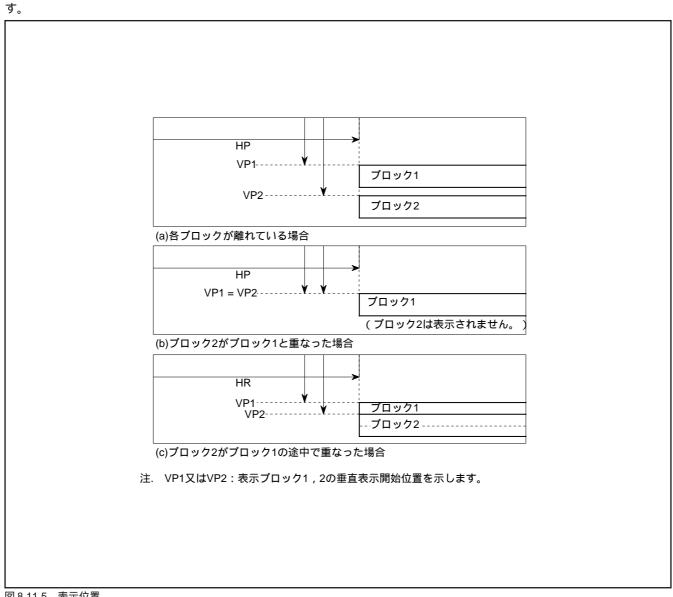

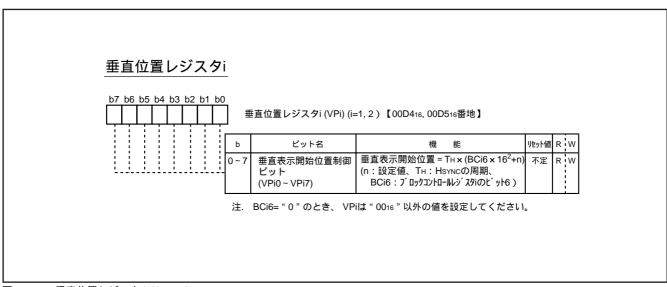

# 8.11.1 表示位置

文字の表示位置はブロック単位で指定します。ブロックは ブロック1、ブロック2の2つあり、1つのブロックには最大 32文字まで表示できます(後述「8.11.5 OSD用メモリ」を 参照してください。

各ブロックの表示位置は水平方向、垂直方向ともソフトウ エアによって設定できます。

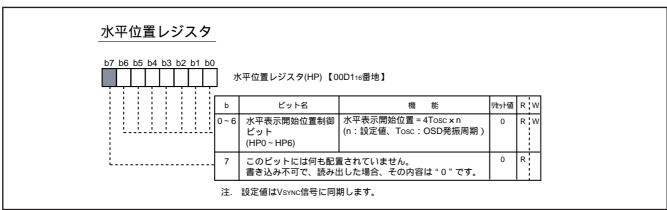

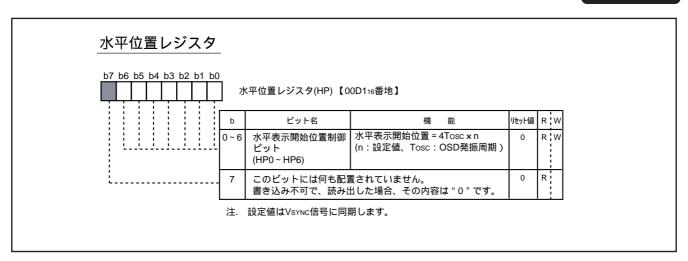

水平方向の表示開始位置は全ブロック共通で 4Tosc (Tosc: OSD 発振周期)単位で128段階の表示位置の中から 選択します。

垂直方向の表示開始位置はブロックごとに1TH(TH:水平 同期信号周期)単位で512段階の表示位置の中から選択しま

ブロックは以下の規則に従って表示されます。

- ・ ブロック 1 とブロック 2 が重なった場合(図 8.11.5 の (b) ) ブロック1が前面に表示されます。

- ・ 1つのブロック表示中に、他のブロックの表示開始位 置がきた場合(図8.11.5の(c))は、垂直表示開始位置 の設定値が大きい方が表示されます。

図 8.11.5 表示位置

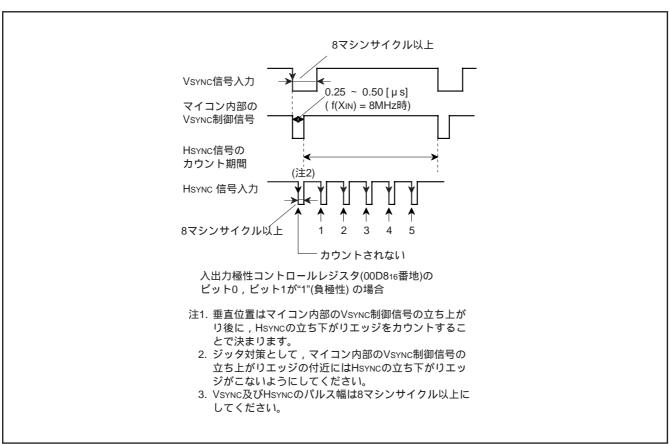

垂直方向の表示開始位置は水平同期信号(HSYNC)をカウントすることによって確定されます。この際、VSYNC、HSYNC信号が正極性(負極性)入力の場合VSYNC信号の立ち上がり(立ち下がり)エッジから一定期間後にHSYNC信号の立ち上がり(立ち下がり)エッジのカウントを開始します。そのため、ジッタ対策として、VSYNC信号の立ち上がり(立ち下がり)エッジまでの間隔は充分(2マシンサイクル以上)とるようにしてください。HSYNC信号及びVSYNC信号の極性は、入出力極性コントロールレジスタ(00D816番地)によって正極性、負極性のいずれかを選択できます。

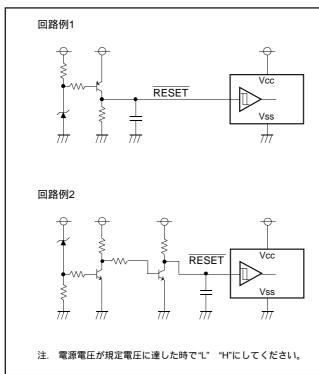

図 8.11.6 表示位置補足説明