# RENESAS

# R1QHA4436RBG,R1QHA4418RBG

| 144-Mbit DDR™II+ SRAM 2-word Burst    | R10DS0145EJ0200          |

|---------------------------------------|--------------------------|

| Architecture (2.0 Cycle Read latency) | Rev.2.00<br>Aug 01, 2014 |

## Description

The R1QHA4436RBG is a 4,194,304-word by 36-bit and the R1QHA4418RBG is a 8,388,608-word by 18-bit synchronous double data rate static RAM fabricated with advanced CMOS technology using full CMOS six-transistor memory cell. It integrates unique synchronous peripheral circuitry and a burst counter. All input registers are controlled by an input clock pair (K and /K) and are latched on the positive edge of K and /K. These products are suitable for applications which require synchronous operation, high speed, low voltage, high density and wide bit configuration. These products are packaged in 165-pin plastic FBGA package.

## Features

- Power Supply

- 1.8 V for core (VDD), 1.4 V to VDD for I/O (VDDQ)

- Clock

- Fast clock cycle time for high bandwidth

- Two input clocks (K and /K) for precise DDR timing at clock rising edges only

- Two output echo clocks (CQ and /CQ) simplify data capture in high-speed systems

- Clock-stop capability with µs restart

#### ■ I/O

- Common data input/output bus

- Pipelined double data rate operation

- HSTL I/O

- User programmable output impedance

- PLL circuitry for wide output data valid window and future frequency scaling

- Data valid pin (QVLD) to indicate valid data on the output

- Function

- Two-tick burst for low DDR transaction size

- Internally self-timed write control

- Simple control logic for easy depth expansion

- JTAG 1149.1 compatible test access port

- Package

- 165 FBGA package (15 x 17 x 1.4 mm)

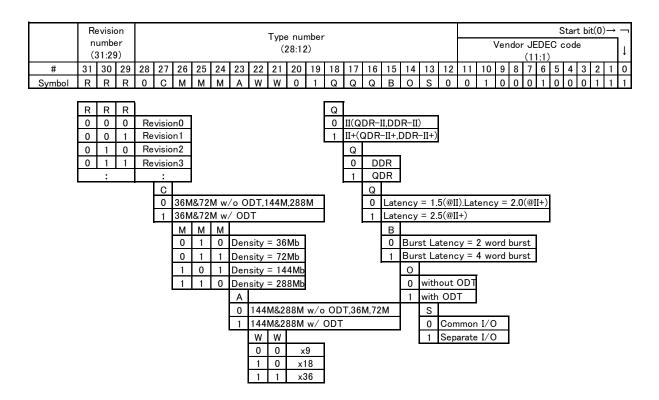

## Part Number Definition

| Column No. | 0   | 1     | 2       | 3     | 4       | 5     | 6      | 7      | 8      | 9       | 10     | 11     | -      | 12    | 13     | 14      | 15   | 16 |

|------------|-----|-------|---------|-------|---------|-------|--------|--------|--------|---------|--------|--------|--------|-------|--------|---------|------|----|

| Example    | R   | 1     | Q       | Н     | Α       | 4     | 4      | 3      | 6      | R       | В      | G      | -      | 2     | 5      | Ι       | В    | 0  |

|            | The | above | part nu | umber | is just | examp | le for | 144M I | DDRII+ | + B2 x3 | 36 400 | MHz, ´ | 15x17r | nm PK | G, Pb- | free pa | art. |    |

| No.    | -        | Comments                                                                                                                                     | No.                                                                                                           | -                    | Comments           | No.   | -       | Comments                 |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------|--------------------|-------|---------|--------------------------|

| 0-1    | R1       | Renesas Memory Prefix                                                                                                                        | 4                                                                                                             | A                    | Vdd = 1.8 V        |       | 60      | Frequency = 167MHz       |

|        | Q2       | QDR II B2 <sup>[*1]</sup> (L15) <sup>[*2]</sup>                                                                                              |                                                                                                               | 36                   | Density = 36Mb     |       | 50      | Frequency = 200MHz       |

|        | Q3       | QDR    B4 (L15)                                                                                                                              | 5-6                                                                                                           | 72                   | Density = 72Mb     |       | 40      | Frequency = 250MHz       |

|        | Q4       | DDR II B2 (L15)                                                                                                                              | B2 (L15) 44 Density = 144Mb   B4 (L15) 88 Density = 288Mb   B2 SIO <sup>[13]</sup> (L15) 09 Data width = 9bit |                      |                    |       | 36      | Frequency = 275MHz       |

|        | Q5       | DDR II B4 (L15)                                                                                                                              | 1                                                                                                             | 88                   | Density = 288Mb    |       | 33      | Frequency = 300MHz       |

|        | Q6       | DDR II B2 SIO <sup>[*3]</sup> (L15)                                                                                                          |                                                                                                               | 09                   | Data width = 9bit  | 40.40 | 30      | Frequency = 333MHz       |

|        | QA       | QDR II+ B4 L25 <sup>[*2]</sup>                                                                                                               | 7-8                                                                                                           | 18                   | Data width = 18bit | 12-13 | 27      | Frequency = 375MHz       |

|        | QB       | DDR II+ B2 L25                                                                                                                               |                                                                                                               | 36                   | Data width = 36bit |       | 25      | Frequency = 400MHz       |

|        | QC       | DDR II+ B4 L25                                                                                                                               |                                                                                                               | R                    | 1st Generation     |       | 22      | Frequency = 450MHz       |

|        | QD<br>QE | QDR II+ B4 L25 w/ODT <sup>[*4]</sup>                                                                                                         | 1                                                                                                             | Α                    | 2nd Generation     |       | 20      | Frequency = 500MHz       |

|        |          | DDR II+ B2 L25 w/ODT                                                                                                                         | -                                                                                                             | В                    | 3rd Generation     |       | 19      | Frequency = 533MHz       |

| 2-3    | QF       | DDR II+ B4 L25 w/ODT                                                                                                                         | 9                                                                                                             | С                    | 4th Generation     |       | 18      | Frequency = 550MHz       |

| 20     | QG       | QDR II+ B4 L20                                                                                                                               |                                                                                                               | D                    | 5th Generation     |       |         | Commercial temp.         |

|        | QH       | DDR II+ B2 L20                                                                                                                               |                                                                                                               | E                    | 6th Generation     |       | R       | Ta range = 0°C to 70°C   |

|        | QJ       | DDR II+ B4 L20                                                                                                                               |                                                                                                               | F                    | 7th Generation     | 14    | 1       | Industrial temp.         |

|        | QK       | QDR II+ B4 L20 w/ODT                                                                                                                         | 10-11                                                                                                         | BG                   | PKG= BGA 15x17 mm  |       | I       | Ta range = -40°C to 85°C |

|        | QL       | DDR II+ B2 L20 w/ODT                                                                                                                         | 10-11                                                                                                         | BB                   | PKG= BGA 13x15 mm  |       | Α       | Pb and Tray              |

|        | QM       | DDR II+ B4 L20 w/ODT                                                                                                                         |                                                                                                               |                      |                    | 15    | В       | Pb-free and Tray         |

|        | QN       | QDR II+ B2 L20                                                                                                                               |                                                                                                               |                      |                    | 15    | Т       | Pb and Tape&Reel         |

|        | QP       | QDR II+ B2 L20 w/ODT                                                                                                                         |                                                                                                               | -                    |                    |       | S       | Pb-free and Tape&Reel    |

|        |          |                                                                                                                                              | -                                                                                                             |                      | -                  | 16    | 0 to 9, |                          |

|        | -        | -                                                                                                                                            |                                                                                                               |                      |                    |       | A to Z  | Renesas internal use     |

|        |          |                                                                                                                                              |                                                                                                               |                      |                    |       | or None |                          |

| Note1: |          | [*1] B=Burst length (B2: Burst leng<br>[*2] L=Read Latency (L15: Read L<br>[*3] SIO=Separate VO<br>[*4] ODT=On die termination               |                                                                                                               |                      |                    | ·)    |         |                          |

| Note2: |          | Package Marking Name<br>Pb parts: Marking Name = Part N<br>Pb-free parts: Marking Name = P<br>(Example) R1QAA4436RBG-20F<br>R1QAA4436RBG-20F | art Number(<br>R                                                                                              | (0-14) + "I<br>Pb pa | ts                 |       |         |                          |

| Note3: |          | Pb : RoHS Compliance Level<br>Pb-free: RoHS Compliance Level                                                                                 |                                                                                                               |                      |                    |       |         |                          |

|        |          | R1Q*A series support both "Comn                                                                                                              |                                                                                                               | When all the dust of |                    |       |         |                          |

#### Part Number Information

| Ordering part number | Organization<br>(word x bit) | Cycle time | Clock<br>frequency | Operating<br>Ambient<br>Temperature | Core<br>Supply<br>Voltage<br>(V) | Package                |

|----------------------|------------------------------|------------|--------------------|-------------------------------------|----------------------------------|------------------------|

| R1QHA4436RBG-25IA0   | 4M x 36                      | 2.50ns     | 400MHz             | T <sub>A</sub> = −40 to 85°C        | 1.8 ± 0.1                        | 165-pin<br>PLASTIC BGA |

| R1QHA4418RBG-25IA0   | 8M x 18                      | 2.50ns     | 400MHz             |                                     |                                  | (15 x 17)<br>Pb        |

| R1QHA4436RBG-25IB0   | 4M x 36                      | 2.50ns     | 400MHz             | T <sub>A</sub> = −40 to 85°C        | 1.8 ± 0.1                        | 165-pin<br>PLASTIC BGA |

| R1QHA4418RBG-25IB0   | 8M x 18                      | 2.50ns     | 400MHz             |                                     |                                  | (15 x 17)<br>Pb-Free   |

## **Pin Arrangement**

|   |       |      |      |      | []   | (op View) | )    |      |      |      |      |

|---|-------|------|------|------|------|-----------|------|------|------|------|------|

|   | 1     | 2    | 3    | 4    | 5    | 6         | 7    | 8    | 9    | 10   | 11   |

| Α | /CQ   | SA   | SA   | R-/W | /BW2 | /K        | /BW1 | /LD  | SA   | SA   | CQ   |

| в | NC    | DQ27 | DQ18 | SA   | /BW3 | К         | /BW0 | SA   | NC   | NC   | DQ8  |

| С | NC    | NC   | DQ28 | VSS  | SA   | NC        | SA   | VSS  | NC   | DQ17 | DQ7  |

| D | NC    | DQ29 | DQ19 | VSS  | VSS  | VSS       | VSS  | VSS  | NC   | NC   | DQ16 |

| Е | NC    | NC   | DQ20 | VDDQ | VSS  | VSS       | VSS  | VDDQ | NC   | DQ15 | DQ6  |

| F | NC    | DQ30 | DQ21 | VDDQ | VDD  | VSS       | VDD  | VDDQ | NC   | NC   | DQ5  |

| G | NC    | DQ31 | DQ22 | VDDQ | VDD  | VSS       | VDD  | VDDQ | NC   | NC   | DQ14 |

| н | /DOFF | VREF | VDDQ | VDDQ | VDD  | VSS       | VDD  | VDDQ | VDDQ | VREF | ZQ   |

| J | NC    | NC   | DQ32 | VDDQ | VDD  | VSS       | VDD  | VDDQ | NC   | DQ13 | DQ4  |

| κ | NC    | NC   | DQ23 | VDDQ | VDD  | VSS       | VDD  | VDDQ | NC   | DQ12 | DQ3  |

| L | NC    | DQ33 | DQ24 | VDDQ | VSS  | VSS       | VSS  | VDDQ | NC   | NC   | DQ2  |

| М | NC    | NC   | DQ34 | VSS  | VSS  | VSS       | VSS  | VSS  | NC   | DQ11 | DQ1  |

| Ν | NC    | DQ35 | DQ25 | VSS  | SA   | SA        | SA   | VSS  | NC   | NC   | DQ10 |

| Ρ | NC    | NC   | DQ26 | SA   | SA   | QVLD      | SA   | SA   | NC   | DQ9  | DQ0  |

| R | TDO   | тск  | SA   | SA   | SA   | NC        | SA   | SA   | SA   | TMS  | TDI  |

[R1QHA4436RBG]

4M x 36

Notes: 1. Address expansion order for future higher density SRAMs:  $10A \rightarrow 2A \rightarrow 7A \rightarrow 5B$ .

2. NC pins can be left floating or connected to 0V to VDDQ

#### [R1QHA4418RBG]

8M x 18

(Top View)

|   | 1     | 2    | 3    | 4    | 5    | 6          | 7    | 8    | 9    | 10   | 11  |

|---|-------|------|------|------|------|------------|------|------|------|------|-----|

| Α | /CQ   | SA   | SA   | R-/W | /BW1 | / <b>K</b> | SA   | /LD  | SA   | SA   | CQ  |

| в | NC    | DQ9  | NC   | SA   | NC   | к          | /BW0 | SA   | NC   | NC   | DQ8 |

| С | NC    | NC   | NC   | VSS  | SA   | NC         | SA   | VSS  | NC   | DQ7  | NC  |

| D | NC    | NC   | DQ10 | VSS  | VSS  | VSS        | VSS  | VSS  | NC   | NC   | NC  |

| Е | NC    | NC   | DQ11 | VDDQ | VSS  | VSS        | VSS  | VDDQ | NC   | NC   | DQ6 |

| F | NC    | DQ12 | NC   | VDDQ | VDD  | VSS        | VDD  | VDDQ | NC   | NC   | DQ5 |

| G | NC    | NC   | DQ13 | VDDQ | VDD  | VSS        | VDD  | VDDQ | NC   | NC   | NC  |

| н | /DOFF | VREF | VDDQ | VDDQ | VDD  | VSS        | VDD  | VDDQ | VDDQ | VREF | ZQ  |

| J | NC    | NC   | NC   | VDDQ | VDD  | VSS        | VDD  | VDDQ | NC   | DQ4  | NC  |

| κ | NC    | NC   | DQ14 | VDDQ | VDD  | VSS        | VDD  | VDDQ | NC   | NC   | DQ3 |

| L | NC    | DQ15 | NC   | VDDQ | VSS  | VSS        | VSS  | VDDQ | NC   | NC   | DQ2 |

| м | NC    | NC   | NC   | VSS  | VSS  | VSS        | VSS  | VSS  | NC   | DQ1  | NC  |

| Ν | NC    | NC   | DQ16 | VSS  | SA   | SA         | SA   | VSS  | NC   | NC   | NC  |

| Ρ | NC    | NC   | DQ17 | SA   | SA   | QVLD       | SA   | SA   | NC   | NC   | DQ0 |

| R | TDO   | тск  | SA   | SA   | SA   | NC         | SA   | SA   | SA   | TMS  | TDI |

Notes: 1. Address expansion order for future higher density SRAMs:  $10A \rightarrow 2A \rightarrow 7A \rightarrow 5B$ .

2. NC pins can be left floating or connected to 0V to VDDQ

# **Pin Descriptions**

| Name       | I/O type | Descriptions                                                                                                                                                                                                                                                                                                                                                                                   | Note |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| SA         | Input    | Synchronous address inputs: These inputs are registered and must meet the setup and hold times around the rising edge of K. These inputs are ignored when device is deselected.                                                                                                                                                                                                                |      |

| /LD        | Input    | Synchronous load: This input is brought low when a bus cycle sequence is to be defined. This definition includes address and READ / WRITE direction.                                                                                                                                                                                                                                           |      |

| R-/W       | Input    | Synchronous read / write Input: When /LD is low, this input designates the access type (READ when R-/W is high, WRITE when R-/W is low) for the loaded address. R-/W must meet the setup and hold times around the rising edge of K.                                                                                                                                                           |      |

| /BWx       | Input    | Synchronous byte writes: When low, these inputs cause their respective byte to be registered and written during WRITE cycles. These signals are sampled on the same edge as the corresponding data and must meet setup and hold times around the rising edges of K and /K for each of the rising edge comprising the WRITE cycle. See Byte Write Truth Table for signal to data relationship.  |      |

| K, /K      | Input    | Input clock: This input clock pair registers address and control inputs on the rising edge of K, and registers data on the rising edge of K and the rising edge of /K. /K is ideally 180 degrees out of phase with K. All synchronous inputs must meet setup and hold times around the clock rising edges. These balls cannot remain V <sub>REF</sub> level.                                   |      |

| /DOFF      | Input    | PLL disable: When low, this input causes the PLL to be bypassed for stable, low frequency operation.                                                                                                                                                                                                                                                                                           |      |

| TMS<br>TDI | Input    | IEEE1149.1 test inputs: 1.8 V I/O levels. These balls may be left unconnected if the JTAG function is not used in the circuit.                                                                                                                                                                                                                                                                 |      |

| ТСК        | Input    | IEEE1149.1 clock input: 1.8 V I/O levels. This ball must be tied to $V_{\rm SS}$ if the JTAG function is not used in the circuit.                                                                                                                                                                                                                                                              |      |

| ZQ         | Input    | Output impedance matching input: This input is used to tune the device outputs to the system data bus impedance. DQ and CQ output impedance are set to $0.2 \times RQ$ , where RQ is a resistor from this ball to ground. This ball can be connected directly to $V_{DDQ}$ , which enables the minimum impedance mode. This ball cannot be connected directly to $V_{SS}$ or left unconnected. |      |

| Name             | I/O type        | Descriptions                                                                                                                                                                                                                                                                        | Note |

|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $DQ_0$ to $DQ_n$ | Input<br>Output | Synchronous data I/Os: Input data must meet setup and hold times around the rising edges of K and /K. Output data is synchronized to the K clock.<br>The $\times$ 18 device uses DQ0 to DQ17. DQ18 to DQ35 should be treated as NC pin.<br>The $\times$ 36 device uses DQ0 to DQ35. |      |

| CQ, /CQ          | Output          | Synchronous echo clock outputs: The edges of these outputs are tightly matched to the synchronous data outputs and can be used as a data valid indication. These signals run freely and do not stop when DQ tri-states.                                                             |      |

| TDO              | Output          | IEEE 1149.1 test output: 1.8 V I/O level.                                                                                                                                                                                                                                           |      |

| QVLD             | Output          | Valid output indicator: The Q Valid indicates valid output data. QVLD is edge aligned with CQ and /CQ.                                                                                                                                                                              |      |

| V <sub>DD</sub>  | Supply          | Power supply: 1.8 V nominal. See DC Characteristics and Operating Conditions for range.                                                                                                                                                                                             | 1    |

| V <sub>DDQ</sub> | Supply          | Power supply: Isolated output buffer supply. Nominally 1.5 V. See DC Characteristics and Operating Conditions for range.                                                                                                                                                            | 1    |

| V <sub>SS</sub>  | Supply          | Power supply: Ground.                                                                                                                                                                                                                                                               | 1    |

| V <sub>REF</sub> | -               | HSTL input reference voltage: Nominally $V_{DDQ}/2$ , but may be adjusted to improve system noise margin. Provides a reference voltage for the HSTL input buffers.                                                                                                                  |      |

| NC               | -               | No connect: These pins can be left floating or connected to $0V$ to $V_{DDQ}$ .                                                                                                                                                                                                     |      |

Notes:

1. All power supply and ground balls must be connected for proper operation of the device.

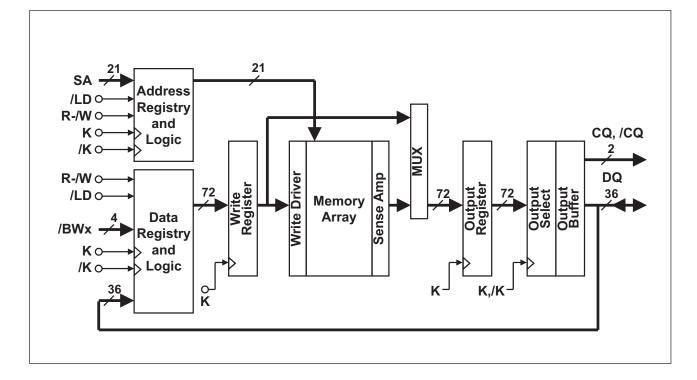

#### **Block Diagram**

## [R1QHA4436RBG]

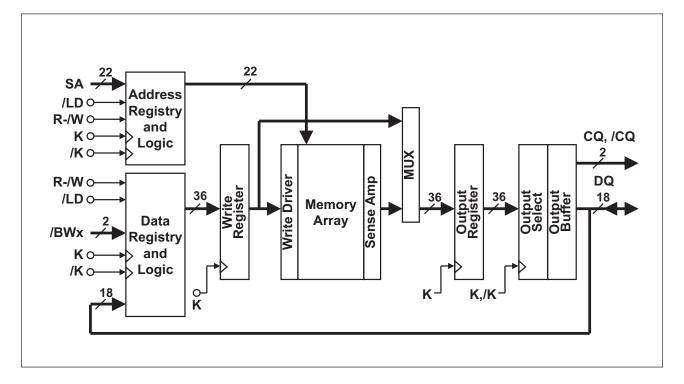

#### [R1QHA4418RBG]

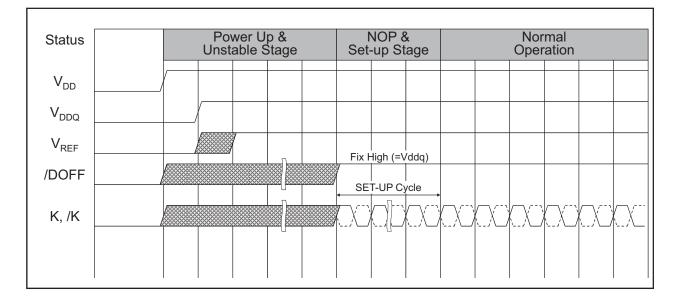

## **Power-up and Initialization Sequence**

V<sub>DD</sub> must be stable before K, /K clocks are applied.

- Recommended voltage application sequence :  $V_{SS} \rightarrow V_{DD} \rightarrow V_{DDQ}$  &  $V_{REF} \rightarrow V_{IN}$ . (0 V to  $V_{DD}$ ,  $V_{DDQ} < 200$  ms)

- Apply  $V_{\text{REF}}$  after  $V_{\text{DDQ}}$  or at the same time as  $V_{\text{DDQ}}.$

- Then execute either one of the following sequences.

#### 1. Single Clock Mode

- Drive /DOFF high (/DOFF can be tied high from the start).

- Then provide stable clocks (K, /K) for at least 20 us.

#### 2. PLL Off Mode (/DOFF tied low)

- In the "NOP and setup stage", provide stable clocks (K, /K) for at least 20 us.

## **PLL Constraints**

- 1. These chips use the PLL. The clock input should have low phase jitter which is specified as tKC var.

- The lower end of the frequency at which the PLL can operate is 250 MHz. (Please refer to AC Characteristics table for detail.)

- 3. When the operating frequency is changed or /DOFF level is changed, setup cycles are required again.

## Programmable Output Impedance

1. Output buffer impedance can be programmed by terminating the ZQ ball to  $V_{SS}$  through a precision resistor (RQ). The value of RQ is five times the output impedance desired. The allowable range of RQ to guarantee impedance matching with a tolerance of 15% is between 175  $\Omega$  and 350  $\Omega$ . The total external capacitance of ZQ ball must be less than 7.5 pF.

## QVLD (Valid data indicator)

1. QVLD is provided on the QDR-II+ and DDR-II+ to simplify data capture on high speed systems. The Q Valid indicates valid output data. QVLD is activated half cycle before the read data for the receiver to be ready for capturing the data. QVLD is inactivated half cycle before the read finish for the receiver to stop capturing the data. QVLD is edge aligned with CQ and /CQ.

## K Truth Table

| Operation                                                                                     | К            | /LD    | R-/W |                                              | DQ                 |                     |

|-----------------------------------------------------------------------------------------------|--------------|--------|------|----------------------------------------------|--------------------|---------------------|

| Write Cycle:<br>Load address, input write<br>data on two consecutive<br>K and /K rising edges | Î            | L      | L    | Data in<br>Input<br>data<br>Input<br>clock   | D(A+0)<br>K(t+1) ↑ | D(A+1)<br>/K(t+1) ↑ |

| Read Cycle:<br>Load address, output read<br>data on two consecutive<br>K and /K rising edges  | î            | L      | н    | Data out<br>Output<br>data<br>Input<br>clock | Q(A+0)<br>K(t+2) ↑ | Q(A+1)<br>/K(t+2) ↑ |

| NOP (No operation)<br>Standby (Clock stopped)                                                 | ↑<br>Stopped | H<br>× | ×××  | High-Z<br>Previous                           | state              |                     |

- 1. H: high level, L: low level,  $\times$ : don't care,  $\uparrow$ : rising edge.

- 2. Data inputs are registered at K and /K rising edges. Data outputs are delivered at K clock edges.

- 3. /LD and R-/W must meet setup/hold times around the rising edges (low to high) of K and are registered at the rising edge of K.

- 4. This device contains circuitry that will ensure the outputs will be in high-Z during power-up.

- 5. Refer to state diagram and timing diagrams for clarification.

- 6. When clocks are stopped, the following cases are recommended; the case of K = low, /K = high, or the case of K = high, /K = low. This condition is not essential, but permits most rapid restart by overcoming transmission line charging symmetrically.

- 7. A+0 refers to the address input during a WRITE or READ cycle. A+1 refers to the next internal burst address in accordance with the linear burst sequence.

## Byte Write Truth Table ( x 36 )

| Operation        | К        | /K       | /BW0 | /BW1 | /BW2 | /BW3 |

|------------------|----------|----------|------|------|------|------|

| Write D0 to D35  | ↑        | -        | L    | L    | L    | L    |

|                  | -        | <b>↑</b> | L    | L    | L    | L    |

| Write D0 to D8   | ↑        | -        | L    | Н    | Н    | Н    |

|                  | -        | <b>↑</b> | L    | Н    | Н    | Н    |

| Write D9 to D17  | <b>↑</b> | -        | Н    | L    | Н    | Н    |

|                  | -        | <b>↑</b> | Н    | L    | Н    | Н    |

| Write D18 to D26 | ↑ (      | -        | Н    | Н    | L    | Н    |

|                  | -        | ↑        | Н    | Н    | L    | Н    |

| Write D27 to D35 | ↑        | -        | Н    | Н    | Н    | L    |

|                  | -        | <b>↑</b> | Н    | Н    | Н    | L    |

| Write nothing    | <b>↑</b> | -        | Н    | Н    | Н    | Н    |

|                  | -        | <b>↑</b> | Н    | Н    | Н    | Н    |

Notes:

- 1. H: high level, L: low level,  $\uparrow$ : rising edge.

- 2. Assumes a WRITE cycle was initiated. /BWx can be altered for any portion of the BURST WRITE operation provided that the setup and hold requirements are satisfied.

## Byte Write Truth Table (x 18)

| Operation       | К | /K  | /BW0 | /BW1 |

|-----------------|---|-----|------|------|

| Write D0 to D17 | 1 | -   | L    | L    |

| -               | - | ↑ ( | L    | L    |

| Write D0 to D8  | ↑ | -   | L    | Н    |

| -               | - | ↑ ( | L    | Н    |

| Write D9 to D17 | ↑ | -   | Н    | L    |

| -               | - | ↑ ( | Н    | L    |

| Write nothing   | ↑ | -   | Н    | Н    |

|                 | - | ↑ ( | Н    | Н    |

- 1. H: high level, L: low level,  $\uparrow$ : rising edge.

- 2. Assumes a WRITE cycle was initiated. /BWx can be altered for any portion of the BURST WRITE operation provided that the setup and hold requirements are satisfied.

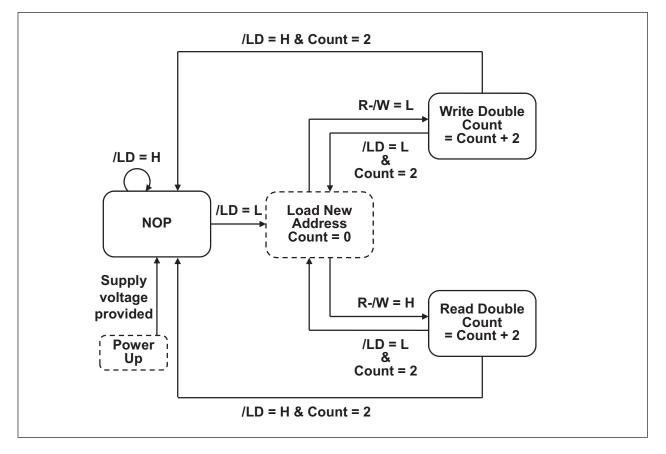

## **Bus Cycle State Diagram**

- 1. Bus cycle is terminated at the end of this sequence (burst count = 2).

- 2. State machine control timing sequence is controlled by K.

## **Electrical Characteristics**

#### **Absolute Maximum Ratings**

| Parameter                 | Symbol           | Rating                                         | Unit | Notes |

|---------------------------|------------------|------------------------------------------------|------|-------|

| Input voltage on any ball | V <sub>IN</sub>  | –0.5 to V <sub>DD</sub> + 0.5<br>(2.5 V max.)  | V    | 1,4   |

| Input/output voltage      | V <sub>I/O</sub> | –0.5 to V <sub>DDQ</sub> + 0.5<br>(2.5 V max.) | V    | 1,4   |

| Core supply voltage       | V <sub>DD</sub>  | –0.5 to 2.5                                    | V    | 1,4   |

| Output supply voltage     | V <sub>DDQ</sub> | -0.5 to V <sub>DD</sub>                        | V    | 1,4   |

| Junction temperature      | Tj               | +125 (max)                                     | °C   | 5     |

| Storage temperature       | T <sub>STG</sub> | –55 to +125                                    | °C   |       |

Notes:

- 1. All voltage is referenced to V<sub>SS</sub>.

- 2. Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted the Operation Conditions. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

- 3. These CMOS memory circuits have been designed to meet the DC and AC specifications shown in the tables after thermal equilibrium has been established.

- 4. The following supply voltage application sequence is recommended:  $V_{SS}$ ,  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{REF}$  then  $V_{IN}$ . Remember, according to the Absolute Maximum Ratings table,  $V_{DDQ}$  is not to exceed 2.5 V, whatever the instantaneous value of  $V_{DDQ}$ .

- 5. Some method of cooling or airflow should be considered in the system.

| Parameter                   | Symbol               | Min                    | Тур  | Мах                    | Unit | Notes |

|-----------------------------|----------------------|------------------------|------|------------------------|------|-------|

| Power supply voltage core   | V <sub>DD</sub>      | 1.7                    | 1.8  | 1.9                    | V    | 1     |

| Power supply voltage I/O    | V <sub>DDQ</sub>     | 1.4                    | 1.5  | V <sub>DD</sub>        | V    | 1,2   |

| Input reference voltage I/O | V <sub>REF</sub>     | 0.68                   | 0.75 | 0.95                   | V    | 3     |

| Input high voltage          | V <sub>IH (DC)</sub> | V <sub>REF</sub> + 0.1 | -    | V <sub>DDQ</sub> + 0.3 | V    | 1,4,5 |

| Input low voltage           | VIL (DC)             | -0.3                   | -    | V <sub>REF</sub> - 0.1 | V    | 1,4,5 |

#### **Recommended DC Operating Conditions**

Notes:

- 1. At power-up,  $V_{DD}$  and  $V_{DDQ}$  are assumed to be a linear ramp from 0V to  $V_{DD}$ (min.) or  $V_{DDQ}$ (min.) within 200ms. During this time,  $V_{DDQ} < V_{DD}$  and  $V_{IH} < V_{DDQ}$ . During normal operation,  $V_{DDQ}$  must not exceed  $V_{DD}$ .

- 2. Please pay attention to Tj not to exceed the temperature shown in the absolute maximum ratings table due to current from V<sub>DDQ</sub>.

- 3. Peak to peak AC component superimposed on  $V_{REF}$  may not exceed 5% of  $V_{REF}$ .

- 4. These are DC test criteria. The AC  $V_{IH}$  /  $V_{IL}$  levels are defined separately to measure timing parameters.

- 5. Overshoot:  $V_{IH (AC)} \le V_{DDQ} + 0.5 V$  for  $t \le t_{KHKH}/2$

Undershoot:  $V_{IL (AC)} \ge -0.5 \text{ V}$  for  $t \le t_{KHKH/2}$

During normal operation,  $V_{IH(DC)}$  must not exceed  $V_{DDQ}$  and  $V_{IL(DC)}$  must not be lower than  $V_{SS.}$

## **DC Characteristics**

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, V_{DD} = 1.8\text{V} \pm 0.1\text{V}, V_{DDQ} = 1.5\text{V}, V_{REF} = 0.75\text{V})$

| Parameter              | Symbol                   | Test condition              | MIN.                     | MAX.                       | Unit | Notes |

|------------------------|--------------------------|-----------------------------|--------------------------|----------------------------|------|-------|

|                        |                          |                             |                          | -25                        |      |       |

| Operating Supply       | I <sub>DD</sub>          | (x36)                       |                          | 1070                       | mA   |       |

| Current                |                          | (x18)                       |                          | 910                        |      | 1,2,3 |

| (Write / Read)         |                          |                             |                          |                            |      |       |

| Standby Supply         | I <sub>SB1</sub>         | (x36)                       |                          | 880                        | mA   |       |

| Current                |                          | (x18)                       |                          | 770                        |      | 2,4,5 |

| (NOP)                  |                          |                             |                          |                            |      |       |

| Input leakage current  | ILI                      | <b>i</b>                    | -2                       | 2                          | μA   | 9     |

| Output leakage current | ILO                      |                             | -5                       | 5                          | μA   | 10    |

| Output high voltage    | V <sub>он</sub><br>(Low) | I <sub>OH</sub>   ≤ 0.1 mA  | $V_{\text{DDQ}} - 0.2$   | V <sub>DDQ</sub>           | V    | 8     |

|                        | V <sub>OH</sub>          | Note 6                      | $V_{DDQ}/2 - 0.12$       | V <sub>DDQ</sub> /2 + 0.12 | V    | 8     |

| Output low voltage     | V <sub>o∟</sub><br>(Low) | $I_{OL} \le 0.1 \text{ mA}$ | V <sub>SS</sub>          | 0.2                        | V    | 8     |

|                        | V <sub>oL</sub>          | Note 7                      | V <sub>DDQ</sub> /2-0.12 | V <sub>DDQ</sub> /2+ 0.12  | V    | 8     |

- 1. All inputs (except ZQ,  $V_{REF}$ ) are held at either  $V_{IH}$  or  $V_{IL}$ .

- 2.  $I_{OUT} = 0$  mA.  $V_{DD} = V_{DD}$  max,  $t_{KHKH} = t_{KHKH}$  min.

- Operating supply currents (I<sub>DD</sub>) are measured at 100% bus utilization. I<sub>DD</sub> of DDR family is current of device with 100% write cycle (if I<sub>DD</sub>(Write) > I<sub>DD</sub>(Read)) or 100% read cycle (if I<sub>DD</sub>(Write) < I<sub>DD</sub>(Read)).

- 4. All address / data inputs are static at either  $V_{IN} > V_{IH}$  or  $V_{IN} < V_{IL}$ .

- 5. Reference value. (Condition = NOP currents are valid when entering NOP after all pending READ and WRITE cycles are completed. )

- 6. Outputs are impedance-controlled.  $|I_{OH}| = (V_{DDQ}/2)/(RQ/5)$  for values of 175  $\Omega \le RQ \le 350 \Omega$ .

- 7. Outputs are impedance-controlled.  $I_{OL} = (V_{DDQ}/2)/(RQ/5)$  for values of 175  $\Omega \le RQ \le 350 \Omega$ .

- 8. AC load current is higher than the shown DC values. AC I/O curves are available upon request.

- 9.  $0 \le V_{IN} \le V_{DDQ}$  for all input balls (except  $V_{REF}$ , ZQ, TCK, TMS, TDI ball).

- 10.  $0 \le V_{OUT} \le V_{DDQ}$  (except TDO ball), output disabled.

#### Thermal Resistance

| Parameter           | Symbol          | Airflow | Тур | Unit | Test condition   | Notes |

|---------------------|-----------------|---------|-----|------|------------------|-------|

| Junction to Ambient | θ <sub>JA</sub> | 1 m/s   | 9.7 | °C/W | EIA/JEDEC JESD51 | 1     |

| Junction to Case    | θ <sub>JC</sub> | -       | 4.4 |      |                  |       |

Notes:

1. These parameters are calculated under the condition. These are reference values.

2.  $Tj = Ta + \theta_{JA} \times Pd$

$Tj = Tc + \theta_{JC} \times Pd$

where

Tj : junction temperature when the device has achieved a steady-state after application of Pd (°C) Ta :ambient temperature (°C)

Tc :temperature of external surface of the package or case (°C)

$\theta_{JA}$ :thermal resistance from junction-to-ambient (°C/W)

$\theta_{JC}$ :thermal resistance from junction-to-case (package) (°C/W)

Pd :power dissipation that produced change in junction temperature (W) (cf.JESD51-2A)

#### Capacitance

$(T_A = +25^{\circ}C, Frequency = 1.0MHz, V_{DD} = 1.8V, V_{DDQ} = 1.5V)$

| Parameter                           | Symbol           | Min | Тур | Мах | Unit | Test condition         | Note |

|-------------------------------------|------------------|-----|-----|-----|------|------------------------|------|

| Input capacitance (SA, /R, /W, /BW) | C <sub>IN</sub>  | -   | 4   | 5   | pF   | V <sub>IN</sub> = 0 V  | 1,2  |

| Clock input capacitance (K, /K)     | C <sub>CLK</sub> | -   | 4   | 5   | pF   | V <sub>CLK</sub> = 0 V | 1,2  |

| Output capacitance (DQ, CQ, /CQ)    | C <sub>I/O</sub> | -   | 5   | 6   | pF   | $V_{I/O} = 0 V$        | 1,2  |

Notes:

1. Except JTAG (TCK, TMS, TDI, TDO) pins.

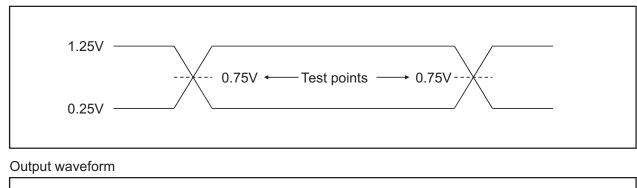

#### **AC Test Conditions**

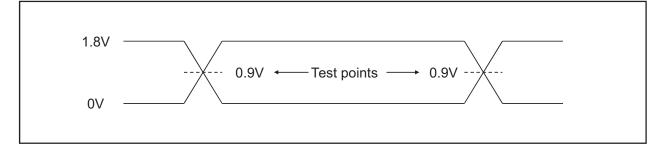

Input waveform (Rise/fall time ≤ 0.3 ns)

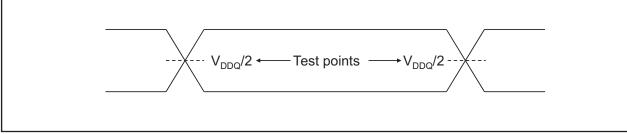

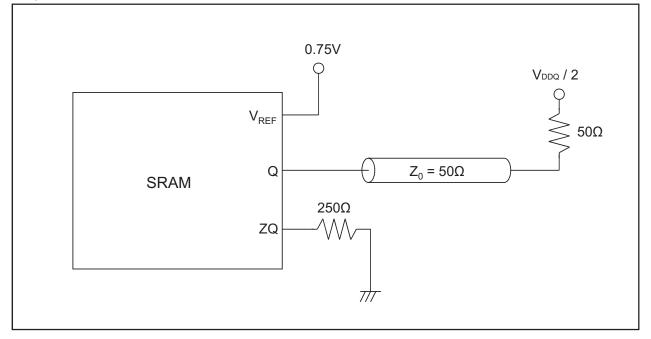

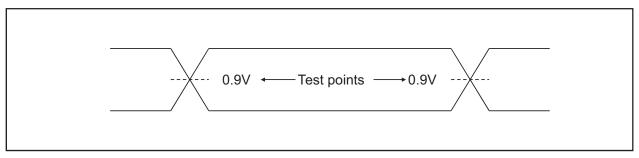

#### Output load conditions

#### **AC Operating Conditions**

| Parameter          | Symbol               | Min                    | Тур | Max             | Unit | Notes   |

|--------------------|----------------------|------------------------|-----|-----------------|------|---------|

| Input high voltage | V <sub>IH (AC)</sub> | V <sub>REF</sub> + 0.2 | -   | -               | V    | 1,2,3,4 |

| Input low voltage  | V <sub>IL (AC)</sub> | -                      | -   | $V_{REF} - 0.2$ | V    | 1,2,3,4 |

- 1. All voltages referenced to  $V_{SS}$  (GND). During normal operation,  $V_{DDQ}$  must not exceed  $V_{DD}$ .

- 2. These conditions are for AC functions only, not for AC parameter test.

- 3. Overshoot:  $V_{IH (AC)} \le V_{DDQ} + 0.5 V$  for  $t \le t_{KHKH}/2$ Undershoot:  $V_{IL (AC)} \ge -0.5 V$  for  $t \le t_{KHKH}/2$ Control input signals may not have pulse widths less than  $t_{KHKL}$  (min) or operate at cycle rates less than  $t_{KHKH}$  (min).

- 4. To maintain a valid level, the transitioning edge of the input must:

- a. Sustain a constant slew rate from the current AC level through the target AC level,  $V_{IL (AC)}$  or  $V_{IH (AC)}$ .

- b. Reach at least the target AC level.

- c. After the AC target level is reached, continue to maintain at least the target DC level, V<sub>IL (DC)</sub> or V<sub>IH (DC)</sub>.

## **AC Characteristics**

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, V_{DD} = 1.8\text{V} \pm 0.1\text{V}, V_{DDQ} = 1.5\text{V}, V_{REF} = 0.75\text{V})$

| Parameter                                | Symbol                | -:    | 25   | Unit  | Notes |

|------------------------------------------|-----------------------|-------|------|-------|-------|

| <b>-</b>                                 |                       | Min   | Max  |       |       |

| Clock                                    | 1                     |       |      |       |       |

| Average clock cycle time<br>(K, /K)      | tкнкн                 | 2.50  | 4.00 | ns    |       |

| Clock high time (K, /K)                  | t <sub>KHKL</sub>     | 0.40  | -    | Cycle |       |

| Clock low time (K, /K)                   | t <sub>KLKH</sub>     | 0.40  | -    | Cycle |       |

| Clock to /clock (K to /K)                | t <sub>кн/кн</sub>    | 0.425 | -    | Cycle |       |

| /Clock to clock (/K to K)                | t <sub>/KHKH</sub>    | 0.425 | -    | Cycle |       |

| PLL Timing                               |                       |       |      |       | -     |

| Clock phase jitter (K, /K)               | t <sub>ĸc</sub> var   | -     | 0.20 | ns    | 3     |

| Lock time (K)                            | $t_{KC}$ lock         | 20    | -    | us    | 2     |

| K static to PLL reset                    | $t_{\text{KC}}$ reset | 30    | -    | ns    | 5     |

| Output Times                             |                       |       |      |       |       |

| K, /K high to output valid               | t <sub>CHQV</sub>     | -     | 0.45 | ns    |       |

| K, /K high to output hold                | t <sub>CHQX</sub>     | -0.45 | -    | ns    |       |

| K, /K high to<br>echo clock valid        | t <sub>CHCQV</sub>    | -     | 0.45 | ns    |       |

| K, /K high to<br>echo clock hold         | t <sub>CHCQX</sub>    | -0.45 | -    | ns    |       |

| CQ, /CQ high to<br>output valid          | t <sub>санаv</sub>    | -     | 0.20 | ns    | 5     |

| CQ, /CQ high to<br>output hold           | t <sub>CQHQX</sub>    | -0.20 | -    | ns    | 5     |

| K, /K high to output high-Z              | t <sub>CHQZ</sub>     | -     | 0.45 | ns    | 4     |

| K, /K high to output low-Z               | t <sub>CHQX1</sub>    | -0.45 | -    | ns    | 4     |

| CQ high to QVLD valid                    | t <sub>QVLD</sub>     | -0.20 | 0.20 | ns    | 5     |

| Setup Times                              | 1 1                   |       | T    |       |       |

| Address valid to<br>K rising edge        | t <sub>avkh</sub>     | 0.40  | -    | ns    | 1     |

| Control inputs valid to<br>K rising edge | t <sub>ıvкн</sub>     | 0.40  | -    | ns    | 1     |

| Data-in valid to<br>K, /K rising edge    | t <sub>DVKH</sub>     | 0.28  | -    | ns    | 1     |

| Hold Times                               |                       |       |      |       |       |

| K rising edge to<br>address hold         | t <sub>KHAX</sub>     | 0.40  | -    | ns    | 1     |

| K rising edge to<br>control inputs hold  | t <sub>кніх</sub>     | 0.40  | -    | ns    | 1     |

| K, /K rising edge to<br>data-in hold     | t <sub>KHDX</sub>     | 0.28  | -    | ns    | 1     |

Notes:

- 1. This is a synchronous device. All addresses, data and control lines must meet the specified setup and hold times for all latching clock edges.

- 2.  $V_{DD}$  and  $V_{DDQ}$  slew rate must be less than 0.1 V DC per 50 ns for PLL lock retention. PLL lock time begins once  $V_{DD}$ ,  $V_{DDQ}$  and input clock are stable.

- It is recommended that the device is kept inactive during these cycles.

- 3. Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

- 4. Echo clock is very tightly controlled to data valid / data hold. By design, there is a  $\pm 0.1$  ns variation from echo clock to data. The datasheet parameters reflect tester guardbands and test setup variations.

- 5. Transitions are measured  $\pm 100$  mV from steady-state voltage.

- 6. These parameters are sampled.

#### Remarks:

- 1. Test conditions as specified with the output loading as shown in AC Test Conditions unless otherwise noted.

- 2. Control input signals may not be operated with pulse widths less than t<sub>KHKL</sub> (min).

- 3.  $V_{DDQ}$  is +1.5 V DC.  $V_{REF}$  is +0.75 V DC.

- 4. Control signals are /LD and R-/W. Setup and hold times of /BWx signals must be the same as those of Data-in signals.

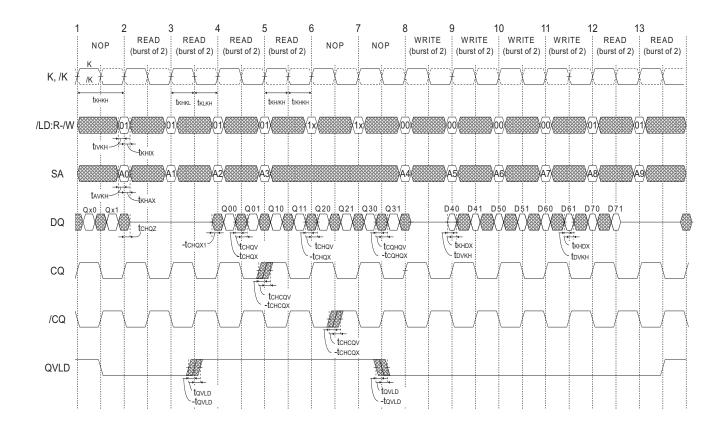

## **Read and Write Timing**

- 1. Q00 refers to output from address A0. Q01 refers to output from the next internal burst address following A0, i.e., A0+1.

- 2. In this example, if address A8 = A7, then data Q80 = D70, Q81 = D71, etc. Write data is forwarded immediately as read results.

- 3. To control read and write operations, /BW signals must operate at the same timing as Data-in signals.

- 4. It recommends two NOP cycles during transition from READ to WRITE cycle for correct device operation.

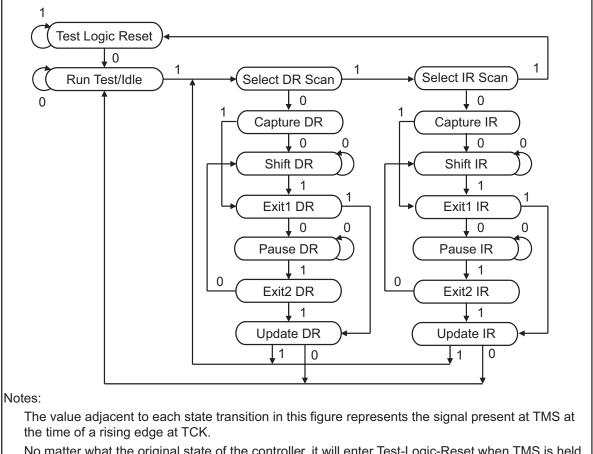

## JTAG Specification

These products support a limited set of JTAG functions as in IEEE standard 1149.1.

#### **Disabling the Test Access Port**

It is possible to use this device without utilizing the TAP. To disable the TAP controller without interfering with normal operation of the device, TCK must be tied to  $V_{SS}$  to preclude mid level inputs. TDI and TMS are internally pulled up and may be unconnected, or may be connected to VDD through a pull up resistor. TDO should be left unconnected.

#### **Test Access Port (TAP) Pins**

| Symbol I/O | Pin assignments | Description                                                                                                                                                                                                                                                                      | Notes |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| тск        | 2R              | Test clock input. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.                                                                                                                                                      |       |

| TMS        | 10R             | Test mode select. This is the command input for the TAP controller state machine.                                                                                                                                                                                                |       |

| TDI        | 11R             | Test data input. This is the input side of the serial registers placed<br>between TDI and TDO. The register placed between TDI and TDO is<br>determined by the state of the TAP controller state machine and the<br>instruction that is currently loaded in the TAP instruction. |       |

| TDO        | 1R              | Test data output. Output changes in response to the falling edge of TCK. This is the output side of the serial registers placed between TDI and TDO.                                                                                                                             |       |

Notes:

The device does not have TRST (TAP reset). The Test-Logic Reset state is entered while TMS is held high for five rising edges of TCK. The TAP controller state is also reset on SRAM POWER-UP.

#### TAP DC Operating Characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, V_{DD} = 1.8\text{V} \pm 0.1\text{V})$

| Parameter              | Symbol           | Min  | Тур | Мах                   | Unit | Notes                                        |

|------------------------|------------------|------|-----|-----------------------|------|----------------------------------------------|

| Input high voltage     | V <sub>IH</sub>  | +1.3 | -   | V <sub>DD</sub> + 0.3 | V    |                                              |

| Input low voltage      | VIL              | -0.3 | -   | +0.5                  | V    |                                              |

| Input leakage current  | ILI              | -5.0 | -   | +5.0                  | μΑ   | $0~V \leq V_{IN} \leq V_{DD}$                |

| Output leakage current | I <sub>LO</sub>  | -5.0 | -   | +5.0                  | μA   | $0 V \le V_{IN} \le V_{DD},$ output disabled |

| Output low voltage     | V <sub>OL1</sub> | -    | -   | 0.2                   | V    | I <sub>OLC</sub> = 100 μA                    |

| Output low voltage     | V <sub>OL2</sub> | -    | -   | 0.4                   | V    | I <sub>OLT</sub> = 2 mA                      |

| Output high voltage    | V <sub>OH1</sub> | 1.6  | -   | -                     | V    | I <sub>OHC</sub>   = 100 μA                  |

| Output high voltage    | V <sub>OH2</sub> | 1.4  | -   | -                     | V    | I <sub>ОНТ</sub>   = 2 mA                    |

Notes:

- 1. All voltages referenced to  $V_{SS}$  (GND).

- 2. At power-up,  $V_{DD}$  and  $V_{DDQ}$  are assumed to be a linear ramp from 0V to  $V_{DD}$ (min.) or  $V_{DDQ}$ (min.) within 200ms. During this time  $V_{DDQ} < V_{DD}$  and  $V_{IH} < V_{DDQ}$ .

During normal operation,  $V_{DDQ}$  must not exceed  $V_{DD}$ .

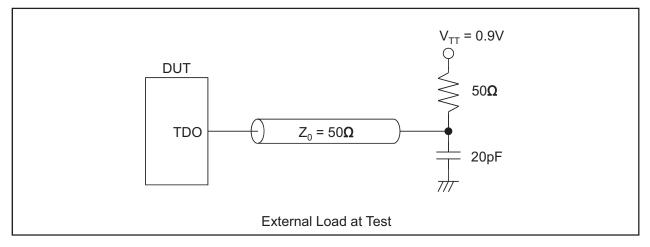

#### TAP AC Test Conditions

| Parameter                                         | Symbol           | Conditions  | Unit | Notes |

|---------------------------------------------------|------------------|-------------|------|-------|

| Input timing measurement reference levels         | V <sub>REF</sub> | 0.9         | V    |       |

| Input pulse levels                                | $V_{IL}, V_{IH}$ | 0 to 1.8    | V    |       |

| Input rise/fall time                              | tr, tf           | ≤ 1.0       | ns   |       |

| Output timing measurement reference levels        |                  | 0.9         | V    |       |

| Test load termination supply voltage ( $V_{TT}$ ) |                  | 0.9         | V    |       |

| Output load                                       |                  | See figures |      |       |

#### Input waveform

#### Output waveform

#### **Output load condition**

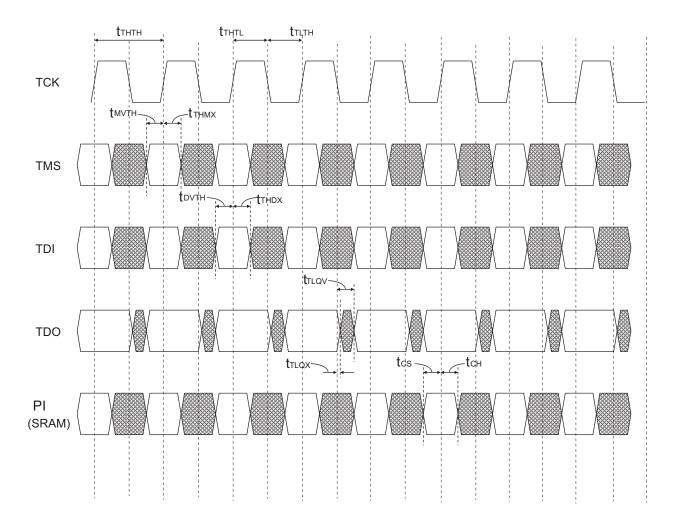

#### **TAP AC Operating Characteristics**

$(T_{\rm A}$  = -40 to +85°C ,  $V_{\rm DD}$  = 1.8V  $\pm 0.1 \rm V)$

| Parameter                    | Symbol              | Min | Тур | Мах | Unit | Notes |

|------------------------------|---------------------|-----|-----|-----|------|-------|

| Test clock (TCK) cycle time  | t <sub>THTH</sub>   | 50  | -   | -   | ns   |       |

| TCK high pulse width         | t <sub>THTL</sub>   | 20  | -   | -   | ns   |       |

| TCK low pulse width          | t <sub>⊤∟⊤н</sub>   | 20  | -   | -   | ns   |       |

| Test mode select (TMS) setup | t <sub>MVTH</sub>   | 5   | -   | -   | ns   |       |

| TMS hold                     | t <sub>THMX</sub>   | 5   | -   | -   | ns   |       |

| Capture setup                | t <sub>cs</sub>     | 5   | -   | -   | ns   |       |

| Capture hold                 | t <sub>CH</sub>     | 5   | -   | -   | ns   |       |

| TDI valid to TCK high        | t <sub>DVTH</sub>   | 5   | -   | -   | ns   |       |

| TCK high to TDI invalid      | t <sub>THDX</sub>   | 5   | -   | -   | ns   |       |

| TCK low to TDO unknown       | t <sub>TLQX</sub>   | 0   | -   | -   | ns   |       |

| TCK low to TDO valid         | $\mathbf{t}_{TLQV}$ | -   | -   | 10  | ns   |       |

Notes:

1.

$t_{CS}$  +  $t_{CH}$  defines the minimum pause in RAM I/O pad transitions to assure pad data capture.

## TAP Controller Timing Diagram

#### **Test Access Port Registers**

| Register name          | Length  | Symbol     | Notes |

|------------------------|---------|------------|-------|

| Instruction register   | 3 bits  | IR [2:0]   |       |

| Bypass register        | 1 bits  | BP         |       |

| ID register            | 32 bits | ID [31:0]  |       |

| Boundary scan register | 109 bit | BS [109:1] |       |

#### **TAP Controller Instruction Set**

| IR2 | IR1 | IR0 | Instruction          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Notes   |

|-----|-----|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 0   | 0   | 0   | EXTEST               | The EXTEST instruction allows circuitry external to the component<br>package to be tested. Boundary scan register cells at output balls<br>are used to apply test vectors, while those at input balls capture test<br>results. Typically, the first test vector to be applied using the<br>EXTEST instruction will be shifted into the boundary scan register<br>using the PRELOAD instruction. Thus, during the Update-IR state<br>of EXTEST, the output driver is turned on and the PRELOAD data is<br>driven onto the output balls.                                                                                                                                                    | 1,2,3,4 |

| 0   | 0   | 1   | IDCODE               | The IDCODE instruction causes the ID ROM to be loaded into the ID register when the controller is in capture-DR mode and places the ID register between the TDI and TDO balls in shift-DR mode. The IDCODE instruction is the default instruction loaded in at power up and any time the controller is placed in the Test-Logic-Reset state.                                                                                                                                                                                                                                                                                                                                              |         |

| 0   | 1   | 0   | SAMPLE-Z             | If the SAMPLE-Z instruction is loaded in the instruction register, all<br>RAM outputs are forced to an inactive drive state (high-Z), moving<br>the TAP controller into the capture-DR state loads the data in the<br>RAMs input into the boundary scan register, and the boundary scan<br>register is connected between TDI and TDO when the TAP<br>controller is moved to the shift-DR state.                                                                                                                                                                                                                                                                                           | 3,4     |

| 0   | 1   | 1   | RESERVED             | The RESERVED instruction is not implemented but is reserved for future use. Do not use this instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| 1   | 0   | 0   | SAMPLE<br>(/PRELOAD) | When the SAMPLE instruction is loaded in the instruction register,<br>moving the TAP controller into the capture-DR state loads the data<br>in the RAMs input and I/O buffers into the boundary scan register.<br>Because the RAM clock(s) are independent from the TAP clock<br>(TCK) it is possible for the TAP to attempt to capture the I/O ring<br>contents while the input buffers are in transition (i.e., in a metastable<br>state). Although allowing the TAP to SAMPLE metastable input will<br>not harm the device, repeatable results cannot be expected.<br>Moving the controller to shift-DR state then places the boundary<br>scan register between the TDI and TDO balls. | 3,4     |

| 1   | 0   | 1   | RESERVED             | The RESERVED instruction is not implemented but is reserved for future use. Do not use this instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| 1   | 1   | 0   | RESERVED             | The RESERVED instruction is not implemented but is reserved for future use. Do not use this instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| 1   | 1   | 1   | BYPASS               | The BYPASS instruction is loaded in the instruction register when<br>the bypass register is placed between TDI and TDO. This occurs<br>when the TAP controller is moved to the shift-DR state. This allows<br>the board level scan path to be shortened to facilitate testing of<br>other devices in the scan path.                                                                                                                                                                                                                                                                                                                                                                       |         |

- 1. Data in output register is not guaranteed if EXTEST instruction is loaded.

- 2. After performing EXTEST, power-up conditions are required in order to return part to normal operation.

- 3. RAM input signals must be stabilized for long enough to meet the TAPs input data capture setup plus hold time (t<sub>CS</sub> plus t<sub>CH</sub>). The RAMs clock inputs need not be paused for any other TAP operation except capturing the I/O ring contents into the boundary scan register.

- 4. Clock recovery initialization cycles are required after boundary scan.

x36 DQ29 NC NC DQ30 DQ21 NC NC DQ22 DQ31 /DOFF NC NC DQ23 DQ32 NC NC DQ33 DQ24 NC NC DQ25 DQ34 NC NC DQ26 DQ35 NC NC SA SA SA SA SA SA Internal

## **Boundary Scan Order**

| Bit# I | Ball | Signal names |      | Б | Bit# | Ball | Signal names |      | Bit# | Ball | Signal names |         |

|--------|------|--------------|------|---|------|------|--------------|------|------|------|--------------|---------|

|        | ID   | x18          | x36  |   | 11#  | ID   | x18          | x36  | BIt# | ID   | x18          | x36     |

| 1      | 6R   | NC           | NC   | 3 | 38   | 9E   | NC           | NC   | 75   | 2D   | NC           | DQ29    |

| 2      | 6P   | QVLD         | QVLD | 3 | 39   | 10C  | DQ7          | DQ17 | 76   | 2E   | NC           | NC      |

| 3      | 6N   | SA           | SA   | 4 | 10   | 11D  | NC           | DQ16 | 77   | 1E   | NC           | NC      |

| 4      | 7P   | SA           | SA   | 4 | 11   | 9C   | NC           | NC   | 78   | 2F   | DQ12         | DQ30    |

| 5      | 7N   | SA           | SA   | 4 | 12   | 9D   | NC           | NC   | 79   | 3F   | NC           | DQ21    |

| 6      | 7R   | SA           | SA   | 4 | 13   | 11B  | DQ8          | DQ8  | 80   | 1G   | NC           | NC      |

| 7      | 8R   | SA           | SA   | 4 | 14   | 11C  | NC           | DQ7  | 81   | 1F   | NC           | NC      |

| 8      | 8P   | SA           | SA   | 4 | 15   | 9B   | NC           | NC   | 82   | 3G   | DQ13         | DQ22    |

| 9      | 9R   | SA           | SA   | 4 | 16   | 10B  | NC           | NC   | 83   | 2G   | NC           | DQ31    |

| 10     | 11P  | DQ0          | DQ0  | 4 | 17   | 11A  | CQ           | CQ   | 84   | 1H   | /DOFF        | /DOFF   |

| 11     | 10P  | NC           | DQ9  | 4 | 18   | 10A  | SA           | SA   | 85   | 1J   | NC           | NC      |

| 12     | 10N  | NC           | NC   | 4 | 19   | 9A   | SA           | SA   | 86   | 2J   | NC           | NC      |

| 13     | 9P   | NC           | NC   | 5 | 50   | 8B   | SA           | SA   | 87   | 3K   | DQ14         | DQ23    |

| 14     | 10M  | DQ1          | DQ11 | 5 | 51   | 7C   | SA           | SA   | 88   | 3J   | NC           | DQ32    |

| 15     | 11N  | NC           | DQ10 | 5 | 52   | 6C   | NC           | NC   | 89   | 2K   | NC           | NC      |

| 16     | 9M   | NC           | NC   | 5 | 53   | 8A   | /LD          | /LD  | 90   | 1K   | NC           | NC      |

| 17     | 9N   | NC           | NC   | 5 | 54   | 7A   | SA           | /BW1 | 91   | 2L   | DQ15         | DQ33    |

| 18     | 11L  | DQ2          | DQ2  | 5 | 55   | 7B   | /BW0         | /BW0 | 92   | 3L   | NC           | DQ24    |

| 19     | 11M  | NC           | DQ1  | 5 | 56   | 6B   | K            | K    | 93   | 1M   | NC           | NC      |

| 20     | 9L   | NC           | NC   | 5 | 57   | 6A   | /K           | /K   | 94   | 1L   | NC           | NC      |

| 21     | 10L  | NC           | NC   | 5 | 58   | 5B   | NC           | /BW3 | 95   | 3N   | DQ16         | DQ25    |

| 22     | 11K  | DQ3          | DQ3  | 5 | 59   | 5A   | /BW1         | /BW2 | 96   | 3M   | NC           | DQ34    |

| 23     | 10K  | NC           | DQ12 | 6 | 60   | 4A   | R-/W         | R-/W | 97   | 1N   | NC           | NC      |

| 24     | 9J   | NC           | NC   | 6 | 61   | 5C   | SA           | SA   | 98   | 2M   | NC           | NC      |

| 25     | 9K   | NC           | NC   | 6 | 62   | 4B   | SA           | SA   | 99   | 3P   | DQ17         | DQ26    |

| 26     | 10J  | DQ4          | DQ13 | 6 | 66   | 3A   | SA           | SA   | 100  | 2N   | NC           | DQ35    |

| 27     | 11J  | NC           | DQ4  | 6 | 64   | 2A   | SA           | SA   | 101  | 2P   | NC           | NC      |

| 28     | 11H  | ZQ           | ZQ   | 6 | 65   | 1A   | /CQ          | /CQ  | 102  | 1P   | NC           | NC      |

| 29     | 10G  | NC           | NC   | 6 | 66   | 2B   | DQ9          | DQ27 | 103  | 3R   | SA           | SA      |

| 30     | 9G   | NC           | NC   | 6 | 67   | 3B   | NC           | DQ18 | 104  | 4R   | SA           | SA      |

| 31     | 11F  | DQ5          | DQ5  | 6 | 68   | 1C   | NC           | NC   | 105  | 4P   | SA           | SA      |

| 32     | 11G  | NC           | DQ14 | 6 | 69   | 1B   | NC           | NC   | 106  | 5P   | SA           | SA      |

| 33     | 9F   | NC           | NC   | 7 | 70   | 3D   | DQ10         | DQ19 | 107  | 5N   | SA           | SA      |

| 34     | 10F  | NC           | NC   |   | 71   | 3C   | NC           | DQ28 | 108  | 5R   | SA           | SA      |

| 35     | 11E  | DQ6          | DQ6  |   | 72   | 1D   | NC           | NC   | 109  | -    | Internal     | Interna |

| 36     | 10E  | NC           | DQ15 | 7 | 73   | 2C   | NC           | NC   |      |      |              |         |

| 37     | 10D  | NC           | NC   |   | 74   | 3E   | DQ11         | DQ20 |      |      |              |         |

#### Notes:

In boundary scan mode,

- 1. Clock balls (K, /K) are referenced to each other and must be at opposite logic levels for reliable operation.

- 2. CQ and /CQ data are synchronized to the K clock (except EXTEST, SAMPLE-Z).

## **ID Register**

## **TAP Controller State Diagram**

No matter what the original state of the controller, it will enter Test-Logic-Reset when TMS is held high for at least five rising edges of TCK.

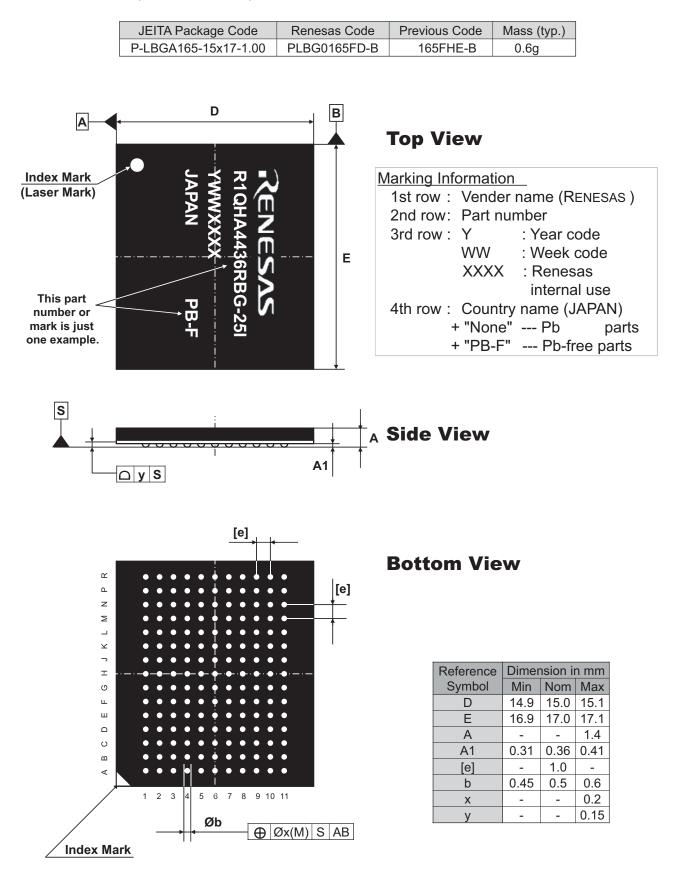

## Package Dimensions and Marking Information

Both Pb parts and Pb-free parts are available.

## **Revision History**

R1QHA4436RBG,R1QHA4418RBG

|          |           |      | Description                                              |  |

|----------|-----------|------|----------------------------------------------------------|--|

| Rev.     | Date      | Page | Summary                                                  |  |

| Rev.1.00 | '13.11.01 | -    | New Datasheet.                                           |  |

| Rev.2.00 | '14.08.01 | P15  | Modification : DC Characteristics ,Spec of IDD and ISB1. |  |

QDR RAMs and Quad Data Rate RAMs comprise a new family of products developed by Cypress Semiconductor, and Renesas Electronics Corporation. http://www.qdrconsortium.org/

The information contained herein is subject to change without notice.

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infrigment of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or

- technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics may way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### SALES OFFICES

Refer to "http://www.renesas.com/" for the latest and detailed information

#### **Renesas Electronics Corporation**

http://www.renesas.com