# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

MOS集積回路 MOS Integrated Circuit

# $\mu$ PD784935A,784936A,784937A,784938A

# 16ビット・シングルチップ・マイクロコンピュータ

$\mu$  PD784935A, 784936A, 784937A, 784938Aは, 78K/ シリーズの中の $\mu$  PD784938Aサブシリーズの製品です。  $\mu$  PD784908サブシリーズをベースに内部ROM, RAM容量を拡大し, ROMコレクション機能を追加したものです。 また,マスクROM製品と同じ電源電圧範囲で,動作可能なフラッシュ・メモリ内蔵製品 $\mu$  PD78F4938Aや各種開発ツールも用意しております。

詳しい機能説明などは次のユーザーズ・マニュアルに記載しております。設計の際には必ずお読みください。

$\mu$  PD784938Aサプシリーズ ユーザーズ・マニュアル ハードウエア編 : U13987J 78K/ シリーズ ユーザーズ・マニュアル 命令編 : U10905J

#### 特徵

78/ シリーズ

最小命令実行時間: 320 ns (fxx = 6.29 MHz動作時)

160 ns (fxx = 12.5 MHz動作時)

I/Oポート:80本 タイマ / カウンタ

> : 16ビット・タイマ / イベント・カウンタ×1ユニット 8/16ビット・タイマ / イベント・カウンタ×2ユニット

> > :2チャネル

8/16ビット・タイマ×1ユニット

シリアル・インタフェース : 4チャネル  $\cdot$  UART/IOE ( 3線式シリアルI/O ) : 2チャネル

PWM出力:2出力 スタンバイ機能

HALT/STOP/IDLE ₹ - F

CSI(3線式シリアルI/O)

クロック分周機能

#### 応用分野

カー・オーディオなど

外部拡張機能

ROMコレクション機能内蔵

ウォッチドッグ・タイマ:1チャネル

クロック出力機能:

fclk, fclk/2, fclk/4, fclk/8, fclk/16から選択

A/Dコンバータ:8ビット分解能×8チャネル

IEBus™コントローラ内蔵

時計用タイマ

低消費電力

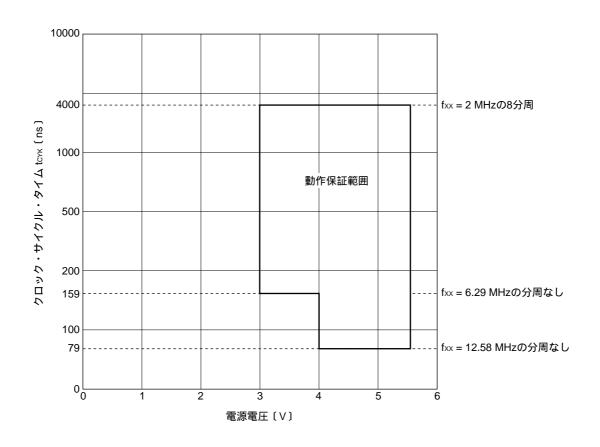

電源電圧

・VDD = 4.0~5.5 V (12.58 MHz動作時)

・VDD = 3.0~5.5 V (6.29 MHz動作時)

この資料では,特に断りがないかぎりµPD784938Aを代表製品として説明しています。

本資料の内容は、予告なく変更することがありますので、最新のものであることをご確認の上ご使用ください。

# オーダ情報

| オーダ名称                         | パッケージ                  | 内部ROM(バイト) | 内部RAM (バイト) |

|-------------------------------|------------------------|------------|-------------|

| $\mu$ PD784935AGF- × × × -3BA | 100ピン・プラスチックQFP(14×20) | 96 Kバイト    | 5120バイト     |

| $\mu$ PD784936AGF- × × × -3BA | 100ピン・プラスチックQFP(14×20) | 128 Kバイト   | 6656バイト     |

| $\mu$ PD784937AGF- x x x -3BA | 100ピン・プラスチックQFP(14×20) | 192 Kバイト   | 8192バイト     |

| $\mu$ PD784938AGF- × × × -3BA | 100ピン・プラスチックQFP(14×20) | 256 Kバイト   | 10496バイト    |

備考 ×××はROMコード番号です。

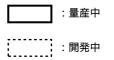

#### ★ 78K/ シリーズ製品展開図

**備考** 蛍光表示管の一般的な英語名称はVFD ( Vacuum Fluorescent Display ) ですが , ドキュメントによってはFIP® (Fluorescent Indicator Panel ) と記述しているものがあります。VFDとFIPは同等の機能です。

# 機能一覧

(1/2)

|                      |            | 1                                                                                     |                       |                  | ( 1/2       |  |  |

|----------------------|------------|---------------------------------------------------------------------------------------|-----------------------|------------------|-------------|--|--|

|                      | 品名         | μ PD784935A                                                                           | μ PD784936A           | μ PD784937A      | μ PD784938A |  |  |

| 項目                   |            |                                                                                       |                       |                  |             |  |  |

| 基本命令(二モ              | ニック)数      | 113                                                                                   |                       |                  |             |  |  |

| 汎用レジスタ               |            | •                                                                                     | ×8バンク,または16ビ          |                  | ク(メモリ・マップ)  |  |  |

| 最小命令実行時              | 間          | · ·                                                                                   | s/2.54 µ s(6.29 MHz動作 |                  |             |  |  |

|                      |            | <b>†</b>                                                                              | /1.27 μ s(12.58 MHz動作 |                  | 1           |  |  |

| 内部メモリ                | ROM        | 96 Kバイト                                                                               | 128 Kバイト              | 192 Kバイト         | 256 Kバイト    |  |  |

|                      | RAM        | 5120バイト                                                                               | 6656バイト               | 8192バイト          | 10496バイト    |  |  |

| メモリ空間                |            | プログラム / データあ                                                                          | 5わせて1 Mバイト            |                  |             |  |  |

| I/Oポート               | 合 計        | 80本                                                                                   |                       |                  |             |  |  |

|                      | 入力         | 8本                                                                                    |                       |                  |             |  |  |

|                      | 入出力        | 72本                                                                                   |                       |                  |             |  |  |

|                      | LEDダイレクト・  | 24本                                                                                   |                       |                  |             |  |  |

| き端子 <sup>注</sup>     | ドライブ出力     |                                                                                       |                       |                  |             |  |  |

|                      | トランジスタ・    |                                                                                       |                       |                  |             |  |  |

|                      | ダイレクト・ド    |                                                                                       |                       |                  |             |  |  |

|                      | ライブ        |                                                                                       |                       |                  |             |  |  |

|                      | N-chオープン・  | 4本                                                                                    |                       |                  |             |  |  |

|                      | ドレーン       |                                                                                       |                       |                  |             |  |  |

| リアルタイム出              | 力ポート       | 4ビット×2,または8ビット×1                                                                      |                       |                  |             |  |  |

| IEBusコントロ            | ーラ         | 内蔵(簡易版)                                                                               |                       |                  |             |  |  |

| タイマ / カウン            | <b>'</b> タ | タイマ / イベント・カウンタ0:タイマ・カウンタ×1 パルス出力可                                                    |                       |                  |             |  |  |

|                      |            | (16ビット) キャプチャ・レジスタ×1 ・トグル出力                                                           |                       |                  |             |  |  |

|                      |            |                                                                                       | コンペア・レ                |                  | VM/PPG出力    |  |  |

|                      |            |                                                                                       |                       |                  | ンショット・パルス出力 |  |  |

|                      |            |                                                                                       | ]ウンタ1:タイマ・カウ<br>      |                  | タイム出力ポート    |  |  |

|                      |            | (16ビット)                                                                               | キャプチャ・                |                  |             |  |  |

|                      |            |                                                                                       |                       | ペア・レジスタ×1        |             |  |  |

|                      |            |                                                                                       | コンペア・レ                |                  |             |  |  |

|                      |            |                                                                                       | Jウンタ2:タイマ・カウ<br>      |                  |             |  |  |

|                      |            | (16ビット)                                                                               | _                     |                  | グル出力        |  |  |

|                      |            |                                                                                       |                       | ペア・レジスタ×1・PV     | VIVI/PPG出力  |  |  |

|                      |            | タイマ3                                                                                  | コンペア・レ                |                  |             |  |  |

|                      |            | タ1 マ3<br>(16ビット)                                                                      | : タイマ・カウ:             |                  |             |  |  |

| <br>時計用タイマ           |            |                                                                                       | コンペア・レ                |                  |             |  |  |

| 1寸百 1 円 ブイ く         |            | 0.5秒間隔で割り込み要求発生(時計クロック発振回路を内蔵)<br>入力クロックは,メイン・クロック(12.58 MHz)と時計クロック(32.768 kHz)の選択可能 |                       |                  |             |  |  |

|                      |            |                                                                                       |                       |                  |             |  |  |

| フロック田/バ<br>PWM出力     |            | fclк, fclк/2, fclк/4, fclк/8, fclк/16から選択(1ビット出力ポートとしても使用可能) 12ビット分解能×2チャネル           |                       |                  |             |  |  |

| -vvivi山/リ<br>シリアル・イン | <u></u>    | •                                                                                     |                       | <br>( ボー・レート・ジェウ | しータ内蔵)      |  |  |

| ンツァル・イン              | フノエース      | UART/IOE(3線式シリアルI/O):2チャネル(ボー・レート・ジェネレータ内蔵)<br>CSI(3線式シリアルI/O) : 2チャネル                |                       |                  |             |  |  |

|                      |            | 1                                                                                     |                       |                  |             |  |  |

| Δ/ロコンバータ             |            | 8ビット分解能×8チャネル                                                                         |                       |                  |             |  |  |

| A/Dコンバータ<br>ウォッチドック  | ・ タイフ      | 1チャネル                                                                                 | 177                   |                  |             |  |  |

注 付加機能付き端子は,I/O端子の中に含まれています。

(2/2)

|                                           | 品名       | μ PD784935A                                | μ PD784936A            | μ PD784937A | μ PD784938A |  |  |

|-------------------------------------------|----------|--------------------------------------------|------------------------|-------------|-------------|--|--|

| 項 目                                       |          |                                            |                        |             |             |  |  |

| 外部拡張機能                                    | 能        | あり ( 1 Mバイトまで可                             | )                      |             |             |  |  |

| スタンバイ                                     |          | HALT/STOP/IDLE = -                         | *                      |             |             |  |  |

| 割り込み                                      | ハードウエア要因 | 27(内部20,外部7(サ                              | ンプリング・クロック可            | 变入力:1))     |             |  |  |

|                                           | ソフトウエア要因 | BRK命令, BRKCS命令                             | RK命令,BRKCS命令,オペランド・エラー |             |             |  |  |

|                                           | ノンマスカブル  | 内部:1,外部:1                                  |                        |             |             |  |  |

|                                           | マスカブル    | 内部:19,外部:6                                 |                        |             |             |  |  |

|                                           |          | 4レベルのプログラマブル・プライオリティ                       |                        |             |             |  |  |

| 3種類の処理形態:ベクタ割り込み/マクロ・サービス/コンテキスト・スイッチン    |          |                                            |                        |             | スイッチング      |  |  |

| 電源電圧                                      |          | ・V <sub>DD</sub> = 4.0~5.5 V(12.58 MHz動作時) |                        |             |             |  |  |

| ・V <sub>DD</sub> = 3.0~5.5 V(6.29 MHz動作時) |          |                                            |                        |             |             |  |  |

| パッケージ                                     |          | ・100ピン・プラスチッ                               | クQFP (14×20)           |             |             |  |  |

# 目 次

| 1. | μ PD784938A <b>サブシリーズ製品間の違い</b> 8                                       |

|----|-------------------------------------------------------------------------|

| 2. | $\mu$ PD784908サプシリーズ, $\mu$ PD784038サプシリーズ, $\mu$ PD78098サプシリーズとの主な違い 9 |

| 3. | <b>端子接続図(</b> Top View <b>)</b> 10                                      |

| 4. | システム構成例(車載オーディオ(チューナ・デッキ部)) 12                                          |

| 5. | <b>プロック図</b> 13                                                         |

| 6. | <b>端子機能</b> 14                                                          |

|    | 6.1 ポート端子 14                                                            |

|    | 6.2 ポート以外の端子 16                                                         |

|    | 6.3 端子の入出力回路と未使用端子の処理 18                                                |

| 7. | CPU <b>アーキテクチャ</b> 22                                                   |

|    | 7.1 メモリ空間 22                                                            |

|    | 7.2 CPUレジスタ 27                                                          |

|    | 7. 2. 1 汎用レジスタ 27                                                       |

|    | 7. 2. 2 制御レジスタ 28                                                       |

|    | 7. 2. 3 特殊機能レジスタ(SFR) 29                                                |

| 8. | <b>周辺ハードウエア機能</b> 34                                                    |

|    | 8.1 ポート 34                                                              |

|    | 8.2 クロック発生回路 36                                                         |

|    | 8.3 リアルタイム出力ポート 39                                                      |

|    | 8.4 タイマ/カウンタ 40                                                         |

|    | 8.5 時計用タイマ 42                                                           |

|    | 8.6 PWM出力 (PWM0, PWM1) 43                                               |

|    | 8.7 A/Dコンバータ 44                                                         |

|    | 8.8 シリアル・インタフェース 45                                                     |

|    | 8. 8. 1 アシンクロナス・シリアル・インタフェース / 3線式シリアルI/O(UART/IOE) 46                  |

|    | 8. 8. 2 クロック同期式シリアル・インタフェース(CSI) 48                                     |

|    | 8.9 クロック出力機能 49                                                         |

|    | 8. 10 エッジ検出機能 50                                                        |

|    | 8. 11 ウォッチドッグ・タイマ 50                                                    |

|    | 8. 12 簡易版IEBusコントローラ 51                                                 |

| 9. | <b>割り込み機能</b> 54                                                        |

|    | 9.1 割り込み要因 54                                                           |

9.2 ベクタ割り込み ... 56

- 9.3 コンテキスト・スイッチング ... 57

- 9.4 マクロ・サービス ... 57

- 9.5 マクロ・サービスの応用例 ... 58

- 10. ローカル・パス・インタフェース ... 60

- 10.1 メモリ拡張 ... 60

- 10.2 メモリ空間 ... 61

- 10.3 プログラマブル・ウエイト ... 62

- 10.4 疑似スタティックRAMリフレッシュ機能 ... 62

- 10.5 バス・ホールド機能 ... 62

- 11. スタンパイ機能 ... 63

- 12. リセット機能 ... 64

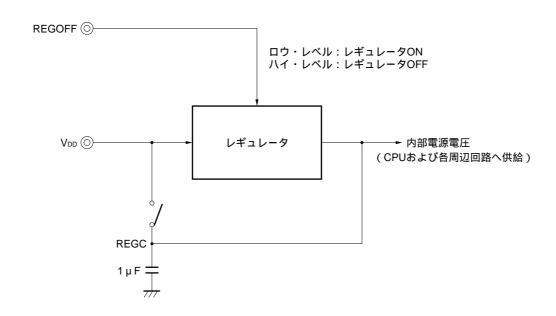

- 13. **レギュレータ** ... 65

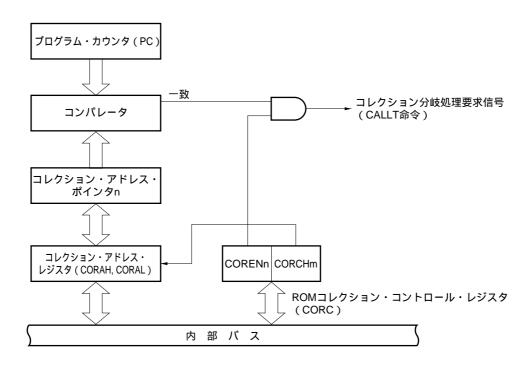

- 14. ROMコレクション ... 66

- 15. 命令セット ... 67

- 16. 電気的特性 ... 72

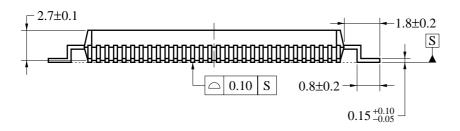

- 17. 外形図 ... 92

- 18. **半田付け推奨条件** ... 93

- 付録A. 開発ツール ... 94

- **付録**B. **関連資料** ... 97

# 1. μ PD784938A**サブシリーズ製品間の違い**

μ PD784935A, 784936A, 784937A, 784938Aは, 内部メモリ容量が異なるだけです。

$\mu$  PD78F4938Aは,上記製品のマスクROMを256 Kバイトのフラッシュ・メモリに置き換えた製品です。相違点を表1 - 1に示します。

表1 - 1  $\mu$  PD784938A**サブシリーズ製品間の違い**

| 品名                  | μ PD784935A | μ PD784936A             | μ PD784937A | μ PD784938A | μ PD78F4938A |  |

|---------------------|-------------|-------------------------|-------------|-------------|--------------|--|

| 項目                  |             |                         |             |             |              |  |

| 内部ROM               | 96 Kバイト     | 128 Kバイト                | 192 Kバイト    | 256 Kバイト    |              |  |

|                     | マスクROM      |                         |             |             | フラッシュ・メモリ    |  |

| 内部RAM               | 5120バイト     | 6656バイト                 | 8192バイト     | 10496バイト    |              |  |

| レギュレータ              | あり          | なし                      |             |             |              |  |

| 電気的特性               | 個別の製品のデータ   | 個別の製品のデータ・シートを参照してください。 |             |             |              |  |

| 内部メモリ・サイズ切り         | なし          | なし                      |             |             |              |  |

| 替えレジスタ <sup>注</sup> |             |                         |             |             |              |  |

| IC端子                | あり          | なし                      |             |             |              |  |

| Vpp端子               | なし          |                         |             |             | あり           |  |

注 内部メモリ・サイズ切り替えレジスタ (IMS) により,内蔵フラッシュ・メモリ容量,内部RAM容量の変更可能。

# 2. $\mu$ PD784908サプシリーズ , $\mu$ PD784038サプシリーズ , $\mu$ PD78098サプシリーズとの主な違い

|         | シリーズ名          | μPD784938Aサブシリーズ              | μPD784908サブシリーズ               | μPD784038サブシリーズ               | μPD78098サブシリーズ                |

|---------|----------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| 項目      |                |                               |                               |                               |                               |

| 基本命令    | (ニモニック)数       | 113                           |                               |                               | 63                            |

| 最小命令到   | 実行時間           | 160 ns                        |                               | 125 ns                        | 480 ns                        |

|         |                | (内部12.5 MHz動作時)               |                               | ( 32 MHz動作時 )                 | (6.29 MHz動作時)                 |

| メモリ空間   | <b></b>        | 1 Mバイト                        |                               |                               | 60 Kバイト                       |

| ( プログラ  | ム・データ)         |                               |                               |                               |                               |

| タイマ / フ | カウンタ           | 16ビット・タイマ / イベ                | ベント・カウンタ×1                    | 16ビット・タイマ / イベ                | 16ビット・タイマ / イベ                |

|         |                | 8/16ビット・タイマノイ                 | ベント・カウンタ×2                    | ント・カウンタ×1                     | ント・カウンタ×1                     |

|         |                | 8/16ビット・タイマ×1                 |                               | 8/16ビット・タイマ / イ               | 8ビット・タイマ / イベン                |

|         |                | 時計用タイマ                        |                               | ベント・カウンタ×2                    | ト・カウンタ×2                      |

|         |                |                               |                               | 8/16ビット・タイマ×1                 | 時計用タイマ                        |

|         |                | シングル・クロック                     |                               | シングル・クロック                     | デュアル・クロック                     |

|         |                | 時計動作用に時計クロッ                   | <b>ッ</b> クあり                  |                               |                               |

| シリアル    | ・インタフェース       | UART/IOE(3線式シリ                | アルI/O):2チャネル                  | UART/IOE(3線式シリ                | UART (3線式シリアル                 |

|         |                | (ボー・レート・ジェネ                   | レータ内蔵)                        | アルI/O): 2チャネル                 | I/O):1チャネル                    |

|         |                | CSI(3線式シリアルI/O                | ):2チャネル                       | CSI( 3線式シリアルI/O,              | CSI/SBI(3線式シリア                |

|         |                |                               |                               | 2線式シリアルI/O):                  | ルI/O):1チャネル                   |

|         |                |                               |                               | 1チャネル                         | CSI(3線式シリアル                   |

|         |                |                               |                               |                               | I/O):1チャネル                    |

| PWM出力   |                | 12ビット分解能×2チャ                  | ネル                            |                               | なし                            |

| D/Aコンハ  | <b>、</b> ータ    | なし                            |                               | 8ビット分解能×2チャネ                  | <b>ネル</b>                     |

| 割り込み    | ハードウエア要因       | 27本                           |                               | 24本                           | 23本(テスト・フラグ2本)                |

|         | 内部             | 20本                           |                               | 17本                           | 14本                           |

|         | 外部             | 7本                            |                               | 7本                            | 7本                            |

| 外部拡張    | 幾能             | あり(1 Mバイトまで可                  | )                             |                               | なし                            |

| IEBusコン | ·トロ <b>ー</b> ラ | 内蔵(簡易版)                       |                               | 内蔵しない                         | 内蔵 (完全ハードウエア)                 |

| ROMコレ   | クション           | 内蔵(4ポイント設定可)                  | 内蔵しない                         |                               |                               |

| 電源電圧    |                | V <sub>DD</sub> = 4.0 ~ 5.5 V | V <sub>DD</sub> = 3.5 ~ 5.5 V | V <sub>DD</sub> = 2.7 ~ 5.5 V | V <sub>DD</sub> = 2.7 ~ 6.0 V |

|         |                |                               | (マスクROM品)                     |                               |                               |

|         |                |                               | V <sub>DD</sub> = 4.0 ~ 5.5 V |                               |                               |

|         |                |                               | (PROM品)                       |                               |                               |

| パッケーシ   | ブ              | 100ピン・プラスチッ                   | 100ピン・プラスチッ                   | 80ピン・プラスチック                   | 80ピン・プラスチック                   |

|         |                | クQFP (14×20)                  | クQFP (14×20)                  | QFP (14 x 14)                 | TQFP(ファインピッ                   |

|         |                |                               |                               | 80ピン・プラスチック                   | チ) (14×14)                    |

|         |                |                               |                               | TQFP (ファインピッ                  | 80ピン・プラスチック                   |

|         |                |                               |                               | チ) (14×14)                    | WQFN (14×14):                 |

|         |                |                               |                               | 80ピン・プラスチック                   | μ PD78P098Aのみ                 |

| 1       |                |                               |                               | WQFN (14×14):                 |                               |

|         |                |                               |                               |                               |                               |

注 付加機能付き端子は,I/O端子の中に含まれています。

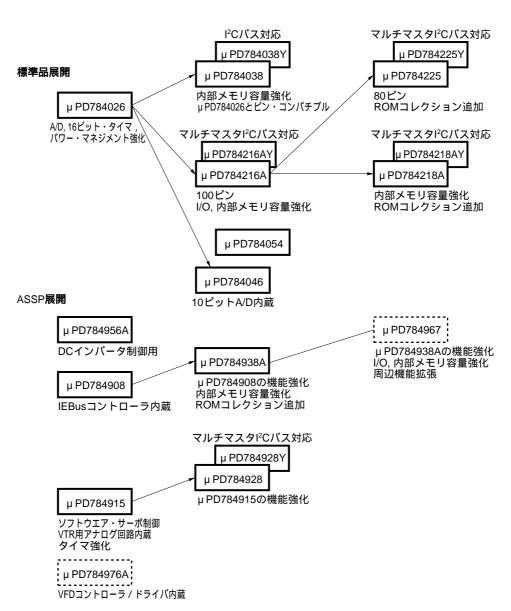

#### 3. **端子接続図(**Top View**)**

```

・100ピン・プラスチックQFP (14×20)

```

```

\mu PD784935AGF- \times \times \times -3BA \mu PD784936AGF- \times \times \times -3BA \mu PD784937AGF- \times \times \times -3BA \mu PD784938AGF- \times \times -3BA

```

注意1. IC (Internally Connected) 端子はVssに直接接続してください。

- 2. AVpp端子はVppに直接接続してください。

- 3. AVss端子はVssに直接接続してください。

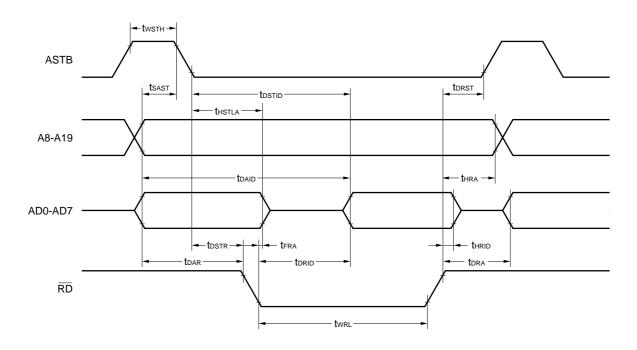

A8-A19 : Address Bus

AD0-AD7 : Address/Data Bus

ANI0-ANI7 : Analog Input

ASCK, ASCK2: Asynchronous Serial Clock

ASTB : Address Strobe

AV<sub>DD</sub> : Analog Power Supply

AVREF1 : Reference Voltage

AVss : Analog Ground

CI : Clock Input

CLKOUT : Clock Output

HLDAK : Hold Acknowledge

HLDRQ : Hold Request

IC : Internally Connected

INTP0-INTP5 : Interrupt from Peripherals

NMI : Non-maskable Interrupt

P00-P07 : Port0

P10-P17 : Port1

P20-P27 : Port2

P30-P37 : Port3

P40-P47 : Port4

P50-P57 : Port5

P60-P67 : Port6

P70-P77 : Port7

P90-P97 : Port9

P100-P107 : Port10

PWM0, PWM1 : Pulse Width Modulation Output

RD : Read Strobe

REFRQ : Refresh Request

REGC : Regulator Capacitance

REGOFF : Regulator Off

RESET : Reset

RX : IEBus Receive Data

RxD, RxD2 : Receive Data

SCK0-SCK3 : Serial Clock

SI0-SI3 : Serial Input

SO0-SO3 : Serial Output

TO0-TO3 : Timer Output

TX : IEBus Transmit Data

TxD, TxD2 : Transmit Data

V<sub>DD</sub> : Power Supply

Vss : Ground

WAIT : Wait

WR : Write Strobe

X1, X2 : Crystal (Main System Clock)

XT1, XT2 : Crystal (Watch)

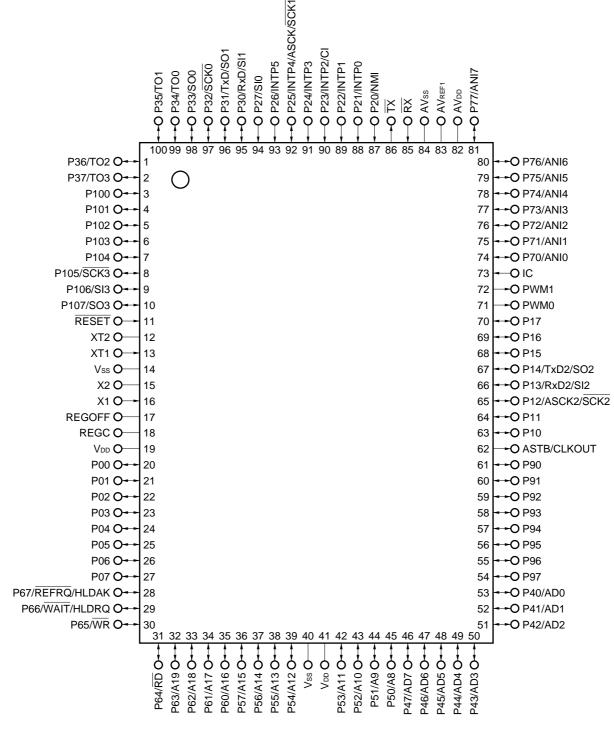

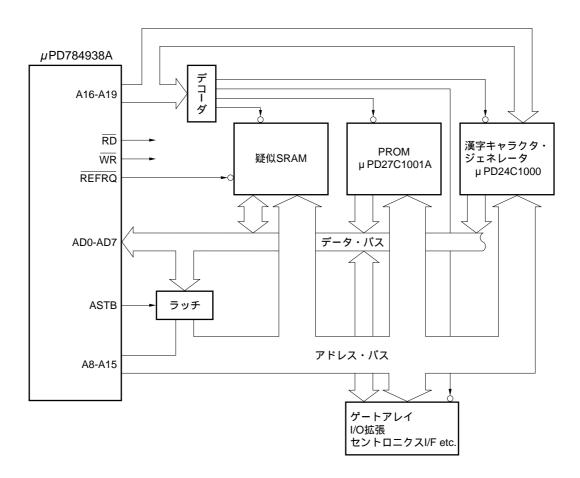

# 4. システム構成例(車載オーディオ(チューナ・デッキ部))

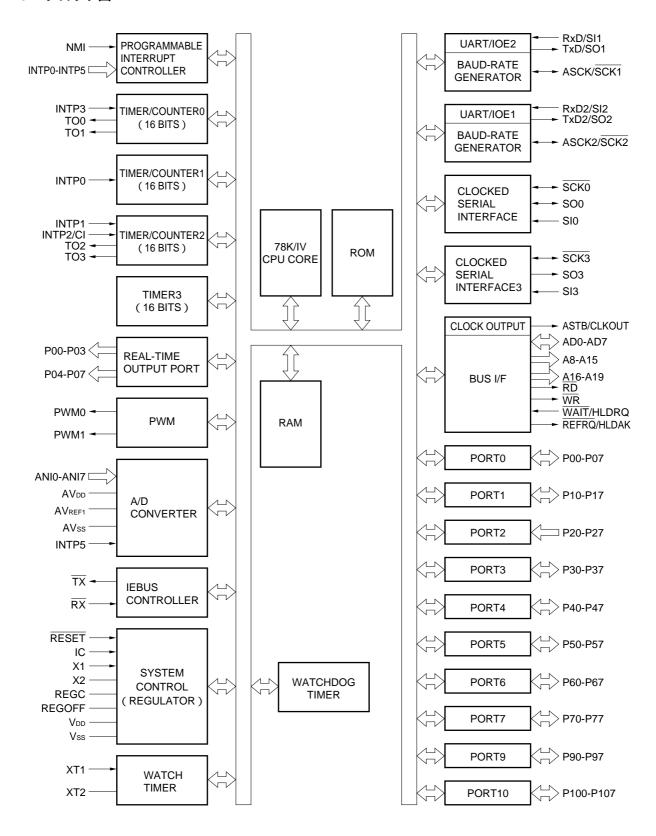

#### 5. **ブロック図**

備考 内部ROM, RAM容量は製品によって異なります。

# 6. 端子機能

# 6.1 **ポート端子(**1/2)

| 端子名称    | 入出力 | 兼用端子            | 機能                                             |

|---------|-----|-----------------|------------------------------------------------|

| P00-P07 | 入出力 | -               | ポート0(P0):                                      |

|         |     |                 | ・8ビット入出力ポート                                    |

|         |     |                 | ・リアルタイム出力ポート(4ビット×2)として使用可能                    |

|         |     |                 | ・1ビット単位に入力 / 出力の指定可能                           |

|         |     |                 | ・入力モードの端子について,ソフトウエアで一括して内蔵プルアップ抵抗の            |

|         |     |                 | 接続の指定可能                                        |

|         |     |                 | ・トランジスタ駆動可能                                    |

| P10     | 入出力 | -               | ポート1(P1):                                      |

| P11     |     | -               | ・8ビット入出力ポート                                    |

| P12     |     | ASCK2/SCK2      | ・1ビット単位に入力/出力の指定可能                             |

| P13     |     | RxD2/SI2        | ・入力モードの端子について,ソフトウエアで一括して内蔵プルアップ抵抗の            |

| P14     |     | TxD2/SO2        | 接続の指定可能                                        |

| P15-P17 |     | -               | ・LED駆動可能                                       |

| P20     | 入力  | NMI             | ポート2(P2):                                      |

| P21     |     | INTP0           | ・8ビット入力専用ポート                                   |

| P22     |     | INTP1           | ・P20は汎用ポートとしては使用不可(ノンマスカブル割り込み)。ただし,           |

| P23     |     | INTP2/CI        | 割り込みルーチンにおいて,入力レベルの確認可能                        |

| P24     |     | INTP3           | ・P22-P27は6ビット単位でソフトウエアによる内蔵プルアップ抵抗の接続の         |

| P25     |     | INTP4/ASCK/SCK1 | 指定可能                                           |

| P26     |     | INTP5           | ・P25/INTP4/ASCK/SCK1端子は,CSIM1の指定により,SCK1入出力端子と |

| P27     |     | SIO             | して動作                                           |

| P30     | 入出力 | RxD/SI1         | ポート3(P3):                                      |

| P31     | =   | TxD/SO1         | ・8ビット入出力ポート                                    |

| P32     |     | SCK0            | ・1ビット単位に入力 / 出力の指定可能                           |

| P33     |     | SO0             | ・<br>・入力モードの端子について,ソフトウエアで一括して内蔵プルアップ抵抗の       |

| P34-P37 |     | TO0-TO3         | 接続の指定可能                                        |

|         |     |                 | ・P32, P33は,N-chオープン・ドレーン接続の指定可能                |

| P40-P47 | 入出力 | AD0-AD7         | ポート4 (P4):                                     |

|         |     |                 | ・8ビット入出力ポート                                    |

|         |     |                 | ・1ビット単位に入力/出力の指定可能                             |

|         |     |                 | ・入力モードの端子について,ソフトウエアで一括して内蔵プルアップ抵抗の            |

|         |     |                 | 接続の指定可能                                        |

|         |     |                 | ・LED駆動可能                                       |

| P50-P57 | 入出力 | A8-A15          | ポート5(P5):                                      |

|         |     |                 | ・8ビット入出力ポート                                    |

|         |     |                 | ・1ビット単位に入力/出力の指定可能                             |

|         |     |                 | <br>  ・入力モードの端子について,ソフトウエアで一括して内蔵プルアップ抵抗の      |

|         |     |                 | 接続の指定可能                                        |

|         |     |                 | │<br>・LED駆動可能                                  |

# 6.1 ポート端子(2/2)

| 端子名称      | 入出力 | 兼用端子        | 機能                                  |

|-----------|-----|-------------|-------------------------------------|

| P60-P63   | 入出力 | A16-A19     | ポート6(P6):                           |

| P64       |     | RD          | ・8ビット入出力ポート                         |

| P65       |     | WR          | ・1ビット単位に入力/出力の指定可能                  |

| P66       |     | WAIT/HLDRQ  | ・入力モードの端子について,ソフトウエアで一括して内蔵プルアップ抵抗の |

| P67       |     | REFRQ/HLDAK | 接続の指定可能                             |

| P70-P77   | 入出力 | ANI0-ANI7   | ポート7(P7):                           |

|           |     |             | ・8ビット入出力ポート                         |

|           |     |             | ・1ビット単位に入力/出力の指定可能                  |

| P90-P97   | 入出力 | -           | ポート9(P9):                           |

|           |     |             | ・8ビット入出力ポート                         |

|           |     |             | ・1ビット単位に入力/出力の指定可能                  |

|           |     |             | ・入力モードの端子について,ソフトウエアで一括して内蔵プルアップ抵抗の |

|           |     |             | 接続可能                                |

| P100-P104 | 入出力 | -           | ポート10 (P10):                        |

| P105      | -   | SCK3        | ・8ビット入出力ポート                         |

| P105      |     | SCK3        | ・1ビット単位に入力/出力の指定可能                  |

| P106      |     | SI3         | ・入力モードの端子について,ソフトウエアで一括して内蔵プルアップ抵抗の |

| D407      | -   | 000         | 接続可能                                |

| P107      |     | SO3         | ・P105, P107は,N-chオープン・ドレーン接続の指定可能   |

# 6.2 ポート以外の端子(1/2)

| 端子名称    | 入出力 | 兼用端子           | 機能                                      |  |  |

|---------|-----|----------------|-----------------------------------------|--|--|

| TO0-TO3 | 出力  | P34-P37        | タイマ出力                                   |  |  |

| CI      | 入力  | P23/INTP2      | タイマ / カウンタ2へのカウント・クロック入力                |  |  |

| RxD     | 入力  | P30/SI1        | シリアル・データ入力(UARTO)                       |  |  |

| RxD2    |     | P13/SI2        | シリアル・データ入力(UART2)                       |  |  |

| TxD     | 出力  | P31/SO1        | シリアル・データ出力(UARTO)                       |  |  |

| TxD2    |     | P14/SO2        | シリアル・データ出力(UART2)                       |  |  |

| ASCK    | 入力  | P25/INTP4/SCK1 | ボー・レート・クロック入力(UARTO)                    |  |  |

| ASCK2   |     | P12/SCK2       | ボー・レート・クロック入力(UART2)                    |  |  |

| SI0     | 入力  | P27            | シリアル・データ入力 ( 3線式シリアルI/O0 )              |  |  |

| SI1     |     | P30/RxD        | シリアル・データ入力 ( 3線式シリアルI/O1 )              |  |  |

| SI2     |     | P13/RxD2       | シリアル・データ入力 ( 3線式シリアルI/O2 )              |  |  |

| SI3     |     | P106           | シリアル・データ入力 ( 3線式シリアルI/O3 )              |  |  |

| SO0     | 出力  | P33            | シリアル・データ出力(3線式シリアルI/O0)                 |  |  |

| SO1     |     | P31/TxD        | シリアル・データ出力(3線式シリアルI/O1)                 |  |  |

| SO2     |     | P14/TxD2       | シリアル・データ出力 ( 3線式シリアルI/O2 )              |  |  |

| SO3     |     | P107           | シリアル・データ出力(3線式シリアルI/O3)                 |  |  |

| SCK0    | 入出力 | P32            | シリアル・クロック入力 / 出力 ( 3線式シリアルI/O0 )        |  |  |

| SCK1    |     | P25/INTP4/ASCK | シリアル・クロック入力 / 出力(3線式シリアルI/O1)           |  |  |

| SCK2    |     | P12/ASCK2      | シリアル・クロック入力 / 出力 ( 3線式シリアルI/O2 )        |  |  |

| SCK3    |     | P105           | シリアル・クロック入力 / 出力(3線式シリアルI/O3)           |  |  |

| NMI     | 入力  | P20            | 外部割り込み要求 -                              |  |  |

| INTP0   |     | P21            | ・タイマ / カウンタ1へのカウント・クロック入力               |  |  |

|         |     |                | ・CR11またはCR12のキャプチャ・トリガ信号                |  |  |

| INTP1   |     | P22            | ・タイマ / カウンタ2へのカウント・クロック入力               |  |  |

|         |     |                | ・CR22のキャプチャ・トリガ信号                       |  |  |

| INTP2   |     | P23/CI         | ・タイマ / カウンタ2へのカウント・クロック入力               |  |  |

|         |     |                | ・CR21のキャプチャ・トリガ信号                       |  |  |

| INTP3   |     | P24            | ・タイマ / カウンタ0へのカウント・クロック入力               |  |  |

|         |     |                | ・CR02のキャプチャ・トリガ信号                       |  |  |

| INTP4   |     | P25/ASCK/SCK1  | -                                       |  |  |

| INTP5   |     | P26            | A/Dコンバータの変換スタート・トリガ入力                   |  |  |

| AD0-AD7 | 入出力 | P40-P47        | 時分割アドレス / データ・バス (外部メモリ接続)              |  |  |

| A8-A15  | 出力  | P50-P57        | 上位アドレス・バス(外部メモリ接続)                      |  |  |

| A16-A19 | 出力  | P60-P63        | アドレス拡張時の上位アドレス(外部メモリ接続)                 |  |  |

| RD      | 出力  | P64            | 外部メモリへのリード・ストロープ                        |  |  |

| WR      | 出力  | P65            | 外部メモリへのライト・ストローブ                        |  |  |

| WAIT    | 入力  | P66/HLDRQ      | ウエイト挿入                                  |  |  |

| REFRQ   | 出力  | P67/HLDAK      | 外部疑似スタティック・メモリへのリフレッシュ・パルス出力            |  |  |

| HLDRQ   | 入力  | P66/WAIT       | バス・ホールド要求入力                             |  |  |

| HLDAK   | 出力  | P67/REFRQ      | バス・ホールド応答出力                             |  |  |

| ASTB    | 出力  | CLKOUT         | 時分割アドレス(A0-A7)のラッチ・タイミング出力(外部メモリ・アクセス時) |  |  |

| CLKOUT  | 出力  | ASTB           | クロック出力                                  |  |  |

| PWM0    | 出力  | -              | PWM出力0                                  |  |  |

# 6.2 ポート以外の端子(2/2)

| 端子名称               | 入出力 | 兼用端子    | 機能                                      |

|--------------------|-----|---------|-----------------------------------------|

| PWM1               | 出力  | -       | PWM出力1                                  |

| RX                 | 入力  | -       | データ入力 ( IEBus )                         |

| TX                 | 出力  | -       | データ出力(IEBus)                            |

| REGC               | -   | -       | レギュレータ出力安定用容量接続 / レギュレータ停止時の電源          |

| REGOFF             | -   | -       | レギュレータ動作指定信号                            |

| RESET              | 入力  | -       | チップ・リセット                                |

| X1                 | 入力  | -       | システム・クロック発振用クリスタル接続 ( X1にクロック入力も可能 )    |

| X2                 | -   |         |                                         |

| XT1                | 入力  | -       | 時計クロック接続                                |

| XT2                | -   | -       |                                         |

| ANI0-ANI7          | 入力  | P70-P77 | A/Dコンバータ用アナログ電圧入力                       |

| AV <sub>REF1</sub> | -   | -       | A/Dコンバータ用基準電圧印加                         |

| AVDD               |     |         | A/Dコンバータ用正電源                            |

| AVss               |     |         | A/Dコンバータ用GND                            |

| V <sub>DD</sub>    |     |         | 正電源                                     |

| Vss                |     |         | GND                                     |

| IC                 | 入力  |         | 内部接続されています。Vssと直接接続してください(ICテスト用の端子です)。 |

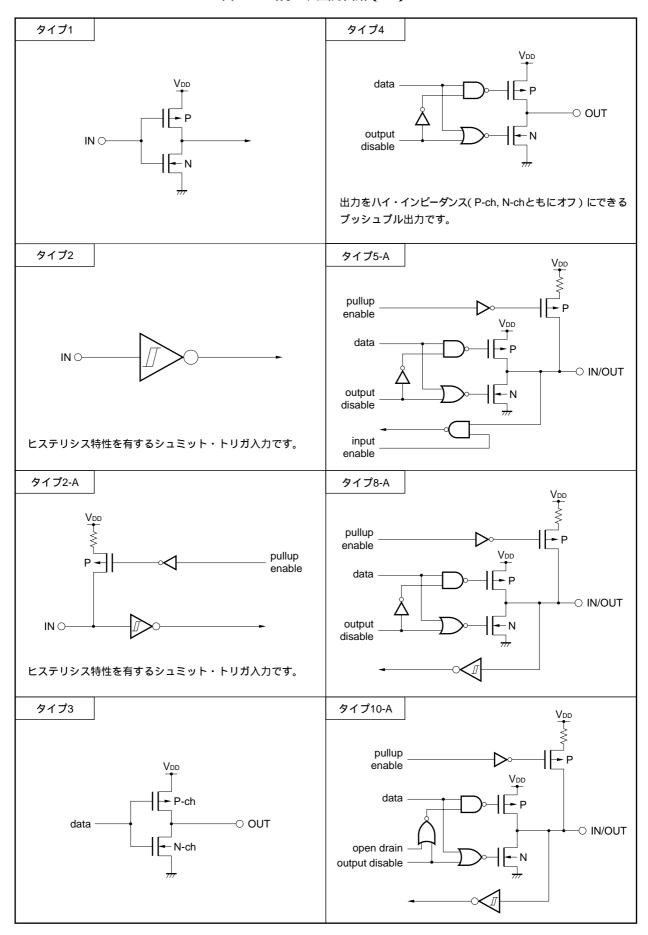

#### 6.3 端子の入出力回路と未使用端子の処理

各端子の入出力回路タイプと,未使用端子の処理を表6-1に示します。 また,各タイプの入出力回路については図6-1を参照してください。

表6-1 各端子の入出力回路タイプと未使用端子の処理(1/2)

| 端子名称                | 入出力回路タイプ | 入出力 | 未使用時の推奨接続方法             |

|---------------------|----------|-----|-------------------------|

| P00-P07             | 5-A      | 入出力 | 入力時:Vppに接続してください。       |

| P10, P11            |          |     | 出力時:オープンにしてください。        |

| P12/ASCK2/SCK2      | 8-A      | 1   |                         |

| P13/RxD2/SI2        | 5-A      | 1   |                         |

| P14/TxD2/SO2        |          |     |                         |

| P15-P17             |          |     |                         |

| P20/NMI             | 2        | 入力  | VpoまたはVssに接続してください。     |

| P21/INTP0           |          |     |                         |

| P22/INTP1           | 2-A      | 1   | Vodに接続してください。           |

| P23/INTP2/CI        |          |     |                         |

| P24/INTP3           |          |     |                         |

| P25/INTP4/ASCK/SCK1 | 8-A      | 入出力 | 入力時:Vppに接続してください。       |

|                     |          |     | <br>  出力時:オープンにしてください。  |

| P26/INTP5           | 2-A      | 入力  | Vpcに接続してください。           |

| P27/SI0             |          |     |                         |

| P30/RxD/SI1         | 5-A      | 入出力 | 入力時:Vppに接続してください。       |

| P31/TxD/SO1         |          |     | 出力時:オープンにしてください。        |

| P32/SCK0            | 10-A     | 1   |                         |

| P33/SO0             |          |     |                         |

| P34/TO0-P37/TO3     | 5-A      | 1   |                         |

| P40/AD0-P47/AD7     |          |     |                         |

| P50/A8-P57/A15      |          |     |                         |

| P60/A16-P63/A19     |          |     |                         |

| P64/RD              |          |     |                         |

| P65/WR              |          |     |                         |

| P66/WAIT/HLDRQ      |          |     |                         |

| P67/REFRQ/HLDAK     |          |     |                         |

| P70/ANI0-P77/ANI7   | 20       | 入出力 | 入力時:VppまたはVssに接続してください。 |

| P90-P97             | 5-A      | 1   | 出力時:オープンにしてください。        |

| P100-P104           |          |     |                         |

| P105/SCK3           | 10-A     | 1   |                         |

| P106/SI3            | 8-A      | 1   |                         |

| P107/SO3            | 10-A     | 1   |                         |

| ASTB/CLKOUT         | 4        | 出力  | オープンにしてください。            |

| RESET               | 2        | 入力  | -                       |

| IC                  | 1        | 1   | Vssに直接接続してください。         |

| XT2                 | -        | -   | オープンにしてください。            |

| XT1                 | -        | 入力  | Vssに接続してください。           |

| REGOFF              | 1        | -   | VDDに接続してください。           |

表6-1 各端子の入出力回路タイプと未使用端子の処理(2/2)

| 端子名称               | 入出力回路タイプ | 入出力 | 未使用時の推奨接続方法         |

|--------------------|----------|-----|---------------------|

| REGC               | -        | -   | VDDに接続してください。       |

| PWM0, PWM1         | 3        | 出力  | オープンにしてください。        |

| RX                 | 1        | 入力  | VpdまたはVssに接続してください。 |

| TX                 | 3        | 出力  | オープンにしてください。        |

| AV <sub>REF1</sub> | -        | -   | Vssに接続してください。       |

| AVss               |          |     |                     |

| AVDD               |          |     | VDDに接続してください。       |

注意 入出力兼用端子で,入出力のモードが不定な場合は,数十kΩの抵抗を介してVooに接続してください(特に,電源投入時にリセット入力端子がロウ・レベル入力電圧以上になる場合や,ソフトウエアで入出力を切り替えている場合)。

**備考** タイプ番号は78Kシリーズで統一しているため,各製品内では連番とはかぎりません(内蔵しない回路あり)。

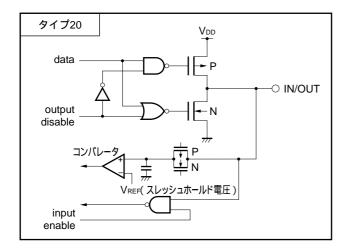

図6 - 1 端子の入出力回路 (1/2)

# 図6-1 端子の入出力回路 (2/2)

#### 7. CPUアーキテクチャ

#### 7.1 メモリ空間

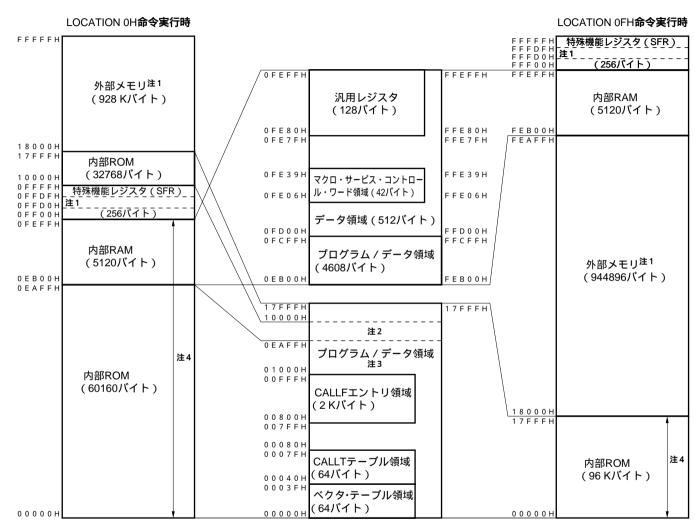

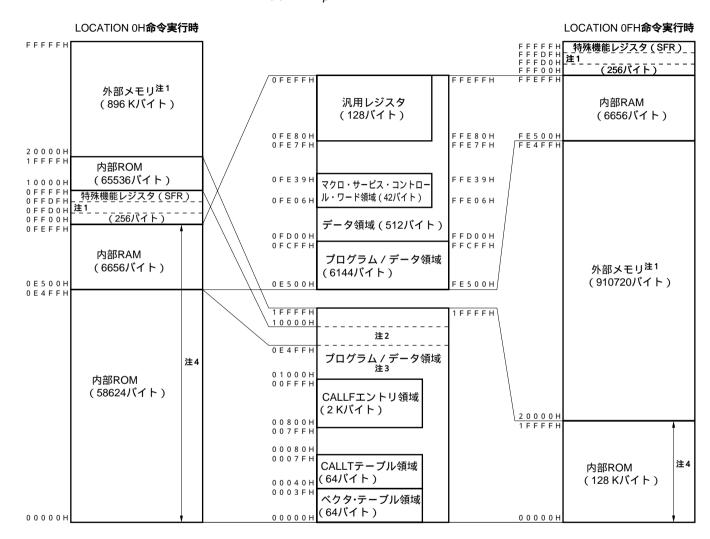

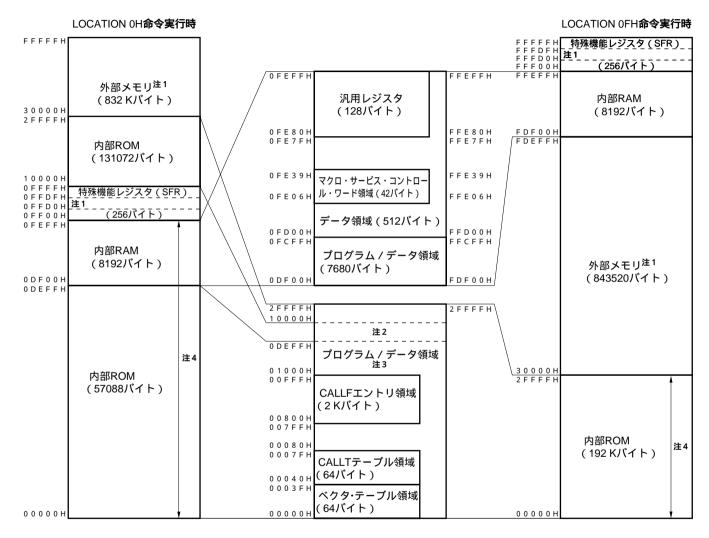

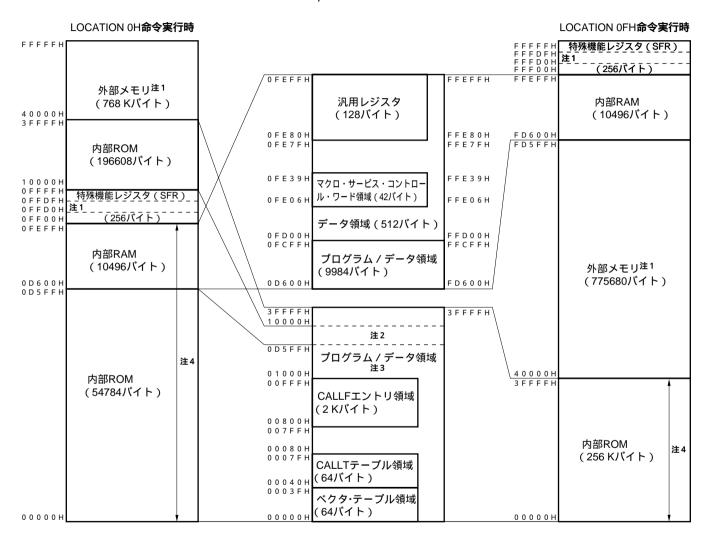

1 Mバイトのメモリ空間をアクセスできます。LOCATION命令によって,内部データ領域(特殊機能レジスタおよび内部RAM)のマッピングを選択できます。また,LOCATION命令は,リセット解除後に必ず実行する必要があり,2回以上使用することはできません。

#### (1) LOCATION 0H命令を実行した場合

#### ・内部メモリ

内部データ領域と内部ROM領域は,次のようになります。

| 品 名         | 内部データ領域       | 内部ROM領域       |

|-------------|---------------|---------------|

| μ PD784935A | 0EB00H-0FFFFH | 00000H-0EAFFH |

|             |               | 10000H-17FFFH |

| μ PD784936A | 0E500H-0FFFFH | 00000H-0E4FFH |

|             |               | 10000H-1FFFFH |

| μ PD784937A | 0DF00H-0FFFFH | 00000H-0DEFFH |

|             |               | 10000H-2FFFFH |

| μ PD784938A | 0D600H-0FFFFH | 00000H-0D5FFH |

|             |               | 10000H-3FFFFH |

# ★ 注意 内蔵しているROMのうち,内部データ領域と重なる次の領域は,LOCATION 0H命令実行時には 使用できません。

| 品 名         | 使用不可領域                    |

|-------------|---------------------------|

| μ PD784935A | 0EB00H-0FFFFH ( 5376バイト ) |

| μ PD784936A | 0E500H-0FFFFH ( 6192バイト ) |

| μ PD784937A | ODF00H-0FFFFH ( 8448バイト ) |

| μ PD784938A | 0D600H-0FFFFH             |

#### ・外部メモリ

外部メモリは,外部メモリ拡張モードでアクセスします。

#### (2) LOCATION 0FH命令を実行した場合

#### ・内部メモリ

内部データ領域と内部ROM領域は,次のようになります。

| 品 名         | 内部データ領域       | 内部ROM領域       |

|-------------|---------------|---------------|

| μ PD784935A | FEB00H-FFFFFH | 00000H-17FFFH |

| μ PD784936A | FE500H-FFFFFH | 00000H-1FFFFH |

| μ PD784937A | FDF00H-FFFFFH | 00000H-2FFFFH |

| μ PD784938A | FD600H-FFFFFH | 00000H-3FFFFH |

### ・外部メモリ

外部メモリは,外部メモリ拡張モードでアクセスします。

PD784935A,784936A,784937A,784938A

- 注1. 外部メモリ拡張モードでアクセス

- 2. この領域の5376バイトは, LOCATION 0FH命令実行時のみ内部ROMとして使用できます

- 3. LOCATION 0H命令実行時: 92928バイト, LOCATION 0FH命令実行時: 98304バイト

- 4. ベース領域,リセットまたは割り込みによるエントリ領域。ただし,リセットについては内部RAMを除く

U13572JJ2V0DS

**図**7 - 2 µPD784936A**のメモリ・マップ**

#### 注1. 外部メモリ拡張モードでアクセス

- 2. この領域の6912バイトは, LOCATION 0FH命令実行時のみ内部ROMとして使用できます

- 3. LOCATION 0H命令実行時: 124160バイト, LOCATION 0FH命令実行時: 131072バイト

- 4. ベース領域,リセットまたは割り込みによるエントリ領域。ただし,リセットについては内部RAMを除く

PD784935A,784936A,784937A,784938A

- 注1. 外部メモリ拡張モードでアクセス

- 2. この領域の8448バイトは, LOCATION 0FH命令実行時のみ内部ROMとして使用できます

- 3. LOCATION 0H命令実行時: 188160バイト, LOCATION 0FH命令実行時: 196608バイト

- 4. ベース領域,リセットまたは割り込みによるエントリ領域。ただし,リセットについては内部RAMを除く

U13572JJ2V0DS

Z

図7 - 4 µPD784938Aのメモリ・マップ

#### 注1. 外部メモリ拡張モードでアクセス

- 2. この領域の10752バイトは, LOCATION 0FH命令実行時のみ内部ROMとして使用できます

- 3. LOCATION 0H命令実行時: 251392バイト, LOCATION 0FH命令実行時: 262144バイト

- 4. ベース領域,リセットまたは割り込みによるエントリ領域。ただし,リセットについては内部RAMを除く

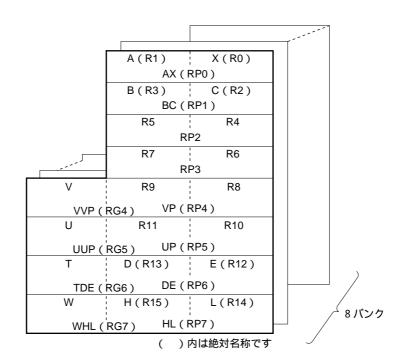

#### 7.2 CPU**レジスタ**

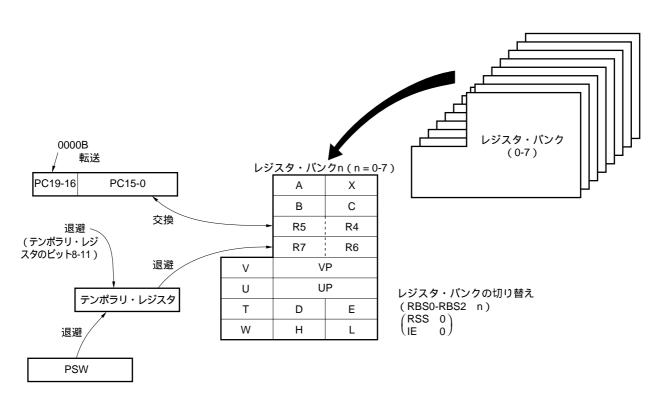

#### 7.2.1 汎用レジスタ

8ビットの汎用レジスタ16本で構成されています。また,8ビット汎用レジスタ2本を組み合わせて16ビット汎用レジスタとして使用できます。さらに,16ビット汎用レジスタのうち4本は,アドレス拡張用の8ビット・レジスタと組み合わせて24ビット・アドレス指定用レジスタとして使用できます。

これらのレジスタ・セットは8バンク用意されており,ソフトウエアまたはコンテキスト・スイッチング機能により切り替えて使用できます。

アドレス拡張用のV, U, T, Wレジスタを除いた汎用レジスタは,内部RAMにマッピングされています。

図7-5 汎用レジスタのフォーマット

注意 R4, R5, R6, R7, RP2, RP3, PSWのRSSビットを1にすることで, それぞれ, X, A, C, B, AX, BCレジスタとして使用できますが, この機能を使用するのは, 78K/ シリーズ用のプログラムを流用する場合だけにしてください。

#### 7.2.2 制御レジスタ

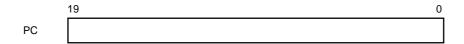

# (1) プログラム・カウンタ (PC)

20ビットのプログラム・カウンタです。プログラムの実行により,自動的に更新されます。

図7-6 プログラム・カウンタ (PC) のフォーマット

# (2) プログラム・ステータス・ワード (PSW)

CPUの各種状態を保持するレジスタです。プログラムの実行により自動的に更新されます。

図7-7 プログラム・ステータス・ワード (PSW) のフォーマット

**注** このフラグは,78K/ シリーズとの互換性を保つために用意されているフラグです。78K/ シリーズ 用のソフトウエアを流用するとき以外は必ず0にしてください。

#### (3) スタック・ポインタ (SP)

スタックの先頭アドレスを保持する24ビットのポインタです。 上位4ビットには,必ず0を書き込んでください。

図7-8 スタック・ポインタ (SP) のフォーマット

|    | _23 |   |   | 20 | U |

|----|-----|---|---|----|---|

| SP | 0   | 0 | 0 | 0  |   |

#### 7.2.3 **特殊機能レジスタ(SFR)**

内蔵周辺ハードウエアのモード・レジスタ,コントロール・レジスタなどの特別な機能が割り付けられたレジスタで,OFF00H-0FFFFH<sup>注</sup>の256バイトの空間にマッピングされています。

注 LOCATION 0H命令実行時。LOCATION 0FH命令実行時はFFF00H-FFFFFH

注意 この領域内で,SFRの割り付けられていないアドレスをアクセスしないでください。誤ってアクセスすると, $\mu$  PD784938Aがデッドロック状態となることがあります。デッドロック状態は,リセット入力によってのみ解除されます。

表7-1に特殊機能レジスタ(SFR)の一覧を示します。表中の項目の意味は次のようになります。

・略 号 ······· 内蔵されたSFRを示す記号。NEC製アセンブラ(RA78K4)では予約語になって

います。Cコンパイラ (CC78K4) では#pragma sfr指令により , sfr変数として

使用できます。

・R/W ・・・・・・・・・ 該当するSFRが読み出し/書き込みが可能かどうかを示します。

R/W:読み出し(Read)/書き込み(Write)可能

R :読み出し(Read)のみW :書き込み(Write)のみ

・操作可能ビット単位 · · 該当するSFRを操作する場合に,適応可能な操作ビット単位を示します。

16ビット操作可能なSFRはオペランドのsfrpに記述でき,アドレスで指定する場

合は偶数アドレスを記述します。

1ビット操作可能なSFRは,ビット操作命令に記述できます。

・リセット時 ・・・・・・・・ RESET入力時の各レジスタの状態を示します。

表7-1 特殊機能レジスタ (SFR) 一覧 (1/4)

| アドレス <sup>注</sup> | 特殊機能レジスタ(SFR)名称                    |                   | 略    | 号     | R/W | 操作   | リセット時 |      |       |

|-------------------|------------------------------------|-------------------|------|-------|-----|------|-------|------|-------|

|                   |                                    |                   |      |       |     | 1ビット |       | 8ビット | 16ビット |

| 0FF00H            | ポート0                               |                   | P0   |       | R/W |      |       | -    | 不定    |

| 0FF01H            | ポート1                               | P1                |      |       |     |      | -     |      |       |

| 0FF02H            | ポート2                               | P2                |      | R     |     |      | -     |      |       |

| 0FF03H            | ポート3                               |                   | P3   |       | R/W |      |       | -    |       |

| 0FF04H            | ポート4                               |                   | P4   |       |     |      |       | -    |       |

| 0FF05H            | ポート5                               |                   | P5   |       |     |      |       | -    |       |

| 0FF06H            | ポート6                               |                   | P6   |       |     |      |       | -    | 00H   |

| 0FF07H            | ポート7                               |                   | P7   |       |     |      |       | -    | 不定    |

| 0FF09H            | ポート9                               |                   | P9   |       |     |      |       | -    |       |

| 0FF0AH            | ポート10                              |                   | P10  |       |     |      |       | -    |       |

| 0FF0EH            |                                    | ポート0バッファ・レジスタL    | P0L  |       |     |      |       | -    |       |

| 0FF0FH            | ポート0バッファ・レジスタH                     |                   | P0H  |       |     |      |       | -    |       |

| 0FF10H            | コンペア・レジスタ(タイマ                      | 7/カウンタ0)          | CR00 |       |     | -    | -     |      |       |

| 0FF12H            | キャプチャ / コンペア・レシ                    | ブスタ(タイマ / カウンタ0)  | CR01 |       |     | -    | -     |      |       |

| 0FF14H            | コンペア・レジスタL(タイ                      | マ / カウンタ1 )       | CR10 | CR10W |     | -    |       |      |       |

| 0FF15H            | コンペア・レジスタH (タイ                     | マ / カウンタ1 )       | -    |       |     | -    | -     |      |       |

| 0FF16H            | キャプチャ / コンペア・レジ                    | 「スタL(タイマ / カウンタ1) | CR11 | CR11W |     | -    |       |      |       |

| 0FF17H            | キャプチャ / コンペア・レジスタH ( タイマ / カウンタ1 ) |                   |      |       |     | -    | -     |      |       |

| 0FF18H            | コンペア・レジスタL (タイマ / カウンタ2 )          |                   |      | CR20W |     | -    |       |      |       |

| 0FF19H            | コンペア・レジスタH (タイ                     | マ / カウンタ2 )       | -    |       |     | -    | -     |      |       |

| 0FF1AH            | キャプチャ / コンペア・レジ                    | 「スタL(タイマ/カウンタ2)   | CR21 | CR21W | ,   | -    |       |      |       |

| 0FF1BH            | キャプチャ / コンペア・レジ                    | スタH(タイマ / カウンタ2)  | -    |       |     | -    | -     |      |       |

| 0FF1CH            | コンペア・レジスタL (タイ                     | ₹3)               | CR30 | CR30W |     | -    |       |      | 1     |

| 0FF1DH            | コンペア・レジスタH (タイ                     | ₹3)               | -    |       |     | -    | -     |      |       |

| 0FF20H            | ポート0モード・レジスタ                       |                   | PM0  |       |     |      |       | -    | FFH   |

| 0FF21H            | ポート1モード・レジスタ                       |                   | PM1  |       |     |      |       | -    |       |

| 0FF23H            | ポート3モード・レジスタ                       |                   | РМ3  |       |     |      |       | -    |       |

| 0FF24H            | ポート4モード・レジスタ                       |                   | PM4  |       |     |      |       | -    |       |

| 0FF25H            | ポート5モード・レジスタ                       |                   | PM5  |       |     |      |       | -    |       |

| 0FF26H            | ポート6モード・レジスタ                       |                   | PM6  |       |     |      |       | -    |       |

| 0FF27H            | ポート7モード・レジスタ                       |                   | PM7  |       |     |      |       | -    |       |

| 0FF29H            | ポート9モード・レジスタ                       |                   | РМ9  |       |     |      |       | -    |       |

| 0FF2AH            | ポート10モード・レジスタ                      |                   | PM10 |       |     |      |       | -    |       |

| 0FF2EH            | リアルタイム出力ポート・コ                      | コントロール・レジスタ       | RTPC |       |     |      |       | -    | 00H   |

| 0FF30H            | キャプチャ / コンペア・コン                    | ノトロール・レジスタ0       | CRC0 |       |     | -    |       | -    | 10H   |

| 0FF31H            | タイマ出力コントロール・し                      | ッジスタ              | TOC  |       |     |      |       | -    | 00H   |

| 0FF32H            | キャプチャ / コンペア・コン                    | ノトロール・レジスタ1       | CRC1 |       |     | -    |       | -    |       |

| 0FF33H            | キャプチャ / コンペア・コン                    | ノトロール・レジスタ2       | CRC2 |       |     | -    |       | -    | 10H   |

| 0FF36H            | キャプチャ・レジスタ(タイ                      | (マ/カウンタ0)         | CR02 |       | R   | -    | -     |      | 0000H |

| 0FF38H            | キャプチャ・レジスタL ( タ                    | イマ / カウンタ1 )      | CR12 | CR12W |     | -    |       |      | 1     |

| 0FF39H            | キャプチャ・レジスタH(タ                      | イマ / カウンタ1 )      | -    | 1     |     | -    | -     |      |       |

注 LOCATION 0H命令を実行した場合。LOCATION 0FH命令を実行した場合は,この値に "F0000H" を加えます。

表7 - 1 特殊機能レジスタ (SFR) 一覧 (2/4)

| アドレス <sup>注</sup> | 特殊機能レジスタ(SFR)名称           | 略号       |          | R/W | 操作   | リセット時 |       |       |

|-------------------|---------------------------|----------|----------|-----|------|-------|-------|-------|

|                   |                           |          |          |     | 1ビット | 8ビット  | 16ビット |       |

| 0FF3AH            | キャプチャ・レジスタL (タイマ / カウンタ2) | CR22     | CR22W    | R   | -    |       |       | 0000H |

| 0FF3BH            | キャプチャ・レジスタH(タイマ / カウンタ2)  | -        |          |     | -    | -     |       |       |

| 0FF41H            | ポート1モード・コントロール・レジスタ       | PMC1     |          | R/W |      |       | -     | 00H   |

| 0FF43H            | ポート3モード・コントロール・レジスタ       | РМС3     |          |     |      |       | -     |       |

| 0FF4AH            | ポート10モード・コントロール・レジスタ      | PMC10    | )        |     |      |       | -     |       |

| 0FF4EH            | プルアップ抵抗オプション・レジスタL        | PUOL     |          |     |      |       | -     |       |

| 0FF4FH            | プルアップ抵抗オプション・レジスタH        | PUOH     |          |     |      |       | -     |       |

| 0FF50H            | タイマ・レジスタ0                 | TMO      |          | R   | -    | -     |       | 0000H |

| 0FF51H            |                           |          |          |     | -    | -     |       |       |

| 0FF52H            | タイマ・レジスタ1                 | TM1      | TM1W     |     | -    |       |       |       |

| 0FF53H            |                           | -        |          |     | -    | -     |       |       |

| 0FF54H            | タイマ・レジスタ2                 | TM2      | TM2W     |     | -    |       |       |       |

| 0FF55H            |                           | -        |          |     | -    | -     |       |       |

| 0FF56H            | タイマ・レジスタ3                 | ТМЗ      | TM3W     |     | -    |       |       |       |

| 0FF57H            |                           | -        |          |     | _    | _     |       |       |

| 0FF5CH            | プリスケーラ・モード・レジスタ0          | PRM0     |          | R/W | -    |       | -     | 11H   |

| 0FF5DH            | タイマ・コントロール・レジスタ0          | TMC0     |          |     |      |       | -     | 00H   |

| 0FF5EH            | プリスケーラ・モード・レジスタ1          | PRM1     |          |     | _    |       | -     | 11H   |

| 0FF5FH            | タイマ・コントロール・レジスタ1          | TMC1     |          |     |      |       | -     | 00H   |

| 0FF68H            | A/Dコンバータ・モード・レジスタ         | ADM      |          |     |      |       | -     | 00H   |

| 0FF6AH            | A/D変換結果レジスタ               | ADCR     |          | R   | -    |       | -     | 不定    |

| 0FF6CH            | A/D電流カット選択レジスタ            | IEAD     |          | R/W |      |       | -     | 00H   |

| 0FF6FH            | 時計用タイマ・モード・レジスタ           | WM       |          |     |      |       | -     |       |

| 0FF70H            | PWMコントロール・レジスタ            | PWMC     |          |     |      |       | -     | 05H   |

| 0FF71H            | PWMプリスケーラ・レジスタ            | PWPR     |          |     | -    |       | -     | 00H   |

| 0FF72H            | PWMモジュロ・レジスタ0             | PWM0     |          |     | -    | -     |       | 不定    |

| 0FF74H            | PWMモジュロ・レジスタ1             | PWM1     |          |     | -    | -     |       |       |

| 0FF78H            | ROMコレクション・コントロール・レジスタ     | CORC     |          |     |      |       | -     | 00H   |

| 0FF79H            | ROMコレクション・アドレス・ポインタH      | CORA     | H        |     | -    |       | -     |       |

| 0FF7AH            | ROMコレクション・アドレス・ポインタL      | CORA     | <u> </u> |     | -    | -     |       |       |

| 0FF7DH            |                           | OSPC     |          |     |      |       | -     | 00H   |

| 0FF80H            |                           | CSIM3    |          |     |      |       | -     |       |

|                   | ジスタ3                      |          |          |     |      |       |       |       |

| 0FF82H            | クロック同期式シリアル・インタフェース・モード・レ | CSIM     |          | :   |      |       | -     |       |

|                   | ジスタ                       |          |          |     |      |       |       |       |

| 0FF84H            | クロック同期式シリアル・インタフェース・モード・レ | ・レ CSIM1 |          |     |      |       | -     | 1     |

|                   | ジスタ1                      |          |          |     |      |       |       |       |

| 0FF85H            | クロック同期式シリアル・インタフェース・モード・レ | CSIM2    |          |     |      |       | -     | 1     |

|                   | ジスタ2                      |          |          |     |      |       |       |       |

| 0FF86H            | シリアル・シフト・レジスタ             | SIO      |          | 1   | _    |       | -     | 不定    |

注 LOCATION 0H命令を実行した場合。LOCATION 0FH命令を実行した場合は,この値に "F0000H" を加えます。

表7-1 **特殊機能レジスタ**(SFR)**一覧**(3/4)

| アドレス <sup>注</sup> | 特殊機能レジスタ(SFR)名称            | 略                          | 号   | R/W | 操作   | リセット時      |       |       |

|-------------------|----------------------------|----------------------------|-----|-----|------|------------|-------|-------|

|                   |                            |                            |     |     | 1ビット | 8ビット       | 16ビット |       |

| 0FF88H            | アシンクロナス・シリアル・インタフェース・モード・  | コナス・シリアル・インタフェース・モード・ ASIM |     | R/W |      |            | -     | 00H   |

|                   | ブスタ                        |                            |     |     |      |            |       |       |

| 0FF89H            | アシンクロナス・シリアル・インタフェース・モード・  | · ASIM2                    |     |     |      |            | -     |       |

|                   | レジスタ2                      |                            |     |     |      |            |       |       |

| 0FF8AH            | アシンクロナス・シリアル・インタフェース・ステータ  | ASIS                       |     | R   |      |            | -     |       |

|                   | ス・レジスタ                     |                            |     |     |      |            |       |       |

| 0FF8BH            | アシンクロナス・シリアル・インタフェース・ステータ  | ASIS2                      |     |     |      |            | -     |       |

|                   | ス・レジスタ2                    |                            |     |     |      |            |       |       |

| 0FF8CH            | シリアル受信バッファ:UART0           | RXB                        |     |     | -    |            | -     | 不定    |

|                   | シリアル送信シフト・レジスタ:UART0       | TXS                        |     | W   | -    |            | -     |       |

|                   | シリアル・シフト・レジスタ : IOE1       | SIO1                       |     | R/W | -    |            | -     |       |

| 0FF8DH            | シリアル受信バッファ:UART2           | RXB2                       |     | R   | -    |            | -     |       |

|                   | シリアル送信シフト・レジスタ:UART2       | TXS2                       |     | W   | -    |            | -     |       |

|                   | シリアル・シフト・レジスタ : IOE2       | SIO2                       |     | R/W | -    |            | -     |       |

| 0FF8EH            | シリアル・シフト・レジスタ3 : IOE3      | SIO3                       |     |     | -    |            | -     |       |

| 0FF90H            | ボー・レート・ジェネレータ・コントロール・レジスタ  | BRGC                       |     |     | -    |            | -     | 00H   |

| 0FF91H            | ボー・レート・ジェネレータ・コントロール・レジスタ2 | BRGC                       | 2   |     | -    |            | -     |       |

| 0FFA0H            | 外部割り込みモード・レジスタ0            | INTM0<br>INTM1             |     |     |      |            | -     |       |

| 0FFA1H            | 外部割り込みモード・レジスタ1            |                            |     |     |      |            | -     |       |

| 0FFA4H            | サンプリング・クロック選択レジスタ          | SCS0                       |     |     | -    |            | -     |       |

| 0FFA8H            | インサービス・プライオリティ・レジスタ        | ISPR                       |     | R   |      |            | -     |       |

| 0FFAAH            | 割り込みモード・コントロール・レジスタ        | IMC                        |     | R/W |      |            | -     | 80H   |

| 0FFACH            | 割り込みマスク・レジスタ0L             | MK0L                       | MK0 |     |      |            |       | FFFFH |

| 0FFADH            | 割り込みマスク・レジスタ0H             | МКОН                       |     |     |      |            |       |       |

| 0FFAEH            | 割り込みマスク・レジスタ1L             | MK1L                       | MK1 |     |      |            |       |       |

| 0FFAFH            | 割り込みマスク・レジスタ1H             | MK1H                       |     |     |      |            |       |       |

| 0FFB0H            | バス・コントロール・レジスタ             | BCR                        | -   |     |      |            | -     | 00H   |

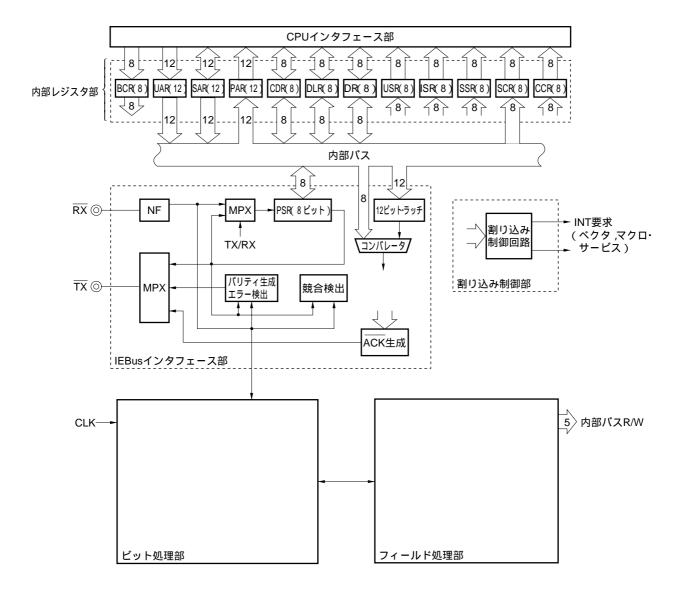

| 0FFB2H            | ユニット・アドレス・レジスタ             | UAR                        |     |     | -    | -          |       | 0000H |

| 0FFB4H            | スレーブ・アドレス・レジスタ             | SAR                        |     |     | -    | -          |       |       |

| 0FFB6H            | パートナー・アドレス・レジスタ            | PAR                        |     | R   | -    | -          |       |       |

| 0FFB8H            | コントロール・データ・レジスタ            | CDR                        |     | R/W | -    |            | -     | 01H   |

| 0FFB9H            | 電文長レジスタ                    | DLR                        |     |     | -    |            | -     |       |

| 0FFBAH            | データ・レジスタ                   | DR                         |     |     | -    |            | -     | 00H   |

| 0FFBBH            | ユニット・ステータス・レジスタ            | USR                        |     | R   |      |            | -     |       |

| 0FFBCH            | インタラプト・ステータス・レジスタ          | ISR                        |     | R/W |      |            | -     |       |

| 0FFBDH            | スレーブ・ステータス・レジスタ            | SSR                        |     | R   |      |            | -     | 41H   |

| 0FFBEH            | サクセス・カウント・レジスタ             | SCR                        |     | 7   | -    |            | -     | 01H   |

| 0FFBFH            | コミュニケーション・カウント・レジスタ        | CCR                        |     | 1   | -    |            | -     | 20H   |

| 0FFC0H            | スタンバイ・コントロール・レジスタ          | STBC                       |     | R/W | -    | <b>注</b> 2 | -     | 30H   |

| 0FFC2H            | ウォッチドッグ・タイマ・モード・レジスタ       | WDM                        |     | 1   | -    | <b>注</b> 2 | -     | 00H   |

- **注**1. LOCATION 0H命令を実行した場合。LOCATION 0FH命令を実行した場合は,この値に"F0000H"を加えます。

- 2. 書き込みは , 専用の命令MOV STBC, #btye命令および , MOV MDM, #byte命令によってのみ可能です。他の命令では , 書き込みはできません。

表7 - 1 特殊機能レジスタ (SFR) 一覧 (4/4)

| アドレス <sup>注</sup> | 特殊機能レジスタ(SFR)名称                 | 略号     | R/W | 操作   | リセット時 |       |       |

|-------------------|---------------------------------|--------|-----|------|-------|-------|-------|

|                   |                                 |        |     | 1ビット | 8ビット  | 16ビット |       |

| 0FFC4H            | メモリ拡張モード・レジスタ                   | MM     | R/W |      |       | -     | 20H   |

| 0FFC5H            | ホールド・モード・レジスタ                   | HLDM   |     |      |       | -     | 00H   |

| 0FFC6H            | クロック出力モード・レジスタ                  | CLOM   |     |      |       | -     |       |

| 0FFC7H            | プログラマブル・ウエイト制御レジスタ1             | PWC1   |     | -    |       | -     | AAH   |

| 0FFC8H            | プログラマブル・ウエイト制御レジスタ2             | PWC2   |     | -    | -     |       | AAAAH |

| 0FFCCH            | リフレッシュ・モード・レジスタ                 | RFM    |     |      |       | -     | 00H   |

| 0FFCDH            | リフレッシュ領域指定レジスタ                  | RFA    |     |      |       | -     |       |

| 0FFCFH            | 発振安定時間指定レジスタ                    | OSTS   |     | -    |       | -     |       |

| 0FFD0H-           | 外部SFR領域                         | -      |     |      |       | -     | -     |

| 0FFDFH            |                                 |        |     |      |       |       |       |

| 0FFE0H            | 割り込み制御レジスタ(INTPO)               | PIC0   |     |      |       | -     | 43H   |

| 0FFE1H            | 割り込み制御レジスタ(INTP1)               | PIC1   |     |      |       | -     |       |

| 0FFE2H            | 割り込み制御レジスタ(INTP2)               | PIC2   |     |      |       | -     |       |

| 0FFE3H            | 割り込み制御レジスタ(INTP3)               | PIC3   |     |      |       | -     |       |

| 0FFE4H            | 割り込み制御レジスタ(INTC00)              | CIC00  |     |      |       | -     |       |

| 0FFE5H            | 割り込み制御レジスタ(INTC01)              | CIC01  |     |      |       | -     |       |

| 0FFE6H            | 割り込み制御レジスタ(INTC10)              | CIC10  |     |      |       | -     |       |

| 0FFE7H            | 割り込み制御レジスタ(INTC11)              | CIC11  |     |      |       | -     |       |

| 0FFE8H            | 割り込み制御レジスタ(INTC20)              | CIC20  |     |      |       | -     |       |

| 0FFE9H            | 割り込み制御レジスタ(INTC21)              | CIC21  |     |      |       | -     |       |

| 0FFEAH            | 割り込み制御レジスタ(INTC30)              | CIC30  |     |      |       | -     |       |

| 0FFEBH            | 割り込み制御レジスタ(INTP4)               | PIC4   |     |      |       | -     |       |

| 0FFECH            | 割り込み制御レジスタ(INTP5)               | PIC5   |     |      |       | -     |       |

| 0FFEDH            | 割り込み制御レジスタ(INTAD)               | ADIC   |     |      |       | -     |       |

| OFFEEH            | 割り込み制御レジスタ(INTSER)              | SERIC  |     |      |       | -     |       |

| 0FFEFH            | 割り込み制御レジスタ(INTSR)               | SRIC   |     |      |       | -     |       |

|                   | 割り込み制御レジスタ(INTCSI1)             | CS C1  |     |      |       | -     |       |

| 0FFF0H            | 割り込み制御レジスタ(INTST)               | STIC   |     |      |       | -     |       |

| 0FFF1H            | 割り込み制御レジスタ(INTCSI)              | cs c   |     |      |       | -     |       |

| 0FFF2H            | 割り込み制御レジスタ(INTSER2)             | SERIC2 |     |      |       | -     |       |

| 0FFF3H            | 割り込み制御レジスタ(INTSR2)              | SRIC2  |     |      |       | -     |       |

|                   | 割り込み制御レジスタ(INTCSI2)             | CS C2  | 1   |      |       | -     |       |

| 0FFF4H            | 割り込み制御レジスタ(INTST2)              | STIC2  | 1   |      |       | -     |       |

| 0FFF6H            | 割り込み制御レジスタ(INTIE1)              | IEIC1  | 1   |      |       | -     |       |

| 0FFF7H            | 割り込み制御レジスタ(INTIE2)              | IEIC2  | 1   |      |       | -     |       |

| 0FFF8H            | 割り込み制御レジスタ (INTW)               | WIC    | 1   |      |       | -     |       |

| 0FFF9H            | 割り込み制御レジスタ (INTCSI3)            | CS C3  | 1   |      |       | -     |       |

| 0FFFCH            | 内部メモリ・サイズ切り替えレジスタ <sup>注2</sup> | IMS    | 1   | _    |       | -     | FFH   |

**注**1. LOCATION 0H命令を実行した場合。LOCATION 0FH命令を実行した場合は,この値に "F0000H" を加えます。

2. 本レジスタへの書き込みは ,  $\mu$  PD78F4938Aの場合のみ意味があります。

# 8. 周辺ハードウエア機能

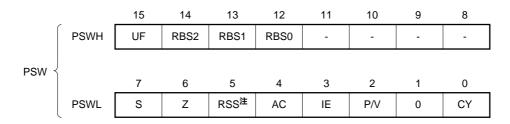

#### 8.1 ポート

図8 - 1のようなポートを備えており,多様な制御ができます。各ポートの機能は表8 - 1のとおりです。ポート0からポート6,ポート9,ポート10は,入力時に,内蔵プルアップをソフトウエアで指定できます。

図8 - 1 ポートの構成

# 表8-1 ポートの機能

| ポート名  | 端子名称      | 機能                               | ソフトウエア・プルアップの指定    |

|-------|-----------|----------------------------------|--------------------|

| ポート0  | P00-P07   | ・1ビット単位で入力か出力に指定可能               | 入力モードの端子について一括して指定 |

|       |           | ・4ビット・リアルタイム出力としても動作可能           |                    |

|       |           | ( P00-P03, P04-P07 )             |                    |

|       |           | ・トランジスタ駆動可能                      |                    |

| ポート1  | P10-P17   | ・1ビット単位で入力か出力に指定可能               | 入力モードの端子について一括して指定 |

|       |           | ·LED駆動可能                         |                    |

| ポート2  | P20-P27   | ・入力ポート                           | 6ビット単位(P22-P27)    |

| ポート3  | P30-P37   | ・1ビット単位で入力か出力に指定可能               | 入力モードの端子について一括して指定 |

|       |           | ・P32/SCK0端子とP33/SO0端子は,N-chオープ   |                    |

|       |           | ン・ドレーンに設定可能                      |                    |

| ポート4  | P40-P47   | ・1ビット単位で入力か出力に指定可能               | 入力モードの端子について一括して指定 |

|       |           | ·LED駆動可能                         |                    |

| ポート5  | P50-P57   | ・1ビット単位で入力か出力に指定可能               | 入力モードの端子について一括して指定 |

|       |           | ·LED駆動可能                         |                    |

| ポート6  | P60-P67   | ・1ビット単位で入力か出力に指定可能               | 入力モードの端子について一括して指定 |

| ポート7  | P70-P77   | ・1ビット単位で入力か出力に指定可能               | -                  |

| ポート9  | P90-P97   | ・1ビット単位で入力か出力に指定可能               | 入力モードの端子について一括して指定 |

| ポート10 | P100-P107 | ・1ビット単位で入力か出力に指定可能               | 入力モードの端子について一括して指定 |

|       |           | ・P105/SCK3端子とP107/SO3端子は,N-chオープ |                    |

|       |           | ン・ドレーンに設定可能                      |                    |

## 8.2 クロック発生回路

動作に必要なクロック発生回路を備えています。また,クロック発生回路には分周回路があり,高速動作が不要な場合は,内部動作周波数を下げることにより,低消費電流を実現できます。

クロック同期式 3 線式シリアルI/O (CSI) アシンクロナス・シリアルI/O (UART/IOE) INTP0ノイズ除去回路 発振安定用タイマ STBC.4,5 タイマ/カウンタ fxx/8 fxx 発振回路 1/2 1/2 1/2 fxx/4 セレクタ fclk CPU fxx/2 各周辺回路 STBC.7 1 セ - IEBusコントローラの動作クロック<sup>注</sup> 0 時計クロック ― 時計用タイマ<sup>注</sup> ► INTW割り込み信号 メイン・クロック 一

図8-2 クロック発生回路のブロック図

**注** メイン・クロックを使用時はスタンバイ・コントロール・レジスタ (STBC) のビット7に1を必ず設定してください。

備考 fxx : 発振周波数

★ fclk : 内部システム・クロック周波数

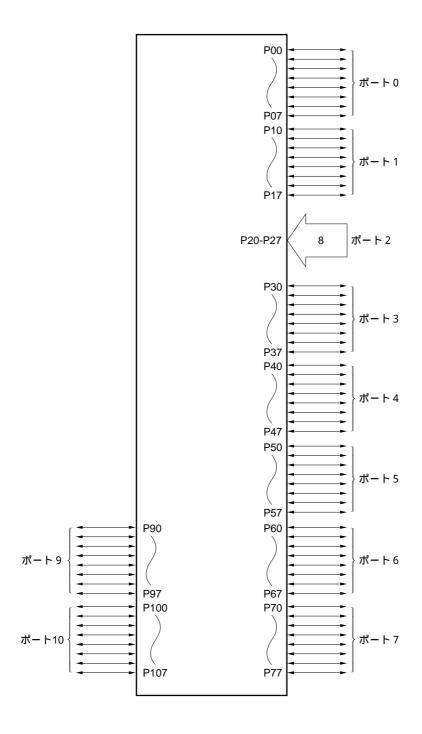

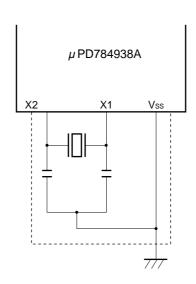

## 図8-3 発振回路の使用例

## クリスタル/セラミック発振

- 注意 クロック発振回路を使用する場合は,配線容量などの影響を避けるために,破線の部分を次のように配線してください。

- ・配線を極力短くする。

- ・ほかの信号線と交差させない。

- ・変化する大電流が流れる線と接近させない。

- ・発振回路のコンデンサの接地点は,常にVssと同電位となるようにする。大電流が流れるグランド・ パターンには接地しない。

- ・発振回路から信号を取り出さない。

サブシステム発振回路は,低消費電流にするために増幅度の低い回路になっており,ノイズに対する誤動作がメイン・システム・クロック発振回路よりも起こりやすくなっています。したがって,サブシステム・クロック回路を使用する場合は,配線方法について特に注意してください。

発振が正常に安定して行われないと、マイコンも正常に安定した動作を行うことができません。また、高精度な 発振周波数を得たい場合などは、発振器メーカと相談してください。

図8-4 発振子の接続の注意点

注意1. 発振回路は, X1, X2 (XT1, XT2) 端子にできるだけ近づけてください。

2. 破線の範囲に他の信号線を通さないでください。

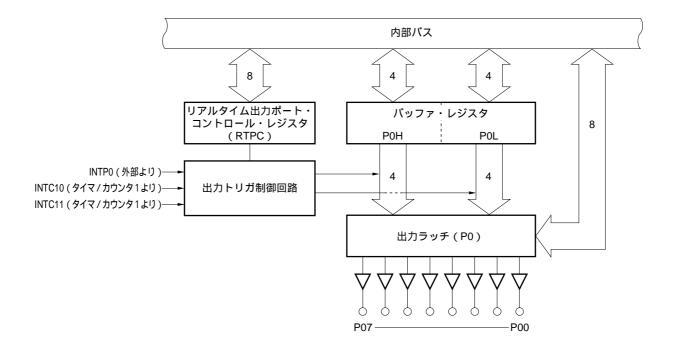

## 8.3 リアルタイム出力ポート

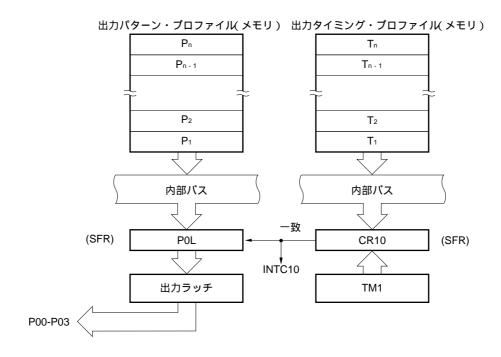

リアルタイム出力ポートは,バッファに格納しておいたデータを,タイマ/カウンタ1の一致割り込みや外部割り込みに同期して出力します。これによって,ジッタのないパルス出力を得られます。

したがって,任意の間隔で任意パターンを出力する応用(ステッピング・モータの開ループ制御など)に最適です。

図8 - 5のように,ポート0とポート0バッファ・レジスタ (POH, POL)が構成の中心です。

図8-5 リアルタイム出力ポートのブロック図

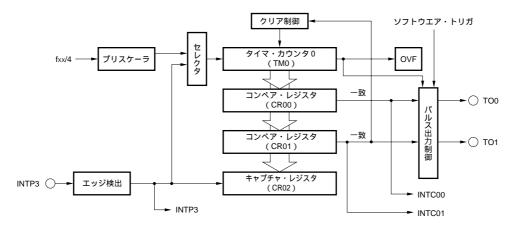

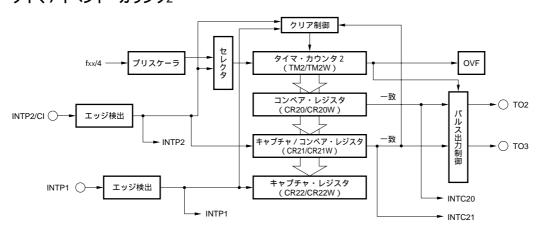

#### 8.4 タイマ/カウンタ

トグル出力 PWM/PPG出力

リアルタイム出力 パルス幅測定

割り込み要求数

ワンショット・パルス出力<sup>注</sup>

タイマ/イベント・カウンタを3ユニット,タイマを1ユニット内蔵しています。

また,計7つの割り込み要求をサポートしていますので,7ユニットのタイマ/カウンタとして機能させることができます。

名 称 タイマ / イベント・ タイマ / イベント・ タイマ / イベント・ タイマ3 項目 カウンタ0 カウンタ1 カウンタ2 カウント幅 8ビット 16ビット 動作モード インターバル・タイマ 2ch 2ch 2ch 1ch 外部イベント・カウンタ ワンショット・タイマ 機能 タイマ出力 2ch 2ch

表8-2 タイマ/カウンタの動作

1入力

1入力

2入力

1

この機能は、タイマ/イベント・カウンタ2のワンショット・タイマ機能とは性質が異なります。

**注** ワンショット・パルス出力機能とは,ソフトウエアによりパルス出力レベルをアクティブにし,ハードウエア(割り込み要求信号)によりインアクティブにする機能です。

## 図8-6 タイマ/カウンタのブロック図

## タイマ/イベント・カウンタ0

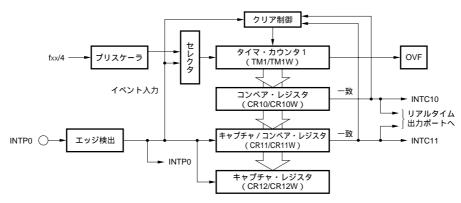

## タイマ/イベント・カウンタ1

# タイマ/イベント・カウンタ2

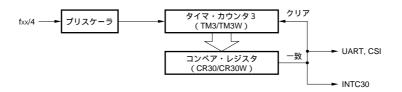

#### **タイマ**3

備考 OVF:オーバフロー・フラグ

#### 8.5 時計用タイマ

時計用タイマに入力するカウント・クロックは,メイン・クロック(12.58 MHz)と時計クロック(32.768 kHz)の2種類があり,制御レジスタにより選択できます。時計クロックは,時計用タイマのみに入力するクロックで,CPUや他の周辺回路には入力しません。したがって,時計クロックによりCPUを低速動作させることはできません。

時計用タイマはカウント・クロックを分周して,0.5秒間隔<sup>注</sup>の割り込み信号(INTW)を発生します。同時に割り込み要求フラグ(WIF)もセットします(ここでのWIFは,割り込み制御レジスタ(WIC)のビット7です)。

また,モード切り替えにより,INTW発生間隔を約1 msに変更できます(早送りモード:通常動作の512倍速)。カウント・クロックにメイン・クロックを選択している場合は,STOPモードとIDLEモードのスタンバイ時には,動作を停止します。ただし,HALTモード時は動作を継続します。また,カウント・クロックに時計クロックを選択した場合は,どのスタンバイ・モード時でも動作を継続できます。時計クロック発振器の動作制御は,時計用タ

μ PD784938Aの時計用タイマには,ブザー出力機能は内蔵しません。

注 動作許可後,はじめのINTWまでは0.5 sではありません。

イマ・モード・レジスタ (WM) で行います。

| カウント・クロックの選択 | 通常動作モード | スタンバイ・モードの種類 |         |         |  |  |  |  |

|--------------|---------|--------------|---------|---------|--|--|--|--|

|              |         | HALTモード      | STOPE-F | IDLEモード |  |  |  |  |

| メイン・クロック     | 動作可能    | 動作可能         | 停止      | 停止      |  |  |  |  |

| 時計クロック       | 動作可能    | 動作可能         | 動作可能    | 動作可能    |  |  |  |  |

表8-3 カウント・クロックと時計用タイマ動作の関係

時計用タイマの構成は,カウント・クロックを3分周する分周回路と,分周回路の出力を2<sup>14</sup>分周するカウンタから構成されています。カウント・クロックは,内部システム・クロックを128分周した信号と,時計クロック発振器からの信号を選択して使用してください。

WM.3 -リセット -3 4 5 6 10 11 12 13 メイン・クロック 3分周 fxx/128 カウンタ カウンタ 0 - INTW SFL SEI 時計クロック 発振器 WM.2 ON/OFF WM.7 WM.6 STBC.7 (メイン・クロック12.58 MHz 時に命令でセットする)

図8-7 時計用タイマのプロック図

#### 8.6 PWM出力 (PWM0, PWM1)

12ビット分解能で、PWM (パルス幅変調)出力回路を2チャネル内蔵しています。このPWM出力は両チャネルとも独立にアクティブ・レベルをハイかロウに選択できます。この出力はDCモータの速度制御用として最適です。

内部バス 16 ∫ 8 [ (モジュロ・<u>レジスタ</u>) PWMコントロール・レジスタ 15 8 7 4 3 PWMn (PWMC) 4 8 リロード制御 8ビット・ 出力 プリスケーラ パルス制御回路 —○ PWMn ( 出力端子 ) 制御 ダウン・カウンタ 4ビット・カウンタ 1/256

図8-8 PWM出力ユニットのプロック図

**備考** n = 0, 1

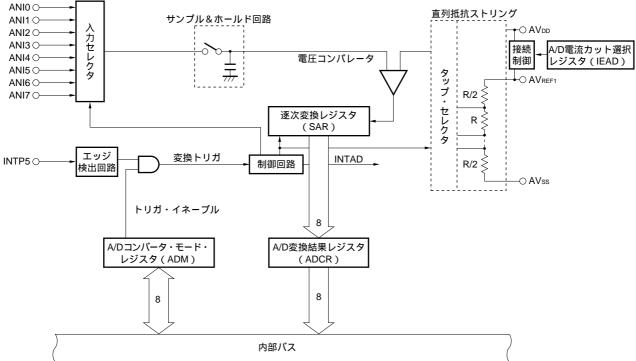

## 8.7 A/Dコンパータ

8マルチプレクスト・アナログ入力(ANIO-ANI7)を持つアナログ / ディジタル(A/D)コンバータを内蔵しています。

変換方式は逐次比較で,変換結果を8ビットのA/D変換結果レジスタ(ADCR)に保持します。このため,高速で高精度に変換します。

A/D変換動作の起動には,次のモードがあります。

- ・ハードウエア・スタート:トリガ入力 (INTP5) により変換開始

- ・ソフトウエア・スタート: A/Dコンバータ・モード・レジスタ (ADM)のビット設定により変換開始。

また,起動後の動作には,次のモードがあります。

- ・スキャン・モード:複数のアナログ入力を順次選択し,複数端子の変換を行います。

- ・セレクト・モード:アナログ入力を1端子に固定し,連続的な変換値を得ます。

以上のモードと変換動作の停止は,すべてADMで指定します。

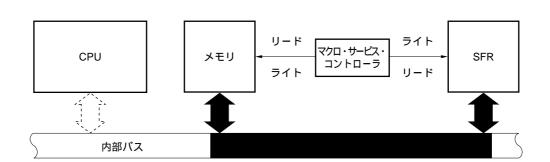

なお、変換結果をADCRへ転送すると、割り込み要求INTADを発生します。これを利用して、マクロ・サービスによって、変換値をメモリへ連続的に転送できます。

注意1. 本製品では,基準電圧入力端子(AVREF1)には,電源電圧(AVDD)と同じ電圧を印加して使用してください。

図8-9 A/Dコンパータのブロック図

2. ポート7を出力ポートとA/D入力を混在して使用している場合には,A/D変換動作中は,出力ポートの操作は行わないでください。

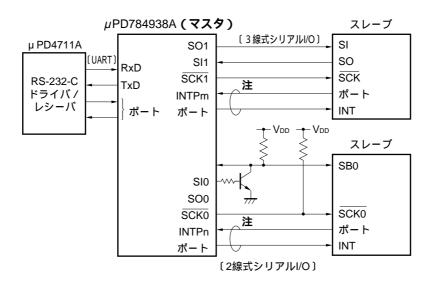

## 8.8 シリアル・インタフェース

独立した4チャネルのシリアル・インタフェースを備えています。

アシンクロナス・シリアル・インタフェース(UART) / 3線式シリアルI/O(IOE)  $\times$  2 クロック同期式シリアル・インタフェース(CSI)  $\times$  2 ・3線式シリアルI/O(IOE)

このため、システム外部との通信と、システム内部のローカルな通信とを同時にできます(図8-10参照)。

図8-10 シリアル・インタフェース例

UART + 3線式シリアルI/O + 2線式シリアルI/O

注 ハンドシェーク・ライン

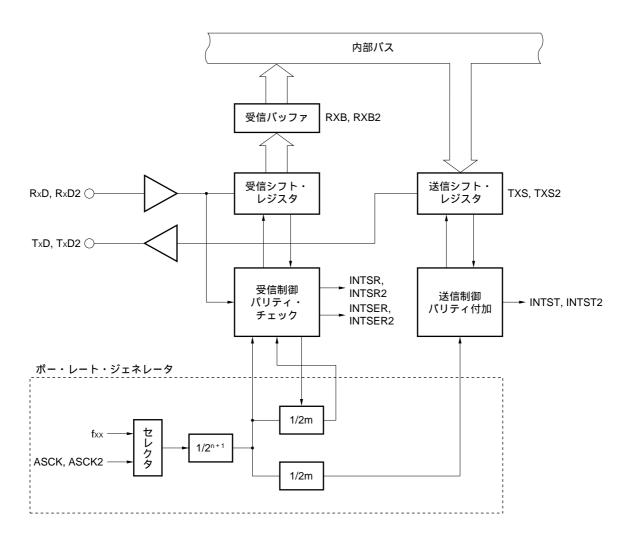

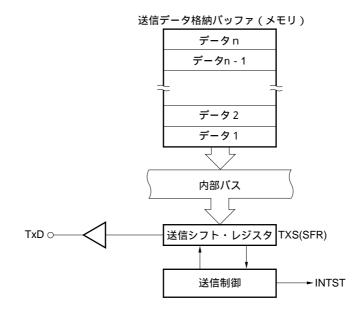

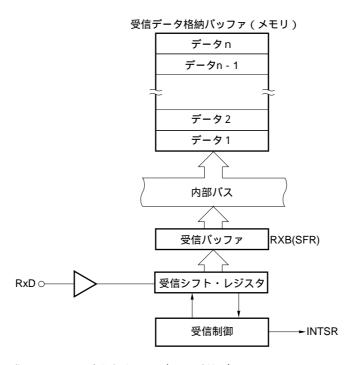

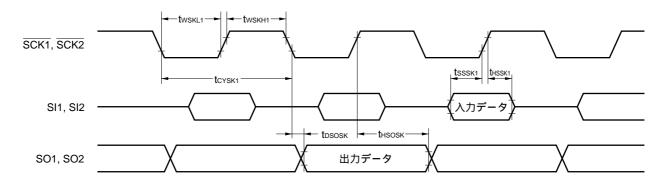

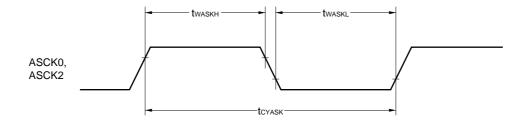

#### 8.8.1 アシンクロナス・シリアル・インタフェース/3線式シリアルI/O (UART/IOE)

アシンクロナス・シリアル・インタフェース・モードと3線式シリアルI/Oモードを選択できるシリアル・インタフェースを2チャネル持っています。

#### (1) アシンクロナス・シリアル・インタフェース・モード

スタート・ビットに続く1バイトのデータを送受信する方式です。

ボー・レート・ジェネレータを内蔵しており、広範囲な任意のボー・レートで通信できます。

また, ASCK端子への入力クロックを分周することで, ボー・レートの定義ができます。

ボー・レート・ジェネレータを使用すると, MIDI規格のボー・レート(31.25 kbps)も得られます。

図8-11 アシンクロナス・シリアル・インタフェース・モード時のプロック図

## ★ **備考** fxx:発振周波数

n = 0-11

m = 16-30

## (2)3線式シリアルI/Oモード

マスタ・デバイスがシリアル・クロックをアクティブにして送信を開始し、このクロックに同期して1バイトのデータを通信する方法です。

従来のクロック同期式シリアル・インタフェースを内蔵するデバイスと通信するためのインタフェースです。 基本的には、シリアル・クロック(SCK)とシリアル・データ(SI,SO)の3線で通信します。

また,一般的には通信状態を確認するため,ハンドシェーク・ラインが必要となります。

図8 - 12 3線式シリアルI/Oモード時のブロック図

### ★ **備考** fxx:発振周波数

n = 0-11

m = 1, 16-30

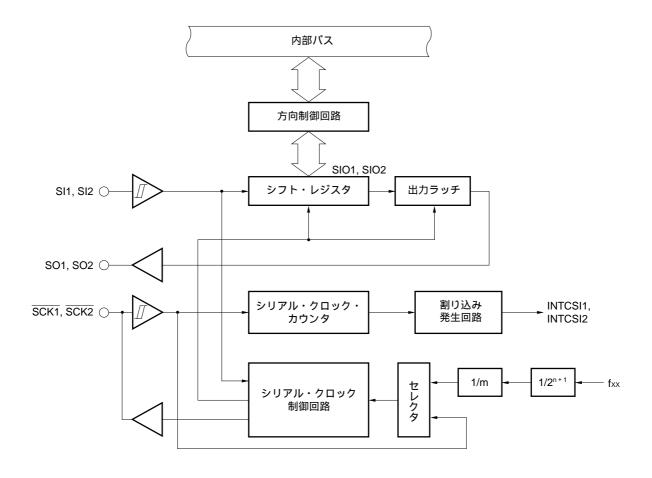

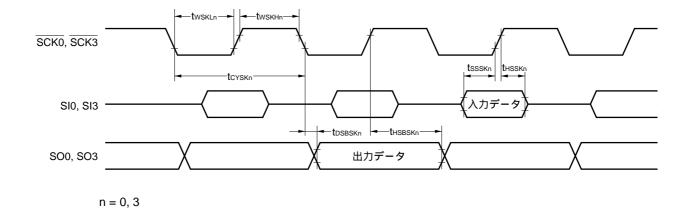

## 8.8.2 クロック同期式シリアル・インタフェース (CSI)

マスタ・デバイスがシリアル・クロックをアクティブにして送信を開始し、このクロックに同期して1バイトのデータを通信する方法です。

内部パス

SIn

SIn

SIOn レジスタ

CSIMn レジスタ

INTCSIn

fxx/8

t fxx/16

fxx/32

fxx/64

fxx/128

図8-13 クロック同期式シリアル・インタフェースのプロック図

★ 備考 fxx:発振周波数

n = 0, 3

## ・3線式シリアルI/Oモード

従来のクロック同期式シリアル・インタフェースを内蔵するデバイスと通信するためのインタフェースです。 基本的には , シリアル・クロック ( $\overline{SCKn}$ ) とシリアル・データ (SCKn) の3線で通信します (N=0,3)。また , 一般的には通信状態を確認するため , ハンドシェーク・ラインが必要となります。

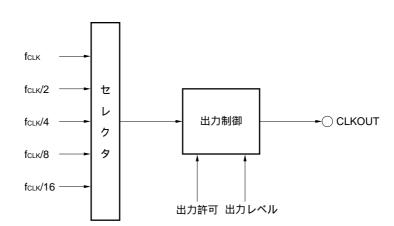

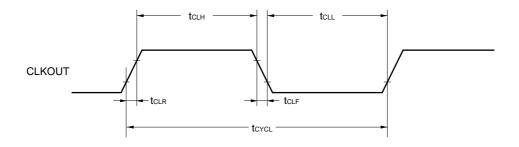

#### 8.9 クロック出力機能

CPUの動作クロックを分周して外部に出力できます。また、1ビットのポートとしても使用できます。

本機能使用時には,ASTB端子とCLKOUT端子が兼用になっているため,ローカル・バス・インタフェースは使用できません。

図8 - 14 クロック出力機能のブロック図

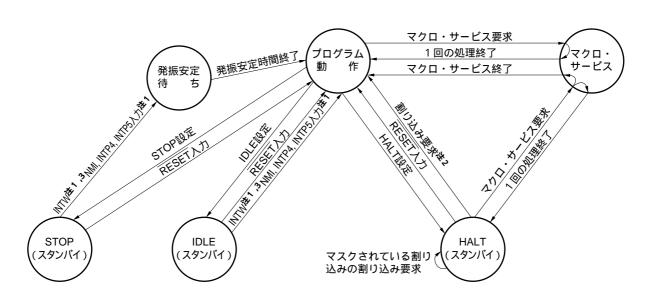

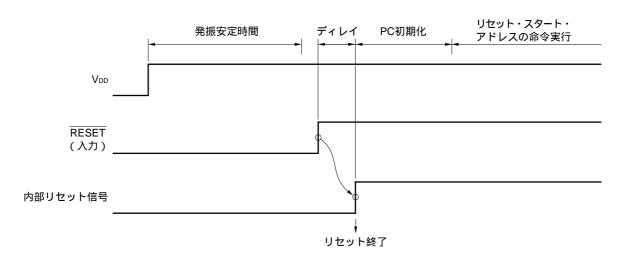

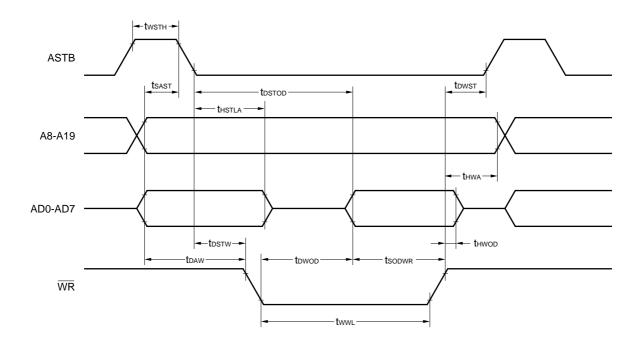

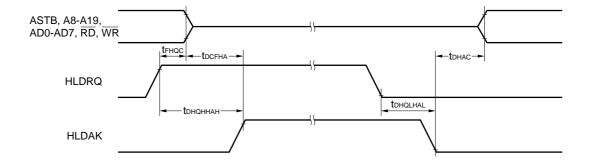

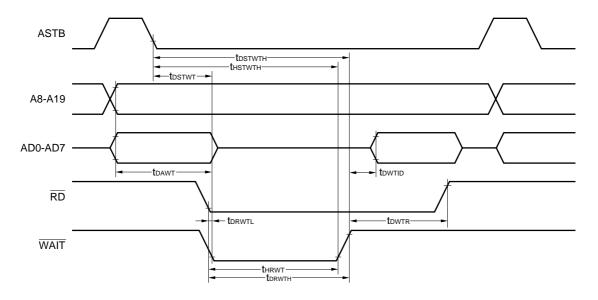

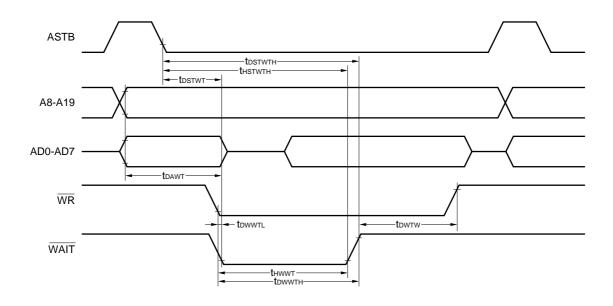

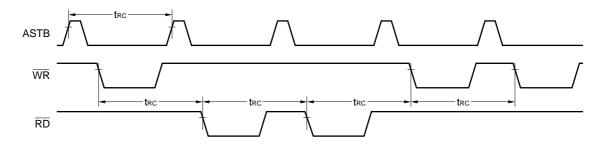

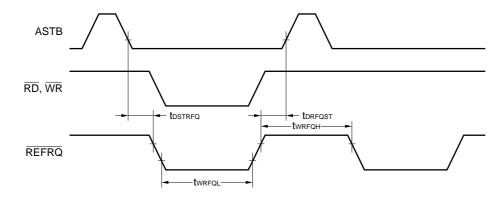

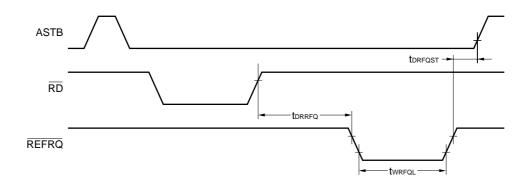

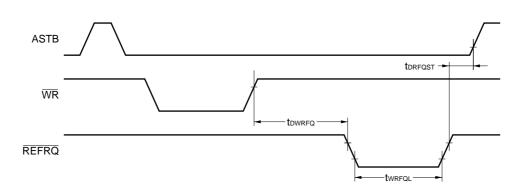

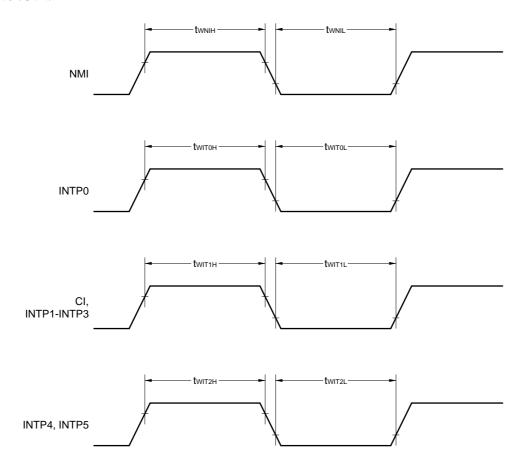

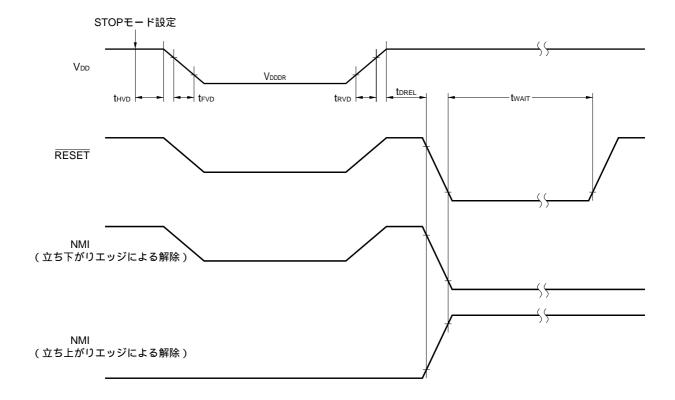

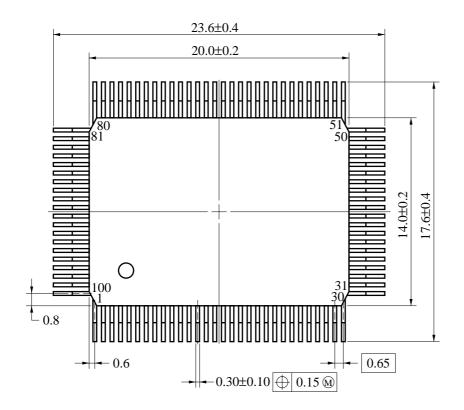

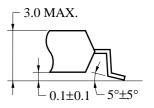

#### 8.10 エッジ検出機能