# **Contents**

| 1 The ZIOL2xxx IC Family Overview                                     | 5  |

|-----------------------------------------------------------------------|----|

| 2 Electrical Characteristics                                          | 6  |

| 2.1. Absolute Maximum Ratings                                         | 6  |

| 2.2. Operating Conditions                                             | 7  |

| 2.3. Electrical Parameters                                            | 8  |

| 3 Detailed Description                                                | 13 |

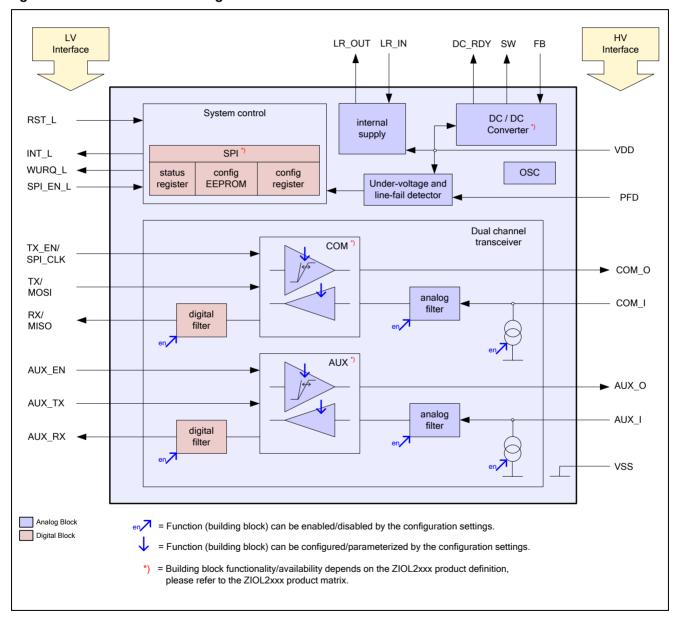

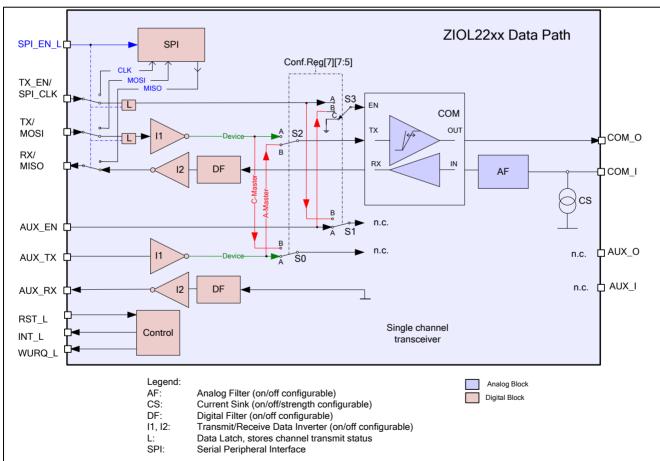

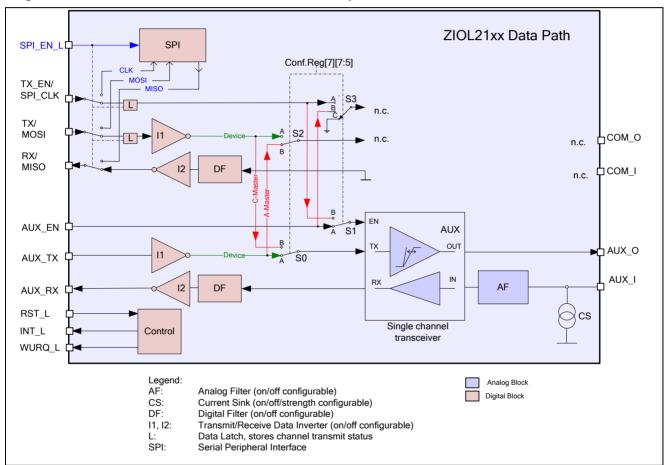

| 3.1. Block schematic                                                  | 13 |

| 3.2. Dual Channel Transceiver                                         | 14 |

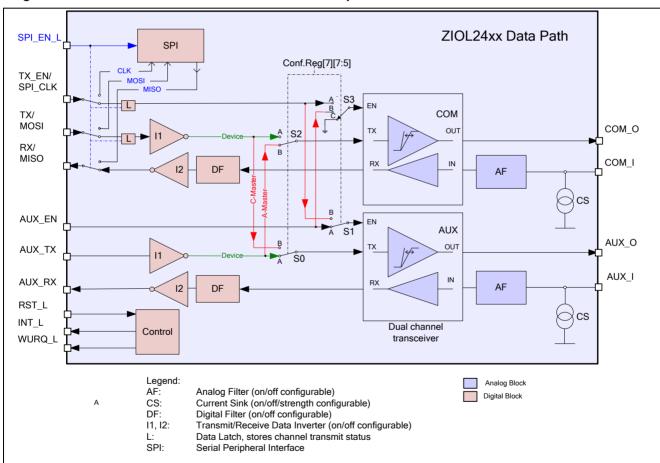

| 3.2.1. IC Data Path Configuration                                     | 14 |

| 3.2.2. Transmitter                                                    | 18 |

| 3.2.3. Receiver                                                       | 20 |

| 3.3. System Control                                                   | 22 |

| 3.3.1. General                                                        | 22 |

| 3.3.2. IO-Link Master and Device Mode                                 | 23 |

| 3.3.3. Internal Exceptions                                            | 23 |

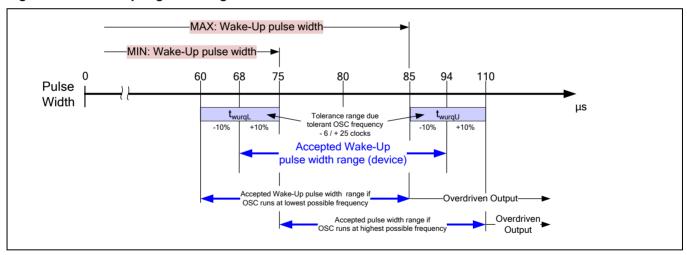

| 3.3.4. IO-Link specific Wake-Up (WURQ)                                | 23 |

| 3.3.5. IC Self-Protection – Lock Mode                                 | 25 |

| 3.3.6. Channel Locking in Master/Device Mode                          | 27 |

| 3.3.7. Memory Unit                                                    | 27 |

| 3.3.8. Serial Peripheral Interface (SPI)                              | 29 |

| 3.3.9. Register Table / Registers for IC Configuration and Monitoring | 34 |

| 3.3.10.Interrupt and IC Lock Mode Control                             | 44 |

| 3.3.11.Die Temperature Measurement                                    | 51 |

| 3.4. Smart Power Supply                                               | 51 |

| 3.5. The Power Fail Detector                                          |    |

| 3.5.1. Overview                                                       | 53 |

| 3.5.2. Line-Fault Detector                                            | 53 |

| 3.5.3. Under-voltage Detector                                         | 54 |

| 3.5.4. Channel Locking and Interrupt Generation                       | 54 |

| 3.5.5. Downward Compatibility                                         | 54 |

| 3.6. DC/DC Converter                                                  | 54 |

| 3.6.1. Principle of Operation                                         | 54 |

| 3.6.2. Principle of Operation                                         | 55 |

| 3.6.3. Dimensioning of external Devices                               | 56 |

| 3.6.4. PCB Layout considerations                        | 58 |

|---------------------------------------------------------|----|

| 4 Application Information                               | 60 |

| 5 Pin Configuration, Latch-Up and ESD Protection        | 65 |

| 5.1. Pin Configuration and Latch-up Conditions          | 65 |

| 5.2. ESD-Protection                                     | 66 |

| 6 Package                                               | 67 |

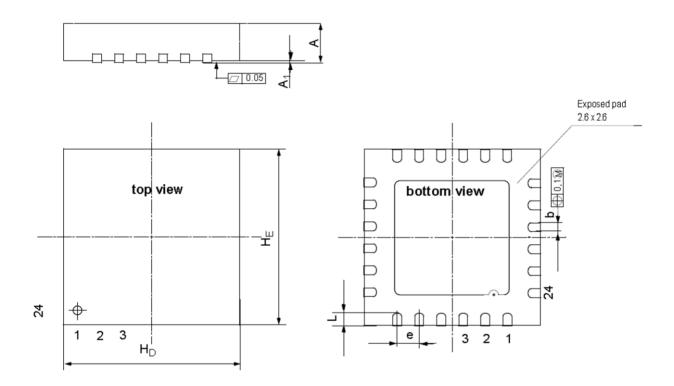

| 6.1. Package Details QFN24 4x4mm                        | 67 |

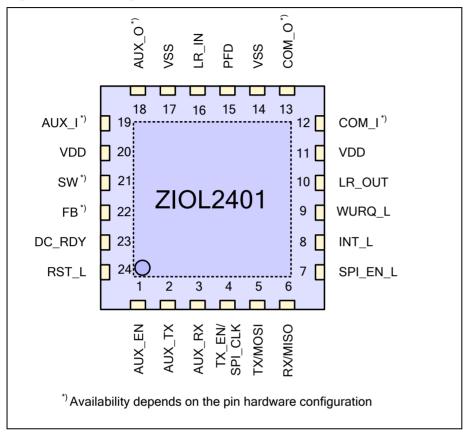

| 6.1.1. Pin Hardware Configurations                      | 67 |

| 6.1.2. Pin Diagram                                      | 67 |

| 6.1.3. Optimal PCB Layout                               |    |

| 6.1.4. Package Outline                                  |    |

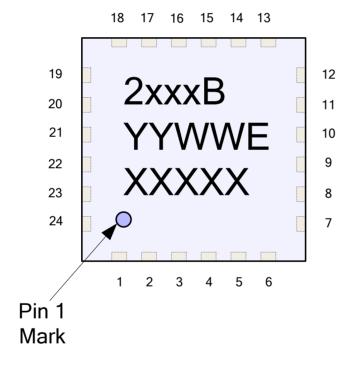

| 6.1.5. Device Marking                                   |    |

| 6.2. Package Details WL-CSP                             |    |

| 6.2.1. Pin Hardware Configurations                      |    |

| 6.2.2. Pin Diagram                                      |    |

| 6.2.3. Optimal PCB Layout                               |    |

| 6.2.4. Package Outline                                  |    |

| 6.2.5. Device Marking                                   |    |

| 7 Ordering Information                                  |    |

| 8 Related Documents                                     |    |

| 9 Glossary                                              |    |

| 9.1. Terms and Abbreviations                            |    |

| 9.2. Symbols used in this Datasheet                     |    |

| 10 Document Revision History                            |    |

| Appendix A ZIOL2xxx Diagnostic Techniques               |    |

| A.1. General Remarks                                    |    |

| A.2. Overload Counter Behavior and Peak Register Access |    |

| A.3. Overload Counter and Lock Reset Methods            |    |

| Appendix B ZIOL2xxx Configuration Techniques            |    |

| Appendix C ZIOL2xxx Line Fail Detector                  | 90 |

# **List of Figures**

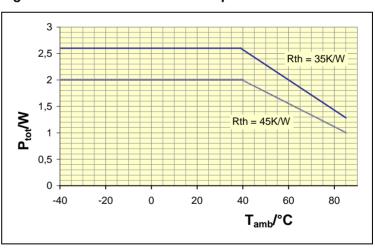

| Figure 2.1  | Max. Total Power Dissipation                                                     | 6  |

|-------------|----------------------------------------------------------------------------------|----|

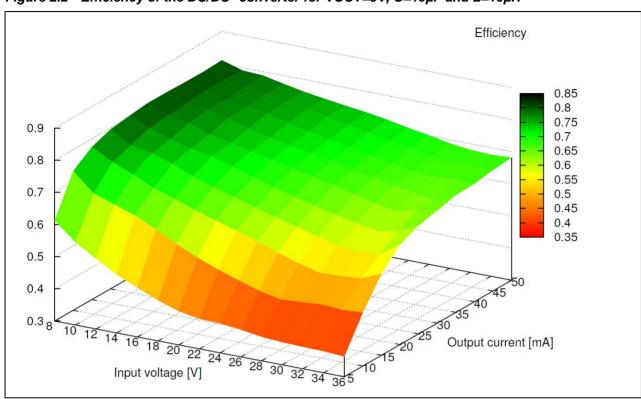

| Figure 2.2  | Efficiency of the DC/DC converter for VOUT=5V, C=10µF and L=10µH                 | 12 |

| Figure 3.1  | Functional Block Diagram of the ZIOL2xxx                                         | 13 |

| Figure 3.2  | ZIOL24xx Transceiver Data Path in Principle                                      | 14 |

| Figure 3.3  | ZIOL22xx Transceiver Data Path in Principle                                      | 15 |

| Figure 3.4  | ZIOL21xx Transceiver Data Path in Principle                                      | 16 |

| Figure 3.5  | ZIOL24xx in Device and Master Mode Application                                   | 19 |

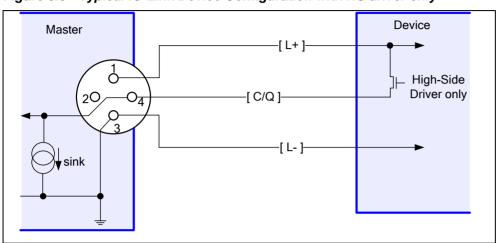

| Figure 3.6  | Typical IO-Link Device Configuration with HS driver only                         | 22 |

| Figure 3.7  | Wake-Up Signal Recognition                                                       | 24 |

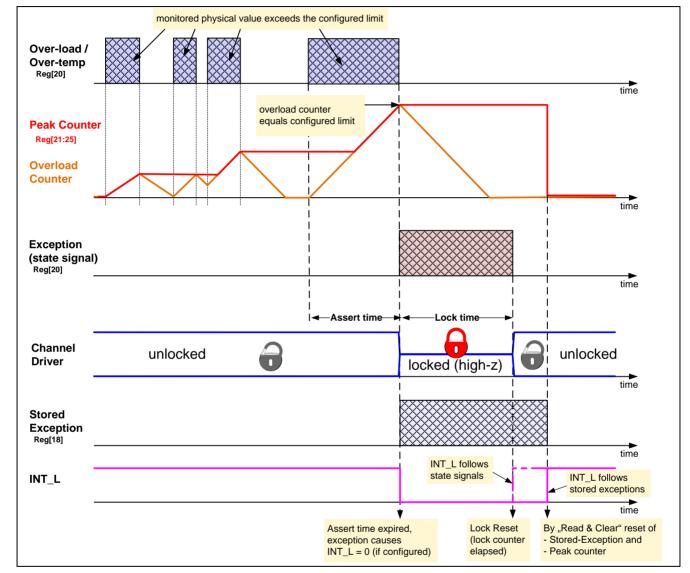

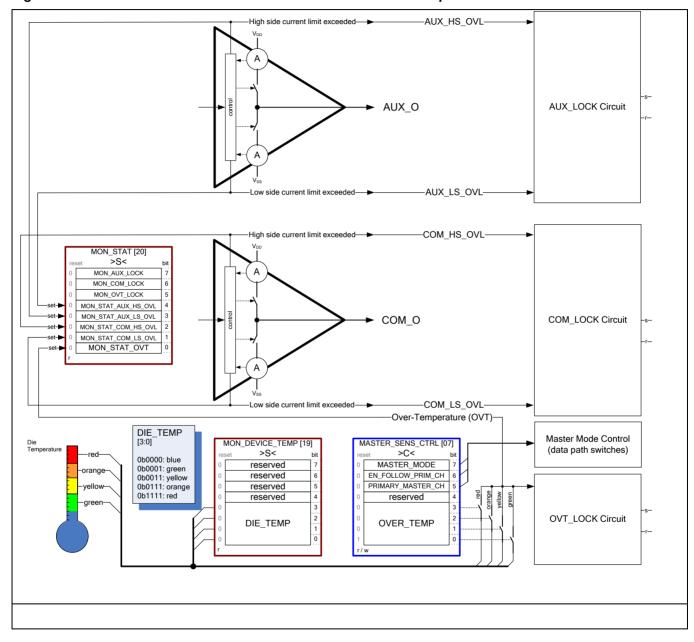

| Figure 3.8  | The Basic Scheme of the IC Self Protection                                       | 26 |

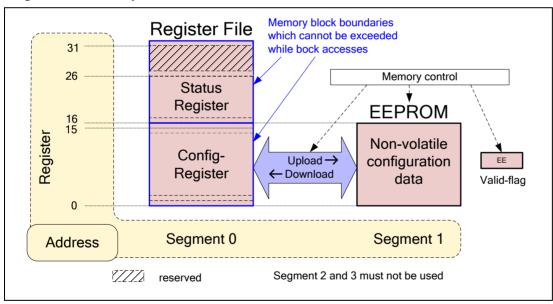

| Figure 3.9  | Memory Unit                                                                      | 28 |

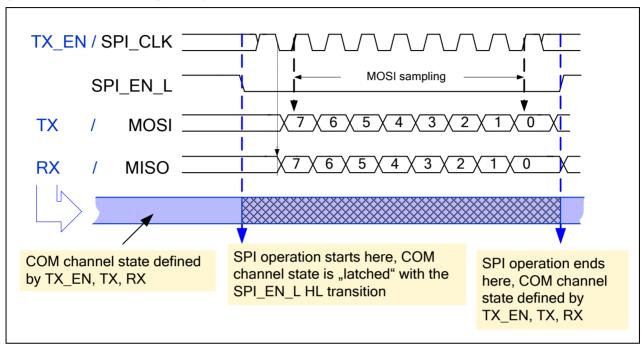

| Figure 3.10 | General timing of a byte transfer                                                | 30 |

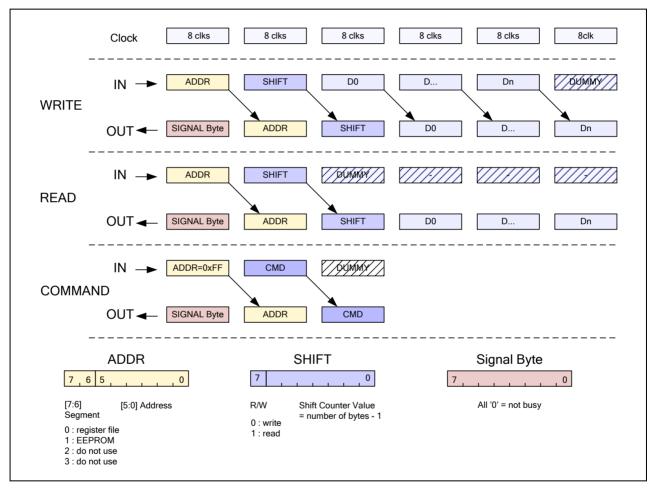

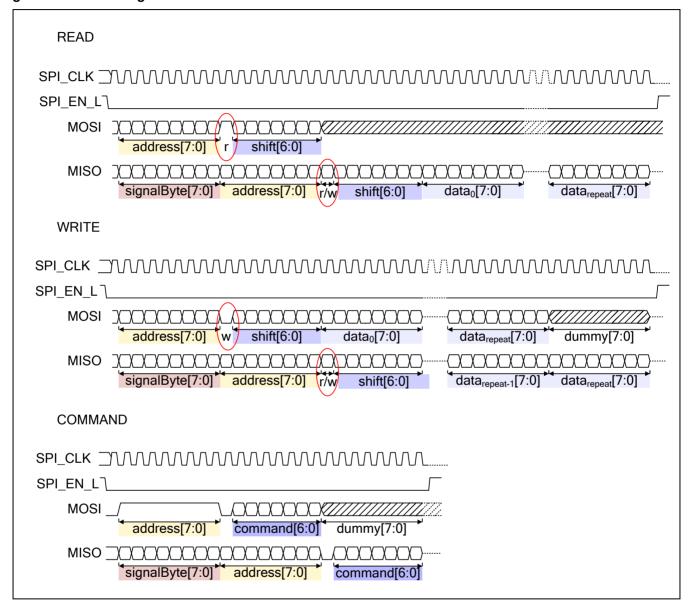

| Figure 3.11 | Structure of SPI accesses                                                        | 31 |

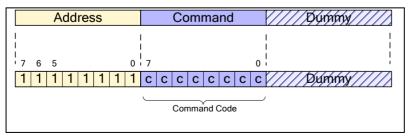

| Figure 3.12 | SPI Command Structure                                                            | 32 |

| Figure 3.13 | SPI Timing                                                                       | 34 |

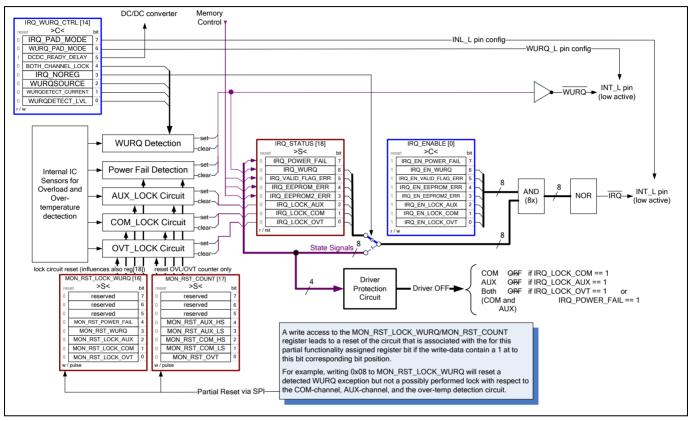

| Figure 3.14 | Interrupt (INT_L pin) and Wake-up (WURQ_L pin) Signaling                         | 45 |

| Figure 3.15 | COM Channel Lock Control                                                         | 46 |

|             | AUX Channel Lock Control                                                         |    |

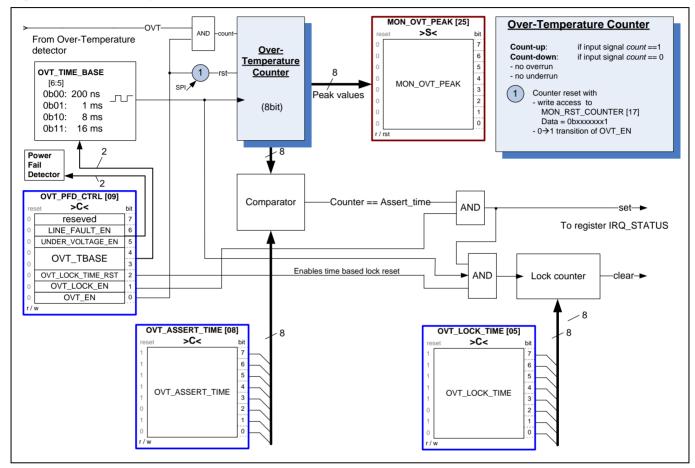

| Figure 3.17 | Over-Temperature Lock Control                                                    | 48 |

| Figure 3.18 | Internal IC Sensors and related Overload and Over-Temperature Detection Circuits | 50 |

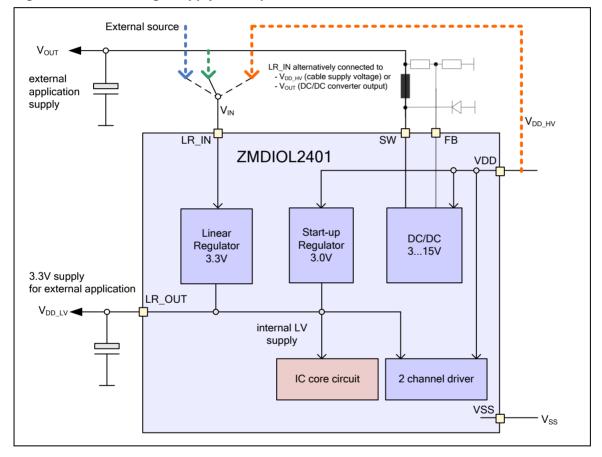

| Figure 3.19 | Low Voltage Supply Concept                                                       | 52 |

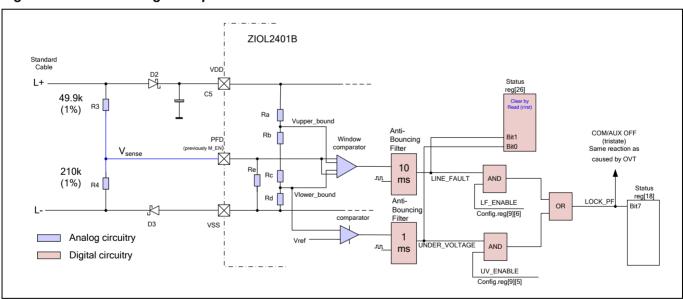

| Figure 3.20 | PFD Working Principle                                                            | 53 |

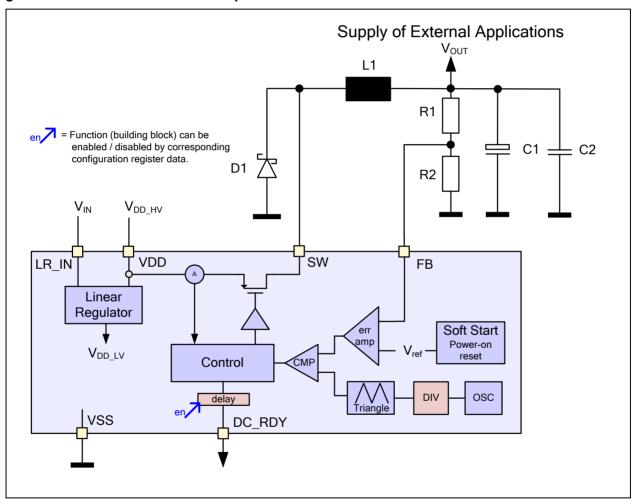

| Figure 3.21 | DC/DC Converter in Principle                                                     | 55 |

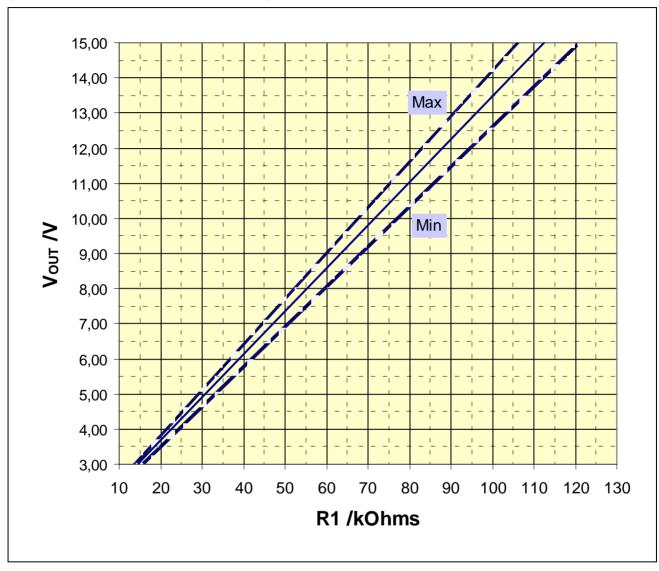

| Figure 3.22 | DC/DC Converter Output Voltage as Function of R1 (R2 = 10kOhms)                  | 57 |

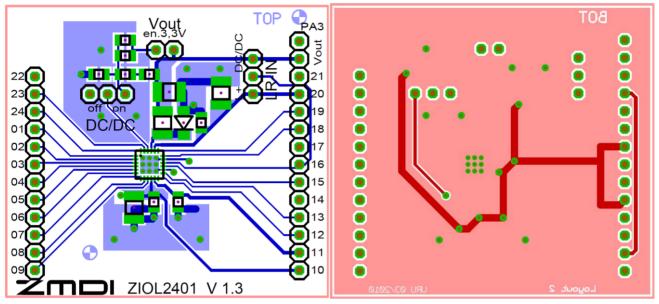

| Figure 3.23 | High frequency critical loops of DC/DC converter for PCB layout                  | 58 |

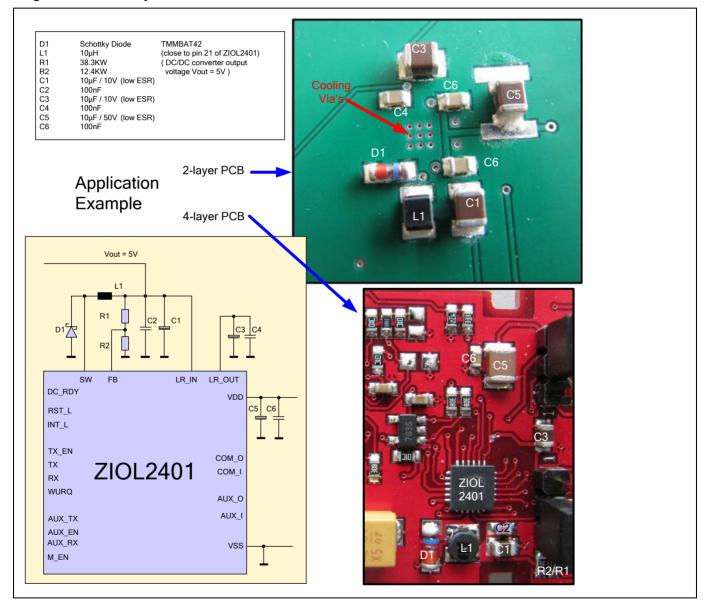

| Figure 3.24 | PCB layout of Evaluation board as an example                                     | 59 |

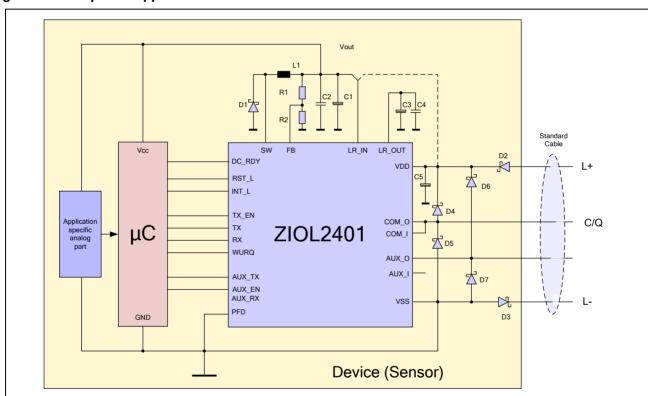

| Figure 4.1  | Simplified Application Circuit with the ZIOL2xxx in Device Mode                  | 60 |

| Figure 4.2  | Simplified Application Circuit with the ZIOL2xxx in Master Mode                  | 61 |

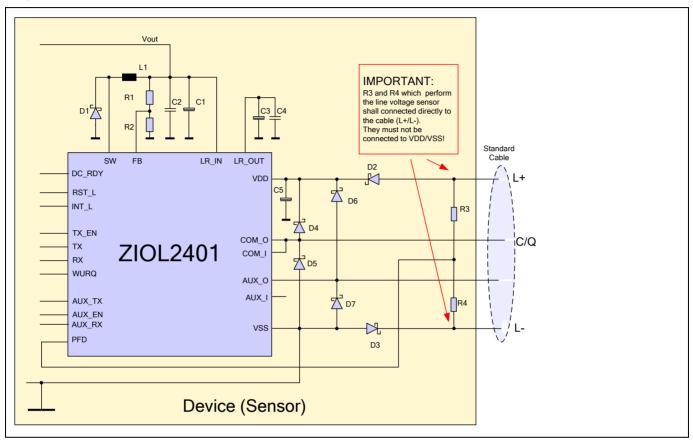

| Figure 4.3  | Power Line Fail Detection                                                        | 62 |

| Figure 4.4  | PCB Layout Recommendations                                                       | 63 |

| Figure 6.1  | Pin Diagram of the ZIOL2xxx                                                      | 68 |

| Figure 6.2  | Package Dimensions                                                               | 69 |

| Figure 6.3  | Top Marking of the ZIOL2xxx                                                      | 70 |

| Figure 6.4  | Package Dimensions                                                               | 72 |

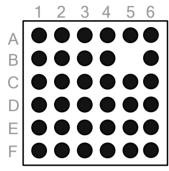

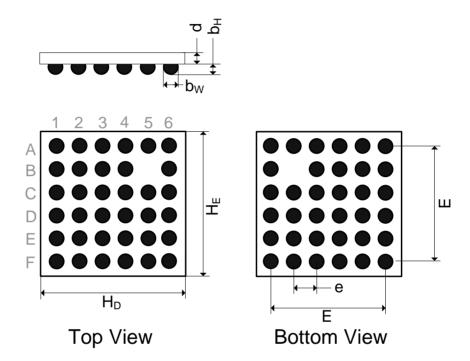

| Figure 6.5  | Package Dimensions WL-CSP                                                        | 73 |

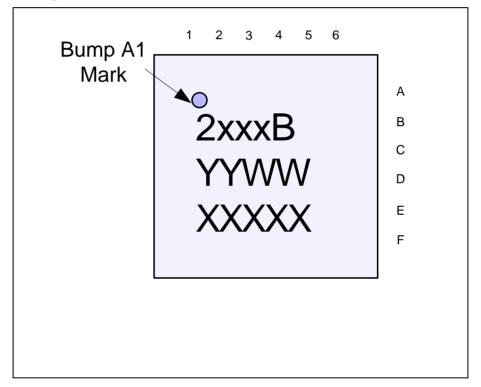

| Figure 6.6  | Top Marking of the ZIOL2xxx CSP                                                  |    |

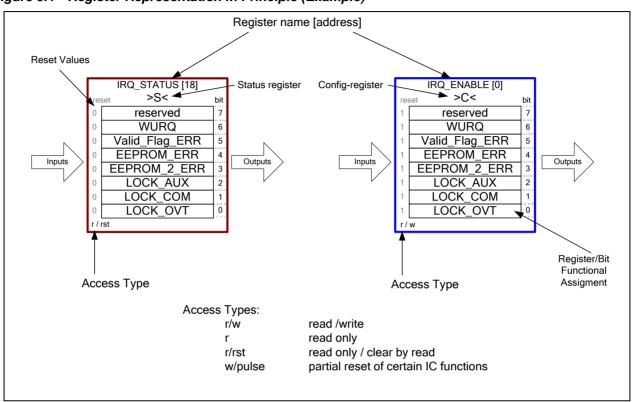

| Figure 9.1  | Register Representation in Principle (Example)                                   | 78 |

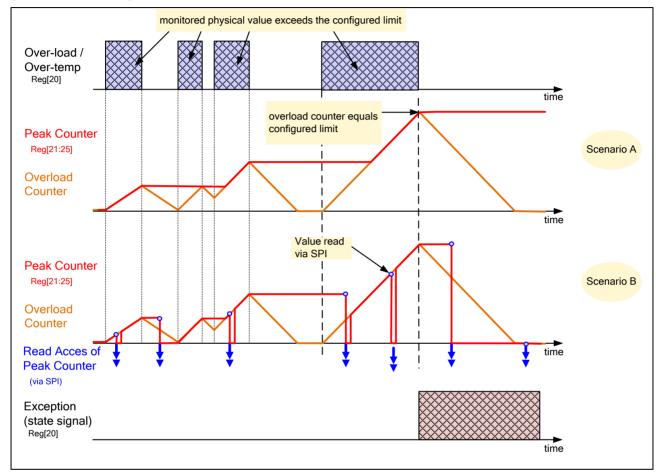

| Figure 10.1 | Peak Register Access Scenarios                                                   |    |

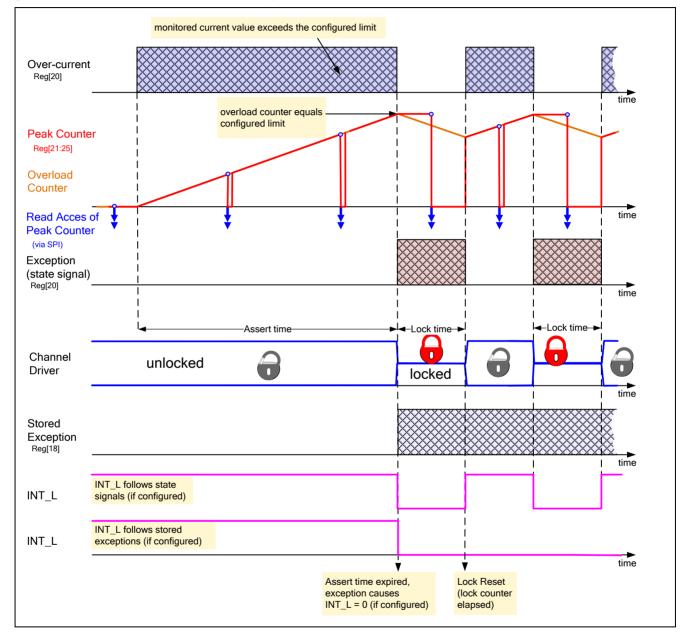

| Figure 10.2 | Overload Counter Behavior in permanent Over-Current Situations                   | 83 |

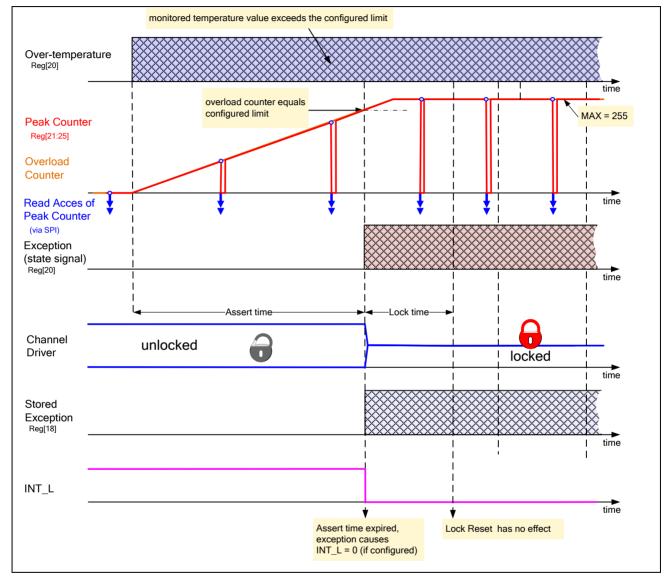

| Figure 10.3 | Overload Counter Behavior in permanent Over-Temperature Situations     | 84 |

|-------------|------------------------------------------------------------------------|----|

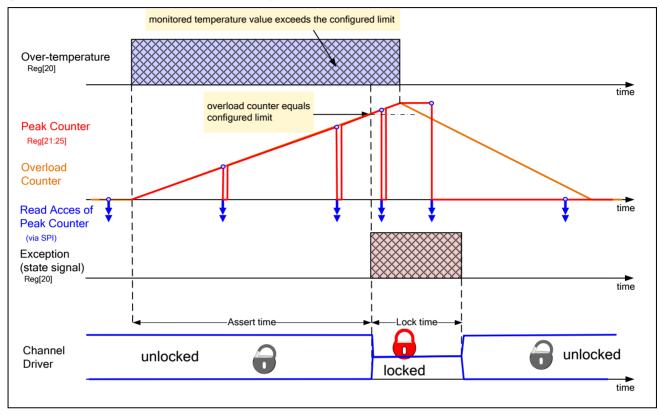

| Figure 10.4 | Overload Counter Behavior in typical Over-Temperature Situations       | 85 |

| Figure 10.5 | Partial Reset of Overload Counter or the entire Lock circuit           | 86 |

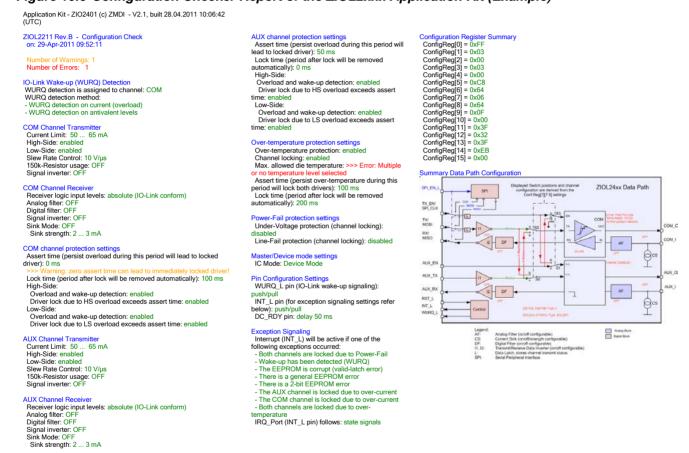

| Figure 10.6 | Configuration Checker Report of the ZIOL2xxx Application Kit (Example) | 88 |

|             |                                                                        |    |

|             |                                                                        |    |

| List of     | Tables                                                                 |    |

| Table 1.1   | ZIOL2xxx Product Matrix and Product Naming Convention                  | 5  |

| Table 2.1   | Absolute Maximum Ratings                                               |    |

| Table 2.2   | Operating Conditions                                                   | 7  |

| Table 2.3   | Electrical Characteristics                                             | 8  |

| Table 3.1   | Master-Device-Mode Function Table                                      | 17 |

| Table 3.2   | Driver configurations                                                  | 20 |

| Table 3.3   | Receiver configurations                                                | 21 |

| Table 3.4   | Sink Mode Configuration in Detail                                      | 22 |

| Table 3.5   | Example for building the SHIFT Byte                                    | 32 |

| Table 3.6   | Valid Address and Length Combinations                                  | 32 |

| Table 3.7   | Register Table                                                         | 35 |

| Table 3.8   | Temperature Sensor Levels                                              | 51 |

| Table 3.9   | Examples for the resistors R1 and R2 using E96 resistor series         | 56 |

| Table 4.1   | Recommended External Components                                        | 64 |

| Table 5.1   | Pin Configuration and Latch-Up Conditions                              | 65 |

| Table 6.1   | Availability of Pin Interconnections                                   | 67 |

| Table 6.2   | Package Dimensions in mm                                               | 69 |

| Table 6.3   | Availability of Pin Interconnections                                   | 71 |

| Table 6.4   | Bump Pin Configuration                                                 | 72 |

| Table 6.5   | Package Dimensions in mm                                               | 73 |

| Table 10.1  | Abnormal Power Supply Situations                                       | 90 |

# 1 The ZIOL2xxx IC Family Overview

IDT provides a universal and IO-Link compatible cable driver IC by issuing the ZIOL2401 integrated circuit. The ZIOL2401 is highly configurable and suitable for a wide range of applications in process and factory automation. In order to fulfill the requirements of specific applications stripped down versions of the IC were required. The ZIOL2xxx IC family is derived from the ZIOL2401 by modification (elimination or disabling) of certain functional building blocks. In this combination the following building blocks or functions are affected:

- The transceiver channels COM and AUX

- The availability of the integrated DC/DC converter

- · The activation of a read-only data access via the SPI interface

This datasheet describes the entire IC family ZIOL2xxx. Respective notes or footnotes describe the availability the above mentioned building blocks or functionality with respect to certain IC family members. Table 1.1 shows an overview concerning the ZIOL2xxx IC family and the used naming convention.

Table 1.1 ZIOL2xxx Product Matrix and Product Naming Convention

| ZIOL2xxx<br>Member | Transceiver<br>Channel | DC/DC<br>Converter | SPI<br>Access | Remarks              |

|--------------------|------------------------|--------------------|---------------|----------------------|

| ZIOL2401           | COM + AUX              | yes                | r/w           | Base type - released |

| ZIOL2201           | COM                    | yes                | r/w           | released             |

| ZIOL2101           | AUX                    | yes                | r/w           | 1)                   |

| ZIOL2411           | COM + AUX              | no                 | r/w           | released             |

| ZIOL2211           | СОМ                    | no                 | r/w           | released             |

| ZIOL2111           | AUX                    | no                 | r/w           | 1)                   |

| ZIOL2402           | COM + AUX              | yes                | r             | 1)                   |

| ZIOL2202           | COM                    | yes                | r             | 1)                   |

| ZIOL2102           | AUX                    | yes                | r             | 1)                   |

| ZIOL2412           | COM + AUX              | no                 | r             | 1)                   |

| ZIOL2212           | СОМ                    | no                 | r             | 1)                   |

| ZIOL2112           | AUX                    | no                 | r             | 1)                   |

TIOL2XXX

SPI Access

1 = read/write

2 = read-only

DC/DC Converter

0 = available

1 = not available

Transceiver Channels

4 = Two Channels (COM and AUX)

2 = COM channel only

1 = AUX Channel only

1 = AUX Channel only

# 2 Electrical Characteristics

# 2.1. Absolute Maximum Ratings

Parameters apply in operation temperature range and without time limitations.

Table 2.1 Absolute Maximum Ratings

| Symbol             | Parameter                       | Min  | Max                     | Unit | Conditions                              |

|--------------------|---------------------------------|------|-------------------------|------|-----------------------------------------|

| V <sub>DD_HV</sub> | Supply voltage                  | -0.3 | 40                      | V    |                                         |

| V <sub>HV</sub>    | Voltage at HV pins              | -0.3 | V <sub>DD_HV</sub> +0.3 | V    |                                         |

| V <sub>LV</sub>    | Voltage at LV pins              | -0.3 | V <sub>DD_LV</sub> +0.3 | V    | 2)                                      |

| V <sub>imp</sub>   | Impulse voltage withstand       | 60   |                         | V    | according to IEC 60947-5-2              |

| V <sub>ESD</sub>   | Abs. ESD test voltage           |      | 2k                      | V    | according to HBM                        |

| Ts                 | Junction temperature            |      | 125                     | °C   | 1)                                      |

| Ta                 | Storage temperature             | -50  | 150                     | °C   |                                         |

| P <sub>tot</sub>   | Average total power dissipation |      | 2.6                     | W    | integration period < 10ms <sup>3)</sup> |

<sup>1)</sup> Average die-temperature.

Figure 2.1 Max. Total Power Dissipation

<sup>&</sup>lt;sup>2)</sup> Exceptions are the digital input pins (μC interface) which tolerate 5V logic signals (refer to Table 5.1).

The allowed total power dissipation depends on the in the PCB design achieved thermal resistance R<sub>th</sub> (package/ambient) and the ambient operation temperature as shown in Figure 2.1. In order to obtain optimal heat distribution (R<sub>th</sub> < 35K/W) certain PCB layout rules shall be applied. Those rules are described in the application note for the used QFN package (refer to chapter 8, [4]).

# 2.2. Operating Conditions

Table 2.2 Operating Conditions

| Symbol               | Parameter                                | Min  | Typ <sup>1)</sup> | Max | Unit     | Conditions                                                                                                                       |

|----------------------|------------------------------------------|------|-------------------|-----|----------|----------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD\_HV}$         | Supply voltage                           | 8.0  | 24                | 36  | V        |                                                                                                                                  |

| V <sub>in</sub>      | Linear regulator input voltage           | 4.75 |                   | 36  | >        | LR_IN can be connected to $V_{DD\_HV}$ or DC/DC output voltage.                                                                  |

| $V_{DD\_LV}$         | Linear regulator output voltage          | 3.0  | 3.3               | 3.6 | <b>V</b> | Voltage LR_OUT → GND pin                                                                                                         |

| l <sub>out</sub>     | Linear regulator output current          |      |                   | 10  | mA       | LR_OUT provides supply current for external applications. <sup>2)</sup>                                                          |

| t <sub>startup</sub> | Startup timing @ V <sub>DD_HV</sub> = 8V |      |                   | 5   | ms       | Time for system start up including loading of configuration registers from EEPROM                                                |

| T <sub>amb</sub>     | Operating ambient temperature            | -40  |                   | +85 | °C       |                                                                                                                                  |

| f <sub>osc</sub>     | Internal oscillator frequency            | 4.5  |                   | 5.5 | MHz      | Internal clock is not available externally. All digital circuit timing parameters of the IC are derived from the internal clock. |

<sup>1)</sup> The mentioned typical values of IC properties are provided for information only.

<sup>&</sup>lt;sup>2)</sup> While start-up (until the voltage at LR\_OUT has reached 1V) the output current may be limited to 5mA.

#### 2.3. **Electrical Parameters**

All parameter values are valid under operating conditions specified in chapter 2.2 if no other conditions are mentioned.

Table 2.3 **Electrical Characteristics**

| Symbol                     | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Min | Typ <sup>1)</sup> | Max                 | Unit | Conditions                                                         |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|---------------------|------|--------------------------------------------------------------------|

| Transmitter Ou             | tput Stages (COM¹/AUX²)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |                   |                     |      |                                                                    |

| I <sub>DAL_0</sub>         | Alarm level threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50  |                   | I <sub>Dout_0</sub> | mA   | Dual mode                                                          |

| I <sub>DAL_1</sub>         | corresponding to configurable output current limitation <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100 |                   | I <sub>Dout_1</sub> | mA   | The active setting is defined in                                   |

| I <sub>DAL_2</sub>         | Dual Driver Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 200 |                   | I <sub>Dout_2</sub> | mA   | the configuration registers                                        |

| I <sub>DAL_3</sub>         | <u>= 333. = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 = 1.11 =</u> | 250 |                   | I <sub>Dout_3</sub> | mA   |                                                                    |

| I <sub>MAL_0</sub>         | Alarm level threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100 |                   | I <sub>Mout_0</sub> | mA   | Tandem mode                                                        |

| I <sub>MAL_1</sub>         | corresponding to configurable output current limitation <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200 |                   | I <sub>Mout_1</sub> | mA   | The active setting is defined in                                   |

| I <sub>MAL_2</sub>         | Tandem Driver Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 400 |                   | I <sub>Mout_2</sub> | mA   | the configuration registers.                                       |

| I <sub>MAL_3</sub>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 500 |                   | I <sub>Mout_3</sub> | mA   |                                                                    |

| I <sub>Dout_0</sub>        | Configurable output current limit <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56  |                   | 95                  | mA   | Dual mode                                                          |

| I <sub>Dout_1</sub>        | <u>Dual Driver Mode</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 112 |                   | 180                 | mA   | The active setting is defined in                                   |

| I <sub>Dout_2</sub>        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 224 |                   | 330                 | mA   | the configuration registers.                                       |

| I <sub>Dout_3</sub>        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 280 |                   | 410                 | mA   |                                                                    |

| I <sub>Mout_0</sub>        | Configurable output current limit <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 112 |                   | 180                 | mA   | Tandem mode                                                        |

| I <sub>Mout_1</sub>        | Tandem Driver Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 224 |                   | 360                 | mA   | The active setting is defined in                                   |

| I <sub>Mout_2</sub>        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 448 |                   | 660                 | mA   | the configuration registers.                                       |

| I <sub>Mout_3</sub>        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 560 |                   | 820                 | mA   |                                                                    |

| SR <sub>38</sub>           | 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6   | 10                | 14 <sup>5)</sup>    | V/µs | referring to IO-Link Spec.:<br>38,4kBaud (COM2),                   |

| SR <sub>230</sub>          | Slew rate <sup>3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40  | 60                | 80 <sup>5)</sup>    | V/µs | referring to IO-Link Spec.:<br>230.4kBaud (COM3)                   |

| t <sub>TLHdelayCOM3</sub>  | OM3 Propagation delay L-H edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                   | 250                 | ns   | Time from LV L-H edge till HV edge begins to rise (COM3 baud rate) |

| t <sub>THLdelay</sub> COM3 | Propagation delay H-L edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                   | 250                 | ns   | Time from LV H-L edge till HV edge begins to fall (COM3 baud rate) |

| t <sub>TLHdelayCOM2</sub>  | Propagation delay L-H edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                   | 700                 | ns   | Time from LV L-H edge till HV edge begins to rise (COM2 baud rate) |

$<sup>^{\</sup>rm 1}$  The COM transmitter is only available inside the products ZIOL24xx/22xx  $^{\rm 2}$  The AUX transmitter is only available inside the products ZIOL24xx/21xx

| Symbol                     | Parameter                                                   | Min   | Typ <sup>1)</sup> | Max              | Unit                 | Conditions                                                                                               |

|----------------------------|-------------------------------------------------------------|-------|-------------------|------------------|----------------------|----------------------------------------------------------------------------------------------------------|

| t <sub>THLdelay</sub> COM2 | Propagation delay H-L edge                                  |       |                   | 700              | ns                   | Time from LV H-L edge till HV edge begins to fall (COM2 baud rate)                                       |

| Receiver Input             | Channels (COM¹/AUX²)                                        |       |                   |                  |                      |                                                                                                          |

| $V_{ih1}$                  | IO-Link specific threshold, High                            | 10.75 |                   | 12.75            | V                    |                                                                                                          |

| V <sub>il1</sub>           | IO-Link specific threshold, Low                             | 8.75  |                   | 10.75            | V                    |                                                                                                          |

| V <sub>ihyst1</sub>        | IO-Link specific thresholds,<br>Hysteresis                  | 1.5   |                   | 2.5              | V                    |                                                                                                          |

| V <sub>ih2</sub>           | Ratiometric threshold, High                                 | 52    |                   | 57               | %*V <sub>DD_HV</sub> |                                                                                                          |

| V <sub>il2</sub>           | Ratiometric threshold, Low                                  | 43    |                   | 47.7             | %*V <sub>DD_HV</sub> |                                                                                                          |

| V <sub>ihyst2</sub>        | Ratiometric thresholds,<br>Hysteresis                       | 7     |                   | 11.6             | %*V <sub>DD_HV</sub> |                                                                                                          |

| R <sub>in</sub>            | Input resistance                                            | 150   |                   |                  | kOhms                |                                                                                                          |

| C <sub>in</sub>            | Input capacitance                                           |       |                   | 20               | pF                   |                                                                                                          |

| t <sub>Rdelay</sub>        | Propagation delay without filtering                         |       |                   | 80<br>100<br>200 | ns<br>ns<br>ns       | No filter within signal path.<br>Input edge with:<br>>30V/µs (COM3)<br>>5V/µs (COM2)<br>>0.75V/µs (COM1) |

| t <sub>FRdelay</sub>       | Propagation delay with analog filtering                     | 750   | 850               | 950              | ns                   | @V <sub>DD_HV</sub> = 24V, Input edge with: >30V/µs (COM3)                                               |

| $t_{Rpulse}$               | Minimal propagated pulse width without filtering            |       | 25                |                  | ns                   |                                                                                                          |

| t <sub>FRpulse</sub>       | Minimal propagated pulse width with analog filtering        |       | 1.1               |                  | μs                   |                                                                                                          |

| t <sub>DIGdelay</sub>      | Additional propagation delay with digital filtering         | 180   |                   | 440              | ns                   |                                                                                                          |

| f <sub>cut</sub>           | Input filter – cut off frequency (-3dB) COM and AUX channel | 100   |                   | 250              | kHz                  | filter characteristic: 1st order                                                                         |

| I <sub>sink1</sub>         | Sink strength 1                                             | 2     | 2.5               | 3                | mA                   | Line input voltage >5V                                                                                   |

| I <sub>sink2</sub>         | Sink strength 2                                             | 5     | 6                 | 7                | mA                   | According to IO-Link<br>Specification                                                                    |

| $R_{pull}$                 | Configurable pull-up/pull-down resistor @ COM_O/AUX_O       | 100k  |                   | 250k             | Ohms                 |                                                                                                          |

$<sup>^1</sup>$  The COM receiver is only available inside the products ZIOL24xx/22xx  $^2$  The AUX receiver is only available inside the products ZIOL24xx/21xx