### カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

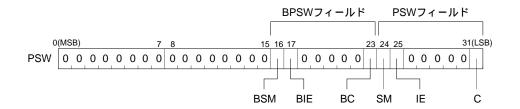

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

## 資料中の「三菱電機」、「三菱XX」等名称の株式会社ルネサス テクノロジへの変更について

2003年4月1日を以って株式会社日立製作所及び三菱電機株式会社のマイコン、ロジック、アナログ、ディスクリート半導体、及びDRAMを除くメモリ(フラッシュメモリ・SRAM等)を含む半導体事業は株式会社ルネサステクノロジに承継されました。

従いまして、本資料中には「三菱電機」、「三菱電機株式会社」、「三菱半導体」、「三菱XX」といった表記が残っておりますが、これらの表記は全て「株式会社ルネサス テクノロジ」に変更されておりますのでご理解の程お願い致します。尚、会社商標・ロゴ・コーポレートステートメント以外の内容については一切変更しておりませんので資料としての内容更新ではありません。

注:「高周波・光素子事業、パワーデバイス事業については三菱電機にて引き続き事業運営を行います。」

2003年4月1日 株式会社ルネサス テクノロジ カスタマサポート部

# 32

# 32170、32174 グループ

ユーザーズマニュアル ルネサス32ビットシングルチップマイクロコンピュータ M32Rファミリ / M32R/Eシリーズ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサスエレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサスエレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

#### 安全設計に関するお願い

・弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

#### 本資料ご利用に際しての留意事項

- ・本資料は、お客様が用途に応じた適切な三菱半導体製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について三菱電機が所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- ・本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用 に起因する損害、第三者所有の権利に対する侵害に関し、三菱電機は責任を負いません。

- ・本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、三菱電機は、予告なしに、本資料に記載した製品または仕様を変更することがあります。三菱半導体製品のご購入に当たりましては、事前に三菱電機または特約店へ最新の情報をご確認頂きますとともに、三菱電機半導体情報ホームページ(http://www.semicon.melco.co.jp/)などを通じて公開される情報に常にご注意ください。

- ・本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述 誤りに起因する損害がお客様に生じた場合には、三菱電機はその責任を負いません。

- ・本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを 流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、シス テム全体で十分に評価し、お客様の責任において適用可否を判断してください。三菱電機 は、適用可否に対する責任は負いません。

- ・本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、三菱電機または特約店へご照会ください。

- ・本資料の転載、複製については、文書による三菱電機の事前の承諾が必要です。

- ・本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたら三菱電機または特約店までご照会ください。

## 改訂履歴

# 32170 / 32174 グループユーザーズマニュアル

| Rev. | 発行日      |       | 改訂内容                                                                         |  |       |                  |

|------|----------|-------|------------------------------------------------------------------------------|--|-------|------------------|

|      |          | ページ   | ポイント                                                                         |  |       |                  |

| 1.0  | 00/03/06 | -     | 初版発行                                                                         |  |       |                  |

| 2.0  | 01/03/05 | 全体    | 32174 グループの説明を追加                                                             |  |       |                  |

|      |          | P1-7  | 図 1.2.1 中の 内蔵フラッシュメモリ、内蔵 RAM に M32174F4、<br>M32174F3 を追加                     |  |       |                  |

|      |          | P1-10 | 表 1.2.4 を追加                                                                  |  |       |                  |

|      |          | P1-11 | 図 1.3.1 の注 1 を修正                                                             |  |       |                  |

|      |          |       | 誤)5V 系電源により動作します。                                                            |  |       |                  |

|      |          |       | 正)3.3V 系及び5V 系で動作します。                                                        |  |       |                  |

|      |          | P1-12 | 図 1.3.2 に M32174F4VWG、M32174F3VWG を追加                                        |  |       |                  |

|      |          |       | 注1を修正                                                                        |  |       |                  |

|      |          |       | 誤)5V 系電源により動作します。                                                            |  |       |                  |

|      |          |       | 正)3.3V 系及び5V 系で動作します。                                                        |  |       |                  |

|      |          | P1-19 | 図 1.4.1 に M32174F4VFP、M32174F3VFP を追加                                        |  |       |                  |

|      |          | P1-22 | 図 1.4.2 に M32174F4VWG、M32174F3VWG を追加                                        |  |       |                  |

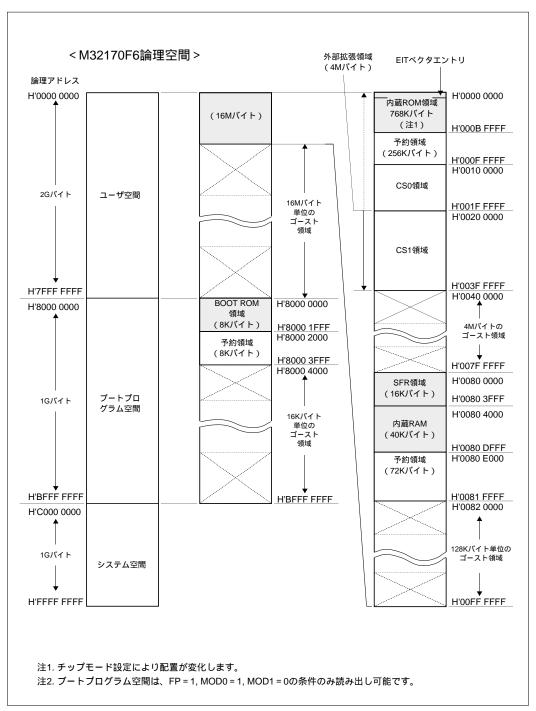

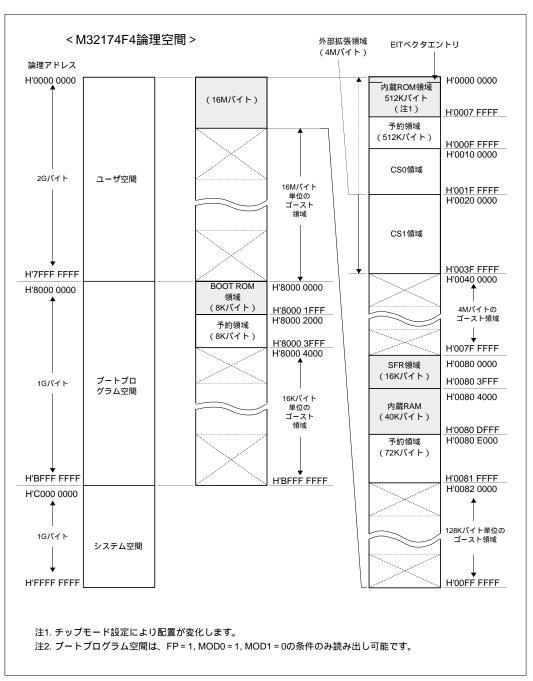

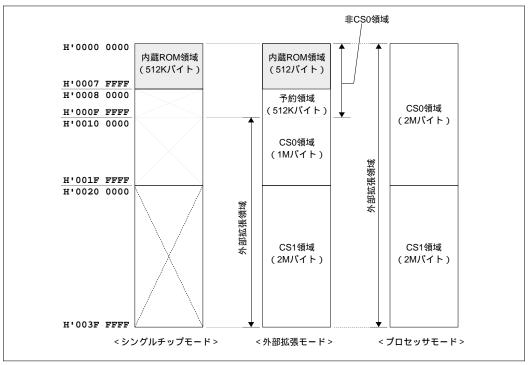

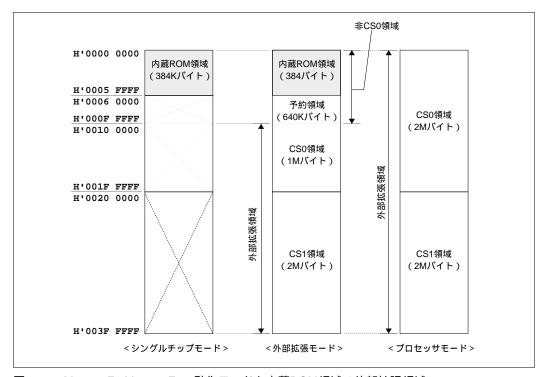

|      |          | P3-6  | 図 3.1.4 M32174F4 のアドレス空間を追加                                                  |  |       |                  |

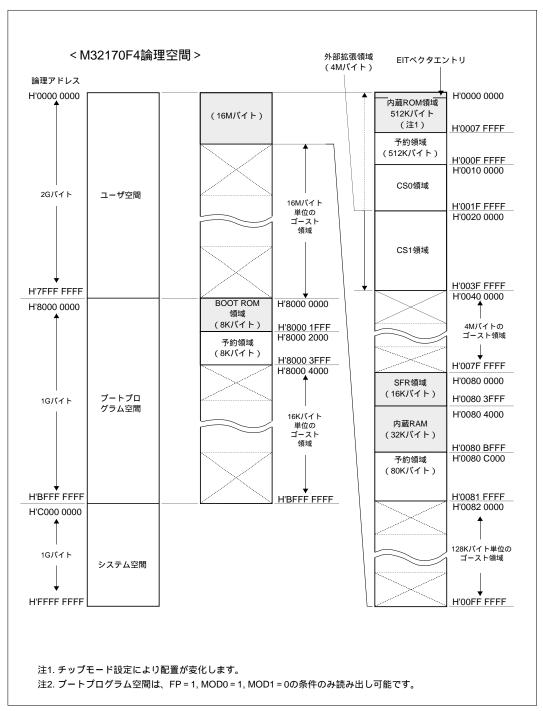

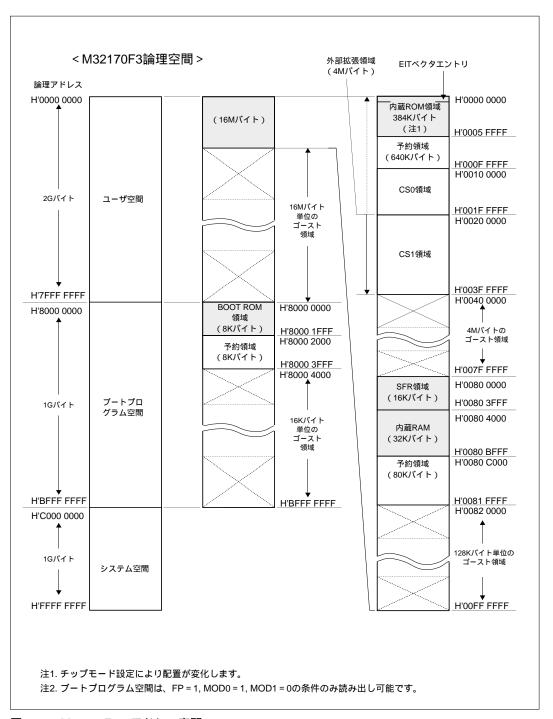

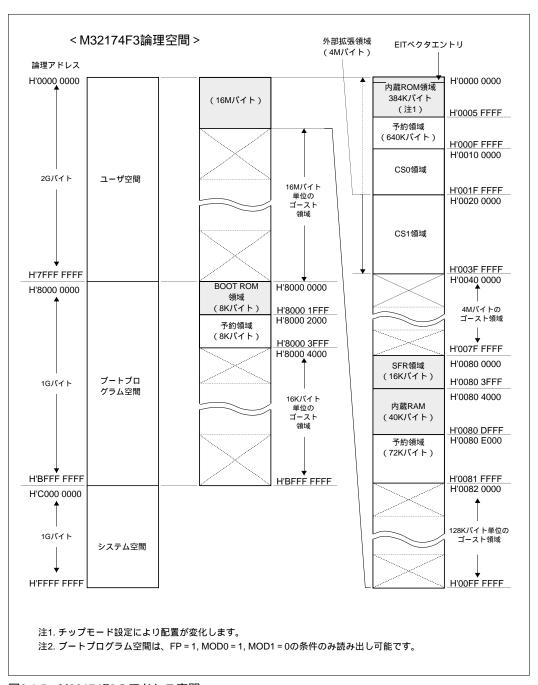

|      |          | P3-7  | 図 3.1.5 M32174F3 のアドレス空間を追加                                                  |  |       |                  |

|      |          | P3-10 | 表 3.3.1 に M32174F4、M32174F3 を追加                                              |  |       |                  |

|      |          | P3-11 | 表 3.4.1 に M32174F4、M32174F3 を追加                                              |  |       |                  |

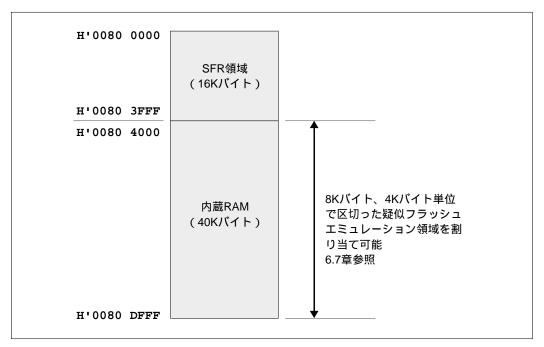

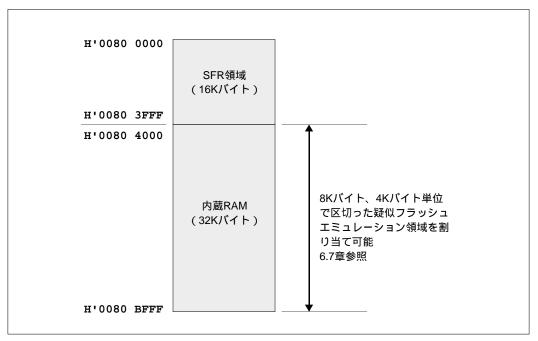

|      |          | P3-12 | 図 3.4.3 M32174F4、M32174F3 内蔵 RAM 領域 /SFR(Special Function<br>Register)の領域を追加 |  |       |                  |

|      |          | P6-2  | 表 6.2.1 に M32174F4、M32174F3 を追加                                              |  |       |                  |

|      |          | P6-3  | 表 6.3.1 に M32174F4、M32174F3 を追加                                              |  |       |                  |

|      |          | P6-40 | 図 6.5.15 を修正                                                                 |  |       |                  |

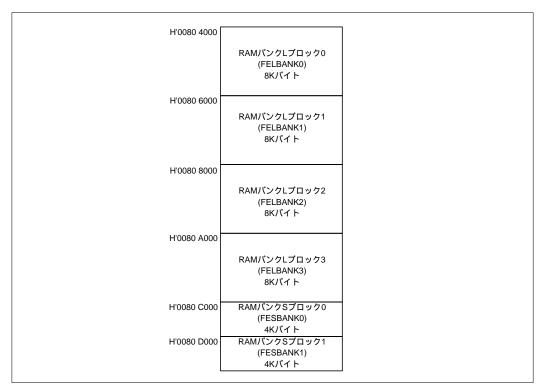

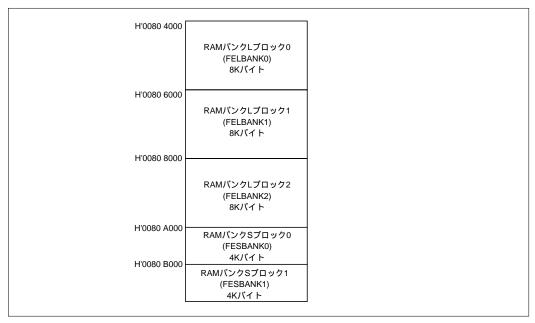

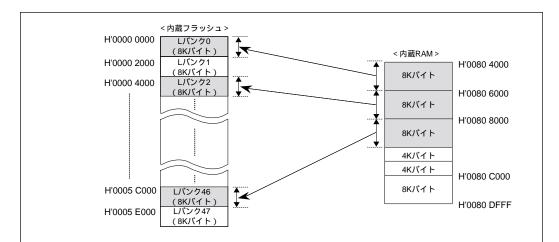

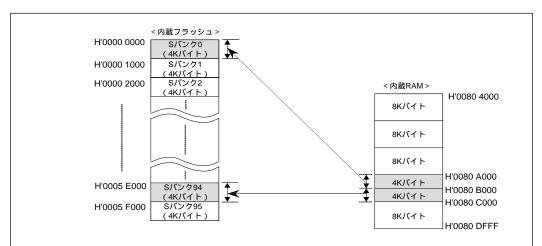

|      |          | P6-45 | 図 6.7.3 M32174F4 および M32174F3 内蔵 RAM のバンク構成を追加                               |  |       |                  |

|      |          |       |                                                                              |  | P6-46 | 注3、注4、注5の注意事項を追加 |

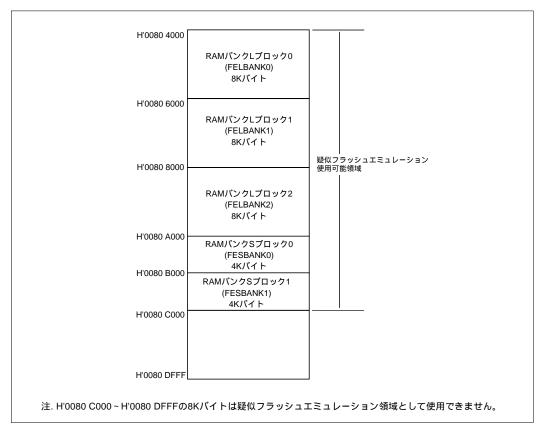

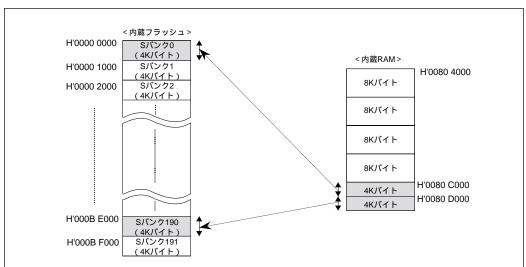

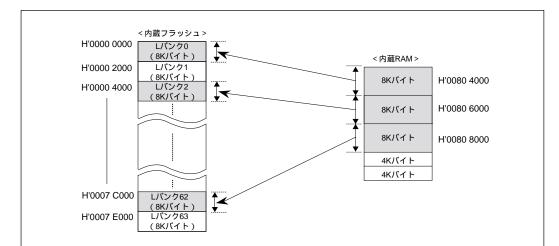

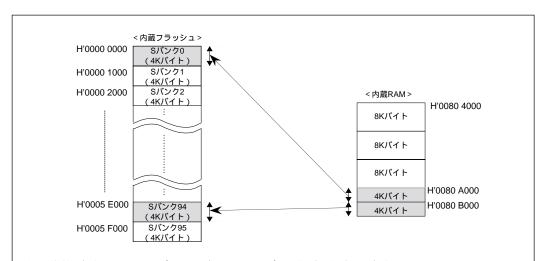

|      |          | P6-50 | 図 6.7.10 M32174F4の 8K バイト単位分割の疑似フラッシュエミュレーション領域を追加                           |  |       |                  |

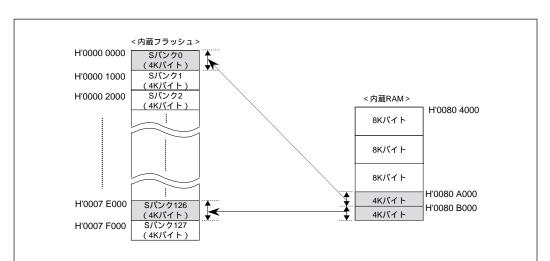

|      |          |       | 図6.7.11 M32174F4の4Kバイト単位分割の疑似フラッシュエミュレーション領域を追加                              |  |       |                  |

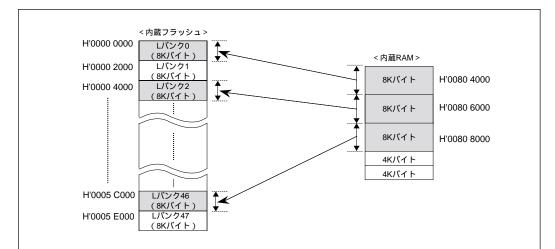

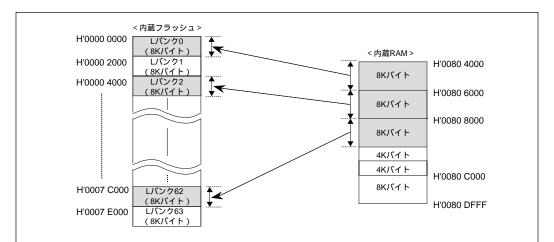

|      |          | P6-51 | 図6.7.12 M32174F3の8Kバイト単位分割の疑似フラッシュエミュレーション領域を追加                              |  |       |                  |

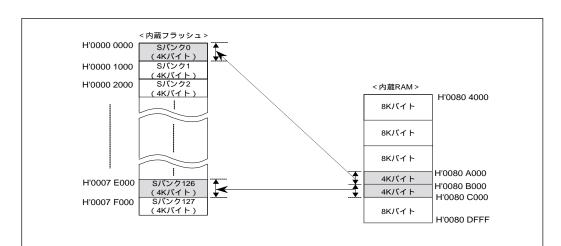

|      |          |       | 図6.7.13 M32174F3の4Kバイト単位分割の疑似フラッシュエミュレーション領域を追加                              |  |       |                  |

|      |          | P7-4  | 表 7.3.2 を追加                                                                  |  |       |                  |

|      |          |       |                                                                              |  |       |                  |

## 改訂履歴

## 32170 / 32174 グループユーザーズマニュアル

| Rev. | 発行日      |           | 改訂内容                                                         |

|------|----------|-----------|--------------------------------------------------------------|

|      |          | ページ       | ポイント                                                         |

| 2.0  | 01/03/05 | P8-31 ~   | 図 8.4.1~図 8.4.4 を修正                                          |

|      |          | P8-34     |                                                              |

|      |          | P8-35     | 8.5 入出力ポートの注意事項を追加                                           |

|      |          | P10-1 ~   | 10 章全体 プリスケ - ラの表記を PRS に統一                                  |

|      |          | P10-232   |                                                              |

|      |          | P10-83    | 図 10.3.8 を修正                                                 |

|      |          | P10-184 ~ | (1)TOD タイマのカウンタへの書き込み許可 / 禁止の条件の追加                           |

|      |          | P10-185   |                                                              |

|      |          |           | (1)TOM タイマのカウンタへの書き込み許可 / 禁止の条件の追加                           |

|      |          | P10-214   |                                                              |

|      |          | P11-3     | 表 11.1.1 を修正                                                 |

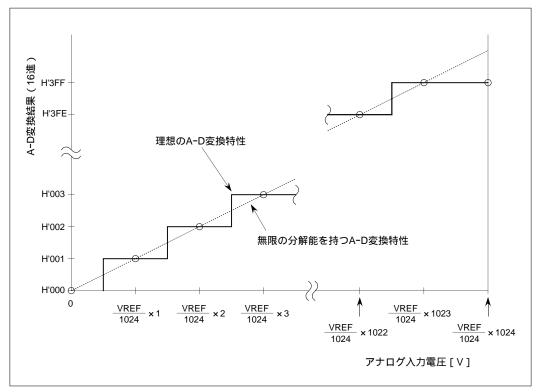

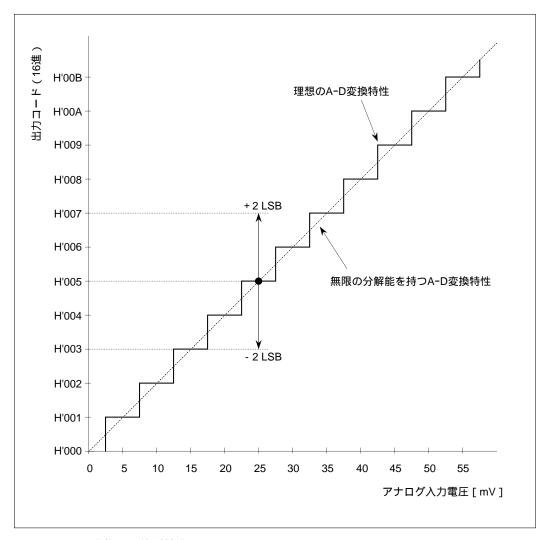

|      |          | P11-48    | 11.3.5 「A-D 変換精度の定義」の説明内容変更                                  |

|      |          | P11-49    | 図 11.3.5 を変更                                                 |

|      |          |           | 図 11.3.6 および図 11.3.7 削除                                      |

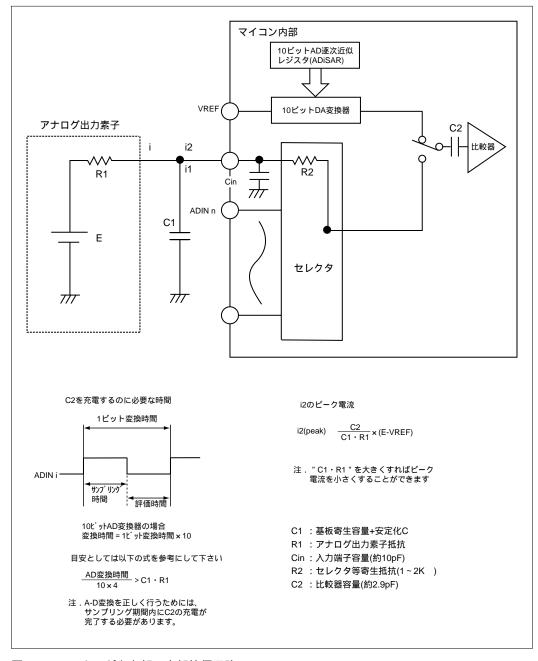

|      |          | P11-51    | 図 11.4.1 アナログ入力部の内部等価回路を追加                                   |

|      |          | P12-27    | 12.2.8 SIO ボーレートレジスタ最終行の記述を修正                                |

|      |          |           | 誤)7以下 正)7以上                                                  |

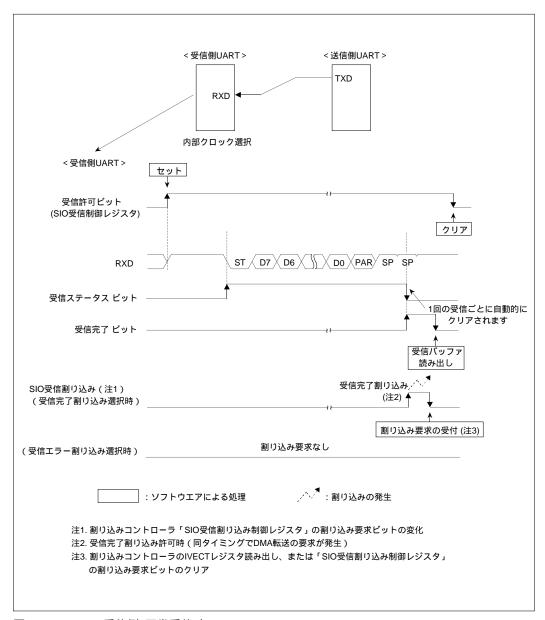

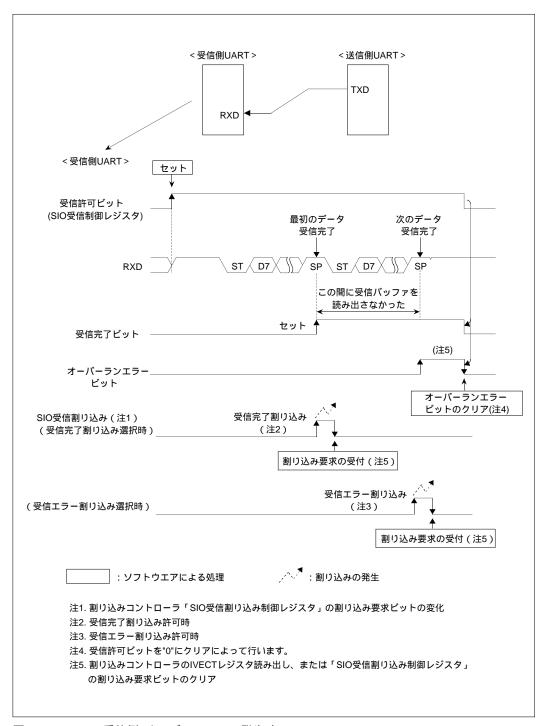

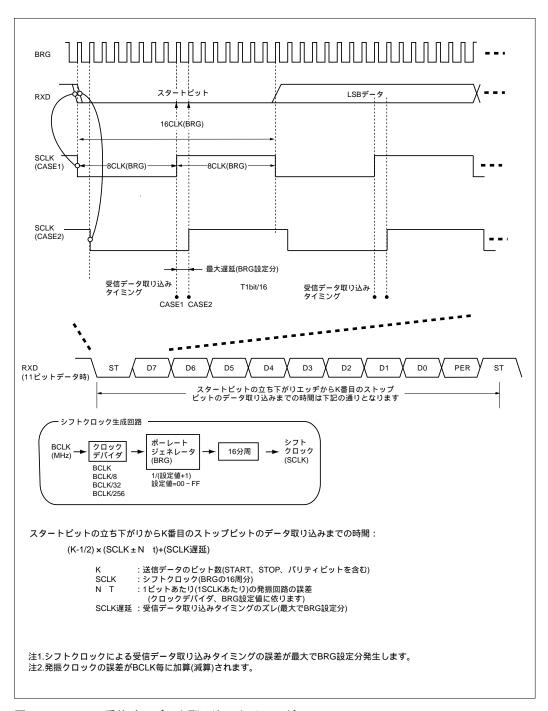

|      |          | P12-61    | 図12.7.5 UART受信時のデータ取り込みタイミングを追加                              |

|      |          | P13-2     | 13.1 CAN モジュールの概要の記述を修正                                      |

|      |          |           | 誤) CAN(Controller Area Network)Specification2.0B 準拠          |

|      |          |           | 正)CAN(Controller Area Network)Specification2.0B active<br>準拠 |

|      |          |           | 表 13.1.1 中のプロトコルの内容説明を修正                                     |

|      |          |           | 誤)CANSpecification2.0B                                       |

|      |          |           | 正)Specification2.0B active                                   |

|      |          |           | 表 13.1.1 に注意事項を追加                                            |

|      |          | P13-9     | (4)FRST(強制リセット)ビット(D11)に注意事項を追加                              |

|      |          | P13-14    | (11)MSN(メッセージスロットナンバー)ビット(D12 ~ D15)に注意事項                    |

|      |          |           | を追加                                                          |

|      |          | P13-17    | 注意事項を追加                                                      |

|      |          |           |                                                              |

|      |          |           |                                                              |

|      |          |           |                                                              |

|      |          |           |                                                              |

### 改訂履歴

# 32170 / 32174 グループユーザーズマニュアル

| Rev. | 発行日      |                    | 改訂内容                                                                                                                                              |

|------|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|      |          | ページ                | ポイント                                                                                                                                              |

| 2.0  | 01/03/05 | P13-21             | 注2の注意事項を追加                                                                                                                                        |

|      |          | P13-35             | 注意事項を追加                                                                                                                                           |

|      |          | P13-37             | 注2の注意事項を削除                                                                                                                                        |

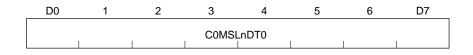

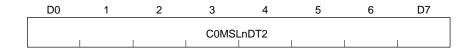

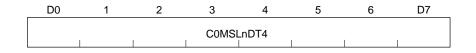

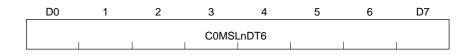

|      |          | P13-44             | CAN メッセージスロットデータ 0(COMSLnDT)の説明に注意事項を追加                                                                                                           |

|      |          | P13-59             | 13.4.2 CAN タイミングの項を追加                                                                                                                             |

|      |          | P13-81             | 図 13.8.2 を修正                                                                                                                                      |

|      |          | P18-2              | 図 18.1.1 注意事項を追加                                                                                                                                  |

|      |          | P19-14             | 32170 用 BSDL 記述(図 19.5.1~図 19.5.19)を削除                                                                                                            |

|      |          | P19-15 ~           | 図 19.6.1 および図 19.7.2 に注意書きを追加                                                                                                                     |

|      |          | P19-16             |                                                                                                                                                   |

|      |          | P19-17 ~           | 図 19.7.1JTAG 未使用時の端子処理(240QFP 使用時)、                                                                                                               |

|      |          | P19-18             | 図 19.7.2JTAG 未使用時の端子処理(255QFP 使用時)を追加                                                                                                             |

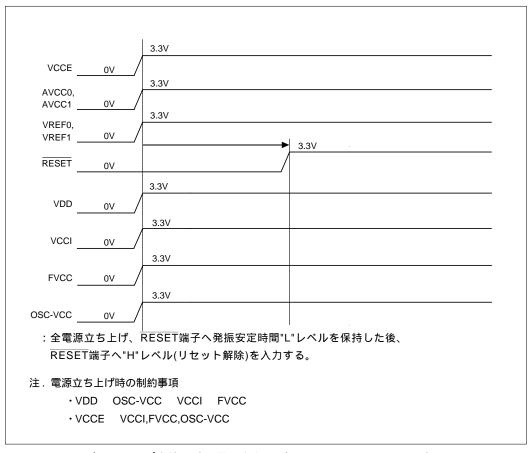

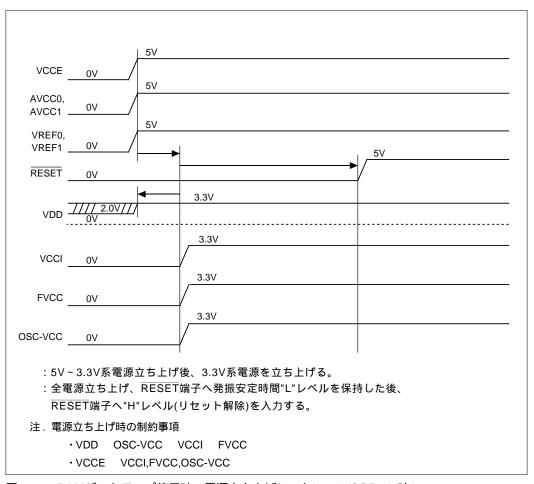

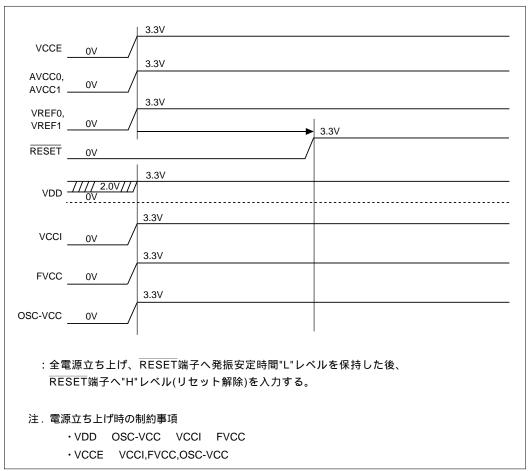

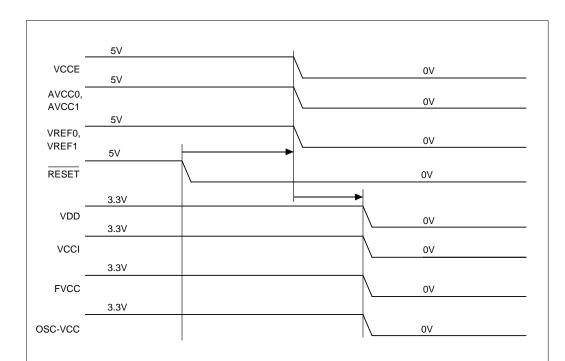

|      |          | P20-1 ~            | 20 章の図に VCCE=3.3V 時の電源立ち上げ / 立ち下げシーケンスを                                                                                                           |

|      |          | P20-16             | 追加                                                                                                                                                |

|      |          | P21-2              | 絶対最大定格(-40 ~ 125 )を修正                                                                                                                             |

|      |          | P21-3              | 推奨動作条件を修正                                                                                                                                         |

|      |          | P21-5              | (1)f=(XIN)=10MHz 時の電気的特性を修正                                                                                                                       |

|      |          | P21-7              | (3)f=(XIN)=8MHz 時の電気的特性を修正                                                                                                                        |

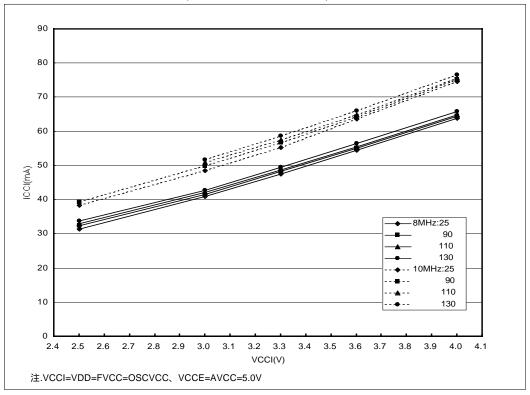

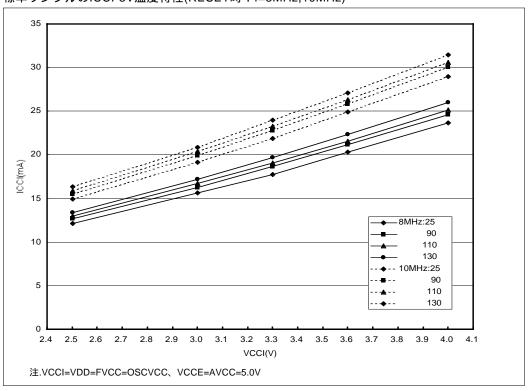

|      |          | P21-9              | 標準サンプルの ICCI-3V 温度特性(動作時:f=8MHz、10MHz)、<br>標準サンプルの ICCI 温度特性(RESET 時:f=8MHz、10MHz)を追加                                                             |

|      |          | P21-11             | A-D 変換特性(指定のない場合は、AVCC=VREF=VCCE=5.12V、<br>Ta=-40 ~ 85 、f(XIN)=10.0MHz)、A-D 変換特性(指定のない場合、<br>AVCC=VREF=VCCE=5.12V、Ta=-40 ~ 125 、f(XIN)=8.0MHz)を修正 |

|      |          | P21-12 ~<br>P21-19 | 21.2 電気的特性(VCCE=3V 時)の節を追加                                                                                                                        |

|      |          | P21-23             | (9)RTD タイミングの規格表を追加                                                                                                                               |

|      |          | P21-33             | 図 21.3.12 RTD タイミングを追加                                                                                                                            |

|      |          | 付録4                | 付録4「未使用端子の処理」を追加                                                                                                                                  |

|      |          |                    |                                                                                                                                                   |

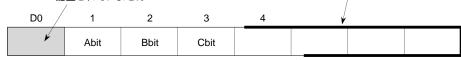

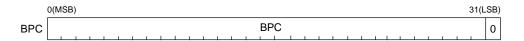

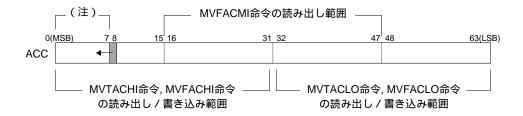

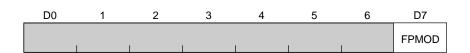

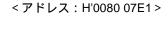

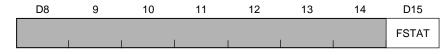

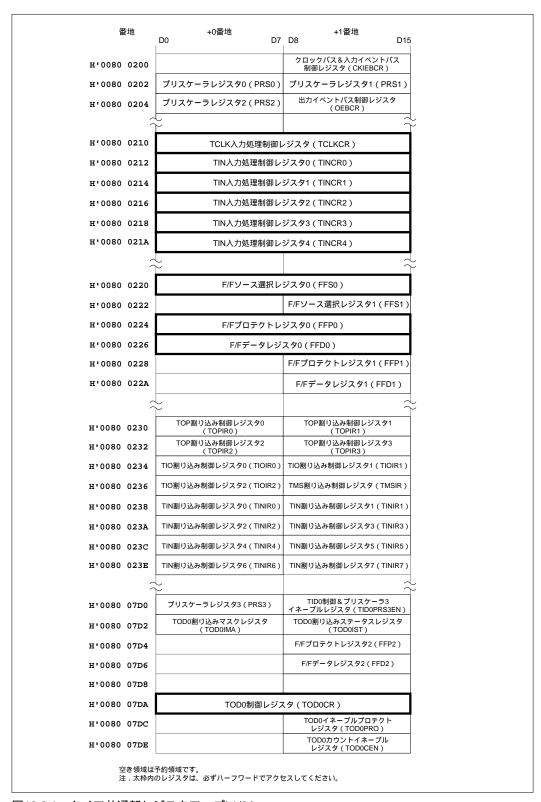

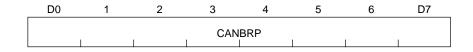

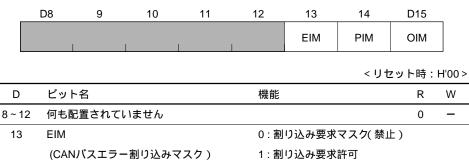

#### 内蔵周辺I/Oレジスタの表の見方

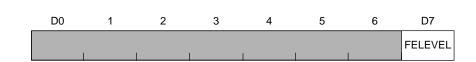

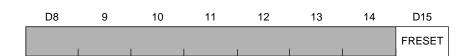

ビット番号: 各レジスタは16ビット幅の内部バスに接続されています。したがって

レジスタのビット番号は、偶数番地はD0~D7に、奇数番地はD8~D15

になります。

リセット時の状態: リセット直後の初期状態を16進数で示します(リセット直後不定

状態のビットがある場合は別に の欄に示します)。

読み出し時の条件: ... 読み出し有効

? ... 読み出し無効(読み出し時データ不定)

0 ... 常に "0" が読み出される 1 ... 常に "1" が読み出される

書き込み時の条件: ... 書き込み有効

... 書き込みデータ条件付き (書き込みに関し何らかの条件があるもの)

- ... 書き込み無効 (書き込み時は "0" でも "1" でもよい)

#### <表記例>

網掛け部分には何も 配置されていません 太枠で囲まれたレジスタはバイト(8ビット) アクセスはできません。ハーフワードまたは ワードでのみアクセスできる条件付きレジス タです。

🦜 < リセット時 : H'04 >

| D | ビット名  |         | 機能 | R        | W        |

|---|-------|---------|----|----------|----------|

| 0 | 何も配置る | されていません |    | 0        | -        |

| 1 | Abit  |         | 0: |          |          |

|   | (     | )       | 1: |          |          |

| 2 | Bbit  |         | 0: |          |          |

|   | (     | )       | 1: |          |          |

| 3 | Cbit  |         | 0: |          |          |

|   | (     | )       | 1: | <b>^</b> | <b>↑</b> |

|   |       |         |    |          |          |

# 目次

| 第1章 概要                          |      |

|---------------------------------|------|

| 1.1 32170/32174 の概要             | 1-2  |

| 1.1.1 M32R ファミリ CPU コア          | 1-2  |

| 1.1.2 積和演算機能の内蔵                 | 1-3  |

| 1.1.3 フラッシュメモリと RAM の内蔵         | 1-3  |

| 1.1.4 クロック逓倍回路の内蔵               | 1-4  |

| 1.1.5 強力な周辺機能の内蔵                | 1-4  |

| 1.1.6 Full-CAN 機能内蔵             | 1-6  |

| 1.1.7 デバッグ機能内蔵                  | 1-6  |

| 1.2 プロック図                       | 1-7  |

| 1.3 端子機能                        | 1-11 |

| 1.4 端子配置                        | 1-19 |

| 第2章 CPU                         |      |

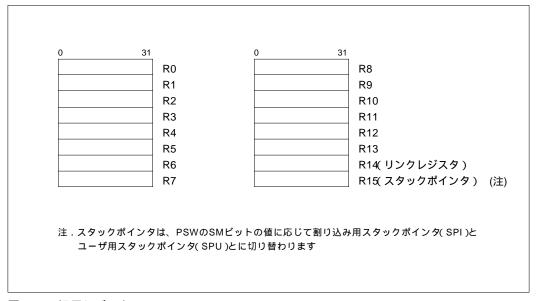

| 2.1 CPU レジスタ                    | 2-2  |

| 2.2 汎用レジスタ                      | 2-2  |

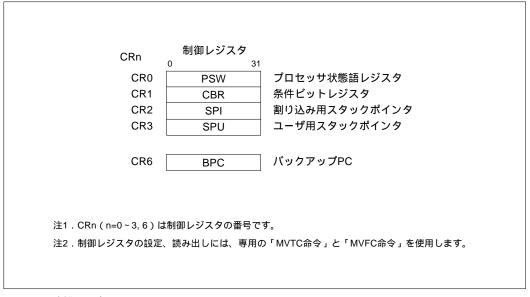

| 2.3 制御レジスタ                      | 2-3  |

| 2.3.1 プロセッサ状態語レジスタ: PSW ( CR0 ) | 2-4  |

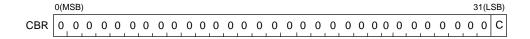

| 2.3.2 条件ビットレジスタ: CBR ( CR1 )    | 2-5  |

| 2.3.3 割り込み用スタックポインタ:SPI(CR2)    | 2-5  |

| ユーザ用スタックポインタ:SPU(CR3)           |      |

| 2.3.4 バックアップ PC : BPC ( CR6 )   | 2-5  |

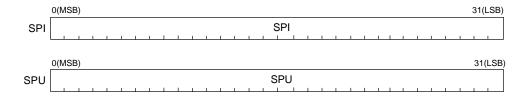

| 2.4 アキュムレータ                     | 2-6  |

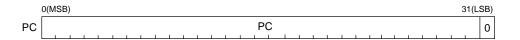

| 2.5 プログラムカウンタ                   | 2-6  |

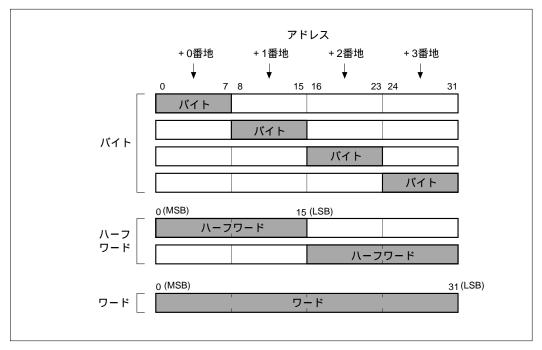

| 2.6 データフォーマット                   | 2-7  |

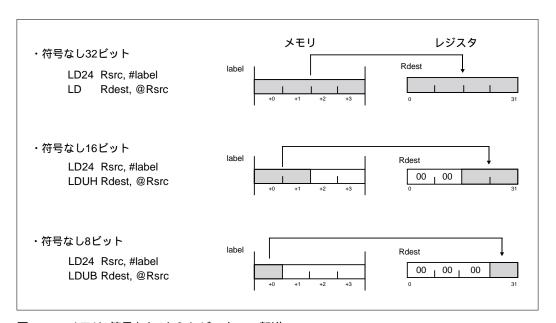

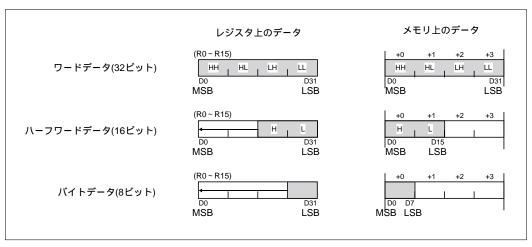

| 2.6.1 データタイプ                    | 2-7  |

| 2.6.2 データフォーマット                 | 2-8  |

| 第3章 | 章 アドレス空間                                   |  |

|-----|--------------------------------------------|--|

| 3.1 | アドレス空間概要                                   |  |

| 3.2 | 動作モード                                      |  |

| 3.3 | 内蔵 ROM 領域 / 外部拡張領域 3-10                    |  |

|     | 3.3.1 内蔵 ROM 領域3-10                        |  |

|     | 3.3.2 外部拡張領域3-10                           |  |

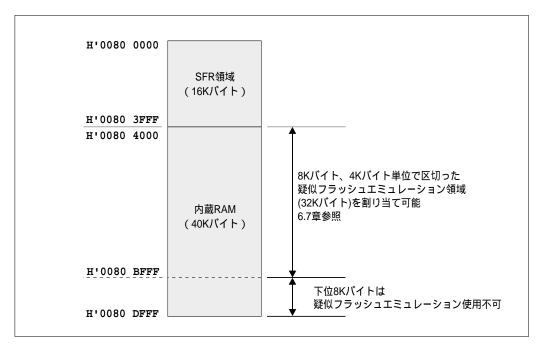

| 3.4 | 内蔵 RAM 領域 / SFR 領域 3-11                    |  |

|     | 3.4.1 内蔵 RAM 領域3-11                        |  |

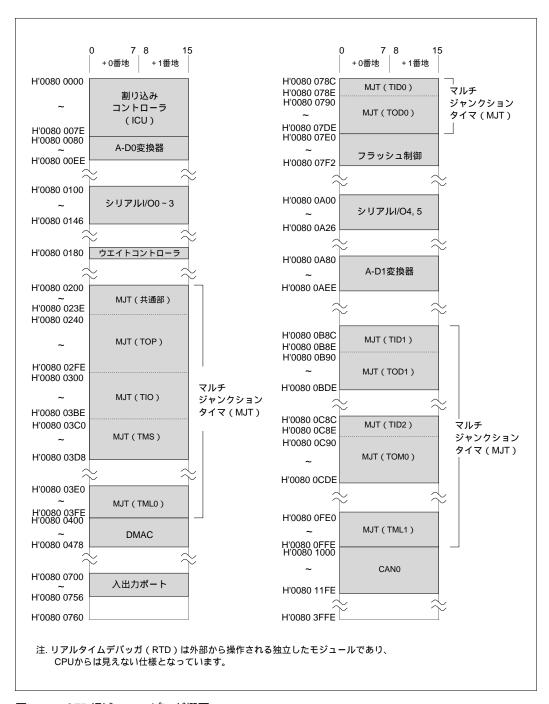

|     | 3.4.2 SFR(Special Function Register)領域3-11 |  |

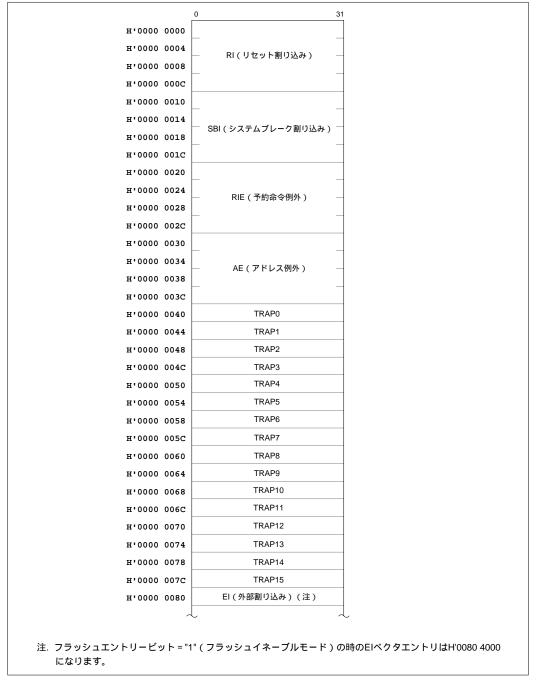

| 3.5 | EIT ベクタエントリ                                |  |

| 3.6 | ICU ベクタテーブル                                |  |

| 3.7 | アドレス空間の注意事項                                |  |

|     |                                            |  |

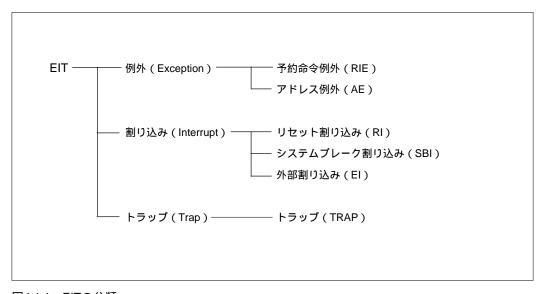

| 第45 | 章 EIT                                      |  |

| 4.1 | EIT の概要 4-2                                |  |

| 4.2 | EIT事象                                      |  |

| 4.2 | 4.2.1 例外(Exception)                        |  |

|     | 4.2.2 割り込み (Interrupt)4-3                  |  |

|     | 4.2.3 トラップ (Trap )4-3                      |  |

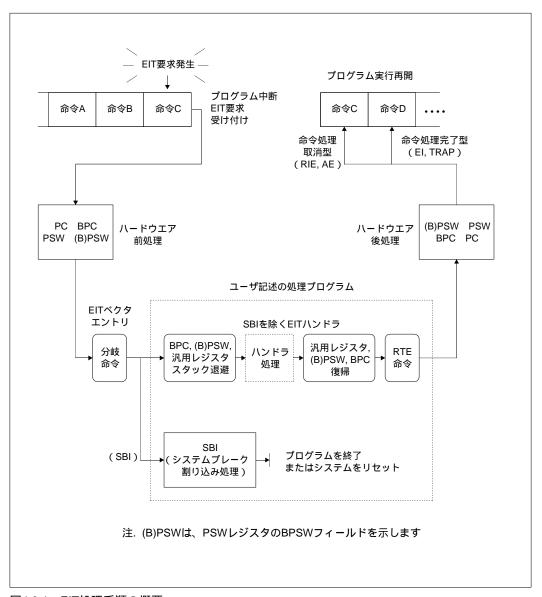

| 4.3 | EIT の処理手順                                  |  |

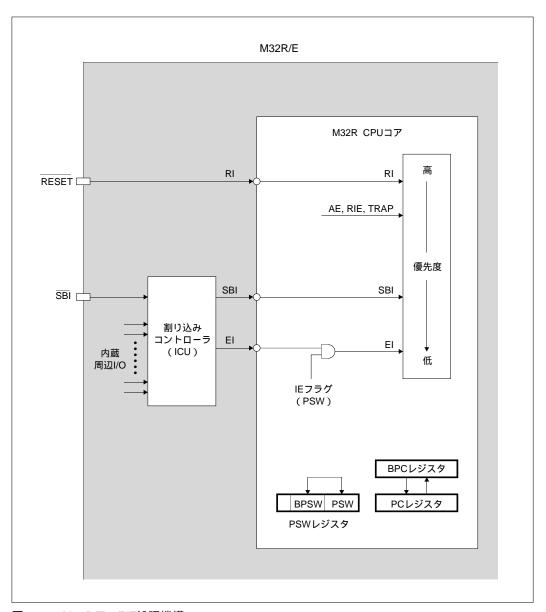

| 4.4 | EIT の処理機構                                  |  |

| 4.5 | EIT 事象の受け付け                                |  |

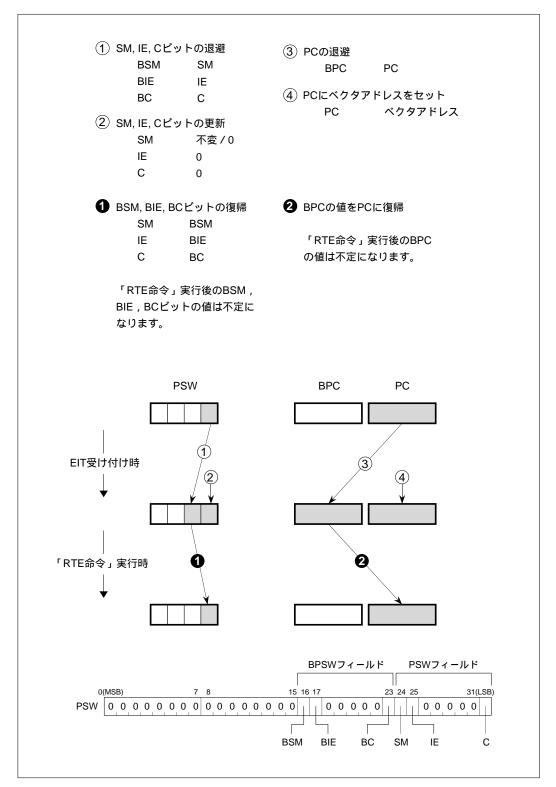

|     |                                            |  |

| 4.6 | PC, PSW の退避と復帰                             |  |

| 4.7 | EIT ベクタエントリ                                |  |

| 4.8 | 例外(Exception)処理                            |  |

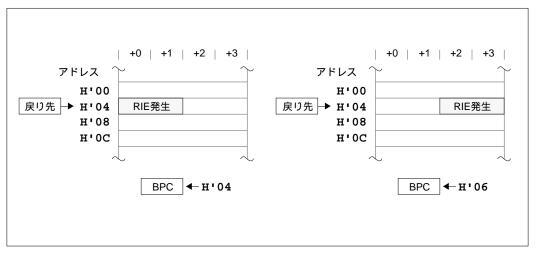

|     | 4.8.1 予約命令例外(RIE)                          |  |

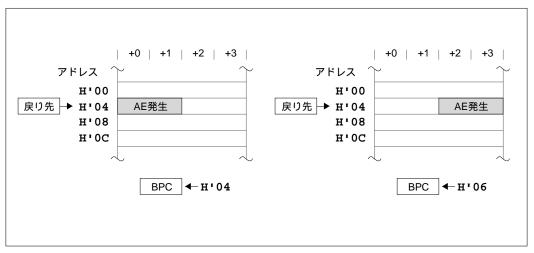

|     | 4.8.2 アドレス例外 (AE)                          |  |

| 4.9 | 割り込み(Interrupt)処理                          |  |

|     | 4.9.1 リセット割り込み (RI)                        |  |

|     | 4.9.2 システムブレーク割り込み(SBI)                    |  |

|     | 4.9.3 外部割り込み(EI)4-18                       |  |

| 4.10 | ) トラップ(Trap)処理                | 4-20 |

|------|-------------------------------|------|

|      | 4.10.1 トラップ(TRAP)             | 4-20 |

| 4.11 | 1 EIT の優先順位                   | 4-22 |

| 4.12 | 2 EIT 処理の例                    | 4-23 |

| 4.13 | 3 EIT の注意事項                   | 4-25 |

| 第5   | 章 割り込みコントローラ(ICU)             |      |

| 5.1  | 割り込みコントローラ(ICU)概要             | 5-2  |

| 5.2  | 内蔵周辺 I/O の割り込み要因              | 5-4  |

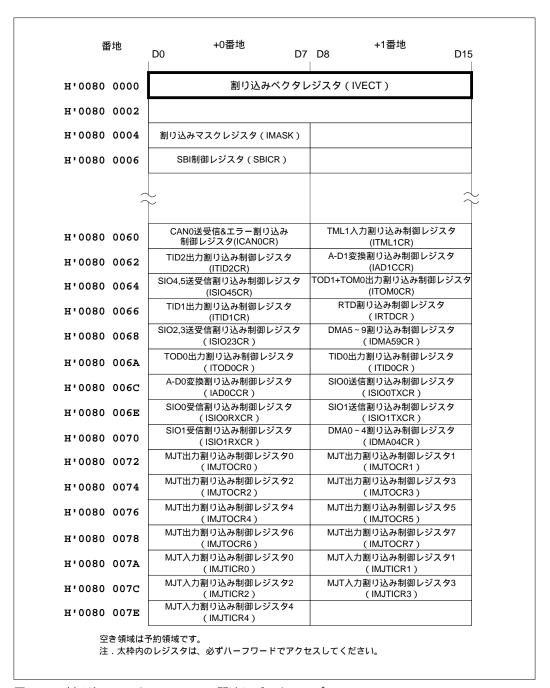

| 5.3  | ICU 関連レジスタ                    | 5-6  |

|      | 5.3.1 割り込みベクタレジスタ             | 5-7  |

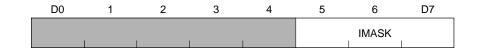

|      | 5.3.2 割り込みマスクレジスタ             | 5-8  |

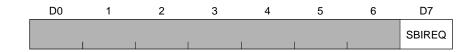

|      | 5.3.3 SBI(システムブレーク割り込み)制御レジスタ | 5-9  |

|      | 5.3.4 割り込み制御レジスタ              | 5-10 |

| 5.4  | ICU ベクタテーブル                   | 5-14 |

| 5.5  | 割り込み動作説明                      | 5-17 |

|      | 5.5.1 内蔵周辺 I/O の割り込み受け付け      | 5-17 |

|      | 5.5.2 内蔵周辺 I/O の割り込みハンドラ処理    | 5-20 |

| 5.6  | システムブレーク割り込み(SBI)動作説明         | 5-22 |

|      | 5.6.1 SBI の受け付け               | 5-22 |

|      | 5.6.2 SBI のハンドラ処理             | 5-22 |

| 第6:  | <br>章 内蔵メモリ                   |      |

| 6.1  | 内蔵メモリ概要                       | 6-2  |

| 6.2  | 内蔵 RAM                        | 6-2  |

| 6.3  | 内蔵フラッシュメモリ                    | 6-3  |

| 6.4  | 内蔵フラッシュメモリ関連レジスタ              | 6-4  |

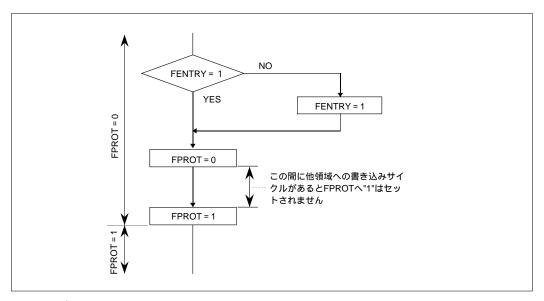

|      | 6.4.1 フラッシュモードレジスタ            | 6-5  |

|      | 6.4.2 フラッシュステータスレジスタ          | 6-6  |

|      | 6.4.3 フラッシュ制御レジスタ             | 6-9  |

|      | 6.4.4 疑似フラッシュLバンクレジスタ         | 6-15 |

|      | 6.4.5 疑似フラッシュSバンクレジスタ         | 6-16 |

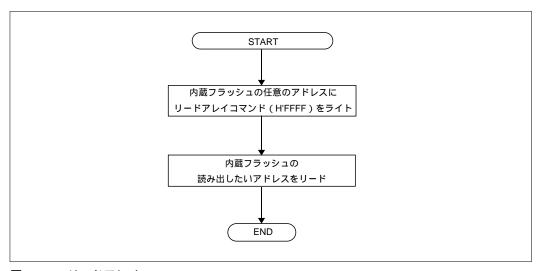

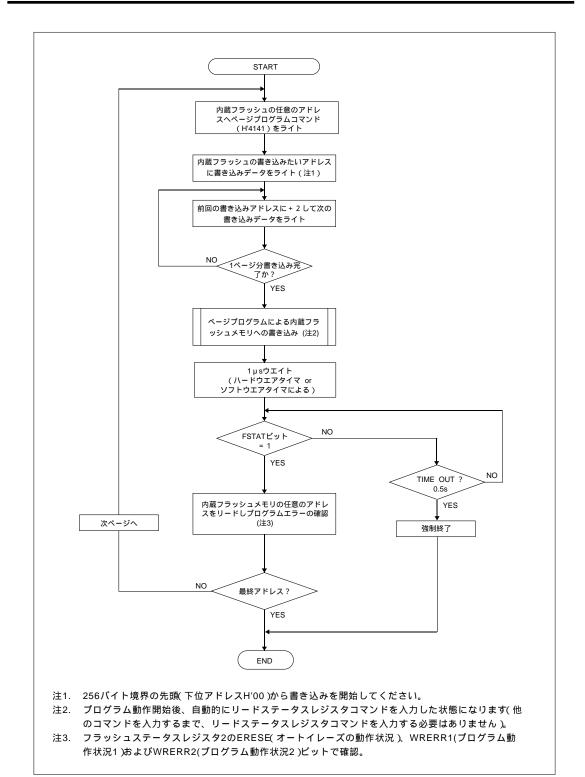

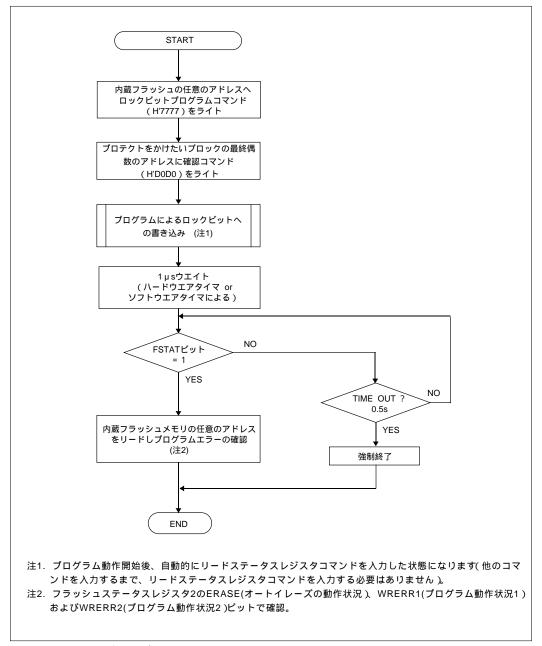

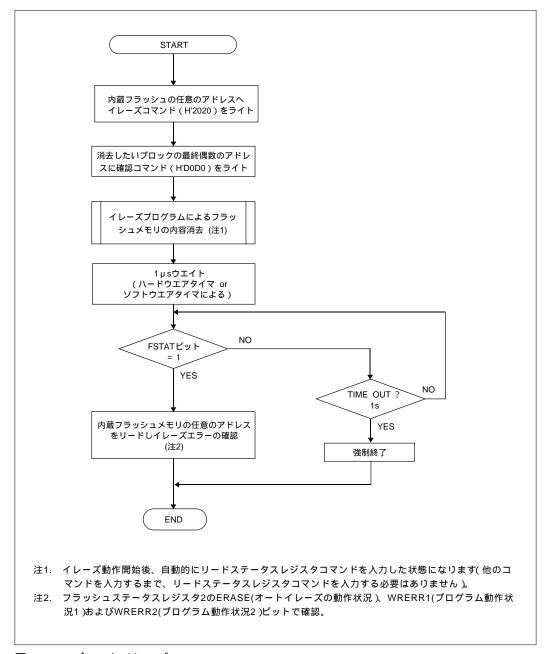

| 6.5 | 内蔵フラッシュメモリの書き込み 6-17              |

|-----|-----------------------------------|

|     | 6.5.1 フラッシュメモリ書き込みの概要6-17         |

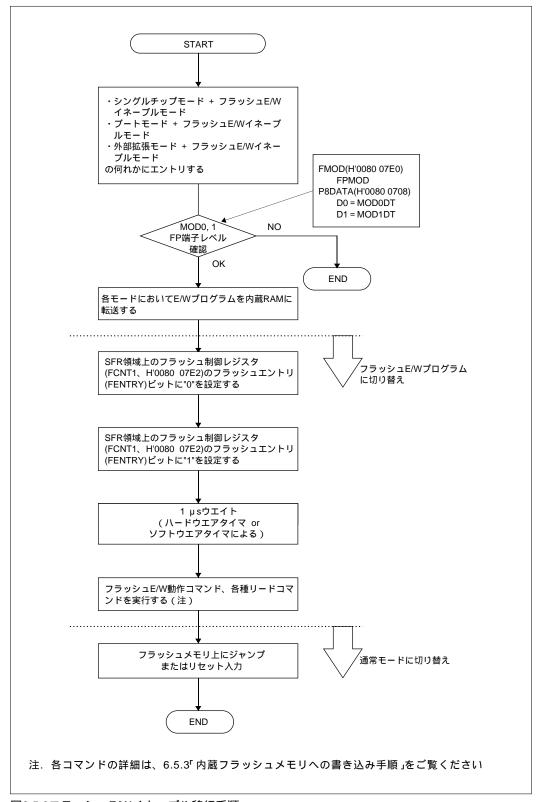

|     | 6.5.2 フラッシュ書き込み時における動作モードの制御 6-23 |

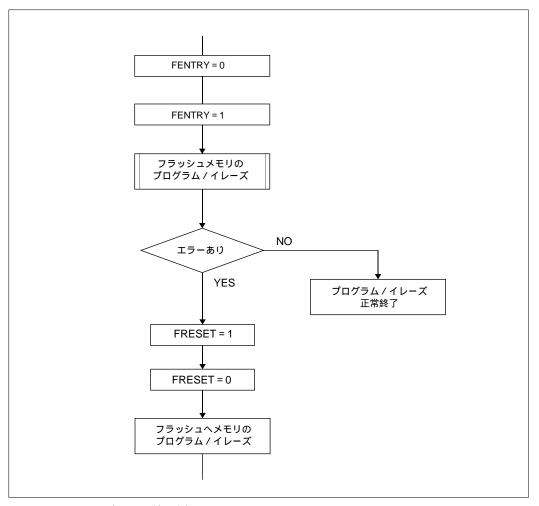

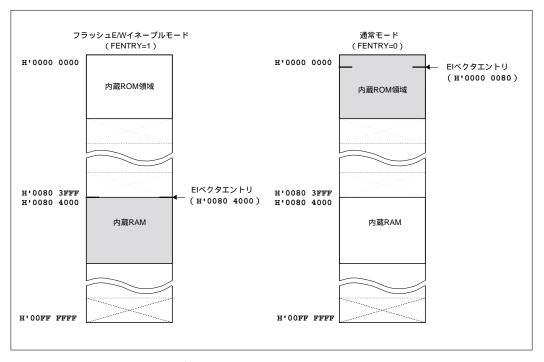

|     | 6.5.3 内蔵フラッシュメモリへの書き込み手順          |

|     | 6.5.4 フラッシュ書き込み時間(参考値)6-41        |

| 6.6 | ブート ROM                           |

| 6.7 | 疑似フラッシュエミュレーション機能                 |

|     | 6.7.1 疑似フラッシュエミュレーション領域           |

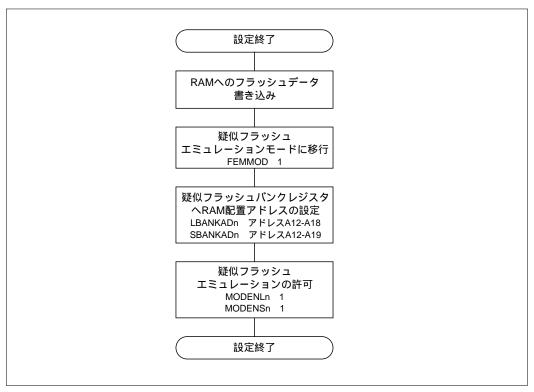

|     | 6.7.2 疑似フラッシュエミュレーションモードへの移行 6-55 |

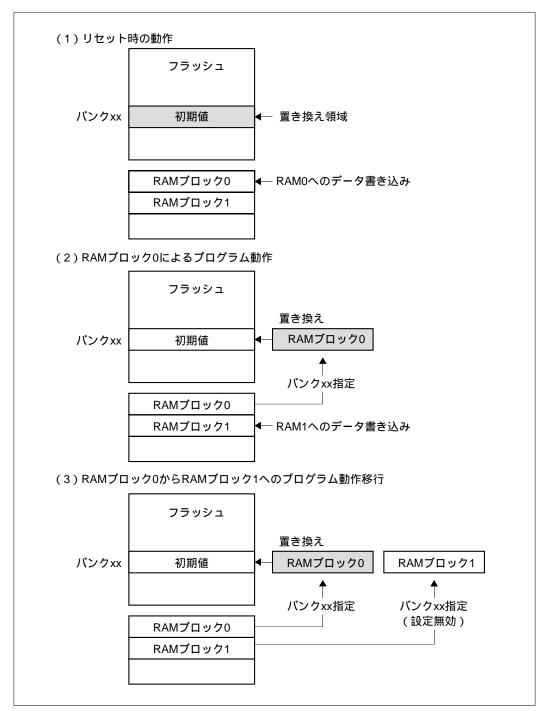

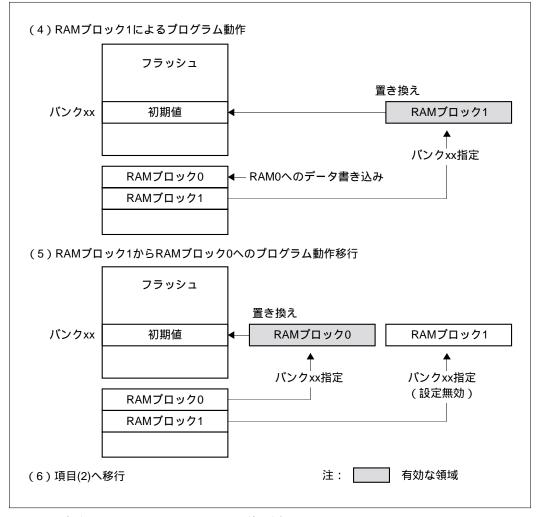

|     | 6.7.3 疑似フラッシュエミュレーションモードの応用例 6-56 |

| 6.8 | シリアルライタとの接続6-58                   |

| 6.9 | フラッシュメモリ書き換え時の注意事項                |

|     |                                   |

| 第75 | 章 リセット                            |

| 7.1 | リセット概要                            |

| 7.2 | リセット動作                            |

|     | 7.2.1 電源投入時のリセット                  |

|     | 7.2.2 動作中のリセット7-2                 |

|     | 7.2.3 フラッシュ書き替え時のリセットベクタ移動        |

| 7.3 | リセット解除直後の内部状態 7-3                 |

| 7.4 | リセット解除後の注意事項                      |

|     |                                   |

| 第8  | 章 入出力ポートと端子機能                     |

| 8.1 | 入出力ポート概要 8-2                      |

| 8.2 | 端子機能の選択 8-4                       |

| 8.3 | 入出力ポート関連レジスタ 8-6                  |

|     | 8.3.1 ポートデータレジスタ8-8               |

|     | 8.3.2 ポート方向レジスタ8-10               |

|     | 8.3.3 ポート動作モードレジスタ8-12            |

| 8.4 | ポート周辺回路                           |

| 8.5 | 入出力ポートの注意事項 8-35                  |

|     |                                   |

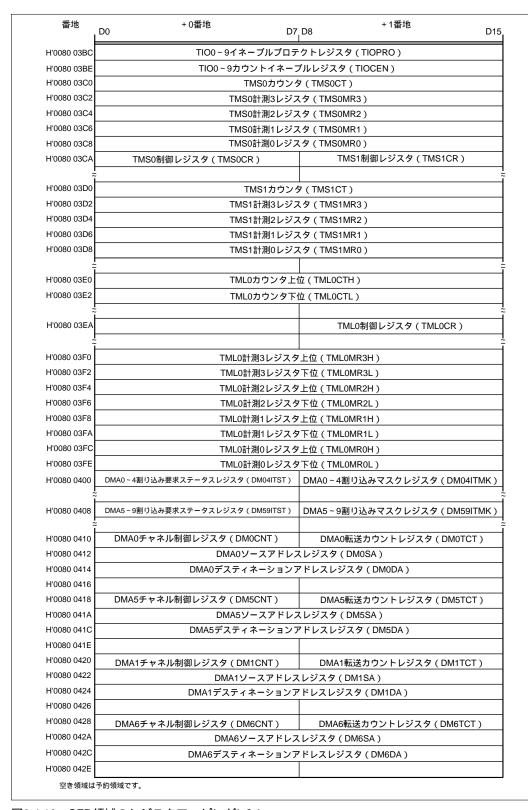

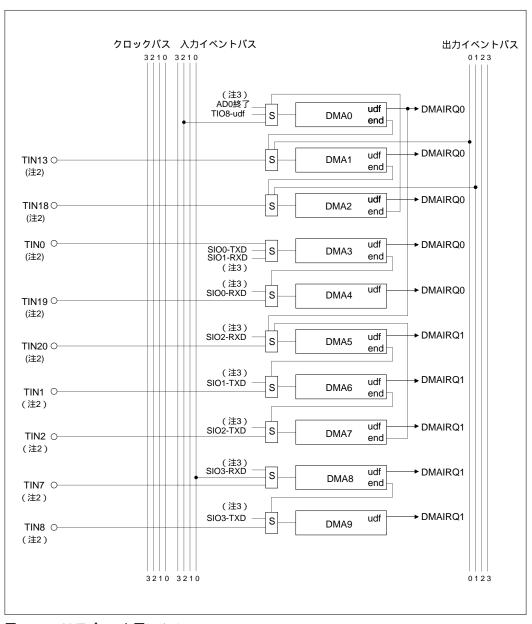

## 第9章 DMAC

| 9.1  | DMAC相  | <b>T要</b>             | 9-2   |

|------|--------|-----------------------|-------|

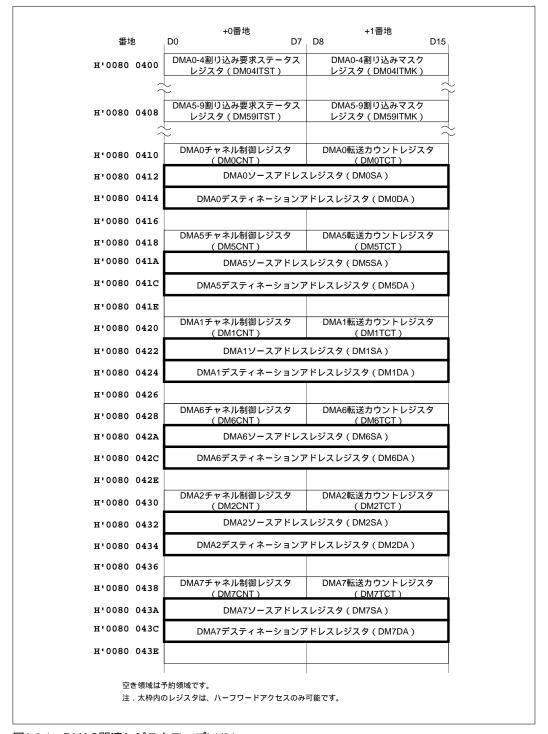

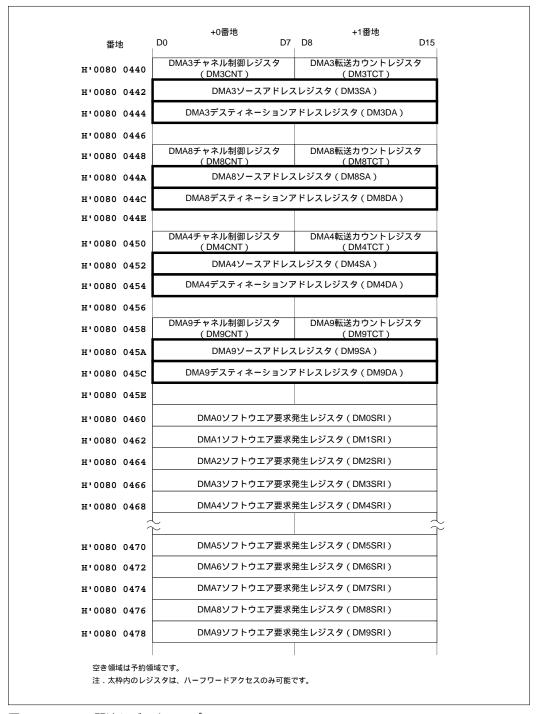

| 9.2  | DMAC身  | 引連レジスタ                | 9-4   |

|      | 9.2.1  | DMA チャネル制御レジスタ        | 9-6   |

|      | 9.2.2  | DMA ソフトウエア要求発生レジスタ    | 9-17  |

|      | 9.2.3  | DMA ソースアドレスレジスタ       | 9-18  |

|      | 9.2.4  | DMA デスティネーションアドレスレジスタ | 9-19  |

|      | 9.2.5  | DMA 転送カウントレジスタ        | 9-20  |

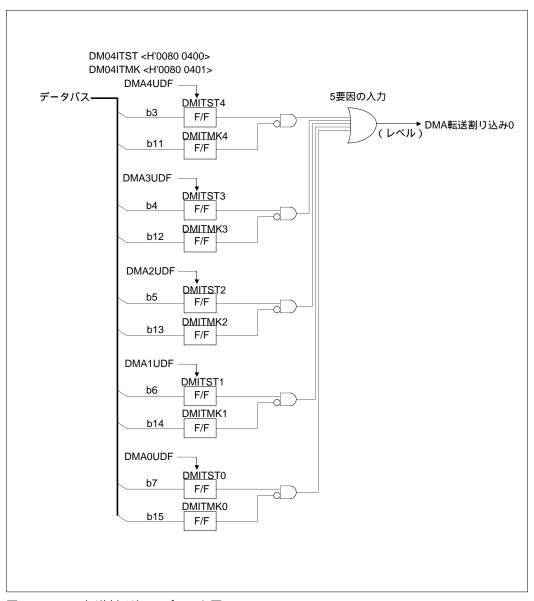

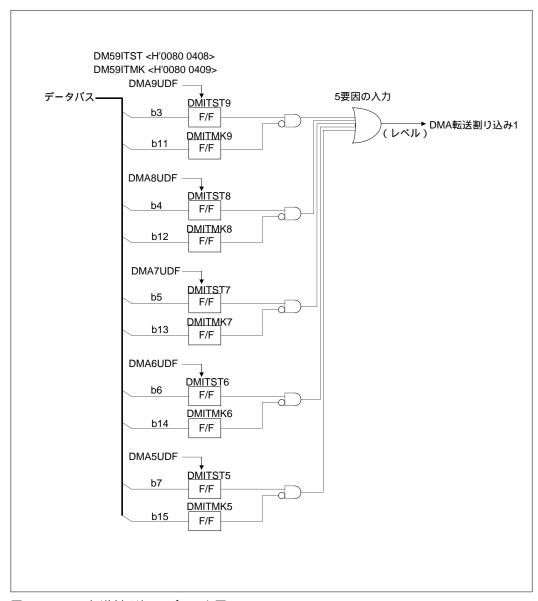

|      | 9.2.6  | DMA 割り込み要求ステータスレジスタ   | 9-21  |

|      | 9.2.7  | DMA 割り込みマスクレジスタ       | 9-23  |

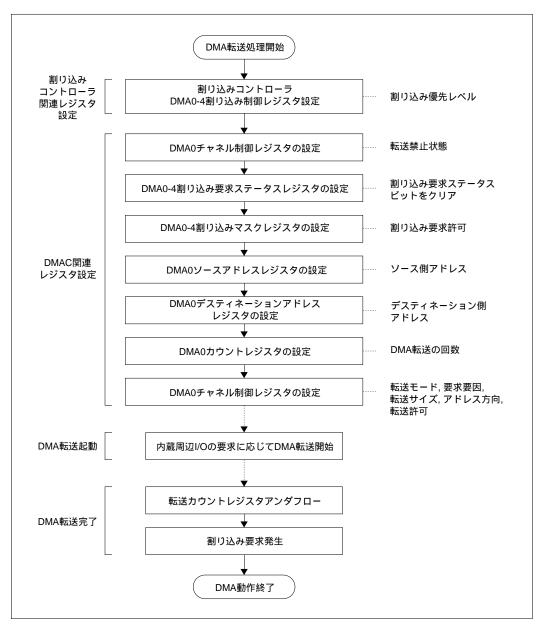

| 9.3  | DMAC 榜 | 後能説明                  | 9-27  |

|      | 9.3.1  | DMA 要求要因              | 9-27  |

|      | 9.3.2  | DMA 転送の処理手順           | 9-31  |

|      | 9.3.3  | DMA の起動               | 9-32  |

|      | 9.3.4  | チャネルの優先順位             | 9-32  |

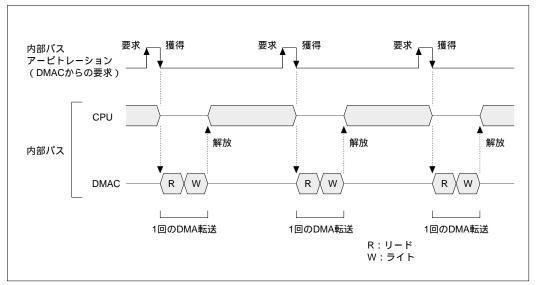

|      | 9.3.5  | 内部バス権の獲得と解放           | 9-33  |

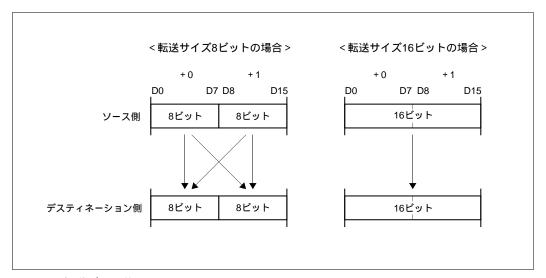

|      | 9.3.6  | 転送単位                  | 9-33  |

|      | 9.3.7  | 転送回数                  | 9-33  |

|      | 9.3.8  | アドレス空間                | 9-34  |

|      | 9.3.9  | 転送動作                  | 9-34  |

|      | 9.3.10 | DMA の終了と割り込み          | 9-37  |

|      | 9.3.11 | DMA 転送終了後の各レジスタの状態    | 9-37  |

| 9.4  | DMAC 0 | )注意事項                 | 9-38  |

| 第 10 | 章マ     | 'ルチジャンクションタイマ         |       |

| 10.1 | マルチ    | ジャンクションタイマ概要          | 10-2  |

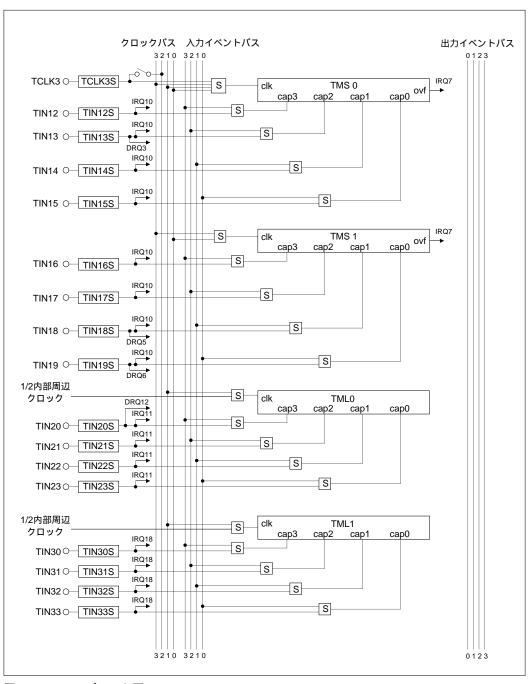

| 10.2 | タイマ    | 共通部                   | 10-9  |

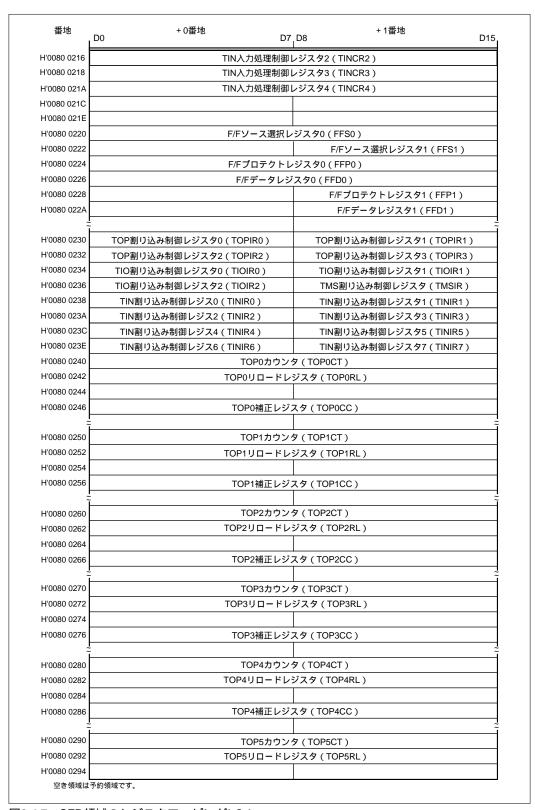

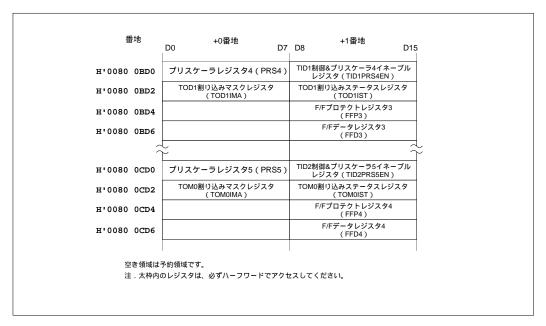

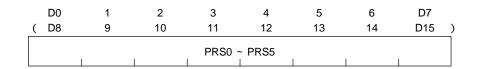

|      | 10.2.1 | タイマ共通部レジスタマップ         | 10-9  |

|      | 10.2.2 | プリスケーラ部               | 10-12 |

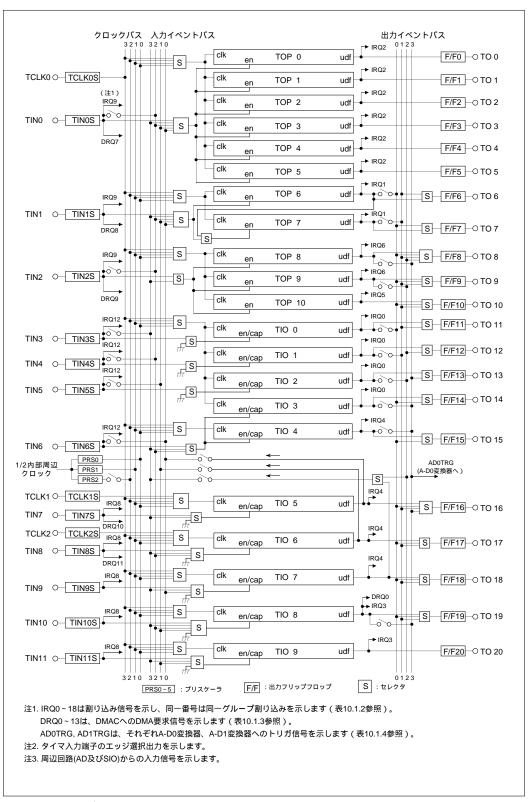

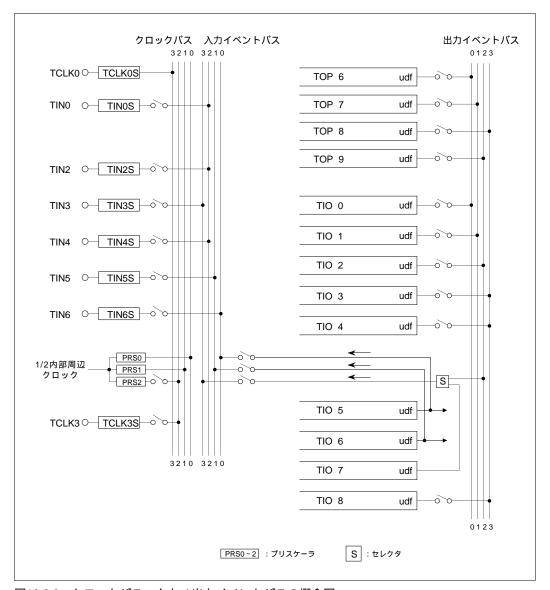

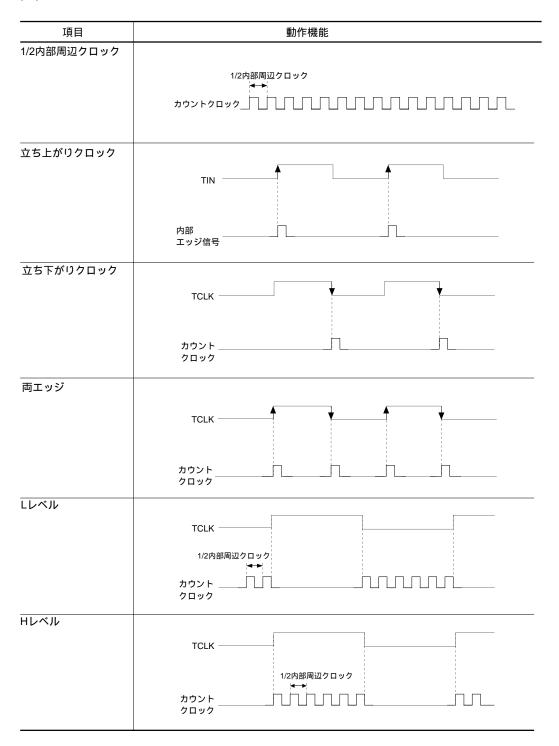

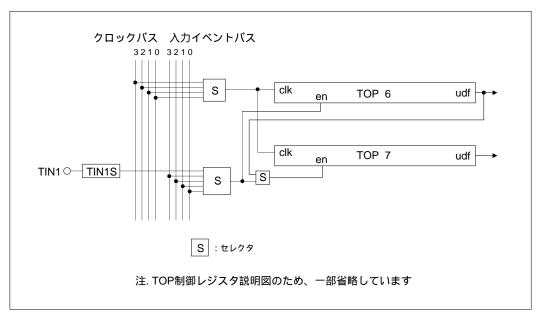

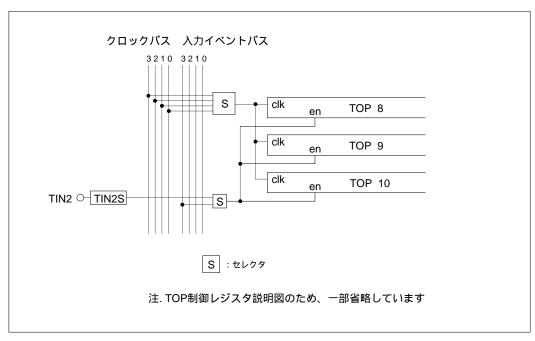

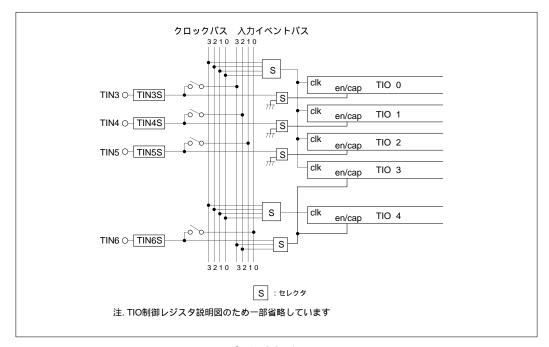

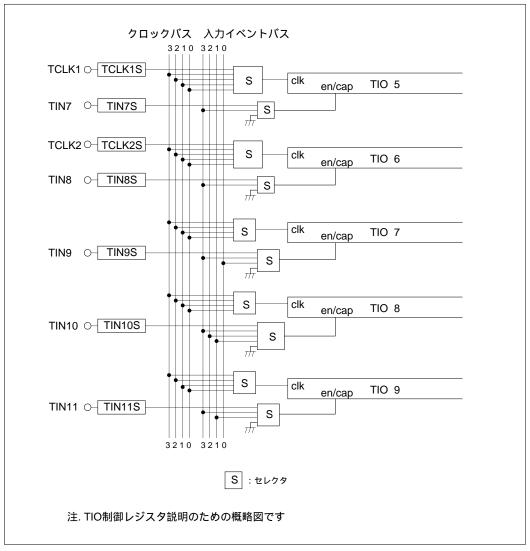

|      | 10.2.3 | クロックバス / 入出力イベントバス制御部 | 10-13 |

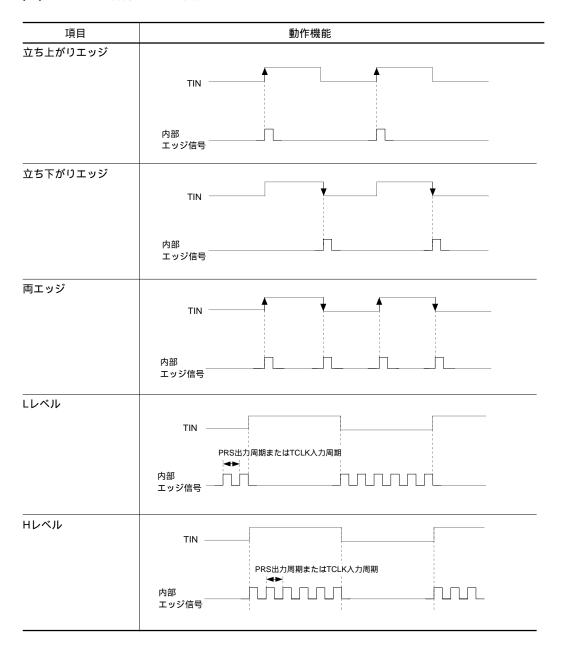

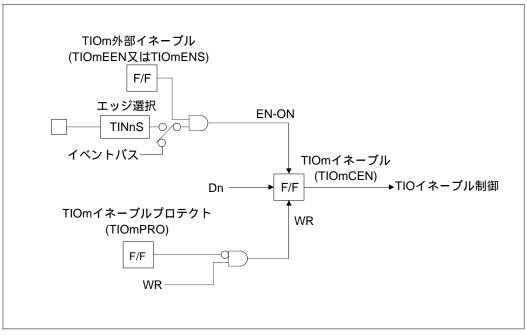

|      | 10.2.4 | 入力処理制御部               | 10-18 |

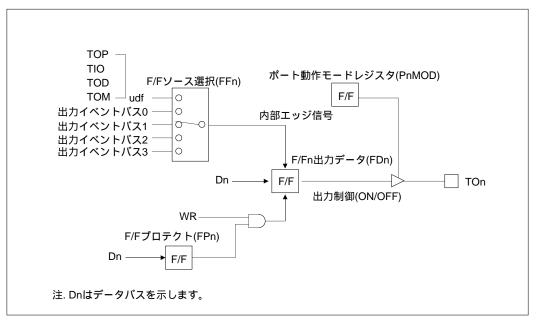

|      | 10.2.5 | 出力フリップフロップ制御部         | 10-26 |

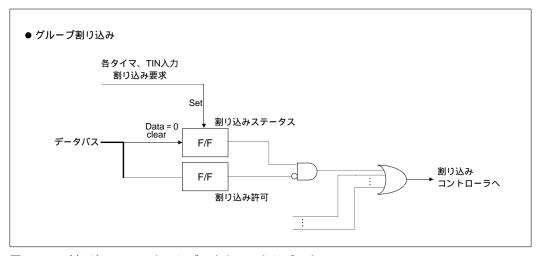

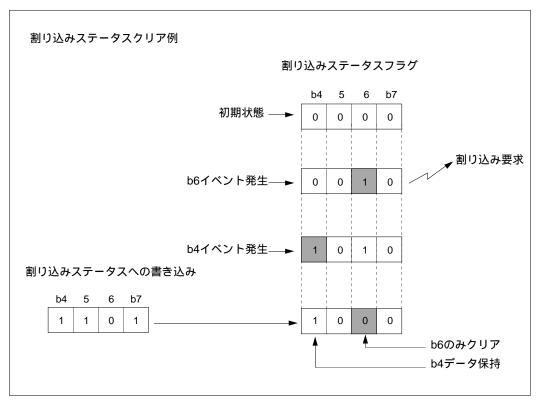

|      | 10.2.6 | 割り込み制御部               | 10-37 |

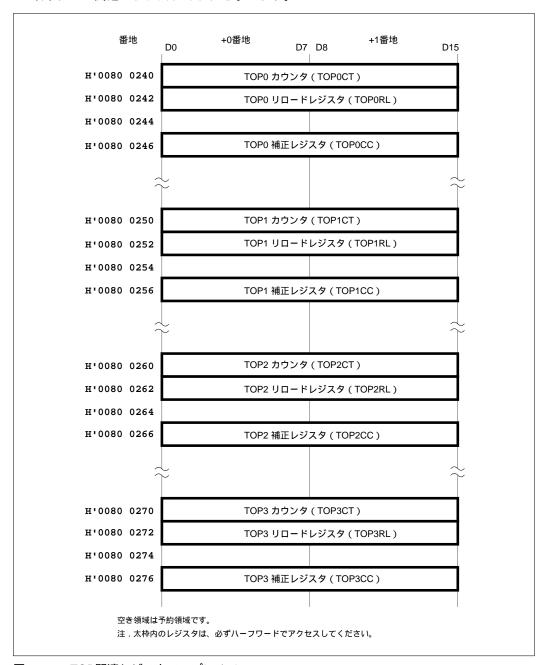

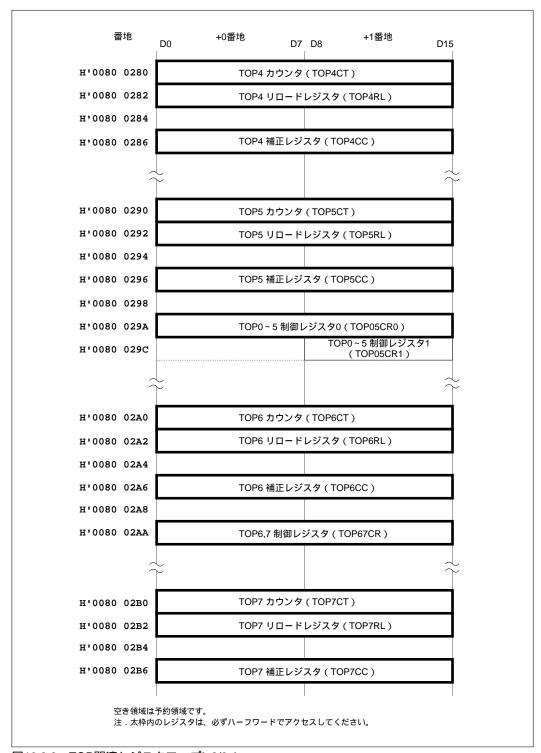

| 10.3 | TOP ( H | 台力系 16 ビットタイマ )                           | 10-63  |

|------|---------|-------------------------------------------|--------|

|      | 10.3.1  | TOP 概要                                    | 10-63  |

|      | 10.3.2  | TOP 各モードの概要                               | 10-65  |

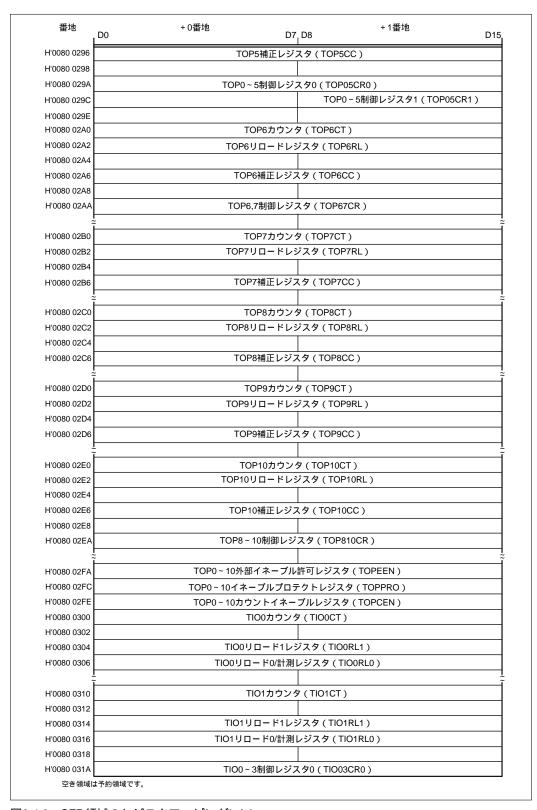

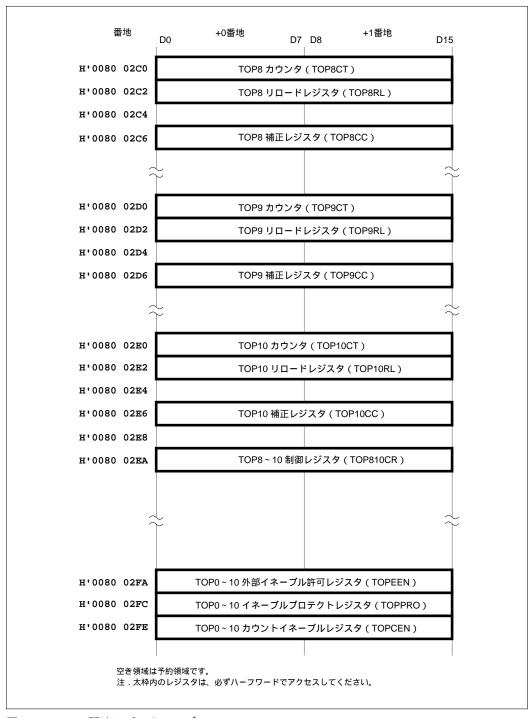

|      | 10.3.3  | TOP 関連レジスタマップ                             | 10-67  |

|      | 10.3.4  | TOP 制御レジスタ                                | 10-70  |

|      | 10.3.5  | TOP カウンタ ( TOP0CT ~ TOP10CT )             | 10-77  |

|      | 10.3.6  | TOP リロードレジスタ (TOP0RL ~ TOP10RL)           | 10-78  |

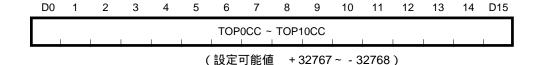

|      | 10.3.7  | TOP 補正レジスタ ( TOP0CC ~ TOP10CC )           | 10-79  |

|      | 10.3.8  | TOP イネーブル制御レジスタ                           | 10-80  |

|      | 10.3.9  | TOP ワンショット出力モード(補正機能あり)の動作                | 10-84  |

|      | 10.3.10 | TOP ディレイドワンショット出力モード(補正機能あり)の動作           | 10-91  |

|      | 10.3.11 | TOP 連続出力モード(補正機能なし)の動作                    | 10-96  |

| 10.4 | TIO(入   | 出力系 16 ビットタイマ )                           | 10-100 |

|      | 10.4.1  | TIO 概要                                    | 10-100 |

|      | 10.4.2  | TIO 各モードの概要                               | 10-102 |

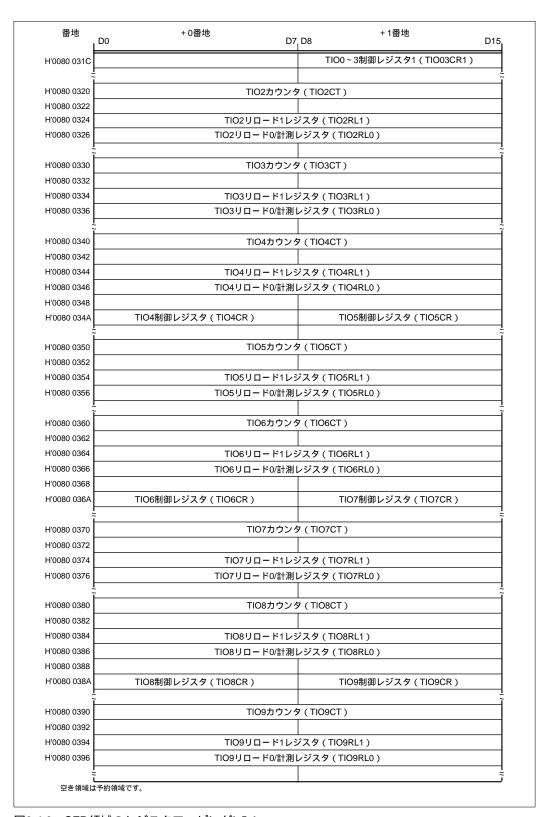

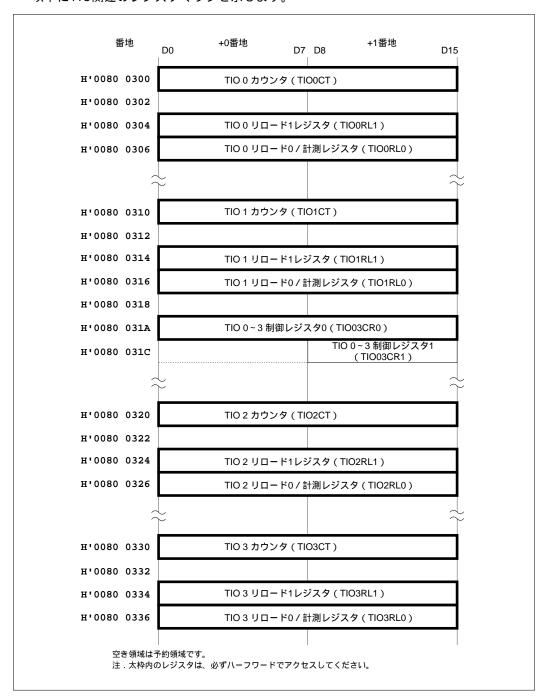

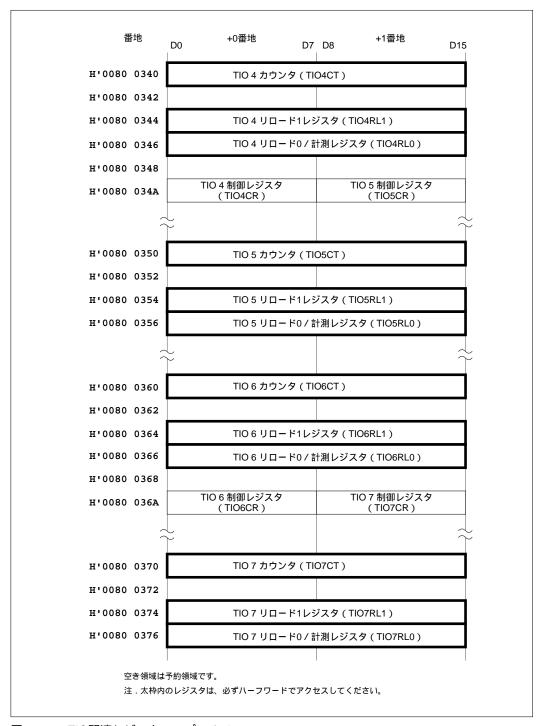

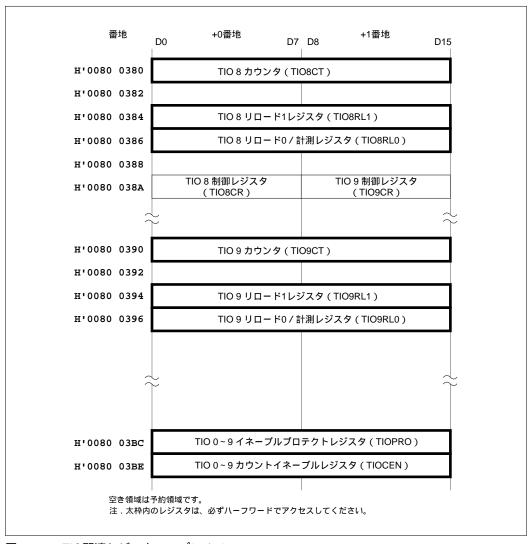

|      | 10.4.3  | TIO 関連レジスタマップ                             | 10-105 |

|      | 10.4.4  | TIO 制御レジスタ                                | 10-108 |

|      | 10.4.5  | TIO カウンタ ( TIO0CT ~ TIO9CT )              | 10-119 |

|      | 10.4.6  | TIO リロード 0 / 計測レジスタ ( TIOORL0 ~ TIO9RL0 ) | 10-120 |

|      | 10.4.7  | TIO リロード 1 レジスタ ( TIO0RL1 ~ TIO9RL1 )     | 10-121 |

|      | 10.4.8  | TIO イネーブル制御レジスタ                           | 10-122 |

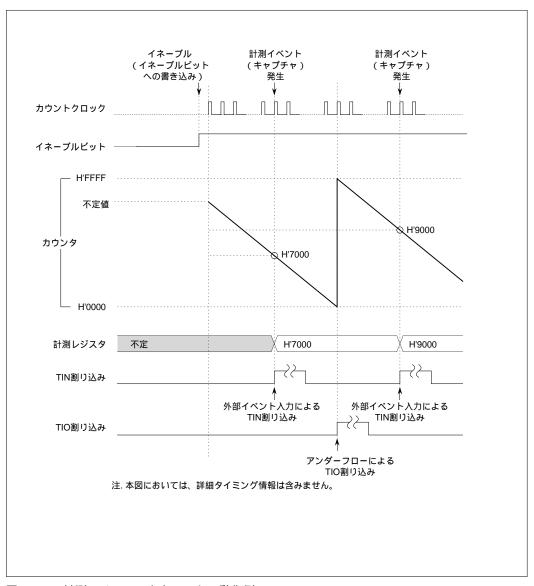

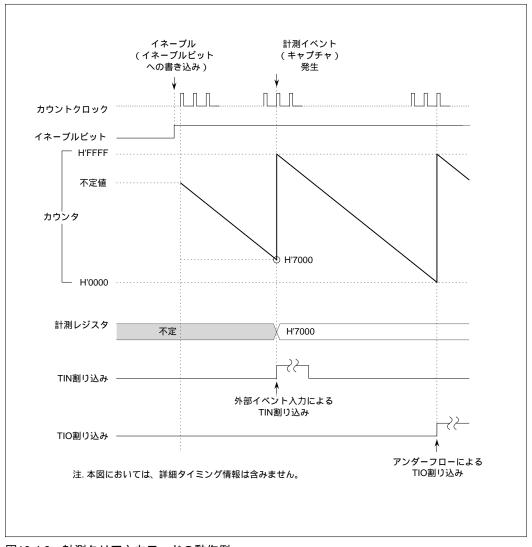

|      | 10.4.9  | TIO 計測(フリーラン / クリア)入力モードの動作               | 10-125 |

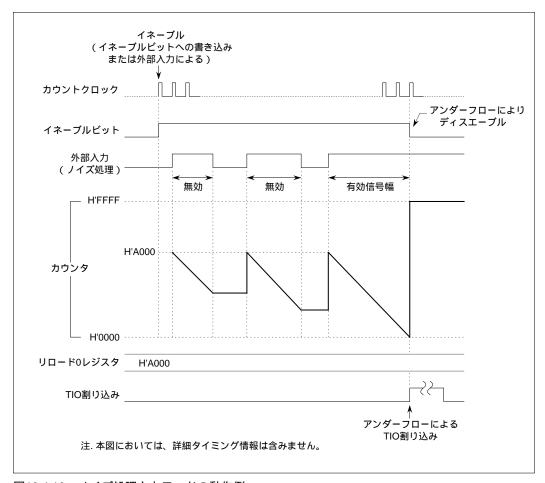

|      | 10.4.10 | TIO ノイズ処理入力モードの動作                         | 10-129 |

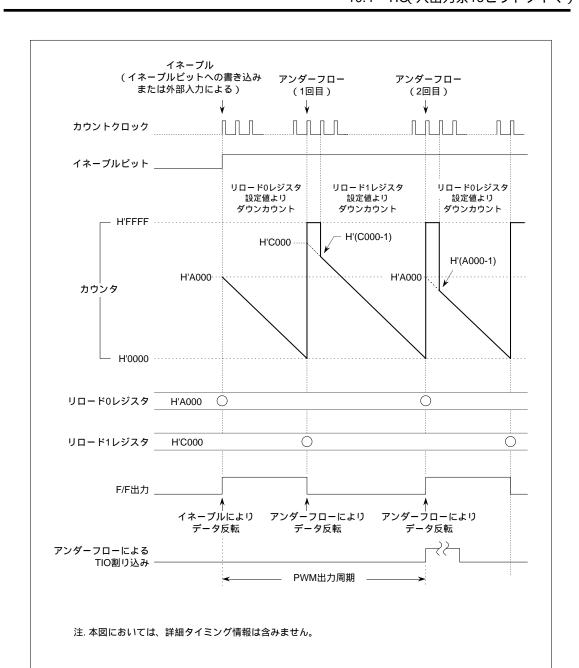

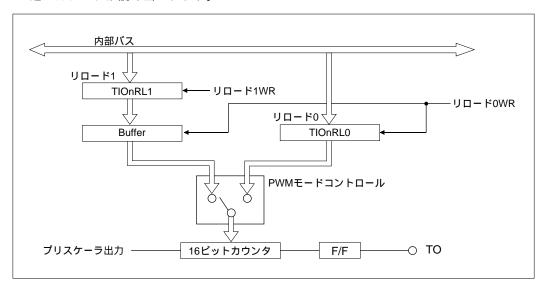

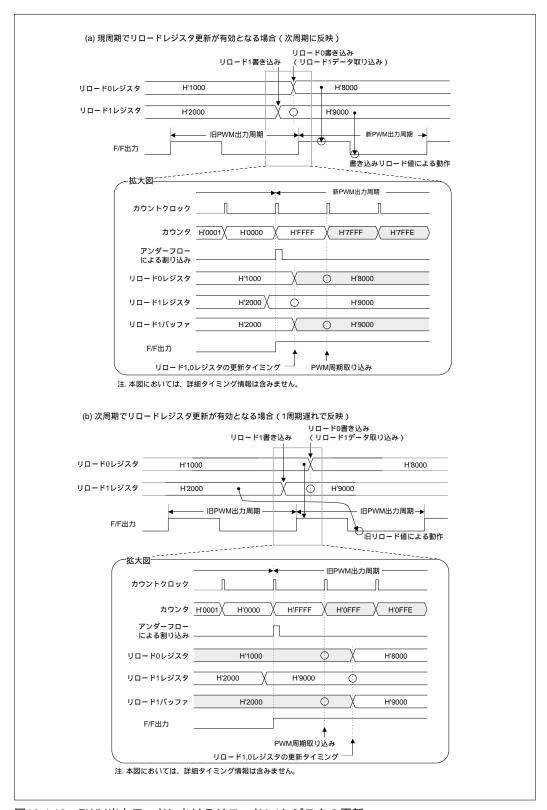

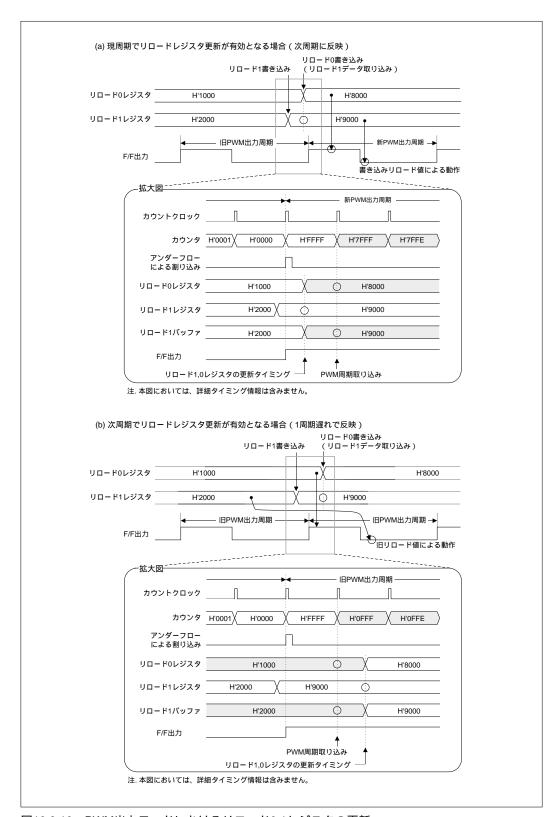

|      | 10.4.11 | TIO PWM 出力モード動作                           | 10-130 |

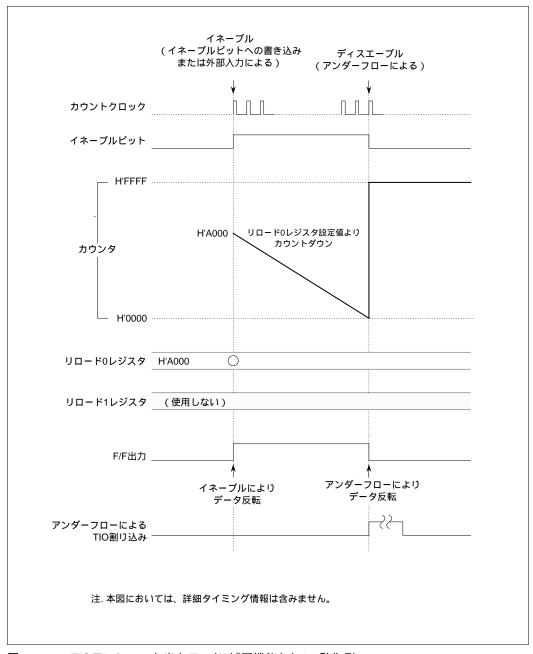

|      | 10.4.12 | TIO ワンショット出力モード(補正機能なし)の動作                | 10-134 |

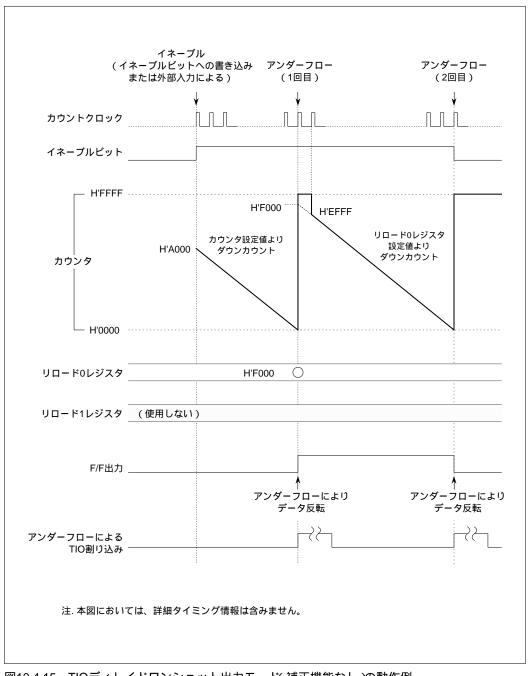

|      | 10.4.13 | TIO ディレイドワンショット出力モード(補正機能なし)の動作           | 10-136 |

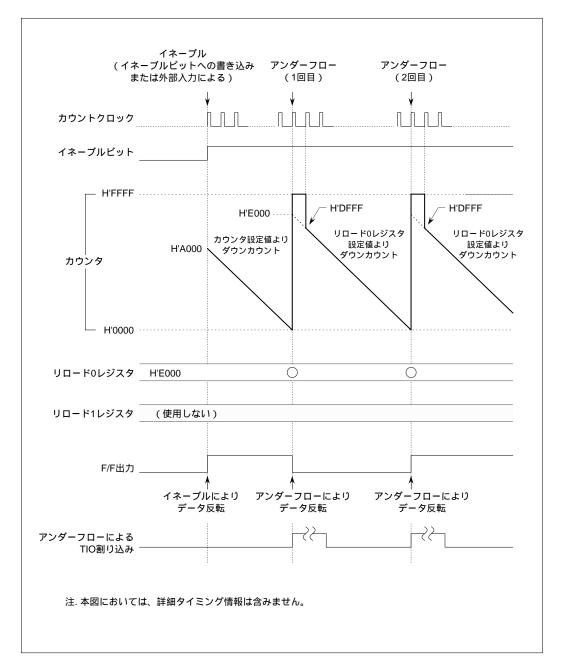

|      | 10.4.14 | TIO 連続出力モード(補正機能なし)の動作                    | 10-138 |

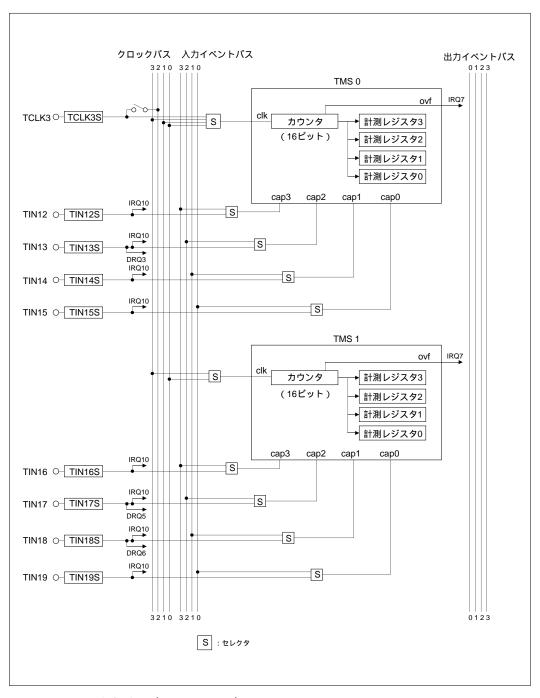

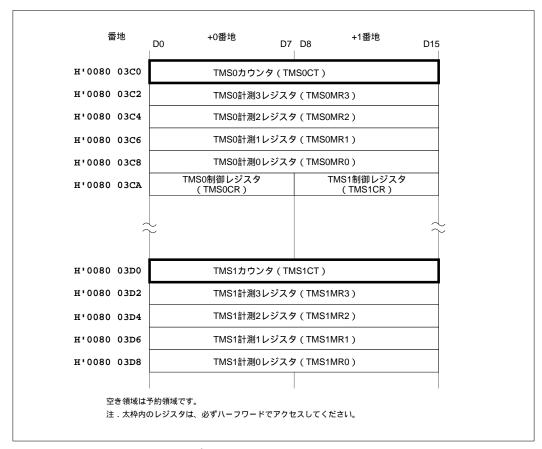

| 10.5 | TMS()   | ∖力系 16 ビットタイマ )                           | 10-140 |

|      | 10.5.1  | TMS 概要                                    | 10-140 |

|      | 10.5.2  | TMS の動作概要                                 | 10-140 |

|      | 10.5.3  | TMS 関連レジスタマップ                             | 10-142 |

|      | 10.5.4  | TMS 制御レジスタ                                | 10-143 |

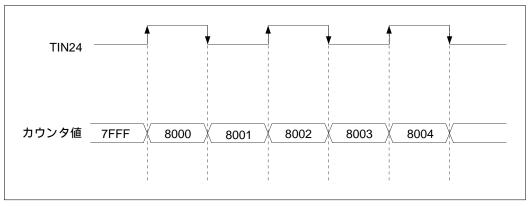

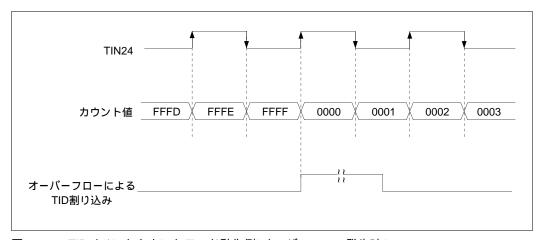

|      | 10.5.5  | TMS カウンタ(TMS0CT, TMS1CT)                  | 10-145 |

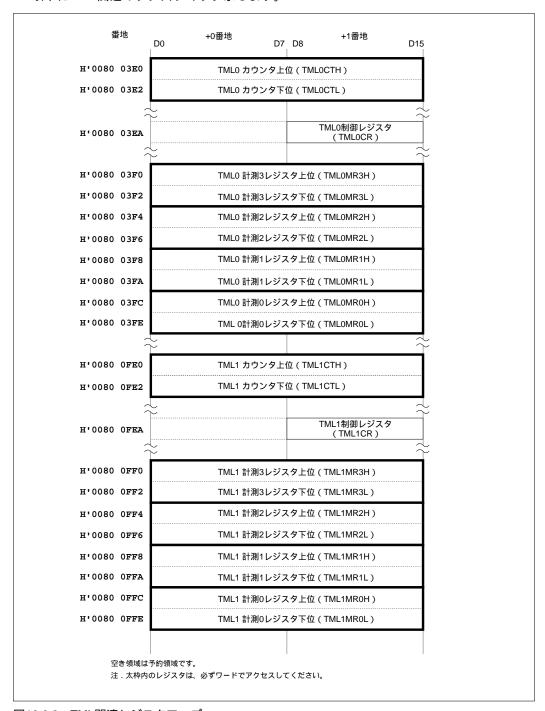

|      | 10.5.6  | TMS 計測レジスタ(TMS0MR3 ~ 0 , TMS1MR3 ~ 0 )    | 10-146 |

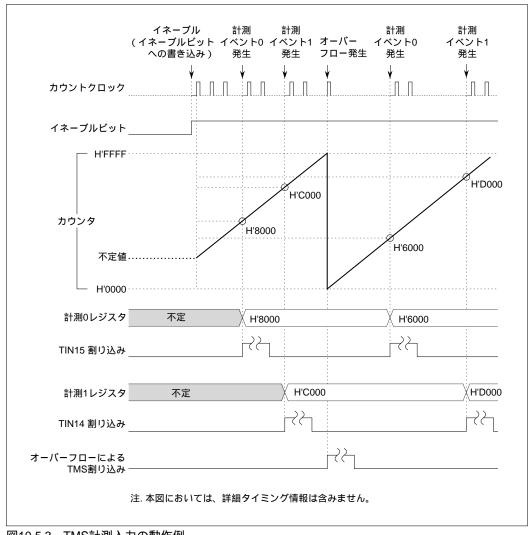

|      | 10.5.7  | TMS 計測入力の動作                               | 10-147 |

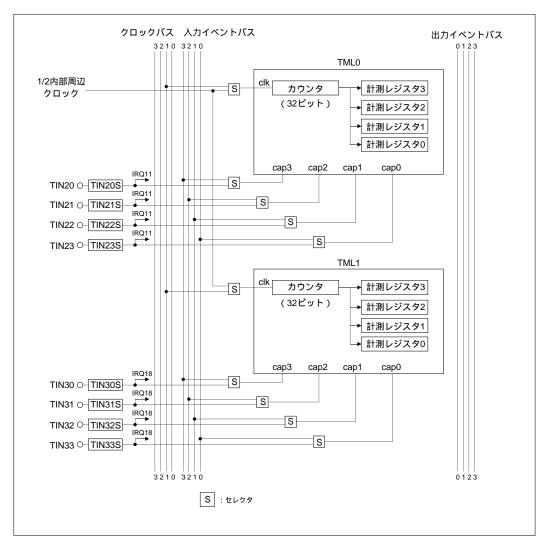

| 10.6 | TML()   | ∖力系 32 ビットタイマ )                       | 10-149 |

|------|---------|---------------------------------------|--------|

|      | 10.6.1  | TML 概要                                | 10-149 |

|      | 10.6.2  | TML の動作概要                             | 10-150 |

|      | 10.6.3  | TML 関連レジスタマップ                         | 10-151 |

|      | 10.6.4  | TML 制御レジスタ                            | 10-152 |

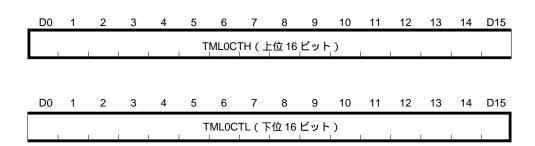

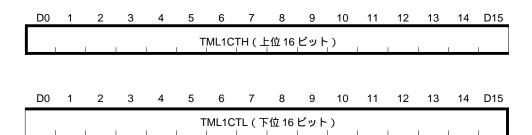

|      | 10.6.5  | TML カウンタ                              | 10-154 |

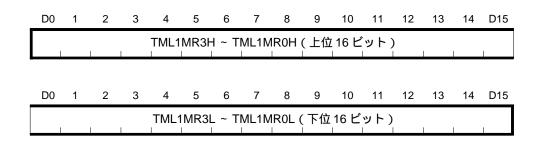

|      | 10.6.6  | TML 計測レジスタ                            | 10-156 |

|      | 10.6.7  | TML 計測入力の動作                           | 10-158 |

| 10.7 | TID(入   | 力系 16 ビットタイマ )                        | 10-160 |

|      | 10.7.1  | TID 概要                                | 10-160 |

|      | 10.7.2  | TID 関連レジスタマップ                         | 10-162 |

|      | 10.7.3  | TID 制御&プリスケーライネーブルレジスタ                | 10-163 |

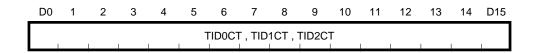

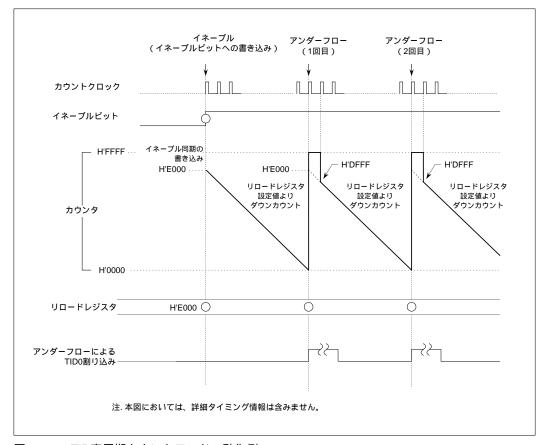

|      | 10.7.4  | TID カウンタ ( TID0CT, TID1CT, TID2CT )   | 10-166 |

|      | 10.7.5  | TID リロードレジスタ (TIDORL, TID1RL, TID2RL) | 10-167 |

|      | 10.7.6  | TID 各モードの概略                           | 10-168 |

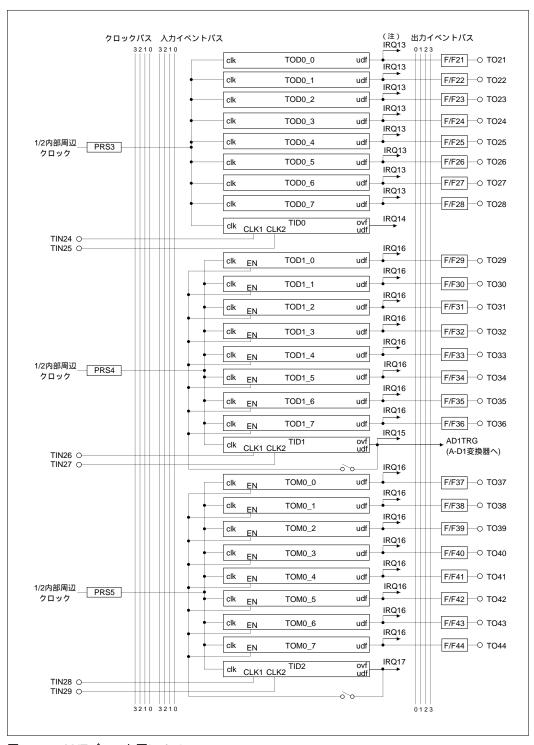

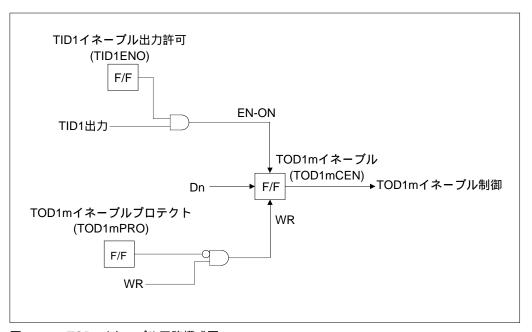

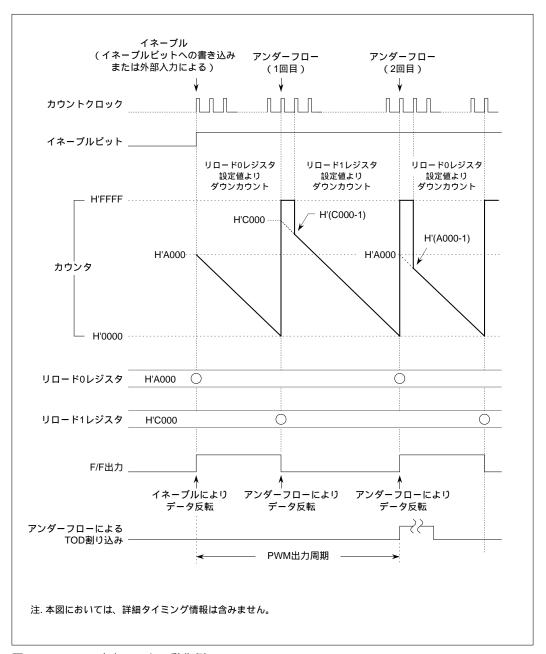

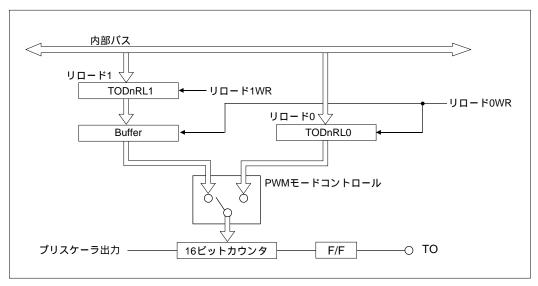

| 10.8 | TOD ( E | 出力系 16 ビットタイマ )                       | 10-173 |

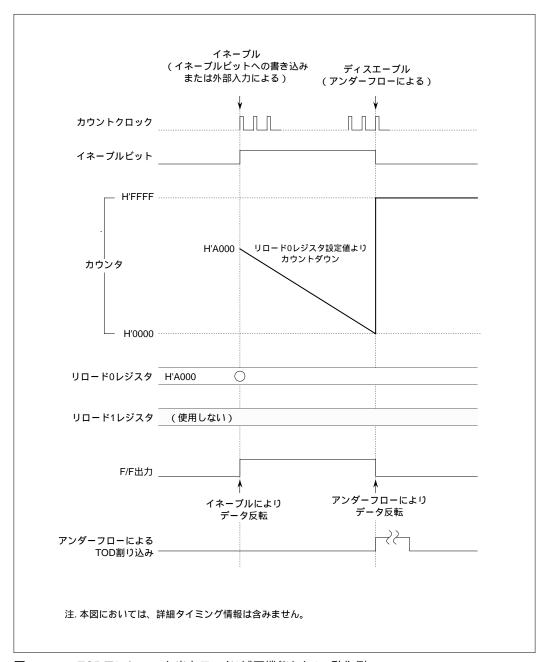

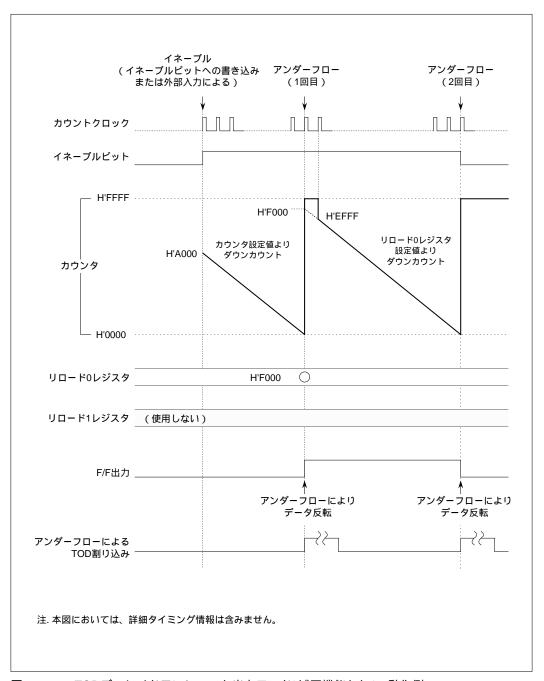

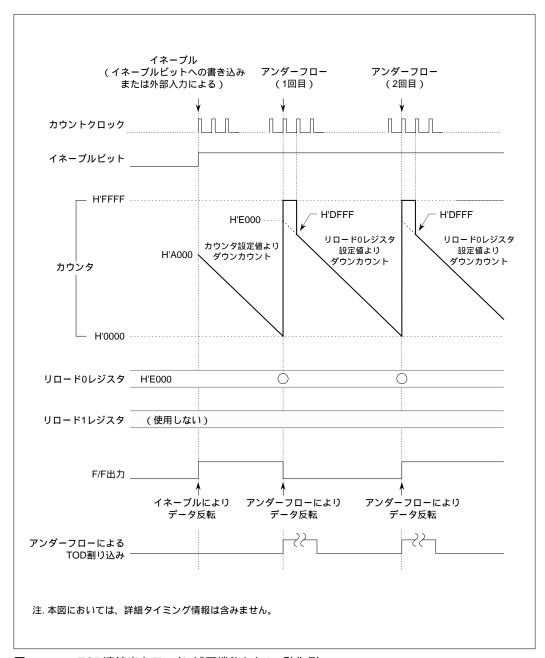

|      | 10.8.1  | TOD 概要                                | 10-173 |

|      | 10.8.2  | TOD 各モードの概要                           | 10-175 |

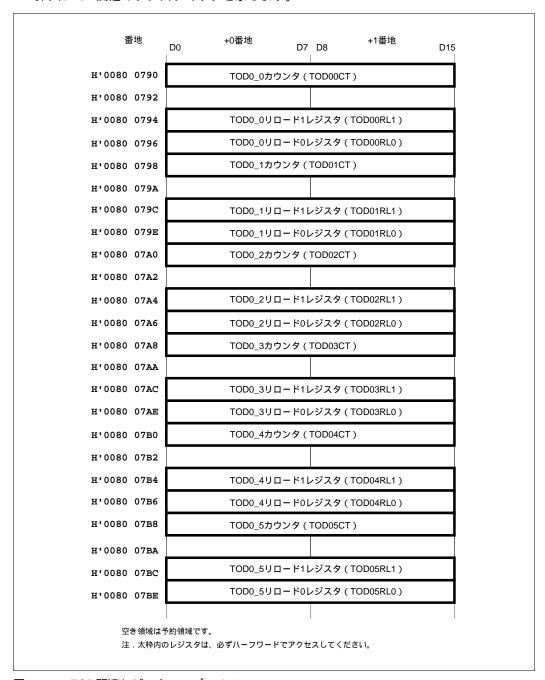

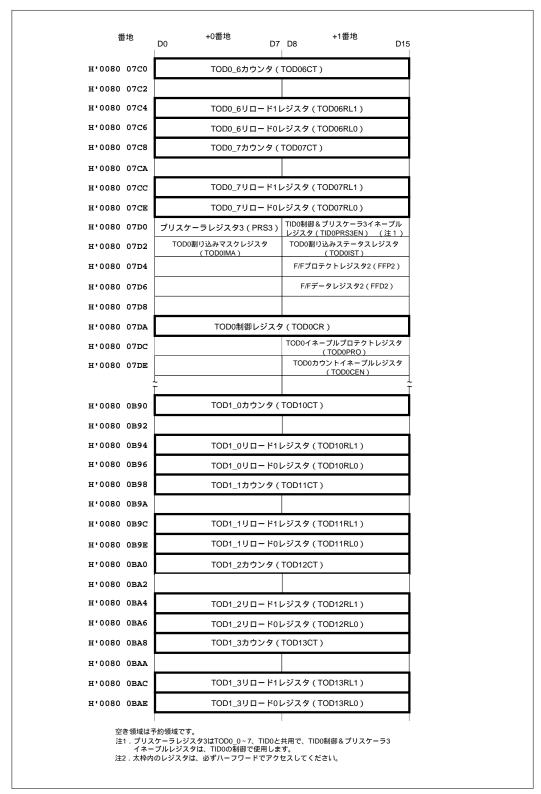

|      | 10.8.3  | TOD 関連レジスタマップ                         | 10-177 |

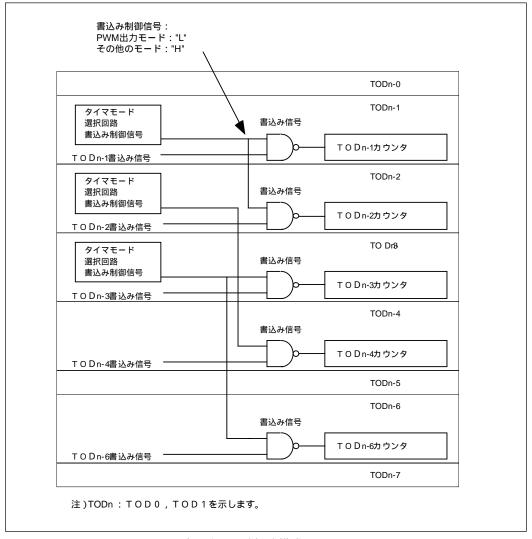

|      | 10.8.4  | TOD 制御レジスタ                            | 10-180 |

|      | 10.8.5  | TOD カウンタ                              | 10-182 |

|      | 10.8.6  | TOD リロード 0 レジスタ                       | 10-186 |

|      | 10.8.7  | TOD リロード 1 レジスタ                       | 10-188 |

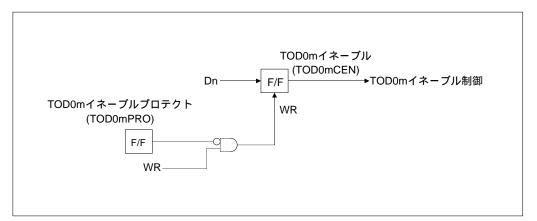

|      | 10.8.8  | TOD イネーブルプロテクトレジスタ                    | 10-190 |

|      | 10.8.9  | TOD カウントイネーブルレジスタ                     | 10-192 |

|      | 10.8.10 | TOD PWM 出力モード動作                       | 10-195 |

|      | 10.8.11 | TOD ワンショット出力モード(補正機能なし)の動作            | 10-199 |

|      | 10.8.12 | TOD ディレイドワンショット出力モード(補正機能なし)の動作       | 10-201 |

|      | 10.8.13 | TOD 連続出力モード(補正機能なし)の動作                | 10-203 |

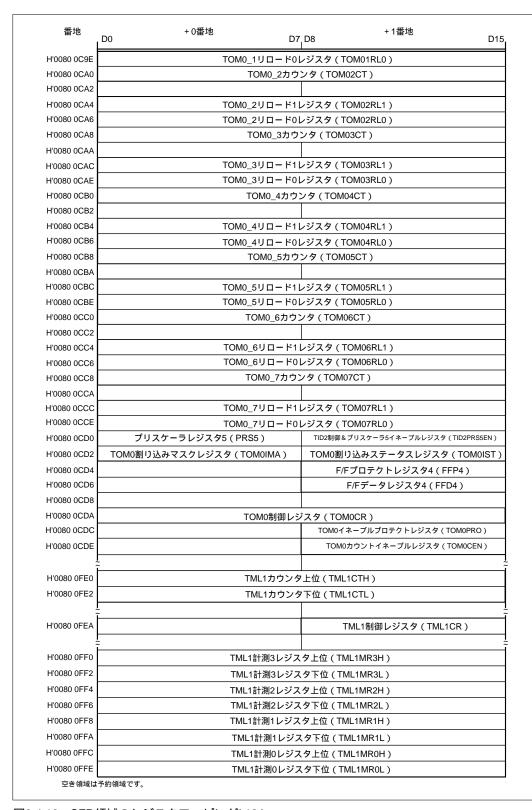

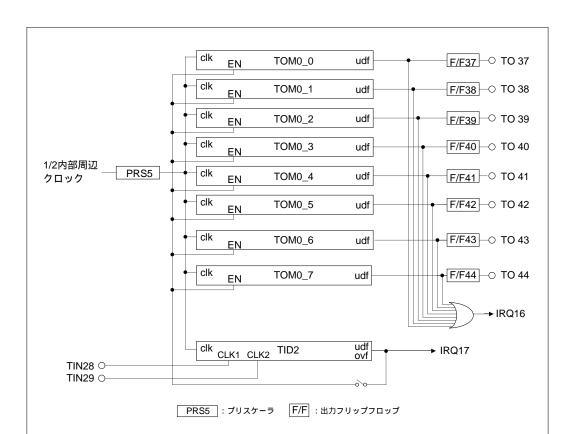

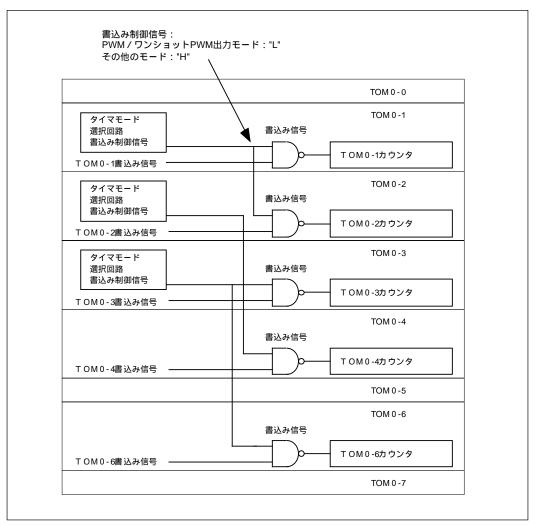

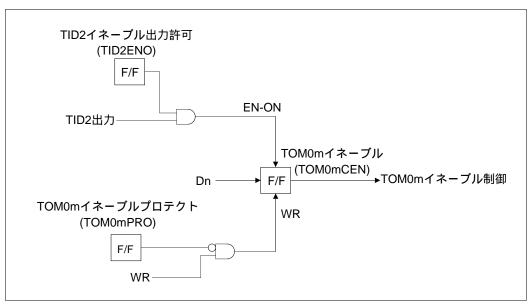

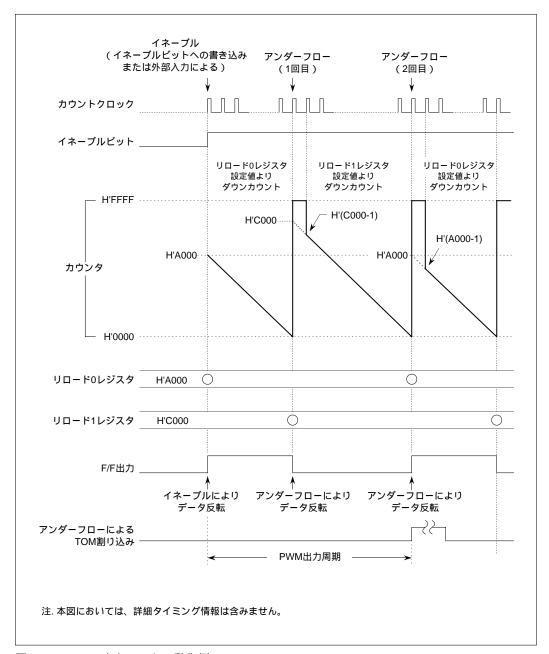

| 10.9 | TOM ( L | 出力系 16 ビットタイマ )                       | 10-205 |

|      | 10.9.1  | TOM 概要                                | 10-205 |

|      | 10.9.2  | TOM 各モードの概要                           | 10-207 |

|      | 10.9.3  | TOM 関連レジスタマップ                         | 10-209 |

|      | 10.9.4  | TOM 制御レジスタ                            | 10-211 |

|      | 10.9.5  | TOM カウンタ                              | 10-212 |

|      | 10.9.6  | TOM リロード 0 レジスタ                       | 10-215 |

|             | 10.9.7  | TOM リロード 1 レジスタ                 | 10-216 |

|-------------|---------|---------------------------------|--------|

|             | 10.9.8  | TOM イネーブルプロテクトレジスタ              | 10-217 |

|             | 10.9.9  | TOM カウントイネーブルレジスタ               | 10-218 |

|             | 10.9.10 | TOM PWM 出力モード動作                 | 10-220 |

|             | 10.9.11 | TOM ワンショット出力モード(補正機能なし)の動作      | 10-224 |

|             | 10.9.12 | TOM ワンショット PWM 出力モード(補正機能なし)の動作 | 10-226 |

|             | 10.9.13 | TOM 連続出力モード(補正機能なし)の動作          | 10-228 |

|             | 10.9.14 | 32170 モータ制御機能への応用例              | 10-230 |

|             |         |                                 |        |

| 第11         | 章 A-l   | D变换器                            |        |

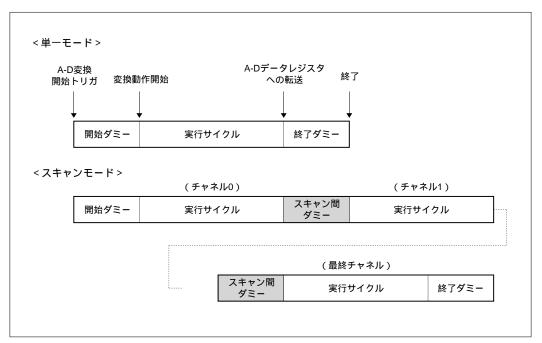

| 11.1        | A-D 変換  | eastage                         | 11-2   |

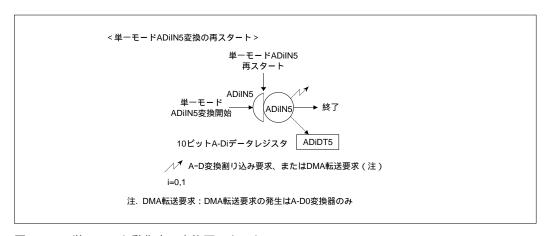

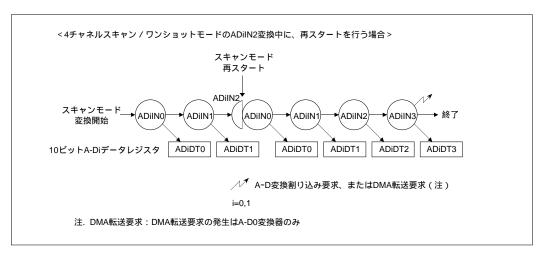

|             | 11.1.1  | 変換モード                           | 11-6   |

|             | 11.1.2  | 動作モード                           | 11-7   |

|             | 11.1.3  | 特殊動作モード                         | 11-11  |

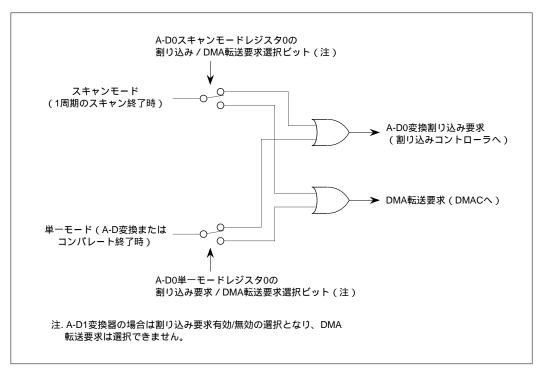

|             | 11.1.4  | A-D 変換器の割り込み要求と DMA 転送要求        | 11-14  |

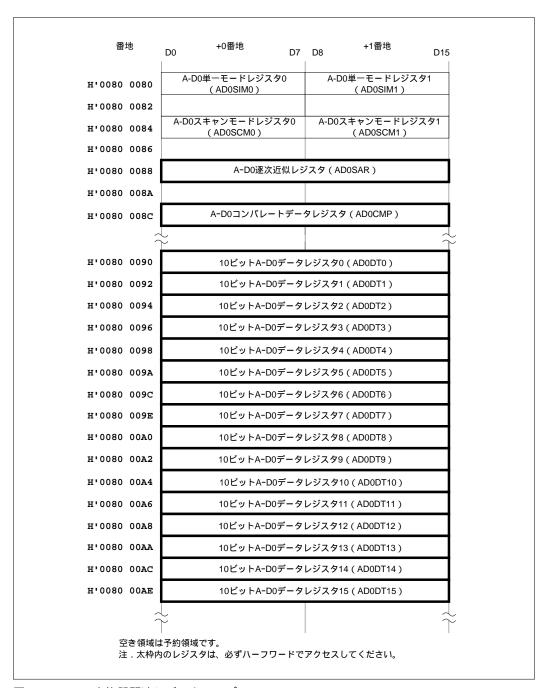

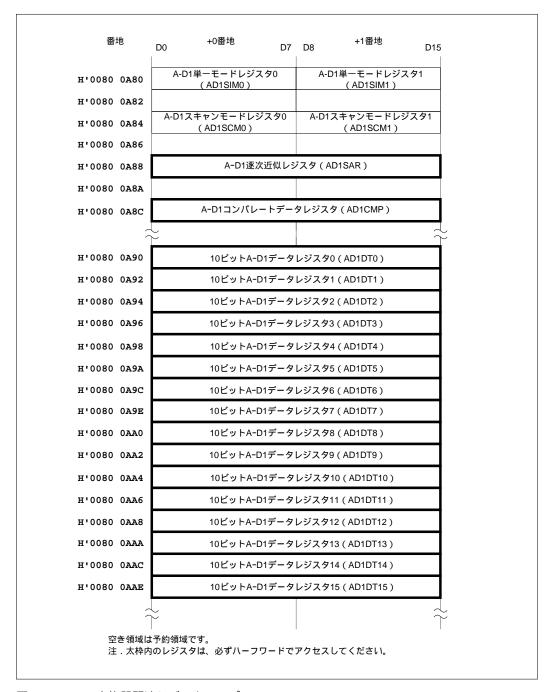

| 11.2        | A-D 変換  | e器関連レジスタ                        | 11-15  |

|             | 11.2.1  | A-D 単一モードレジスタ 0                 | 11-19  |

|             | 11.2.2  | A-D 単一モードレジスタ 1                 | 11-23  |

|             | 11.2.3  | A-D スキャンモードレジスタ 0               | 11-26  |

|             | 11.2.4  | A-D スキャンモードレジスタ 1               | 11-30  |

|             | 11.2.5  | A-D 逐次近似レジスタ                    | 11-33  |

|             | 11.2.6  | A-D コンパレートデータレジスタ               | 11-35  |

|             | 11.2.7  | 10 ビット A-D データレジスタ              | 11-37  |

|             | 11.2.8  | 8 ビット A-D データレジスタ               | 11-39  |

| 11.3        | A-D 変換  | ⊉器機能説明                          | 11-41  |

|             | 11.3.1  | アナログ入力電圧の求め方                    | 11-41  |

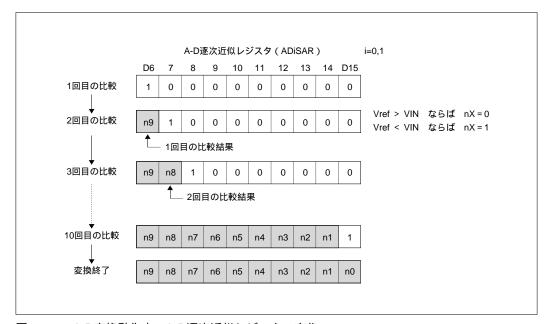

|             | 11.3.2  | 逐次近似比較方式の A-D 変換                | 11-42  |

|             | 11.3.3  | コンパレータ動作                        | 11-44  |

|             | 11.3.4  | A-D 变换時間算出方法                    | 11-45  |

|             | 11.3.5  | A-D 変換精度の定義                     | 11-48  |

| 11.4        | A-D 変換  | 韓器の注意事項                         | 11-50  |

| 笠 4.0       | · ·     |                                 |        |

| <b>第Ⅰ</b> 2 | 早 ン     | リアル //O                         |        |

| 12.1        | シリアル    | レI/O 概要                         | 12-2   |

| 12.2 | シリアル              | レI/O 関連レジスタ        | 12-6  |

|------|-------------------|--------------------|-------|

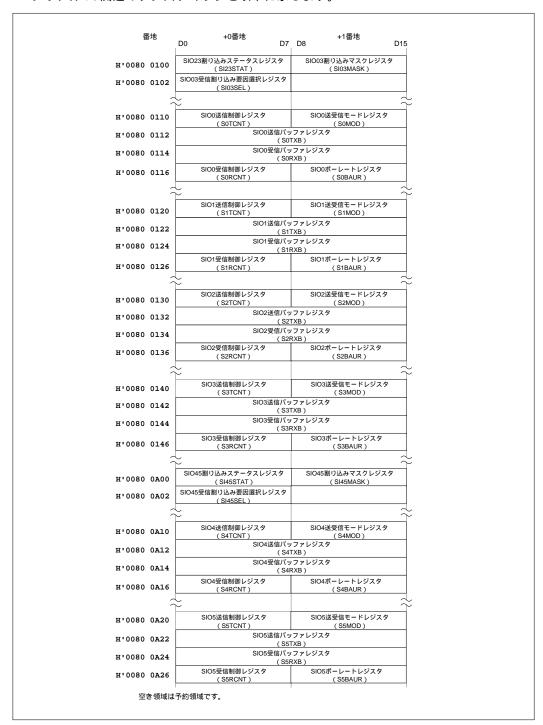

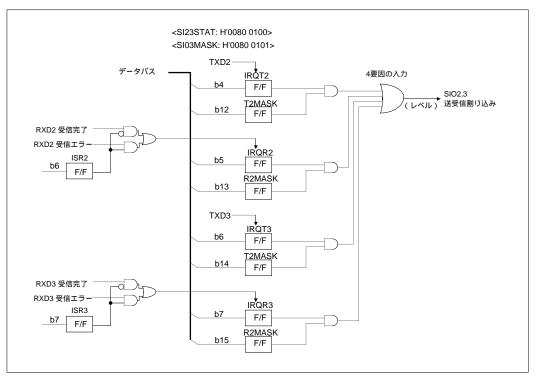

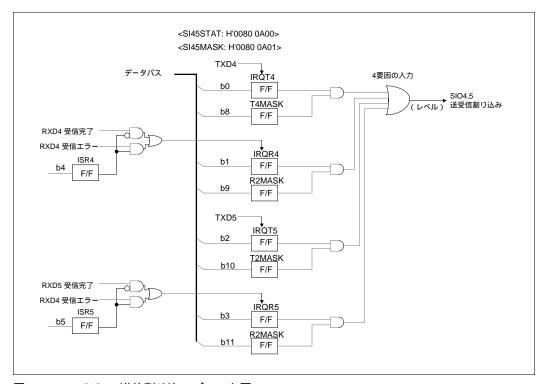

|      | 12.2.1            | SIO 割り込み関連レジスタ     | 12-7  |

|      | 12.2.2            | SIO 割り込み制御レジスタ     | 12-9  |

|      | 12.2.3            | SIO 送信制御レジスタ       | 12-16 |

|      | 12.2.4            | SIO 送受信モードレジスタ     | 12-18 |

|      | 12.2.5            | SIO 送信バッファレジスタ     | 12-21 |

|      | 12.2.6            | SIO 受信バッファレジスタ     | 12-22 |

|      | 12.2.7            | SIO 受信制御レジスタ       | 12-23 |

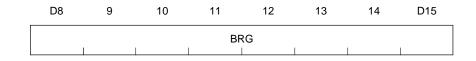

|      | 12.2.8            | SIO ボーレートレジスタ      | 12-26 |

| 12.3 | CSIO ₹            | :ード送信動作説明          | 12-28 |

|      | 12.3.1            | CSIO ボーレートの設定      | 12-28 |

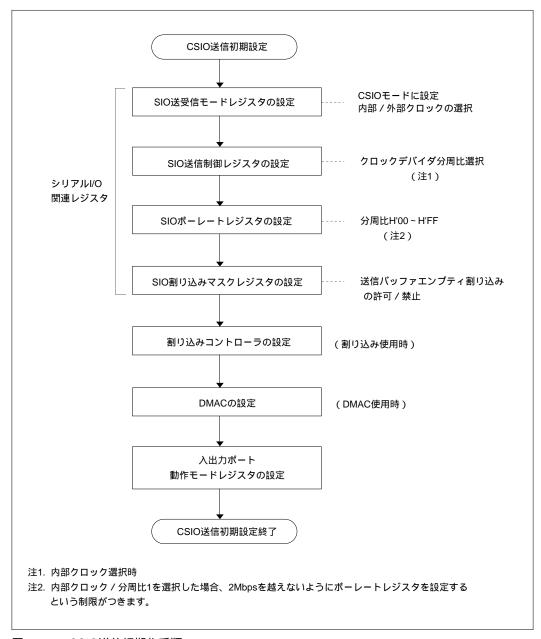

|      | 12.3.2            | CSIO 送信時の初期設定      | 12-29 |

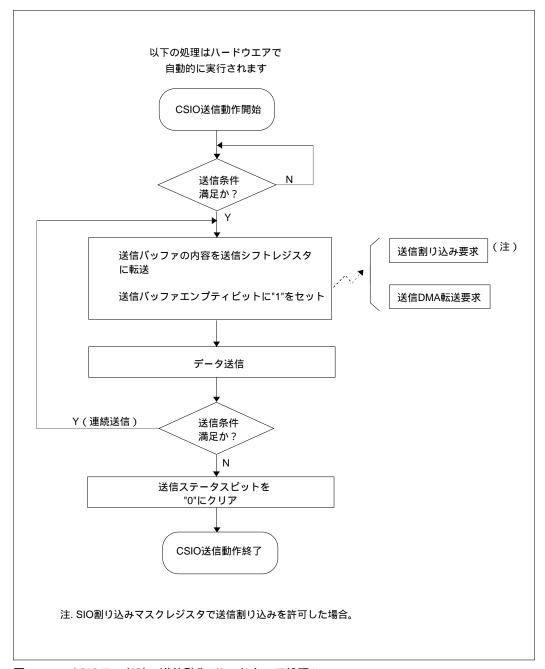

|      | 12.3.3            | CSIO 送信の開始         | 12-31 |

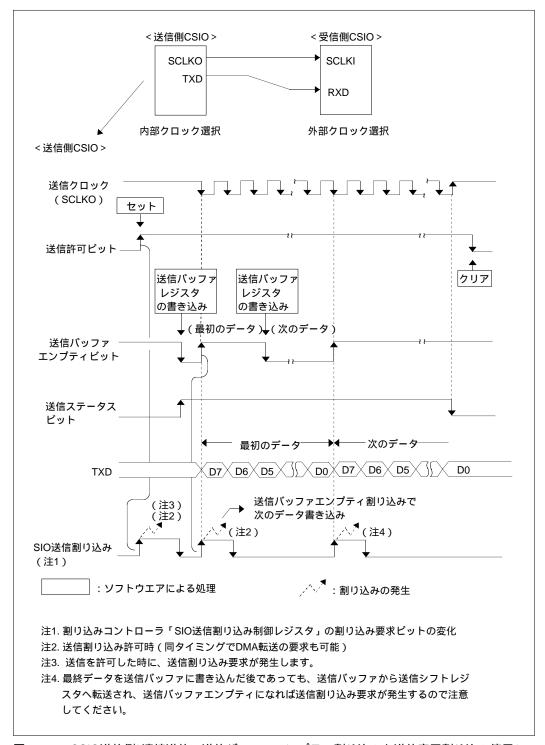

|      | 12.3.4            | CSIO の連続送信         | 12-31 |

|      | 12.3.5            | CSIO 送信完了処理        | 12-32 |

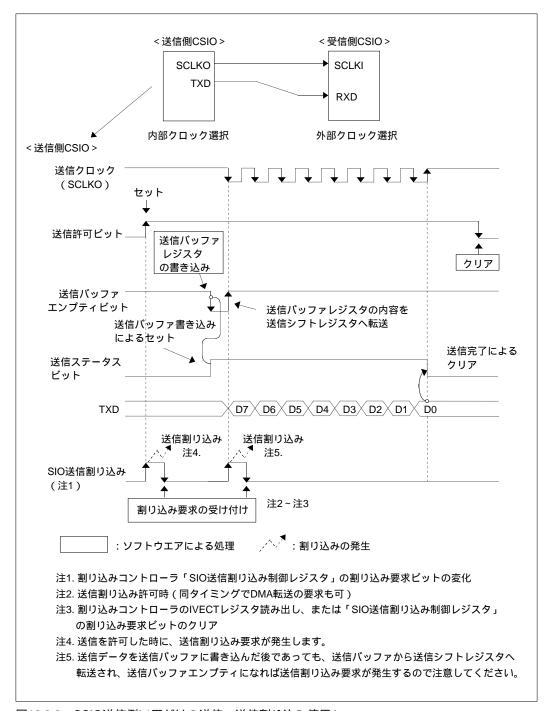

|      | 12.3.6            | 送信割り込み             | 12-32 |

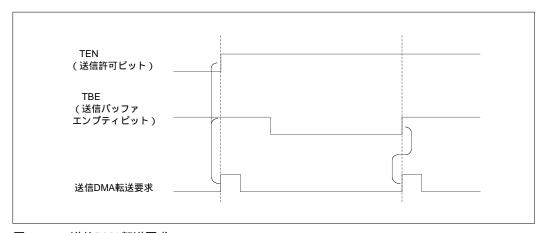

|      | 12.3.7            | 送信 DMA 転送要求        | 12-32 |

|      | 12.3.8            | CSIO 送信動作例         | 12-34 |

| 12.4 | CSIO E            | :ード受信動作説明          | 12-36 |

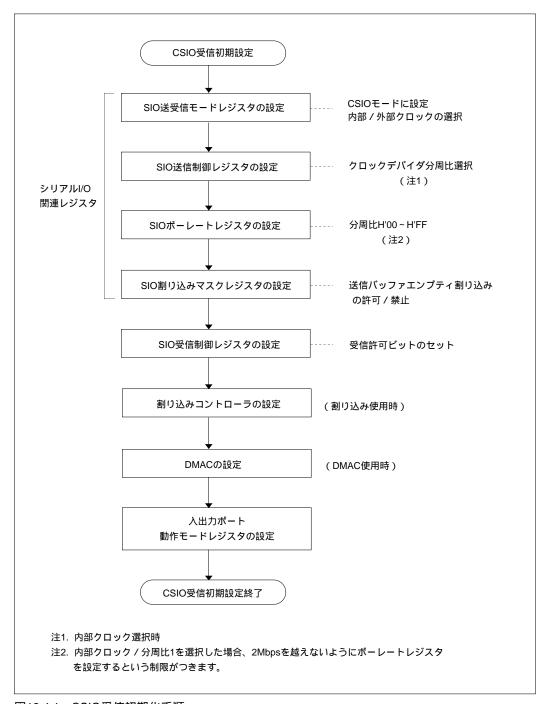

|      | 12.4.1            | CSIO 受信時の初期設定      | 12-36 |

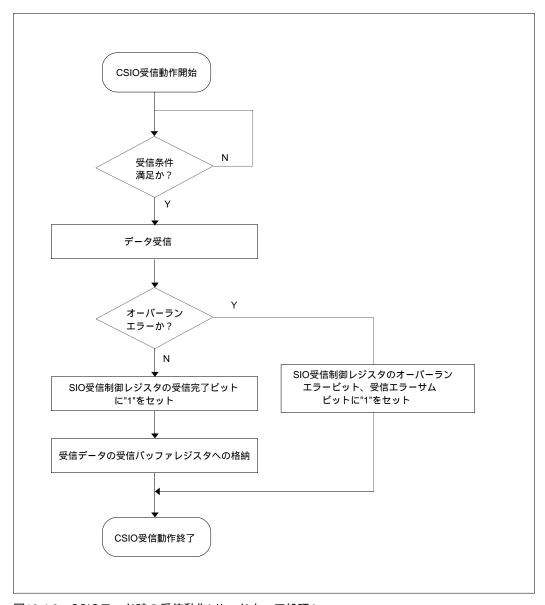

|      | 12.4.2            | CSIO 受信の開始         | 12-38 |

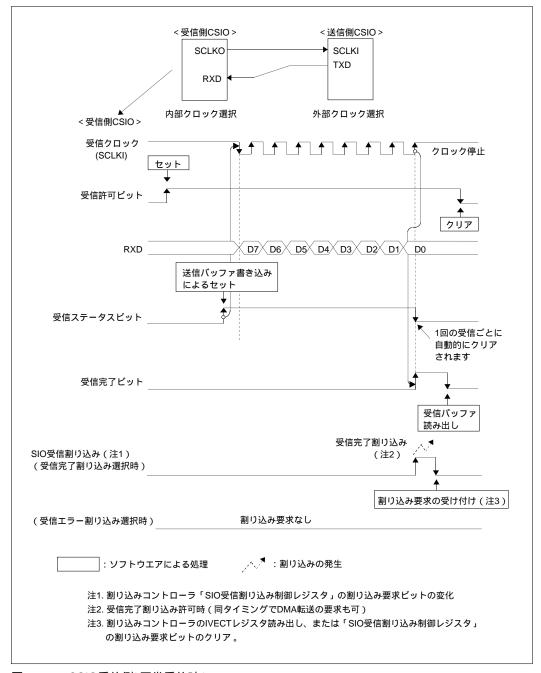

|      | 12.4.3            | CSIO 受信完了処理        | 12-38 |

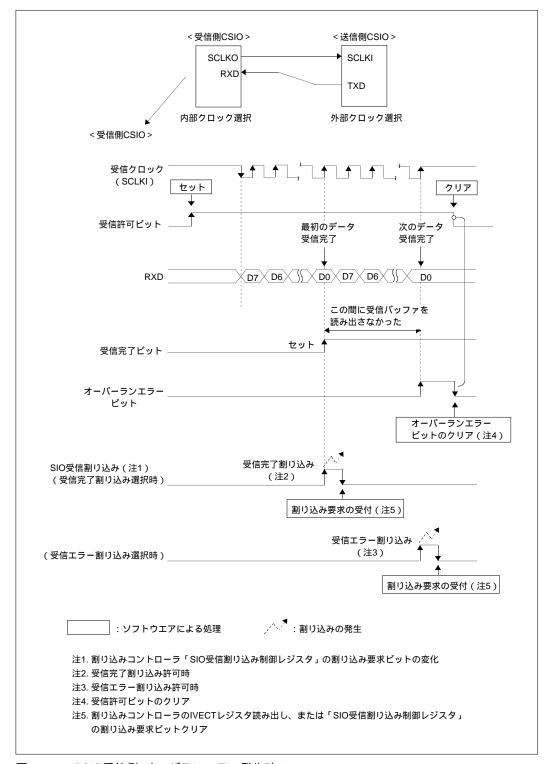

|      | 12.4.4            | 連続受信について           | 12-39 |

|      | 12.4.5            | CSIO 受信動作の状態を示すフラグ | 12-40 |

|      | 12.4.6            | CSIO 受信動作例         | 12-41 |

| 12.5 | CSIO <del>E</del> | :ード時の注意事項          | 12-43 |

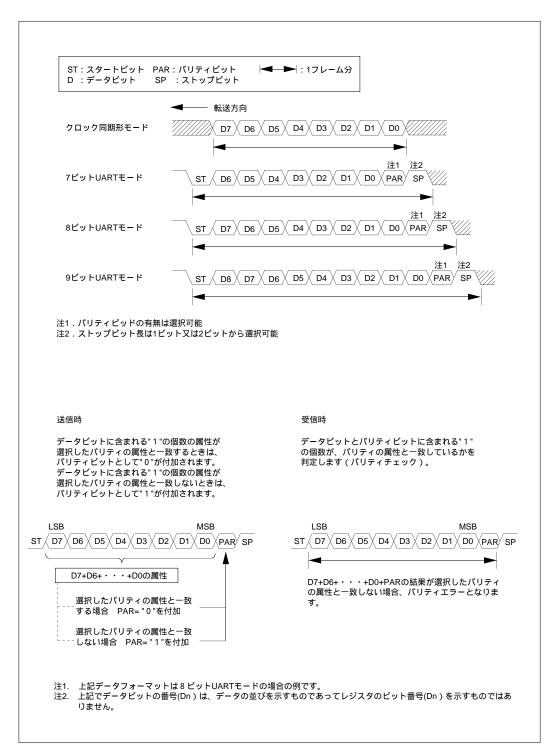

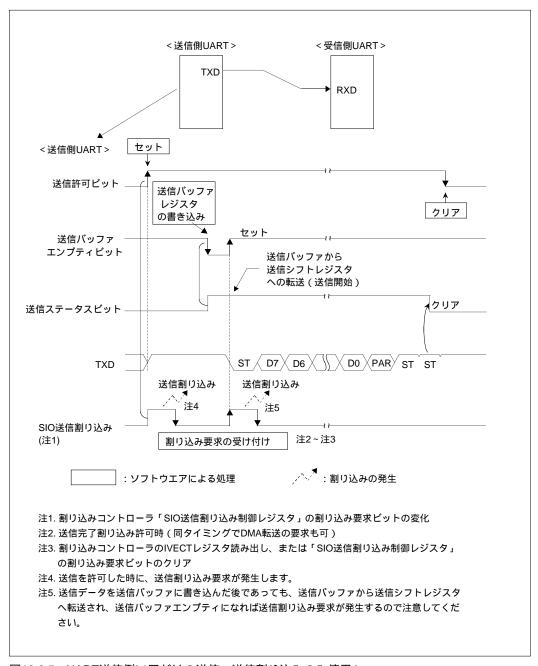

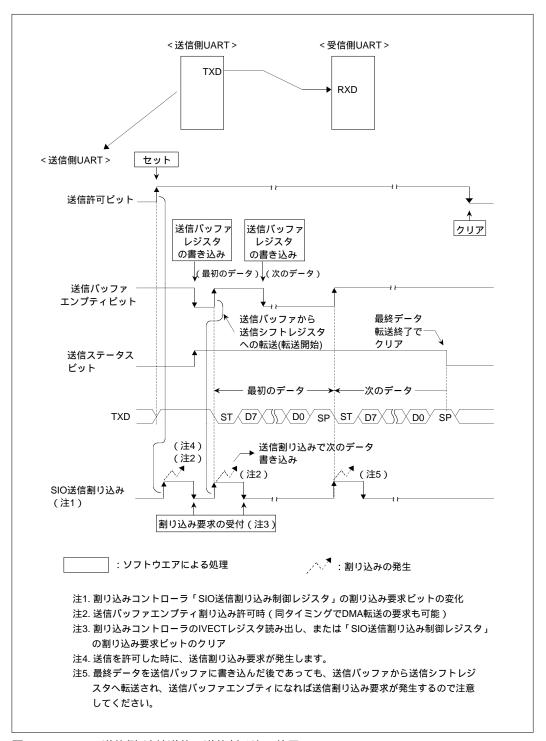

| 12.6 | UART <del>T</del> | Eード送信動作説明          | 12-45 |

|      | 12.6.1            | UART ボーレートの設定      | 12-45 |

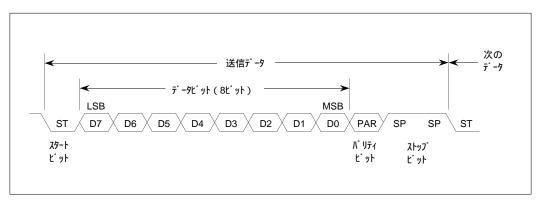

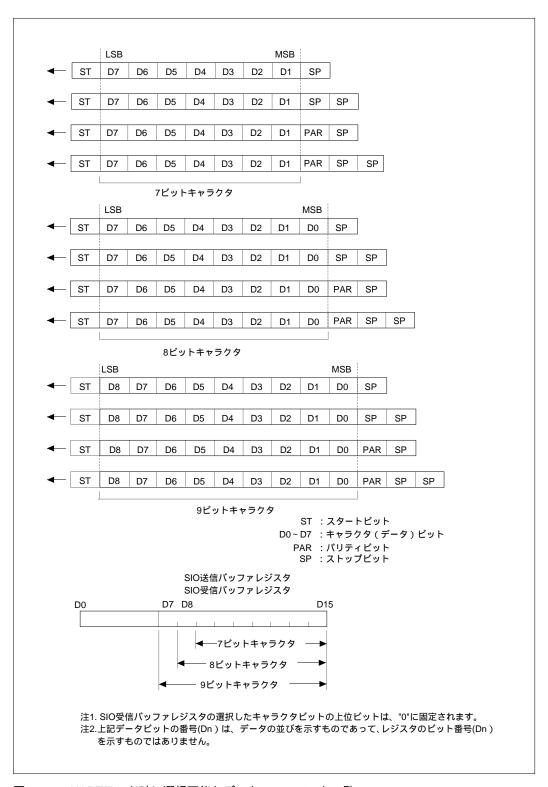

|      | 12.6.2            | UART 送受信データフォーマット  | 12-46 |

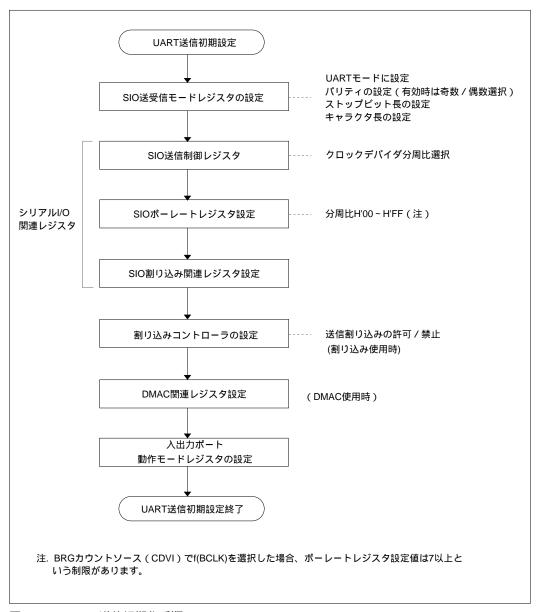

|      | 12.6.3            | UART 送信時の初期設定      | 12-48 |

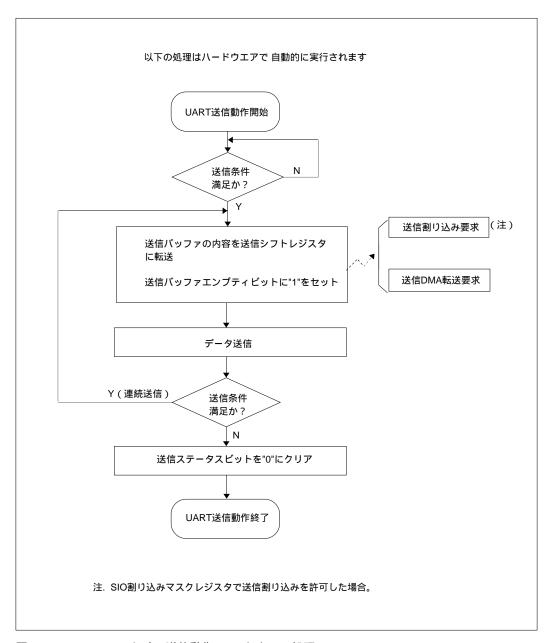

|      | 12.6.4            | UART 送信の開始         | 12-50 |

|      | 12.6.5            | UART の連続送信         | 12-50 |

|      | 12.6.6            | UART 送信完了処理        | 12-51 |

|      | 12.6.7            | 送信割り込み             | 12-51 |

|      | 12.6.8            | 送信 DMA 転送要求        | 12-51 |

|      | 12.6.9            | UART 送信動作例                                                                                       | 12-53 |

|------|-------------------|--------------------------------------------------------------------------------------------------|-------|

| 12.7 | UART <del>T</del> | Eード受信動作説明                                                                                        | 12-55 |

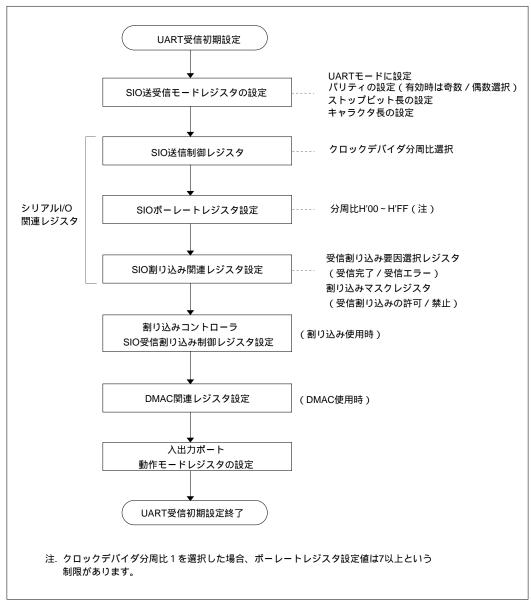

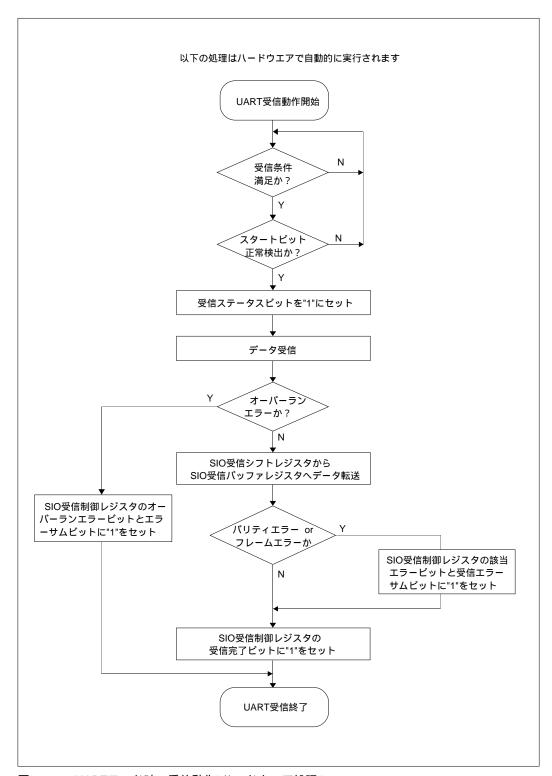

|      | 12.7.1            | UART 受信時の初期設定                                                                                    | 12-55 |

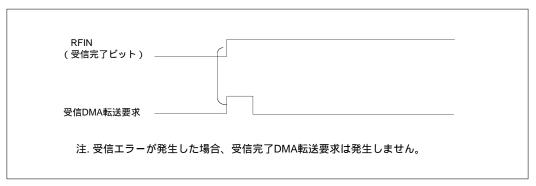

|      | 12.7.2            | UART 受信の開始                                                                                       | 12-57 |

|      | 12.7.3            | UART 受信完了処理                                                                                      | 12-57 |

|      | 12.7.4            | UART 受信動作例                                                                                       | 12-59 |

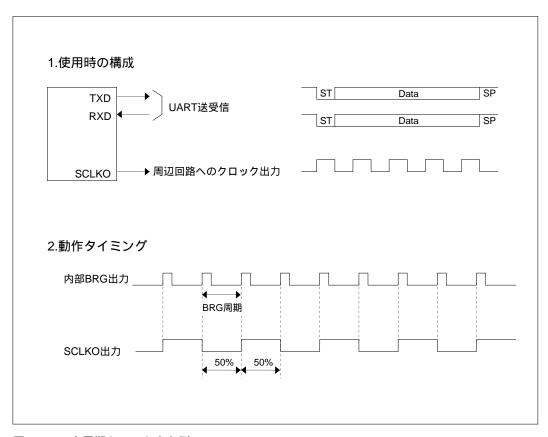

| 12.8 | 定周期な              | 7ロック出力機能                                                                                         | 12-62 |

| 12.9 | UART <del>T</del> | Eード時の注意事項                                                                                        | 12-63 |

|      | <b>0</b> 7        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                          |       |

| 第13  | 章 CA              | N モジュール                                                                                          |       |

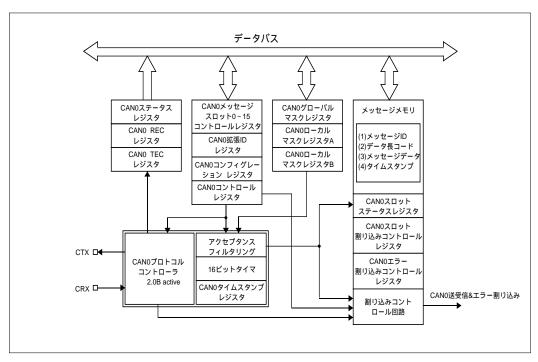

| 13.1 | CAN モシ            | <sup>デ</sup> ュールの概要                                                                              | 13-2  |

| 13.2 | CANモシ             | ·<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・ | 13-4  |

|      | 13.2.1            | CAN コントロールレジスタ                                                                                   | 13-8  |

|      | 13.2.2            | CAN ステータレジスタ                                                                                     | 13-11 |

|      | 13.2.3            | CAN 拡張 ID レジスタ                                                                                   | 13-15 |

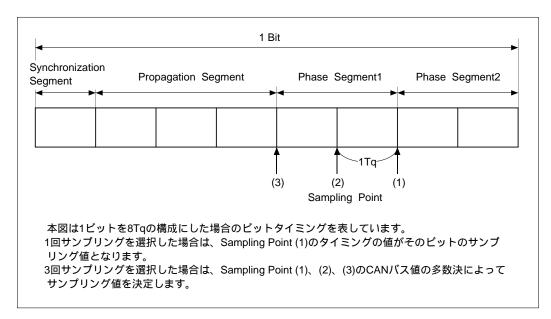

|      | 13.2.4            | CAN コンフィグレーションレジスタ                                                                               | 13-16 |

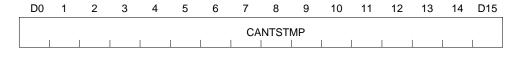

|      | 13.2.5            | CAN タイムスタンプカウントレジスタ                                                                              | 13-19 |

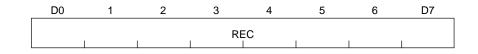

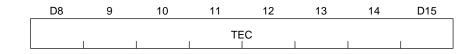

|      | 13.2.6            | CAN エラーカウントレジスタ                                                                                  | 13-20 |

|      | 13.2.7            | CAN ボーレートプリスケーラ                                                                                  | 13-21 |

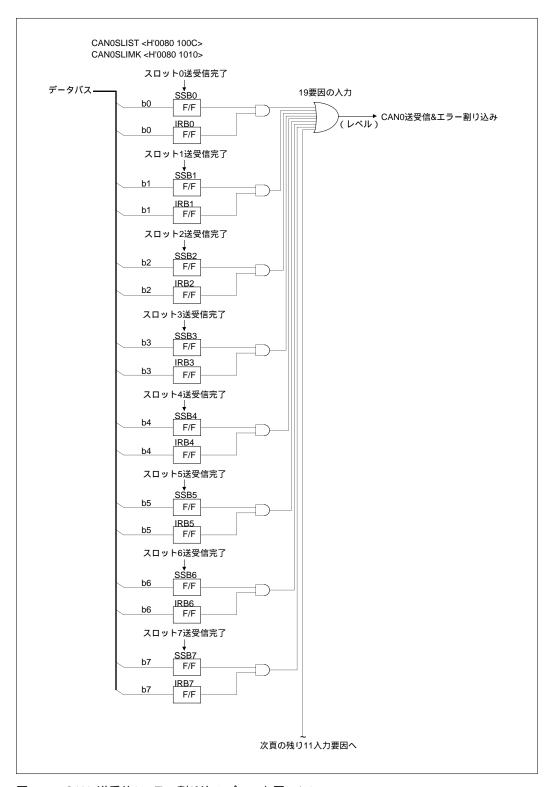

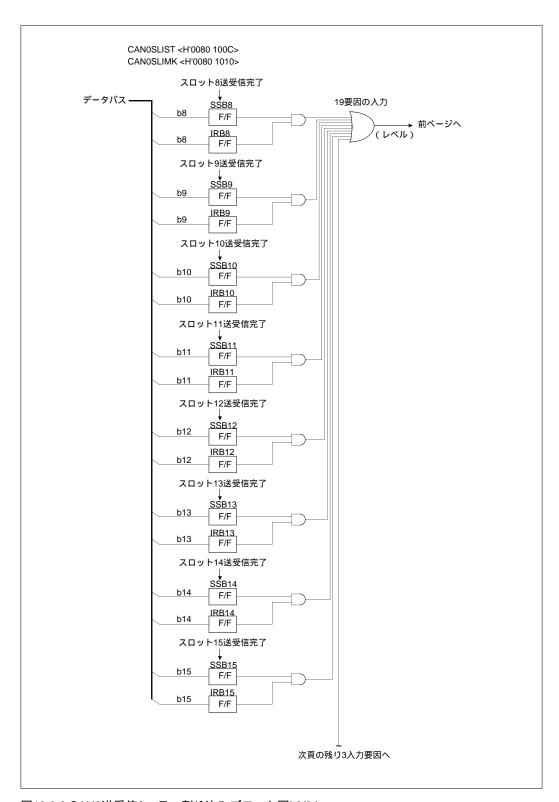

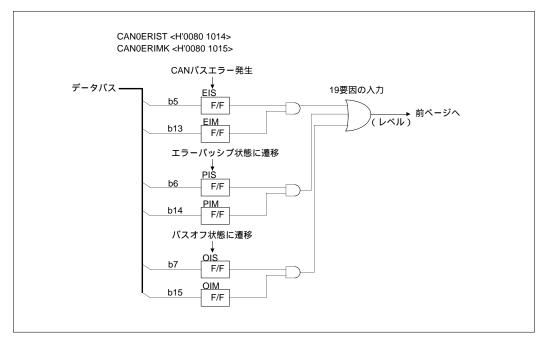

|      | 13.2.8            | CAN 割り込み関連レジスタ                                                                                   | 13-22 |

|      | 13.2.9            | CAN マスクレジスタ                                                                                      | 13-30 |

|      | 13.2.10           | CAN メッセージスロットコントロールレジスタ                                                                          | 13-34 |

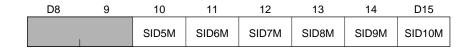

|      | 13.2.11           | CAN メッセージスロット                                                                                    | 13-38 |

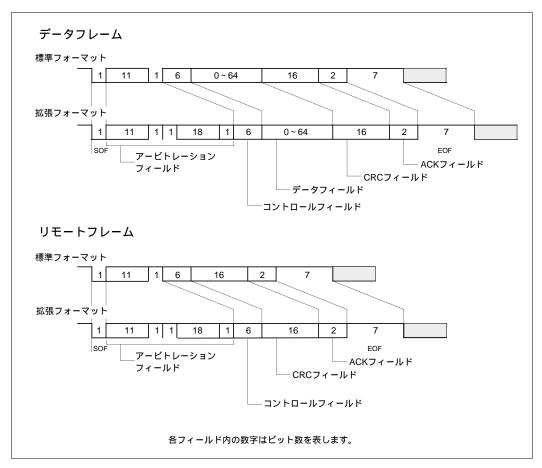

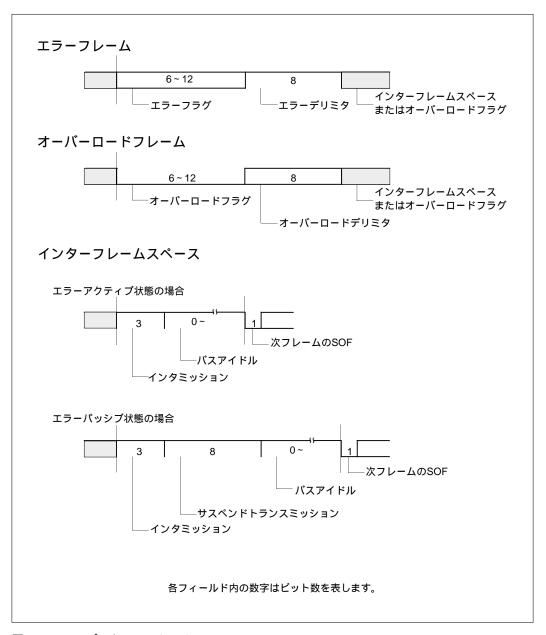

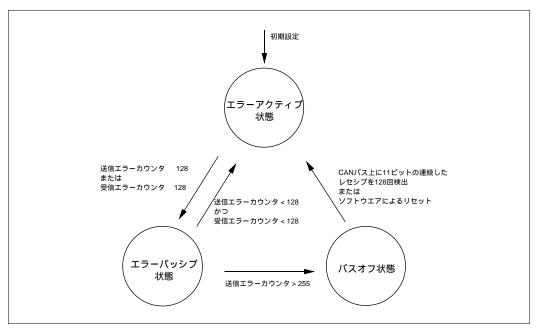

| 13.3 | CANプ              | ロトコル                                                                                             | 13-53 |

|      | 13.3.1            | CAN プロトコルフレーム                                                                                    | 13-53 |

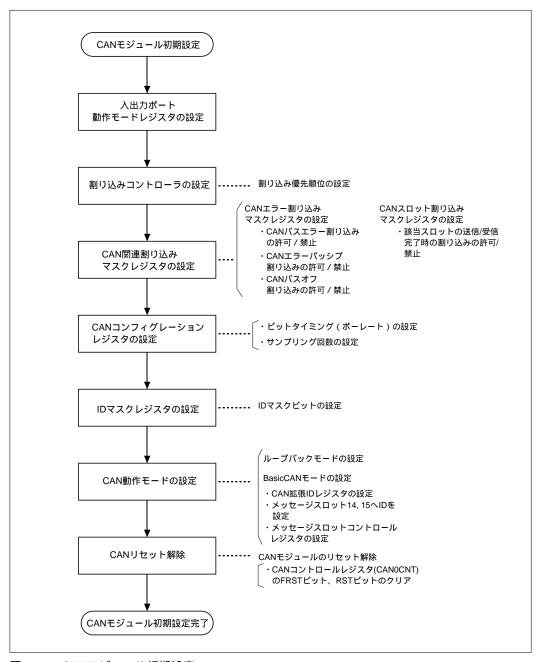

| 13.4 | CAN T             | ジュール初期設定                                                                                         | 13-56 |

|      | 13.4.1            | CAN モジュールの初期設定                                                                                   | 13-56 |

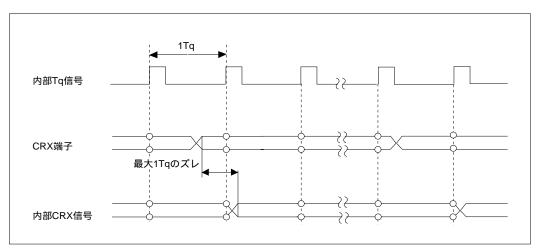

|      | 13.4.2            | CAN タイミング                                                                                        | 13-59 |

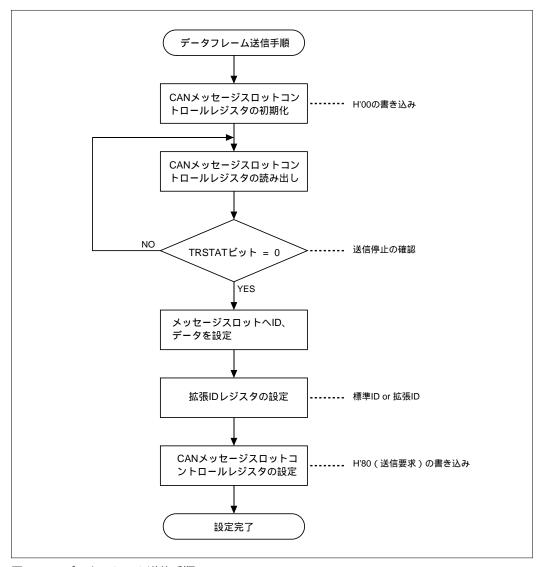

| 13.5 | データフ              | 7レーム送信                                                                                           | 13-60 |

|      |                   | データフレーム送信手順                                                                                      |       |

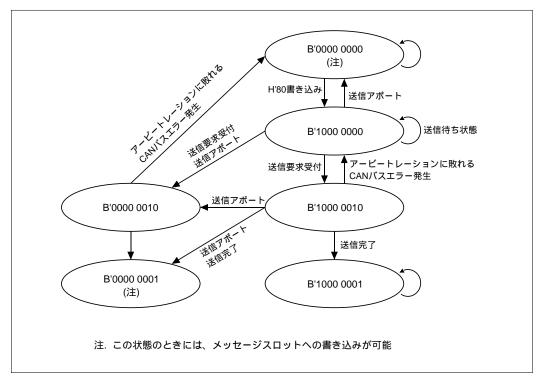

|      |                   | データフレーム送信動作                                                                                      |       |

|      |                   | 送信アボート機能                                                                                         |       |

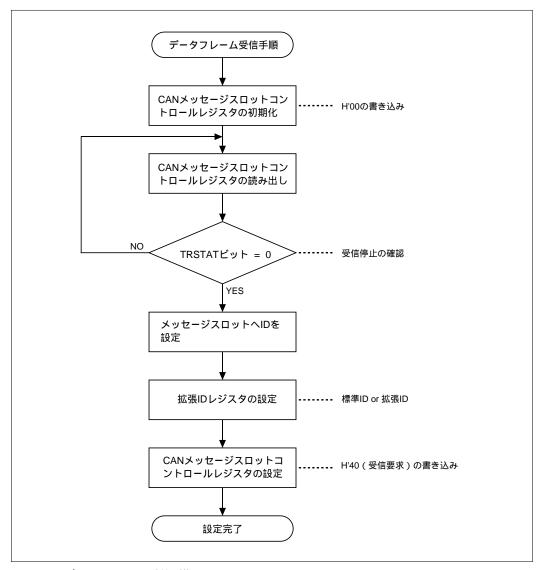

| 13.6 |                   | 7レーム受信                                                                                           |       |

| .0.0 |                   | データフレーム受信手順                                                                                      |       |

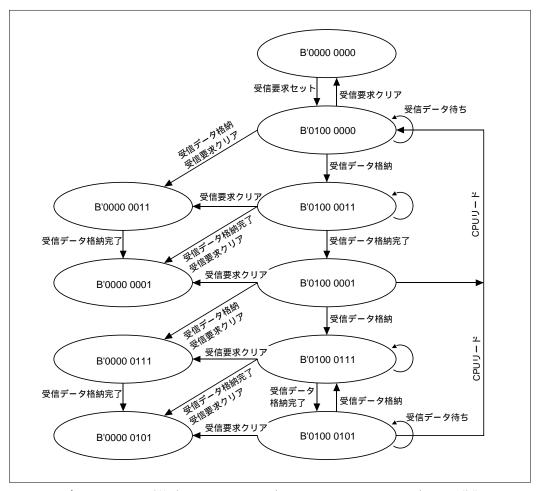

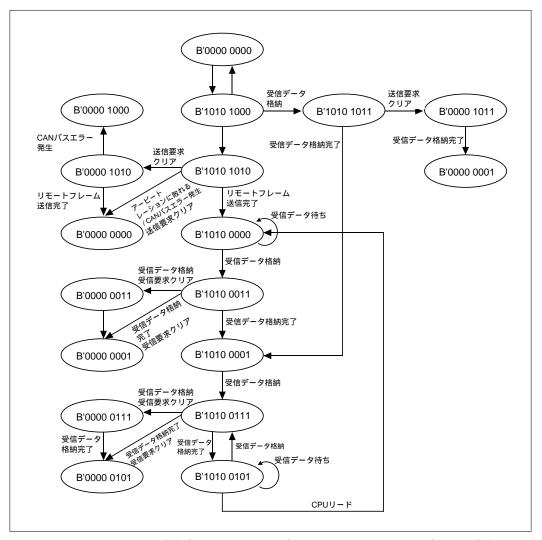

|          | 13.6.2 データフレーム受信動作                     | 13-66 |

|----------|----------------------------------------|-------|

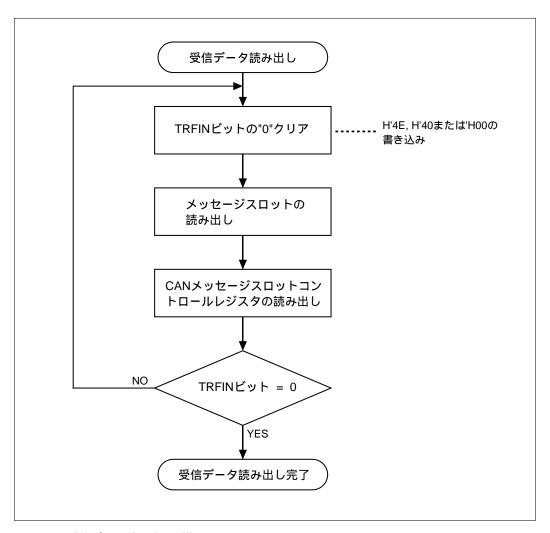

|          | 13.6.3 受信データフレームの読み出し                  | 13-68 |

| 13.7     | リモートフレーム送信                             | 13-70 |

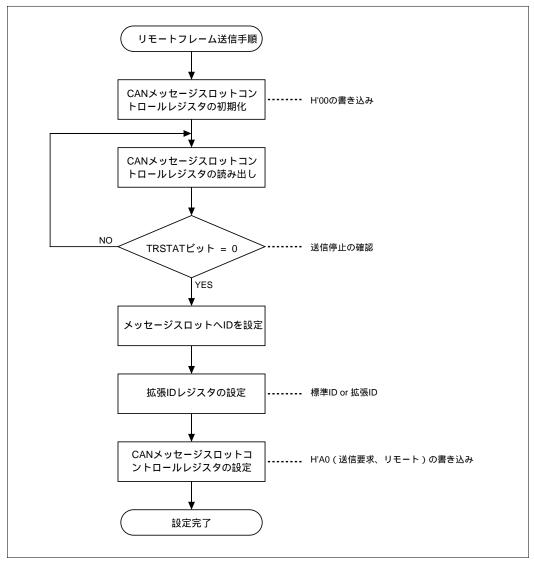

|          | 13.7.1 リモートフレーム送信手順                    | 13-70 |

|          | 13.7.2 リモートフレーム送信動作                    | 13-72 |

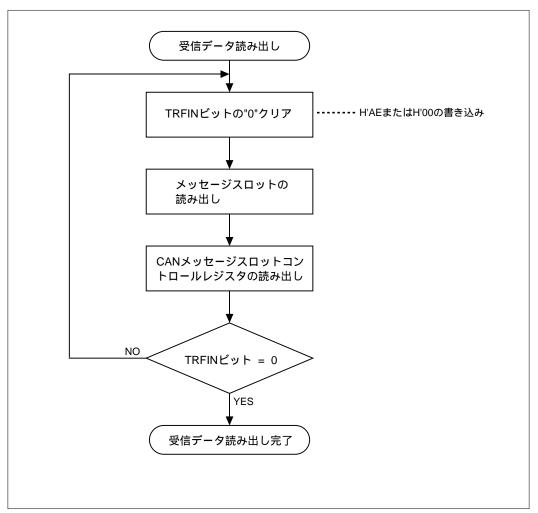

|          | 13.7.3 リモートフレーム送信設定時の受信データフレームの読み出し    | 13-75 |

| 13.8     | リモートフレーム受信                             | 13-77 |

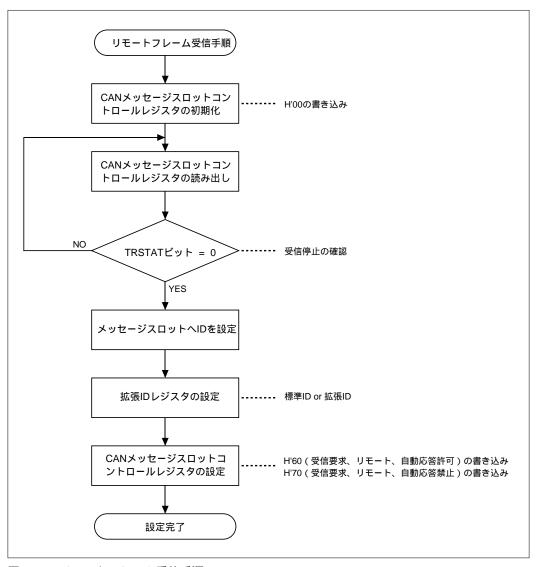

|          | 13.8.1 リモートフレーム受信手順                    | 13-77 |

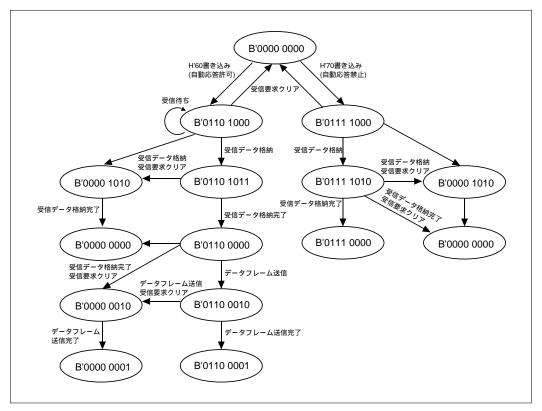

|          | 13.8.2 リモートフレーム受信動作                    | 13-79 |

| <br>第 14 | ニー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |       |

|          |                                        |       |

| 14.1     | リアルタイムデバッガ(RTD)概要                      | 14-2  |

| 14.2     | RTD 端子機能                               | 14-3  |

| 14.3     | RTD 動作説明                               | 14-4  |

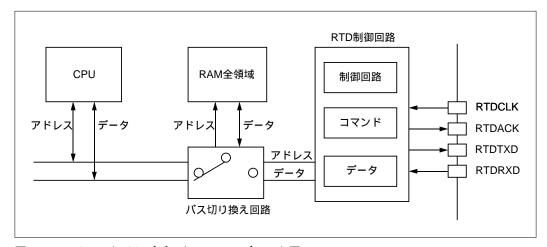

|          | 14.3.1 RTD 動作概要                        | 14-4  |

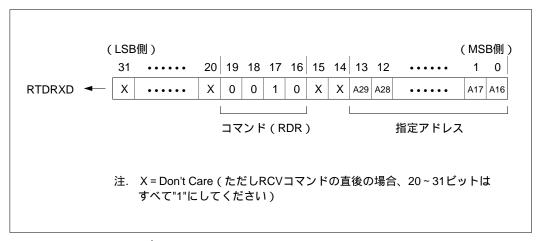

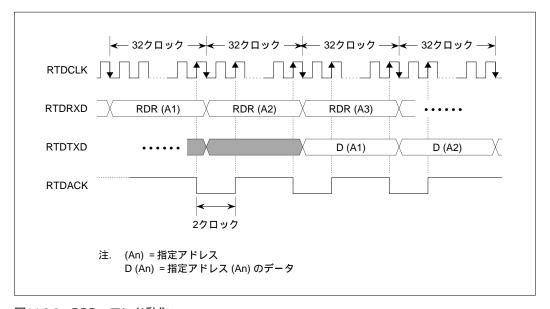

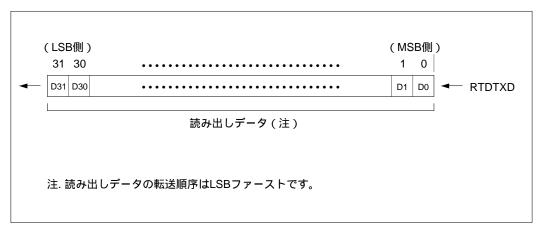

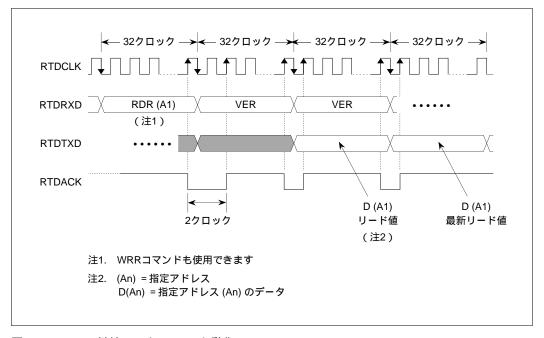

|          | 14.3.2 RDR ( リアルタイム RAM 内容出力 ) 動作      | 14-5  |

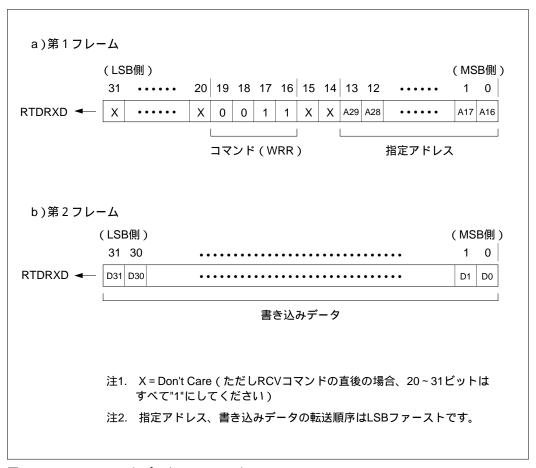

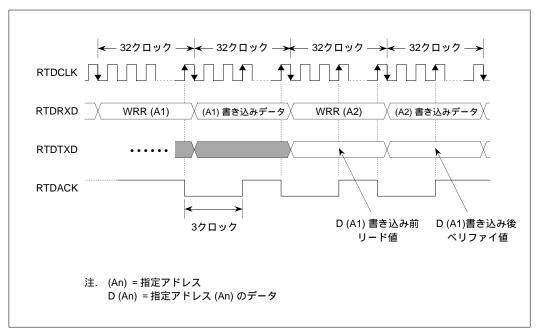

|          | 14.3.3 WRR(RAM 内容強制書き替え)動作             | 14-7  |

|          | 14.3.4 VER(継続モニタ)動作                    | 14-9  |

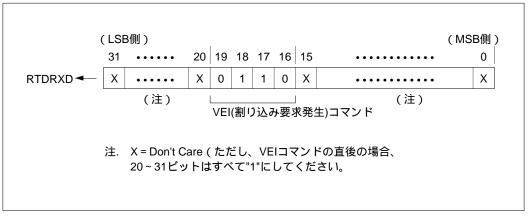

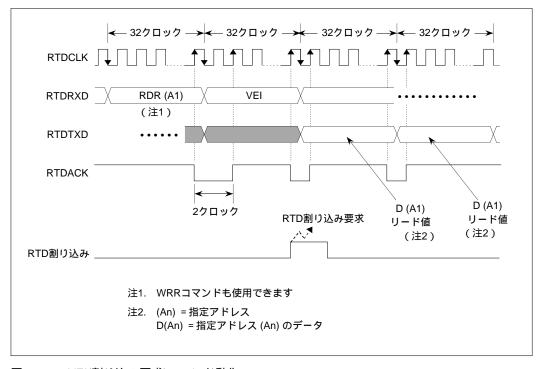

|          | 14.3.5 VEI(割り込み要求)動作                   | 14-10 |

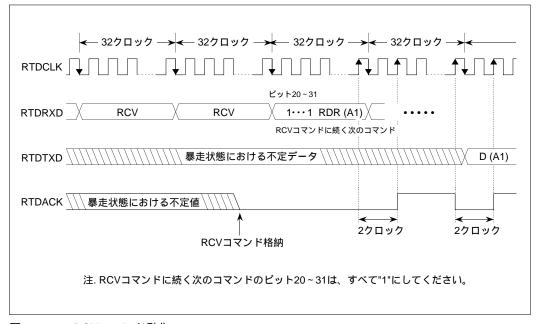

|          | 14.3.6 RCV (暴走状態からの復帰)動作               | 14-11 |

|          | 14.3.7 リアルタイムデバッカ使用時の指定アドレス設定方法        |       |

|          | 14.3.8 RTDのリセット                        | 14-13 |

| 14.4     | ホストとの接続例                               | 14-14 |

| 15章      | 外部バスインターフェース                           |       |

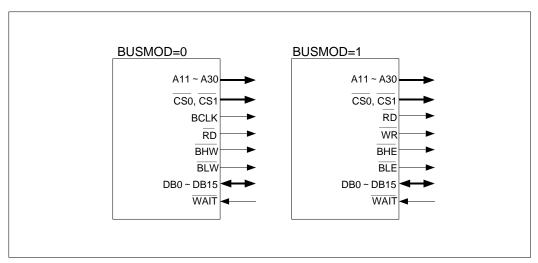

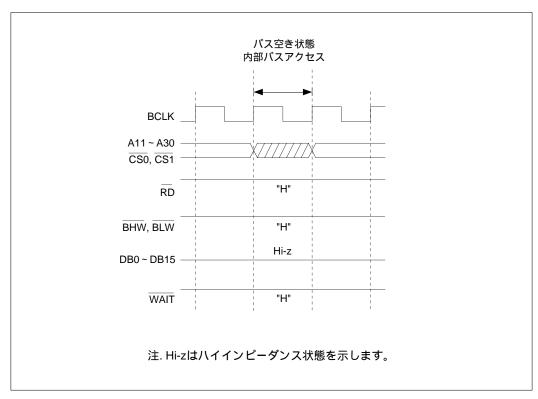

| 15.1     | 外部バスインターフェース関連信号                       | 15-2  |

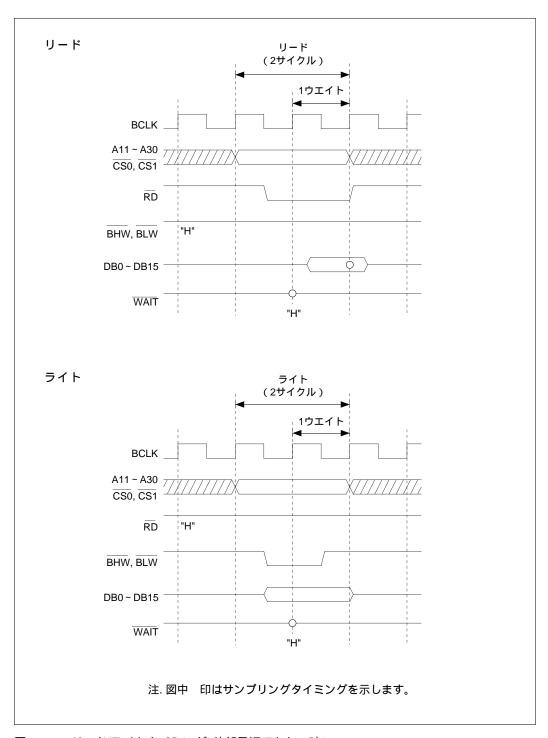

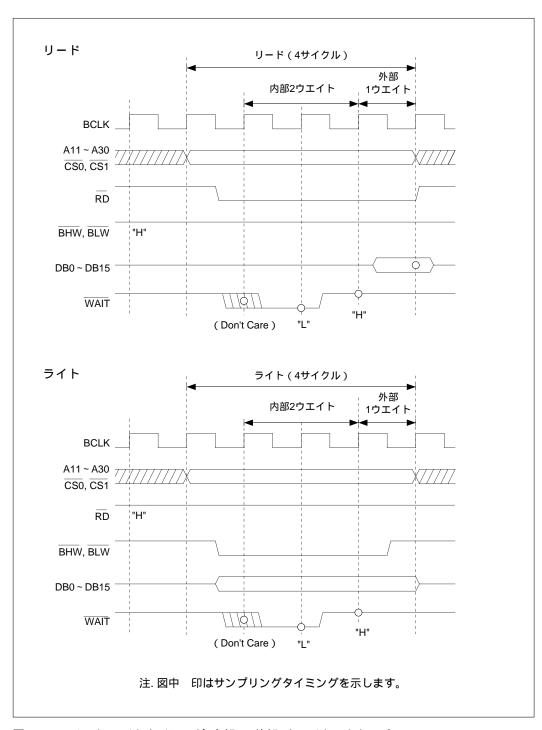

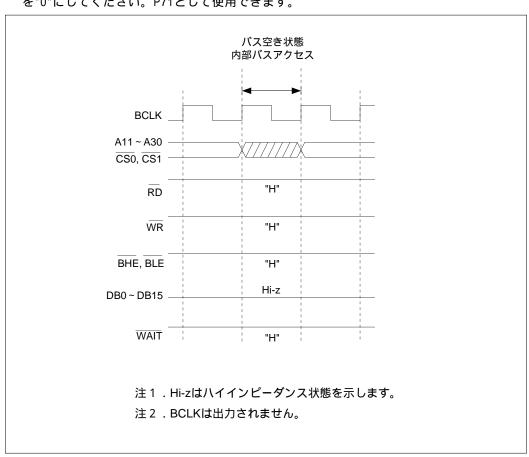

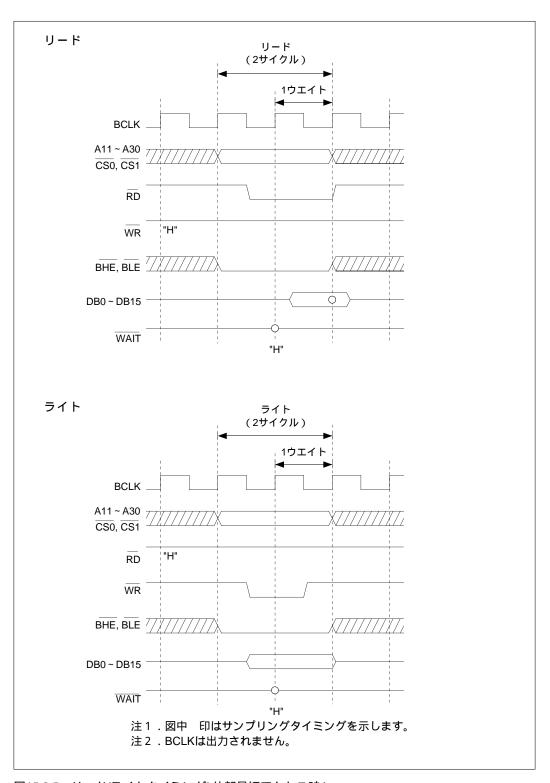

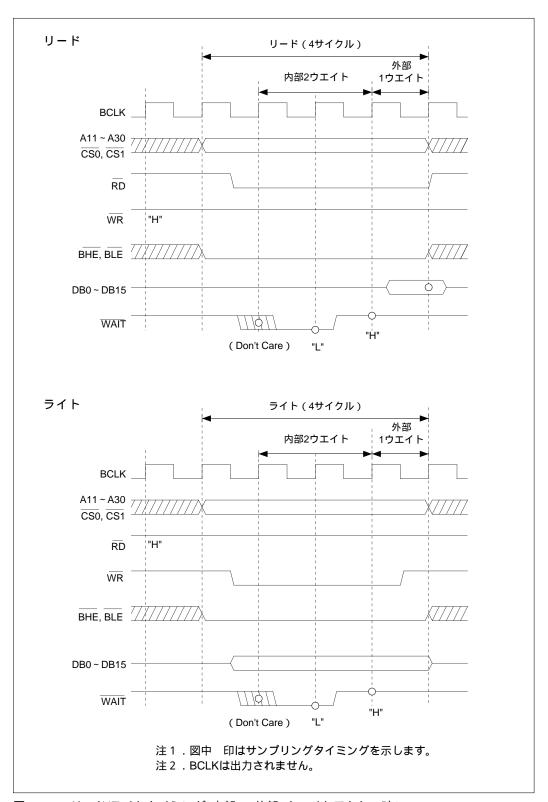

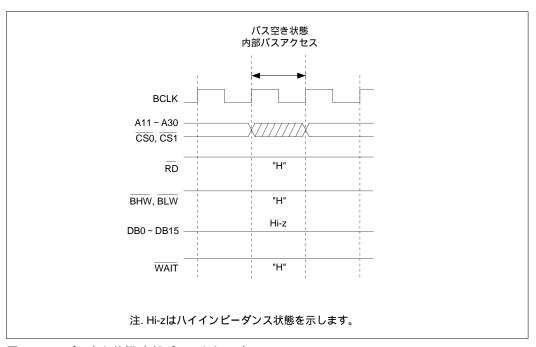

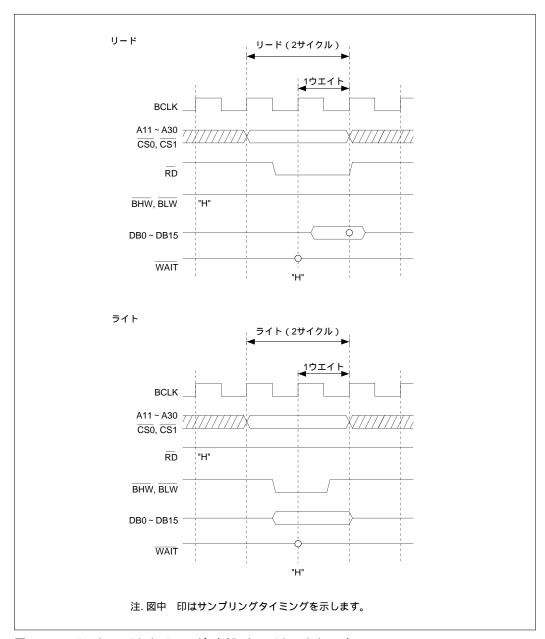

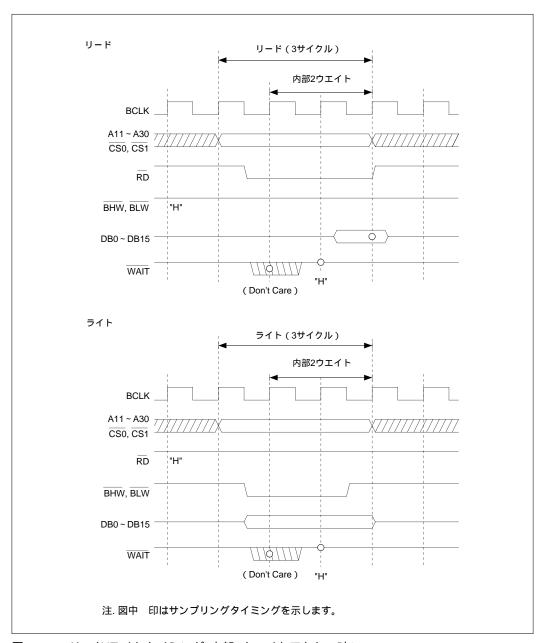

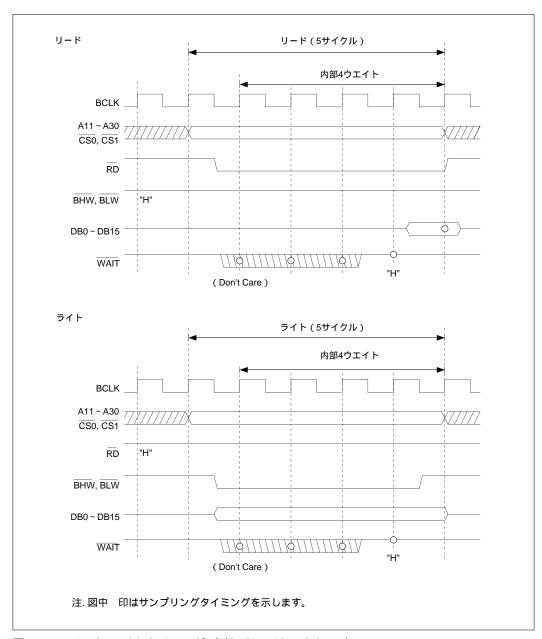

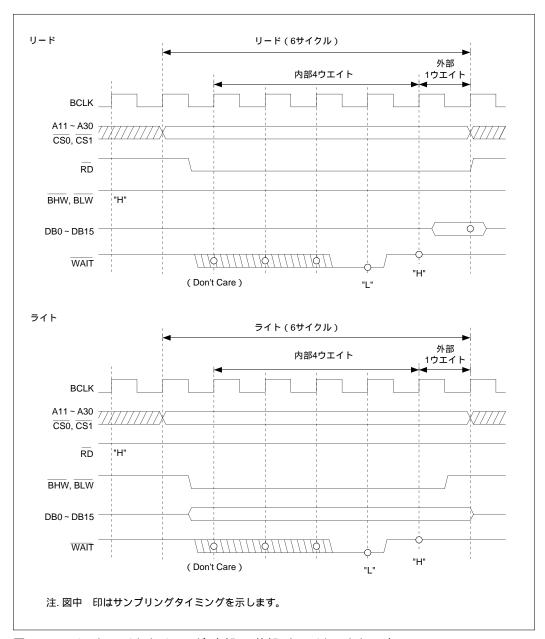

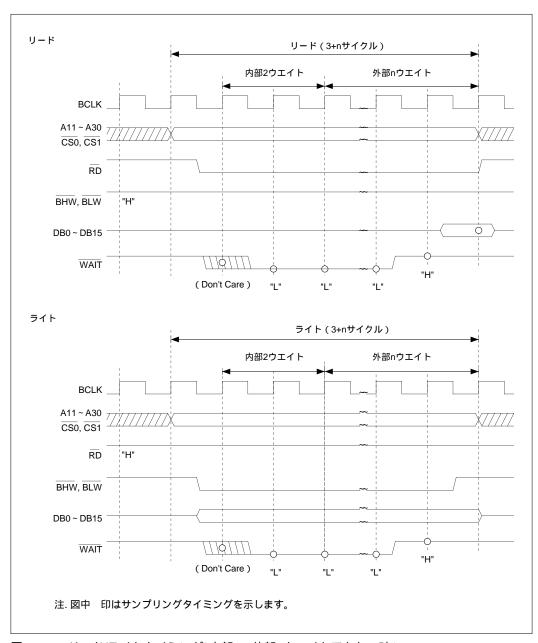

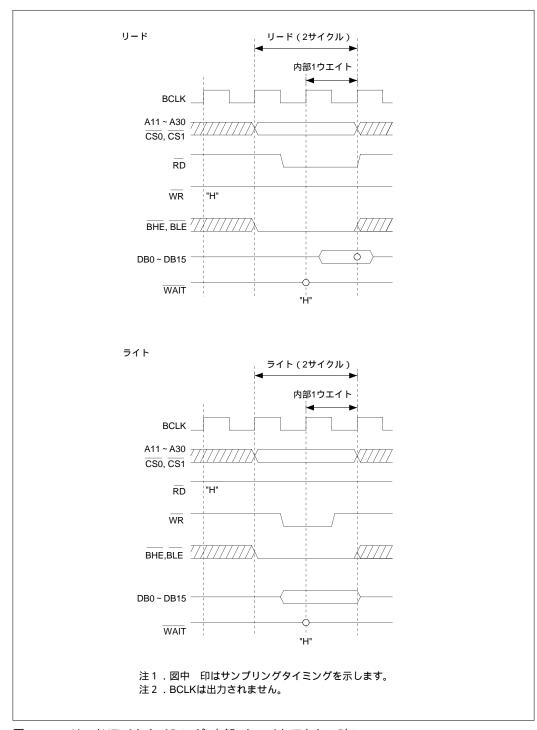

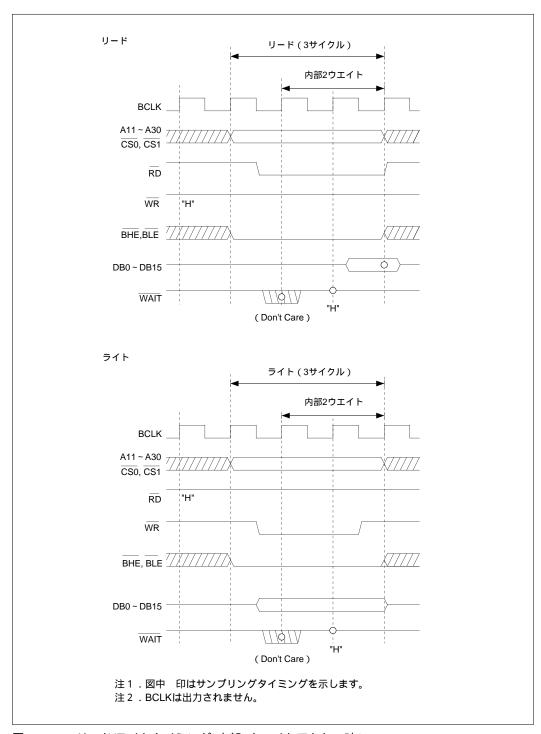

| 15.2     | リード / ライト動作                            | 15-6  |

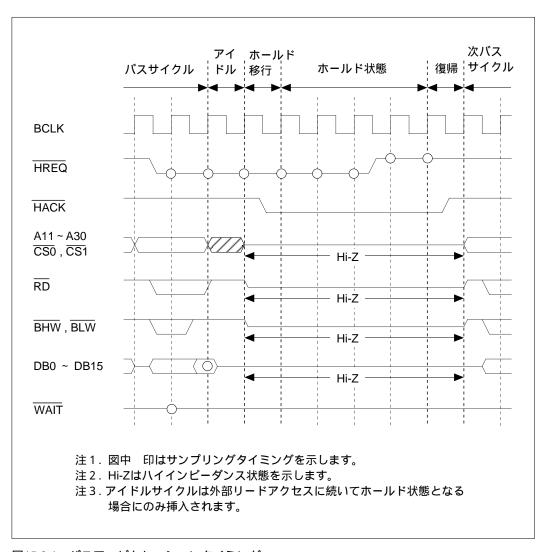

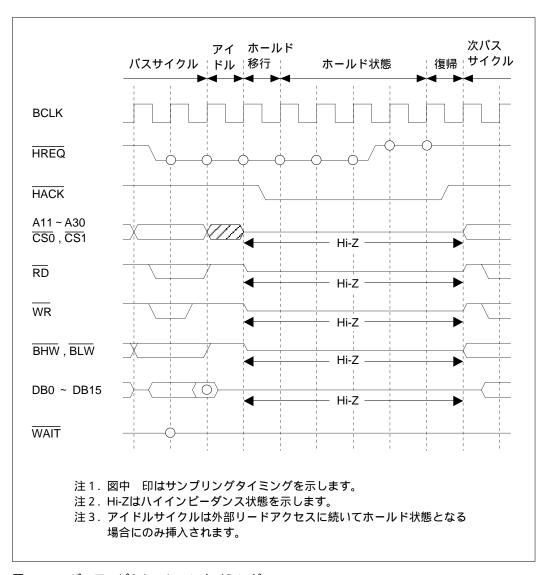

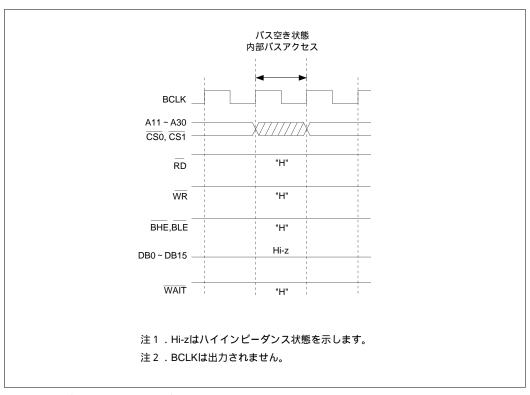

| 15.3     | バスアービトレーション                            | 15-12 |

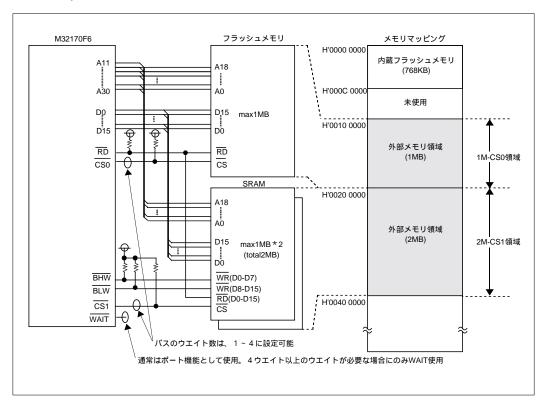

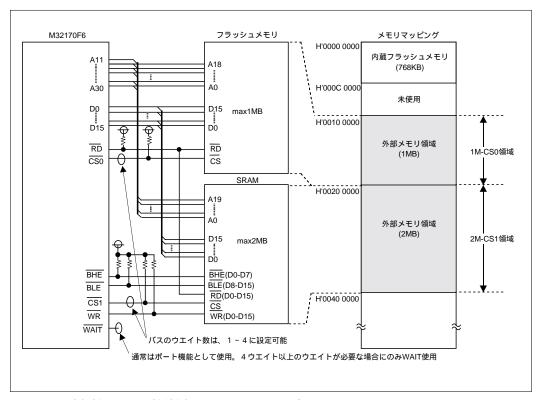

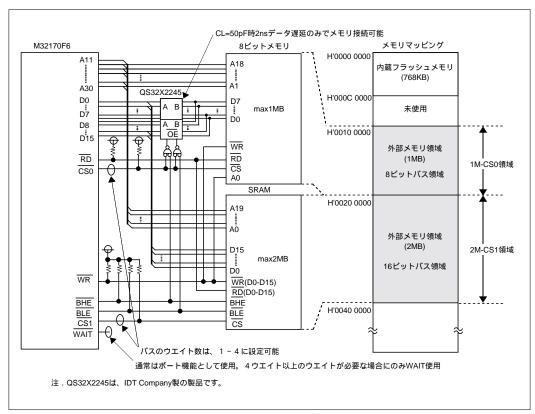

| 15.4     | 外部拡張メモリ接続例                             | 15-14 |

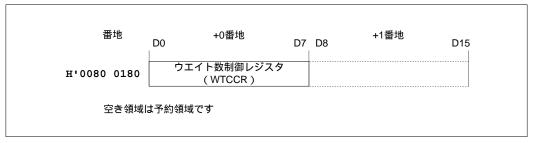

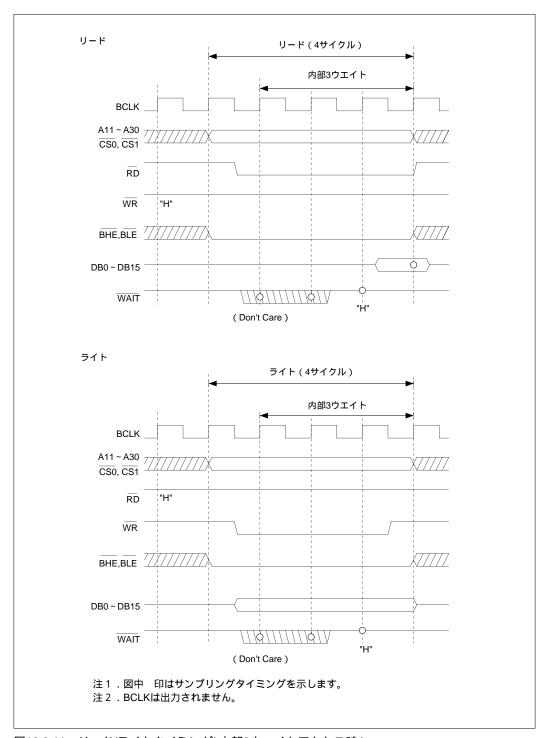

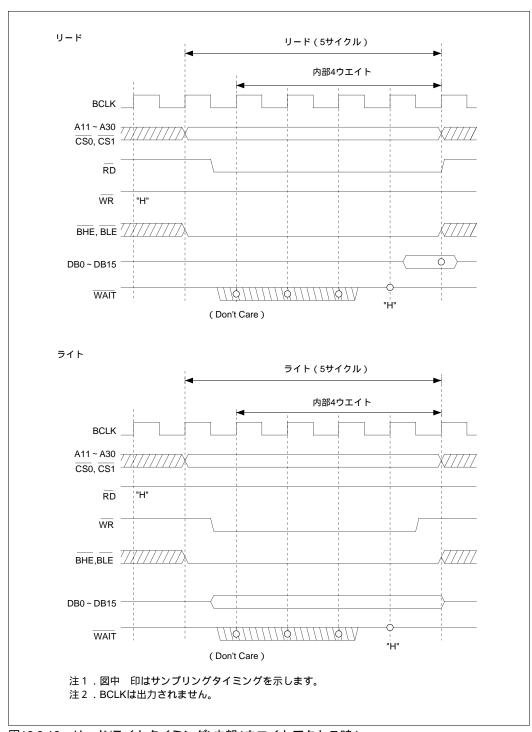

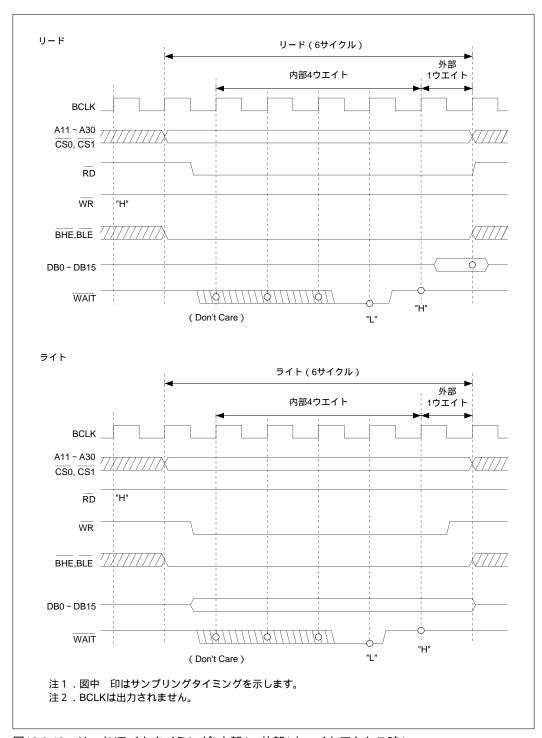

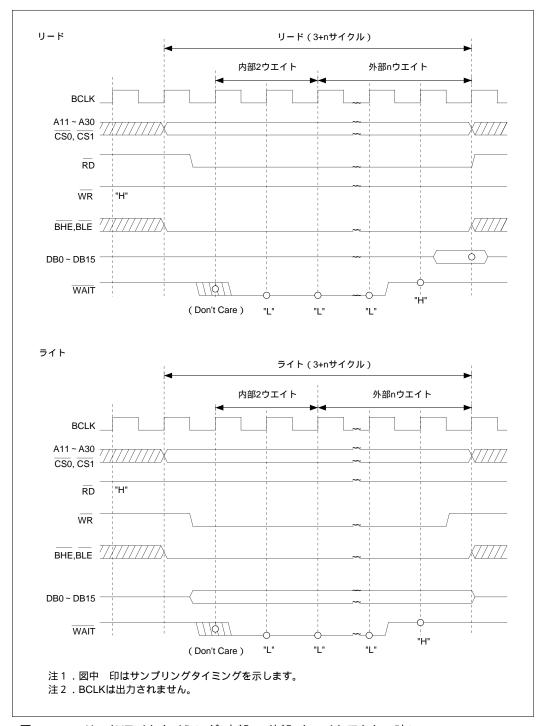

| 16章      | ウエイトコントローラ                             |       |

| 16.1     | ウエイトコントローラ概要                           | 16-2  |

| 16.2                         | ウエイトコントローラ関連レジスタ                                                                       | 16-4                         |

|------------------------------|----------------------------------------------------------------------------------------|------------------------------|

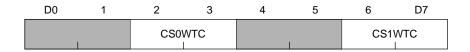

|                              | 16.2.1 ウエイト数制御レジスタ(WTCCR)                                                              | 16-5                         |

| 16.3                         | ウエイトコントローラ動作例                                                                          | 16-6                         |

|                              |                                                                                        |                              |

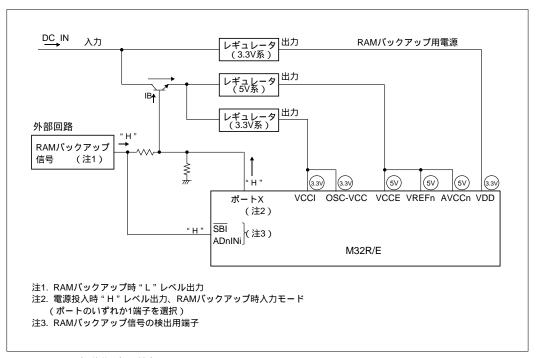

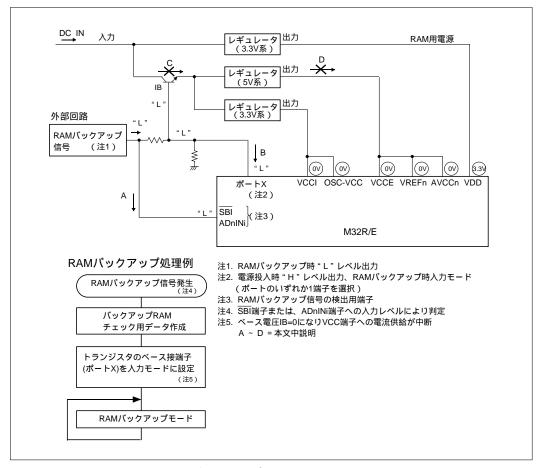

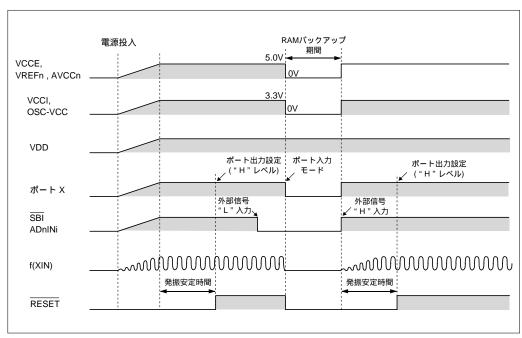

| 第 17                         | 章 RAM バックアップモード                                                                        |                              |

| 17.1                         | 概要                                                                                     | 17-2                         |

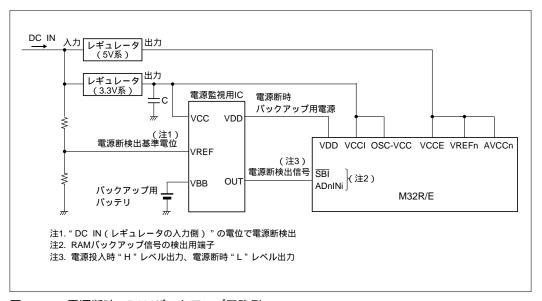

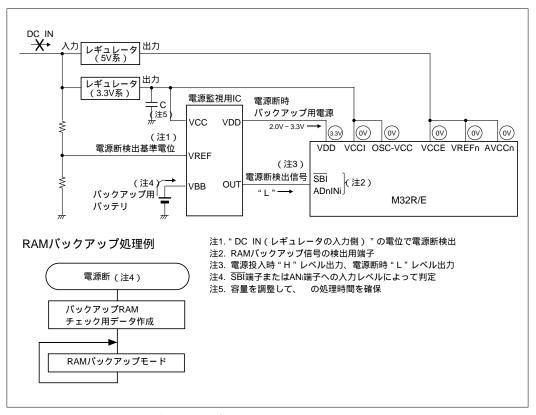

| 17.2                         | 電源断時の RAM バックアップ例                                                                      |                              |

|                              | 17.2.1 通常動作時の状態                                                                        |                              |

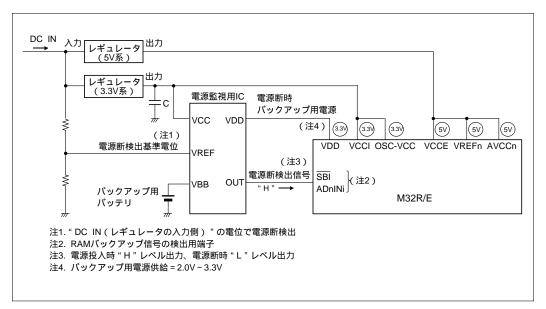

|                              | 17.2.2 RAM バックアップ時の状態                                                                  |                              |

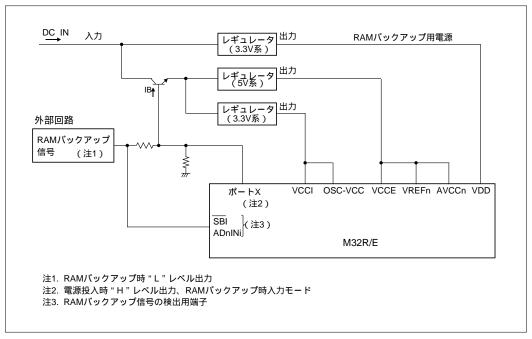

| 17.3                         | 低消費電力化のための RAM バックアップ例                                                                 | 17-5                         |

|                              | 17.3.1 通常動作時の状態                                                                        |                              |

|                              | 17.3.2 RAM バックアップ時の状態                                                                  |                              |

|                              | 17.3.3 電源立ち上げ時の注意事項                                                                    |                              |

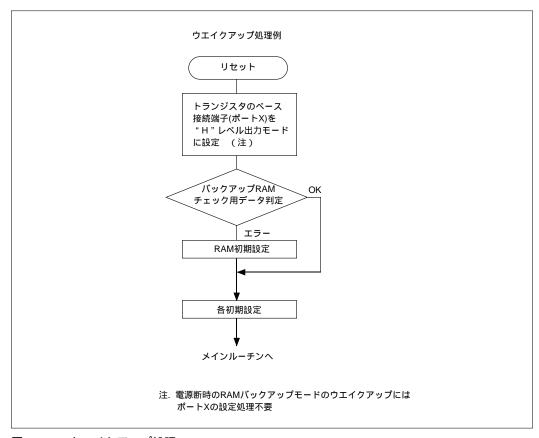

| 17.4                         | RAM バックアップモードの解除 ( ウエイクアップ )                                                           | 17-9                         |

|                              |                                                                                        |                              |

| 第18                          | 章 発振回路                                                                                 |                              |

|                              |                                                                                        |                              |

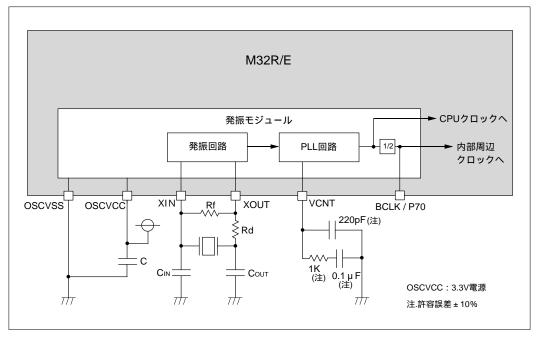

| 18.1                         | 発振回路                                                                                   | 18-2                         |

| 18.1                         | 発振回路                                                                                   |                              |

| 18.1                         |                                                                                        | 18-2                         |

| 18.1                         | 18.1.1 発振回路例                                                                           | 18-2<br>18-3                 |

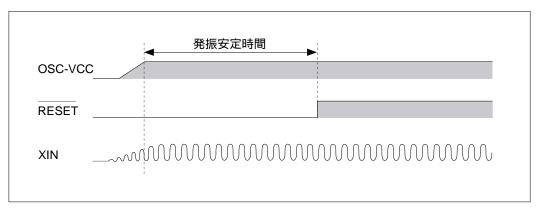

|                              | 18.1.1 発振回路例                                                                           | 18-2<br>18-3<br>18-4         |

|                              | 18.1.1 発振回路例                                                                           | 18-2<br>18-3<br>18-4         |

| 18.2                         | 18.1.1 発振回路例                                                                           | 18-2<br>18-3<br>18-4         |

| 18.2                         | 18.1.1 発振回路例                                                                           | 18-2<br>18-3<br>18-4<br>18-5 |

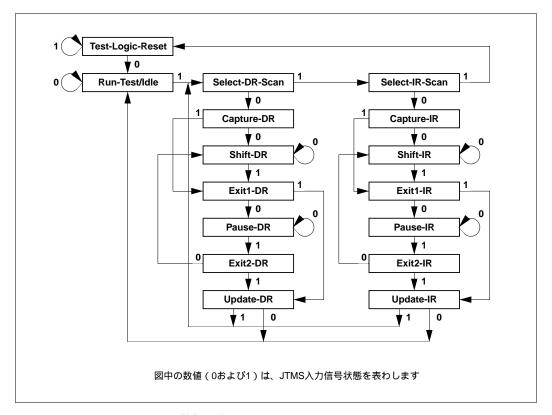

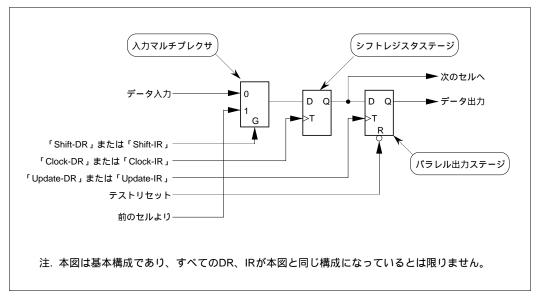

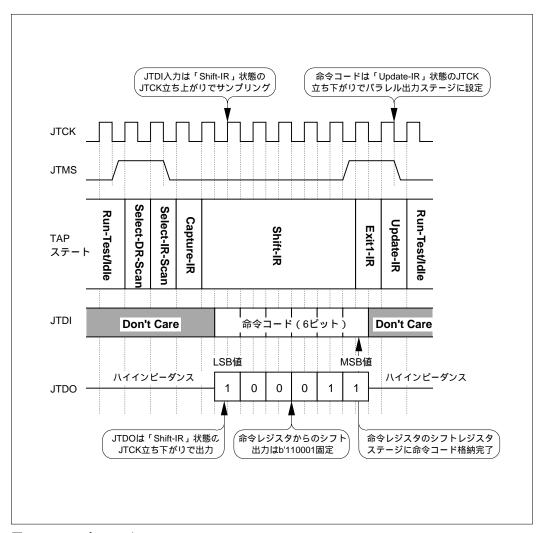

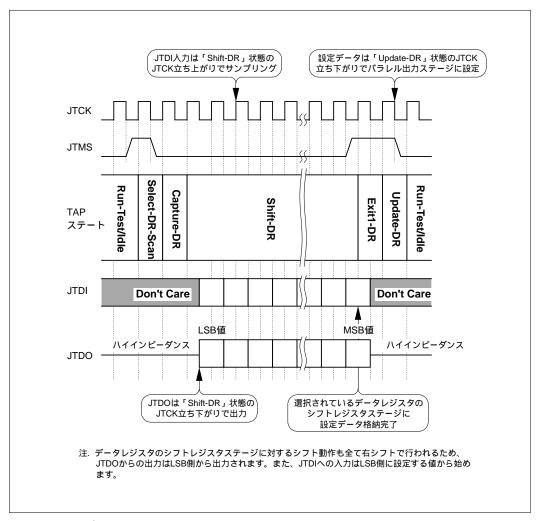

| 18.2<br>第 19<br>19.1         | 18.1.1 発振回路例                                                                           | 18-2<br>18-3<br>18-4<br>18-5 |

| 18.2<br>第 19<br>19.1         | 18.1.1 発振回路例         18.1.2 システムクロックの出力機能         18.1.3 電源投入時の発振安定時間         クロック発生回路 |                              |

| 18.2<br>第 19<br>19.1<br>19.2 | 18.1.1 発振回路例         18.1.2 システムクロックの出力機能         18.1.3 電源投入時の発振安定時間         クロック発生回路 |                              |

| 18.2<br>第 19<br>19.1<br>19.2 | 18.1.1 発振回路例         18.1.2 システムクロックの出力機能         18.1.3 電源投入時の発振安定時間         クロック発生回路 |                              |

| 18.2<br>第 19<br>19.1<br>19.2 | 18.1.1 発振回路例         18.1.2 システムクロックの出力機能         18.1.3 電源投入時の発振安定時間         クロック発生回路 |                              |

| 第 19<br>19.1<br>19.2<br>19.3 | 18.1.1 発振回路例         18.1.2 システムクロックの出力機能         18.1.3 電源投入時の発振安定時間         クロック発生回路 |                              |

| 第 19<br>19.1<br>19.2<br>19.3 | 18.1.1 発振回路例                                                                           |                              |

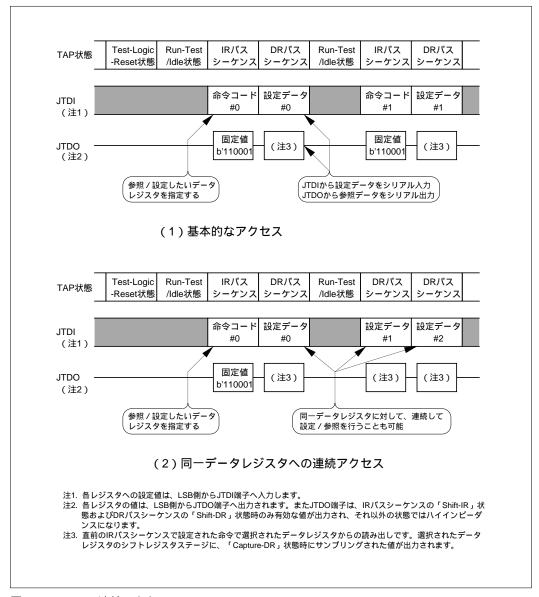

| 19.4.4 データレジスタの参照および設定                                                                                                                                                                                                                                         | 19-12                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 19.5 バウンダリスキャン記述言語                                                                                                                                                                                                                                             | 19-14                                                   |

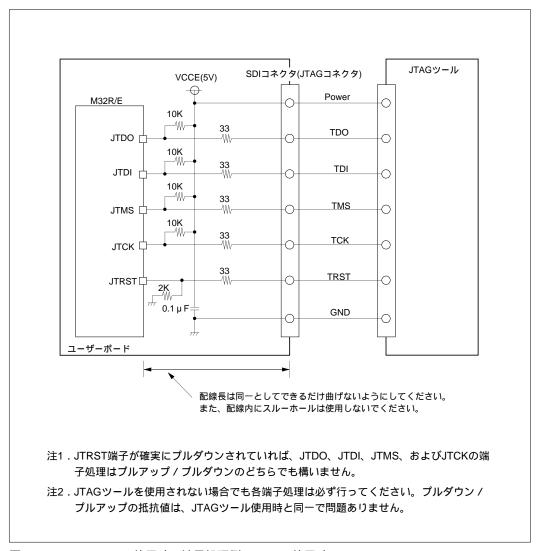

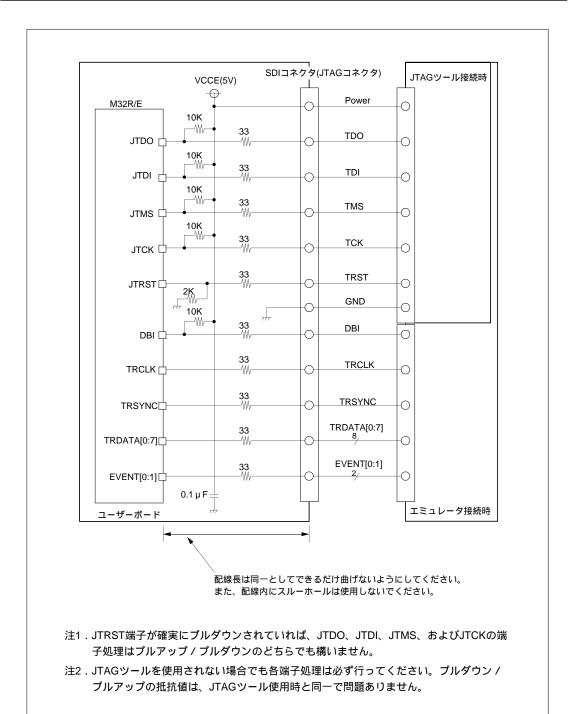

| 19.6 JTAG 使用時のボード設計注意事項                                                                                                                                                                                                                                        | 19-15                                                   |

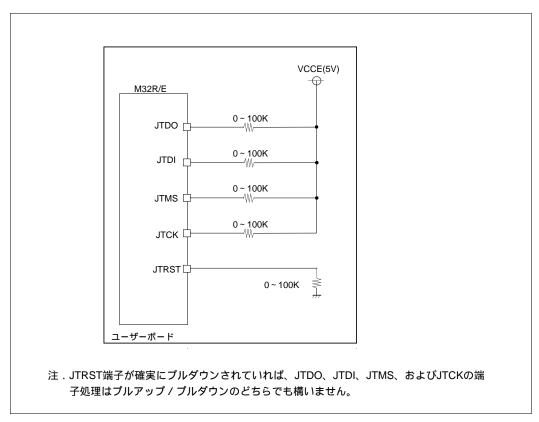

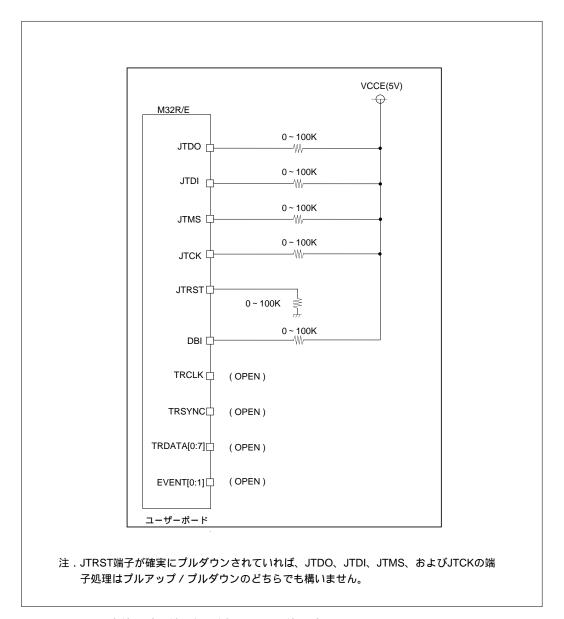

| 19.7 JTAG 未使用時の端子処理                                                                                                                                                                                                                                            | 19-17                                                   |

|                                                                                                                                                                                                                                                                |                                                         |

| 第 20 章 電源立ち上げ / 立ち下げシーケンス                                                                                                                                                                                                                                      |                                                         |

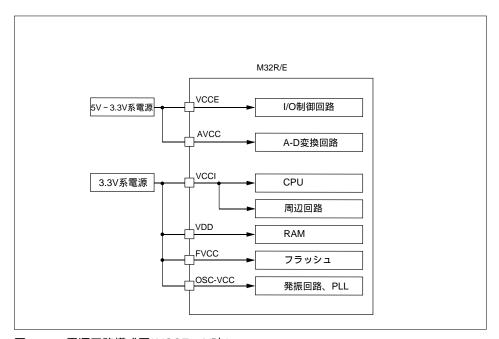

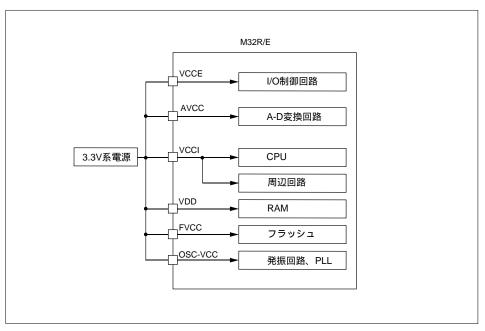

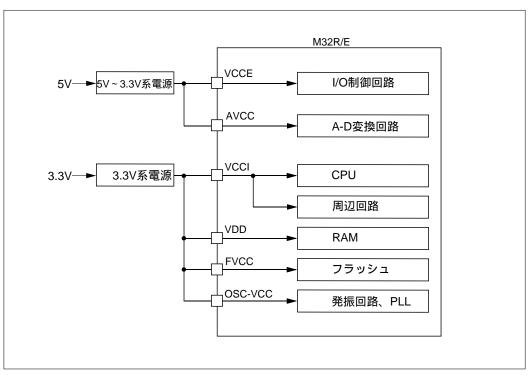

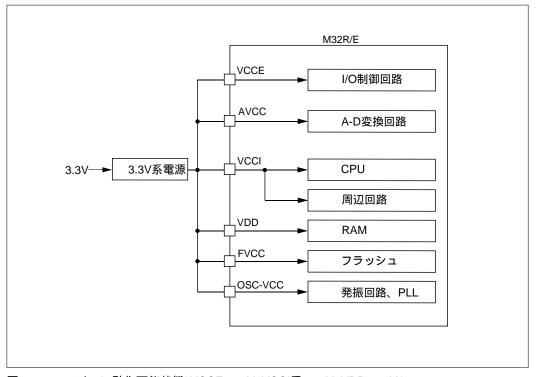

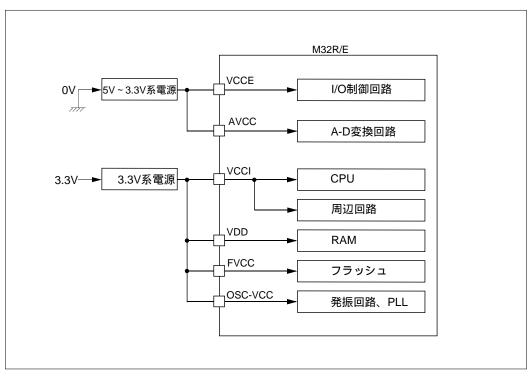

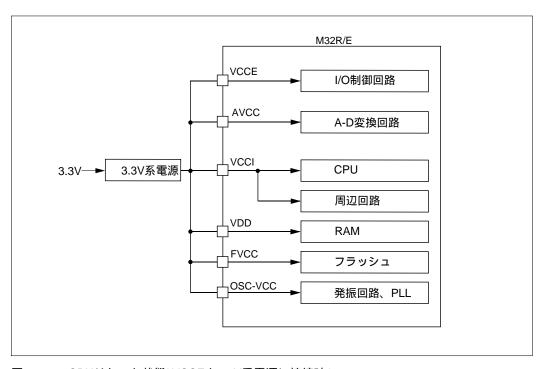

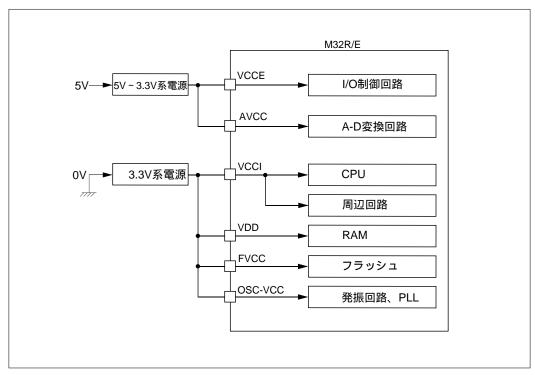

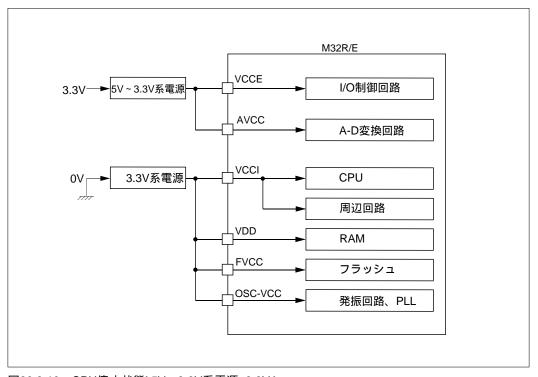

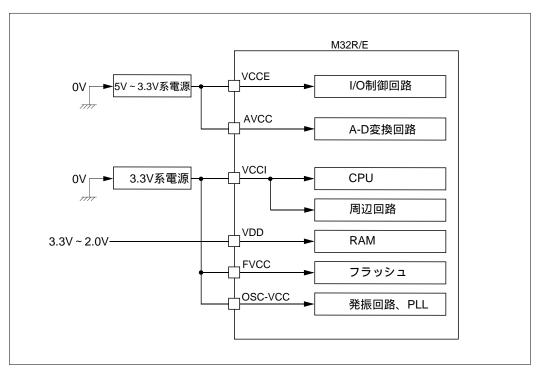

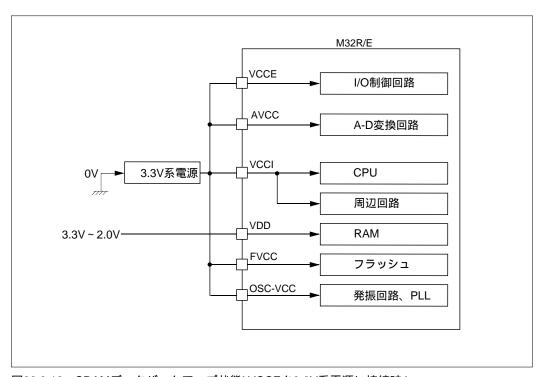

| 20.1 電源回路の構成                                                                                                                                                                                                                                                   | 20-2                                                    |

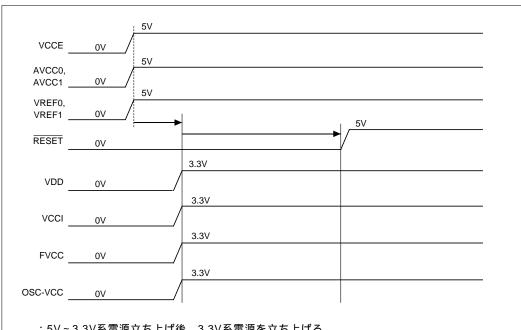

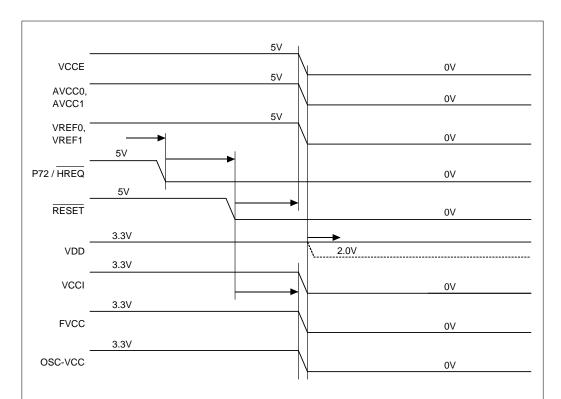

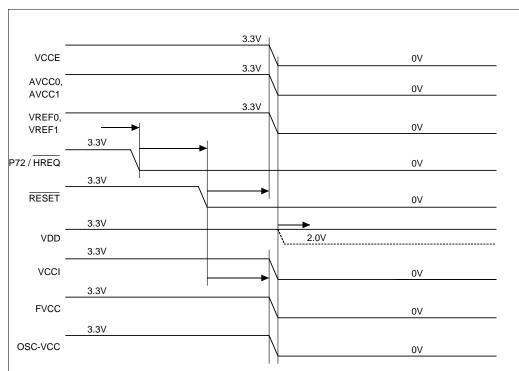

| 20.2 電源立ち上げシーケンス                                                                                                                                                                                                                                               | 20-4                                                    |

| 20.2.1RAM バックアップ未使用時の電源立ち上げシーケンス                                                                                                                                                                                                                               | 20-4                                                    |

| 20.2.2RAM バックアップ使用時の電源立ち上げシーケンス                                                                                                                                                                                                                                | 20-6                                                    |

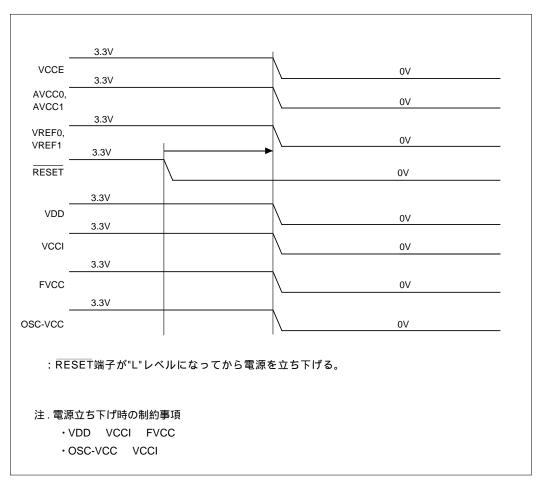

| 20.3 電源立ち下げシーケンス                                                                                                                                                                                                                                               | 20-8                                                    |

| 20.3.1RAM バックアップ未使用時の電源立ち下げシーケンス                                                                                                                                                                                                                               | 20-8                                                    |

| 20.3.2RAM バックアップ使用時の電源立ち下げシーケンス                                                                                                                                                                                                                                |                                                         |

|                                                                                                                                                                                                                                                                |                                                         |

|                                                                                                                                                                                                                                                                |                                                         |

| 第 21 章 電気的特性                                                                                                                                                                                                                                                   |                                                         |

| 第 21 章 電気的特性<br>21.1 電気的特性 (VCCE = 5V 時)                                                                                                                                                                                                                       | 21-2                                                    |

|                                                                                                                                                                                                                                                                |                                                         |

| 21.1 電気的特性 ( VCCE = 5V 時 )                                                                                                                                                                                                                                     | 21-2                                                    |

| 21.1 電気的特性(VCCE = 5V 時)                                                                                                                                                                                                                                        | 21-2<br>21-3                                            |

| 21.1 電気的特性 ( VCCE = 5V 時 )                                                                                                                                                                                                                                     | 21-2<br>21-3<br>21-5                                    |

| 21.1 電気的特性 ( VCCE = 5V 時 )                                                                                                                                                                                                                                     | 21-2<br>21-3<br>21-5<br>21-5                            |

| 21.1 電気的特性 ( VCCE = 5V 時 )                                                                                                                                                                                                                                     | 21-2<br>21-3<br>21-5<br>21-5<br>21-10                   |

| 21.1 電気的特性 (VCCE = 5V 時)         21.1.1 絶対最大定格         21.1.2 推奨動作条件         21.1.3 DC 特性         21.1.3.1 電気的特性         21.1.3.2 フラッシュ関連電気的特性                                                                                                                 | 21-2<br>21-3<br>21-5<br>21-5<br>21-10                   |

| 21.1 電気的特性 (VCCE = 5V 時)                                                                                                                                                                                                                                       | 21-2<br>21-3<br>21-5<br>21-5<br>21-10<br>21-11<br>21-12 |

| 21.1 電気的特性 (VCCE = 5V 時)                                                                                                                                                                                                                                       | 21-2<br>21-3<br>21-5<br>21-5<br>21-10<br>21-11<br>21-12 |

| 21.1 電気的特性 (VCCE = 5V 時)                                                                                                                                                                                                                                       | 21-221-321-521-521-1021-1121-1221-12                    |

| 21.1 電気的特性 (VCCE = 5V 時)         21.1.1 絶対最大定格         21.1.2 推奨動作条件         21.1.3 DC 特性         21.1.3.1 電気的特性         21.1.3.2 フラッシュ関連電気的特性         21.1.4 A-D 変換特性         21.2.1 絶対最大定格         21.2.2 推奨動作条件         21.2.3 DC 特性         21.2.3.1 電気的特性 | 21-221-321-521-521-1021-1121-1221-1221-1321-15          |

| 21.1 電気的特性 (VCCE = 5V 時)                                                                                                                                                                                                                                       | 21-221-321-521-521-1021-1121-1221-1221-1321-15          |

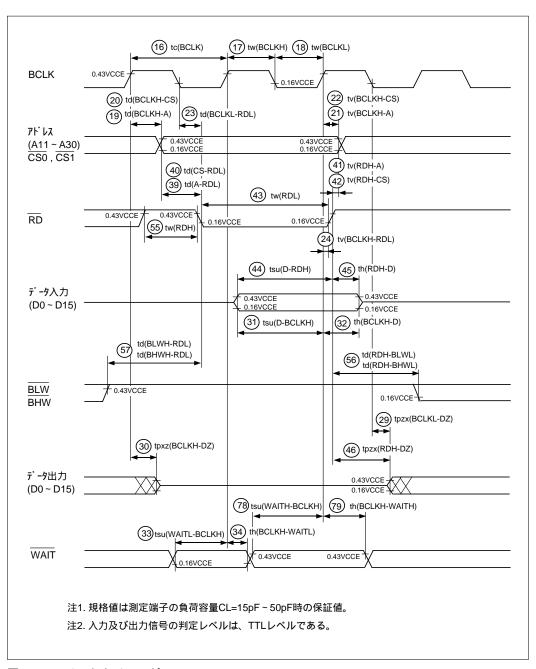

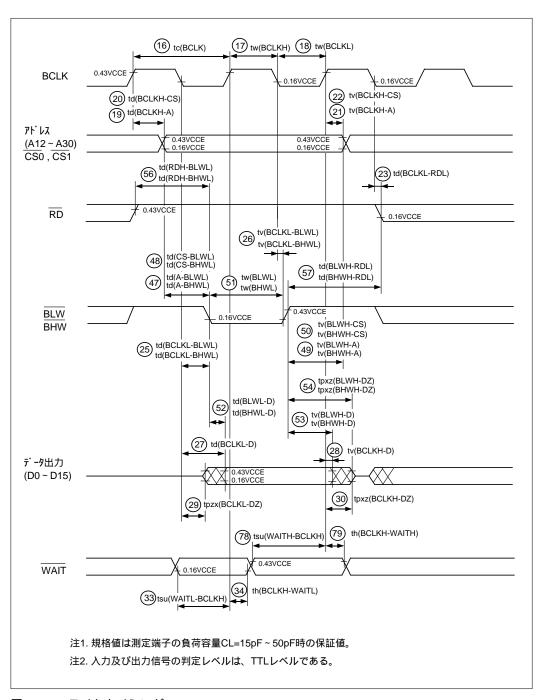

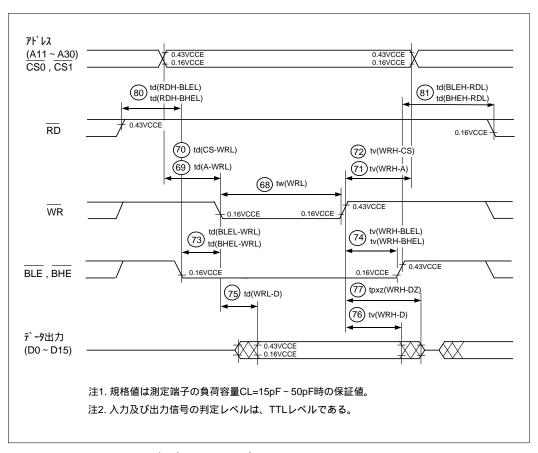

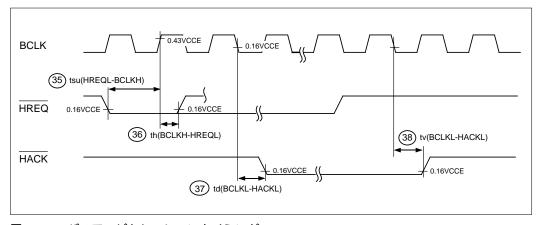

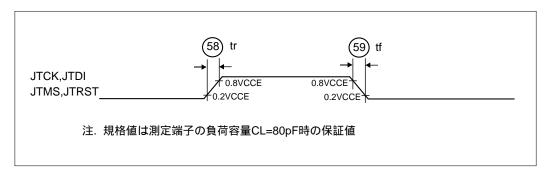

| 21.3 AC 特性                         | 21-20          |

|------------------------------------|----------------|

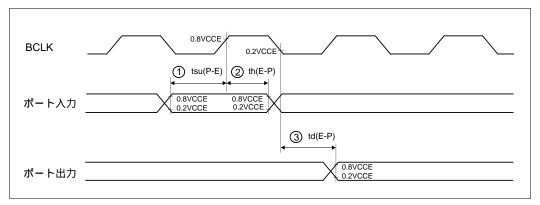

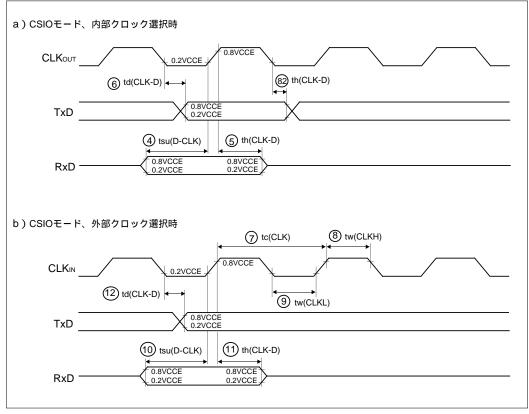

| 21.3.1 タイミング必要条件                   | 21-20          |

| 21.3.2 スイッチング特性                    | 21-24          |

| 21.3.3 AC 特性                       | 21-27          |

|                                    |                |

| 第 22 章 標準特性                        |                |

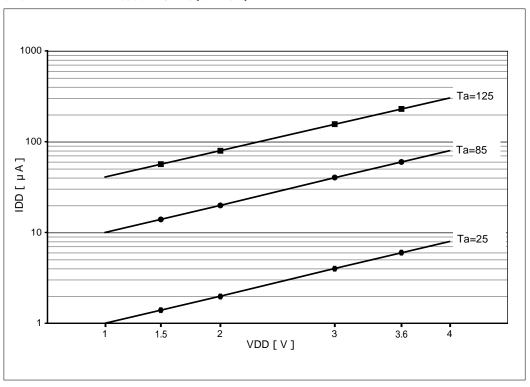

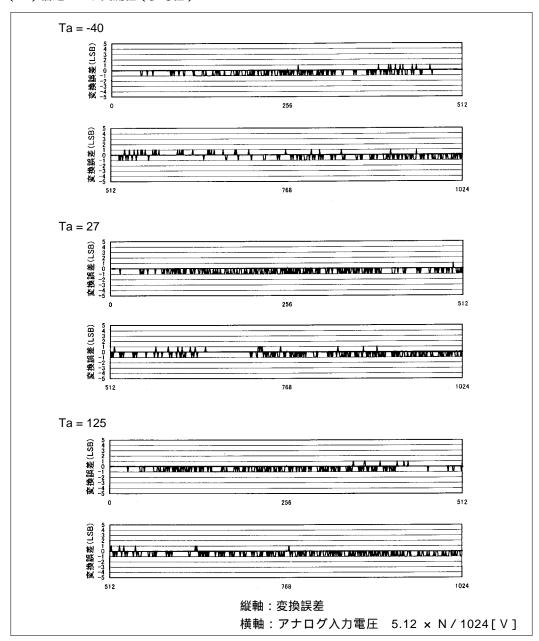

| 22.1 A-D 変換特性                      | 22-2           |

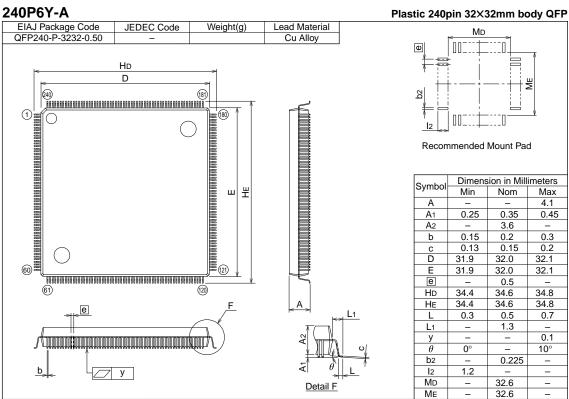

| 付録 1 機械的仕様                         |                |

| 付録 1.1 外形寸法                        | 付録 1-2         |

| 付録2 命令処理時間                         |                |

| 付録 2.1 32170/32174 命令処理時間          | 付録 2-2         |

| 付録3 ノイズに関する注意事項                    |                |

| 付録 3.1 ノイズに関する注意事項                 | 付録 3-2         |

| 付録3.1.1 配線長の短縮                     | 付録 3-2         |

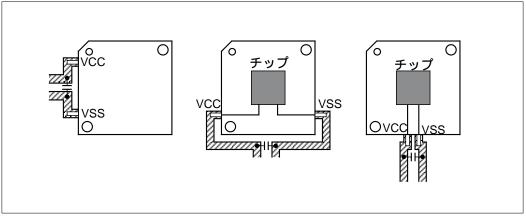

| 付録 3.1.2 VSS-VCC ライン間へのバイパスコンデンサ挿入 | 付録 3-4         |

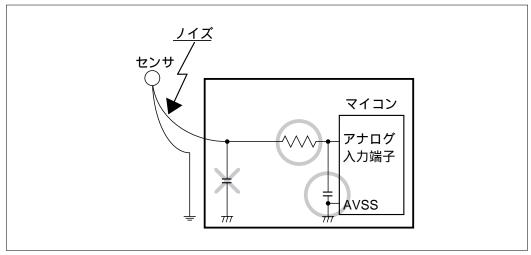

| 付録 3.1.3 アナログ入力端子の配線処理             | 付録 3-5         |

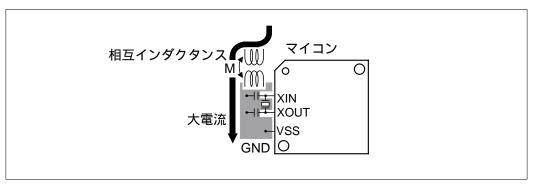

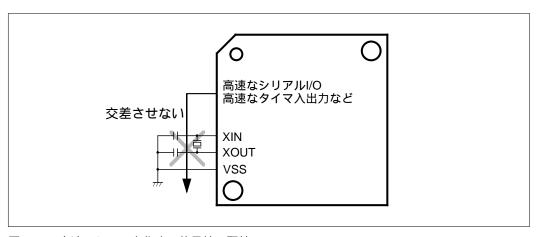

| 付録 3.1.4 発振子への配慮                   | 付録 3-6         |

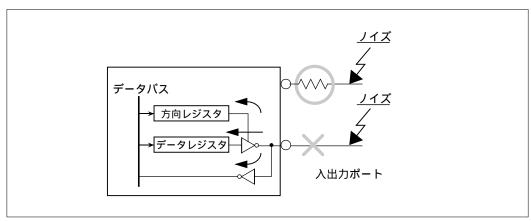

| 付録 3.1.5 入出力ポート処理                  | 付録 3-8         |

| 付録4 未使用端子の処理                       |                |

| (大会) 4.4 一大体中地での加速点                | / <del>-</del> |

# 第1章

# 概要

- 1.1 32170/32174の概要

- 1.2 ブロック図

- 1.3 端子機能

- 1.4 端子配置

#### 1.1 32170/32174の概要

#### 1.1.1 M32RファミリCPUコア

#### (1) RISC アーキテクチャの採用

32170/32174は、32ビットRISCシングルチップマイクロコンピュータで、M32Rファミリ CPUコア(以下M32Rと略)を中心にして、フラッシュメモリ、RAM、および各種周辺機能を1チップに集積しています。

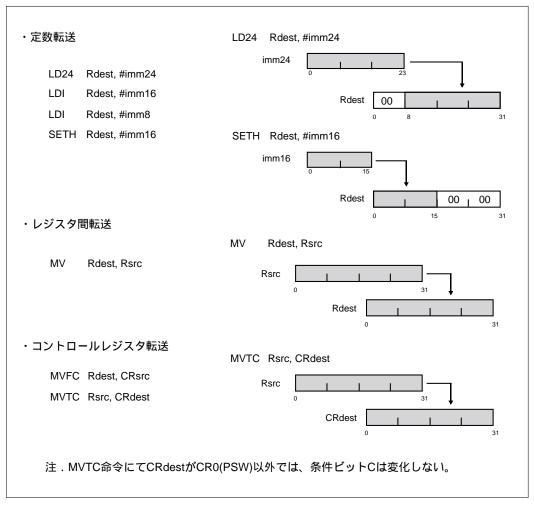

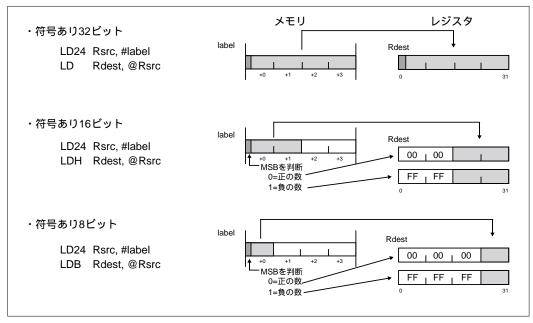

M32Rは、RISCアーキテクチャを採用しています。メモリアクセスはロード命令とストア命令により行い、各種の演算はレジスタ間演算命令で実行します。内部には32ビット汎用レジスタを16本備え、命令数は83あります。

M32Rは、通常のロード命令、ストア命令に加えて、ロード&アドレス更新、ストア&アドレス更新といった複合命令もサポートしています。これらの命令はデータ転送の高速化に有効です。

#### (2)5ステージのパイプライン処理

M32Rは、命令フェッチ、デコード、実行、メモリアクセス、ライトバックの5ステージのパイプライン処理により、命令を処理します。ロード命令、ストア命令、レジスタ間演算命令だけでなく、ロード&アドレス更新、ストア&アドレス更新といった複合命令も1サイクルで実行します。

命令は、フェッチされた順に実行ステージに投入されますが、先に投入されたロード命令やストア命令の実行がメモリアクセスのウエイトサイクルの挿入により延びた場合には、後続のレジスタ間演算命令が先に実行される場合があります。M32Rは、このような「out-of-order-completion」などの採用により、クロックサイクルをむだにしない命令実行制御を行います。

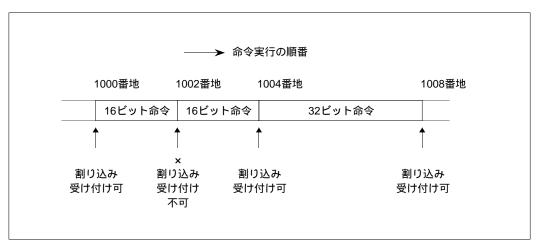

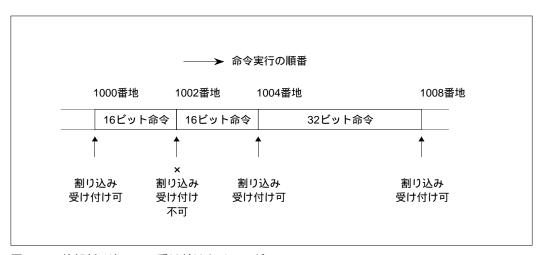

#### (3) コンパクトな命令コード

M32Rの命令には、16ビット長命令と32ビット長命令の2つの形式があります。特に16ビット長の命令形式の採用により、プログラムのコードサイズを抑えることができます。

32ビット長命令には、実行中の命令のアドレスから±32Mバイトの範囲に直接分岐することができる命令があり、アドレス空間がセグメント化されたアーキテクチャに比べ、プログラミングが容易になっています。

#### 1.1.2 積和演算機能の内蔵

#### (1) 高速乗算器の内蔵

M32Rは、32ビット×16ビットの高速乗算器の内蔵により、32ビット×32ビットの整数乗算命令を3サイクル CPUクロック40MHz時、1サイクルは25ns)で実行します。

#### (2) DSP に匹敵する積和演算命令をサポート

M32Rは、56ビットのアキュムレータによる積和演算命令(または乗算命令)として、次の4つをサポートしており、いずれも1サイクルで実行できます。

レジスタの上位16ビット×レジスタの上位16ビット レジスタの下位16ビット×レジスタの下位16ビット レジスタの32ビット全体×レジスタの上位16ビット レジスタの32ビット全体×レジスタの下位16ビット

M32Rは、アキュムレータに格納された値を16ビットまたは32ビットに丸める命令や、アキュムレータ値の桁合わせのため、シフトしてレジスタに格納する命令を備えています。これらの命令も1サイクルで実行するため、ロード&アドレス更新、ストア&アドレス更新などの高速データ転送命令と組み合わせて使うことにより、DSPに匹敵するデータ処理能力を発揮できます。

#### 1.1.3 フラッシュメモリとRAMの内蔵

32170/32174は、ノーウエイトでアクセスが可能なのフラッシュメモリとRAMを内蔵しており、高速な組み込みシステムを構成できます。

内蔵フラッシュメモリは、プリント基板に実装した状態での書き込み(オンボード書き込み)が可能です。フラッシュメモリの採用で開発時のチップがそのまま量産に使え、試作から量産へプリント基板を変更することなくスムーズに移行することができます。

内蔵フラッシュメモリは、100回書き換えることができます。

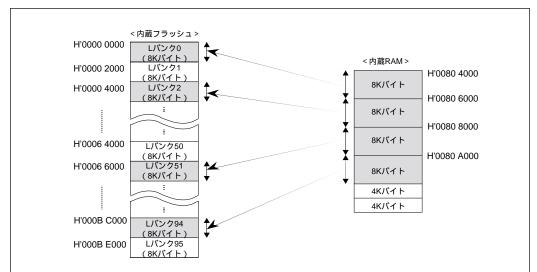

内蔵フラッシュメモリは、疑似フラッシュエミュレーション機能を備えており、内蔵フラッシュメモリの一部に疑似的に内蔵RAMをマッピングすることができます。この機能と内蔵リアルタイムデバッガ(RTD)を組み合わせることにより、ROMテーブル上のデータチューニングが容易に行えます。

内蔵RAMは、RTD(リアルタイムデバッガ)を使用することで、M32Rとは独立して外部からデータの読み出しや書き替えができます。外部との通信は、RTDの専用クロック同期形シリアルI/Oで行います。

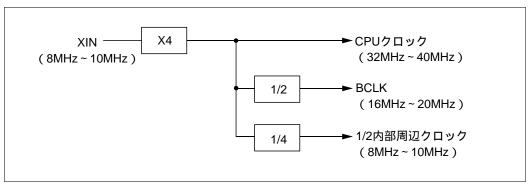

#### 1.1.4 クロック逓倍回路の内蔵

32170/32174は、入力したクロック信号の周波数を内部で4倍(内部周辺クロックは2倍)にして使用しており、入力クロック周波数が10.0MHzの場合、CPUクロック周波数は40MHz、内部周辺クロック周波数は20MHzとなります。

#### 1.1.5 強力な周辺機能の内蔵

#### (1) マルチジャンクションタイマ (MJT) の内蔵

マルチジャンクションタイマは、下記のタイマにより構成しています。

16ビット出力系タイマ35チャネル

16ビット入出力系タイマ10チャネル

16ビット入力系タイマ11チャネル(4逓倍カウンタ3チャネル内蔵)

32ビット入力系タイマ8チャネル

各タイマは複数のモードを持ち、用途に応じた選択が可能です。

マルチジャンクションタイマは、内部にクロックバス、入力イベントバス、出力イベントバスを持ち、複数のタイマを内部で組み合わせて利用できます。これによりフレキシブルなタイマ機能の活用が可能です。

出力系タイマ(TOP)は補正機能を備えています。この機能によりカウント中のタイマのカウント値を自由に増減させることができ、リアルタイムな出力制御を実現できます。

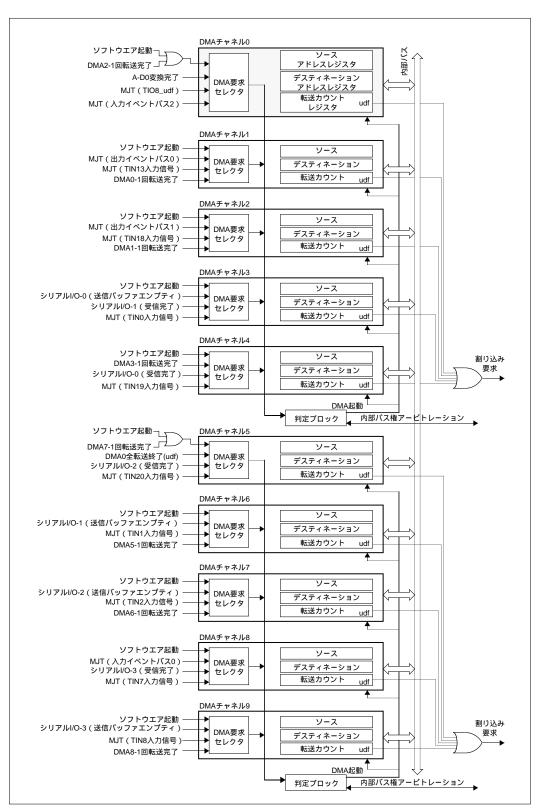

#### (2) 10 チャネルの DMA 内蔵

DMAは10チャネル内蔵しており、内蔵周辺I/O間または内蔵周辺I/Oと内蔵RAM間のデータ転送をサポートします。DMA転送要求はソフトウエアのほか、内蔵周辺I/O(A-D変換器、MJT、シリアルI/O)の発生する信号をトリガとすることができます。

DMAチャネル間のカスケード接続(あるチャネルの転送終了で他のチャネルのDMA転送を起動)もサポートしており、CPUに負荷をかけることなく高度な転送処理が可能です。

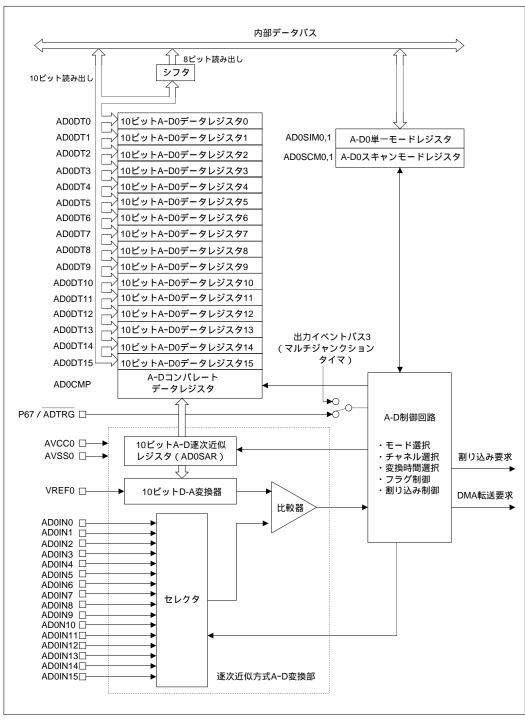

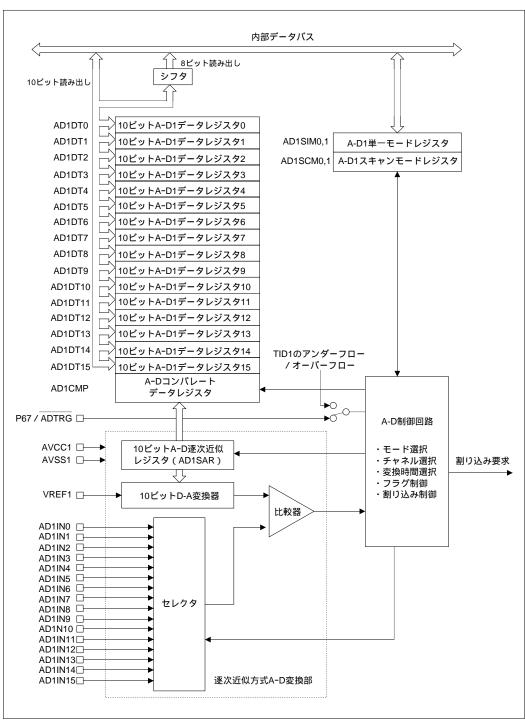

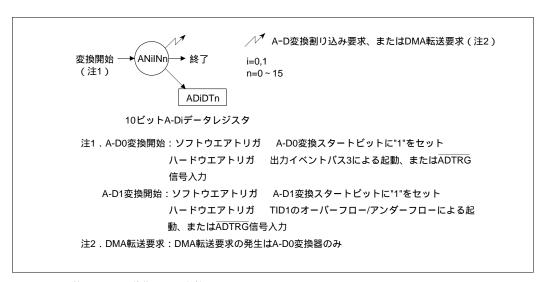

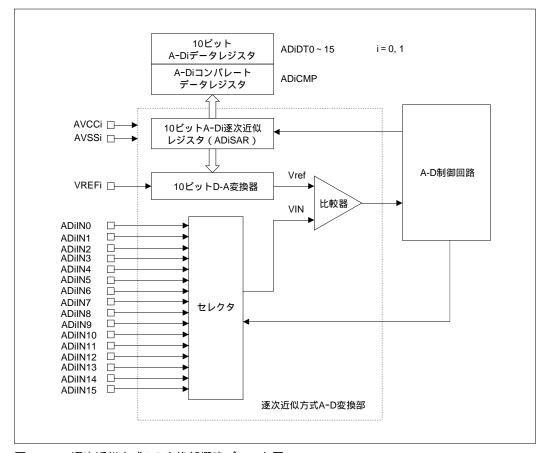

#### (3) 16 チャネルの A-D 変換器内蔵

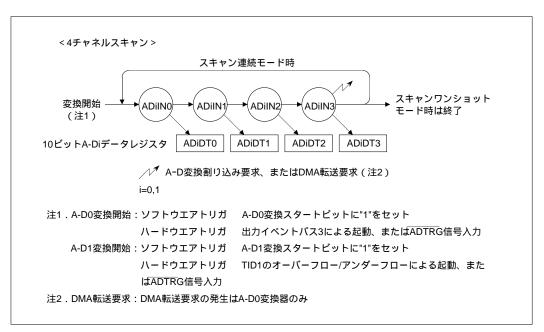

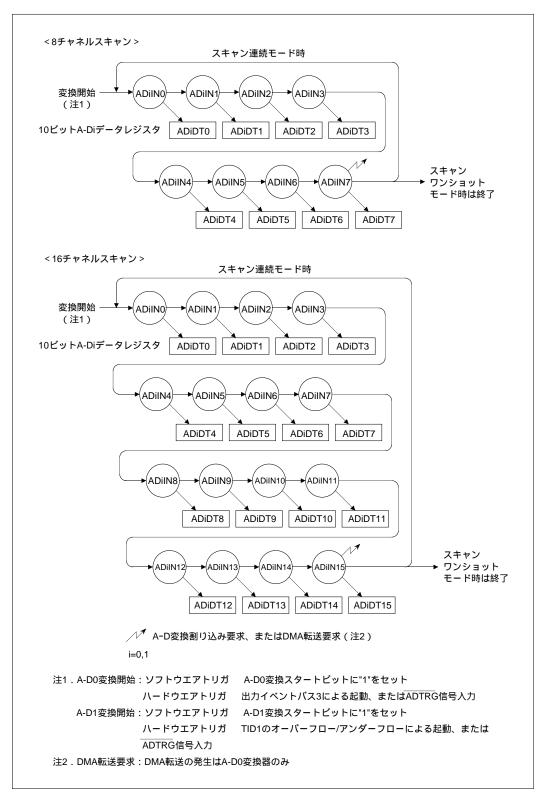

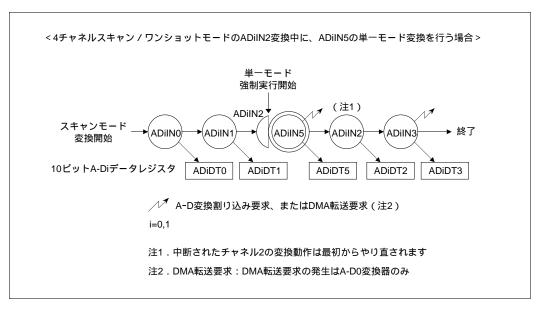

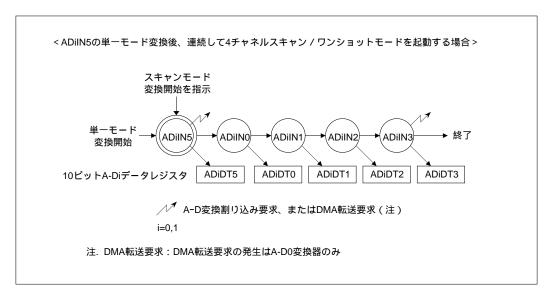

10ビット分解能で、16チャネルのA-D変換器を2つ内蔵しています。各チャネル単独のA-D変換のほか、4チャネル、8チャネルまたは16チャネルを1つのグループとした連続的なA-D変換も可能です。

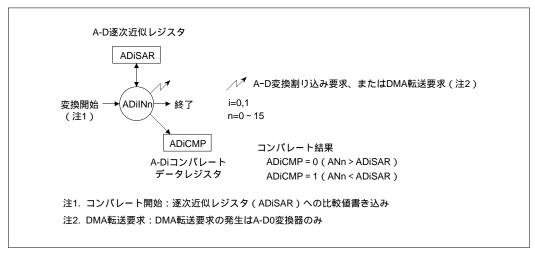

通常のA-D変換のほかに、ある設定値とのA-D変換の結果を比較して、その大小を判別するコンパレータモードをサポートしています。

A-D変換の終了時には割り込みを発生するほか、DMA転送要求を発生することもできます。

A-D変換結果の読み出し機能として、8ビットと10ビットの両モードをサポートしています。

#### (4) 高速シリアル I/O

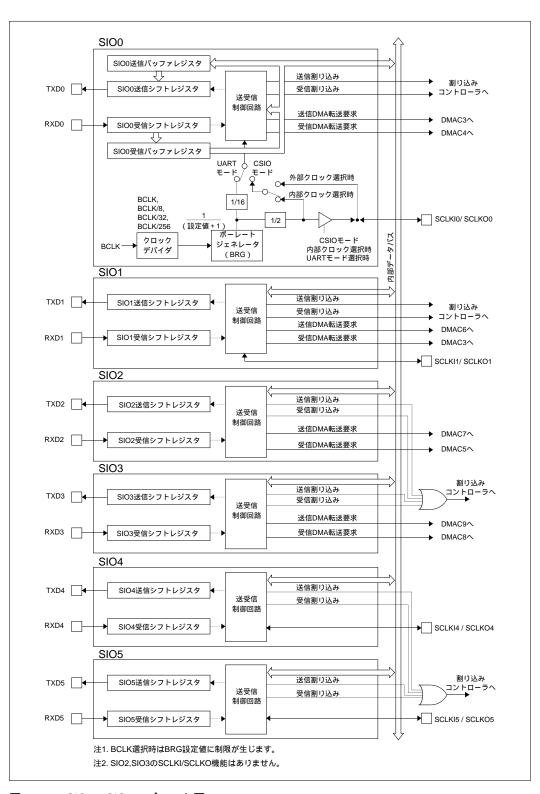

シリアルI/Oは6チャネルを内蔵しており、クロック同期形シリアルI/O、またはUARTに設定できます。

転送速度はクロック同期形シリアルI/O時に2Mビット/秒の高速データ転送が可能です。

データ受信完了時、または送信レジスタが空になった時に、DMAの転送要求信号を発生する機能を持ちます。

#### (5) リアルタイムデバッガ (RTD) の内蔵

リアルタイムデバッガ(RTD)は、M32R/Eの内蔵RAMを外部から直接アクセスする機能を提供します。外部との通信は、専用のクロック同期形シリアルI/Oで行います。

RTDを使うことで、M32Rとは独立して外部から内蔵RAMの内容を読み出したり、データの書き替えが可能になります。

RTDを使用したデータ送受信の完了を知らせるための、RTD割り込みを発生することができます。

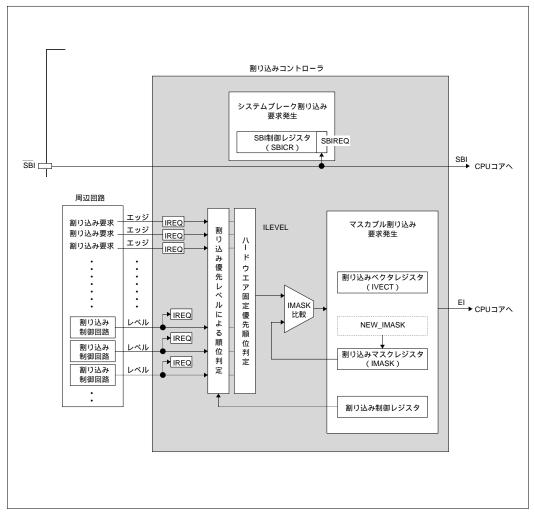

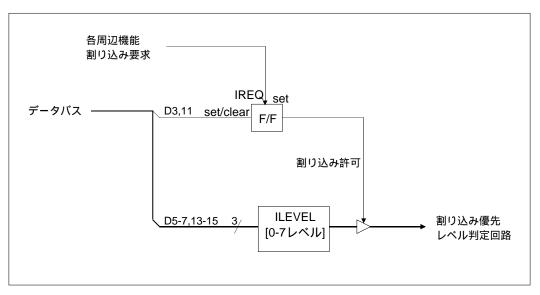

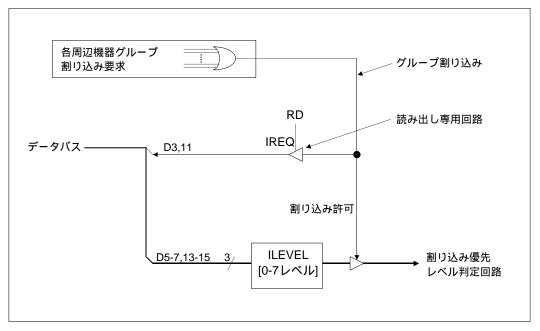

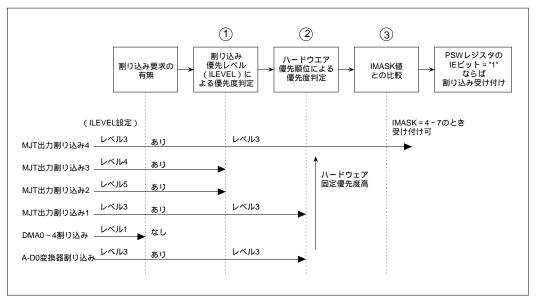

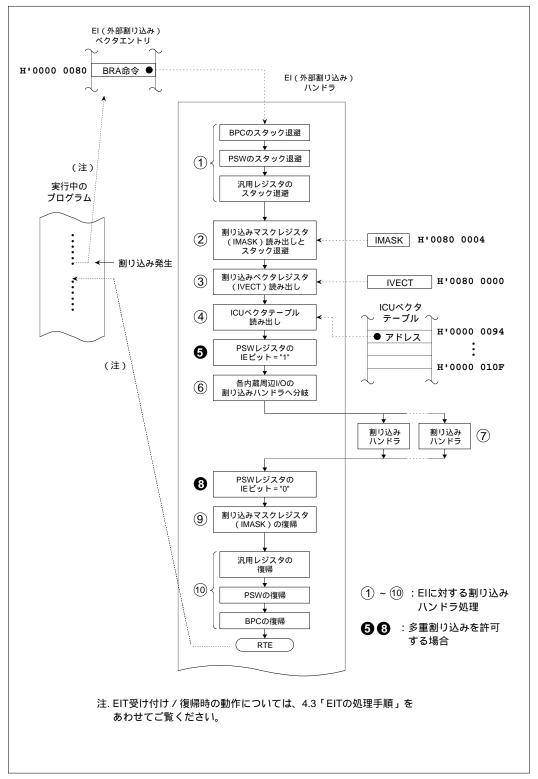

#### (6)8レベルの割り込みコントローラ

割り込みコントローラは、各内蔵周辺I/Oからの割り込み要求を、割り込み禁止状態を含めて8レベルの優先順位を設けて管理します。また、電源断検出やウォッチドックタイマで発生した外部割り込み要求をシステムブレーク割り込み(SBI)として受け付けることができます。

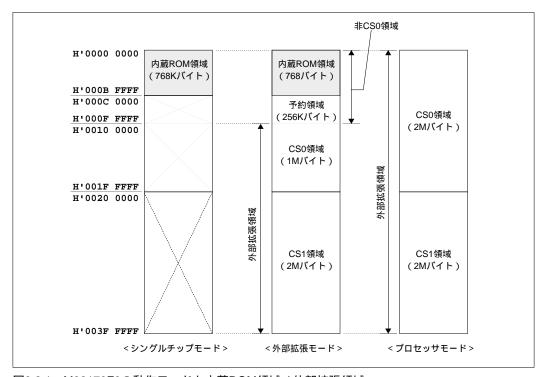

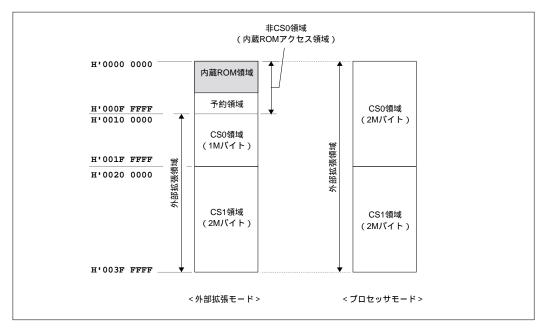

#### (7) 3 つの動作モード

M32R/Eは、シングルチップモード、外部拡張モードおよびプロセッサモードの3つの動作モードを備えています。M32R/Eのアドレス空間と外部端子機能は各モードに応じて切り替わります。モードの設定は、MOD0、MOD1端子で行います。

#### (8) ウエイトコントローラ

ウエイトコントローラは、外付けデバイスのアクセスをサポートします。シングルチップモード以外のモードでは、外部拡張領域は最大4Mバイトの空間が用意されています。

#### 1.1.6 Full-CAN機能内蔵

32170/32174は、CAN specification 2.0B active準拠のCANモジュールを内蔵しており、16本のメッセージスロットを有しています。

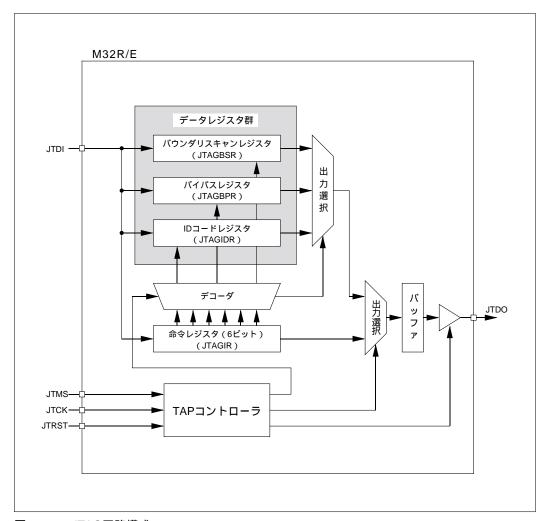

#### 1.1.7 デバッグ機能内蔵

32170/32174は、JTAGインタフェースをサポートしています。このJTAGインタフェースを用いてバウンダリスキャンテストが可能です。

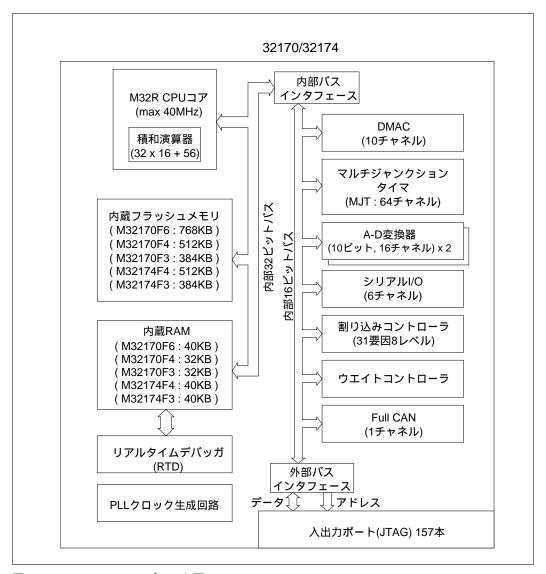

### 1.2 ブロック図

図1.2.1に32170/32174のブロック図を示し、それぞれのブロックの特長を表1.2.1~表1.2.3に示します。

図1.2.1 32170/32174のブロック図

#### 表1.2.1 M32RファミリCPUコアの特長

| 機能ブロック   | 特長                             |

|----------|--------------------------------|

| M32Rファミリ | パス仕様                           |

| CPUコア    | 基本バスサイクル: 25ns( CPUクロック40MHz時) |

|          | 論理アドレス空間:4Gバイトリニア              |

|          | 外部拡張領域:最大4Mバイト                 |

|          | 外部データバス:16ビット                  |

|          | インプリメンテーション:5段パイプライン方式         |

|          | コア内部32ビット構成                    |

|          | レジスタ構成                         |

|          | 汎用レジスタ:32ビット×16本               |

|          | 制御レジスタ:32ビット×5本                |

|          | 命令セット                          |

|          | 16ビット / 32ビット命令形式              |

|          | 83命令 / 9アドレッシングモード             |

|          | 積和演算器内蔵(32×16+56)              |

### 表1.2.2 内蔵メモリの特長

| 機能ブロック   | 特長                                         |

|----------|--------------------------------------------|

| RAM      | 容量                                         |

|          | M32170F6, M32174F4, M32174F3 : 40Kバイト      |

|          | M32170F4, M32170F3 : 32Kバイト                |

|          | ノーウエイトアクセス                                 |

|          | RTD( リアルタイムデバッガ )を使用することで、M32Rとは独立して外部から内蔵 |

|          | RAMのデータ読み出しや書き替えが可能                        |

| フラッシュメモリ | 容量                                         |

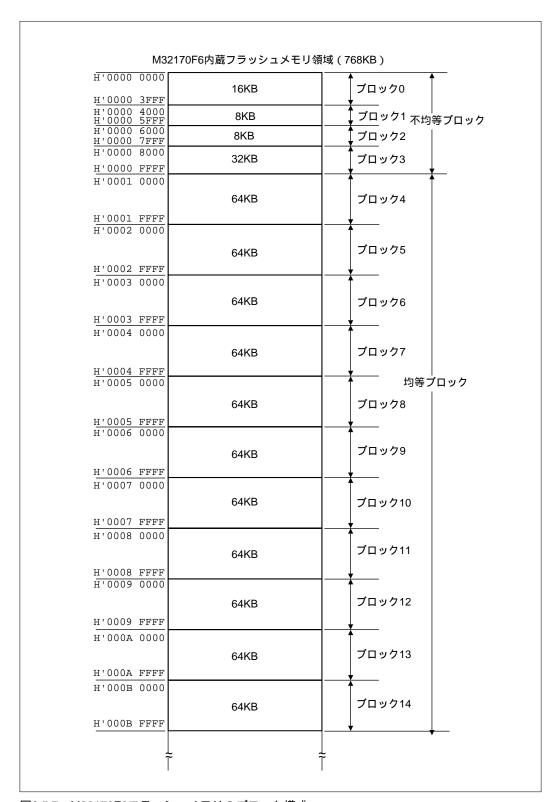

|          | M32170F6 : 768Kバイト                         |

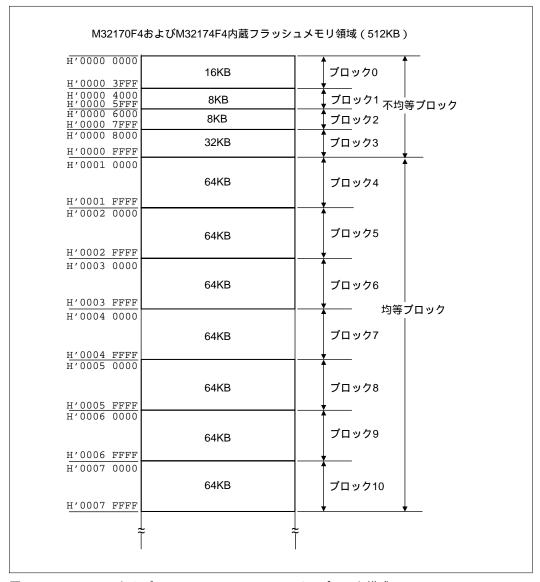

|          | M32170F4, M32174F4:512Kバイト                 |

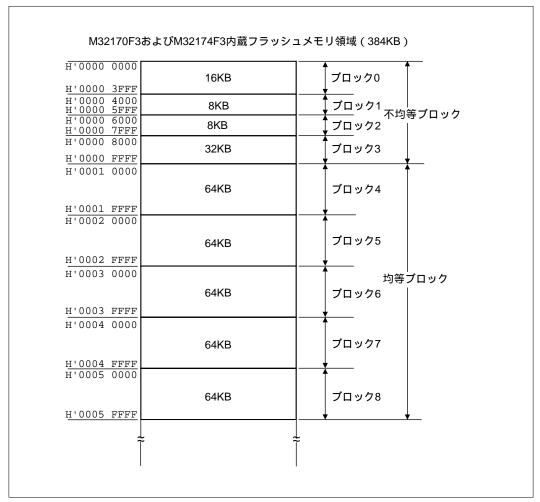

|          | M32170F3, M32174F3:384Kバイト                 |

|          | ノーウエイトアクセス                                 |

|          | 書き換え回数:100回                                |

|          | 書き換え回数:100回<br>                            |

#### 表1.2.3 内蔵周辺I/Oの特長

| 機能ブロック         | 特長                                                                                                                                            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| DMA            | 10チャネルのDMAC<br>内蔵周辺I/O間、内蔵RAM間、または内蔵周辺I/Oと内蔵RAM間の転送サポート<br>内蔵周辺I/Oとのコンビネーションにより、高度なDMA転送が可能<br>DMA各チャネルのカスケード接続 あるチャネルの転送終了で他のチャネルの起動)<br>が可能 |

| マルチ<br>ジャンクション | 64チャネルの多機能タイマ<br>出力系タイマ35チャネル、入出力系タイマ10チャネル、16ビット入力系タイマ11<br>チャネル、32ビット入力系タイマ8チャネル内蔵<br>各チャネルの相互接続によるフレキシブルなタイマ構成が可能                          |

| A-D変換器         | 16チャネル、10ビット分解能A-D変換器 X 2<br>コンパレータモード内蔵<br>A-D変換終了時の割り込みまたはDMA転送の起動が可能<br>8ビット/10ビット変換結果読み出しが可能                                              |

| シリアル/(0        | 6チャネルのシリアルI/O<br>クロック同期形シリアルI/O、またはUARTに設定可能<br>クロック同期時2Mビット/秒、UART時156Kビット/秒の高速データ転送                                                         |

| リアルタイム<br>デバッガ | 外部からのコマンド入力による、CPUとは独立した内蔵RAMの書き換え/モニタ機能専用クロック同期シリアルポート装備                                                                                     |

| 割り込み<br>コントローラ | 内蔵周辺I/Oからの割り込み要求管理<br>割り込み禁止状態を含めて8レベルの優先順位                                                                                                   |

| ウエイトコントローラ     | 外部拡張領域のアクセスに対するウエイト制御<br>ソフトウエア設定による1~4ウエイト挿入 + 外部WAIT信号入力によるウエイト延長                                                                           |

| クロックPLL        | 4逓倍のクロック発生回路<br>最大CPUクロック40MHz(CPU,内蔵ROM,内蔵RAMのアクセス)<br>最大内部周辺クロック20MHz(周辺モジュールのアクセス)<br>最大外部入力クロック周波数は10.0MHz                                |

| CAN            | 16本のメッセージスロット                                                                                                                                 |

| JTAG           | バウンダリスキャン機能                                                                                                                                   |

表1.2.4 形名一覧

| 形名          | RAM容量(Kバイト) | ROM容量(Kバイト) | パッケージ形名 | ピン数 |

|-------------|-------------|-------------|---------|-----|

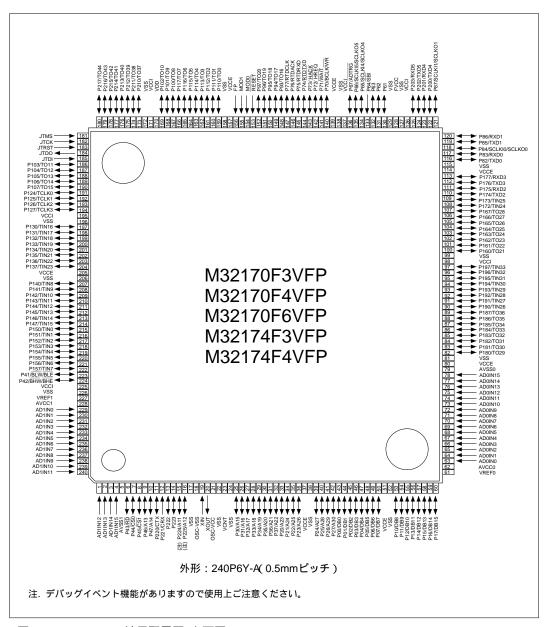

| M32170F3VFP | 32          | 384         | 240QFP  | 240 |

| M32170F4VFP | 32          | 512         | 240QFP  | 240 |

| M32170F6VFP | 40          | 768         | 240QFP  | 240 |

| M32170F3VWG | 32          | 384         | 255FBGA | 255 |

| M32170F4VWG | 32          | 512         | 255FBGA | 255 |

| M32170F6VWG | 40          | 768         | 255FBGA | 255 |

| M32174F3VFP | 40          | 384         | 240QFP  | 240 |

| M32174F4VFP | 40          | 512         | 240QFP  | 240 |

| M32174F3VWG | 40          | 384         | 255FBGA | 255 |

| M32174F4VWG | 40          | 512         | 255FPGA | 255 |

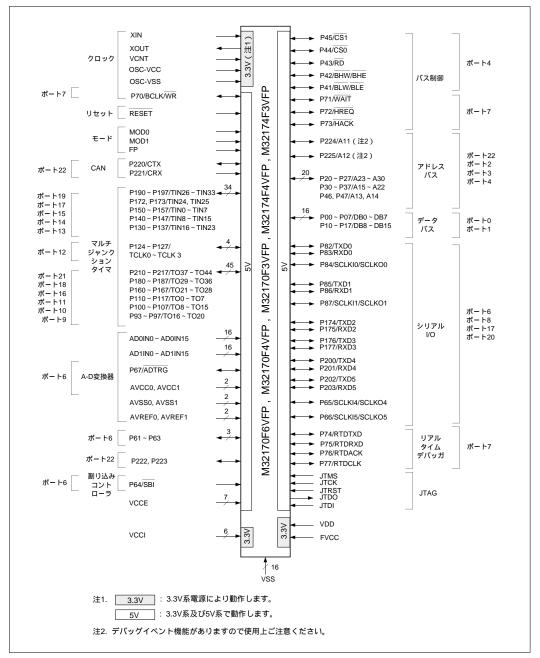

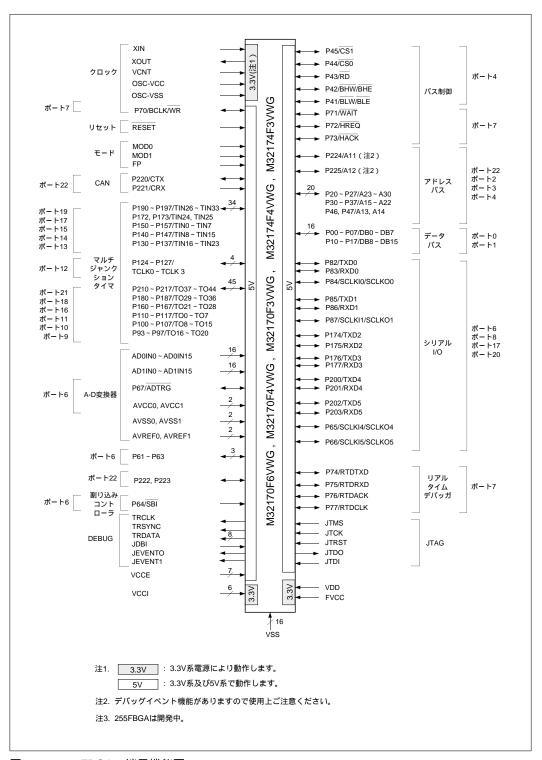

#### 1.3 端子機能

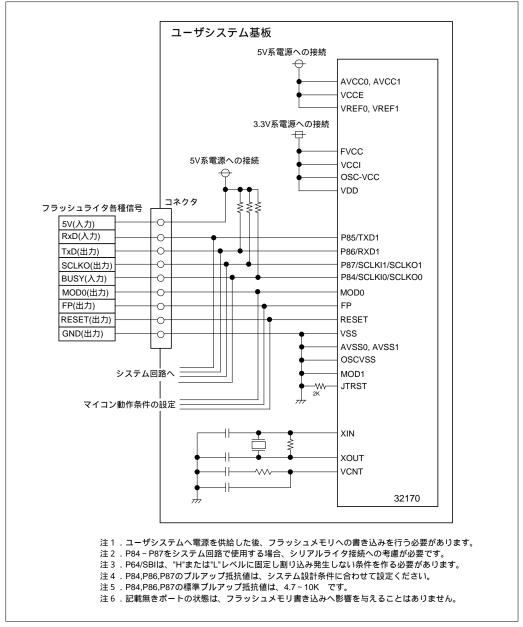

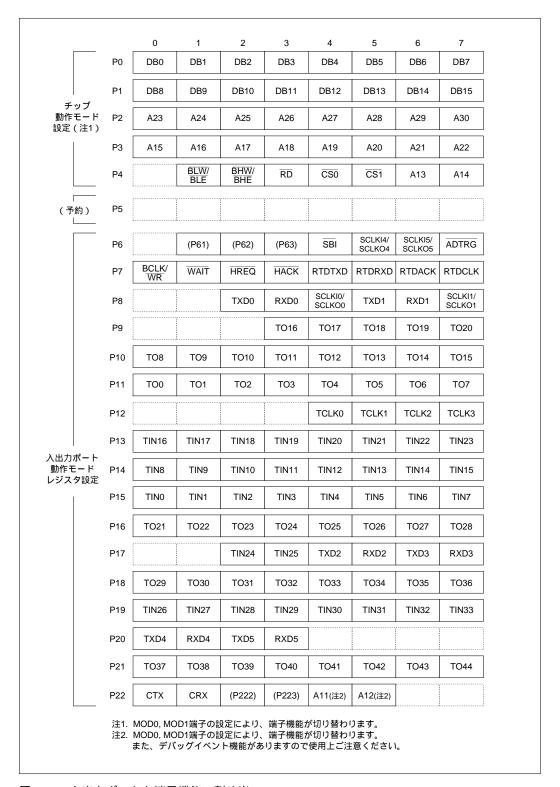

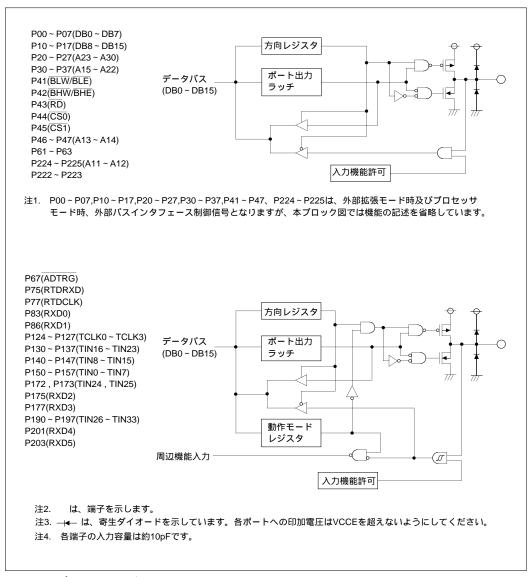

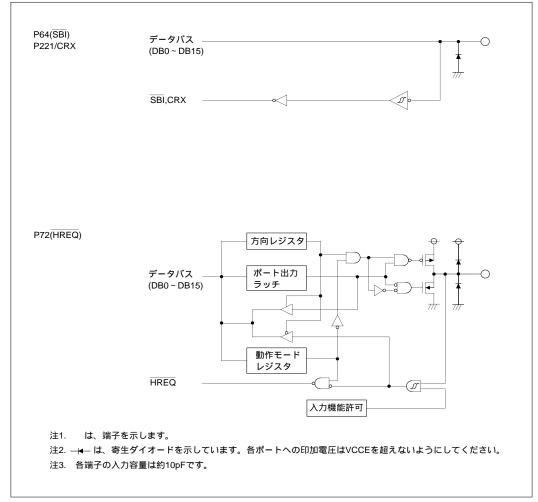

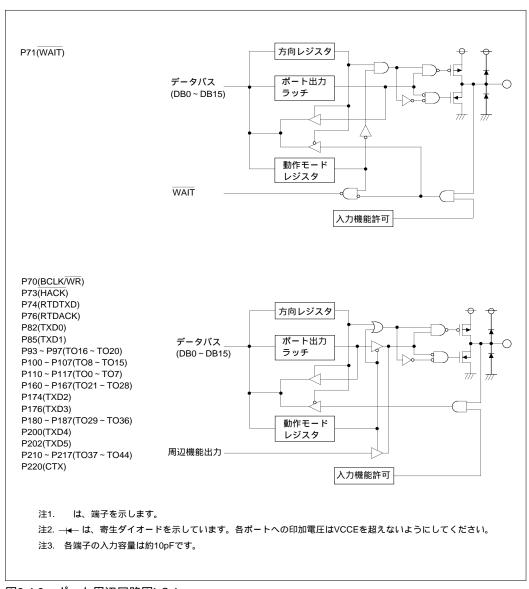

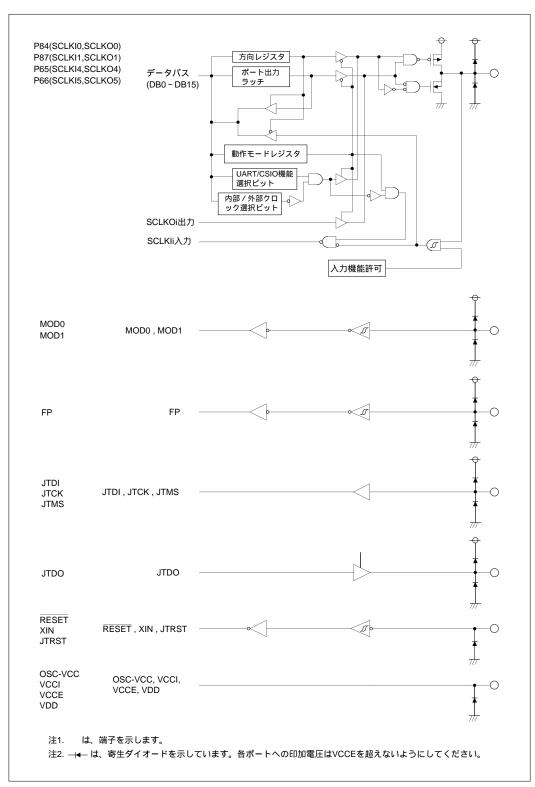

図1.3.1に240QFPの端子機能図を、図1.3.2に255FBGAの端子機能図を示し、表1.3.1に 端子機能説明を、表1.3.2に255FBGAのデバッグ専用端子機能説明を示します。

図1.3.1 240QFPの端子機能図

図1.3.2 255FBGAの端子機能図

表1.3.1 端子機能説明(1/6)

| 種類   | 端子名       | 名称      | 入出力 | 機能                                 |                            |        |                    |  |  |

|------|-----------|---------|-----|------------------------------------|----------------------------|--------|--------------------|--|--|

| 電源   | VCCE      | 電源      | -   | 外部I/0                              | 外部I/Oポートへの供給電源(5Vまたは3.3V)。 |        |                    |  |  |

|      | VCCI      | 電源      | -   | 内部口                                | 内部ロジックへの供給電源( 3.3V )。      |        |                    |  |  |

|      | VDD       | RAM電源   | -   | 内蔵R                                | 内蔵RAMバックアップ用電源端子( 3.3V )。  |        |                    |  |  |

|      | FVCC      | FLASH電源 | -   | 内蔵フラッシュメモリ用電源端子(3.3V)。             |                            |        |                    |  |  |

|      | VSS       | グランド    | -   | vssit                              | VSSはすべてグランド( GND )に接続します。  |        |                    |  |  |

| クロック | XIN,      | クロック    | 入力  | クロッ                                | ク入出力                       | 端子です   | 。PLLによる逓倍回路を内蔵して   |  |  |

|      | XOUT      |         | 出力  | おり、                                | 動作周波                       | 数の1/40 | D周波数のクロックを入力します    |  |  |

|      |           |         |     | (CPU?                              | フロック4                      | OMHz時: | XIN入力 = 10.0MHz )。 |  |  |

|      | BCLK/WR   | システム    | 出力  | BCLK                               | 端子を選打                      | 沢した場合  | 合、外部入力クロックの2倍の周波   |  |  |

|      |           | クロック /  |     | 数のク                                | ロックを                       | 出力しま   | す( 外部入力クロック10MHz時: |  |  |

|      |           | ライト     |     | BCLK                               | 出力 = 20N                   | MHz)。外 | 部で同期設計を行う場合に使用し    |  |  |

|      |           |         |     | ます。                                |                            |        |                    |  |  |

|      |           |         |     |                                    | WR端子を選択した場合、外部デバイスへのライト時に有 |        |                    |  |  |

|      |           |         |     | 効なデータが転送されるバイト位置を示します。             |                            |        |                    |  |  |

|      | OSC-VCC   | 電源      | -   | PLL回路の電源です。OSC-VCCは電源(3.3V)に接続します。 |                            |        |                    |  |  |

|      | OSC-VSS   | グランド    | -   | OSC-VSSはグランドに接続します。                |                            |        |                    |  |  |

|      | VCNT      | PLL制御   | 入力  | PLL回路の制御端子で、抵抗とコンデンサを接続します。        |                            |        |                    |  |  |

|      |           |         |     | (外付け回路については、18.1.1「発振回路例」をご覧く      |                            |        |                    |  |  |

|      |           |         |     | ださい                                | 1)                         |        |                    |  |  |

| リセット | RESET     | リセット    | 入力  | 内部回                                | 路をリセ                       | ットしま   | す。                 |  |  |

| モード  | MOD0      | モード     | 入力  | 動作モ                                | ードを設                       | 定します   |                    |  |  |

|      | MOD1      |         |     | FP                                 | MOD0                       | MOD1   | モード                |  |  |

|      |           |         |     | Х                                  | 0                          | 0      | シングルチップモード         |  |  |

|      |           |         |     | Χ                                  | 0                          | 1      | 外部拡張モード            |  |  |

|      |           |         |     | 0                                  | 1                          | 0      | プロセッサモード           |  |  |

|      |           |         |     | 1                                  | 1                          | 0      | (ブートモード) (注)       |  |  |

|      |           |         |     | Х                                  | 1                          | 1      | (Reserved)         |  |  |

| アドレス | A11 ~ A30 | アドレス    | 出力  | 最大2N                               | /Bメモリ                      | 空間を2系  |                    |  |  |

| バス   |           | バス      |     | スA11~A30 )を持っています。A31は出力されません。     |                            |        |                    |  |  |

注. ブートモードについては、第6章「内蔵メモリ」をご覧ください。

表1.3.1 端子機能説明(2/6)

| 種類                 | 端子名                 | 名称                      | 入出力 | 機能                                                                                                                 |  |  |  |  |

|--------------------|---------------------|-------------------------|-----|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| データ<br>バス          | DB0 ~<br>DB15       | データ<br>バス               | 入出力 | 外部デバイス接続用の16ビットデータバスです。<br>ライトサイクルでは16ビットのデータバスのうち、有効な書                                                            |  |  |  |  |

|                    |                     |                         |     | き込みを行うバイト位置をBHW/BHE, BLW/BLEとして出力<br>します。リードサイクルでは常に16ビットのデータバスを<br>読み込みます。ただしM32Rの内部へは、有効なバイト位<br>置のデータのみが転送されます。 |  |  |  |  |

| バス制御               | CS0,<br>CS1         | チップ<br>セレクト             | 出力  | 外部デバイスのチップセレクト信号です。チップセレクト<br>信号の出力される領域については、第3章「アドレス空間」を<br>ご覧ください。                                              |  |  |  |  |

|                    | RD                  | リード                     | 出力  | 外部デバイスのリード時に出力される信号です。                                                                                             |  |  |  |  |

|                    | BHW/BHE             | バイトハイ<br>ライト/イネーブ/      | 出力  | 外部デバイスへのライト時に、有効なデータが転送される<br>バイト位置を示します。BHW/BHEが上位アドレス側 D0                                                        |  |  |  |  |

|                    | BLW/BLE             | E バイトロー 出力<br>ライト/イネーブル |     | D7が有効) BLW/BLEが下位アドレス側 D8~D15が有効)<br>に対応しています。                                                                     |  |  |  |  |

| -<br>!             | WAIT                | ウエイト                    | 入力  | M32Rが外部デバイスをアクセスした場合、WAITに"L"信号が入力されていると、ウエイトサイクルが延長されます。                                                          |  |  |  |  |

|                    | HREQ                | ホールド<br>リクエスト           | 入力  | 外部のデバイスが外部バスのバス権を要求するための<br>入力端子です。HREQ端子に"L"信号を入力すると<br>M32Rはホールド状態へ遷移します。                                        |  |  |  |  |

|                    | HACK                | ホールド<br>アクノリッジ          | 出力  | M32Rがホールド状態へ遷移し、外部バスのバス権を解放<br>したことを通知するための信号です。                                                                   |  |  |  |  |

| マルチジャンク<br>ションクタイマ | TIN0<br>~ TIN33     | タイマ入力                   | 入力  | マルチジャンクションタイマの入力端子です。                                                                                              |  |  |  |  |

|                    | TO0 ~ TO44          | タイマ出力                   | 出力  | マルチジャンクションタイマの出力端子です。                                                                                              |  |  |  |  |

|                    | TCLK0<br>~ TCLK3    | タイマ<br>クロック             | 入力  | マルチジャンクションタイマのクロック入力端子です。                                                                                          |  |  |  |  |

| A-D<br>変換器         | AVCC0,<br>AVCC1     | アナログ電源                  | -   | AVCC0はA-D0変換器の電源です。AVCC1はA-D1変換器の電源です。AVCC0,1は電源(5Vまたは3.3V)に接続します。                                                 |  |  |  |  |

|                    | AVSS0,<br>AVSS1     | アナログ<br>グランド            | -   | AVSS0はA-D0変換器のアナロググランドです。AVSS1はA-D1変換器のアナロググランドです。AVSS0,1はグランドに接続します。                                              |  |  |  |  |

|                    | AD0IN0<br>~ AD0IN15 | アナログ入力                  | 入力  | A-D0変換器の16チャネルアナログ入力端子です。                                                                                          |  |  |  |  |

|                    | AD1IN0<br>~ AD1IN15 | 5                       |     | A-D1変換器の16チャネルアナログ入力端子です。                                                                                          |  |  |  |  |

表1.3.1 端子機能説明(3/6)

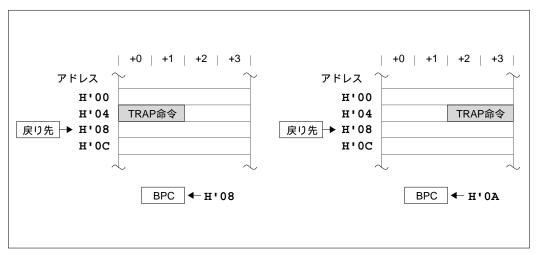

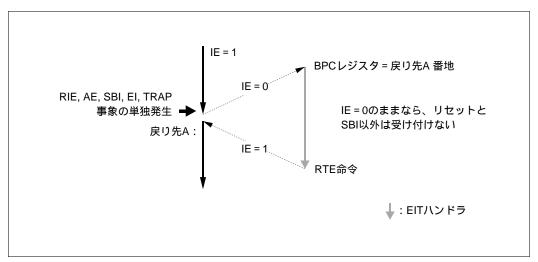

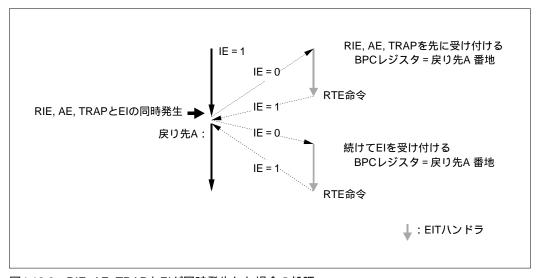

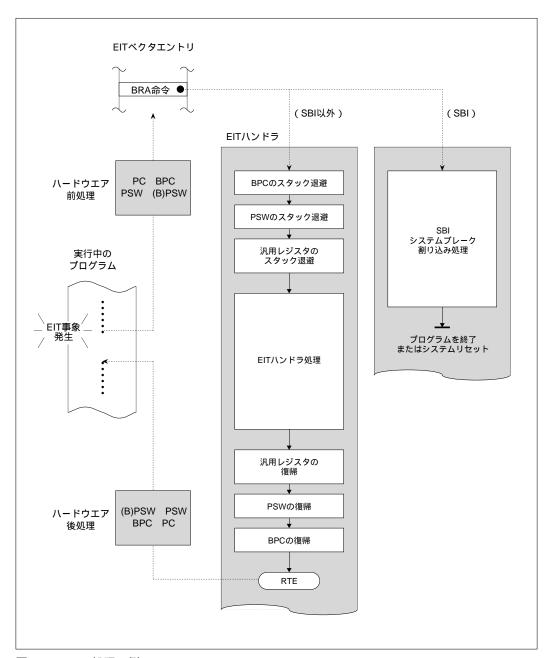

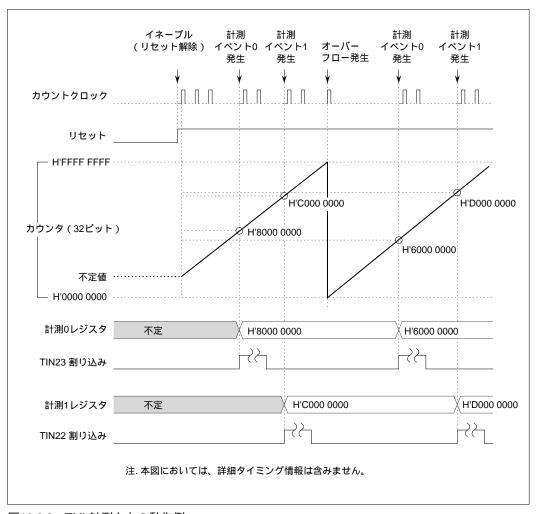

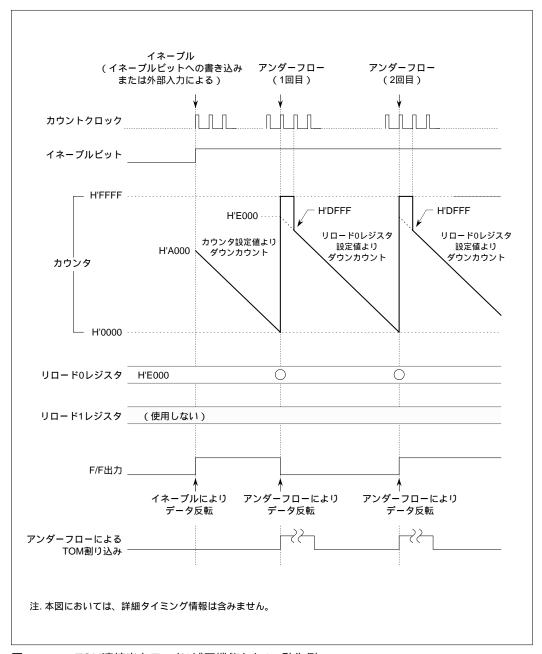

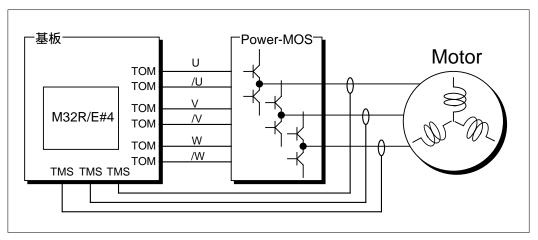

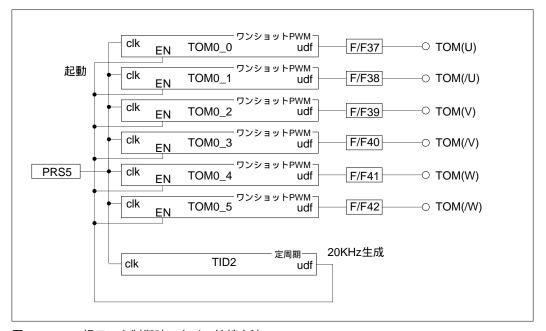

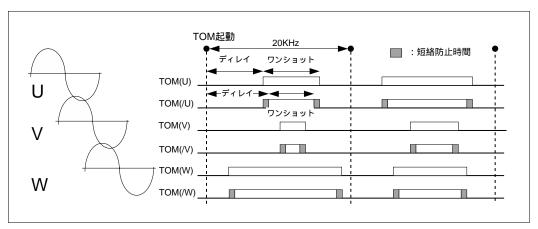

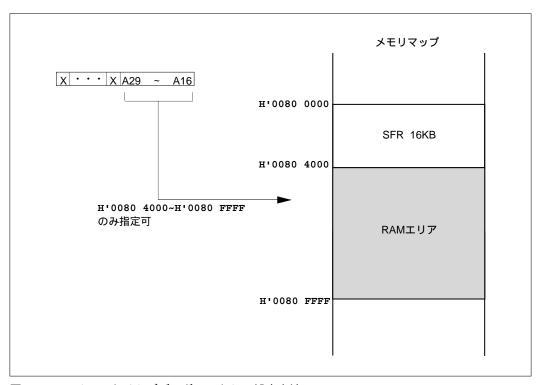

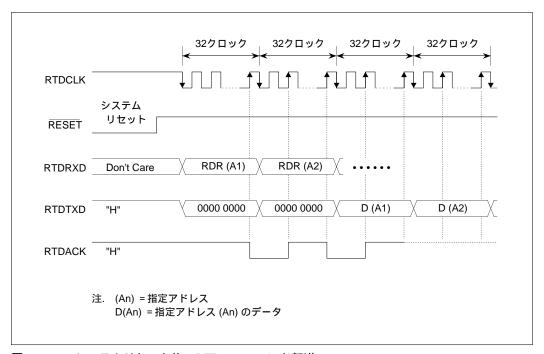

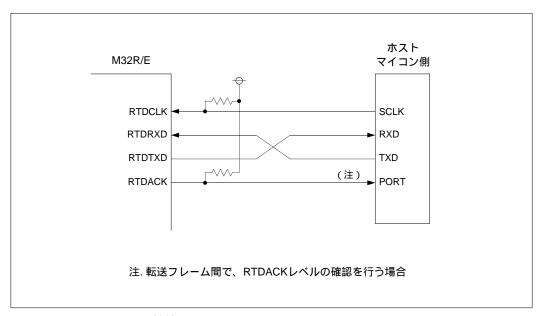

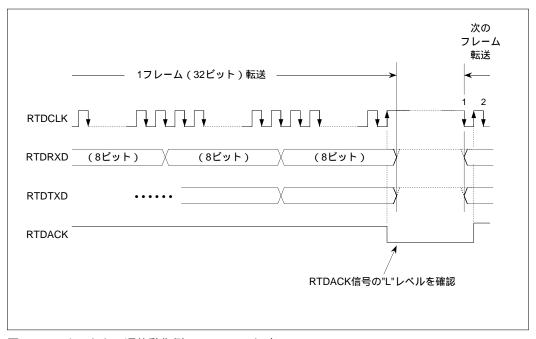

| 種類                 | 端子名                | 名称                                                 | 入出力 | 機能                                                                                                                                     |