# RL78/L1A

User's Manual: Hardware

16-Bit Single-Chip Microcontrollers

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

# **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

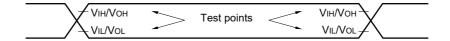

6. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between VIL (Max.) and VIH (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between VIL (Max.) and VIH (Min.).

7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not quaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

# How to Use This Manual

#### Readers

This manual is intended for user engineers who wish to understand the functions of the RL78/L1A and design and develop application systems and programs for these devices.

The target products are as follows.

• 80-pin: R5F11MMx (x = D, E, F) • 100-pin: R5F11MPx (x = E, F, G)

#### **Purpose**

This manual is intended to give users an understanding of the functions described in the Organization below.

#### Organization

The RL78/L1A manual is separated into two parts: this manual and the software edition (common to the RL78 family).

> RL78/L1A **User's Manual Hardware** (This Manual)

**RL78 Family User's Manual Software**

- · Pin functions

- · Internal block functions

- Interrupts

- Other on-chip peripheral functions

- · Electrical specifications

- CPU functions

- · Instruction set

- · Explanation of each instruction

How to Read This Manual It is assumed that the readers of this manual have general knowledge of electrical engineering, logic circuits, and microcontrollers.

- To gain a general understanding of functions:

- ightarrow Read this manual in the order of the **CONTENTS**. The mark "<R>" shows major revised points. The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

- · How to interpret the register format:

- ightarrow For a bit number enclosed in angle brackets, the bit name is defined as a reserved word in the assembler, and is defined as an sfr variable using the #pragma sfr directive in the compiler.

- To know details of the RL78/L1A Microcontroller instructions:

- → Refer to the separate document RL78 Family User's Manual Software (R01US0015E).

**Conventions** Data significance: Higher digits on the left and lower digits on the right

Active low representations:  $\overline{\times\!\times\!\times}$  (overscore over pin and signal name)

**Note:** Footnote for item marked with Note in the text

Caution: Information requiring particular attention

Remark: Supplementary information

Numerical representations: Binary.....xxx or xxxxB

Decimal......XXXX

Hexadecimal.....XXXH

However, preliminary versions are not marked as such.

#### **Documents Related to Devices**

| Document Name                      | Document No. |

|------------------------------------|--------------|

| RL78/L1A User's Manual Hardware    | This manual  |

| RL78 Family User's Manual Software | R01US0015E   |

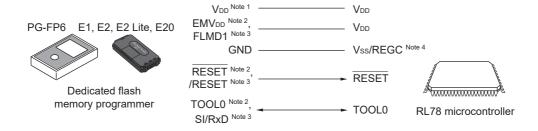

#### **Documents Related to Flash Memory Programming (User's Manual)**

| Document Name                                                            | Document No. |

|--------------------------------------------------------------------------|--------------|

| PG-FP6 Flash Memory Programmer User's Manual                             | R20UT4025E   |

| E1, E20 Emulator User's Manual                                           | R20UT0398E   |

| E2 Emulator User's Manual                                                | R20UT3538E   |

| E2 Lite Emulator User's Manual                                           | R20UT3240E   |

| Renesas Flash Programmer Flash Memory Programming Software User's Manual | R20UT4066E   |

| Renesas Flash Development Toolkit User's Manual                          | R20UT0508E   |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

## **Other Documents**

| Document Name                        | Document No. |

|--------------------------------------|--------------|

| Renesas Microcontrollers RL78 Family | R01CP0003E   |

| Semiconductor Package Mount Manual   | R50ZZ0003E   |

| Semiconductor Reliability Handbook   | R51ZZ0001E   |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

All trademarks and registered trademarks are the property of their respective owners.

EEPROM is a trademark of Renesas Electronics Corporation.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

$\label{lem:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:caution:c$

# **CONTENTS**

| 1. OU  | TLINE                                                                            | 1  |

|--------|----------------------------------------------------------------------------------|----|

| 1.1    | Features                                                                         | 1  |

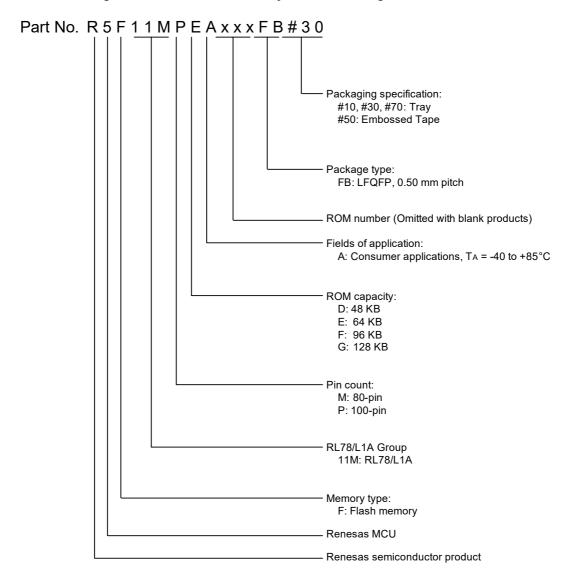

| 1.2    | Ordering Information                                                             | 5  |

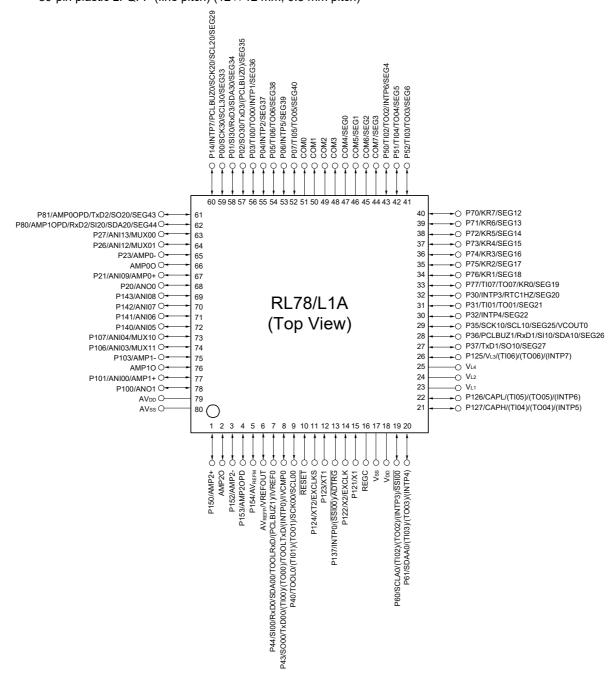

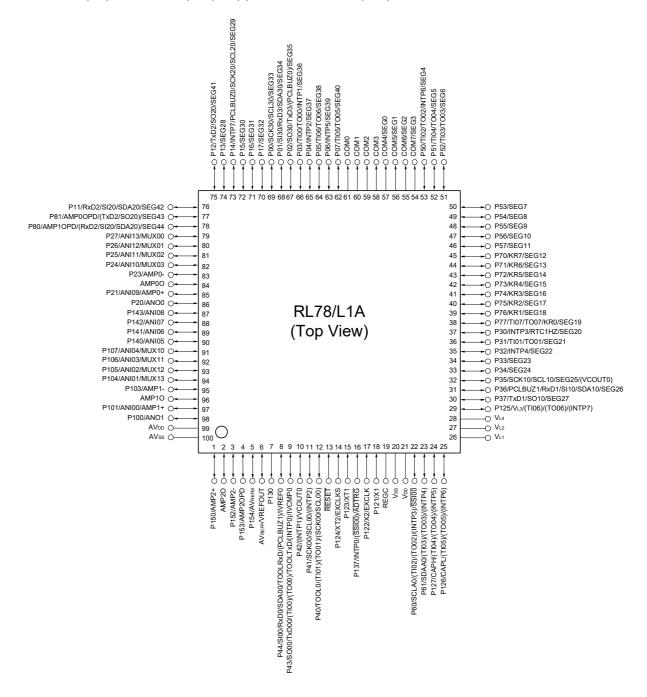

| 1.3    | Pin Configuration (Top View)                                                     | 6  |

| 1.3.1  | 80-pin products                                                                  | 6  |

| 1.3.2  | 100-pin products                                                                 | 7  |

| 1.4    | Pin Identification                                                               | 8  |

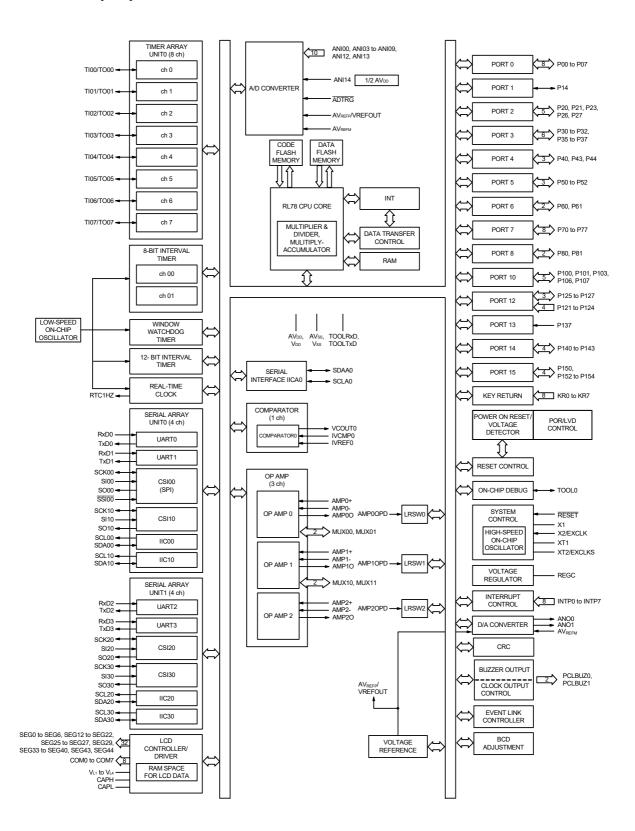

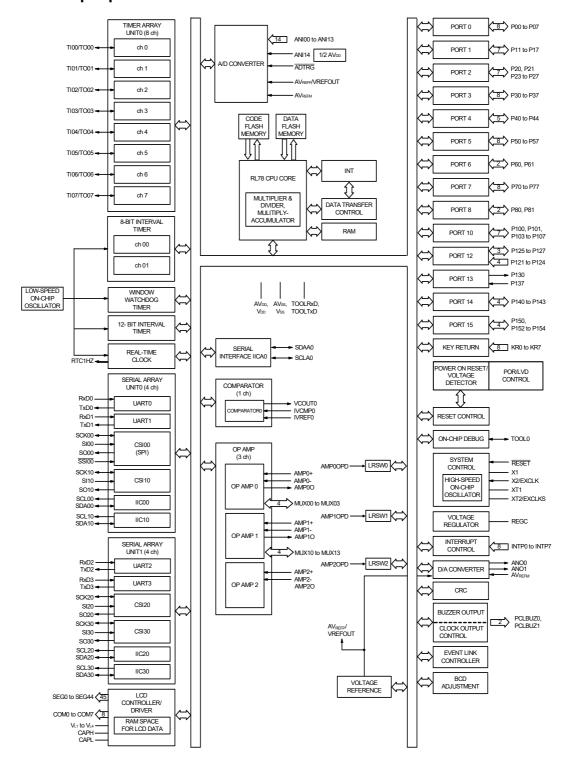

| 1.5    | Block Diagram                                                                    | 9  |

| 1.5.1  | 80-pin products                                                                  | 9  |

| 1.5.2  | 100-pin products                                                                 | 10 |

| 1.6    | Outline of Functions                                                             | 11 |

| 2. PIN | FUNCTIONS                                                                        | 13 |

| 2.1    | Port Function                                                                    | 13 |

| 2.1.1  | 80-pin products                                                                  | 14 |

| 2.1.2  | 100-pin products                                                                 | 17 |

| 2.2    | Functions other than port pins                                                   | 21 |

| 2.2.1  | With functions for each product                                                  | 21 |

| 2.2.2  | Description of Functions                                                         | 26 |

| 2.3    | Connection of Unused Pins                                                        | 28 |

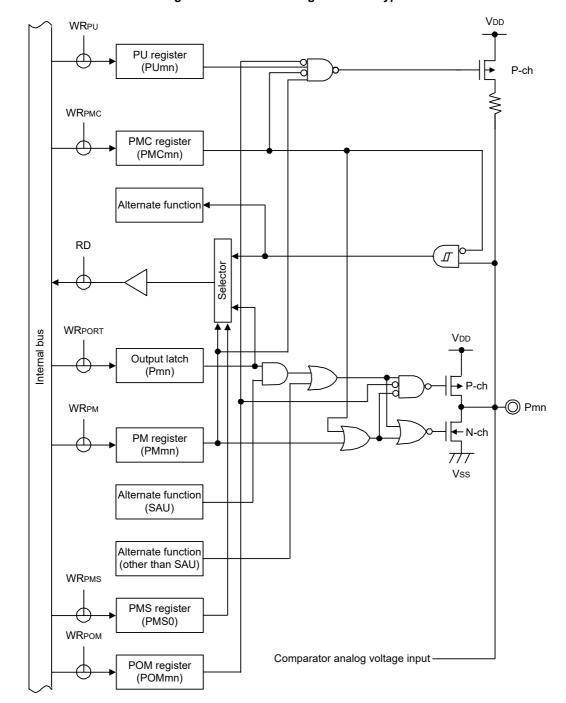

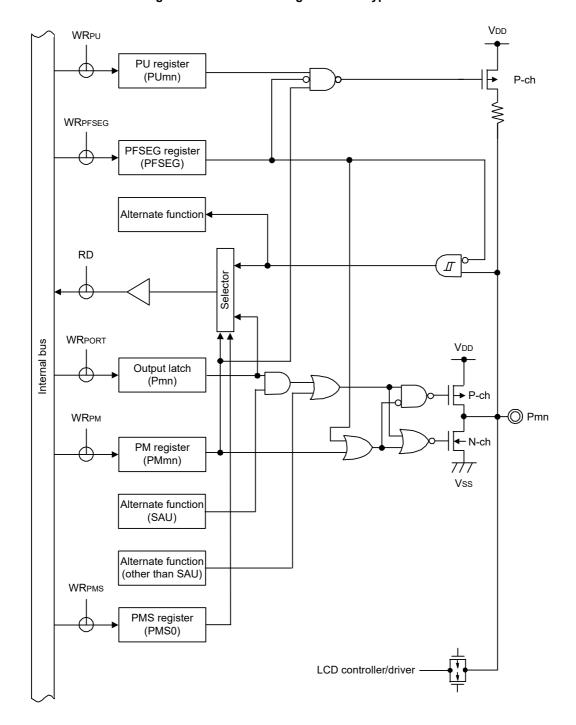

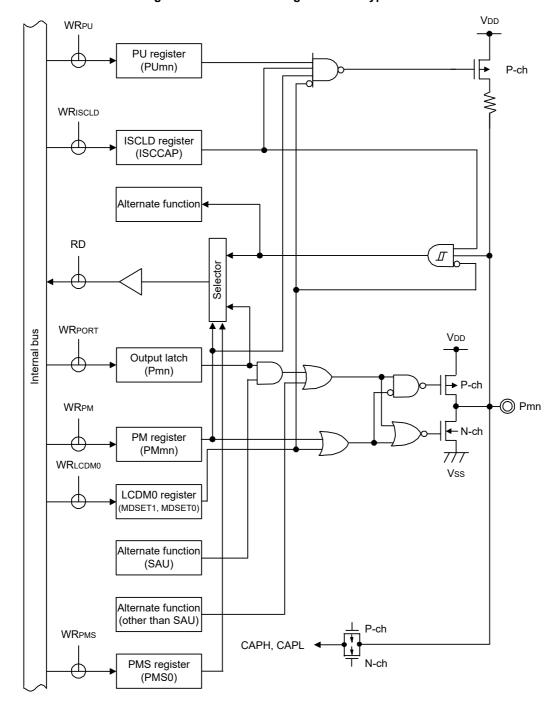

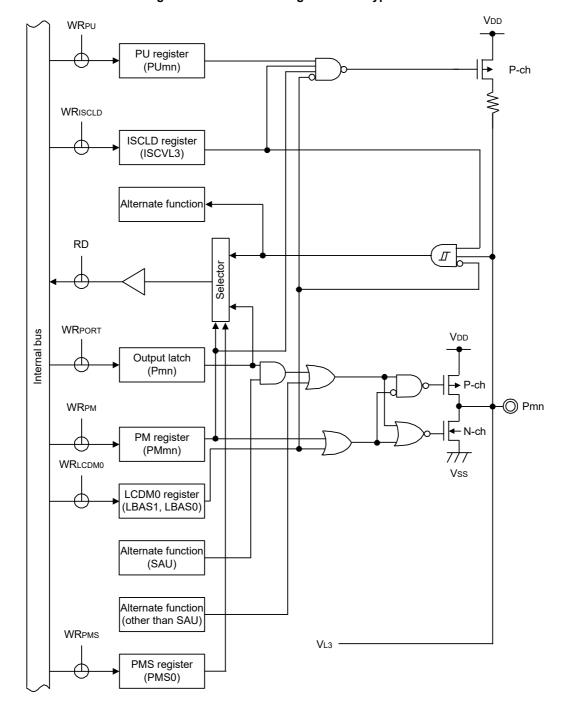

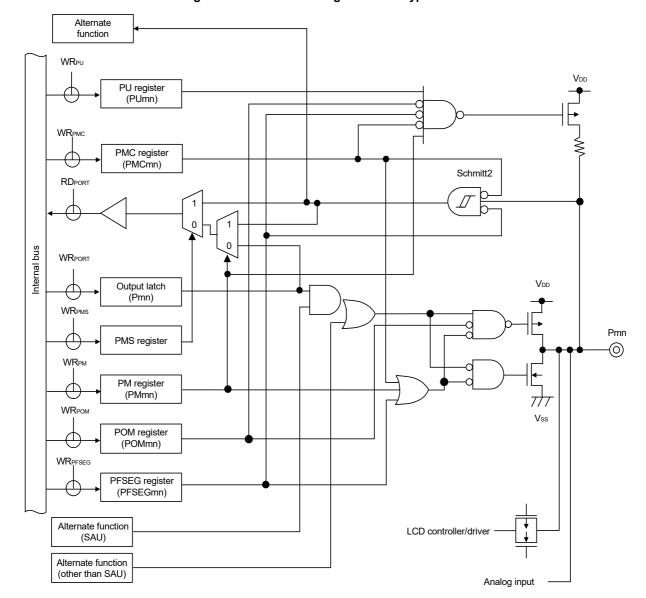

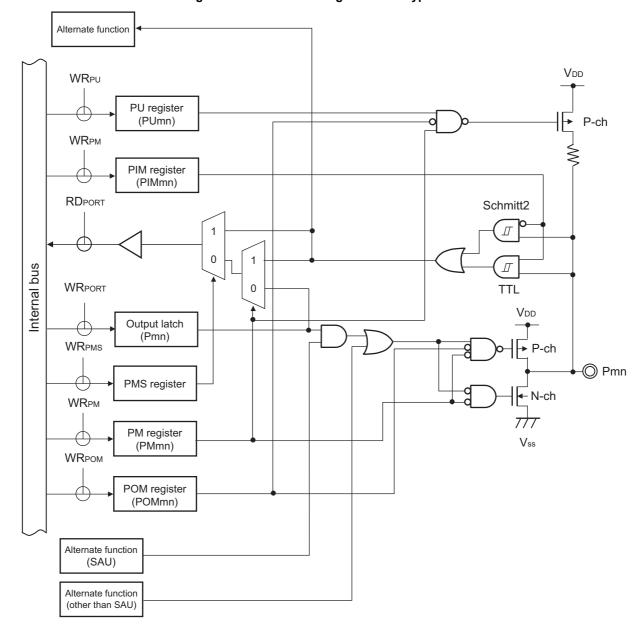

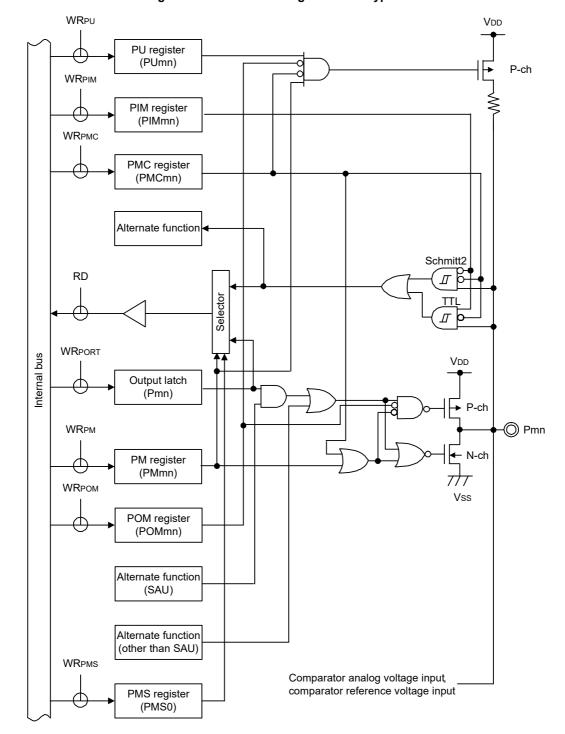

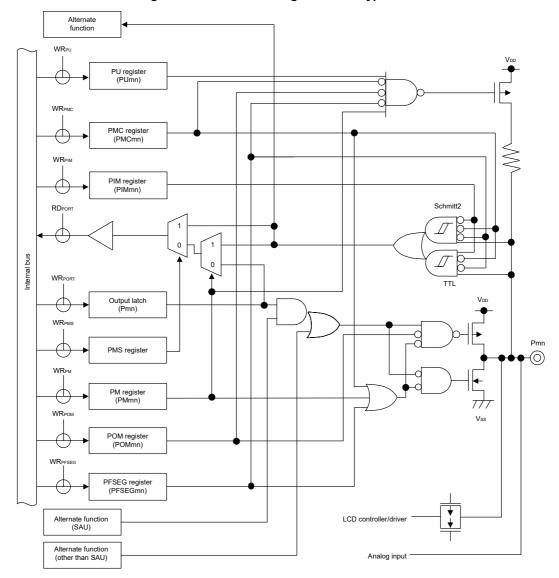

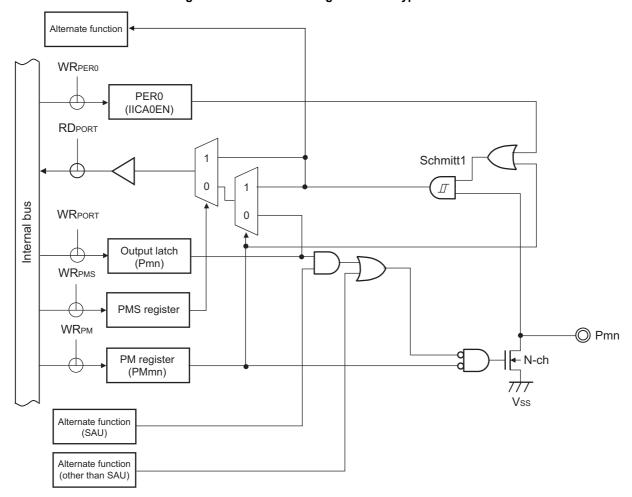

| 2.4    | Pin Block Diagrams                                                               | 29 |

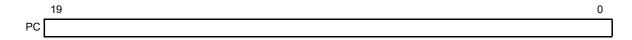

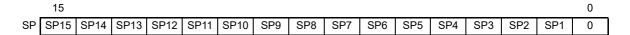

| 3. CP  | U ARCHITECTURE                                                                   | 47 |

| 3.1    | Overview                                                                         | 47 |

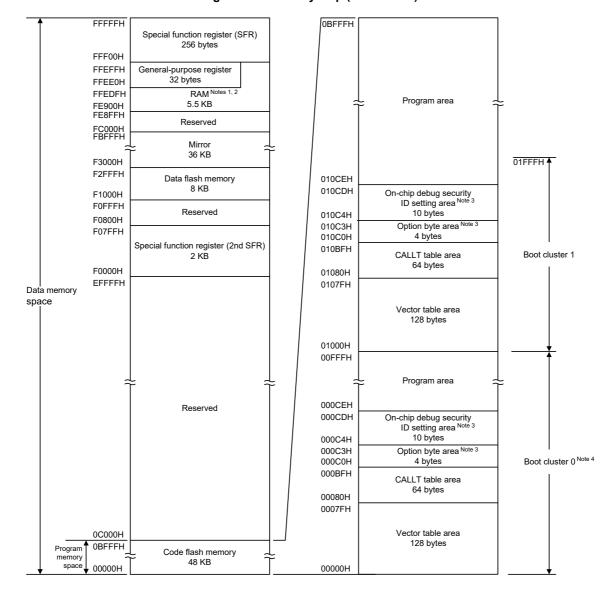

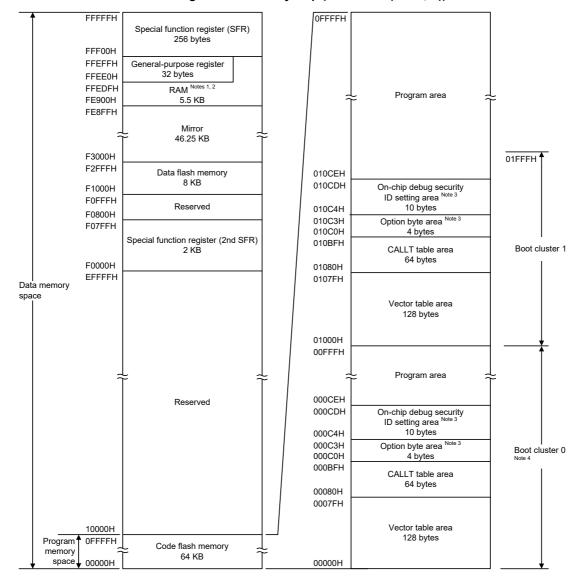

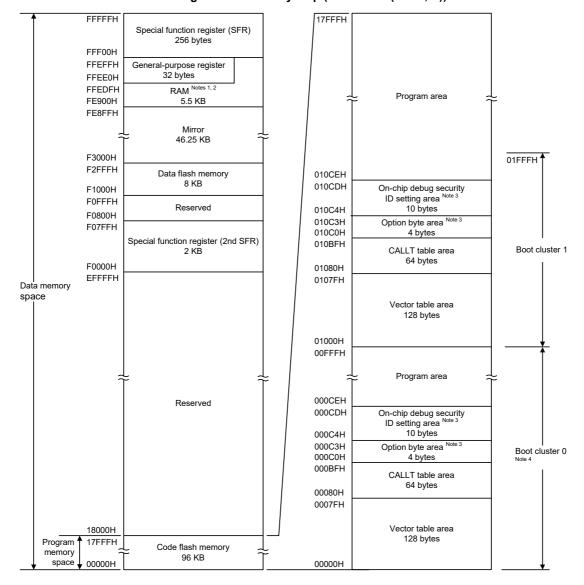

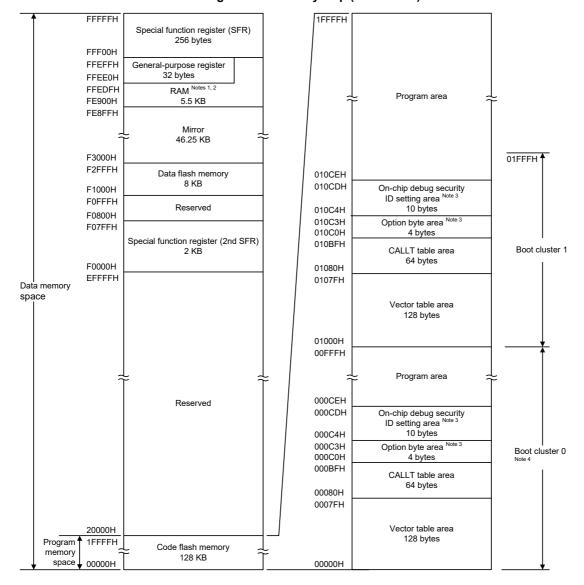

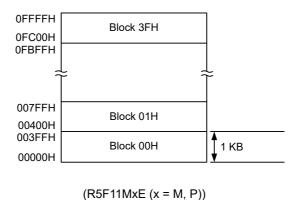

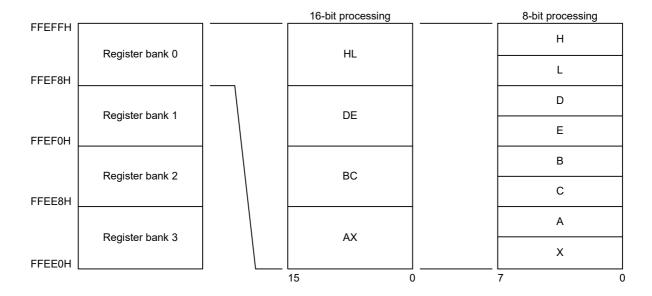

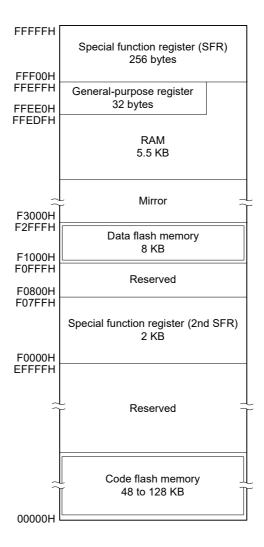

| 3.2    | Memory Space                                                                     | 47 |

| 3.2.1  | Internal program memory space                                                    | 54 |

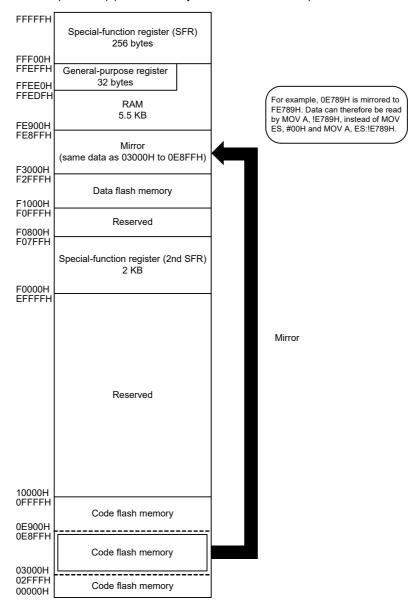

| 3.2.2  | Mirror area                                                                      | 57 |

| 3.2.3  | Internal data memory space                                                       | 59 |

| 3.2.4  | Special function register (SFR) area                                             | 60 |

| 3.2.5  | Extended special function register (2nd SFR: 2nd Special Function Register) area | 60 |

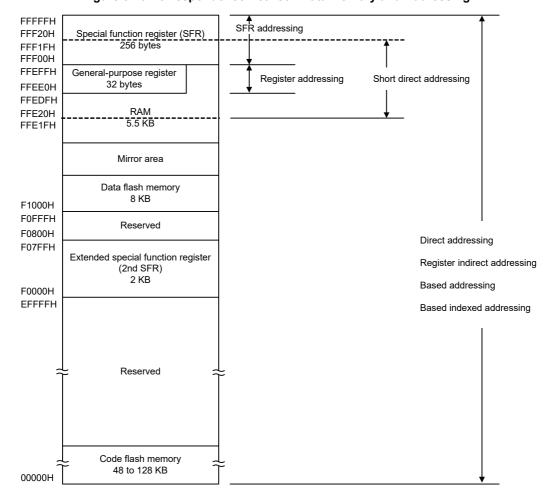

| 3.2.6  | Data memory addressing                                                           | 61 |

| 3.3    | Processor Registers                                                              | 62 |

| 3.3.1  | Control registers                                                                | 62 |

| 3.3.2  | General-purpose registers                                                        | 65 |

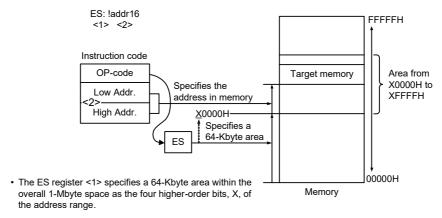

| 3.3.3  | ES and CS registers                                                              |    |

| 3.3.4  | Special function registers (SFRs)                                                |    |

| 3.3.5  | Extended special function registers (2nd SFRs: 2nd Special Function Registers)   |    |

| 3.4    | Instruction Address Addressing                                                   |    |

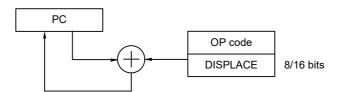

| 3.4.1  | Relative addressing                                                              |    |

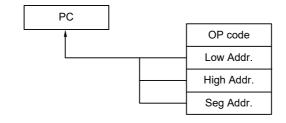

| 3.4.2  | Immediate addressing                                                             |    |

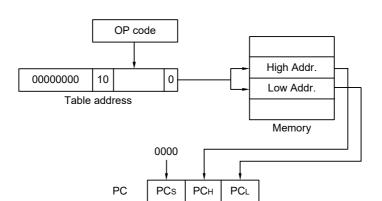

| 3.4.3  | Table indirect addressing                                                        |    |

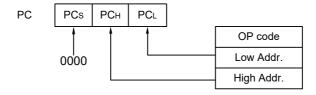

| 3.4.4  | Register direct addressing                                                       |    |

| 3.5    | Addressing for Processing Data Addresses                                         |    |

| 3.5.1  | Implied addressing                                                               |    |

| 3.5.2  | Register addressing                                                              | 86 |

| 3.5.3  | Direct addressing                                                          | 27   |

|--------|----------------------------------------------------------------------------|------|

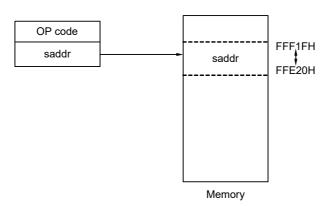

| 3.5.4  | Short direct addressing                                                    |      |

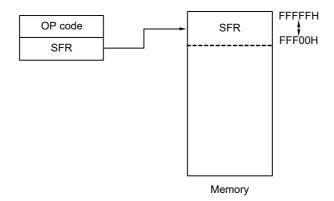

| 3.5.4  | SFR addressing                                                             |      |

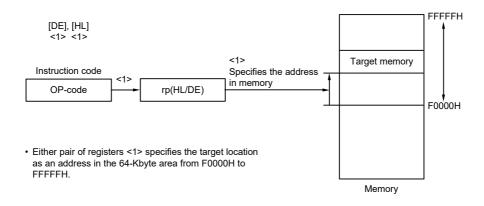

| 3.5.6  | Register indirect addressing                                               |      |

| 3.5.7  | Based addressing                                                           |      |

| 3.5.8  | Based indexed addressing                                                   |      |

| 3.5.9  | Stack addressing                                                           |      |

| 0.0.0  | Clask addressing                                                           | . 00 |

| 4. PO  | RT FUNCTIONS                                                               | . 98 |

| 4.1    | Port Functions                                                             | . 98 |

| 4.2    | Port Configuration                                                         | . 98 |

| 4.2.1  | Port 0                                                                     | . 99 |

| 4.2.2  | Port 1                                                                     | . 99 |

| 4.2.3  | Port 2                                                                     | 100  |

| 4.2.4  | Port 3                                                                     | 100  |

| 4.2.5  | Port 4                                                                     | 101  |

| 4.2.6  | Port 5                                                                     | 101  |

| 4.2.7  | Port 6                                                                     | 101  |

| 4.2.8  | Port 7                                                                     | 102  |

| 4.2.9  | Port 8                                                                     | 102  |

| 4.2.10 | Port 10                                                                    | 103  |

| 4.2.11 | Port 12                                                                    | 103  |

| 4.2.12 | Port 13                                                                    | 104  |

| 4.2.13 | Port 14                                                                    | 104  |

| 4.2.14 | Port 15                                                                    | 104  |

| 4.3    | Registers Controlling Port Function                                        | 105  |

| 4.3.1  | Port mode registers (PMxx)                                                 | 110  |

| 4.3.2  | Port registers (Pxx)                                                       | 111  |

| 4.3.3  | Pull-up resistor option registers (PUxx)                                   | 112  |

| 4.3.4  | Port input mode registers (PIMxx)                                          | 113  |

| 4.3.5  | Port output mode registers (POMxx)                                         | 114  |

| 4.3.6  | Port mode control registers (PMCxx)                                        | 115  |

| 4.3.7  | Peripheral I/O redirection register (PIOR)                                 | 116  |

| 4.3.8  | LCD port function registers 0 to 5 (PFSEG0 to PFSEG5)                      | 117  |

| 4.3.9  | LCD input switch control register (ISCLCD)                                 | 119  |

| 4.4    | Port Function Operations                                                   | 120  |

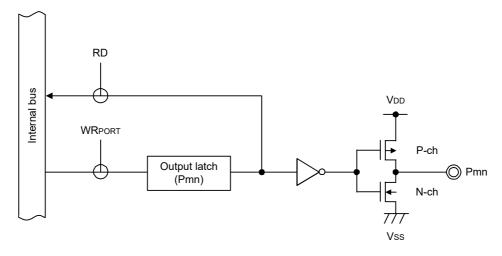

| 4.4.1  | Writing to I/O port                                                        | 120  |

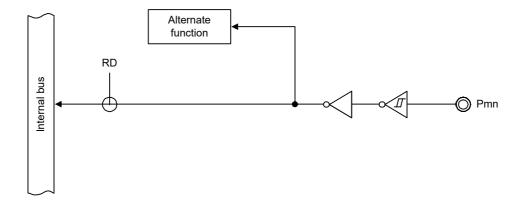

| 4.4.2  | Reading from I/O port                                                      | 120  |

| 4.4.3  | Operations on I/O port                                                     | 120  |

| 4.4.4  | Handling different potential (1.8 V, 2.5 V) by using I/O buffers           | 121  |

| 4.5    | Register Settings When Using Alternate Function                            | 124  |

| 4.5.1  | Basic concept when using alternate function                                | 124  |

| 4.5.2  | Register settings for alternate function whose output function is not used | 125  |

| 4.5.3  | Register setting examples for used port and alternate functions            | 126  |

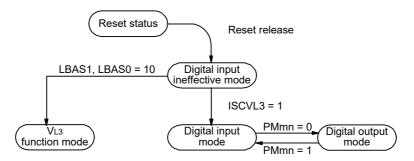

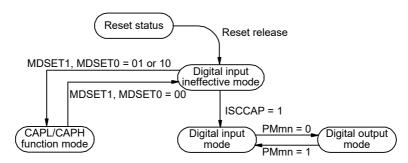

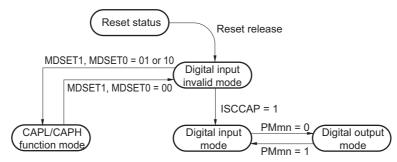

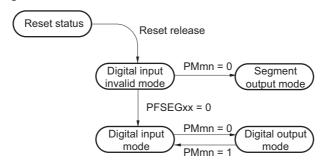

| 4.5.4  | Operation of ports that alternately function as SEGxx pins                 | 134  |

| 4.5.5  | Operation of ports that alternately function as VL3, CAPL, and CAPH pins   | 136  |

| 4.6    | Cautions When Using Port Function                                          |      |

| 4.6.1  | Cautions on 1-Bit Manipulation Instruction for Port Register n (Pn)        | 138  |

| 462    | Notes on specifying the nin settings                                       | 139  |

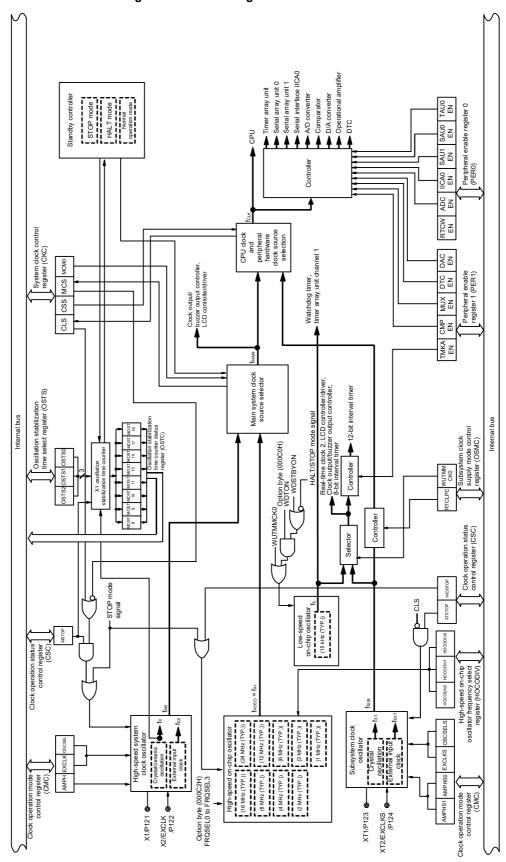

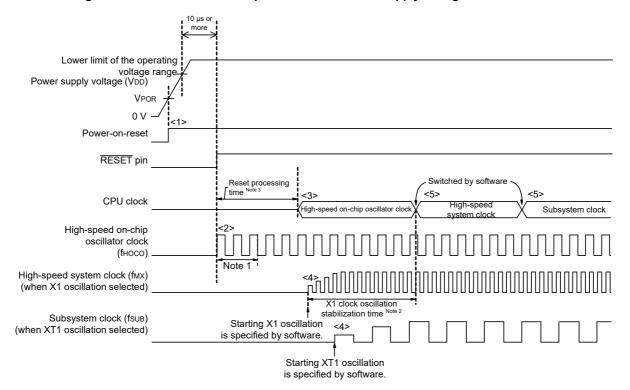

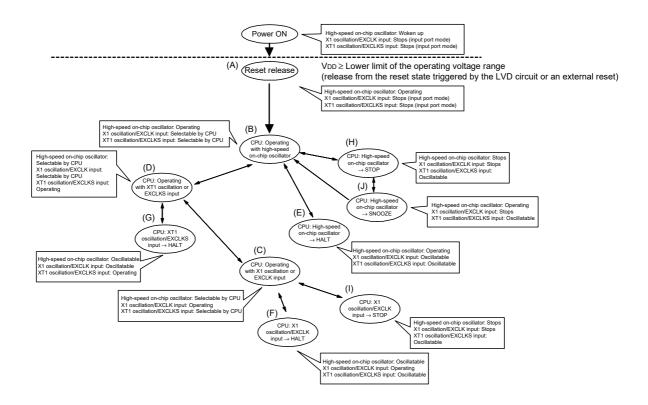

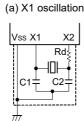

| 5. C | CLOCK GENERATOR                                                     | 140 |

|------|---------------------------------------------------------------------|-----|

| 5.1  | Functions of Clock Generator                                        | 140 |

| 5.2  | Configuration of Clock Generator                                    | 142 |

| 5.3  | Registers Controlling Clock Generator                               | 144 |

| 5.3  | .1 Clock operation mode control register (CMC)                      | 145 |

| 5.3. | 2 System clock control register (CKC)                               | 147 |

| 5.3  | .3 Clock operation status control register (CSC)                    | 148 |

| 5.3. | 4 Oscillation stabilization time counter status register (OSTC)     | 149 |

| 5.3. | 5 Oscillation stabilization time select register (OSTS)             | 151 |

| 5.3. | 6 Peripheral enable registers 0, 1 (PER0, PER1)                     | 153 |

| 5.3. | 7 Subsystem clock supply mode control register (OSMC)               | 156 |

| 5.3  | 8 High-speed on-chip oscillator frequency select register (HOCODIV) | 157 |

| 5.3  | 9 High-speed on-chip oscillator trimming register (HIOTRM)          | 158 |

| 5.4  | System Clock Oscillator                                             | 159 |

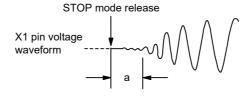

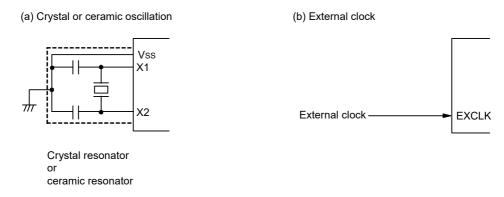

| 5.4. | 1 X1 oscillator                                                     | 159 |

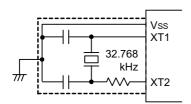

| 5.4. | 2 XT1 oscillator                                                    | 159 |

| 5.4. | 3 High-speed on-chip oscillator                                     | 163 |

| 5.4. | 4 Low-speed on-chip oscillator                                      | 163 |

| 5.5  | Clock Generator Operation                                           | 164 |

| 5.6  | Controlling Clock                                                   | 166 |

| 5.6. | 1 Example of setting high-speed on-chip oscillator                  | 166 |

| 5.6. | 2 Example of setting X1 oscillation clock                           | 168 |

| 5.6. | 3 Example of setting XT1 oscillation clock                          | 169 |

| 5.6. | 4 CPU clock status transition diagram                               | 170 |

| 5.6. |                                                                     |     |

| 5.6  | ,                                                                   |     |

| 5.6. | 7 Conditions before clock oscillation is stopped                    | 180 |

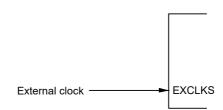

| 5.7  | Resonator and Oscillator Constants                                  | 181 |

| ·    | TIMED ADDAY UNIT                                                    | 400 |

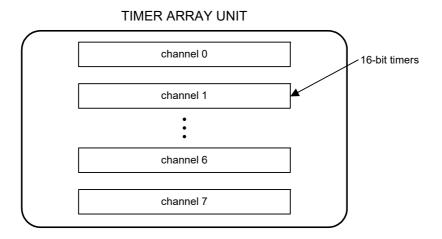

|      | TIMER ARRAY UNIT                                                    |     |

| 6.1  | Functions of Timer Array Unit                                       |     |

| 6.1. | ·                                                                   |     |

| 6.1. | •                                                                   |     |

| 6.1. | 1                                                                   |     |

| 6.1. | 11 0 ( ),                                                           |     |

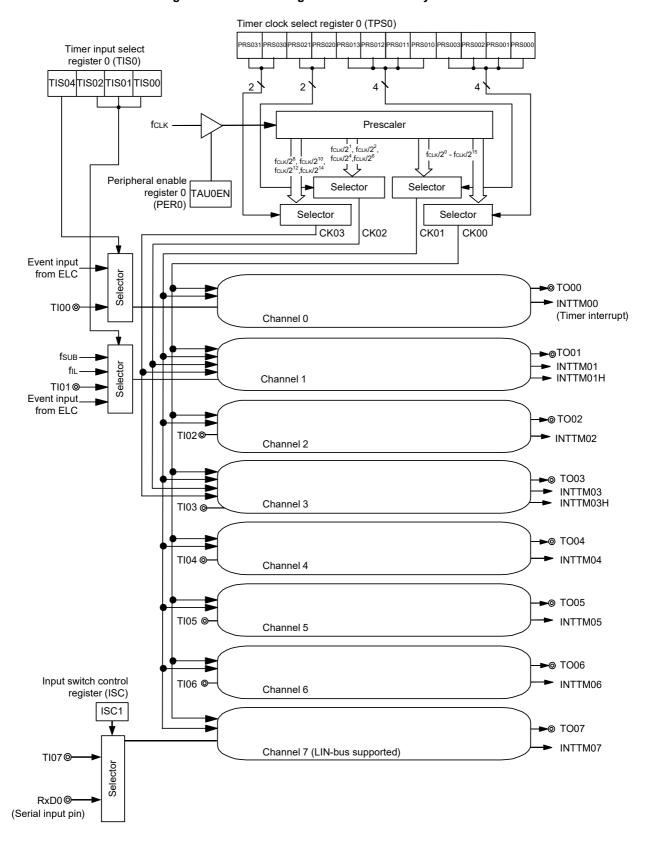

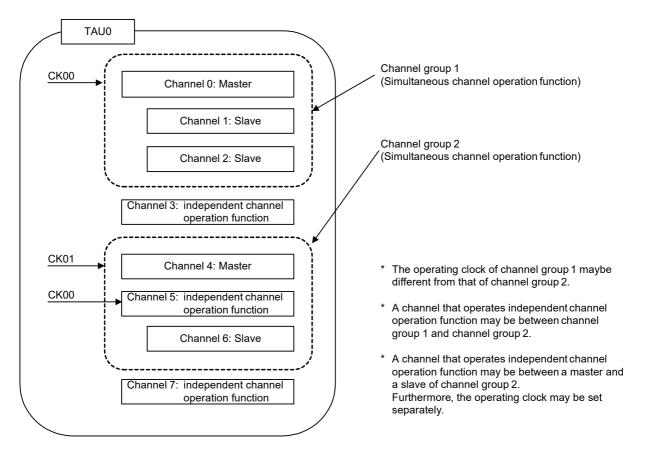

| 6.2  | Configuration of Timer Array Unit                                   |     |

| 6.2. | 9 ( )                                                               |     |

| 6.2. |                                                                     |     |

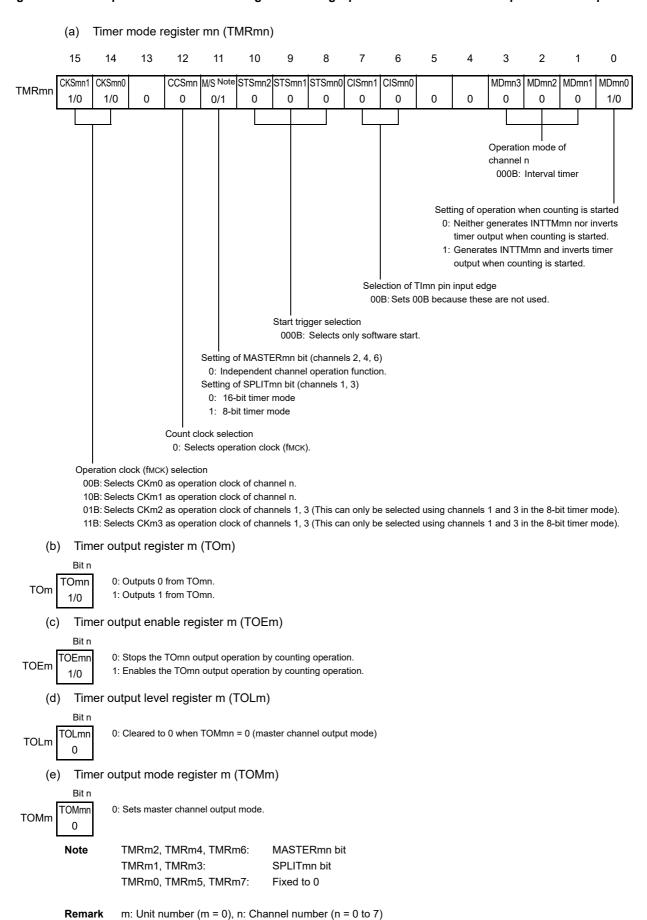

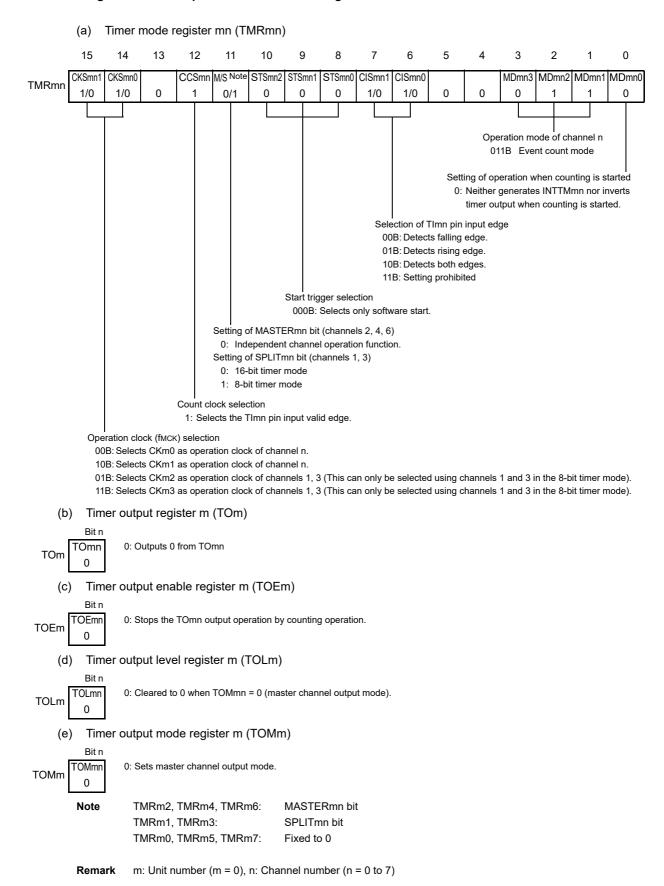

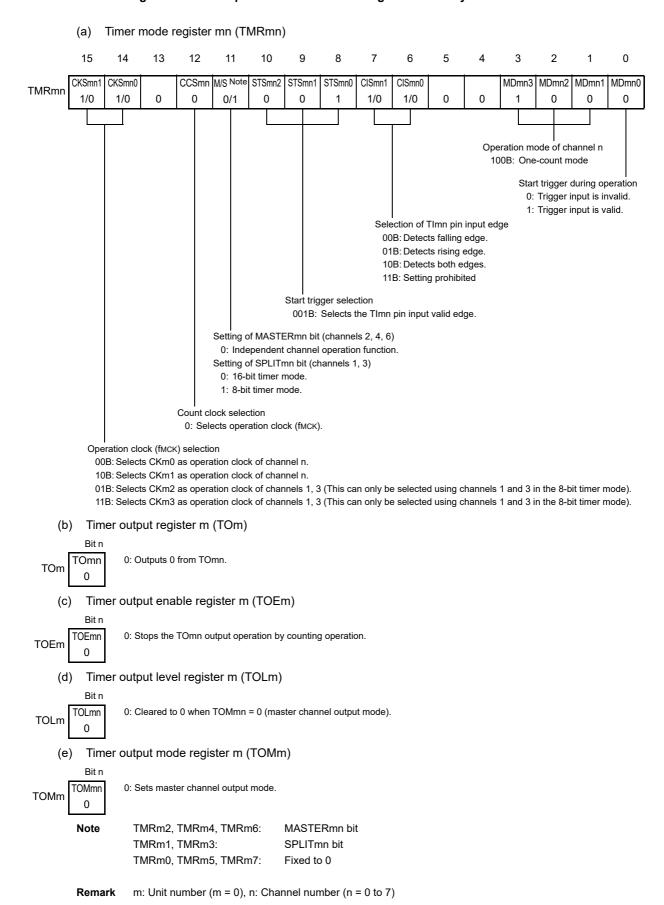

| 6.3  | Registers Controlling Timer Array Unit                              |     |

| 6.3. | 1 3 - ( )                                                           |     |

| 6.3. |                                                                     |     |

| 6.3. |                                                                     |     |

| 6.3. |                                                                     |     |

| 6.3. | <b>5</b>                                                            |     |

| 6.3. | 3 ,                                                                 |     |

| 6.3. | 1 6 ( )                                                             |     |

| 6.3. | . ,                                                                 |     |

| 6.3. |                                                                     |     |

| 6.3  | 10 Timer output register m (TOm)                                    | 213 |

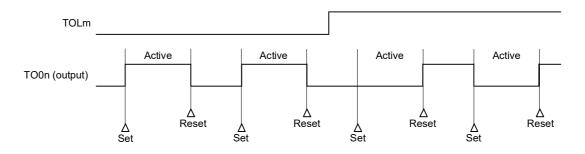

| 6.3.11 | Timer output level register m (TOLm)                                  | . 214 |

|--------|-----------------------------------------------------------------------|-------|

| 6.3.12 | 2 Timer output mode register m (TOMm)                                 | 215   |

| 6.3.13 | 3 Input switch control register (ISC)                                 | 216   |

| 6.3.14 | 4 Noise filter enable register 1 (NFEN1)                              | 217   |

| 6.3.15 | 5 Registers that control port functions of timer input/output pins    | 219   |

| 6.4    | Basic Rules of Timer Array Unit                                       | 220   |

| 6.4.1  | Basic rules of simultaneous channel operation function                | 220   |

| 6.4.2  | Basic rules of 8-bit timer operation function (channels 1 and 3 only) | . 222 |

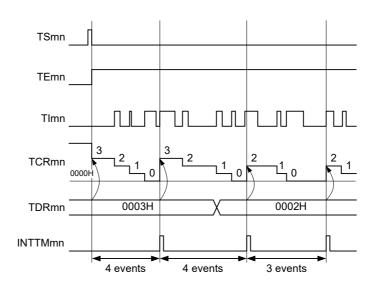

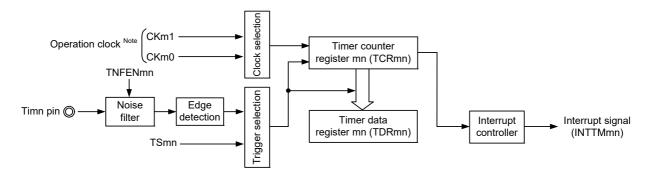

| 6.5    | Operation of Counter                                                  | . 223 |

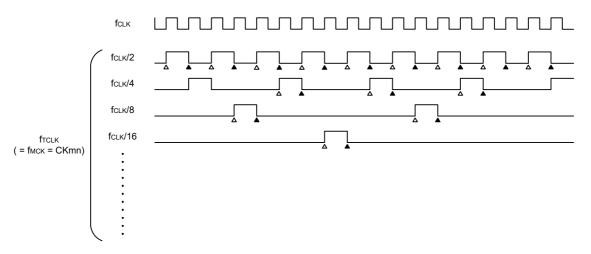

| 6.5.1  | Count clock (fTCLK)                                                   | . 223 |

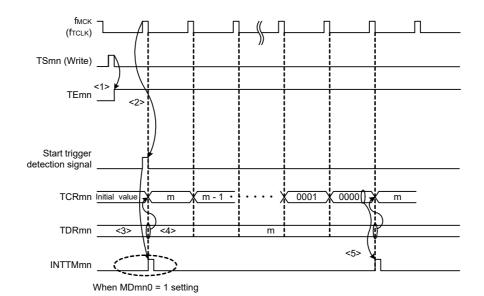

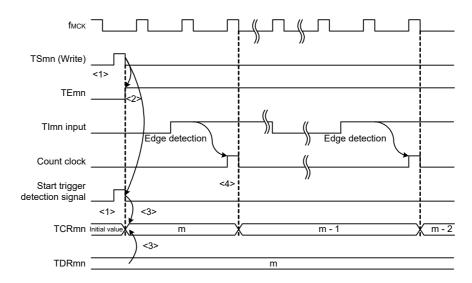

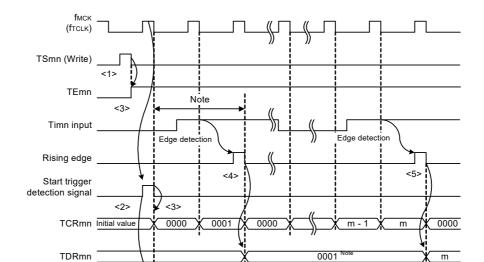

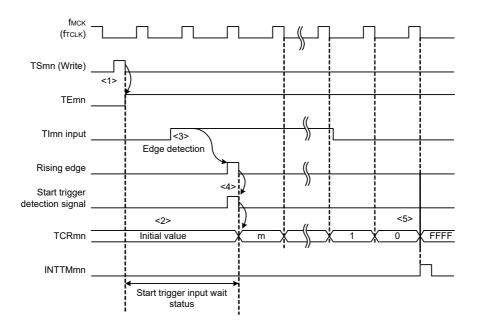

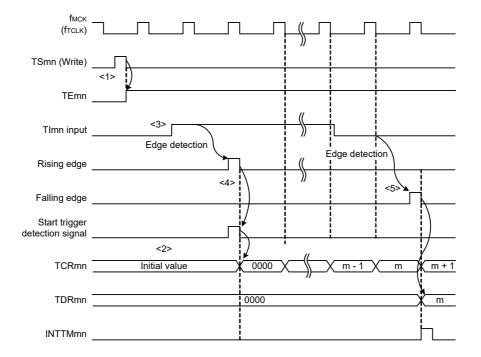

| 6.5.2  | Start timing of counter                                               | . 225 |

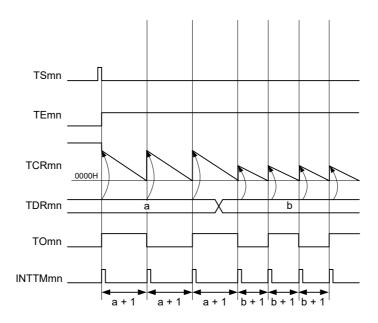

| 6.5.3  | Operation of counter                                                  | 226   |

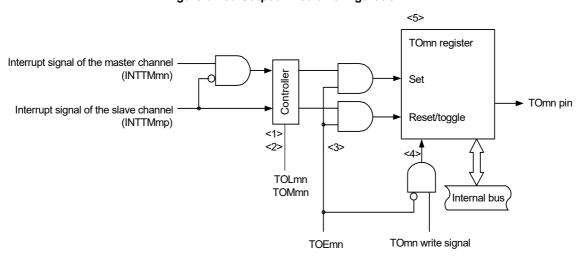

| 6.6    | Channel Output (TOmn pin) Control                                     | 231   |

| 6.6.1  | TOmn pin output circuit configuration                                 | 231   |

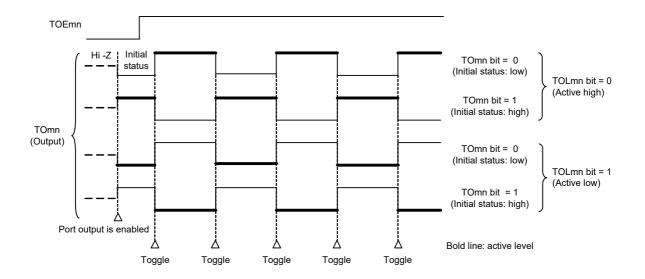

| 6.6.2  | TOmn Pin Output Setting                                               | 232   |

| 6.6.3  | Cautions on Channel Output Operation                                  |       |

| 6.6.4  | Collective manipulation of TOmn bit                                   |       |

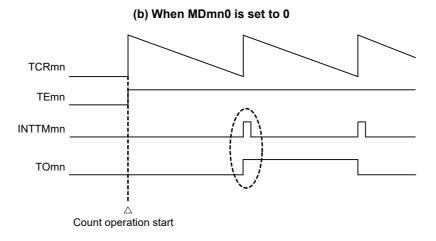

| 6.6.5  | Timer Interrupt and TOmn Pin Output at Operation Start                |       |

| 6.7    | Timer Input (TImn) Control                                            | 240   |

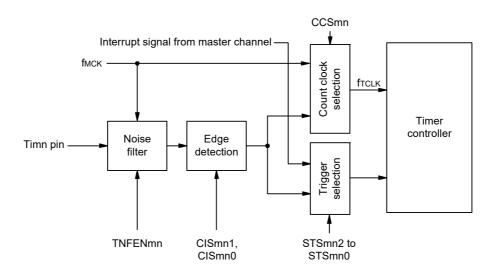

| 6.7.1  | Tlmn input circuit configuration                                      | 240   |

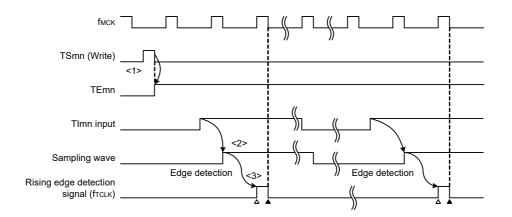

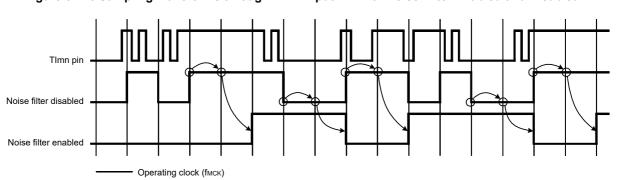

| 6.7.2  | Noise filter                                                          | 240   |

| 6.7.3  | Cautions on channel input operation                                   | . 241 |

| 6.8    | Independent Channel Operation Function of Timer Array Unit            | 242   |

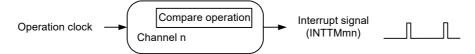

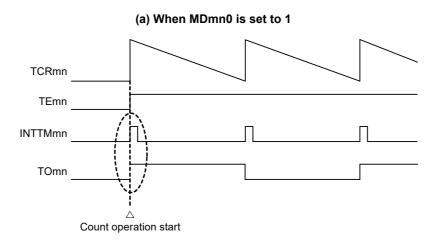

| 6.8.1  | Operation as interval timer/square wave output                        | 242   |

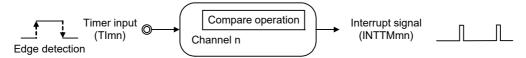

| 6.8.2  | Operation as external event counter                                   | . 247 |

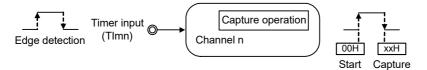

| 6.8.3  | Operation as input pulse interval measurement                         | 251   |

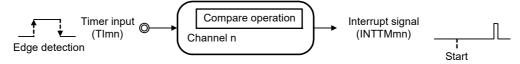

| 6.8.4  | Operation as input signal high-/low-level width measurement           | 255   |

| 6.8.5  | Operation as delay counter                                            | 259   |

| 6.9    | Simultaneous Channel Operation Function of Timer Array Unit           |       |

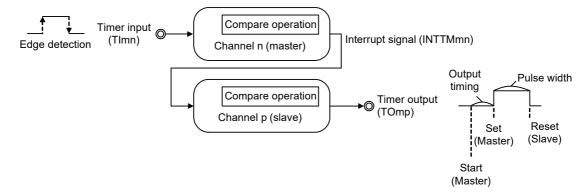

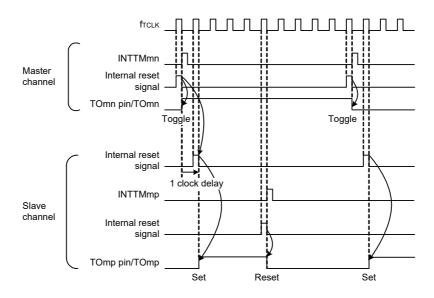

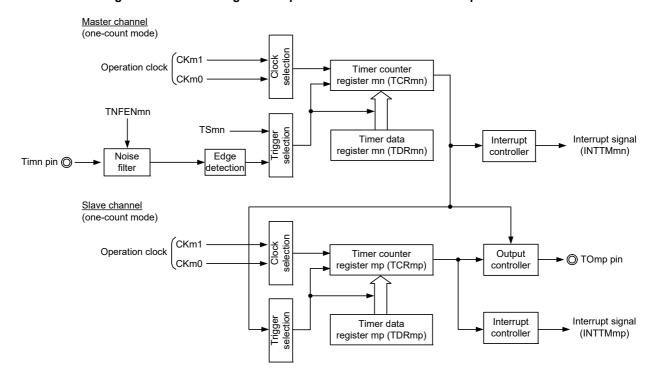

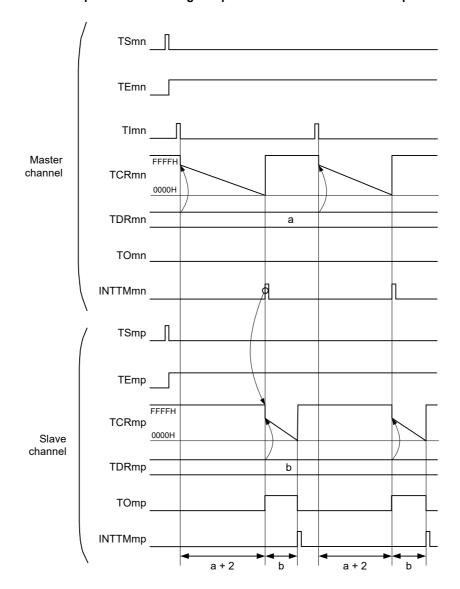

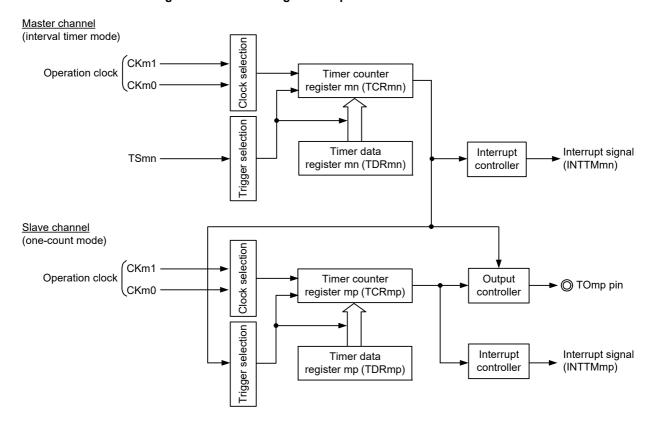

| 6.9.1  | Operation as one-shot pulse output function                           | 263   |

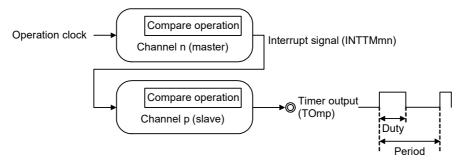

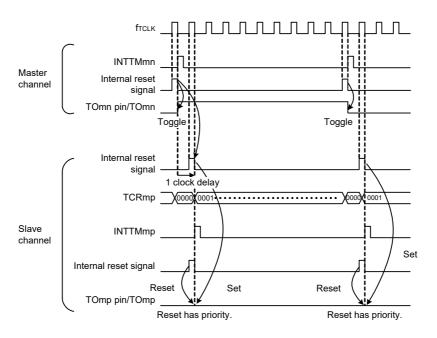

| 6.9.2  | Operation as PWM function                                             | 270   |

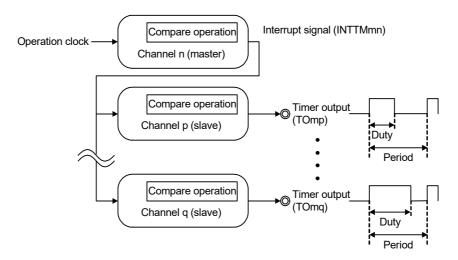

| 6.9.3  | Operation as multiple PWM output function                             |       |

| 6.10   | Cautions When Using Timer Array Unit                                  | . 285 |

| 6.10.1 | 1 Cautions When Using Timer output                                    | 285   |

|        |                                                                       |       |

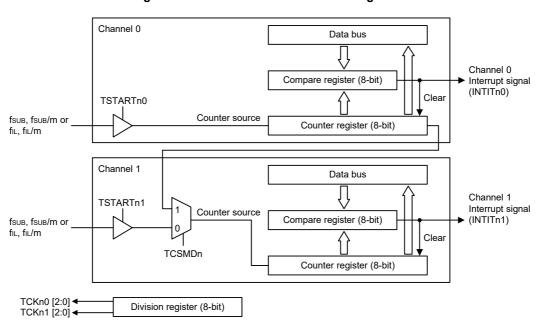

| 7. 8-E | BIT INTERVAL TIMER                                                    | 286   |

| 7.1    | Overview                                                              | 286   |

| 7.2    | I/O Pins                                                              | 288   |

| 7.3    | Registers                                                             | 288   |

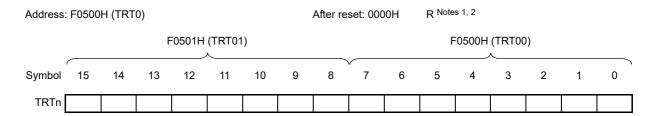

| 7.3.1  | 8-bit interval timer counter register ni (TRTni) (n = 0, i = 0, 1)    | 289   |

| 7.3.2  | 8-bit interval timer counter register n (TRTn) (n = 0)                | 289   |

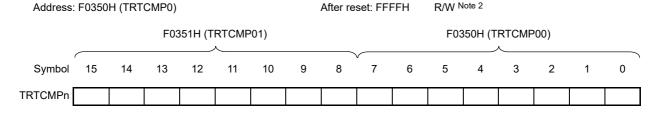

| 7.3.3  | 8-bit interval timer compare register ni (TRTCMPni) (n = 0, i = 0, 1) | 290   |

| 7.3.4  | 8-bit interval timer compare register n (TRTCMPn) (n = 0)             | 290   |

| 7.3.5  | 8-bit interval timer control register n (TRTCRn) (n = 0)              | . 291 |

| 7.3.6  | 8-bit interval timer division register n (TRTMDn) (n = 0)             | 292   |

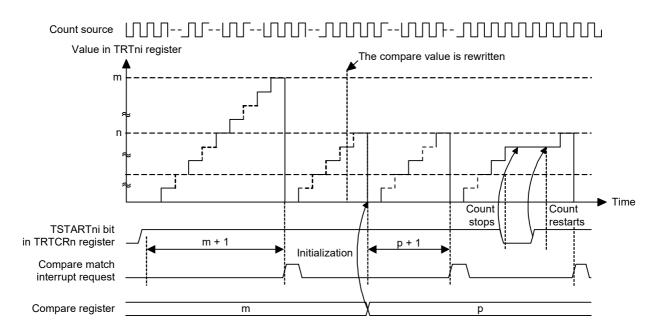

| 7.4    | Operation                                                             | 293   |

| 7.4.1  | Count mode                                                            | 293   |

| 7.4.2  | Timer operation                                                       | 294   |

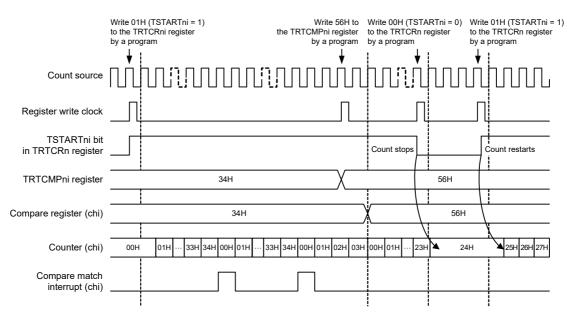

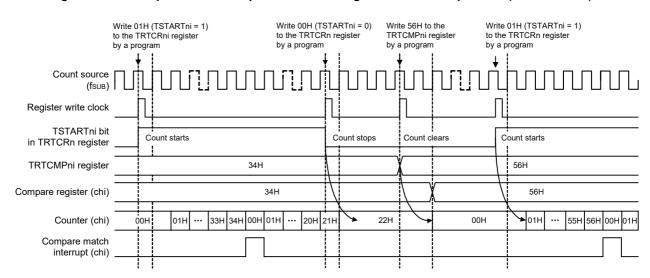

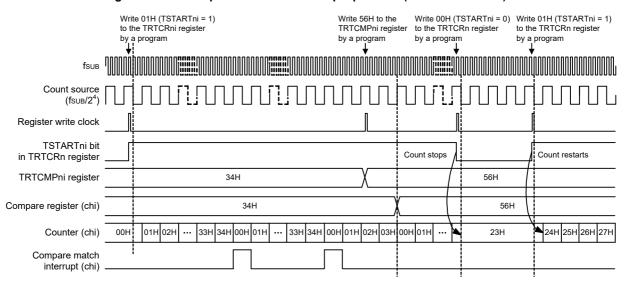

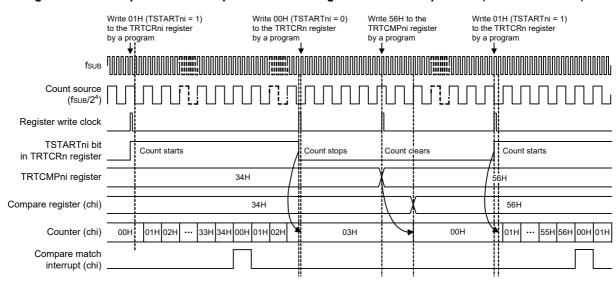

| 7.4.3  | Start/stop timing                                                     | 296   |

| 7.4          | .3.1 When count source (fsub) is selected                                           | . 296 |

|--------------|-------------------------------------------------------------------------------------|-------|

| 7.4          | .3.2 When count source (fSUB/2m) is selected                                        | . 298 |

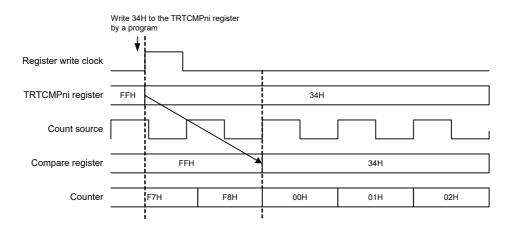

| 7.4.4        | Timing for updating compare register values                                         | . 300 |

| 7.5          | Notes on 8-Bit Interval Timer                                                       | . 301 |

| 7.5.1        | Changing settings of operating mode                                                 | . 301 |

| 7.5.2        | Accessing compare registers                                                         | . 301 |

| 7.5.3        | 8-bit interval timer setting procedure                                              | . 301 |

| 8. RE        | AL-TIME CLOCK 2                                                                     | 303   |

|              |                                                                                     |       |

| 8.1          | Functions of Real-time Clock 2                                                      |       |

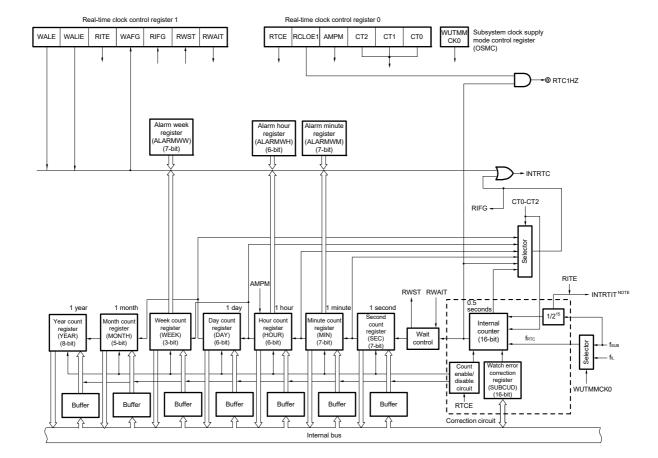

| 8.2          | Configuration of Real-time Clock 2                                                  |       |

| 8.3          | Registers Controlling Real-time Clock 2                                             |       |

| 8.3.1        | Peripheral enable register 0 (PER0)                                                 |       |

| 8.3.2        | Subsystem clock supply mode control register (OSMC)                                 |       |

| 8.3.3        | Real-time clock control register 0 (RTCC0)                                          |       |

| 8.3.4        | Real-time clock control register 1 (RTCC1)                                          |       |

| 8.3.5        | Second count register (SEC)                                                         |       |

| 8.3.6        | Minute count register (MIN)                                                         |       |

| 8.3.7        | Hour count register (HOUR)                                                          |       |

| 8.3.8        | Day count register (DAY)                                                            |       |

| 8.3.9        | Week count register (WEEK)                                                          |       |

| 8.3.10       |                                                                                     |       |

| 8.3.11       | 3 ( )                                                                               |       |

| 8.3.12       | <b>3</b>                                                                            |       |

| 8.3.13       | ,                                                                                   |       |

| 8.3.14       |                                                                                     |       |

| 8.3.15       | 5 Alarm week register (ALARMWW)                                                     | . 322 |

| 8.4          | Real-time Clock 2 Operation                                                         |       |

| 8.4.1        | Starting operation of real-time clock 2                                             |       |

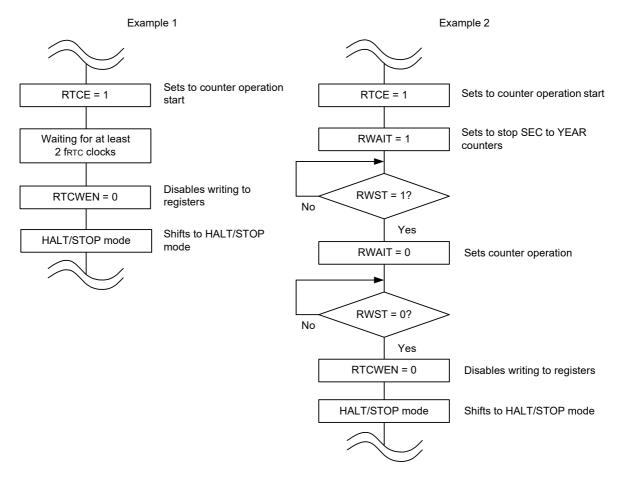

| 8.4.2        | Shifting to HALT/STOP mode after starting operation                                 |       |

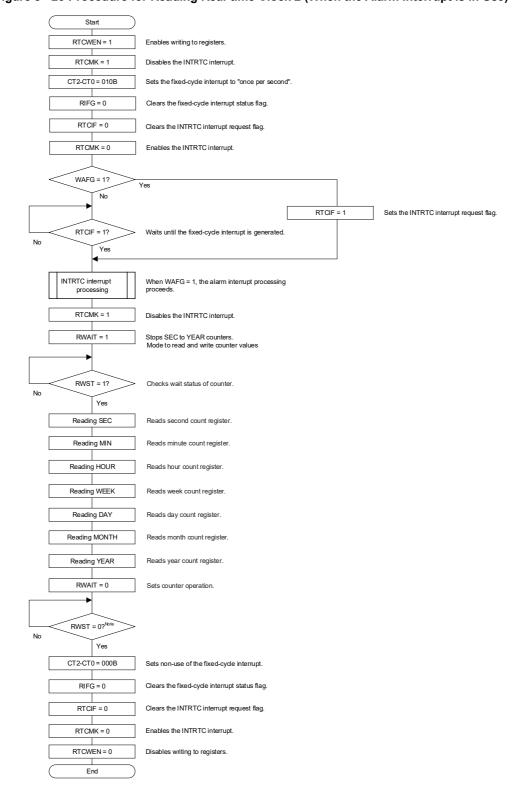

| 8.4.3        | Reading real-time clock 2                                                           | . 325 |

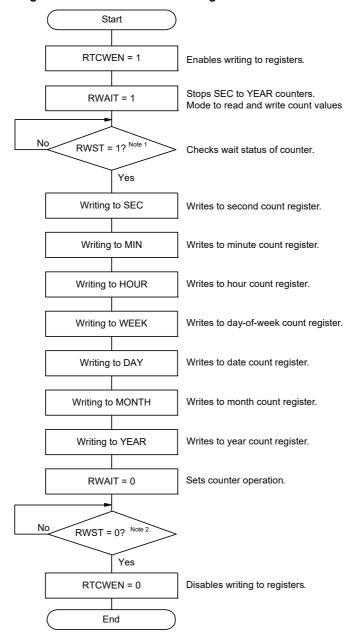

| 8.4.4        | Writing to real-time clock 2 counter                                                |       |

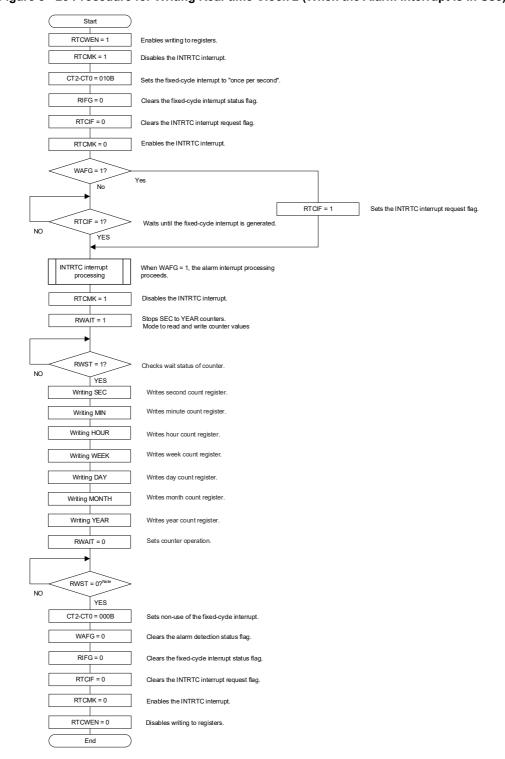

| 8.4.5        | Setting alarm of real-time clock 2                                                  | . 329 |

| 8.4.6        | 1 Hz output of real-time clock 2                                                    | . 330 |

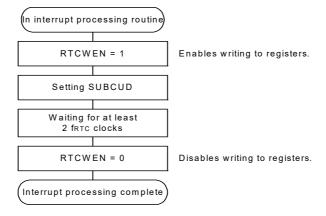

| 8.4.7        | Clock error correction register setting procedure                                   | . 331 |

| 8.4.8        | Example of watch error correction of real-time clock 2                              | . 332 |

| 9. 12-       | BIT INTERVAL TIMER                                                                  | . 334 |

| 9.1          | Functions of 12-bit Interval Timer                                                  |       |

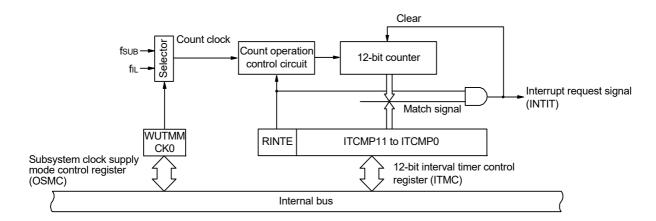

| 9.2          | Configuration of 12-bit Interval Timer                                              |       |

| 9.3          | Registers Controlling 12-bit Interval Timer                                         |       |

| 9.3.1        | Peripheral enable register 1 (PER1)                                                 |       |

| 9.3.1        | Subsystem clock supply mode control register (OSMC)                                 |       |

| 9.3.2        | 12-bit interval timer control register (ITMC)                                       |       |

|              | 12-bit Interval Timer Operation                                                     |       |

| 9.4<br>9.4.1 |                                                                                     |       |

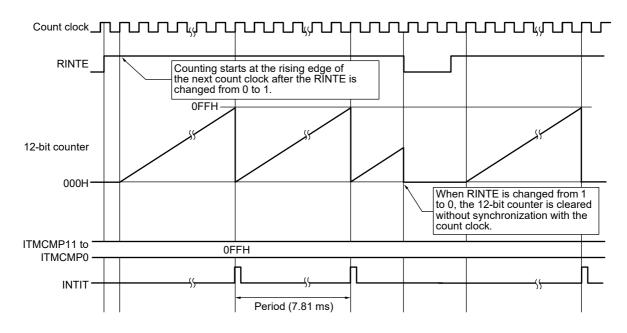

| 9.4.1        | 12-bit interval timer operation timing                                              |       |

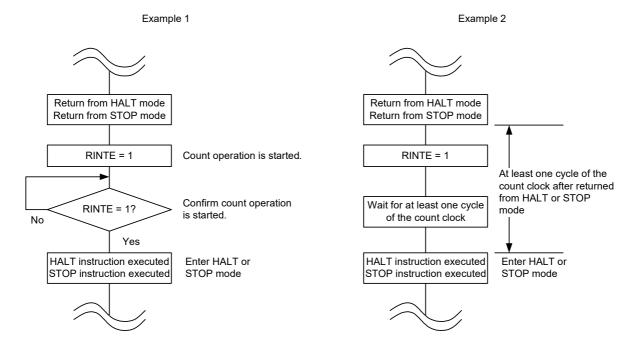

| 9.4.2        | Start of count operation and re-enter to HALT/STOP mode after returned from HALT/ST | 330   |

| 10. CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 340 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10.1 Functions of Clock Output/Buzzer Output Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 340 |

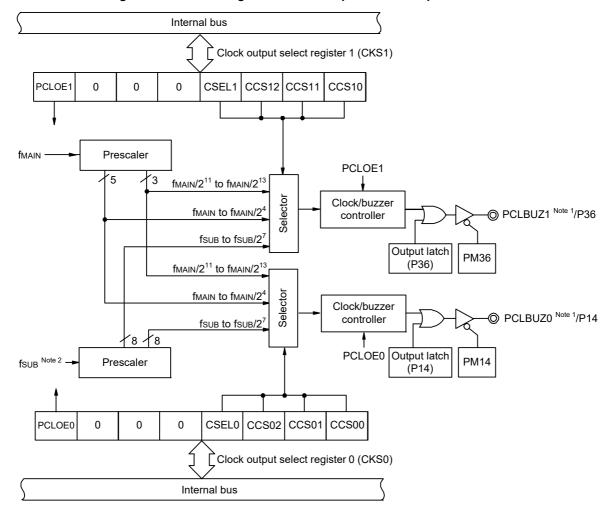

| 10.2 Configuration of Clock Output/Buzzer Output Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 10.3 Registers Controlling Clock Output/Buzzer Output Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 342 |

| 10.3.1 Clock output select registers n (CKSn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 342 |

| 10.3.2 Registers that control port functions of clock output/buzzer output pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 344 |

| 10.4 Operations of Clock Output/Buzzer Output Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 345 |

| 10.4.1 Operation as output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 345 |

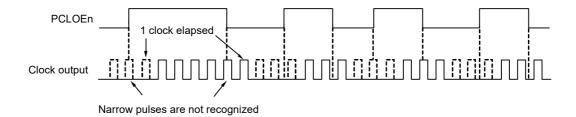

| 10.5 Cautions of clock output/buzzer output controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 345 |

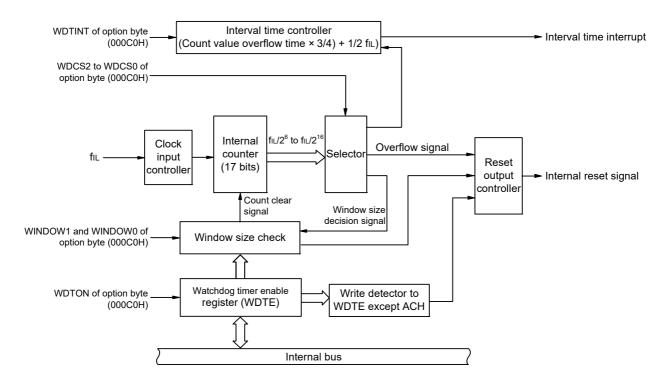

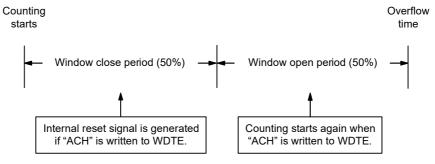

| 11. WATCHDOG TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 346 |

| 11.1 Functions of Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 346 |

| 11.2 Configuration of Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 11.3 Register Controlling Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 11.3.1 Watchdog timer enable register (WDTE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 11.4 Operation of Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |