# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

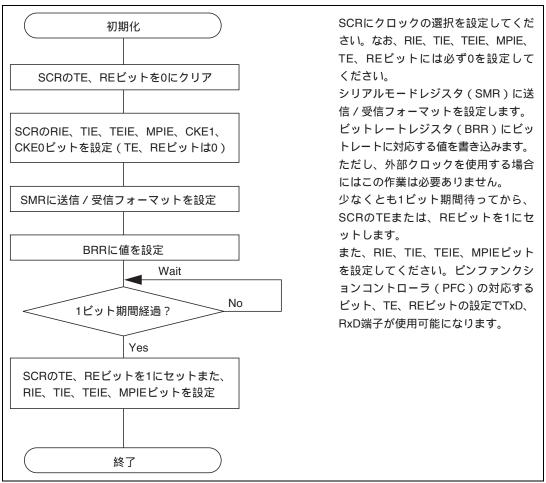

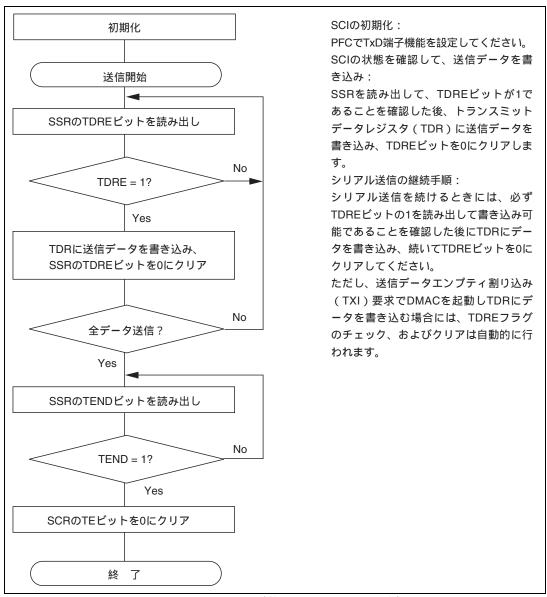

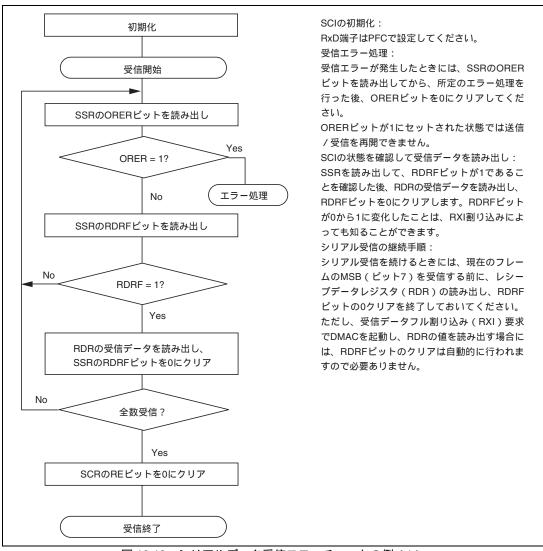

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

# SH7014、SH7016、SH7017F-ZTAT $^{TM}$

ハードウェアマニュアル

ルネサス32ビットRISCマイクロコンピュータ SuperH<sup>™</sup> RISC engineファミリ/ SH7010シリーズ

> SH7014 HD6417014F28 HD6417014RF28

SH7016 HD6437016F28 SH7017 HD64F7017F28

### ■ 本資料ご利用に際しての留意事項 ■

- 1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報 の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負い ません。

- 3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認頂きますとともに、弊社ホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意下さい。

- 5. 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに 起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

- 6 . 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム 全体で十分に評価し、お客様の責任において適用可否を判断して下さい。弊社は、適用可否に 対する責任は負いません。

- 7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会下さい。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないで下さい。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1)生命維持装置。

- 2)人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行なうもの。

- 4)その他、直接人命に影響を与えるもの。

- 9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件 およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品 をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

- 10.弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が 発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作 が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において 冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウエアおよびソフトウエ ア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に マイコンソフトウエアは、単独での検証は困難なため、お客様が製造された最終の機器・システム としての安全検証をお願い致します。

- 11.本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の 事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、 お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故に つきましては、弊社はその責任を負いません。

- 12.本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固くお断り致します。

- 13.本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業窓口までご照会下さい。

### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

### 2. 電源投入時の処置

【注意】電源投入時は,製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザープアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。 プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

# はじめに

SH7014、SH7016、SH7017 は、ルネサス テクノロジオリジナルの RISC (Reduced instruction set computer )方式の CPU をコアにして、システム構成に必要な周辺機能を集積したシングルチップ RISC マイコンです。

本 LSI の CPU は、RISC 方式の命令セットを持っており、基本命令は1命令1ステート(1システムクロックサイクル)で動作するので、命令実行速度が飛躍的に向上しています。また内部 32 ビット構成を採用しており、データ処理能力を強化しています。本 LSI の CPU によって、従来のマイコンでは実現が不可能だった、高速性が要求されるリアルタイム制御などのアプリケーションでも、低コストでかつ高性能/高機能なシステムを組むことができるようになります。

さらに本 LSI はシステム構成に必要な周辺機能として、大容量 ROM (ROM レス版の SH7014 を除く)、RAM、タイマ、シリアルコミュニケーションインタフェース (SCI)、A/D 変換器、割り込みコントローラ (INTC)、I/O ポートなどを内蔵しています。また、外部メモリアクセスサポート機能により、メモリや周辺 LSI とを効率的に接続できます。これらにより、システムコストの大幅な低減が可能です。

内蔵 ROM にはマスク ROM 版、およびフラッシュメモリ版があります。フラッシュメモリは本 LSI の書き込みをサポートしているライタを用いてプログラムの書き込みができるほか、ソフトウェアで書き込み / 消去することもできます。

このハードウェアマニュアルでは、本LSIのハードウェアについて説明します。命令の詳細については、プログラミングマニュアルをご覧ください。

#### 関連するマニュアル

SH7014、SH7016、SH7017 の実行命令について

「SH-1/SH-2/SH-DSP ソフトウェアマニュアル」

開発環境システムについては、弊社営業所までお問い合わせください。

# 本版で改訂された箇所

| 修正項目                                                                      | ページ   | 修正内容(詳細はマニュアル参照)                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 全体                                                                        | -     | 社名変更による修正<br>(修正前)日立製作所 → (修正後)ルネサス テクノロジ                                                                                                                                                                                                       |

| はじめに                                                                      | -     | 記述を修正<br>さらに本 LSI はシステム構成に必要な周辺機能として、大容量 ROM<br>(ROM レス版の SH7014 を除く)、RAM、タイマ、シリアルコミュニケーションインタフェース(SCI)、A/D 変換器、割り込みコントローラ(INTC)、I/O ポートなどを内蔵しています。                                                                                             |

| 1.1 SH7014/16/17 の特長表 1.1 特長                                              | 1-3   | 表を修正      頂目                                                                                                                                                                                                                                    |

| 5.1.2 例外処理の動作表 5.2 例外要因検出と例外処理開始タイミング                                     | 5-2   | 表を修正         例外処理         要因検出および処理開始タイミング           命令         トラップ命令<br>一般不当命令         TRAPA 命令の実行により開始される           過距づ飲命令(選延スロット)以外にある未定義コードがデコードされると開始される           スロット不当命令         遅延分岐命令(遅延スロット)に配置された未定義コードまたはPCを書き換える命令がデコードされると開始される |

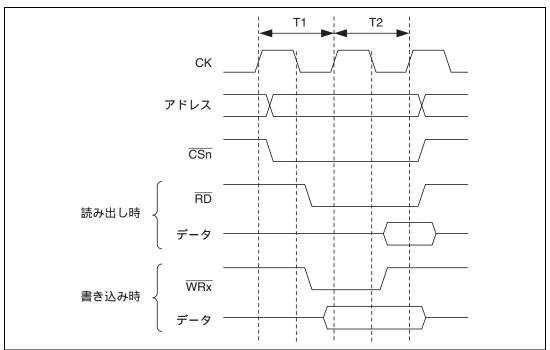

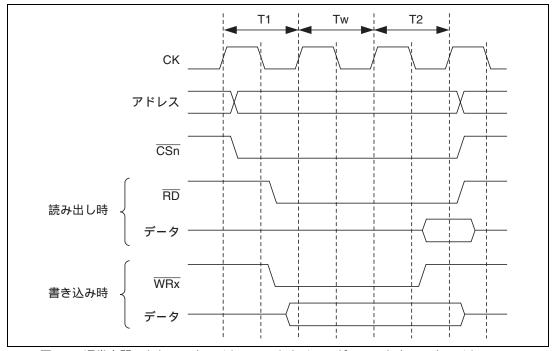

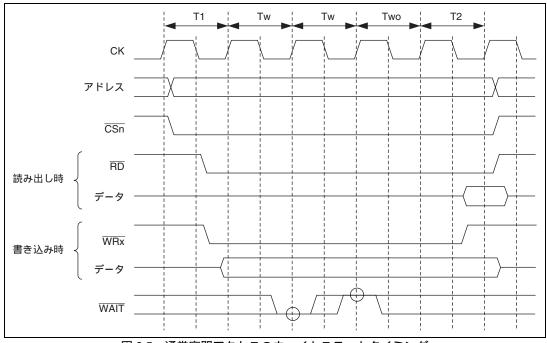

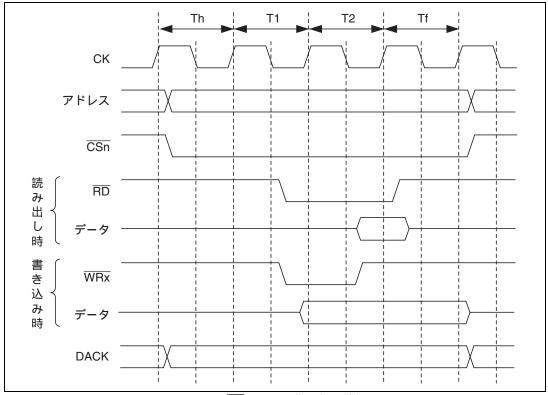

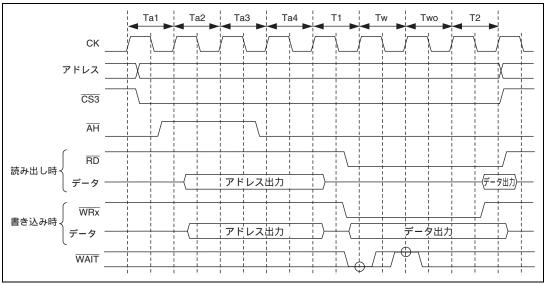

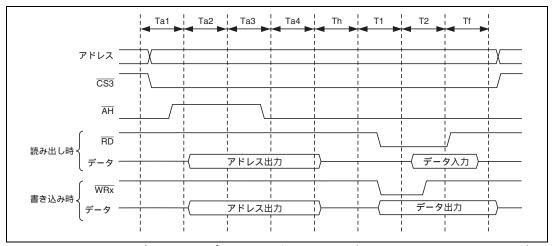

| 8.3.3 CS アサート期間拡張<br>図 8.6 CS アサート期間拡張<br>機能                              | 8-22  | 図を修正<br>書き<br>込込<br>み<br>時                                                                                                                                                                                                                      |

| 9.5 使用上の注意                                                                | 9-30  | 記述を修正<br>(6) DMAC に起動をかける場合は、CHCR、DMAOR の設定を最後に行ってください。それ以外のレジスタを最後に設定すると正常に動作しない場合があります。                                                                                                                                                       |

| 10.2.4 タイマインタラプトイネーブルレジスタ ( TIER )<br>ビット 3 : TGR インタラプトイネーブル D ( TGIED ) | 10-22 | 記述を修正<br>チャネル 0 で TSR レジスタの TGFD ビットが 1 にセットされたとき、TGFD による割り込み要求を許可または禁止します。                                                                                                                                                                    |

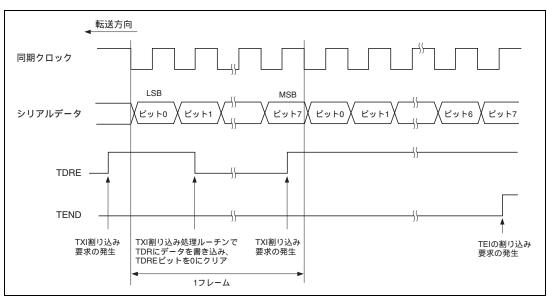

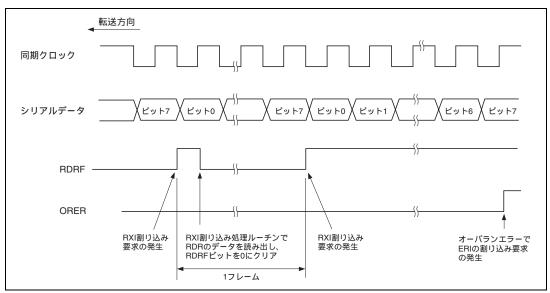

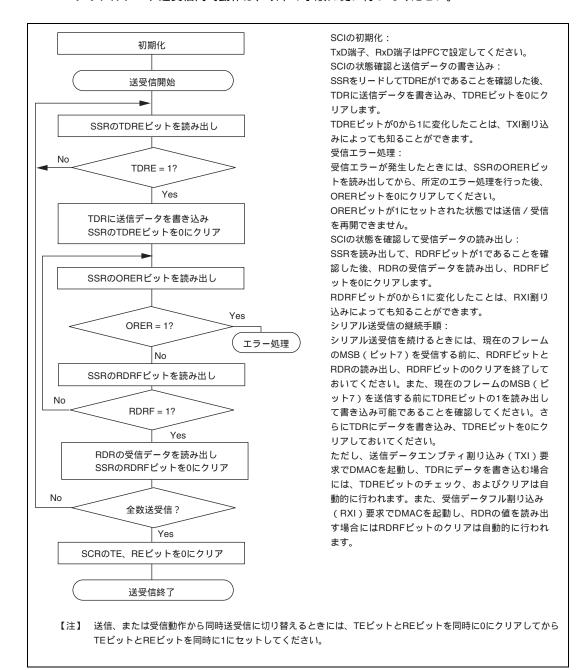

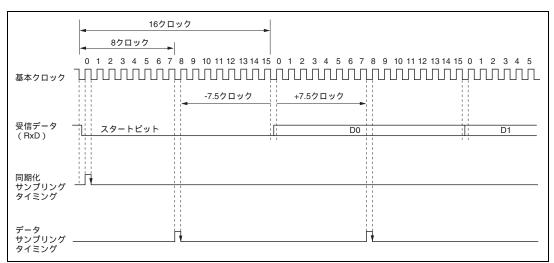

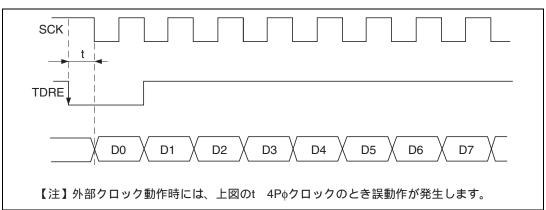

| 12.5 使用上の注意<br>図 12.22 DMAC によるクロッ<br>ク同期式送信時の例                           | 12-55 | 注を追加<br>【注】外部クロック動作時には、上記の t 4Pφクロックのとき誤動<br>作が発生します。                                                                                                                                                                                           |

改-1

| 修正項目                                                                                                                                  | ページ   | 修正内容(詳細はマニュアル参照)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

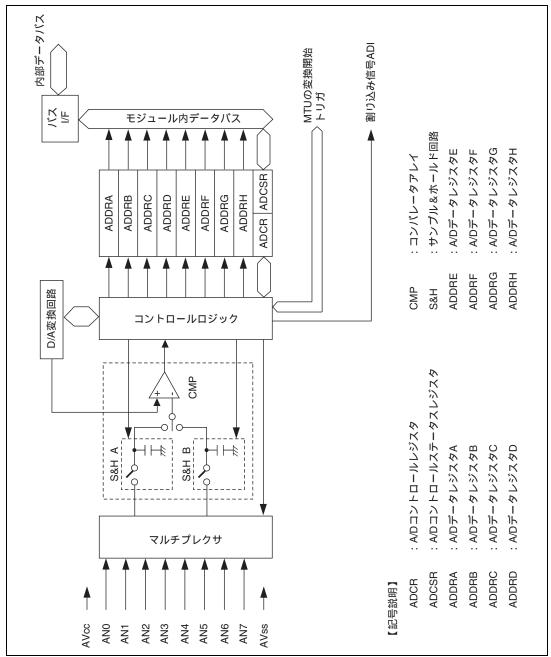

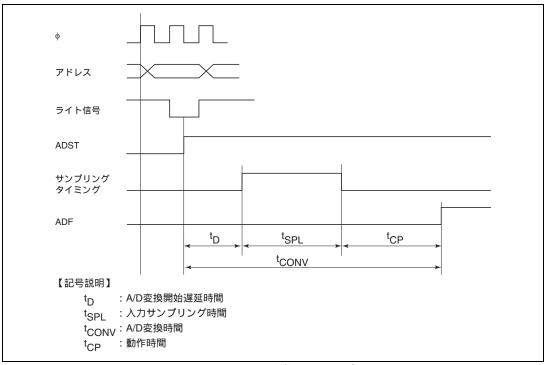

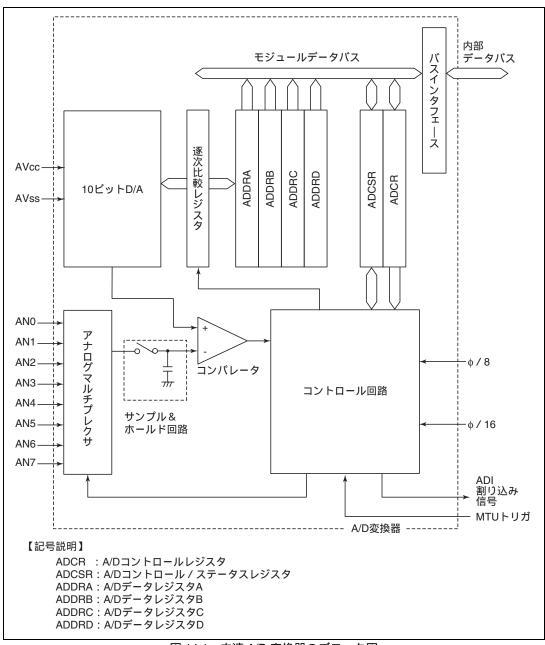

| 修正項目<br>13.1.2 プロック図<br>図 13.1 高速 A/D 変換器のプロック図                                                                                       | 13-2  | WELN合(詳細はマニュアル参照)  図を修正  AVcc ANO ADDRA |

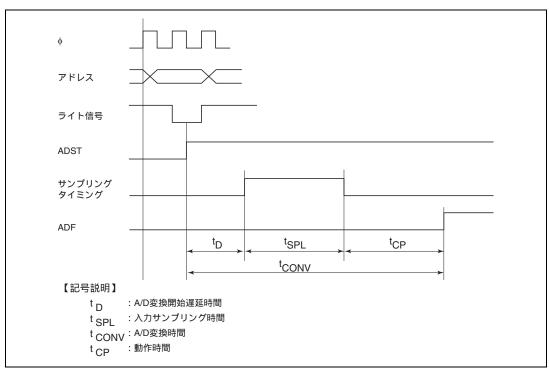

| 13.4.8 A/D 変換時間                                                                                                                       | 13-21 | 記述を修正 ADCSRのCKS ビットは動作時間 t <sub>CONV</sub> が、2μs 以上になるように設定してください。動作周波数と CKS ビットの設定を表 13.7 に示します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14.5 割り込み                                                                                                                             | 14-14 | 説明を修正<br>中速 A/D 変換器の割り込み要因を表 14.5 に示します。<br>ADI 割り込みにより起動された DMAC による A/D のレジスタアクセ<br>スすると ADCSR の ADF ビットは自動的に 0 クリアされます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16.1 概要<br>表 16.1 マルチプレクス一覧<br>表                                                                                                      | 16-1  | 概能1     機能2       (関連モジュール)     (関連モジュール)       (関連モジュール)     (関連モジュール)       A18 出力(BSC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16.3.2 ポート A コントロール<br>レジスタ L1、L2 ( PACRL1、<br>PACRL2 )<br>(1) ポート A コントロールレ<br>ジスタ L1 ( PACRL1 )<br>ビット 8: PA12 モードビット<br>( PA12MD ) | 16-13 | とット8       PA12MD       説 明         0       汎用入出力(PA12)(内蔵 ROM 無効モードではWRL)       (初期値)         1       下位側書き込み出力(WRL)(シルグルチップモードでは PA12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16.3.10 ポートEコントロー<br>ルレジスタ 1、2 (PECR1、<br>PECR2)                                                                                      | 16-30 | 記述を修正 ポート E コントロールレジスタ 1、2 ( PECR1、 PECR2 ) は、それぞれ、16 ビットの読み出し / 書き込み可能なレジスタで、ポート E にある 16 本のマルチプレクス端子の機能を選びます。 PECR1 は、ポート E の上位 8 ビットの端子の機能を、 PECR2 は、ポート E の下位 8 ビットの端子の機能を選びます。 PECR1、PECR2 は、外部からのパワーオンリセットで、それぞれ H'0000 に初期化されます。しかし、WDT によるリセット、スタンバイモード、スリープモードでは初期化されず、前のデータを保持します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

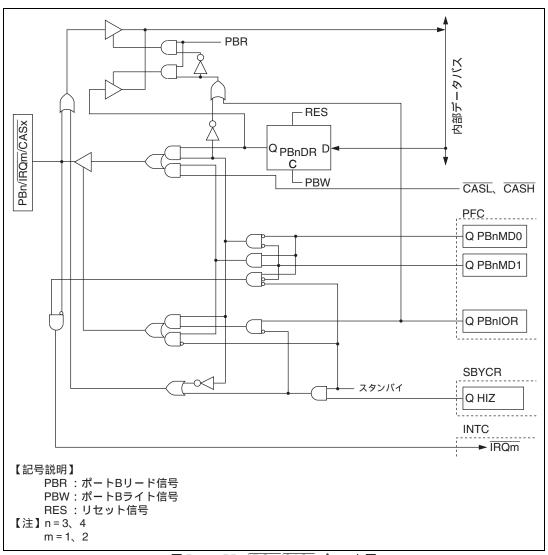

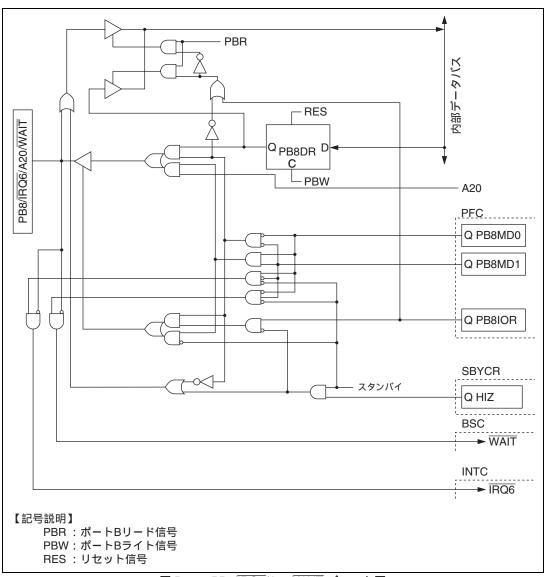

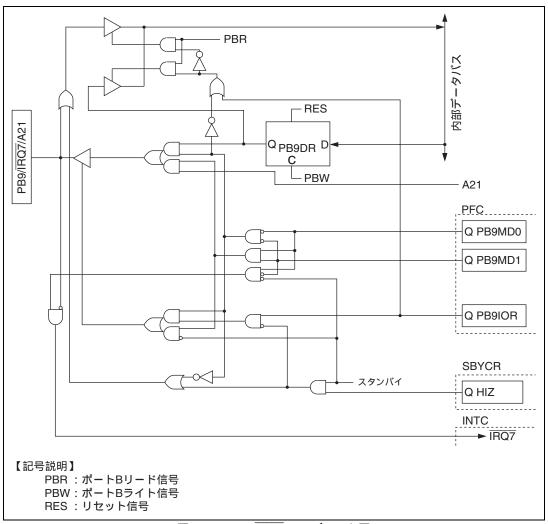

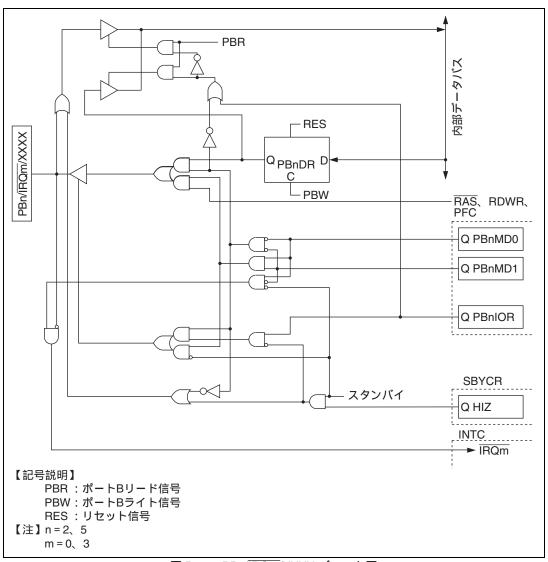

| 17.3 ポートB<br>図 17.2 ポートB                                                                                                              | 17-4  | 図を修正<br>シングルチップ<br>モード*<br>PB9 (入出力) /(RQ7 (入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 修正項目                                                                        | ページ   | 修正内容(詳細はマニュアル参照)                                                                                                                             |

|-----------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 18.5.1 フラッシュメモリコン<br>トロールレジスタ 1(FLMCR1)                                     |       | 図を修正                                                                                                                                         |

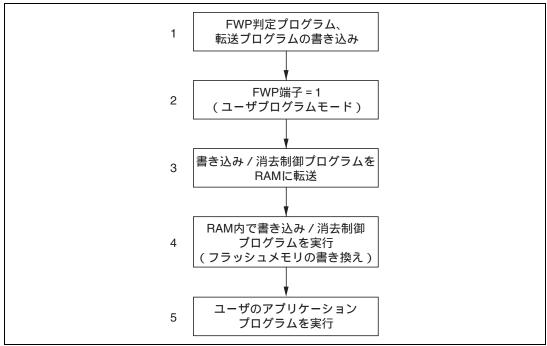

| 18.6.2 ユーザプログラムモード<br>図 18.12 ユーザプログラムモードの実行手順                              | 18-20 | 図を修正  FWP端子 = 1  (ユーザプログラムモード)                                                                                                               |

| 18.7.1 プログラムモード                                                             | 18-21 | 記述を修正<br>次に、プログラムの暴走等により過剰時間書き込みを行わないよう<br>にするために、ウォッチドッグタイマを設定します。WDT のオーバ<br>フロー周期は 300μs 以上にしてください。                                       |

| 18.8.1 ハードウェアプロテクト<br>表 18.8 ハードウェアプロテクト                                    | 18-34 | 表を修正       説明         FWP端子<br>プロテクト       • FWP端子にローレベルが入力されているときには、FLMCR1、EBR1 は初田できた。         が期化され、書き込み/消去プロテクト状態になります。                  |

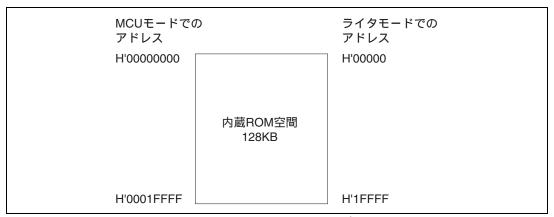

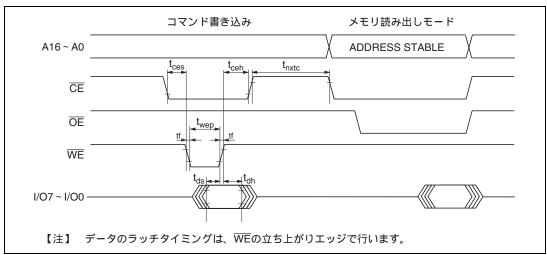

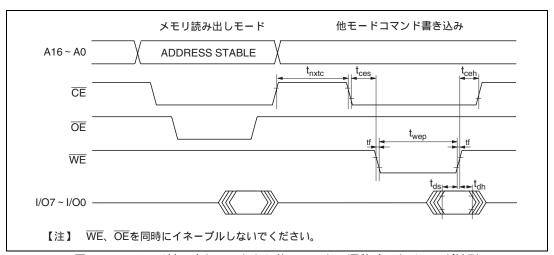

| 18.11.2 ライタモードの動作表 18.11 ライタモード時の各動作モードの設定方法                                | 18-41 | 表を修正       モード       ピン名         A17~A0       リード       Ain         出力ディスエーブル       X         コマンド書き込み       *Ain         チップディスエーブル       X |

| 18.11.6 ステータス読み出し<br>モード<br>表 18.18 ステータス読み出し<br>モード時の AC 特性                | 18-47 | 表を修正                                                                                                                                         |

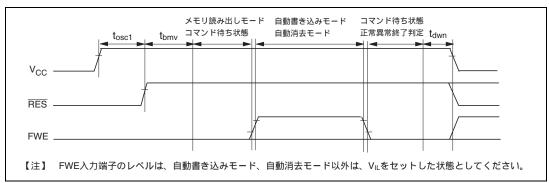

| 18.11.8 ライタモードへの遷<br>移時間<br>図 18.27 発振安定時間、ブー<br>トプログラム転送時間、電源立<br>ち下げシーケンス | 18-49 | 注を修正<br>【注】FWE 入力端子のレベルは、自動書き込みモード、自動消去モード以外は、V <sub>L</sub> をセットした状態としてください。                                                                |

| 修正項目                                                 | ページ    | 修正内容(詳細はマニュアル参照)                                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

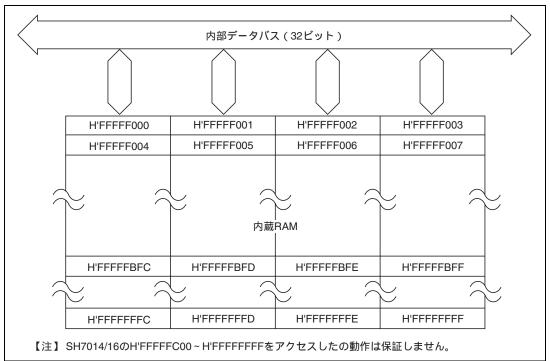

| 20.1 概要                                              | 20-1   | 記述を修正 SH7014/16 は 3K バイト、SH7017 は 4K バイトの RAM を内蔵しています。内蔵 RAM は、32 ビット幅のデータバスを介して、CPU、ダイレクトメモリアクセスコントローラ(DMAC)に接続されており(図 20.1)、8、16 または 32 ビット幅で、内蔵 RAM をアクセスすることができます。 DMAC は 8 または 16 ビット幅でアクセスすることができます。 内蔵 RAM のデータは、常に 1 ステートでアクセスできます。 したがって、高速アクセスが必要なプログラムエリア、あるいはスタックエリアやデータエリアとしての使用に適しています。内蔵 RAM の内容は、スリープモード、スタンバイモードでは保持されます。 |  |  |  |

| 22.2 DC 特性<br>表 22.2 DC 特性                           | 22-2   | 表を修正  項目 測定条件 シュミット PA2、PA5、 VT・Vcc - 0.7 (max ) トリガ入力 PA6~PA9 電圧 PE0~PE15 VT 0.5 (min )                                                                                                                                                                                                                                                    |  |  |  |

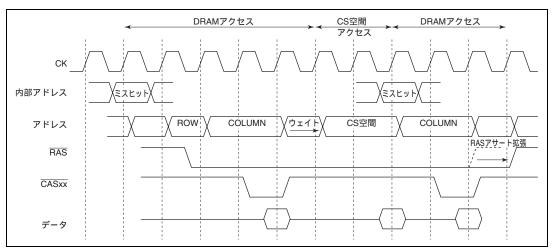

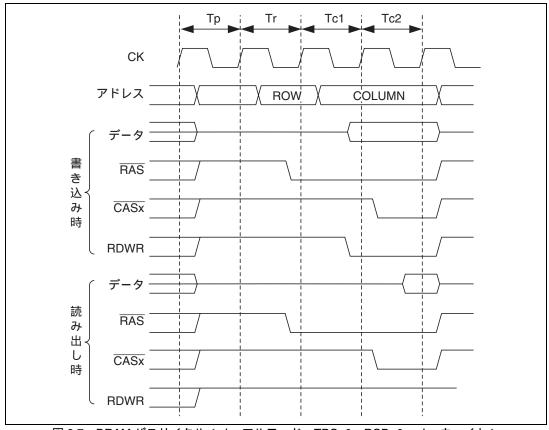

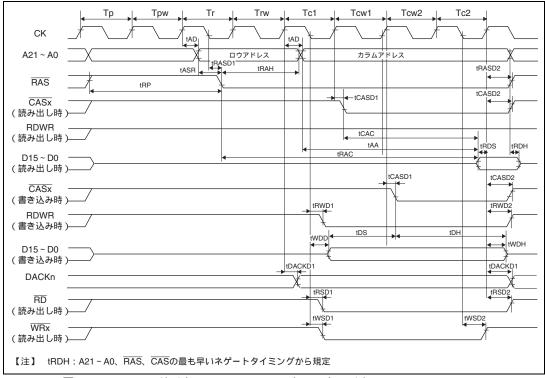

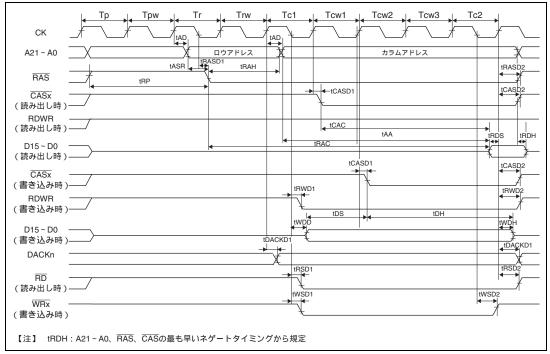

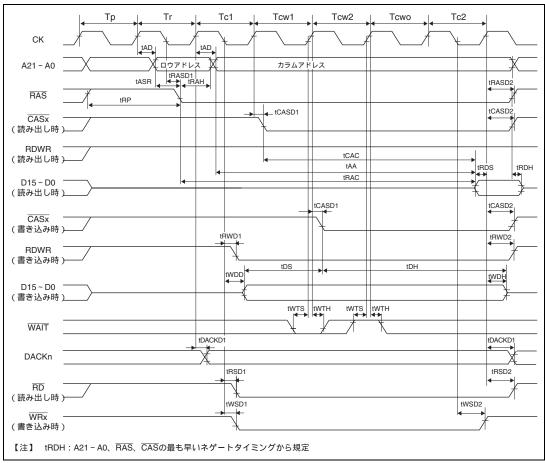

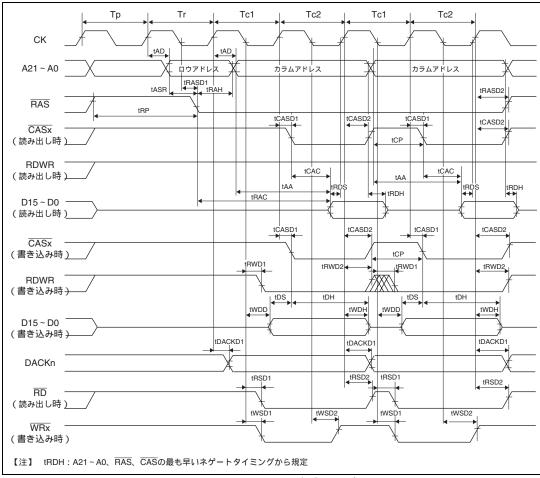

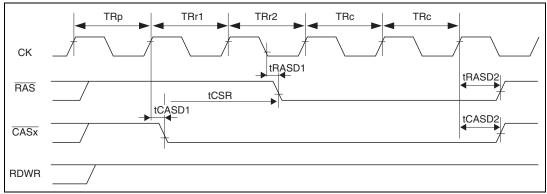

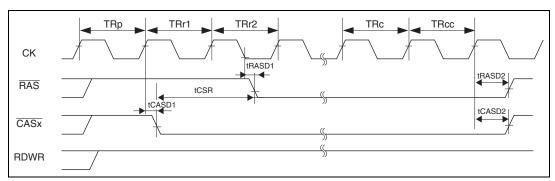

| 22.3.3 バスタイミング<br>図 22.9 DRAM サイクル( ノーマルモード、ノーウェイト ) | 22-13  | タイトルを修正                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| A.2 機能一覧<br>フラッシュメモリコントロー<br>ルレジスタ 1(FLMCR1)         | 付録-87  | ビットの表を修正       近ット       頂目 7 6 5 4 3 2 1 0       ビット名 FWE SWE ESU PSU EV PV E P       初期値 1/0 0 0 0 0 0 0 0 0     0 0 0 0 0       RW R RW RW RW RW RW RW RW RW     RW RW RW                                                                                                                                                                |  |  |  |

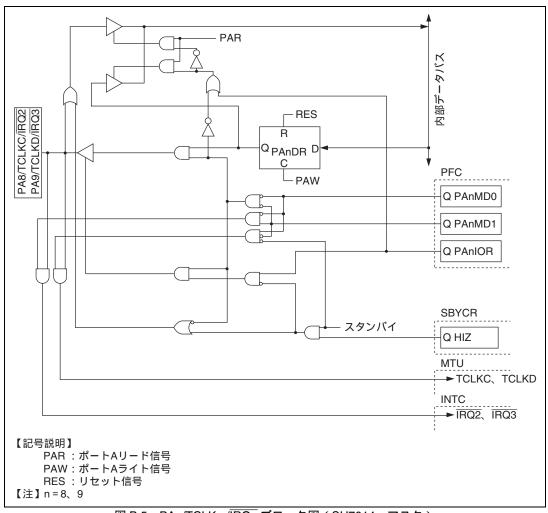

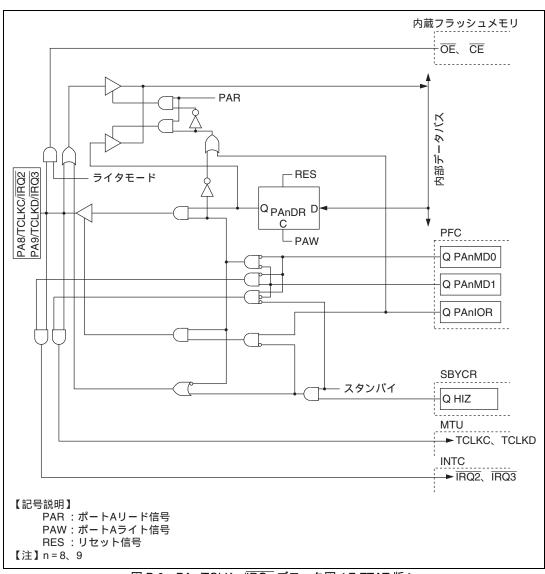

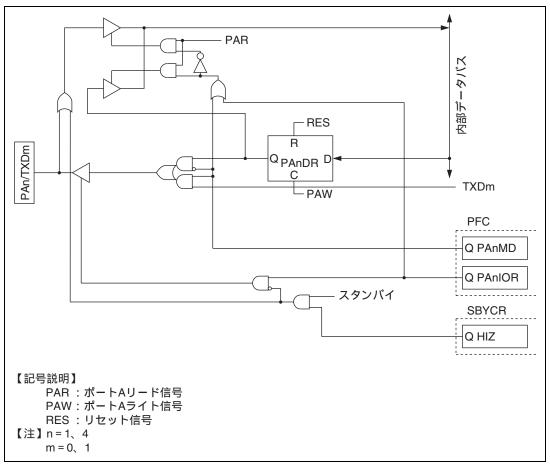

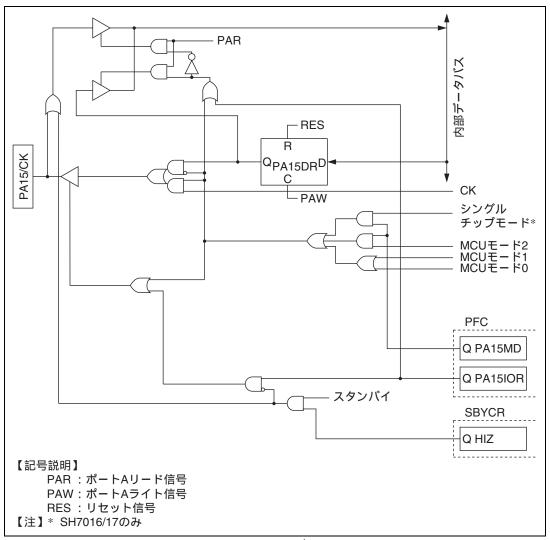

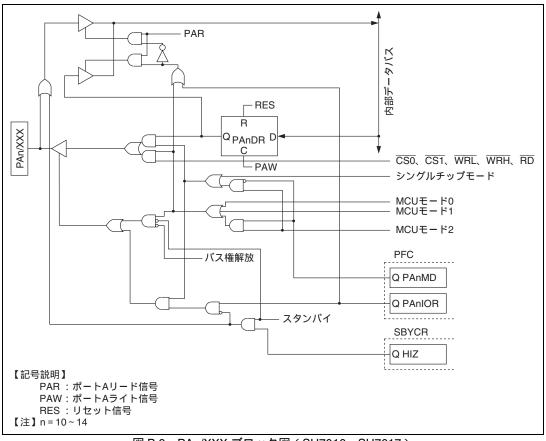

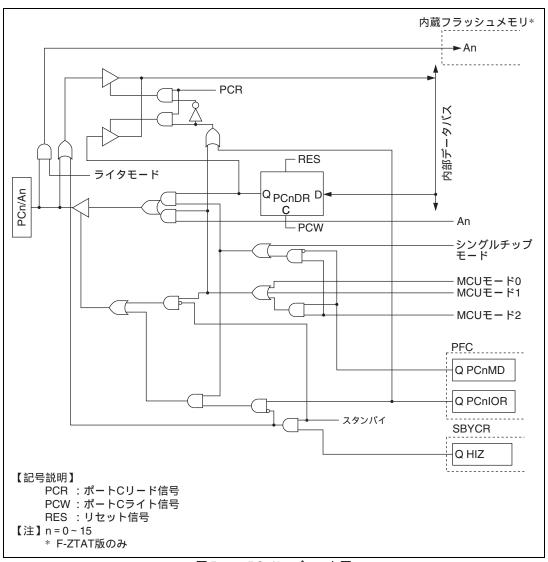

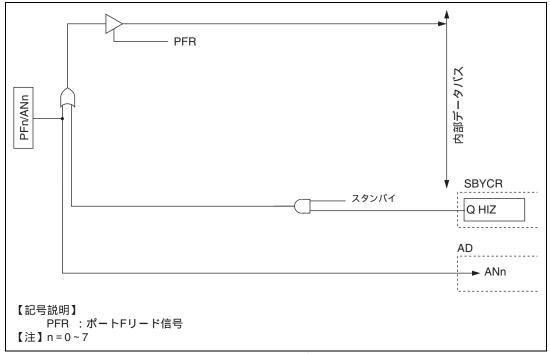

| B. I/O ポートブロック図<br>図 B.17 PCn/An ブロック図               | 付録-107 | タイトルを修正                                                                                                                                                                                                                                                                                                                                     |  |  |  |

すべての商標および登録商標は、それぞれの所有者に帰属します。

# 目次

| 第1    | 章 概要    |                   |      |

|-------|---------|-------------------|------|

| 1.1   | SH7014/ | 16/17 <b>の</b> 特長 | 1-1  |

| 1.2   | ブロック    | 7 図               | 1-4  |

| 1.3   | 端子説明    | ]                 | 1-6  |

|       | 1.3.1   | ピン配置図             | 1-6  |

|       | 1.3.2   |                   |      |

|       | 1.3.3   | 端子機能              | 1-11 |

| 第2    | 章 CPU   |                   |      |

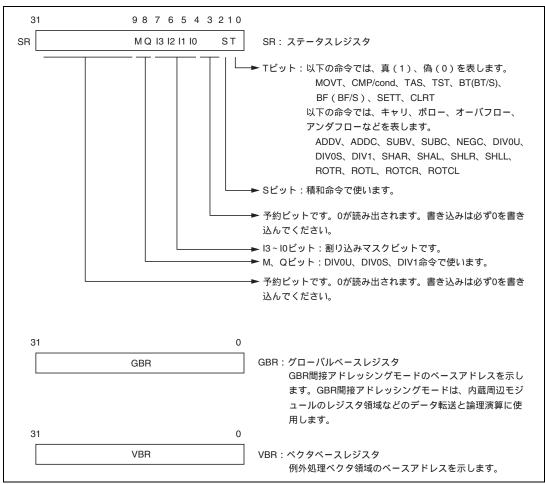

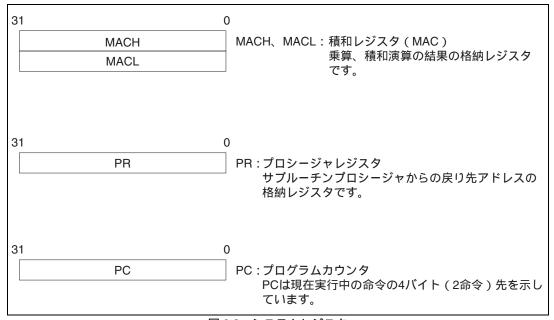

| 2.1   | レジスタ    | 7構成               | 2-1  |

|       | 2.1.1   | 汎用レジスタ(Rn)        | 2-1  |

|       | 2.1.2   | コントロールレジスタ        | 2-2  |

|       | 2.1.3   | システムレジスタ          |      |

|       | 2.1.4   | レジスタの初期値          |      |

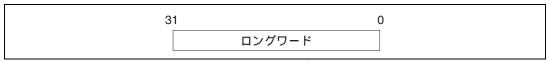

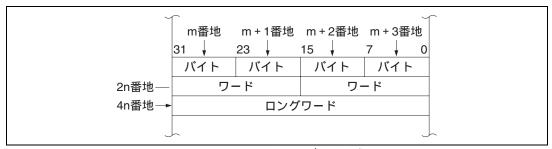

| 2.2   | データ形    | <u> </u>          | 2-4  |

|       | 2.2.1   | レジスタのデータ形式        | 2-4  |

|       | 2.2.2   | メモリ上でのデータ形式       |      |

|       | 2.2.3   | イミディエイトデータのデータ形式  |      |

| 2.3   | 命令の特    | 持長                | 2-5  |

|       | 2.3.1   | RISC 方式           |      |

|       | 2.3.2   | アドレッシングモード        |      |

|       | 2.3.3   | 命令形式              |      |

| 2.4   | 命令セッ    | <i>y</i>          | 2-13 |

|       | 2.4.1   | 分類順命令セット          | 2-13 |

| 2.5   | 処理状態    |                   | 2-21 |

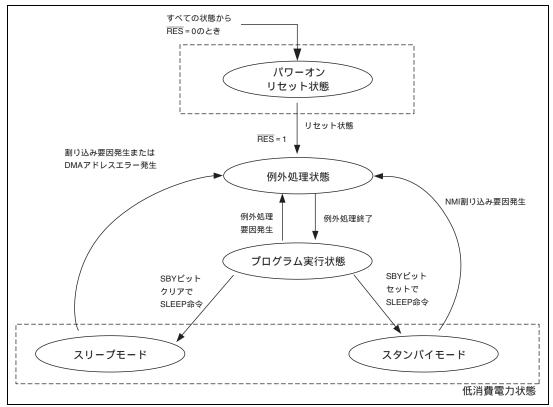

|       | 2.5.1   | 状態遷移              | 2-21 |

|       | 2.5.2   | 低消費電力状態           | 2-22 |

| 第3    | 章 動作も   | <b>∃− ド</b>       |      |

| 3.1   | 動作モー    | - ドの種類と選択         | 3-1  |

| 3.2   | 各動作モ    | Eードの説明            | 3-2  |

| 3.3   | 端子構成    | Ž                 | 3-2  |

| 第 4 : | 章 クロッ   | ック発振器(CPG)        |      |

| 4.1   | 概要      |                   | 4-1  |

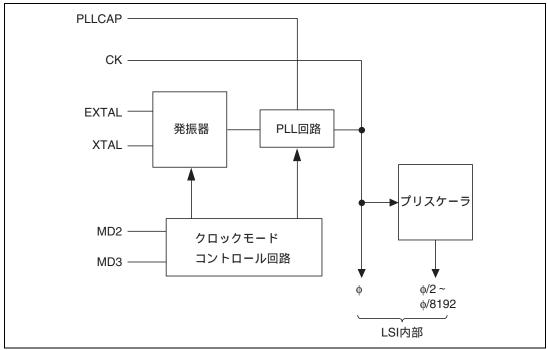

|       | 4.1.1   | ブロック図             | 4-1  |

| 4.2   |         |                   |      |

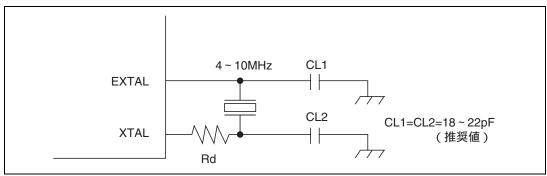

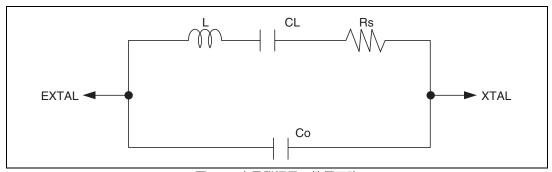

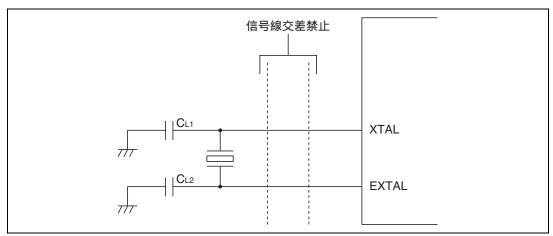

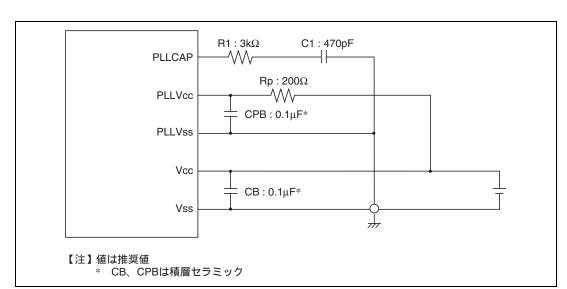

|       | 4.2.1   | 水晶発振子を接続する方法      | 4-2  |

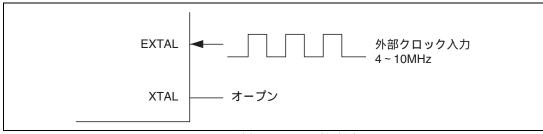

|       | 4.2.2   | 外部クロックを入力する方法     |      |

| 4.3 | プリスケーラ                               | 4-5  |

|-----|--------------------------------------|------|

| 第 5 | 章 例外処理                               |      |

| 5.1 | 概要                                   | 5-1  |

|     | 5.1.1 例外処理の種類と優先順位                   | 5-1  |

|     | 5.1.2 例外処理の動作                        |      |

|     | 5.1.3 例外処理ベクタテーブル                    | 5-2  |

| 5.2 | リセット                                 | 5-4  |

|     | 5.2.1 パワーオンリセット                      | 5-4  |

| 5.3 | アドレスエラー                              | 5-5  |

|     | 5.3.1 アドレスエラー発生要因                    | 5-5  |

|     | 5.3.2 アドレスエラー例外処理                    | 5-5  |

| 5.4 | 割り込み                                 | 5-6  |

|     | 5.4.1 割り込み要因                         | 5-6  |

|     | 5.4.2 割り込み優先順位                       | 5-6  |

|     | 5.4.3 割り込み例外処理                       |      |

| 5.5 | 命令による例外                              | 5-8  |

|     | 5.5.1 命令による例外の種類                     | 5-8  |

|     | 5.5.2 トラップ命令                         |      |

|     | 5.5.3 スロット不当命令                       |      |

|     | 5.5.4 一般不当命令                         |      |

| 5.6 | 例外処理が受け付けられない場合                      |      |

|     | 5.6.1 遅延分岐命令の直後                      |      |

|     | 5.6.2 割り込み禁止命令の直後                    |      |

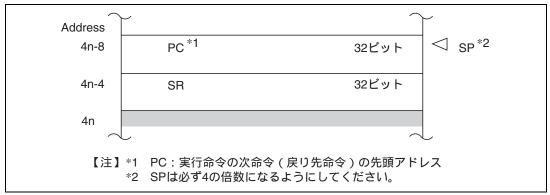

| 5.7 | 例外処理後のスタックの状態                        |      |

| 5.8 | 使用上の注意                               | 5-11 |

|     | 5.8.1 スタックポインタ (SP) の値               |      |

|     | 5.8.2 ベクタベースレジスタ ( VBR ) の値          |      |

|     | 5.8.3 アドレスエラー例外処理のスタッキングで発生するアドレスエラー | 5-11 |

| 第6  | i章 割り込みコントローラ(INTC)                  |      |

| 6.1 | 概要                                   | 6-1  |

|     | 6.1.1 特長                             | 6-1  |

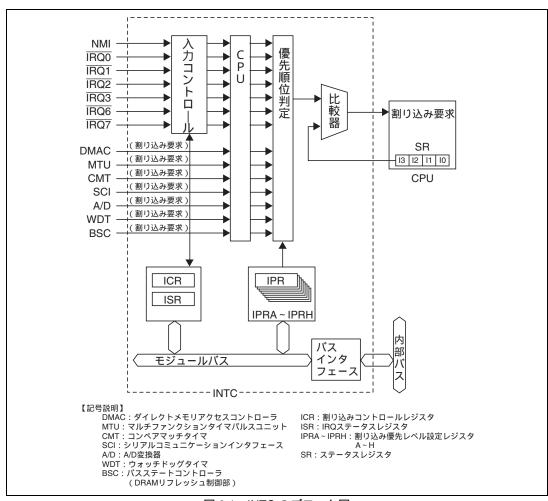

|     | 6.1.2 プロック図                          | 6-2  |

|     | 6.1.3 端子構成                           | 6-3  |

|     | 6.1.4 レジスタ構成                         |      |

| 6.2 | 割り込み要因                               |      |

|     | 6.2.1 NMI 割り込み                       |      |

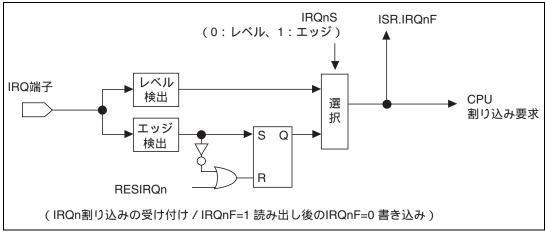

|     | 6.2.2 IRQ 割り込み                       |      |

|     | 6.2.3 内蔵周辺モジュール割り込み                  |      |

|     | 6.2.4 割り込み例外処理ベクタと優先順位               |      |

| 6.3 | レジスタの説明                              |      |

|     | 6.3.1 割り込み優先レベル設定レジスタ A~H(IPRA~IPRH) |      |

|     | 6.3.2 割り込みコントロールレジスタ (ICR)           |      |

|     | 6.3.3 IRQ ステータスレジスタ ( ISR )          | 6-9  |

| 6.4 | 動作説   | 明                                     | 6-11 |

|-----|-------|---------------------------------------|------|

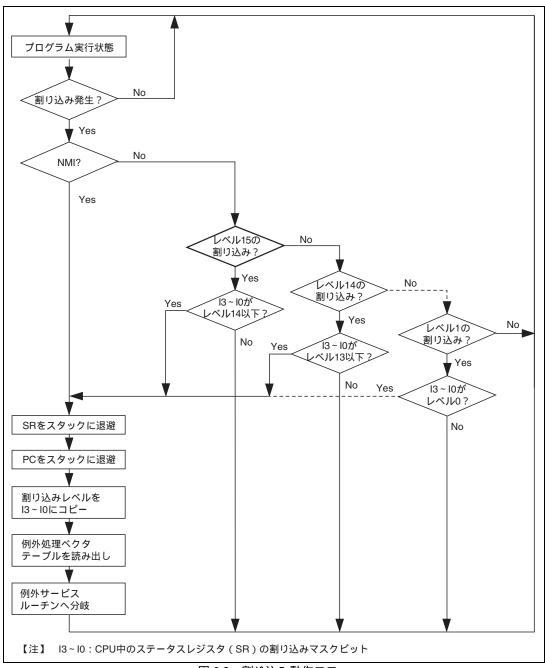

|     | 6.4.1 | 割り込み動作の流れ                             | 6-11 |

|     | 6.4.2 | 割り込み例外処理終了後のスタックの状態                   | 6-13 |

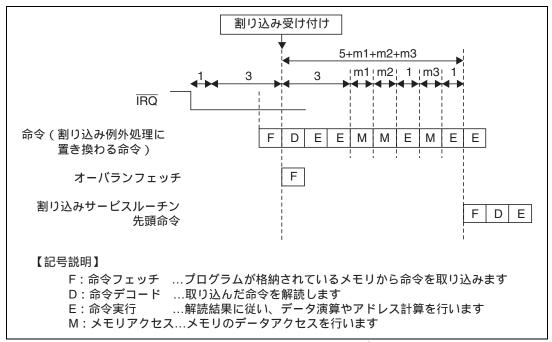

| 6.5 | 割り込む  | み応答時間                                 | 6-14 |

| 6.6 | 割り込む  | み要求信号によるデータ転送                         | 6-16 |

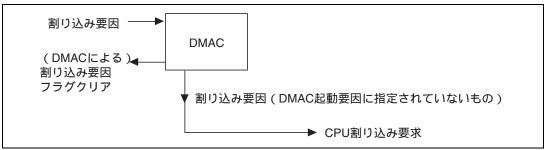

|     | 6.6.1 | 割り込み要求信号を DMAC の起動要因とし、               |      |

|     |       | CPU の割り込み要因としない場合                     | 6-16 |

|     | 6.6.2 | 割り込み要求信号を CPU の割り込み要因とし、              |      |

|     |       | DMAC の起動要因としない場合                      | 6-16 |

| 第7章 | 章 キャ  | ッシュメモリ(CAC)                           |      |

| 7.1 | 概要    |                                       | 7-1  |

|     | 7.1.1 | 特長                                    | 7-1  |

|     | 7.1.2 | ブロック図                                 | 7-2  |

|     | 7.1.3 | レジスタ構成                                | 7-3  |

| 7.2 | レジスケ  | タの説明                                  | 7-4  |

|     | 7.2.1 | キャッシュコントロールレジスタ(CCR)                  | 7-4  |

| 7.3 | アドレ   | スアレイとデータアレイ                           |      |

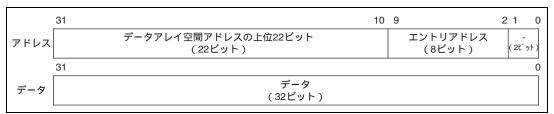

|     | 7.3.1 | キャッシュアドレスアレイ読み出し / 書き込み空間             | 7-6  |

|     | 7.3.2 | キャッシュデータアレイ読み出し / 書き込み空間              | 7-7  |

| 7.4 | 使用上的  | の注意                                   | 7-8  |

|     | 7.4.1 | キャッシュの初期化                             | 7-8  |

|     | 7.4.2 | アドレスアレイ、データアレイへの強制アクセス                |      |

|     | 7.4.3 | キャッシュミス時のペナルティと、キャッシュフィルのタイミング        | 7-8  |

|     | 7.4.4 | キャッシュミス後のキャッシュヒット                     | 7-10 |

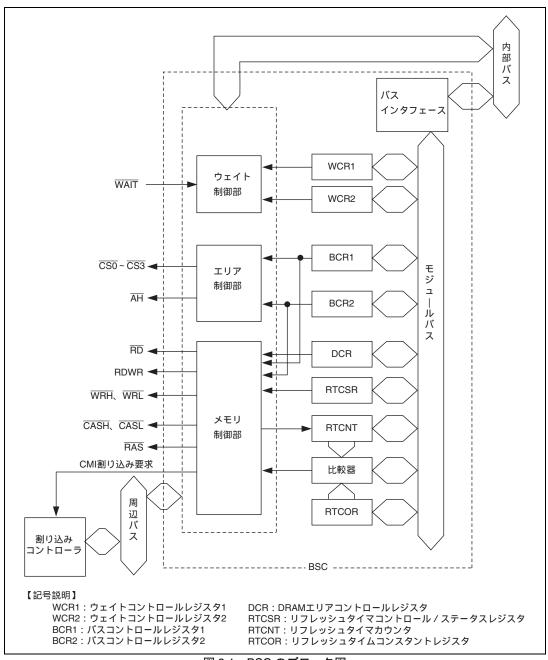

| 第8章 | 章 バス. | ステートコントローラ(BSC)                       |      |

| 8.1 | 概要    |                                       | 8-1  |

|     | 8.1.1 | 特長                                    | 8-1  |

|     | 8.1.2 | ブロック図                                 |      |

|     | 8.1.3 | 端子構成                                  | 8-3  |

|     | 8.1.4 | レジスタ構成                                | 8-3  |

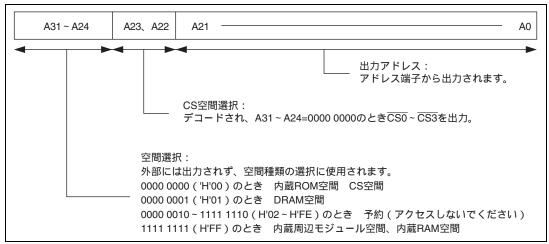

|     | 8.1.5 | アドレスマップ                               | 8-4  |

| 8.2 | レジスケ  | タの説明                                  | 8-6  |

|     | 8.2.1 | バスコントロールレジスタ 1 (BCR1)                 | 8-6  |

|     | 8.2.2 | バスコントロールレジスタ 2 ( BCR2 )               | 8-8  |

|     | 8.2.3 | ウェイトコントロールレジスタ 1 ( WCR1 )             | 8-11 |

|     | 8.2.4 | ウェイトコントロールレジスタ 2 ( WCR2 )             |      |

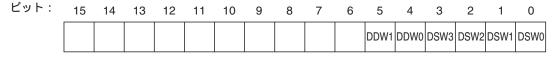

|     | 8.2.5 | DRAM エリアコントロールレジスタ ( DCR )            |      |

|     | 8.2.6 | リフレッシュタイマコントロール / ステータスレジスタ ( RTCSR ) |      |

|     | 8.2.7 | リフレッシュタイマカウンタ ( RTCNT )               |      |

| 0.2 | 8.2.8 | リフレッシュタイムコンスタントレジスタ(RTCOR)            |      |

| 8.3 |       | 間アクセス                                 |      |

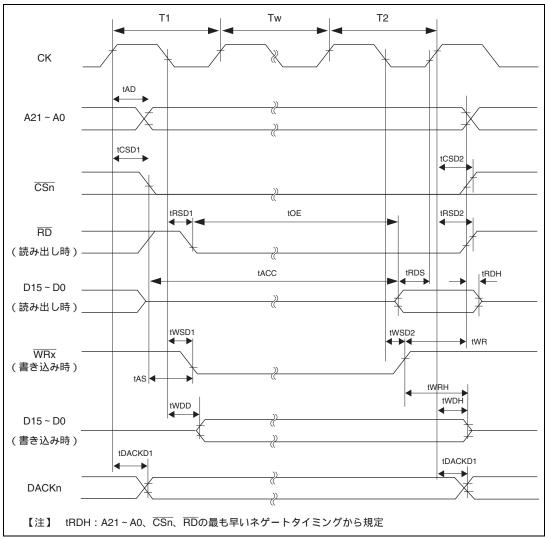

|     | 8.3.1 | 基本タイミング                               |      |

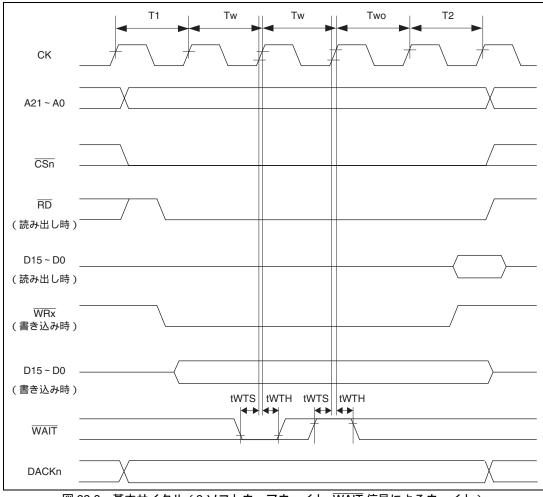

|     | 8.3.2 | ウェイトステート制御                            |      |

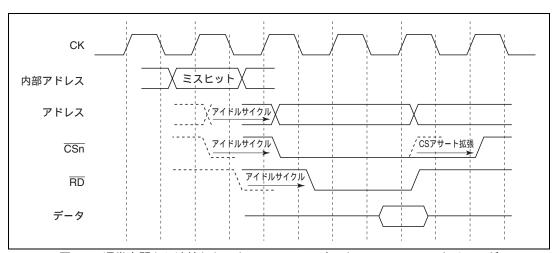

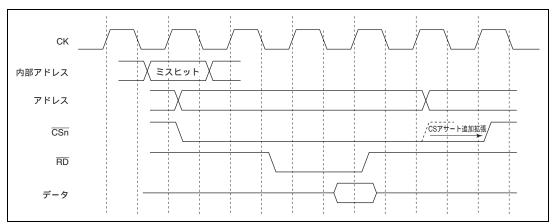

|     | 8.3.3 | <u>CS</u> アサート期間拡張                    | 8-22 |

| 8.4  | DRAM : | アクセス                                     | 8-23 |

|------|--------|------------------------------------------|------|

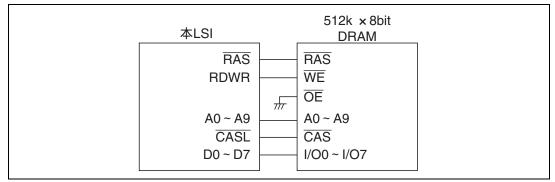

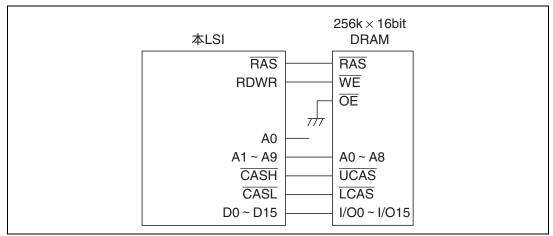

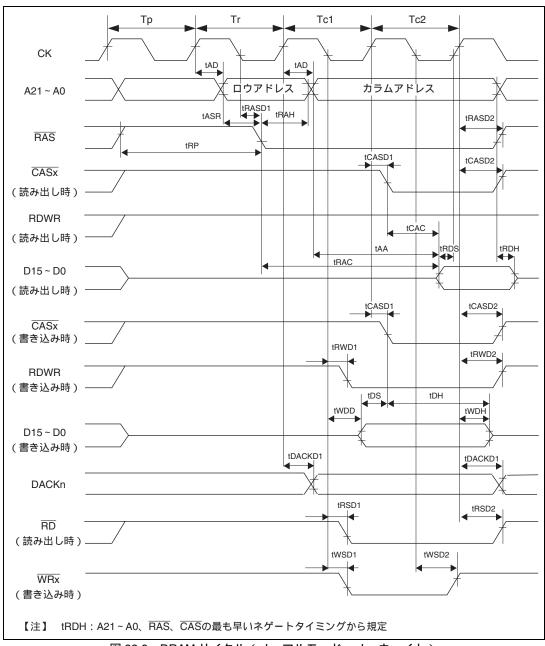

|      | 8.4.1  | DRAM 直結方式                                | 8-23 |

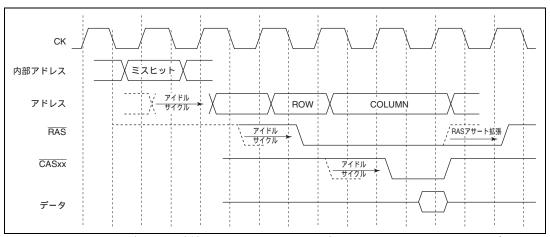

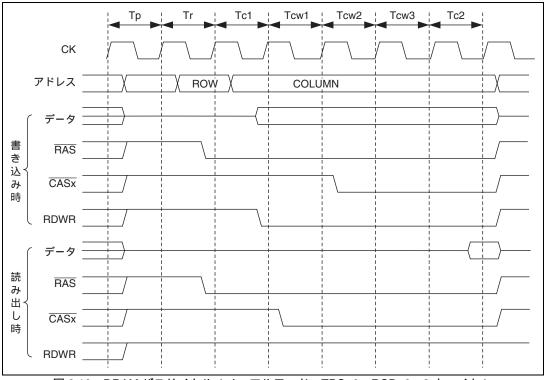

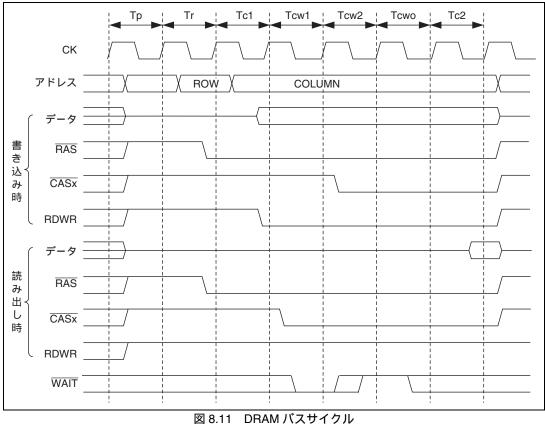

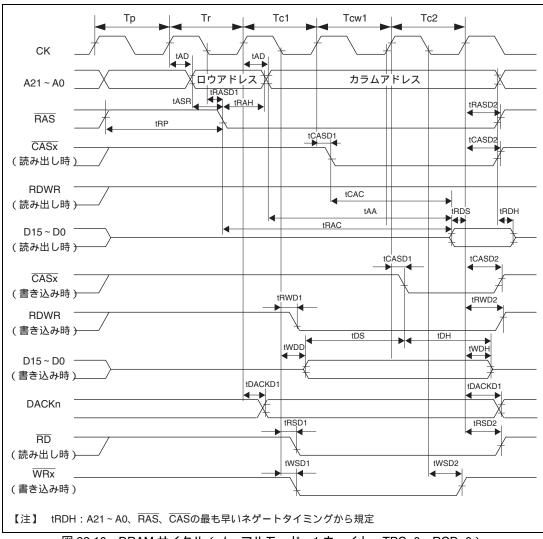

|      | 8.4.2  | 基本タイミング                                  | 8-24 |

|      | 8.4.3  | ウェイトステート制御                               | 8-25 |

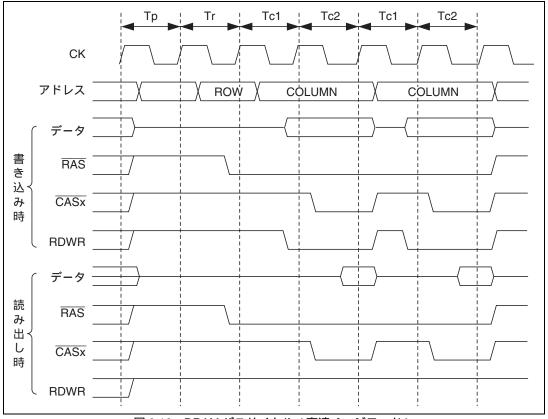

|      | 8.4.4  | バースト動作                                   |      |

|      | 8.4.5  | リフレッシュタイミング                              |      |

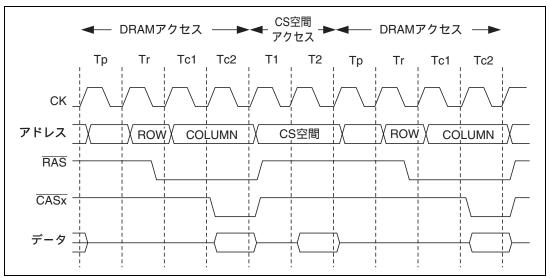

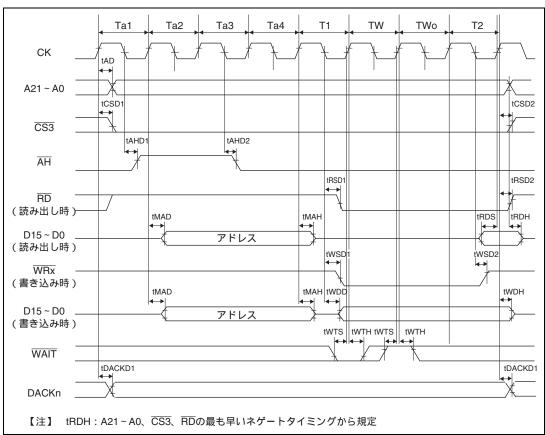

| 8.5  | アドレス   | ス / データマルチプレクス I/O 空間アクセス                | 8-33 |

|      | 8.5.1  | 基本タイミング                                  |      |

|      | 8.5.2  | ウェイトステート制御                               |      |

|      | 8.5.3  | CS アサート拡張                                |      |

| 8.6  | アクセス   | スサイクル間ウェイト                               |      |

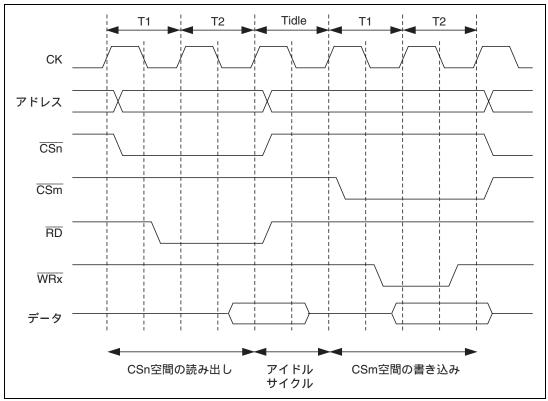

|      | 8.6.1  | データバス衝突防止                                | 8-36 |

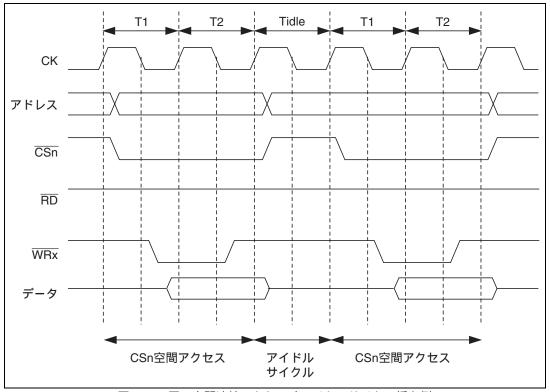

|      | 8.6.2  | バスサイクル開始検出の容易化                           |      |

| 8.7  | バスア-   | - ビトレーション                                | 8-38 |

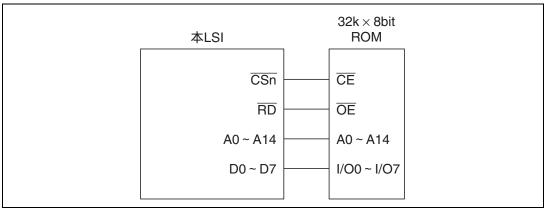

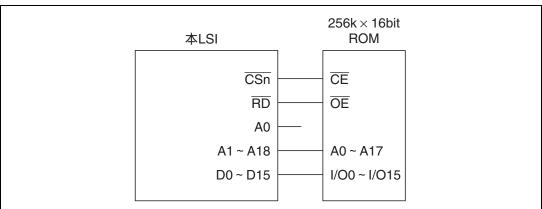

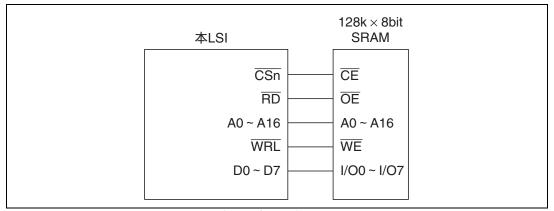

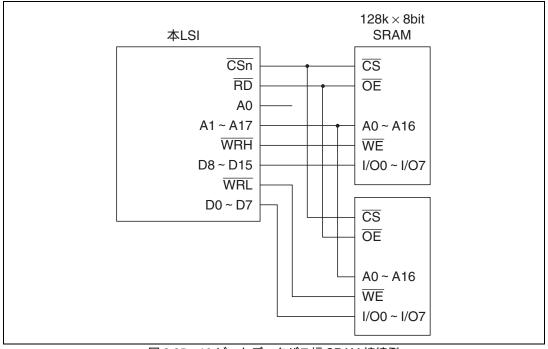

| 8.8  | メモリ持   | 妾続例                                      | 8-38 |

| 8.9  | 内蔵周辺   | □ I/O レジスタのアクセス                          | 8-41 |

| 8.10 | 外部人も   | Eリヘプログラムを配置したときの CPU 動作                  | 8-41 |

| 第9章  | 章 ダイし  | ンクトメモリアクセスコントローラ(DMAC)                   |      |

| 9.1  | 概要     |                                          | 9-1  |

|      | 9.1.1  | 特長                                       | 9-1  |

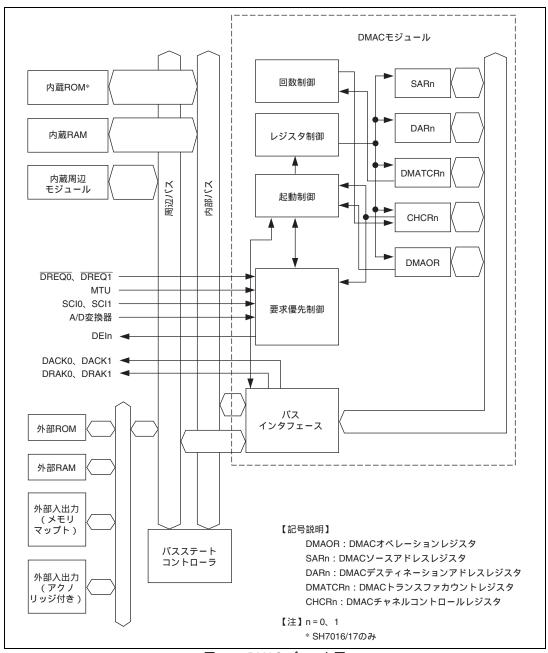

|      | 9.1.2  | DMAC ブロック図                               |      |

|      | 9.1.3  | 端子構成                                     | 9-3  |

|      | 9.1.4  | レジスタ構成                                   | 9-3  |

| 9.2  | 各レジス   | スタの説明                                    | 9-4  |

|      | 9.2.1  | DMA ソースアドレスレジスタ 0、1 (SAR0、SAR1)          | 9-4  |

|      | 9.2.2  | DMA デスティネーションアドレスレジスタ 0、1 ( DAR0、DAR1 )  |      |

|      | 9.2.3  | DMA トランスファカウントレジスタ 0、1 (DMATCR0、DMATCR1) |      |

|      | 9.2.4  | DMA チャネルコントロールレジスタ 0、1 (CHCR0、CHCR1)     | 9-5  |

|      | 9.2.5  | DMA オペレーションレジスタ ( DMAOR )                | 9-10 |

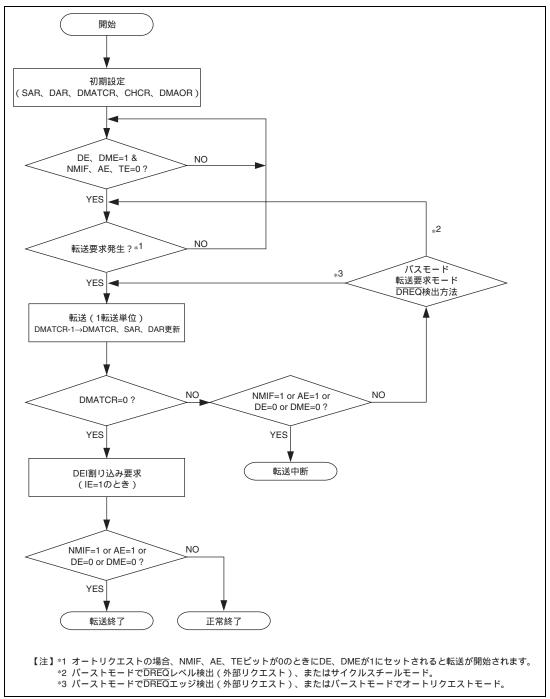

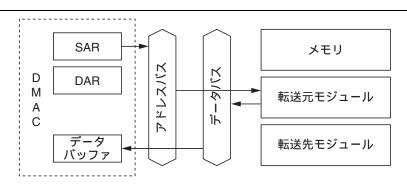

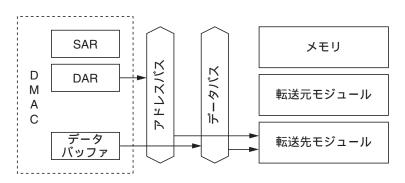

| 9.3  | 動作説明   | 月                                        | 9-12 |

|      | 9.3.1  | 動作説明                                     | 9-12 |

|      | 9.3.2  | DMA 転送要求                                 | 9-14 |

|      | 9.3.3  | チャネルの優先順位                                | 9-16 |

|      | 9.3.4  | DMA 転送の種類                                |      |

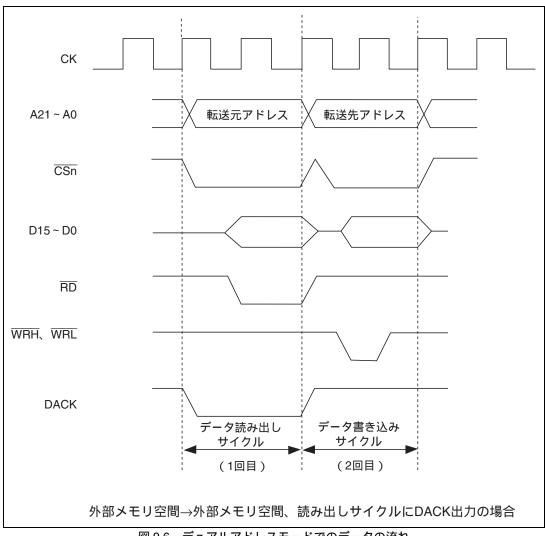

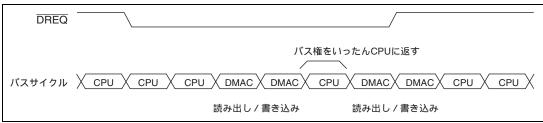

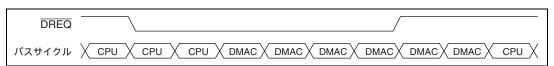

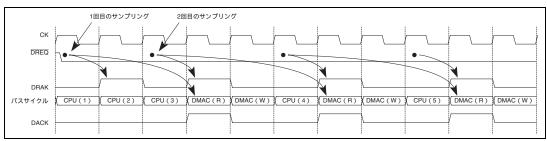

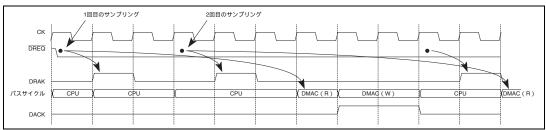

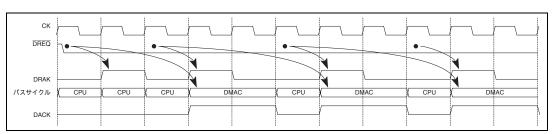

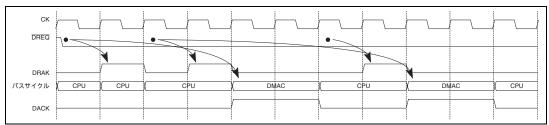

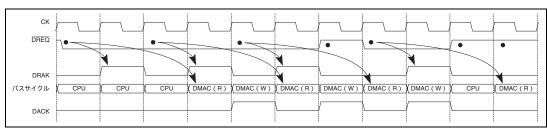

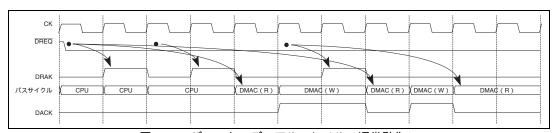

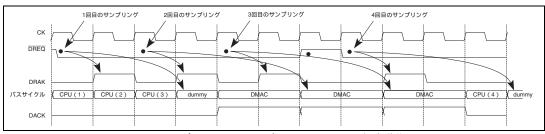

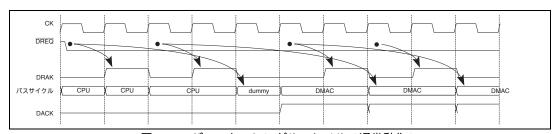

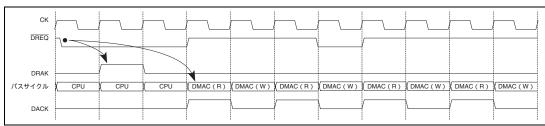

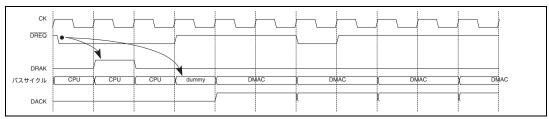

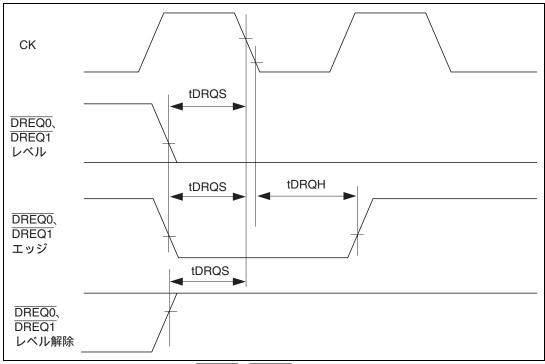

|      | 9.3.5  | バスサイクルのステート数と DREQ 端子のサンプリングタイミング        | 9-23 |

|      | 9.3.6  | DMA 転送終了                                 |      |

|      | 9.3.7  | CPU からの DMAC アクセス                        | 9-28 |

| 9.4  | 使用例    |                                          | 9-29 |

|      | 9.4.1  | 内蔵 SCI と外部メモリとの DMA 転送例                  | 9-29 |

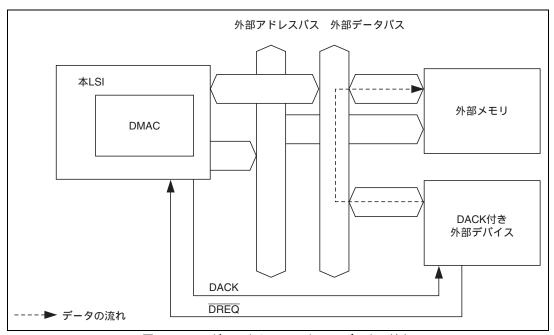

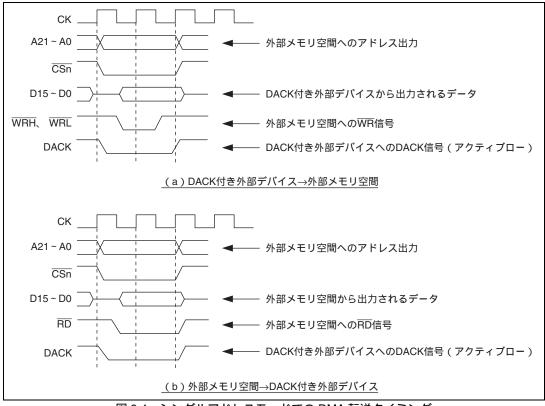

|      | 9.4.2  | 外部 RAM と DACK 付き外部デバイスとの DMA 転送例         |      |

| 9.5  | 使用上0   | D注意                                      |      |

# 第 10 章 マルチファンクションタイマパルスユニット (MTU)

| 10.1 | 概要                    |                             | 10-1  |

|------|-----------------------|-----------------------------|-------|

|      | 10.1.1 特              | 툱                           | 10-1  |

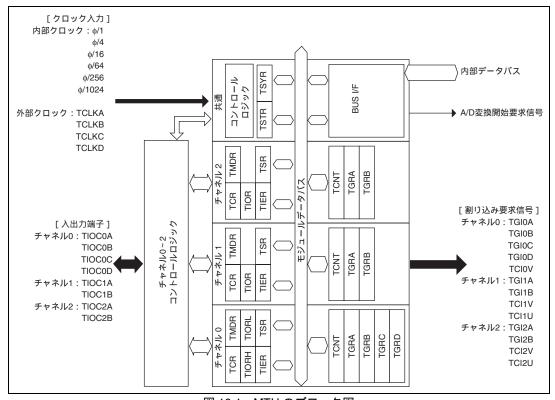

|      | 10.1.2 ブ              | ロック図                        | 10-4  |

|      | 10.1.3 端·             | 子構成                         | 10-5  |

|      | 10.1.4 レ              | ジスタ構成                       | 10-6  |

| 10.2 | レジスタの                 | 説明                          | 10-7  |

|      | 10.2.1 タ              | イマコントロールレジスタ(TCR)           | 10-7  |

|      |                       | イマモードレジスタ(TMDR)             |       |

|      |                       | イマ I/O コントロールレジスタ(TIOR)     |       |

|      | 10.2.4 タ              | イマインタラプトイネーブルレジスタ(TIER)     | 10-21 |

|      | 10.2.5 タ              | イマステータスレジスタ(TSR)            | 10-24 |

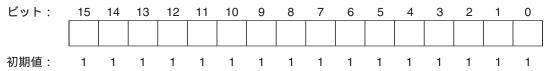

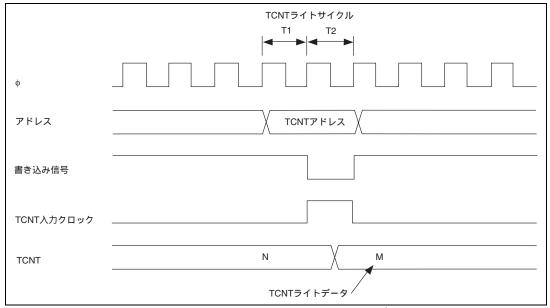

|      |                       | イマカウンタ(TCNT)                |       |

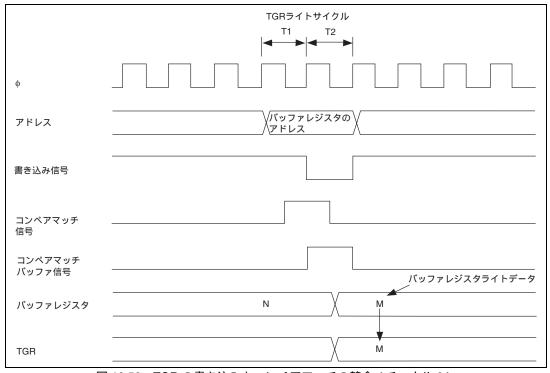

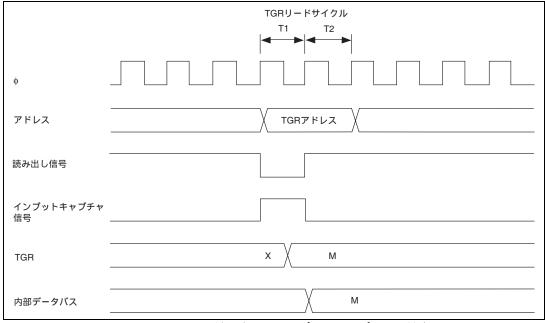

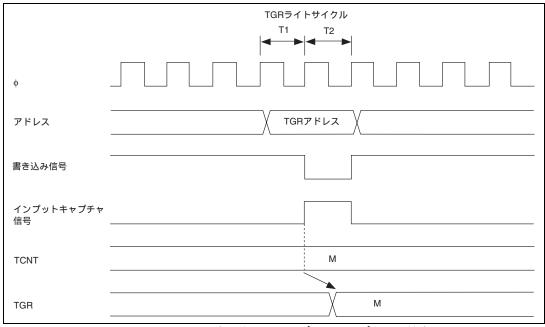

|      | 10.2.7 <b>タ</b>       | イマジェネラルレジスタ ( TGR )         | 10-27 |

|      | 10.2.8 <b>タ</b>       | イマスタートレジスタ ( TSTR )         | 10-28 |

|      | 10.2.9 <b>タ</b>       | イマシンクロレジスタ ( TSYR )         | 10-29 |

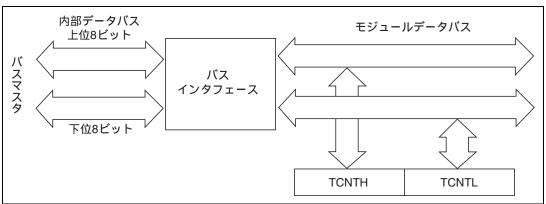

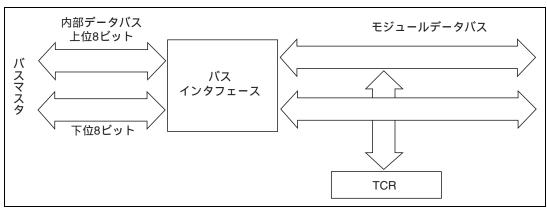

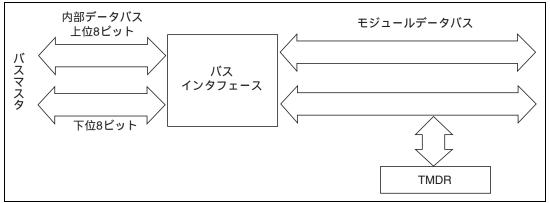

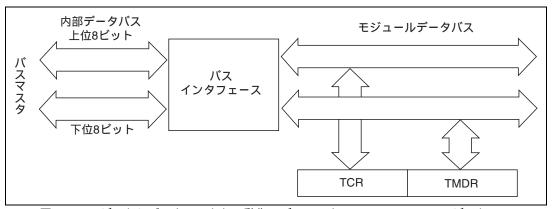

| 10.3 | バスマスタ                 | とのインタフェース                   | 10-30 |

|      | 10.3.1 16             | ビットレジスタ                     | 10-30 |

|      | 10.3.2 8 8            | ビットレジスタ                     | 10-30 |

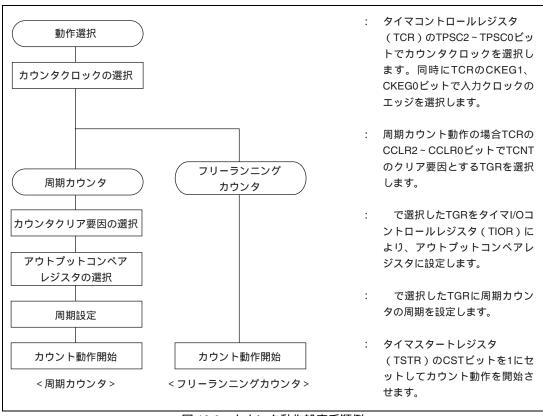

| 10.4 | 動作説明                  |                             | 10-32 |

|      | 10.4.1 概              | 要                           | 10-32 |

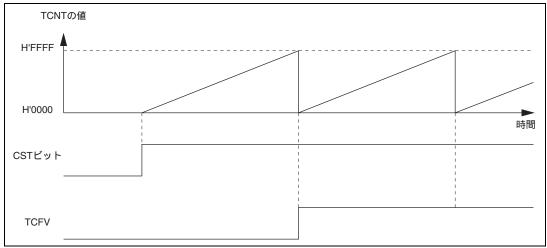

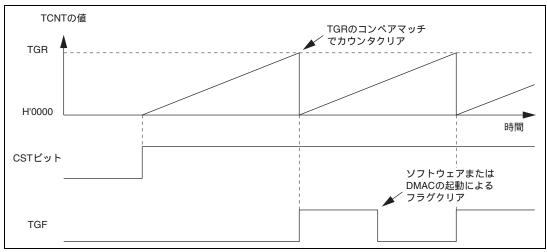

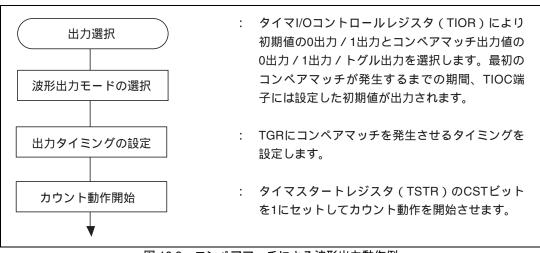

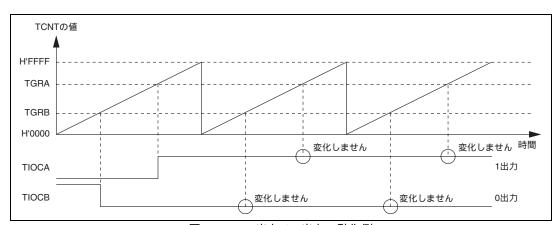

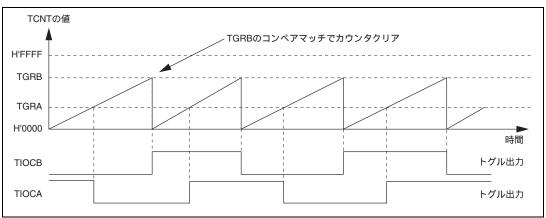

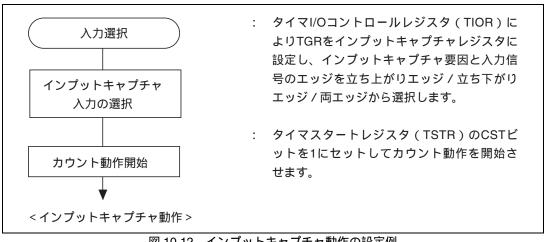

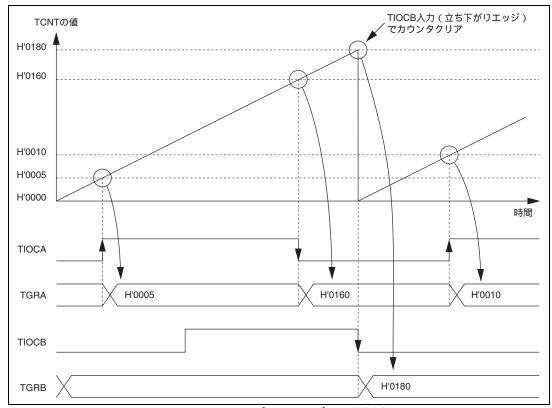

|      | 10.4.2 基:             | 本機能                         | 10-33 |

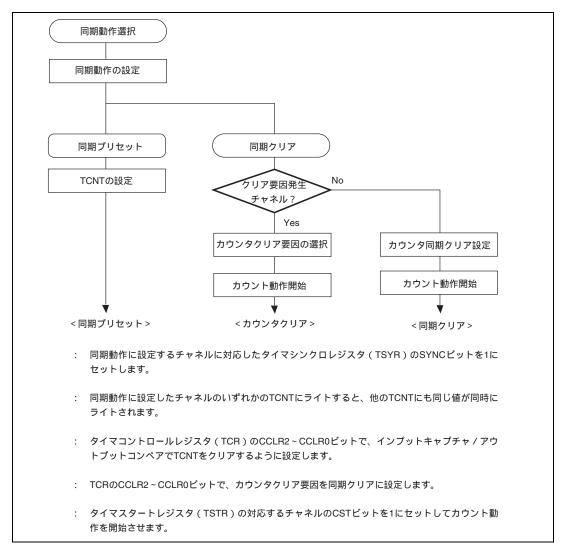

|      | 10.4.3 同              | 期動作                         | 10-39 |

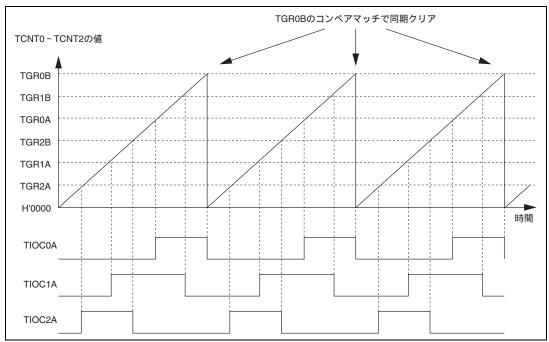

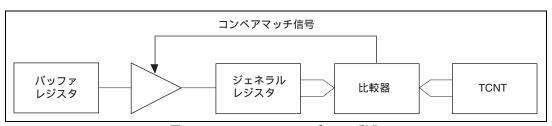

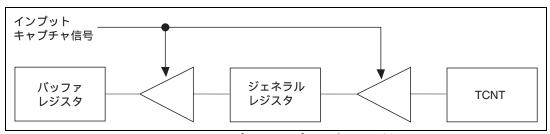

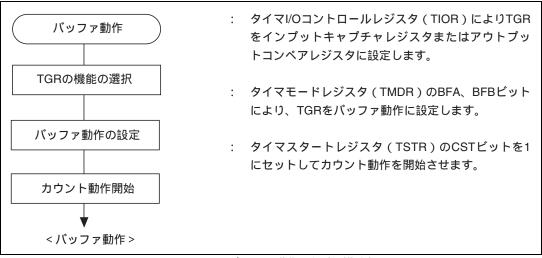

|      | 10.4.4 バ              | ッファ動作                       | 10-41 |

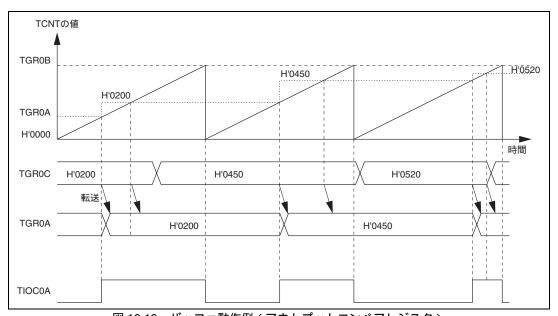

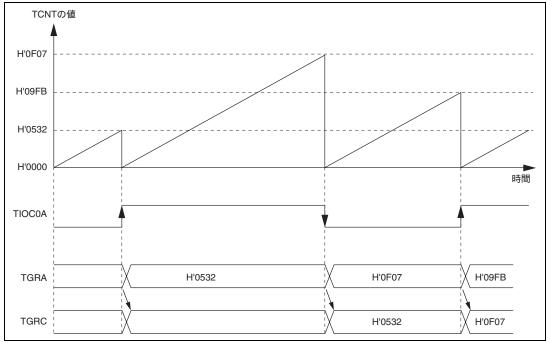

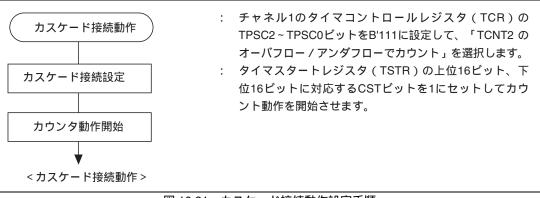

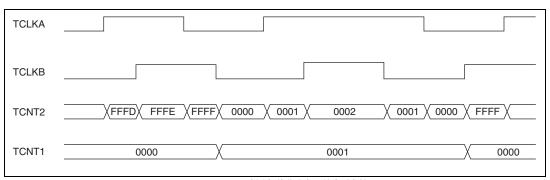

|      | 10.4.5 カ              | スケード接続動作                    | 10-45 |

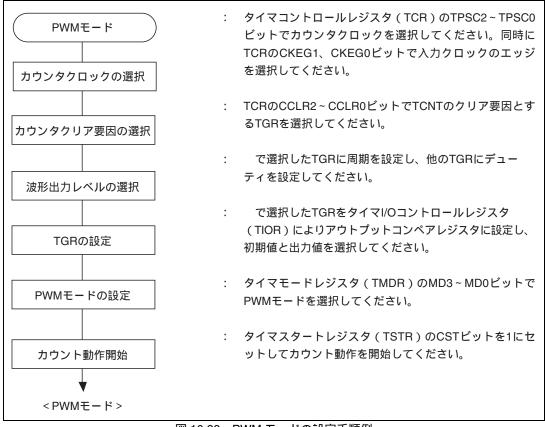

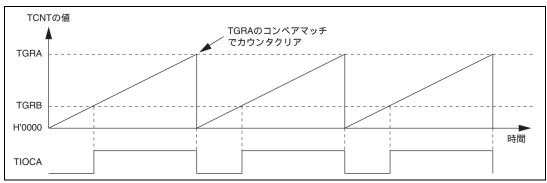

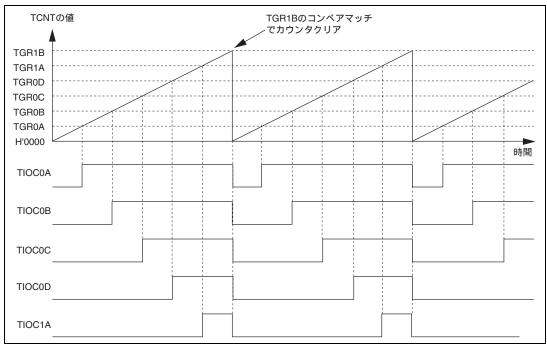

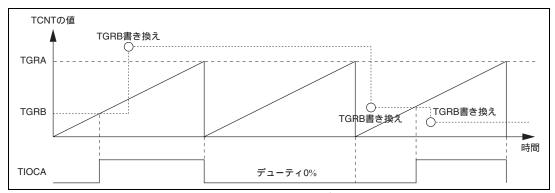

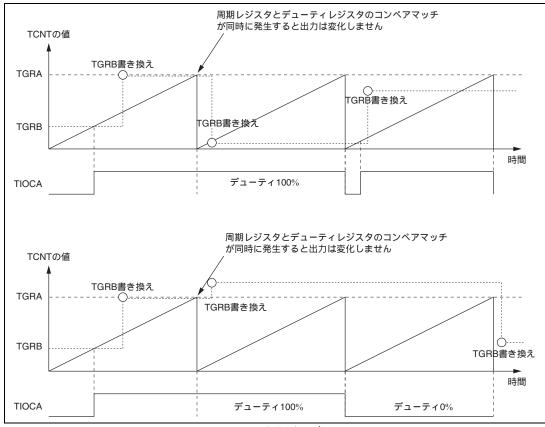

|      | 10.4.6 PW             | VM モード                      | 10-47 |

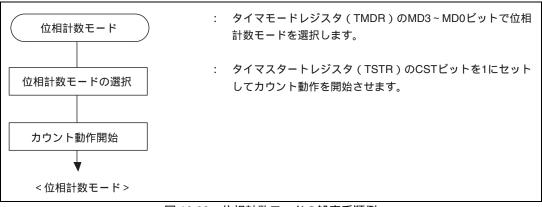

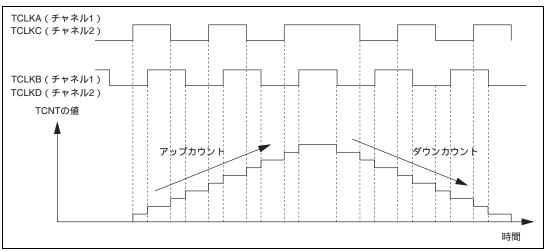

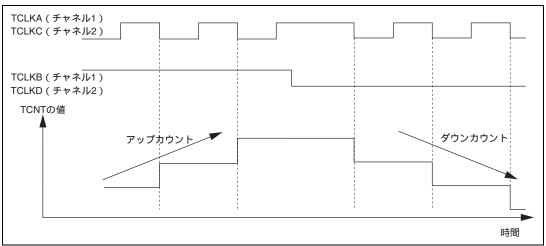

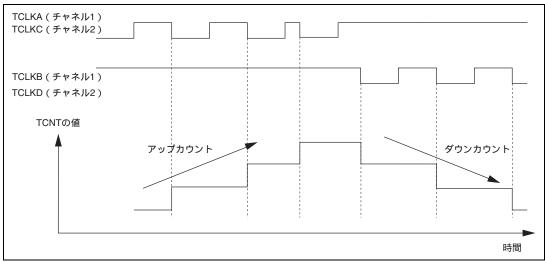

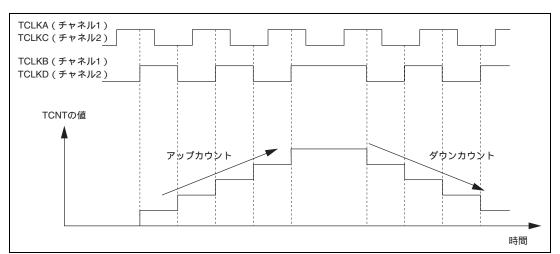

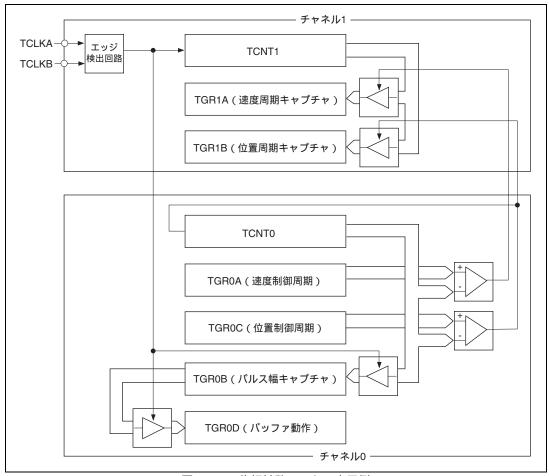

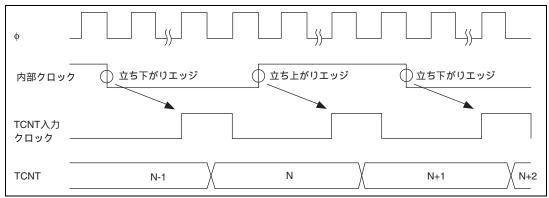

|      | 10.4.7 位2             | 相計数モード                      | 10-53 |

| 10.5 | 割り込み                  |                             | 10-59 |

|      | 10.5.1 割              | り込み要因と優先順位                  | 10-59 |

|      | 10.5.2 DN             | MA コントローラの起動                | 10-60 |

|      | 10.5.3 A/             | D 変換器の起動                    | 10-60 |

| 10.6 | 動作タイミ                 | ング                          | 10-61 |

|      | 10.6.1 入              | 出力タイミング                     | 10-61 |

|      | 10.6.2 割              | り込み信号タイミング                  | 10-66 |

| 10.7 |                       | 意                           |       |

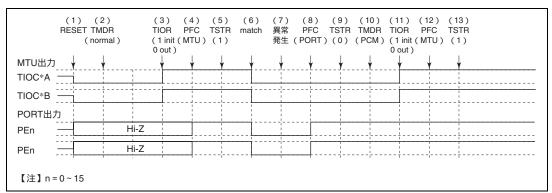

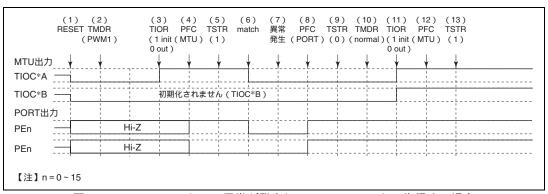

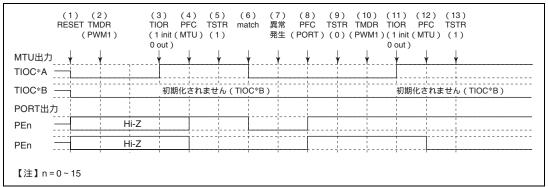

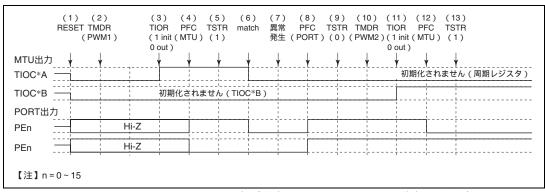

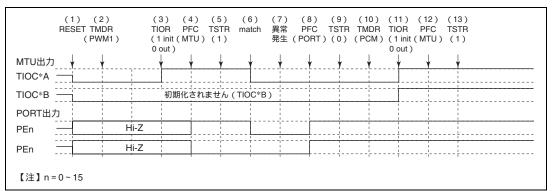

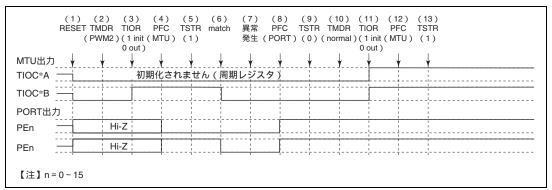

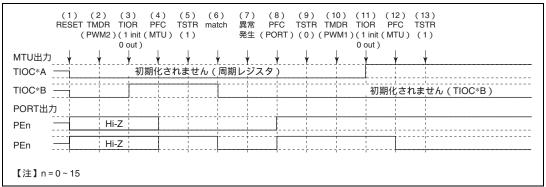

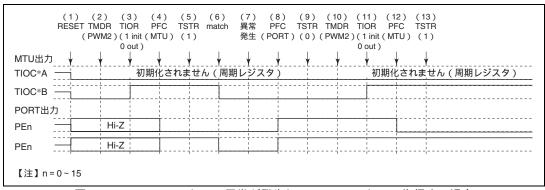

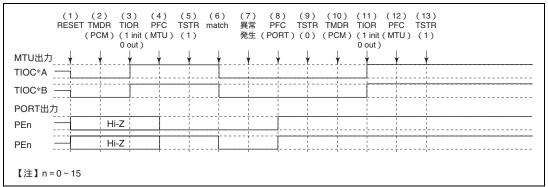

| 10.8 | MTU 出力端               | 端子の初期化方法                    | 10-81 |

|      | 10.8.1 動 <sup>4</sup> | 作モード                        | 10-81 |

|      | 10.8.2 リ              | セットスタート時の動作                 | 10-81 |

|      | 10.8.3 動              | 作中の異常などによる再設定時の動作           | 10-81 |

|      |                       | 作中の異常などによる端子の初期化手順、モード遷移の概要 |       |

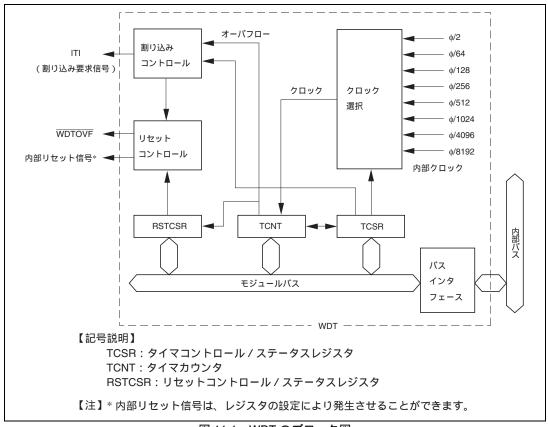

| 第 11 | 章 ウォッチ                | チドッグタイマ ( WDT )             |       |

| 11.1 | 概要                    |                             | 11-1  |

|      |                       | 長                           |       |

|      |                       | ロック図                        |       |

|      |                       |                             |       |

|      | 11.1.3       | 端子構成                                |       |

|------|--------------|-------------------------------------|-------|

| 11.0 | 11.1.4       | レジスタ構成                              |       |

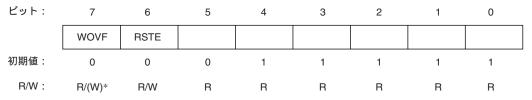

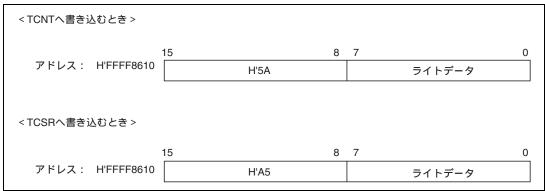

| 11.2 |              | の説明                                 |       |

|      | 11.2.1       | タイマカウンタ ( TCNT )                    |       |

|      | 11.2.2       | タイマコントロール / ステータスレジスタ ( TCSR )      |       |

|      | 11.2.3       | リセットコントロール / ステータスレジスタ (RSTCSR)     |       |

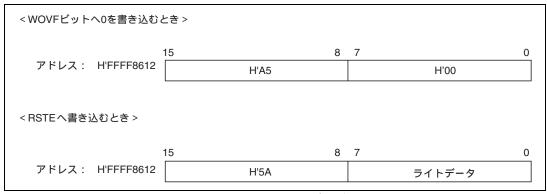

| 11.0 | 11.2.4       | _ レジスタアクセス時の注意                      |       |

| 11.3 | <b>驯作就</b> 明 |                                     |       |

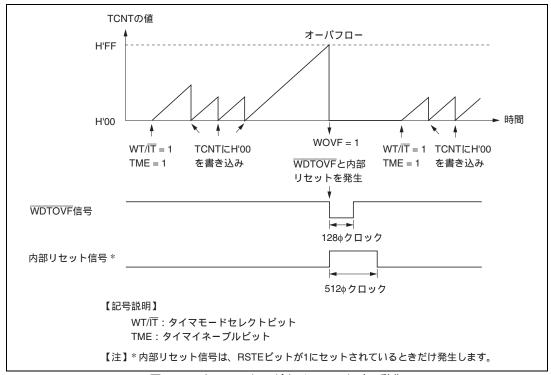

|      | 11.3.1       | ウォッチドッグタイマモード時の動作                   |       |

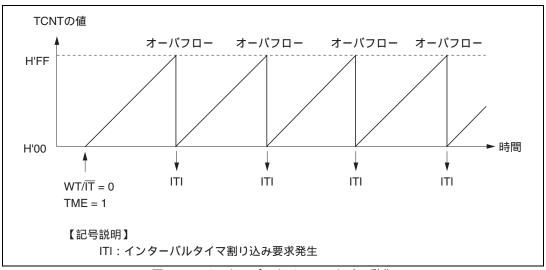

|      | 11.3.2       | インターバルタイマモード時の動作                    |       |

|      | 11.3.3       | スタンバイモード解除時の動作                      |       |

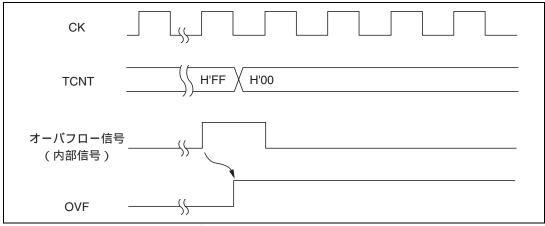

|      | 11.3.4       | オーバフローフラグ (OVF) のセットタイミング           |       |

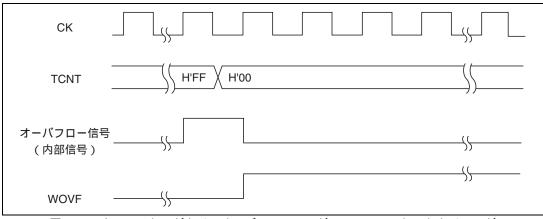

|      | 11.3.5       | ウォッチドッグタイマオーバフローフラグ (WOVF)のセットタイミング |       |

| 11.4 | 使用上の         | 注意                                  |       |

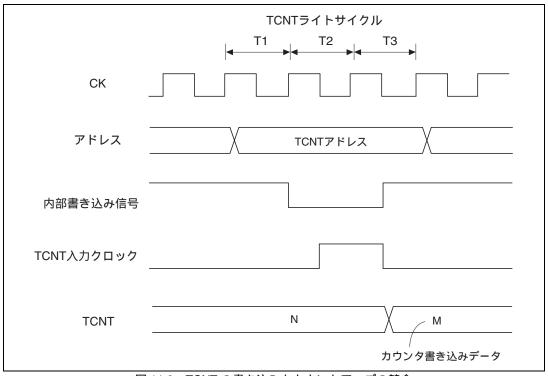

|      | 11.4.1       | タイマカウンタ ( TCNT ) の書き込みとカウントアップの競合   |       |

|      | 11.4.2       | CKS2~CKS0 ビットの書き換え                  |       |

|      | 11.4.3       | ウォッチドッグタイマモードとインターバルタイマモードの切り替え     |       |

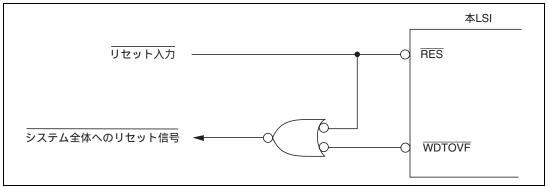

|      | 11.4.4       | WDTOVF 信号によるシステムのリセット               |       |

|      | 11.4.5       | ウォッチドッグタイマモードでの内部リセット               | 11-14 |

| 第 12 | 章 シリ         | アルコミュニケーションインタフェース(SCI)             |       |

| 12.1 | 概要           |                                     | 12-1  |

|      | 12.1.1       | 特長                                  | 12-1  |

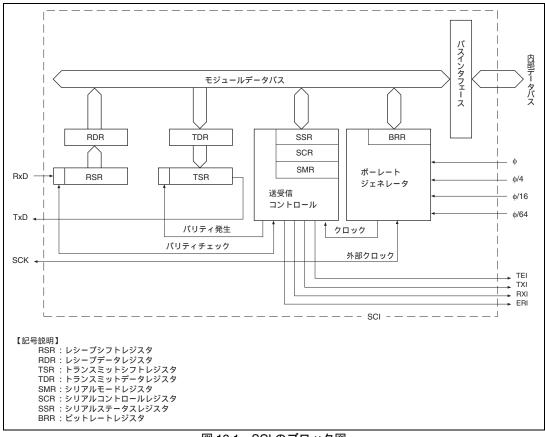

|      | 12.1.2       | ブロック図                               |       |

|      | 12.1.3       | 端子構成                                | 12-3  |

|      | 12.1.4       | レジスタ構成                              |       |

| 12.2 | レジスタ         | の説明                                 |       |

|      | 12.2.1       | レシーブシフトレジスタ ( RSR )                 | 12-4  |

|      | 12.2.2       | レシーブデータレジスタ (RDR)                   |       |

|      | 12.2.3       | トランスミットシフトレジスタ (TSR)                |       |

|      | 12.2.4       | トランスミットデータレジスタ (TDR)                | 12-5  |

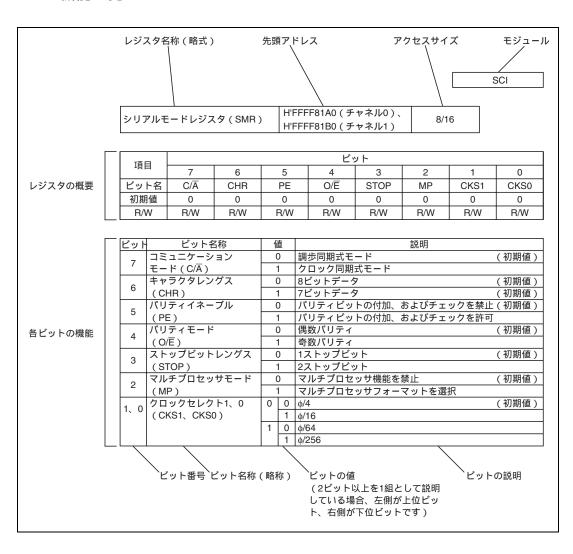

|      | 12.2.5       | シリアルモードレジスタ (SMR)                   | 12-5  |

|      | 12.2.6       | シリアルコントロールレジスタ ( SCR )              | 12-8  |

|      | 12.2.7       | シリアルステータスレジスタ (SSR)                 |       |

|      | 12.2.8       | ビットレートレジスタ(BRR)                     | 12-15 |

| 12.3 | 動作説明         |                                     | 12-25 |

|      | 12.3.1       | 概要                                  | 12-25 |

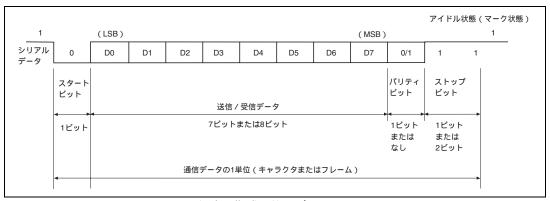

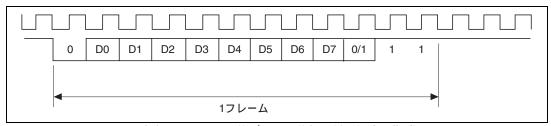

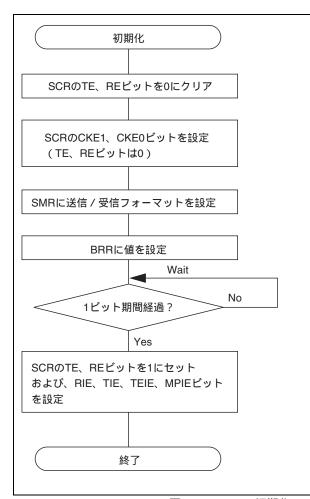

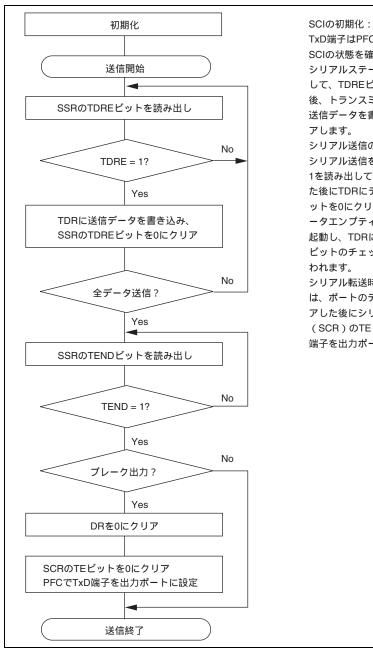

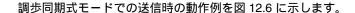

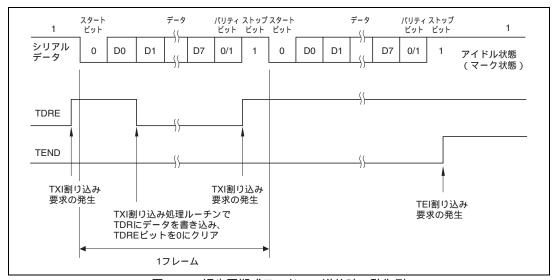

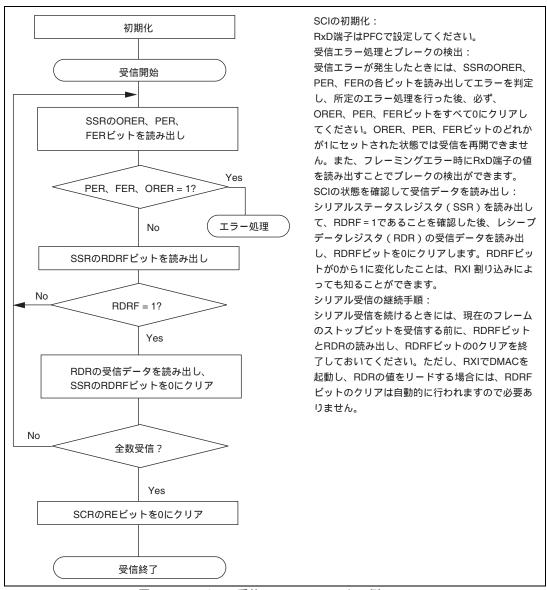

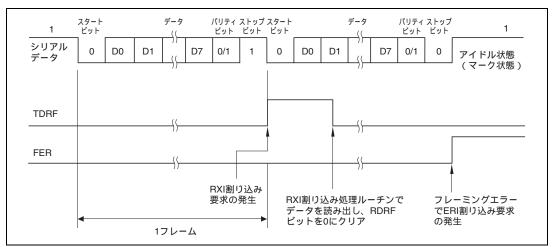

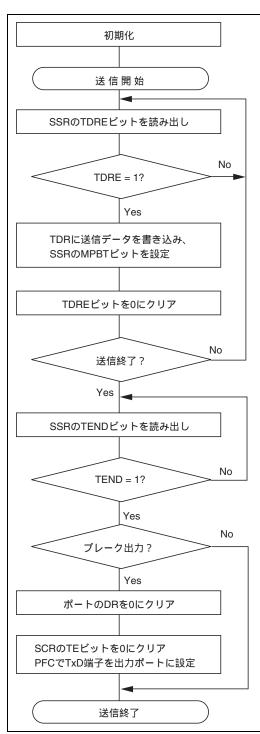

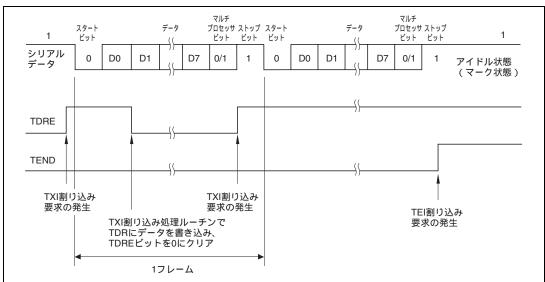

|      | 12.3.2       | 調歩同期式モード時の動作                        | 12-27 |

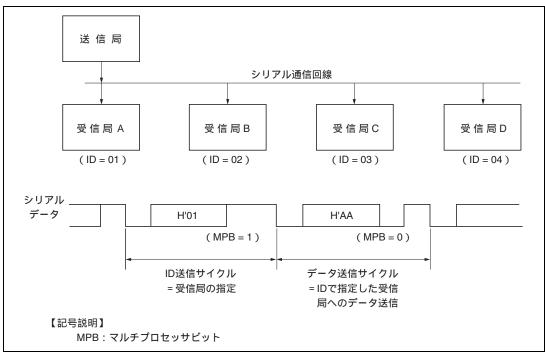

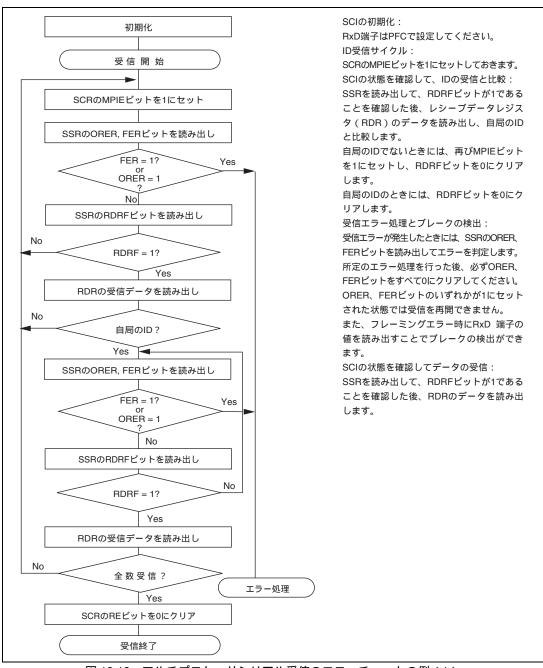

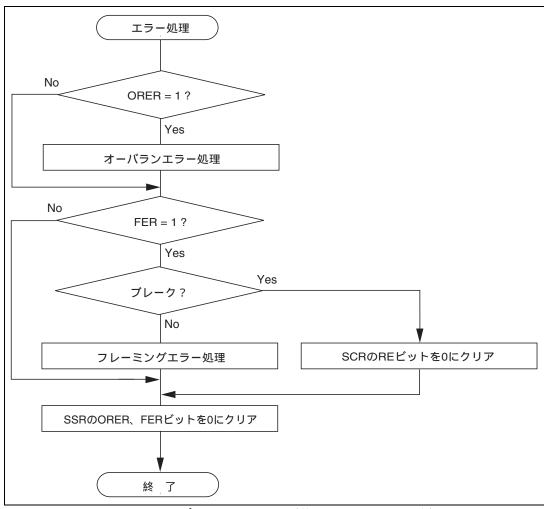

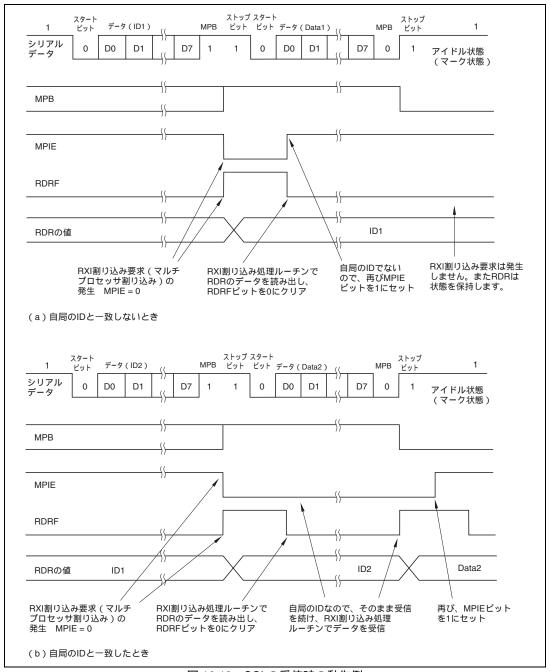

|      | 12.3.3       | マルチプロセッサ通信機能                        | 12-37 |

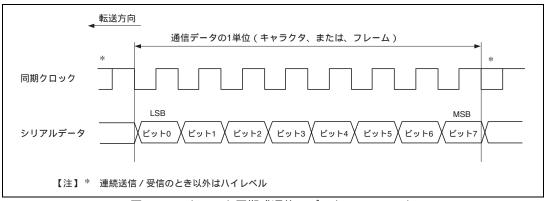

|      | 12.3.4       | クロック同期式モード時の動作                      | 12-44 |

| 12.4 | SCI の割       | り込み要因と DMAC                         | 12-52 |

| 12.5 | 使用上の         | 注意                                  | 12-53 |

| 第 13 | 章 高速         | A/D 变換器(SH7014)                     |       |

| 13.1 |              |                                     | 13-1  |

|      | 13.1.1       | 特長                                  |       |

|      | 1.1.1        | 19 IX                               | 1 2-1 |

|      | 13.1.2 | ブロック図                            | 13-2  |

|------|--------|----------------------------------|-------|

|      | 13.1.3 | 端子構成                             |       |

|      | 13.1.4 | レジスタ構成                           |       |

| 13.2 | レジス    | タの説明                             |       |

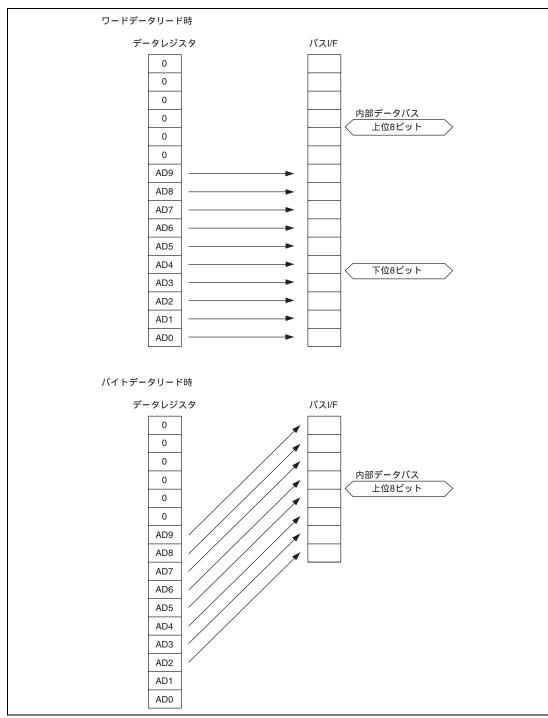

|      | 13.2.1 | A/D データレジスタ A~H(ADDRA~ADDRH)     |       |

|      | 13.2.2 | A/D コントロール / ステータスレジスタ ( ADCSR ) |       |

|      | 13.2.3 | A/D コントロールレジスタ ( ADCR )          |       |

| 13.3 |        | スタとのインタフェース                      |       |

| 13.4 | 動作説    | 明                                | 13-11 |

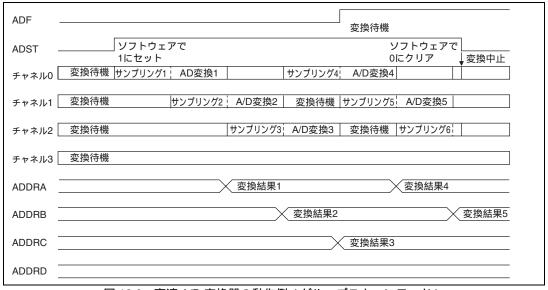

|      | 13.4.1 | セレクトシングルモード                      |       |

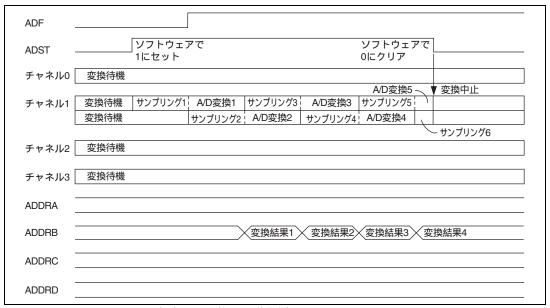

|      | 13.4.2 | セレクトスキャンモード                      |       |

|      | 13.4.3 | グループシングルモード                      |       |

|      | 13.4.4 | グループスキャンモード                      |       |

|      | 13.4.5 | バッファ動作                           |       |

|      | 13.4.6 | 同時サンプリング動作                       |       |

|      | 13.4.7 | 変換開始モード                          |       |

| 12.5 | 13.4.8 | A/D 変換時間                         |       |

| 13.5 |        | み                                |       |

| 13.6 |        | の注意                              | 13-22 |

| 第 14 |        | 速 A/D 変換器(SH7016/17)             |       |

| 14.1 | 概要     |                                  | 14-1  |

|      | 14.1.1 | 特長                               | 14-1  |

|      | 14.1.2 | ブロック図                            | 14-2  |

|      | 14.1.3 | 端子構成                             |       |

|      | 14.1.4 | レジスタ構成                           |       |

| 14.2 | レジス    | タの説明                             |       |

|      | 14.2.1 | A/D データレジスタ A~D ( ADDRA~ADDRD )  |       |

|      | 14.2.2 | A/D コントロール / ステータスレジスタ ( ADCSR ) |       |

|      | 14.2.3 | A/D コントロールレジスタ ( ADCR )          |       |

| 14.3 | CPU と  | のインタフェース                         | 14-8  |

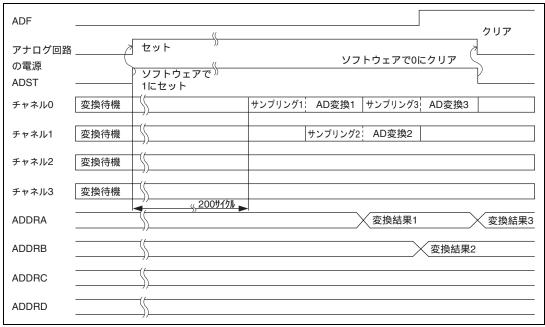

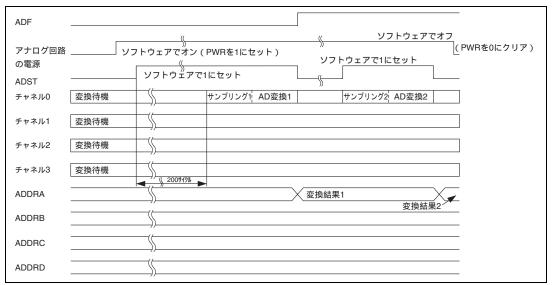

| 14.4 | 動作説    | 明                                | 14-9  |

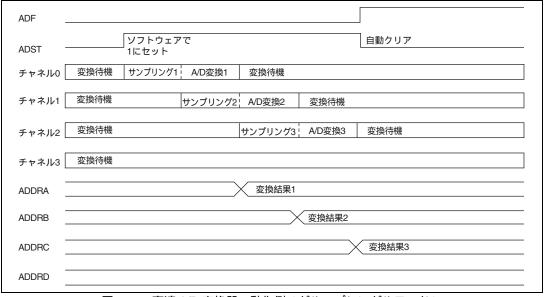

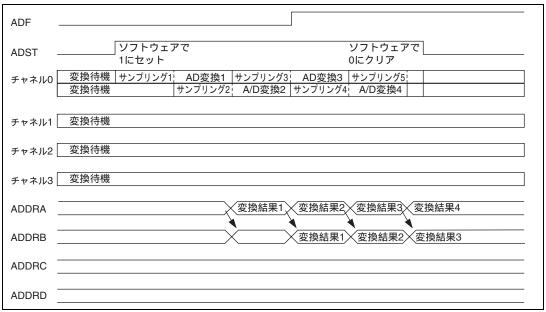

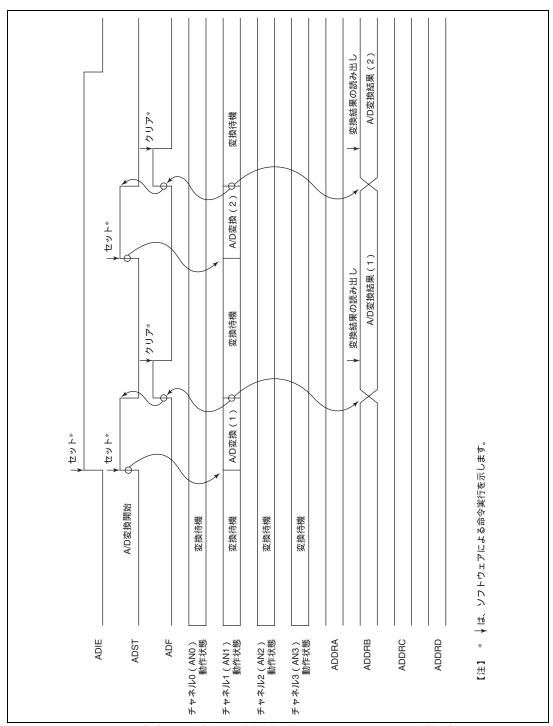

|      | 14.4.1 | 単一モード (SCAN=0)                   | 14-9  |

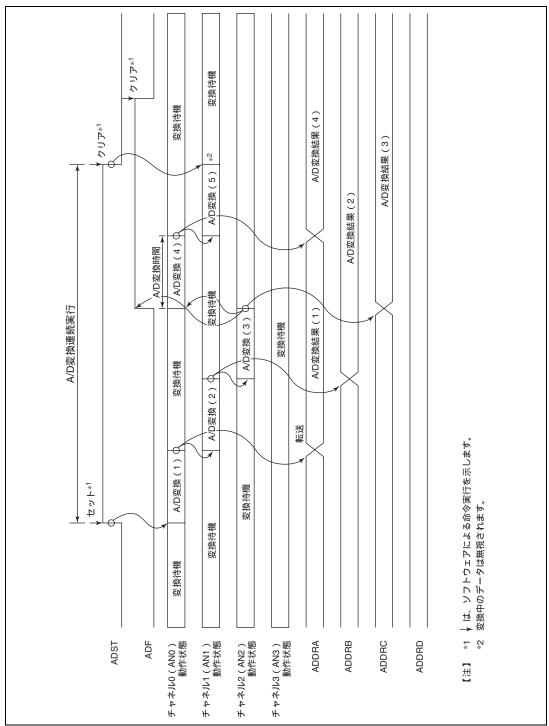

|      | 14.4.2 | スキャンモード ( SCAN = 1 )             |       |

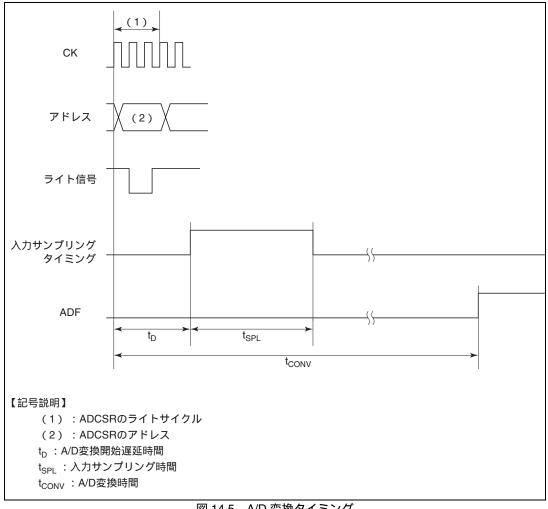

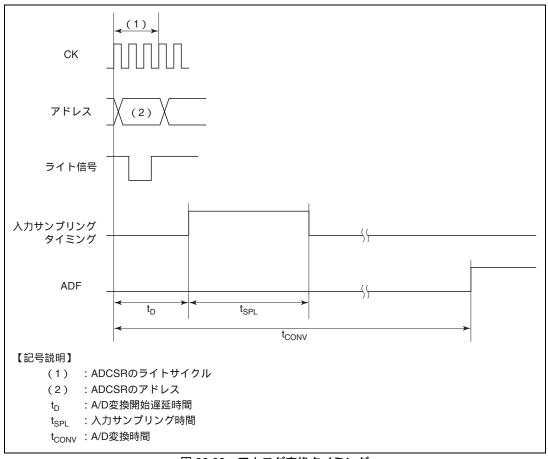

|      | 14.4.3 | 入力サンプリングと A/D 変換時間               | 14-13 |

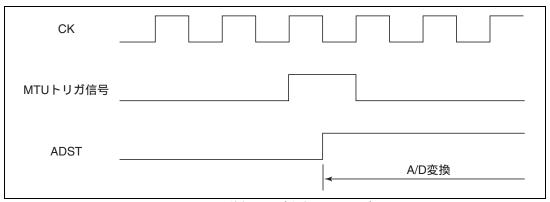

|      | 14.4.4 | MTU トリガ入力タイミング                   | 14-14 |

| 14.5 |        | み                                |       |

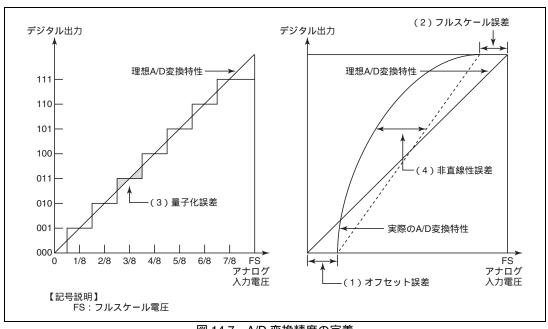

| 14.6 | A/D 変  | 換精度の定義                           | 14-15 |

| 14.7 | 使用上    | の注意                              | 14-16 |

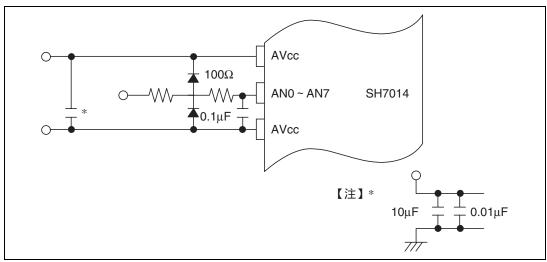

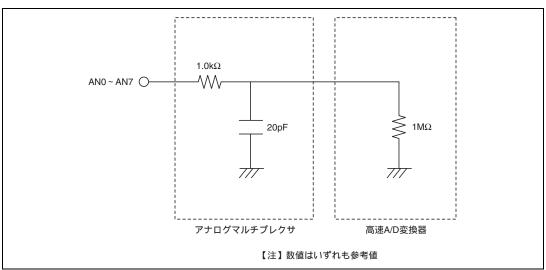

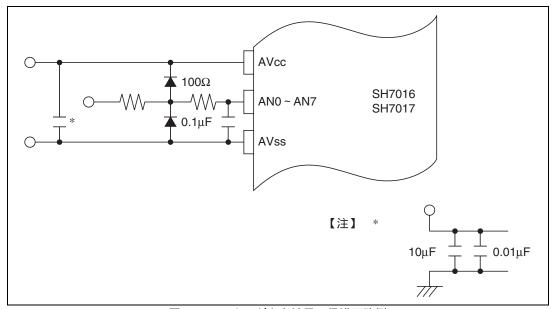

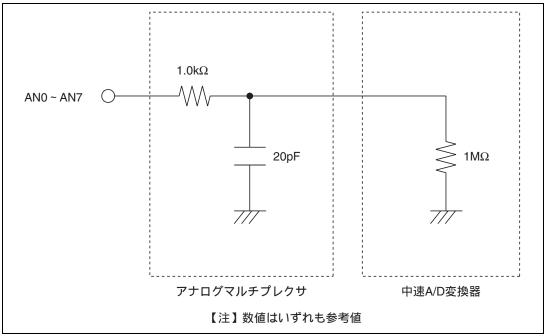

|      | 14.7.1 | アナログ電圧の設定                        | 14-16 |

|      |        | アナログ入力端子の取り扱い                    |       |

| 第 15 | 章コン    | ンペアマッチタイマ(CMT)                   |       |

| 15.1 |        |                                  | 15-1  |

|      | 15.1.1 | 特長                               |       |

|      |        |                                  |       |

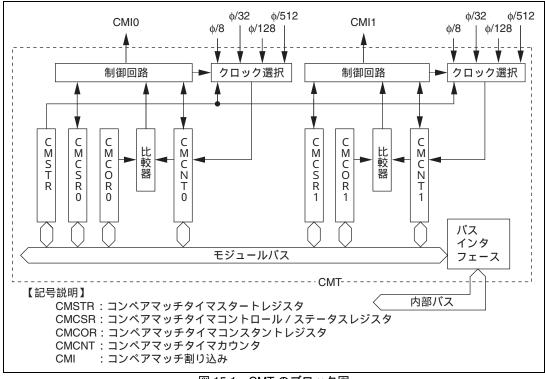

|        | 15.1.2  | ブロック図                                           | 15-2  |

|--------|---------|-------------------------------------------------|-------|

|        | 15.1.3  | レジスタ構成                                          | 15-3  |

| 15.2   | レジスタ    | 7の説明                                            | 15-4  |

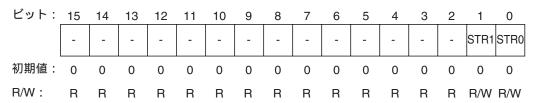

|        | 15.2.1  | コンペアマッチタイマスタートレジスタ ( CMSTR )                    | 15-4  |

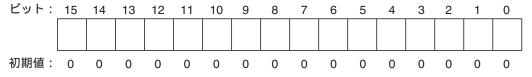

|        | 15.2.2  | コンペアマッチタイマコントロール / ステータスレジスタ (CMCSR)            | 15-5  |

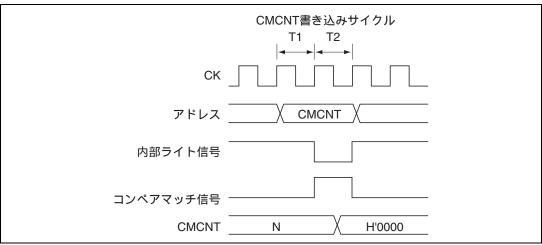

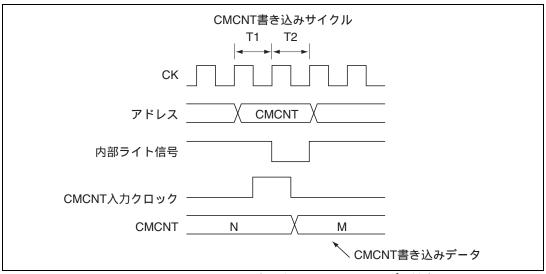

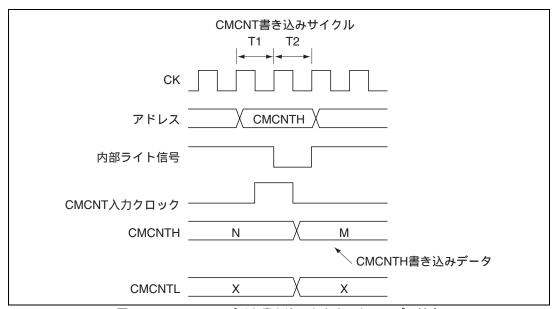

|        | 15.2.3  | コンペアマッチタイマカウンタ ( CMCNT )                        |       |

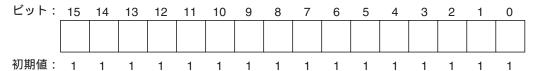

|        | 15.2.4  | コンペアマッチタイマコンスタントレジスタ ( CMCOR )                  |       |

| 15.3   | 動作説明    | <b>1</b>                                        |       |

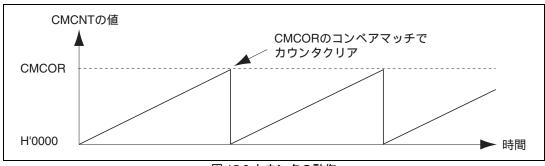

|        | 15.3.1  | 周期カウント動作                                        |       |

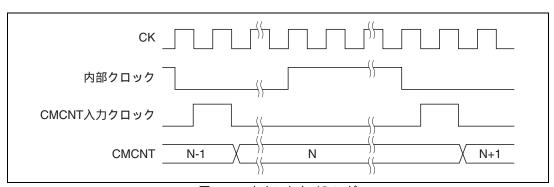

|        | 15.3.2  | CMCNT のカウントタイミング                                |       |

| 15.4   | 割り込み    | <del>}</del>                                    |       |

|        | 15.4.1  | 割り込み要因                                          |       |

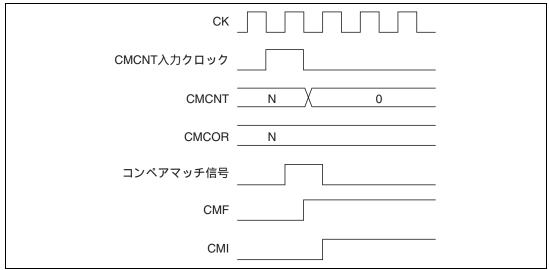

|        | 15.4.2  | コンペアマッチフラグのセットタイミング                             |       |

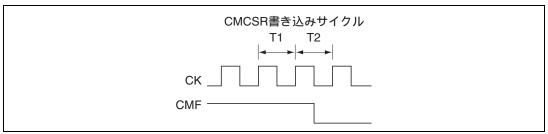

|        | 15.4.3  | コンペアマッチフラグのクリアタイミング                             |       |

| 15.5   |         | )注意                                             | 15-10 |

| 第 16   | 章 ピン    | ファンクションコントローラ ( PFC )                           |       |

| 16.1   | 概要      |                                                 | 16-1  |

| 16.2   | レジスタ    | ヲ構成                                             | 16-10 |

| 16.3   | レジスタ    | 7の説明                                            | 16-11 |

|        | 16.3.1  | ポート A・IO レジスタ L ( PAIORL )                      | 16-11 |

|        | 16.3.2  | ポート A コントロールレジスタ L1、L2 ( PACRL1、PACRL2 )        | 16-11 |

|        | 16.3.3  | ポート B・IO レジスタ ( PBIOR )                         |       |

|        | 16.3.4  | ポート B コントロールレジスタ 1、2 (PBCR1、PBCR2)              |       |

|        | 16.3.5  | ポート C・IO レジスタ ( PCIOR ) - SH7016、SH7017 のみ      |       |

|        | 16.3.6  | ポート C コントロールレジスタ (PCCR) - SH7016、SH7017 のみ      |       |

|        | 16.3.7  | ポート D・IO レジスタ L (PDIORL) - SH7016、SH7017 のみ     |       |

|        | 16.3.8  | ポート D コントロールレジスタ L ( PDCRL ) - SH7016、SH7017 のみ |       |

|        | 16.3.9  | ポートE・IO レジスタ (PEIOR)                            |       |

| ~~ · _ | 16.3.10 | ポート E コントロールレジスタ 1、2(PECR1、PECR2)               | 10-30 |

|        |         | <b>代− ト ( I/O )</b>                             |       |

| 17.1   |         |                                                 |       |

| 17.2   | ポート     | <i>1</i>                                        | 17-2  |

|        | 17.2.1  | レジスタ構成                                          |       |

|        | 17.2.2  | ポート A データレジスタ L ( PADRL )                       | 17-3  |

| 17.3   | ポートI    | 3                                               | 17-4  |

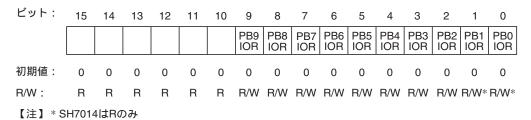

|        | 17.3.1  | レジスタ構成                                          | 17-5  |

|        | 17.3.2  | ポート B データレジスタ (PBDR)                            | 17-5  |

| 17.4   | ポート(    | C SH7016、SH7017 のみ                              | 17-6  |

|        | 17.4.1  | レジスタ構成                                          | 17-6  |

|        | 17.4.2  | ポート C データレジスタ ( PCDR )                          | 17-7  |

| 17.5   | ポートI    | O SH7016、SH7017 のみ                              | 17-8  |

|        | 17.5.1  | レジスタ構成                                          | 17-8  |

|        | 17.5.2  | ポート D データレジスタ L ( PDDRL )                       | 17-9  |

| 17.6  | ポート E              | 3                                             | 17-10 |

|-------|--------------------|-----------------------------------------------|-------|

|       | 17.6.1             | レジスタ構成                                        | 17-10 |

|       | 17.6.2             | ポート E データレジスタ ( PEDR )                        | 17-11 |

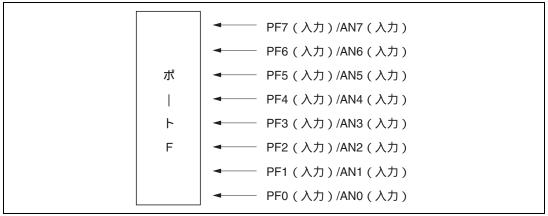

| 17.7  |                    | 3                                             |       |

|       | 17.7.1             | レジスタ構成                                        |       |

|       | 17.7.2             | ポート F データレジスタ(PFDR)                           | 17-12 |

| 第 18  | 章 128년             | 〈B フラッシュメモリ(F-ZTAT)                           |       |

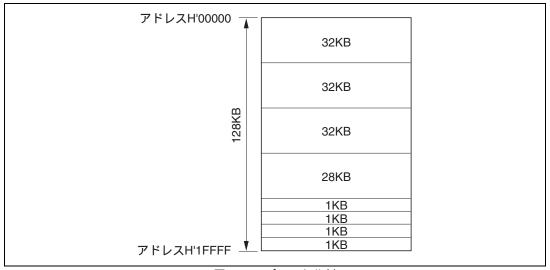

| 18.1  | 特長                 |                                               | 18-1  |

| 18.2  | 概要                 |                                               | 18-2  |

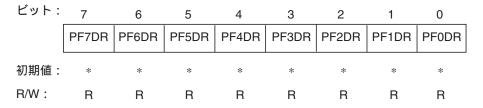

|       | 18.2.1             | ブロック図                                         | 18-2  |

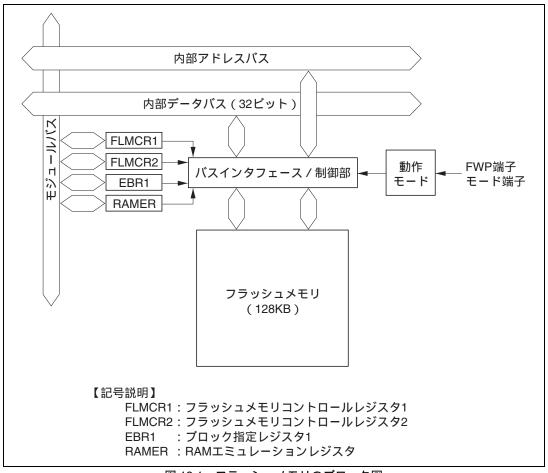

|       | 18.2.2             | モード遷移図                                        |       |

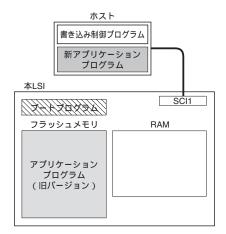

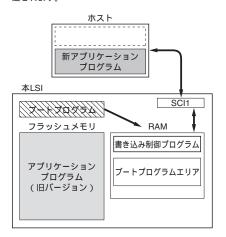

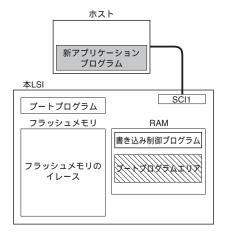

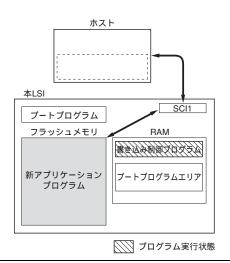

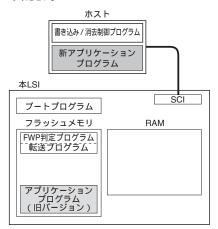

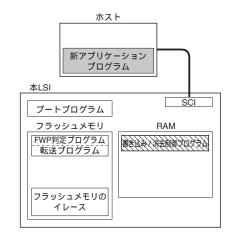

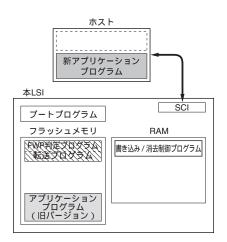

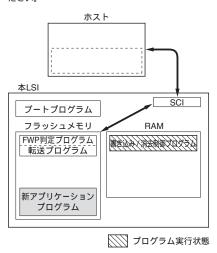

|       | 18.2.3             | オンボードプログラムモード                                 | 18-4  |

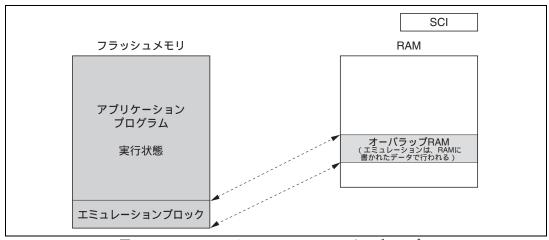

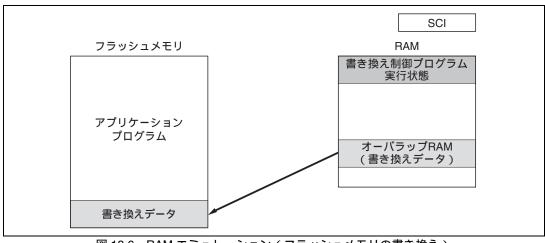

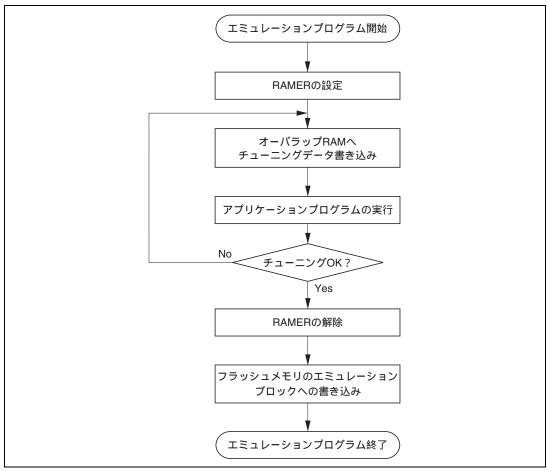

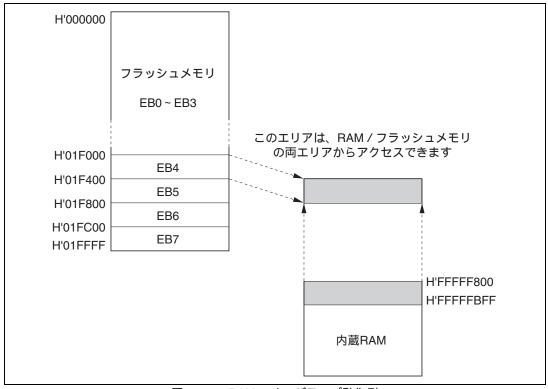

|       | 18.2.4             | RAM によるフラッシュメモリのエミュレーション                      |       |

|       | 18.2.5             | ブートモードとユーザプログラムモードの相違                         |       |

| 10.2  | 18.2.6             | _ ブロック分割法<br><del>t</del>                     |       |

| 18.3  |                    | 艾                                             |       |

| 18.4  |                    | ヲ構成                                           |       |

| 18.5  | レジスタ               | 7の説明                                          |       |

|       | 18.5.1             | フラッシュメモリコントロールレジスタ 1 (FLMCR1)                 |       |

|       | 18.5.2             | フラッシュメモリコントロールレジスタ 2 (FLMCR2)                 |       |

|       | 18.5.3<br>18.5.4   | ブロック指定レジスタ 1(EBR1)<br>RAM エミュレーションレジスタ(RAMER) |       |

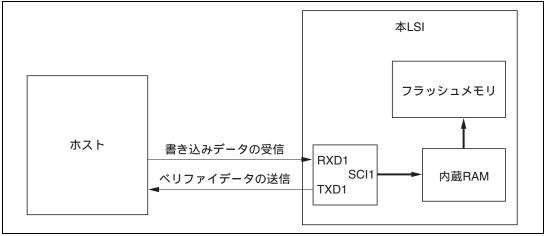

| 18.6  |                    | - ドプログラミングモード                                 |       |

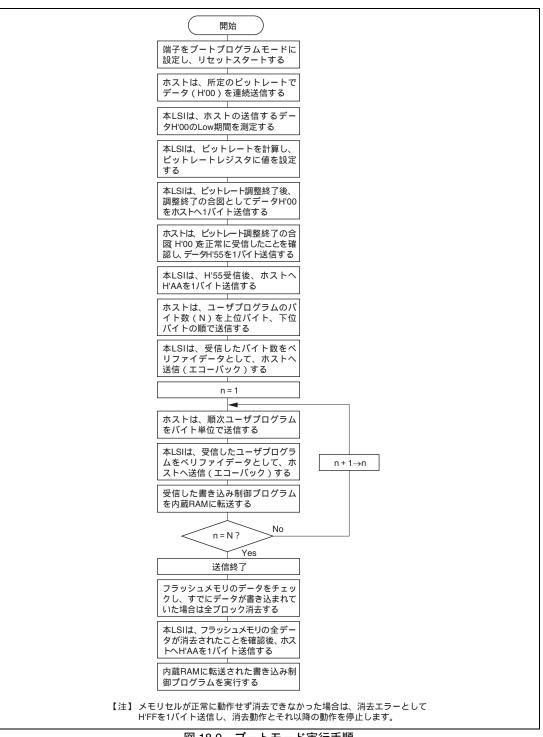

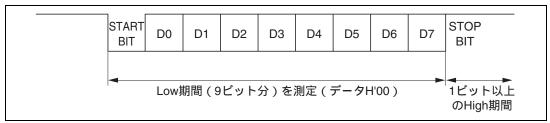

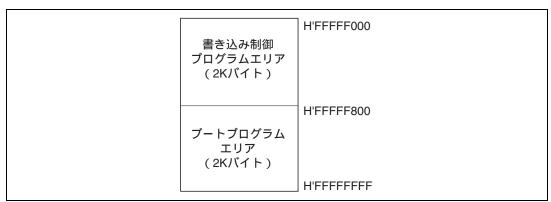

| 10.0  | 18.6.1             |                                               |       |

|       | 18.6.2             | ユーザプログラムモード                                   |       |

| 18.7  |                    | /ュメモリの書き込み / 消去                               |       |

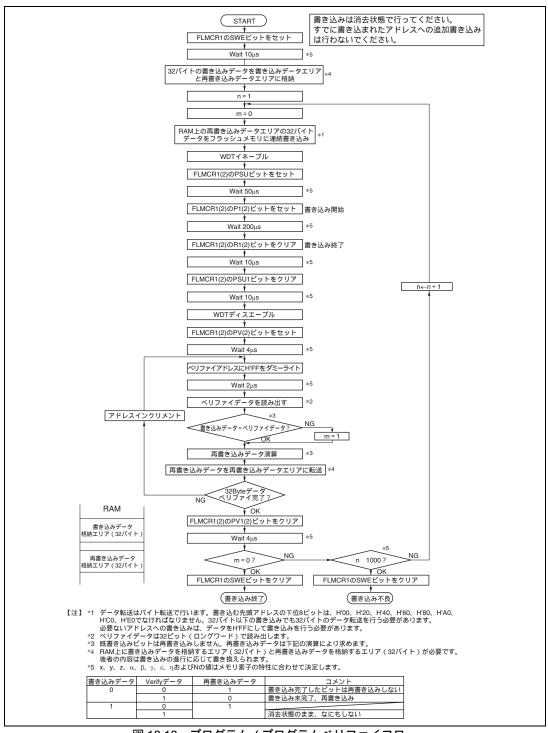

|       | 18.7.1             | プログラムモード                                      |       |

|       | 18.7.2             | プログラムベリファイモード                                 |       |

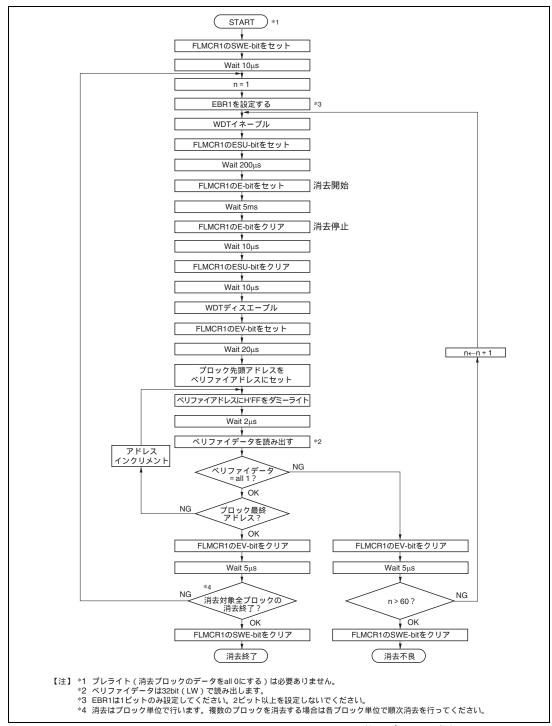

|       | 18.7.3             | イレースモード                                       |       |

|       | 18.7.4             | イレースベリファイモード                                  |       |

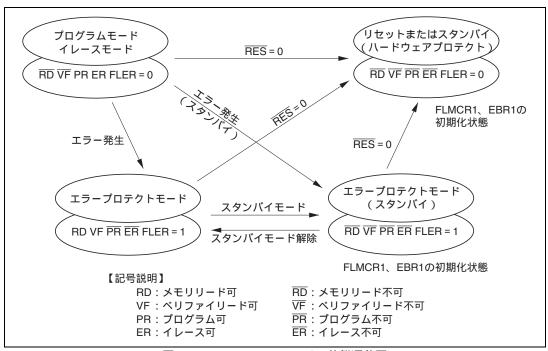

| 18.8  | プロテク               | 7 <b>-</b>                                    | 18-34 |

|       | 18.8.1             | ハードウェアプロテクト                                   |       |

|       | 18.8.2             | ソフトウェアプロテクト                                   |       |

|       | 18.8.3             | エラープロテクト                                      |       |

|       |                    | よるフラッシュメモリのエミュレーション                           |       |

| 18.10 |                    | ノュメモリの書き込み/消去時の注意                             |       |

| 18.11 | フラッシ               | ノュメモリのライタモード                                  |       |

|       | 18.11.1            | ソケットアダプタの端子対応図                                |       |

|       | 18.11.2            | ライタモードの動作                                     |       |

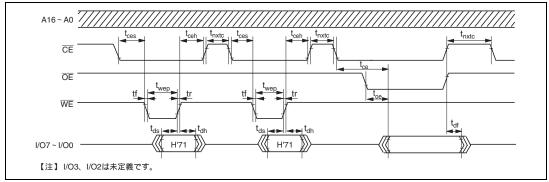

|       | 18.11.3            | メモリ読み出しモード                                    |       |

|       | 18.11.4<br>18.11.5 | 自動書き込みモード<br>自動消去モード                          |       |

|       | 18.11.5            |                                               |       |

|       | 10.11.0            | 77 77 MIO C 1                                 | 10-4/ |

|      | 18.11.7 ステータスポーリング                      |        |

|------|-----------------------------------------|--------|

|      | 18.11.8 ライタモードへの遷移時間                    |        |

|      | 18.11.9 メモリ書き込み注意事項                     | 18-49  |

| 第 19 | )章 マスク ROM                              |        |

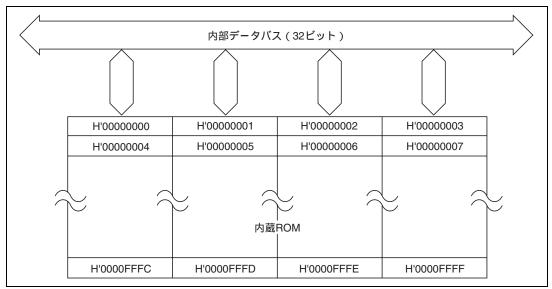

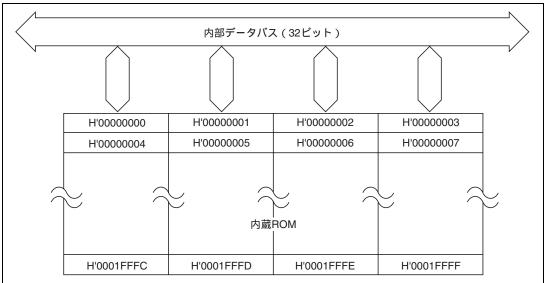

| 19.1 | 概要                                      | 19-1   |

| 第 20 | )章 RAM                                  |        |

| 20.1 | 概要                                      | 20-1   |

|      | 章 低消費電力状態                               |        |

| 21.1 | 概要                                      | 21_1   |

| 21.1 | 21.1.1 低消費電力状態の種類                       |        |

|      | 21.1.2 関連レジスタ                           |        |

| 21.2 | スタンパイコントロールレジスタ (SBYCR)                 |        |

| 21.3 | スリープモード                                 |        |

| 21.3 | 21.3.1 スリープモードへの遷移                      |        |

|      | 21.3.2 スリープモードへの遺移                      |        |

| 21.4 | スタンバイモード                                |        |

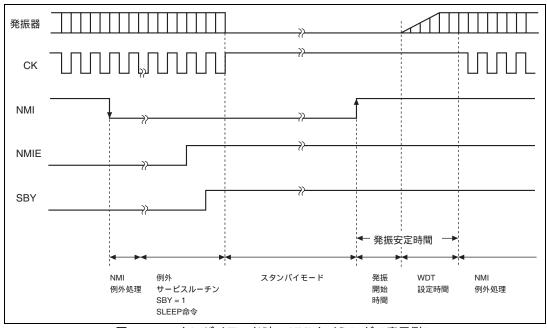

| 21   | 21.4.1 スタンバイモードへの遷移                     |        |

|      | 21.4.2 スタンバイモードの解除                      |        |

|      | 21.4.3 スタンパイモードの応用例                     |        |

| 笙 22 | 2 章 電気的特性【5V 28.7MHz 版】                 |        |

| 22.1 | - 单 - 电                                 | 22_1   |

| 22.2 | DC 特性                                   |        |

|      |                                         |        |

| 22.3 | AC 特性                                   |        |

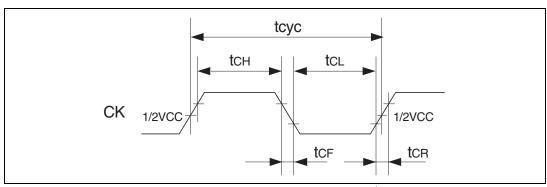

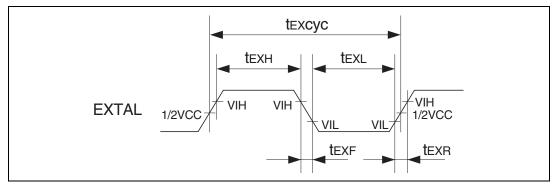

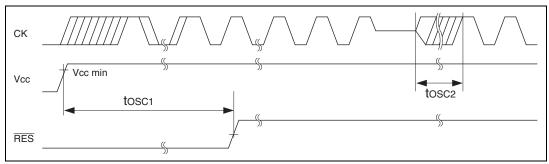

|      | 22.3.1 クロックタイミング                        |        |

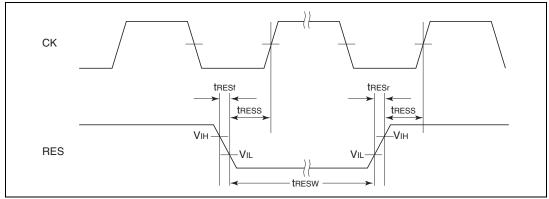

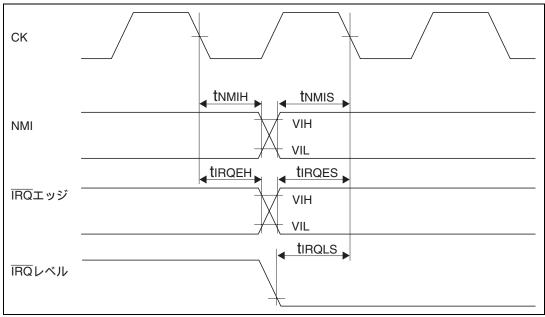

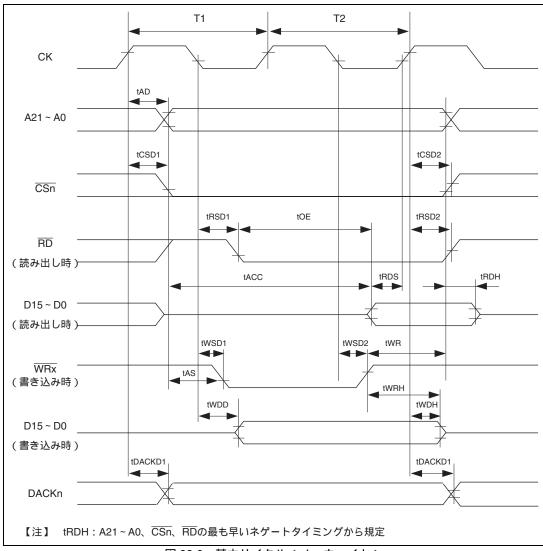

|      | 22.3.2   制御信号タイミング     22.3.3   バスタイミング |        |

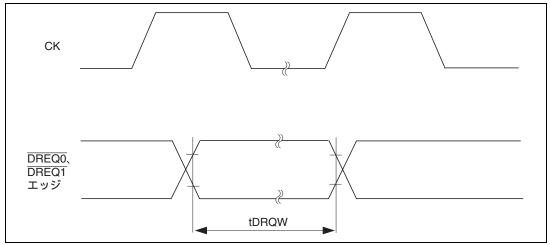

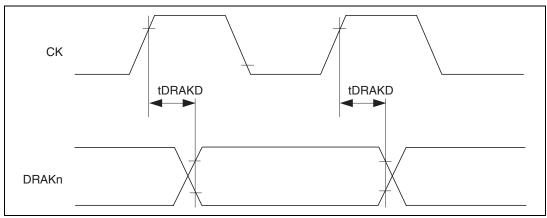

|      | 22.3.4 ダイレクトメモリアクセスコントローラタイミング          |        |

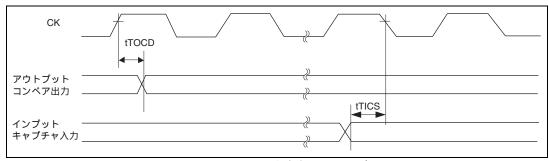

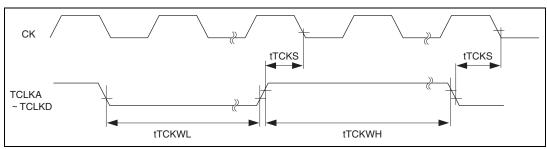

|      | 22.3.5 マルチファンクションタイマパルスユニットタイミンク        |        |

|      | 22.3.6 I/O ポートタイミング                     |        |

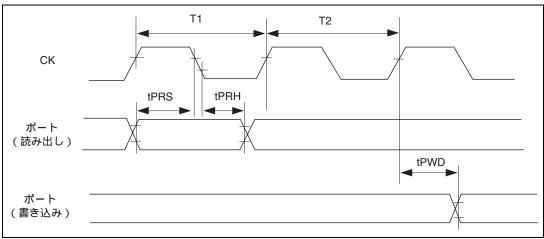

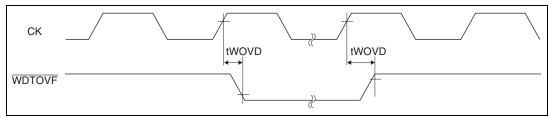

|      | 22.3.7 ウォッチドッグタイマタイミング                  | 22-24  |

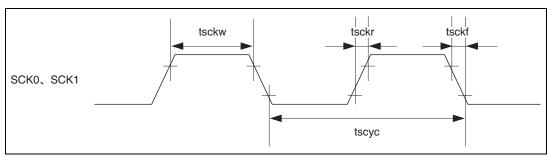

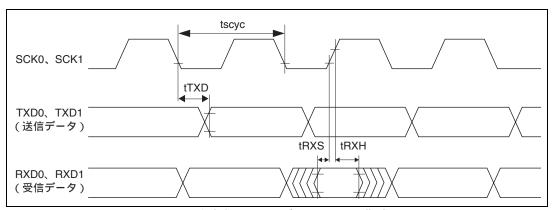

|      | 22.3.8 シリアルコミュニケーションインタフェースタイミング        |        |

|      | 22.3.9 高速 A/D 変換器タイミング (SH7014)         |        |

|      | 22.3.10 中速 A/D 変換器タイミング (SH7016/17)     |        |

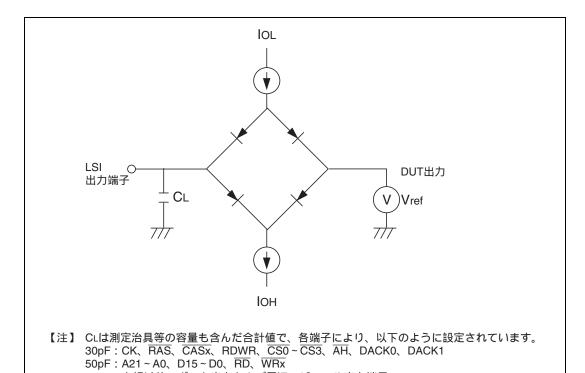

| /    | 22.3.11 AC 特性測定条件                       |        |

| 22.4 | A/D 变换器特性                               | 22-29  |

| 付録   |                                         |        |

| A.   | 内蔵周辺モジュールレジスタ                           | 付録-1   |

|      | A.1 アドレス一覧                              |        |

|      | A.2 機能一覧                                |        |

| B.   | I/O ポートブロック図                            |        |

| C.   | 端子状態                                    | 付録-116 |

|      | C.1 端子状態                                | 付録-116 |

|    | C.2    | バス関連信号の端子状態                 | 付録-117 |

|----|--------|-----------------------------|--------|

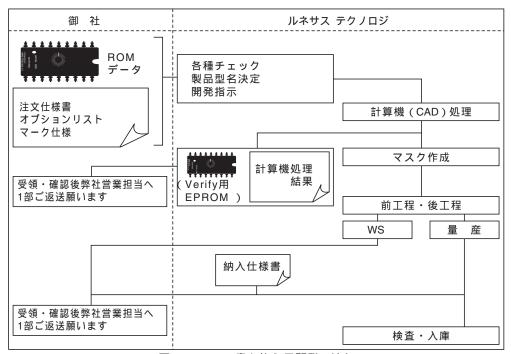

| D. | ROM 発泡 | 主手順                         | 付録-121 |

|    | D.1    | ROM 書き換え品開発の流れ(発注手順)        | 付録-121 |

|    | D.2    | ROM 発注時の注意事項                | 付録-122 |

|    | D.3    | F-ZTAT マイコンのマスク ROM 化時の注意事項 | 付録-122 |

| E. | 型名一覧   |                             | 付録-123 |

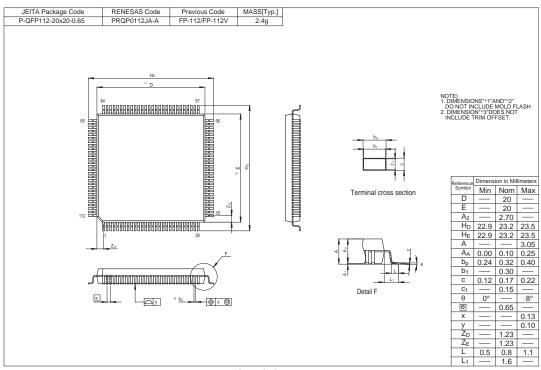

| F. | 外形寸法   | 図                           | 付録-124 |

|    |        |                             |        |

# 1. 概要

### 1.1 SH7014/16/17 の特長

本 LSI は、ルネサス テクノロジオリジナル・アーキテクチャを採用した高速 CPU を核にして、システム構成に必要な周辺機能を集積した CMOS シングルチップマイコンです。

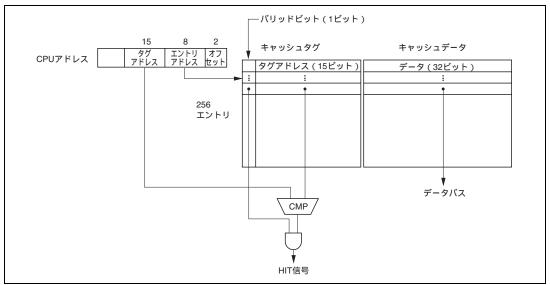

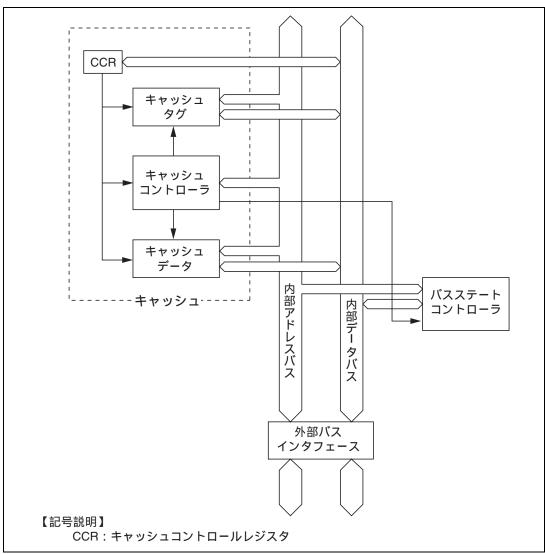

本 LSI の CPU は、RISC(Reduced Instruction Set Computer)タイプの命令セットを持っており、基本的に 1 命令 1 サイクルで動作するので、命令実行速度が飛躍的に向上しています。また内部 32 ビット構成となっており、データ処理能力を強化しています。本 LSI の CPU によって、従来のマイコンでは実現が不可能だった、高速性が要求されるリアルタイム制御等のアプリケーションでも、より低コストでかつ高性能 / 高機能なシステムを組むことができるようになります。その上、本 LSI には 1 KB のキャッシュを搭載しており、外部メモリアクセス時の CPU 性能向上が可能です。

さらに本 LSI は、システム構成に必要な周辺機能として、大容量 ROM(SH7014 は ROM レス)、RAM、タイマ、シリアルコミュニケーションインタフェース(SCI)、A/D 変換器、割込みコントローラ(INTC)、I/O ポートなどを内蔵しています。また、外部メモリアクセスサポート機能により、メモリや周辺 LSI とを効率的に接続できます。これらにより、システムコストの大幅な低減が可能です。

また、内蔵 ROM にはフラッシュメモリを内蔵した F- $ZTAT^{\text{IM}}*$ 版とマスク ROM 版があります。 F- $ZTAT^{\text{IM}}$  は専用ライタとアプリケーションシステムのオンボードでプログラムの書き込みや書き換えが可能です。

【注】\* F-ZTAT は、(株)ルネサス テクノロジの商標です。

表 1 1 特長

| 表 1.1 特長   |                                                 |  |  |

|------------|-------------------------------------------------|--|--|

| 項目         | 仕 様                                             |  |  |

| CPU        | ルネサス テクノロジオリジナルアーキテクチャを採用                       |  |  |

|            | 内部 32 ビット構成                                     |  |  |

|            | 汎用レジスタマシン                                       |  |  |

|            | 汎用レジスタ 32 ビット×16 本                              |  |  |

|            | コントロールレジスタ 32 ビット×3 本                           |  |  |

|            | システムレジスタ 32 ビット×4 本                             |  |  |

|            | RISC(Reduced Instruction Set Computer)タイプの命令セット |  |  |

|            | 命令長:16 ビット固定長による、コード効率の向上                       |  |  |

|            | ロードストアアーキテクチャ(基本演算はレジスタ間で実行)                    |  |  |

|            | 遅延分岐命令の採用で、分岐時のパイプラインの乱れを軽減                     |  |  |

|            | C 言語指向の命令セット                                    |  |  |

|            | 命令実行時間 1 命令 / 1 サイクル (28.7MHz 動作時:35ns / 命令)    |  |  |

|            | アドレス空間 アーキテクチャ上は 4GB                            |  |  |

|            | 乗算器内蔵 乗算器内蔵により、32×32→64 乗算を 2~4 サイクル実行          |  |  |

|            | 32 × 32 + 64→64 積和演算を 2 ~ 4 サイクル実行              |  |  |

|            | パイプライン 5段パイプライン方式                               |  |  |

| 割り込みコントローラ | 外部割り込み端子×7本(NMI、IRQ×6)                          |  |  |

| (INTC)     | 内部割り込み要因 28 要因                                  |  |  |

|            | 16 レベルの優先順位設定が可能                                |  |  |

| 項目             | <u></u>                                           |  |  |  |

|----------------|---------------------------------------------------|--|--|--|

| バスステート         | 外部拡張時のメモリアクセスをサポート                                |  |  |  |

| コントローラ         | 外部データバスは 8/16 ビット                                 |  |  |  |

| (BSC)          | アドレス空間を 5 エリアに分割(SRAM 空間×4 エリア、DRAM 空間×1 エリア)     |  |  |  |

|                | おのおののエリアに以下の特性を設定可能                               |  |  |  |

|                | ウェイトサイクル数                                         |  |  |  |

|                | 各エリアに対応したチップセレクト信号を出力                             |  |  |  |

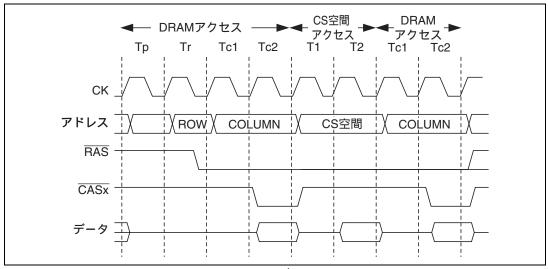

|                | DRAM 空間アクセス時                                      |  |  |  |

|                | ・DRAM 用 RAS、CAS 信号を出力                             |  |  |  |

|                | ・RAS プリチャージタイム確保用 Tp サイクル発生可能                     |  |  |  |

|                | DRAM バーストアクセス機能                                   |  |  |  |

|                | DRAM の高速アクセスモードサポート                               |  |  |  |

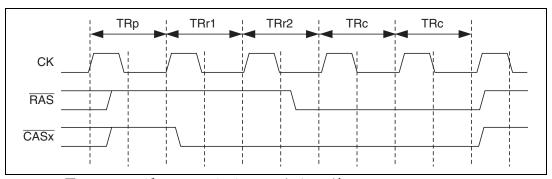

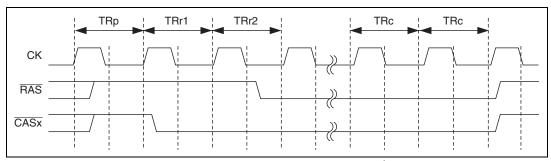

|                | DRAM リフレッシュ機能                                     |  |  |  |

|                | プログラマブルなリフレッシュ間隔                                  |  |  |  |

|                | CAS ビフォア RAS リフレッシュ / セルフリフレッシュをサポート              |  |  |  |

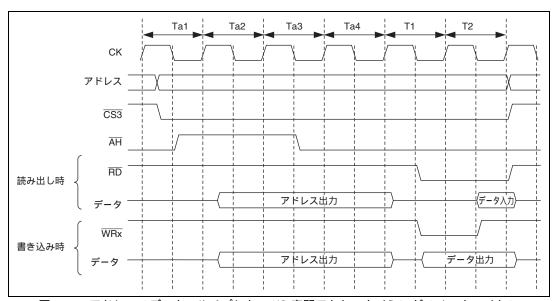

|                | アドレスデータマルチプレクス I/O デバイスをアクセス可能                    |  |  |  |

|                | 外部 WAIT 信号によるウェイトサイクルの挿入可                         |  |  |  |

|                | 【注】バス権解放なし                                        |  |  |  |

| ダイレクトメモリ       | サイクルスチール / バースト転送サポート                             |  |  |  |

| アクセスコントローラ     | シングルアドレスモード / デュアルアドレスモードサポート                     |  |  |  |

| (DMAC)×2チャネル   | 優先順位: ch0 > ch1 固定                                |  |  |  |

|                | 転送カウンタ 16bit                                      |  |  |  |

|                | 転送要求元は外部 DREQ 入力、オートリクエストおよび内蔵周辺モジュール             |  |  |  |

|                | アドレス空間は 4G バイト                                    |  |  |  |

|                | 転送データサイズは 8、16、32 ビットから選択可能                       |  |  |  |

| マルチファンクション     | 16 ビットタイマ 3ch をベースに最大 8 種類の波形出力または最大 8 種類のパルスの    |  |  |  |

| タイマパルスユニット     | 入出力処理が可能                                          |  |  |  |

| (MTU)×3チャネル    | 8 本のアウトプットコンペアレジスタ兼インプットキャプチャレジスタ                 |  |  |  |

|                | 総数8本の独立したコンパレータ                                   |  |  |  |

|                | 8 種類のカウンタ入力クロックを選択可能                              |  |  |  |

|                | インプットキャプチャ機能                                      |  |  |  |

|                | パルス出力モード                                          |  |  |  |

|                | - ワンショット / トグル / PWM                              |  |  |  |

|                | 位相計数モード                                           |  |  |  |

|                | - 2 相エンコーダ計数処理が可能                                 |  |  |  |

| コンペアマッチタイマ     | 16 ビットフリーランニングカウンタ                                |  |  |  |

| (CMT)×2チャネル    | 1つのコンペアレジスタ                                       |  |  |  |

|                | コンペアマッチで割り込み要求を発生                                 |  |  |  |

| ウォッチドッグタイマ     | ウォッチドッグタイマ / インターバルタイマの切り替えが可能                    |  |  |  |

| (WDT)×1チャネル    | カウントオーバフロー時、内部リセット、外部信号、または割り込みを発生                |  |  |  |

| シリアル           | 1チャネルあたり                                          |  |  |  |

| コミュニケーション      | 「ファイルのだり<br>  調歩同期 / クロック同期式モードの選択が可能             |  |  |  |

| インタフェース        | 過少円期 / プログラ円 期式 ビードの送れが 円能   送受信を同時に行うことが可能 (全二重) |  |  |  |

| (SCI)×2チャネル    |                                                   |  |  |  |

| (301) 22) 1770 | マルチプロセッサ間通信機能                                     |  |  |  |

| <br> /O ポート    |                                                   |  |  |  |

| 1/0 M = F      | 入出力: 35 本、入力: 8 本、合計 43 本 ( SH7014 )              |  |  |  |

| A /D ========  | 入出力: 74 本、入力: 8 本、合計 82 本 ( SH7016/17 )           |  |  |  |

| A/D 変換器        | 10 ビット×8 チャネル                                     |  |  |  |

|                | SH7014 は高速 A/D 変換器、SH7016/17 は中速 A/D 変換器内蔵        |  |  |  |

| 項目       |                                                                                                                                                                                                                 |                                       | 1        | 士 榜                | ŧ          |           |        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|--------------------|------------|-----------|--------|

| 内蔵メモリ    |                                                                                                                                                                                                                 | 14 : ROM L<br>6 : 64KB (<br>7 : 128KB | マスク RO   | ,                  |            |           |        |

|          | RAM SH701<br>SH701                                                                                                                                                                                              | 4/16:3KB<br>7:4KB(=                   |          |                    | ,          |           |        |

| 動作モード    | 動作モード 拡張・ROM なしモード(SH7014/16/17) 拡張・ROM ありモード(SH7016/17) シングルチップモード(SH7016/17) 処理状態 プログラム実行状態 例外処理状態 低消費電力モード スリープモード ソフトウェアスタンバイモード                                                                            |                                       |          |                    |            |           |        |

| クロック発振器  | <u> </u>                                                                                                                                                                                                        |                                       | <u> </u> |                    |            |           |        |

| (CPG)    | クロック逓倍用 PLL 回路内蔵                                                                                                                                                                                                |                                       |          |                    |            |           |        |

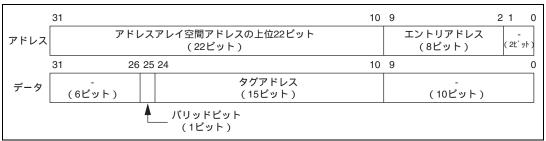

| キャッシュメモリ | 1KB 命令キャッシュ<br>命令コードおよび PC 相対リード・データをキャッシング<br>ライン長は4 バイト(1 ロングワード:2 命令長分)<br>キャッシュタグは 256 エントリ<br>ダイレクトマップ方式<br>内蔵 RAM、内蔵 I/O エリアはキャッシュ対象外<br>内蔵 RAM と兼用しており、キャッシュイネーブル時は内蔵 RAM のうち<br>2KB をアドレスアレイデータアレイとして使用 |                                       |          |                    |            |           |        |

| 製品ラインアップ | 型名                                                                                                                                                                                                              | 内蔵ROM                                 | 内蔵RAM    | A/D精度              | 周波数/電圧     | 温度        | パッケージ  |

|          |                                                                                                                                                                                                                 | ROMなし                                 | 3KB      | ± 15LSB<br>(高速A/D) | 28.7MHz/5V | -20 ~ +75 | FP-112 |

|          | HD6417014RF28                                                                                                                                                                                                   | ROMなし                                 | ЗКВ      | ±8LSB<br>(高速A/D)   | 28.7MHz/5V | -20 ~ +75 | FP-112 |

|          | HD6437016F28 64KB マスクROM 3KB ± 4LSB (中速A/D) 28.7MHz/5V -20~+75 FP-112                                                                                                                                           |                                       |          |                    |            |           |        |

|          | HD64F7017F28                                                                                                                                                                                                    | 128KB<br>フラッシュ<br>メモリ                 | 4KB      | ± 4LSB<br>(中速A/D)  | 28.7MHz/5V | -20 ~ +75 | FP-112 |

# 1.2 ブロック図

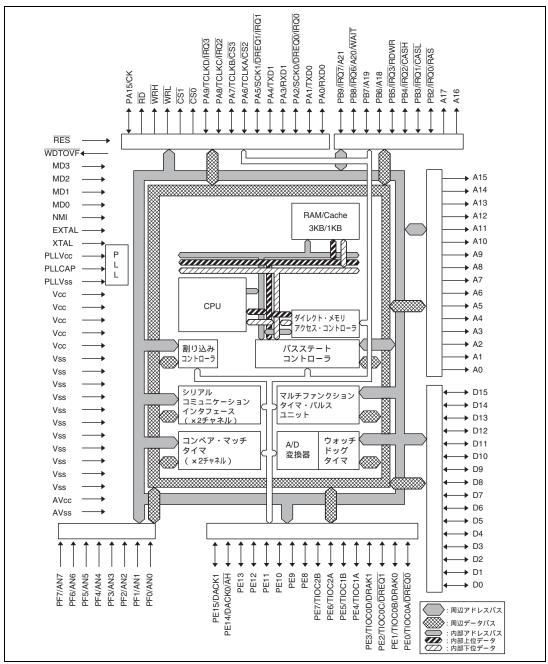

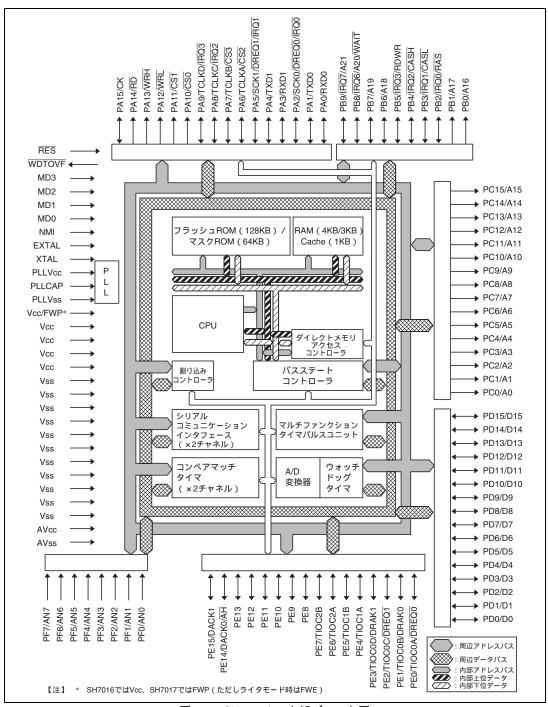

SH7014 のブロック図を図 1.1 に示します。SH7016/17 のブロック図を図 1.2 に示します。

図 1.1 SH7014 内部ブロック図

図 1.2 SH7016/17 内部ブロック図

# 1.3 端子説明

### 1.3.1 ピン配置図

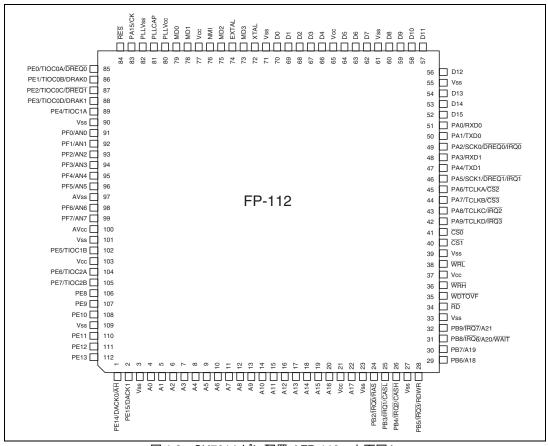

SH7014 のピン配置図を図 1.3 に示します。

図 1.3 SH7014 ピン配置 (FP-112:上面図)

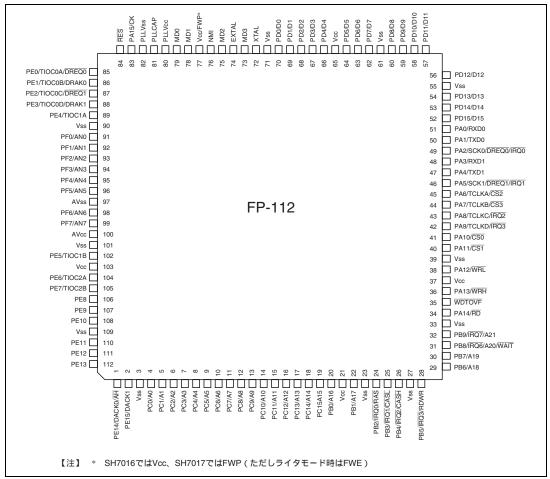

### SH7016/17 のピン配置図を図 1.4 に示します。

図 1.4 SH7016/17 ピン配置 (FP-112:上面図)

# 1.3.2 端子一覧

表 1.2 SH7017F モード別ピン配置

| 端子番号     | 表 1.2 SH/01/F モード) MCU モード | ライタモード |

|----------|----------------------------|--------|

| (FP-112) |                            |        |

| 1        | PE14/DACK0/AH              | NC     |

| 2        | PE15/DACK1                 | NC     |

| 3        | Vss                        | Vss    |

| 4        | PC0/A0                     | A0     |

| 5        | PC1/A1                     | A1     |

| 6        | PC2/A2                     | A2     |

| 7        | PC3/A3                     | A3     |

| 8        | PC4/A4                     | A4     |

| 9        | PC5/A5                     | A5     |

| 10       | PC6/A6                     | A6     |

| 11       | PC7/A7                     | A7     |

| 12       | PC8/A8                     | A8     |

| 13       | PC9/A9                     | A9     |

| 14       | PC10/A10                   | A10    |

| 15       | PC11/A11                   | A11    |

| 16       | PC12/A12                   | A12    |

| 17       | PC13/A13                   | A13    |

| 18       | PC14/A14                   | A14    |

| 19       | PC15/A15                   | A15    |

| 20       | PB0/A16                    | A16    |

| 21       | Vcc                        | Vcc    |

| 22       | PB1/A17                    | NC     |

| 23       | Vss                        | Vss    |

| 24       | PB2/IRQ0/RAS               | NC     |

| 25       | PB3/IRQ1/CASL              | NC     |

| 26       | PB4/IRQ2/CASH              | A17    |

| 27       | Vss                        | Vss    |

| 28       | PB5/IRQ3/RDWR              | NC     |

| 29       | PB6/A18                    | NC     |

| 30       | PB7/A19                    | NC     |

| 31       | PB8/IRQ6/A20/WAIT          | NC     |

| 32       | PB9/IRQ7/A21               | NC     |

| 33       | Vss                        | Vss    |

| 34       | PA14/RD                    | NC     |

| 35       | WDTOVF                     | NC     |

| 36       | PA13/WRH                   | NC     |

| 37       | Vcc                        | Vcc    |

| 38       | PA12/WRL                   | NC     |

| 39       | Vss                        | Vss    |

| 端子番号<br>(FP-112) | MCU モード             | ライタモード |

|------------------|---------------------|--------|

| 40               | PA11/CST            | NC     |

| 41               | PA10/CS0            | NC     |

| 42               | PA9/TCLKD/IRQ3      | CE     |

| 43               | PA8/TCLKC/IRQ2      | ŌĒ     |

| 44               | PA7/TCLKB/CS3       | WE     |

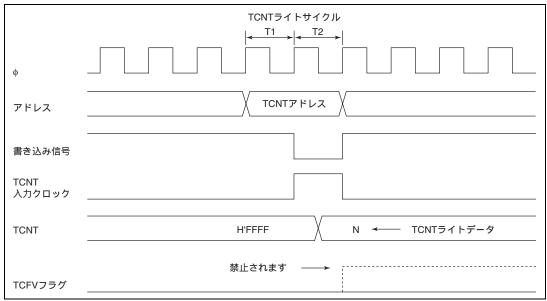

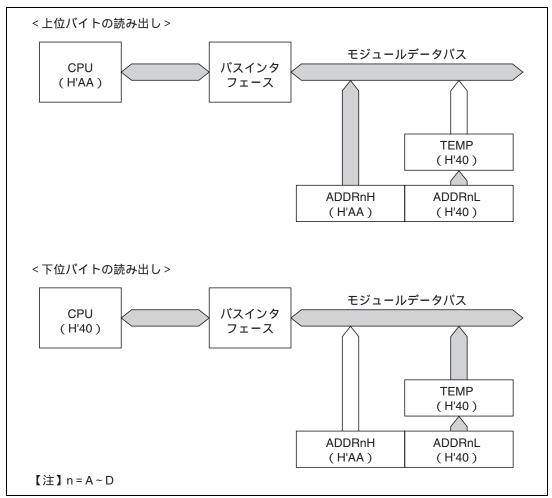

| 45               | PA6/TCLKA/CS2       | NC     |