改訂一覧は改訂箇所をまとめたものであり、 詳細については必ず本文の内容をご確認ください。

# SH7239 グループ、SH7237 グループ

ユーザーズマニュアル ハードウェア編

ルネサス 32 ビット RISC マイクロコンピュータ SuperH<sup>™</sup> RISC engine ファミリ

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器・システムの設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因して、お客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 2. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 3. 本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権に対する侵害に関し、当社は、何らの責任を負うものではありません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を改造、改変、複製等しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、 各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、 家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、 防災・防犯装置、各種安全装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(原子力制御システム、軍事機器等)に使用されることを意図しておらず、使用することはできません。 たとえ、意図しない用途に当社製品を使用したことによりお客様または第三者に損害が生じても、当社は一切その責任を負いません。 なお、ご不明点がある場合は、当社営業にお問い合わせください。

- 6. 当社製品をご使用の際は、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他の保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 9. 本資料に記載されている当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。また、当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途に使用しないでください。当社製品または技術を輸出する場合は、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。

- 10. お客様の転売等により、本ご注意書き記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は何らの責任も負わず、お客様にてご負担して頂きますのでご了承ください。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項 については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の記載が優 先するものとします。

### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS 製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI 周辺のノイズが印加され、LSI 内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

#### 3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。 プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。 同じグループのマイコンでも型名が違うと、内部 ROM、レイアウトパターンの相違などにより、電気的 特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ輻射量などが異なる場合があります。型名が 違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

# このマニュアルの使い方

## 1. 目的と対象者

このマニュアルは、本マイコンのハードウェア機能と電気的特性をユーザに理解していただくためのマニュアルです。本マイコンを用いた応用システムを設計するユーザを対象にしています。このマニュアルを使用するには、電気回路、論理回路、マイクロコンピュータに関する基本的な知識が必要です。

このマニュアルは、大きく分類すると、製品の概要、CPU、システム制御機能、周辺機能、電気的特性、 使用上の注意で構成されています。

本マイコンは、注意事項を十分確認の上、使用してください。注意事項は、各章の本文中、各章の最後、注意事項の章に記載しています。

改訂記録は旧版の記載内容に対して訂正または追加した主な箇所をまとめたものです。改訂内容すべてを 記録したものではありません。詳細は、このマニュアルの本文でご確認ください。

SH7214 グループ、SH7216 グループでは次のドキュメントを用意しています。ドキュメントは最新版を使用してください。最新版はルネサス エレクトロニクスのホームページに掲載されています。

| ドキュメントの種類         | 記載内容            | 資料名             | 資料番号          |

|-------------------|-----------------|-----------------|---------------|

| データシート            | ハードウェアの概要と電気的   | _               | _             |

|                   | 特性              |                 |               |

| ユーザーズマニュアル        | ハードウェアの仕様(ピン配   | SH7214 グループ、    | 本ユーザーズマニュアル   |

| ハードウェア編           | 置、メモリマップ、周辺機能の  | SH7216 グループ     |               |

|                   | 仕様、電気的特性、タイミング) | ユーザーズマニュアル      |               |

|                   | と動作説明           | ハードウェア編         |               |

| ユーザーズマニュアル        | CPU・命令セットの説明    | SH-2A、SH2A-FPU  | R01US0031JJ   |

| ソフトウェア編           |                 | ユーザーズマニュアル      |               |

|                   |                 | ソフトウェア編         |               |

| アプリケーションノート       | 応用例参考プログラムなど    | ルネサス エレクトロニクスのホ | ニームページに掲載されてい |

| RENESAS TECHNICAL | 製品の仕様、ドキュメント等に  | ます。             |               |

| UPDATE            | 関する速報           |                 |               |

## 2. 数や記号の表記

このマニュアルで使用するレジスタ名やビット名、数字や記号の表記の凡例を以下に説明します。

#### (1) 全体的な表記

本文中ではビットの説明をする場合、モジュールやレジスタとの関連を明確にするため、ビット名を 「モジュール名・レジスタ名・ビット名」または「レジスタ名・ビット名」と表記している場合があります。

#### (2) レジスタの表記

同一または類似した機能が複数チャネルに存在する場合に「レジスタ名\_チャネル番号」の表記を使用します。 (例) CMCSR\_0: コンペアマッチタイマのチャネル0(\_0) のCMCSRレジスタを示します。

#### (3) 数字の表記

2進数はB'nnnn (明らかに2進数と判断できる場合はB'を省略) 、16進数はH'nnnnまたは0xnnnn、10進数はnnnで表します。

(例) 2進数: B'11または11

16進数: H'EFAOまたは0xEFAO

10進数:1234

#### (4) ローアクティブの表記

ローアクティブの信号および端子には上線を付けて表記しています。

#### (例) WDTOVE

【注】 上記した図中のビット名や文章は例であり、マニュアルの内容とは関係がありません。

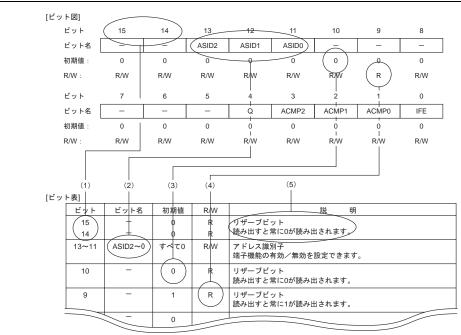

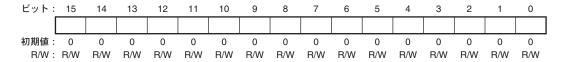

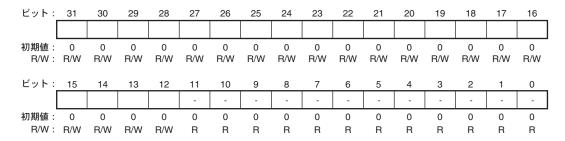

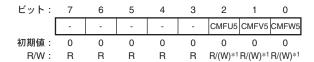

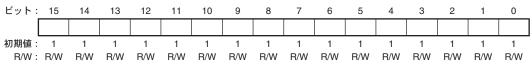

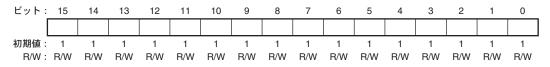

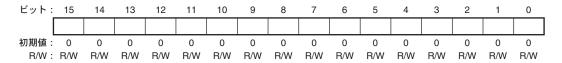

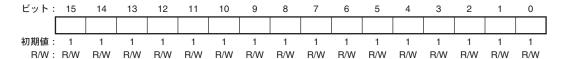

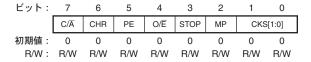

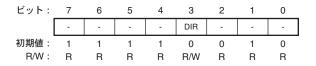

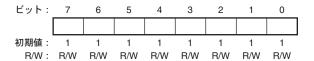

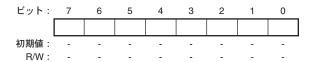

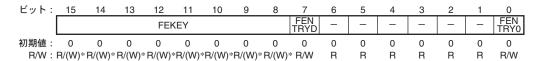

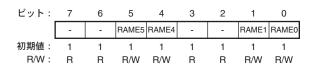

## 3. レジスタの表記

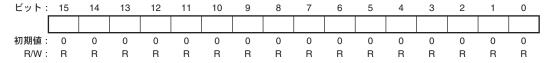

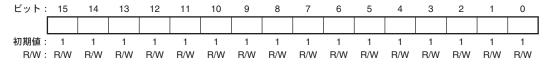

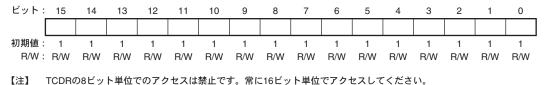

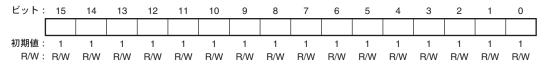

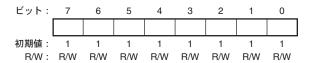

各レジスタの説明には、ビットの並びを示すビット図とビットに設定する内容を説明するビット表があります。

使用する記号、用語を以下に説明します。

【注】 上記した図中のビット名や文章は例であり、マニュアルの内容とは関係がありません。

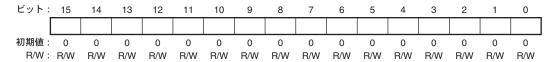

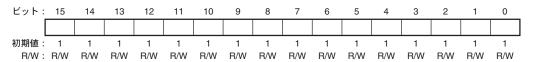

#### (1) ビット

ビット番号を示します。

32ビットレジスタの場合は31から0の順に、16ビットレジスタの場合は15から0の順に示します。

#### (2) ビット名

ビット名またはフィールド名を示します。

フィールドでビット桁数を明示する必要があるときは、ASID[3:0]というように桁数の表記を追加します。

また、リザーブビットの場合は「一」と表記します。

ただし、タイムカウンタなどをはじめとして、ビット名の記載をせずに空白のままとしているものもあります。

#### (3) 初期値

各ビットのパワーオンリセット後の値を初期値として示します。

0 : 初期値は0であることを示します。

1 : 初期値は1であることを示します。

- : 初期値は不定であることを示します。

#### (4) R/W

(マイル) 各ビットが読み出し可能か、書き込み可能か、または書き込みも読み出しも不可であるかを示します。 使用する表記を以下に説明します。

R/W: 読み出しおよび書き込みが可能なビットまたはフィールドです。

R/(W) : 読み出しおよび書き込みが可能なビットまたはフィールドです。 ただし書き込みは、フラグをクリアするための書き込みのみ可能です。

: 読み出しが可能なビットまたはフィールドです。

リザーブビットはすべて「R」と表記します。書き込む必要がある場合は、

ビット表で指定された値を書き込んでください。

W:書き込みが可能なビットまたはフィールドです。

#### (5) 説明

ビットの機能について説明しています。

## 4. 略語および略称の説明

以下に本書内で使用されている略語または略称を示します。

## • 本製品固有の略語または略称

| 略称   | 英語名                            | 日本語名                 |

|------|--------------------------------|----------------------|

| BSC  | Bus Controller                 | バスコントローラ             |

| CPG  | Clock Pulse Generator          | クロック発振器              |

| DTC  | Data Transfer Controller       | データトランスファコントローラ      |

| INTC | Interrupt Controller           | 割り込みコントローラ           |

| SCI  | Serial Communication Interface | シリアルコミュニケーションインタフェース |

| WDT  | Watchdog Timer                 | ウォッチドッグタイマ           |

## • その他の略語または略称

| 略語/略称 | 英語名                                          | 日本語名               |

|-------|----------------------------------------------|--------------------|

| ACIA  | Asynchronous Communication Interface Adapter | 調歩同期式通信アダプタ        |

| bps   | bits per second                              | 転送速度を表す単位          |

| CRC   | Cyclic Redundancy Check                      | 周期的冗長検査            |

| DMA   | Direct Memory Access                         | ダイレクトメモリアクセス       |

| DMAC  | Direct Memory Access Controller              | ダイレクトメモリアクセスコントローラ |

| GSM   | Global System for Mobile Communications      | ジーエスエム             |

| Hi-Z  | High Impedance                               | ハイインピーダンス          |

| IEBus | Inter Equipment bus                          | -                  |

| I/O   | Input/Output                                 | 入出力                |

| IrDA  | Infrared Data Association                    | 赤外線データアソシエーション     |

| LSB   | Least Significant Bit                        | 最下位ビット             |

| MSB   | Most Significant Bit                         | 最上位ビット             |

| NC    | Non-Connection                               | 未接続端子              |

| PLL   | Phase Locked Loop                            | 位相ロックループ           |

| PWM   | Pulse Width Modulation                       | パルス幅変調             |

| SFR   | Special Function Registers                   | 周辺回路制御用レジスタ群       |

| SIM   | Subscriber Identity Module                   | ISO-7816 規定の通信方式   |

| UART  | Universal Asynchronous Receiver/Transmitter  | 非同期シリアルインタフェース     |

| VCO   | Voltage Controlled Oscillator                | 電圧制御発振器            |

# 目次

| 1.  | 概要                                 | 1-1  |

|-----|------------------------------------|------|

| 1.1 | 特長                                 | 1-1  |

| 1.2 | 製品一覧                               | 1-8  |

| 1.3 | ブロック図                              | 1-9  |

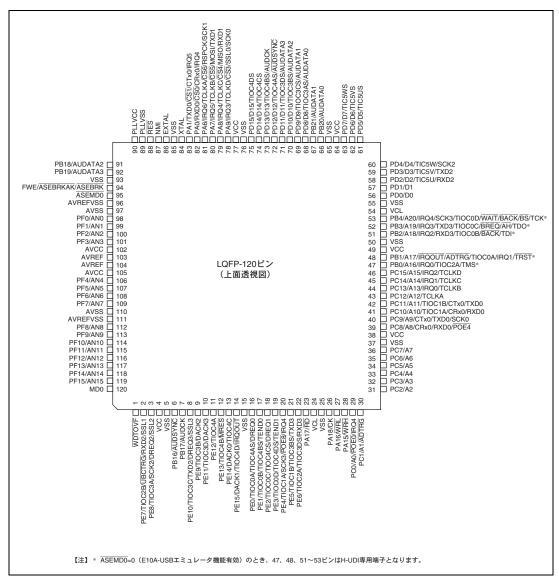

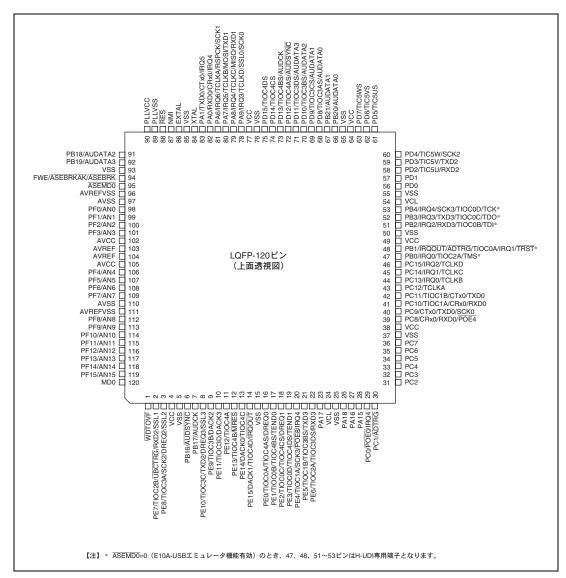

| 1.4 | ピン配置図                              | 1-10 |

| 1.5 | 端子機能                               | 1-12 |

| 2.  | CPU                                | 2-1  |

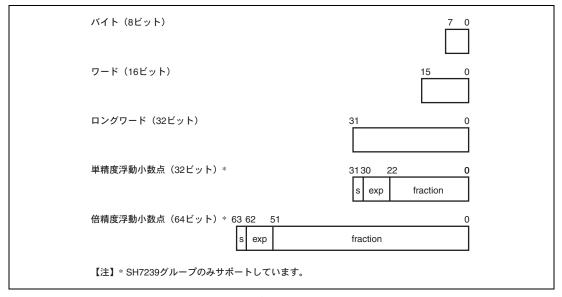

| 2.1 | データフォーマット                          | 2-1  |

| 2.2 | レジスタ構成                             | 2-1  |

| 2.3 | 2.1 汎用レジスタ                         | 2-1  |

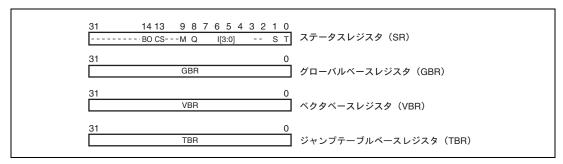

| 2.2 | 2.2 コントロールレジスタ                     | 2-2  |

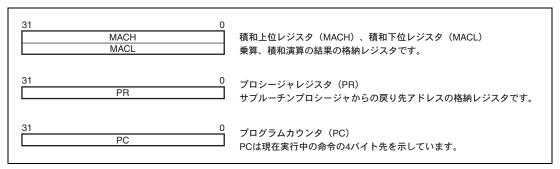

| 2.2 | 2.3 システムレジスタ                       | 2-4  |

| 2.2 | 2.4 浮動小数点レジスタ(SH7239 グループのみ)       | 2-5  |

| 2.2 | 2.5 浮動小数点システムレジスタ(SH7239 グループのみ)   | 2-6  |

| 2.3 | 2.6 レジスタバンク                        | 2-7  |

| 2.2 | 2.7 レジスタの初期値                       | 2-8  |

| 2.3 | データ形式                              | 2-9  |

| 2   | 3.1 レジスタのデータ形式                     | 2-9  |

| 2   | 3.2 メモリのデータ形式                      | 2-9  |

| 2.3 | 3.3 イミディエイトデータのデータ形式               | 2-10 |

| 2.4 | 命令の特長                              | 2-11 |

| 2.4 | 4.1 RISC 方式                        | 2-11 |

| 2.4 | 4.2 アドレッシングモード                     | 2-15 |

| 2.4 | 4.3 命令形式                           | 2-19 |

| 2.5 | 命令セット                              | 2-23 |

| 2.: | 5.1 分類順命令セット                       | 2-23 |

| 2.: | 5.2 データ転送命令                        | 2-28 |

| 2.: | 5.3 算術演算命令                         | 2-31 |

| 2.: | 5.4 論理演算命令                         | 2-33 |

| 2.: | 5.5 シフト命令                          | 2-34 |

| 2.: | 5.6 分岐命令                           | 2-35 |

| 2.: | 5.7 システム制御命令                       | 2-36 |

| 2.: | 5.8 浮動小数点演算命令(SH7239 グループのみ)       | 2-37 |

| 2.: | 5.9 FPU に関する CPU 命令(SH7239 グループのみ) | 2-39 |

| 2.5.10 | ビット操作命令                   | 2-39 |

|--------|---------------------------|------|

| 2.6    | 処理状態                      | 2-41 |

| 3. MC  | U 動作モード                   | 3-1  |

| 3.1    | 動作モードの選択                  | 3-1  |

| 3.2    | 入出力端子                     | 3-2  |

| 3.3    | 各動作モードの説明                 | 3-2  |

| 3.3.1  | モード 2(MCU 拡張モード 2)        | 3-2  |

| 3.3.2  | モード 3(シングルチップモード)         | 3-2  |

| 3.4    | アドレスマップ                   | 3-3  |

| 3.5    | 本LSIの初期状態                 | 3-5  |

| 3.6    | 動作モード変更時の注意事項             | 3-5  |

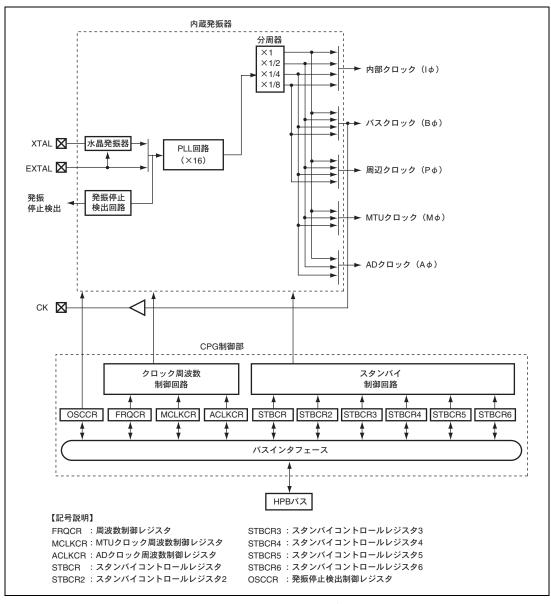

| 4. クロ  | コックパルス発振器(CPG)            | 4-1  |

| 4.1    | 特長                        | 4-1  |

| 4.2    | 入出力端子                     | 4-4  |

| 4.3    | クロック動作モード                 | 4-5  |

| 4.4    | レジスタの説明                   | 4-8  |

| 4.4.1  | 周波数制御レジスタ(FRQCR)          | 4-8  |

| 4.4.2  | MTU クロック周波数制御レジスタ(MCLKCR) | 4-10 |

| 4.4.3  | AD クロック周波数制御レジスタ(ACLKCR)  | 4-11 |

| 4.4.4  | 発振停止検出制御レジスタ(OSCCR)       | 4-12 |

| 4.5    | 周波数変更方法                   | 4-13 |

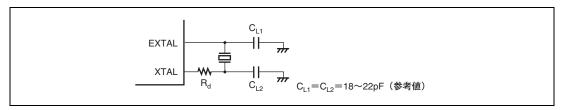

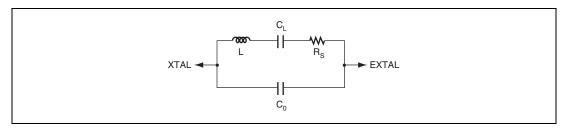

| 4.6    | 発振器                       | 4-14 |

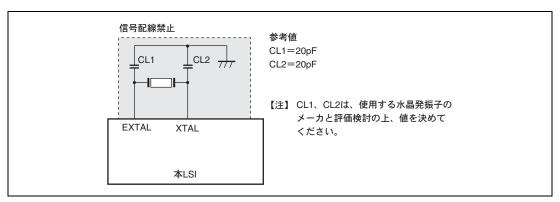

| 4.6.1  | 水晶発振子を接続する方法              | 4-14 |

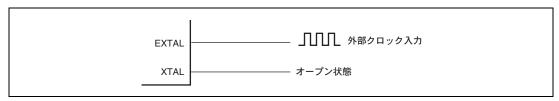

| 4.6.2  | 外部クロックを入力する方法             | 4-15 |

| 4.7    | 発振停止検出機能                  | 4-16 |

| 4.8    | ボード設計上の注意事項               | 4-17 |

| 4.8.1  | 外部水晶発振子使用時の注意             | 4-17 |

| 5. 例夕  | <b>卜</b> 処理               | 5-1  |

| 5.1    | 概要                        | 5-1  |

| 5.1.1  | 例外処理の種類と優先順位              | 5-1  |

| 5.1.2  | 例外処理の動作                   | 5-3  |

| 5.1.3  | 例外処理ベクタテーブル               | 5-5  |

| 5.2    | リセット                      | 5-7  |

| 5.2.1  | リセットの種類                   | 5-7  |

| 5.2.2  | パワーオンリセット                 | 5-8  |

| 5.2.3  | マニュアルリセット                 | 5-9  |

| 5.3    | アドレスエラー                   | 5-10 |

| 5.3.1  | アドレスエラー発生要因               | 5-10 |

| 5.3.2 | アドレスエラー例外処理                                           | 5-11  |

|-------|-------------------------------------------------------|-------|

| 5.4   | レジスタバンクエラー                                            | 5-12  |

| 5.4.1 | レジスタバンクエラー発生要因                                        | 5-12  |

| 5.4.2 | レジスタバンクエラー例外処理                                        | 5-12  |

| 5.5   | 割り込み                                                  | 5-13  |

| 5.5.1 | 割り込み要因                                                | 5-13  |

| 5.5.2 | 割り込み優先順位                                              | 5-14  |

| 5.5.3 | 割り込み例外処理                                              | 5-15  |

| 5.6   | 命令による例外                                               | 5-16  |

| 5.6.1 | 命令による例外の種類                                            | 5-16  |

| 5.6.2 | トラップ命令                                                | 5-16  |

| 5.6.3 | スロット不当命令                                              | 5-17  |

| 5.6.4 | 一般不当命令                                                | 5-17  |

| 5.6.5 | 整数除算命令                                                | 5-17  |

| 5.6.6 | 浮動小数点演算命令(SH7239 グループのみ)                              | 5-18  |

| 5.7   | 例外処理が受け付けられない場合                                       | 5-19  |

| 5.8   | 例外処理後のスタックの状態                                         | 5-20  |

| 5.9   | 使用上の注意事項                                              | 5-21  |

| 5.9.1 | スタックポインタ(SP)の値                                        | 5-21  |

| 5.9.2 | ベクタベースレジスタ(VBR)の値                                     |       |

| 5.9.3 | アドレスエラー例外処理のスタッキングで発生するアドレスエラー                        | 5-21  |

| 5.9.4 | CPU のステータスレジスタ(SR)の割り込みマスクレベル(IMASK)変更時の注意事           | 項5-21 |

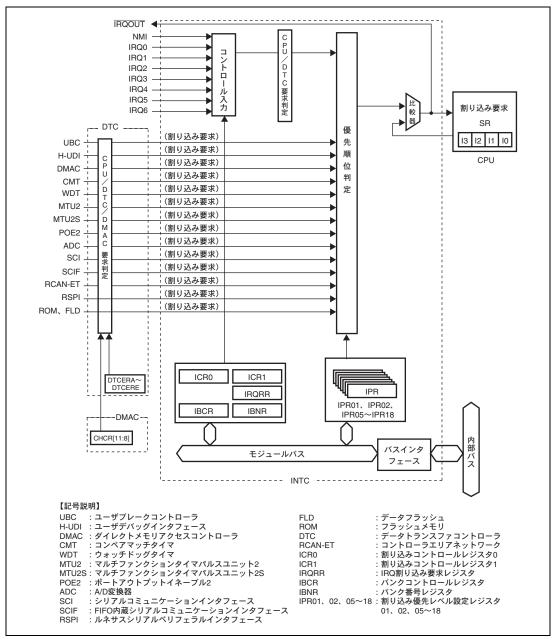

| 6. 割  | J込みコントローラ(INTC)                                       | 6-1   |

| 6.1   | 特長                                                    | 6-1   |

| 6.2   | 入出力端子                                                 | 6-3   |

| 6.3   | レジスタの説明                                               | 6-4   |

| 6.3.1 | 割り込み優先レベル設定レジスタ 01、02、05~18 (IPR01、IPR02、IPR05~IPR18) | 6-5   |

| 6.3.2 | 割り込みコントロールレジスタ 0(ICRO)                                | 6-6   |

| 6.3.3 | 割り込みコントロールレジスタ 1(ICR1)                                | 6-7   |

| 6.3.4 | IRQ 割り込み要求レジスタ(IRQRR)                                 | 6-8   |

| 6.3.5 | バンクコントロールレジスタ(IBCR)                                   | 6-9   |

| 6.3.6 | バンク番号レジスタ(IBNR)                                       | 6-10  |

| 6.4   | 割り込み要因                                                | 6-11  |

| 6.4.1 | NMI 割り込み                                              | 6-11  |

| 6.4.2 | ユーザブレーク割り込み                                           | 6-11  |

| 6.4.3 | H-UDI 割り込み                                            | 6-11  |

| 6.4.4 | IRQ 割り込み                                              | 6-11  |

| 6.4.5 | メモリエラー割り込み                                            | 6-12  |

| 6.4.6 | 内蔵周辺モジュール割り込み                                         | 6-12  |

| 6.5   | 割り込み例外処理ベクタテーブルと優先順位                                  | 6-13  |

| 6.6    | 動作説明                                           | 6-17 |

|--------|------------------------------------------------|------|

| 6.6.1  | 割り込み動作の流れ                                      | 6-17 |

| 6.6.2  | 割り込み例外処理終了後のスタックの状態                            | 6-19 |

| 6.7    | 割り込み応答時間                                       | 6-20 |

| 6.8    | レジスタバンク                                        | 6-25 |

| 6.8.1  | バンクの対象レジスタと入出力方式                               | 6-25 |

| 6.8.2  | バンク退避、復帰の動作                                    | 6-26 |

| 6.8.3  | すべてのバンクに退避が行われた状態での退避、復帰                       | 6-28 |

| 6.8.4  | レジスタバンクの例外                                     | 6-29 |

| 6.8.5  | レジスタバンクエラー例外処理                                 | 6-29 |

| 6.9    | 割り込み要求                                         | 6-30 |

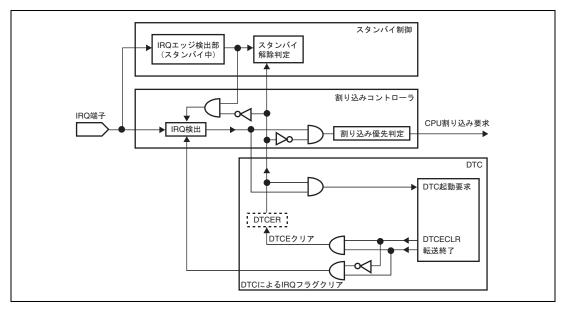

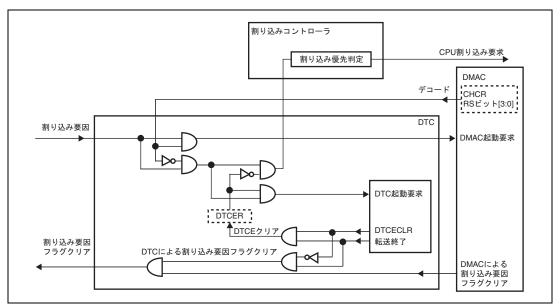

| 6.9.1  | 割り込み要求信号を DTC の起動要因、CPU の割り込み要因とし、DMAC の 起動要因合 |      |

| 6.9.2  | 割り込み要求信号をDMACの起動要因とし、CPUの割り込み要因としない場合          | 6-32 |

| 6.9.3  | 割り込み要求信号を DTC の起動要因とし、CPU の割り込み要因、DMAC の 起動要因合 |      |

| 6.9.4  | 割り込み要求信号を CPU の割り込み要因とし、DTC の起動要因、DMAC 起動要因と   |      |

| 6.10   | 使用上の注意事項                                       | 6-33 |

| 6.10.1 | 割り込み要因クリアのタイミング                                | 6-33 |

| 6.10.2 | NMI を使用しない場合                                   | 6-33 |

| 6.10.3 | IRQOUT のネゲートタイミング                              | 6-33 |

| 6.10.4 | IRQx 割り込み要求によるソフトウェアスタンバイ解除に関する注意事項            | 6-33 |

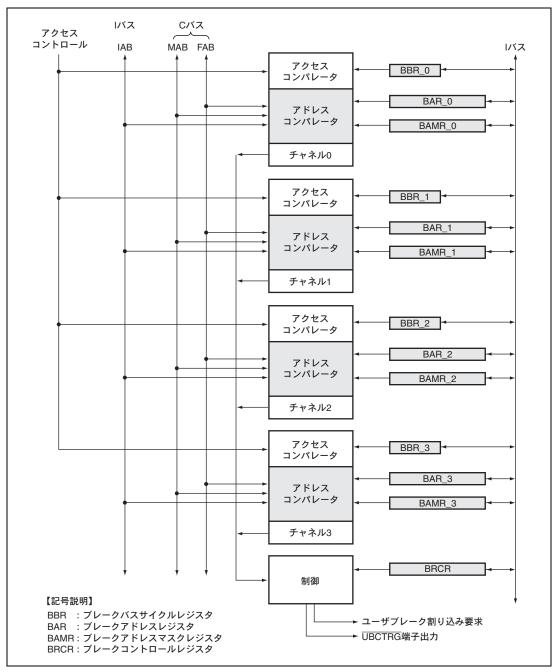

| 7. ユー  | -ザブレークコントローラ(UBC)                              | 7-1  |

| 7.1    | 特長                                             | 7-1  |

| 7.2    | 入出力端子                                          | 7-3  |

| 7.3    | レジスタの説明                                        | 7-4  |

| 7.3.1  | ブレークアドレスレジスタ_0(BAR_0)                          |      |

| 7.3.2  | ブレークアドレスマスクレジスタ_0(BAMR_0)                      | 7-5  |

| 7.3.3  | ブレークバスサイクルレジスタ_0(BBR_0)                        | 7-6  |

| 7.3.4  | ブレークアドレスレジスタ_1(BAR_1)                          | 7-8  |

| 7.3.5  | ブレークアドレスマスクレジスタ_1(BAMR_1)                      | 7-9  |

| 7.3.6  | ブレークバスサイクルレジスタ_1(BBR_1)                        |      |

| 7.3.7  | ブレークアドレスレジスタ_2(BAR_2)                          |      |

| 7.3.8  | ブレークアドレスマスクレジスタ_2(BAMR_2)                      |      |

| 7.3.9  | ブレークバスサイクルレジスタ_2 (BBR_2)                       |      |

| 7.3.10 | ブレークアドレスレジスタ_3 (BAR_3)                         |      |

| 7.3.11 | ブレークアドレスマスクレジスタ_3 (BAMR_3)                     | 7-16 |

| 7.3.12 | ブレークバスサイクルレジスタ_3 (BBR_3)                       | 7-16 |

| 7.3.13 | ブレークコントロールレジスタ(BRCR)                           | 7-18 |

| 7.4    | 動作説明                             | 7-21 |

|--------|----------------------------------|------|

| 7.4.1  | ユーザブレーク動作の流れ                     | 7-21 |

| 7.4.2  | 命令フェッチサイクルでのブレーク                 | 7-22 |

| 7.4.3  | データアクセスサイクルでのブレーク                | 7-23 |

| 7.4.4  | 退避されるプログラムカウンタの値                 | 7-24 |

| 7.4.5  | 使用例                              | 7-24 |

| 7.5    | 割り込み要因                           | 7-27 |

| 7.6    | 使用上の注意事項                         | 7-28 |

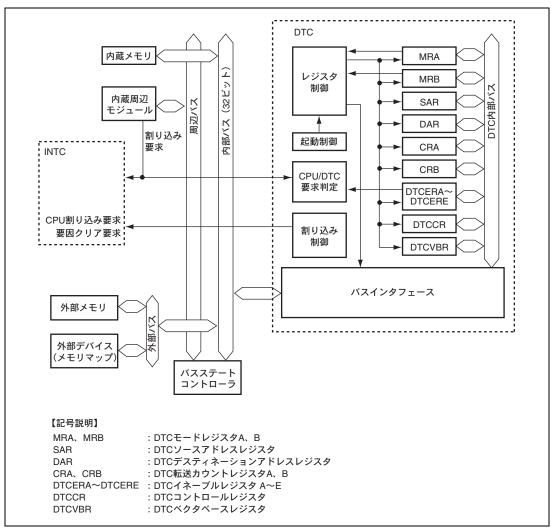

| 8. デー  | -タトランスファコントローラ(DTC)              | 8-1  |

| 8.1    | 特長                               | 8-1  |

| 8.2    | レジスタの説明                          | 8-3  |

| 8.2.1  | DTC モードレジスタ A(MRA)               | 8-4  |

| 8.2.2  | DTC モードレジスタ B (MRB)              | 8-5  |

| 8.2.3  | DTC ソースアドレスレジスタ(SAR)             | 8-6  |

| 8.2.4  | DTC デスティネーションアドレスレジスタ(DAR)       | 8-6  |

| 8.2.5  | DTC 転送カウントレジスタ A(CRA)            | 8-7  |

| 8.2.6  | DTC 転送カウントレジスタ B(CRB)            | 8-7  |

| 8.2.7  | DTC イネーブルレジスタ A~E(DTCERA~DTCERE) | 8-7  |

| 8.2.8  | DTC コントロールレジスタ(DTCCR)            | 8-9  |

| 8.2.9  | DTC ベクタベースレジスタ(DTCVBR)           | 8-10 |

| 8.2.10 | バス機能拡張レジスタ (BSCEHR)              | 8-10 |

| 8.3    | 起動要因                             | 8-10 |

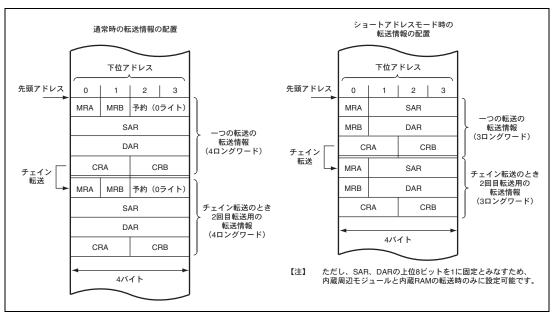

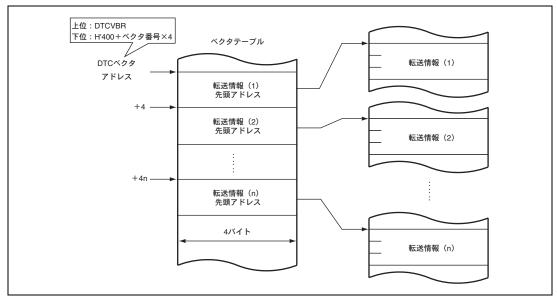

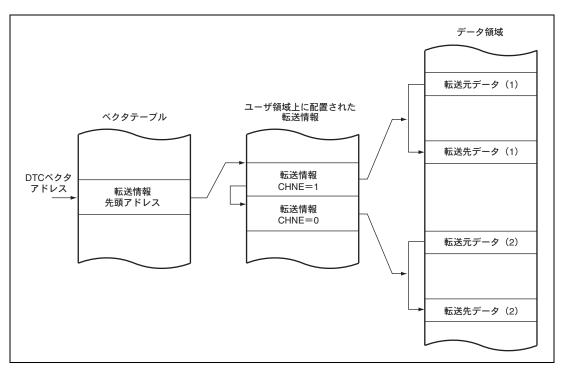

| 8.4    | 転送情報の配置とDTCベクタテーブル               | 8-11 |

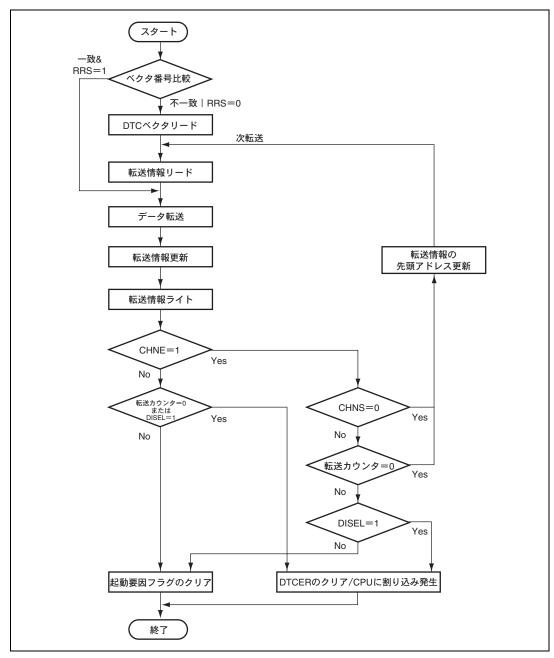

| 8.5    | 動作説明                             | 8-15 |

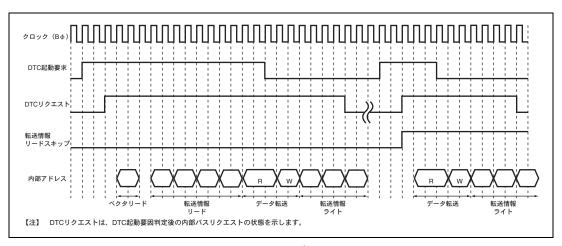

| 8.5.1  | 転送情報リードスキップ機能                    | 8-19 |

| 8.5.2  | 転送情報ライトバックスキップ機能                 | 8-19 |

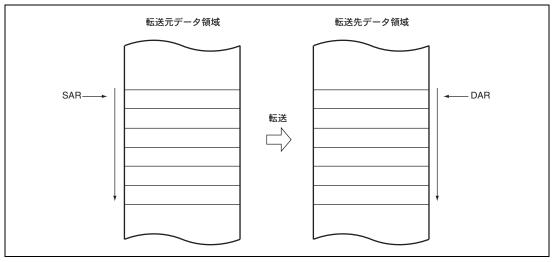

| 8.5.3  | ノーマル転送モード                        | 8-20 |

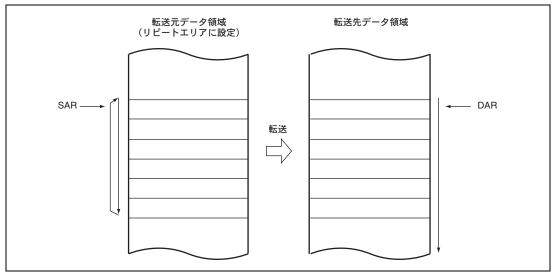

| 8.5.4  | リピート転送モード                        | 8-21 |

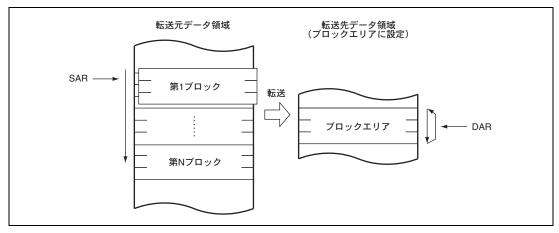

| 8.5.5  | ブロック転送モード                        | 8-22 |

| 8.5.6  | チェイン転送                           | 8-23 |

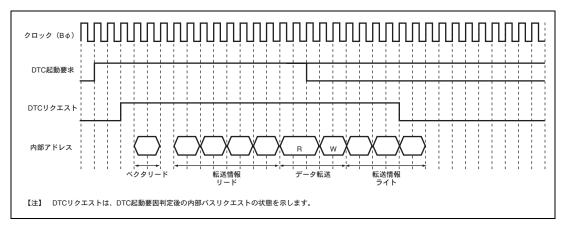

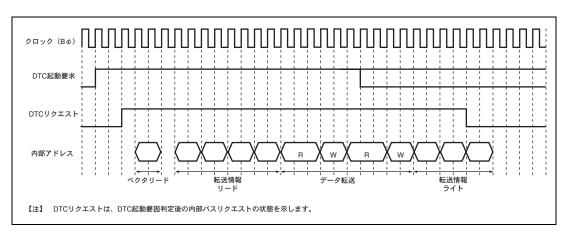

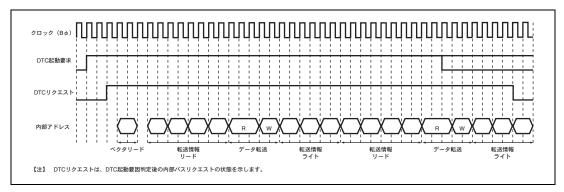

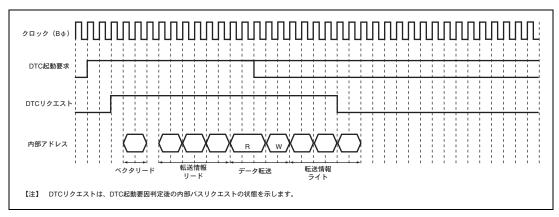

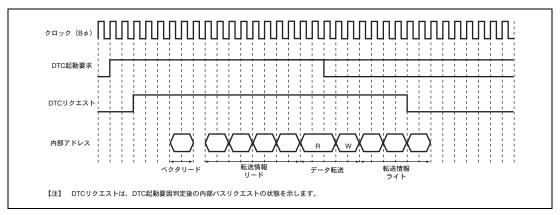

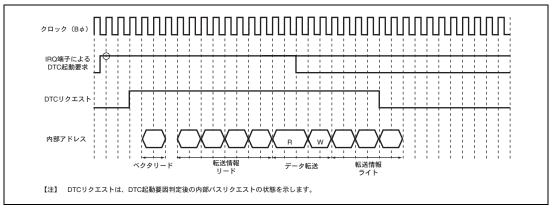

| 8.5.7  | 動作タイミング                          | 8-24 |

| 8.5.8  | DTC の実行ステート                      | 8-27 |

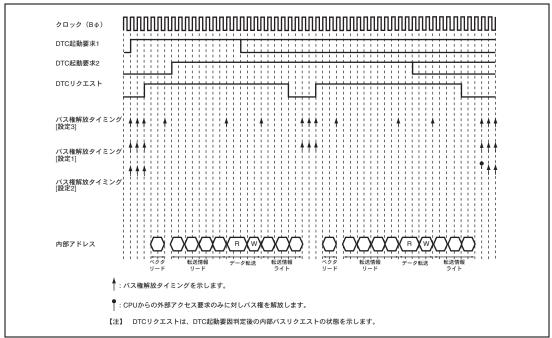

| 8.5.9  | DTC のバス権解放タイミング                  | 8-29 |

| 8.5.10 | DTC 起動の優先順位                      | 8-31 |

| 8.6    | 割り込みによるDTCの起動                    | 8-32 |

| 8.7    | DTC使用例                           | 8-33 |

| 8.7.1  | ノーマル転送                           | 8-33 |

| 8.7.2  | カウンタ=0 のときのチェイン転送                | 8-33 |

| 8.8    | 割り込み要因                           |      |

| 8.9    | 使用上の注意事項                         | 8-35 |

|        |                                  |      |

| 8.9.1  | モジュールスタンバイモードの設定                        | 8-35 |

|--------|-----------------------------------------|------|

| 8.9.2  | 内蔵 RAM                                  | 8-35 |

| 8.9.3  | DTCE ビットの設定                             | 8-35 |

| 8.9.4  | チェイン転送                                  | 8-35 |

| 8.9.5  | 転送情報先頭アドレス/ソースアドレス/デスティネーションアドレス        | 8-35 |

| 8.9.6  | DTC による DTC レジスタのアクセス                   | 8-35 |

| 8.9.7  | IRQ 割り込みを DTC 転送要因にした場合の注意事項            | 8-35 |

| 8.9.8  | SCI および SCIF を DTC 起動要因とする場合の注意事項       | 8-36 |

| 8.9.9  | 割り込み要因フラグのクリア                           | 8-36 |

| 8.9.10 | NMI 割り込みと DTC 起動の競合                     | 8-36 |

| 8.9.11 | DTC 起動要求が途中で取り下げられた場合の動作                | 8-36 |

| 8.9.12 | DTCER の書き込み時の注意事項                       | 8-36 |

| ). バス: | ステートコントローラ(BSC) (SH7239A、SH7237A のみ)    | 9-1  |

| 9.1    | 特長                                      | 9-1  |

| 9.2    | 入出力端子                                   | 9-3  |

| 9.3    | エリアの概要                                  | 9-4  |

| 9.3.1  | アドレスマップ                                 | 9-4  |

| 9.3.2  | 動作モードの設定                                | 9-4  |

| 9.4    | レジスタの説明                                 | 9-5  |

| 9.4.1  | 共通コントロールレジスタ(CMNCR)                     | 9-6  |

| 9.4.2  | CSn 空間バスコントロールレジスタ(CSnBCR) (n=0、1、3~6)  | 9-8  |

| 9.4.3  | CSn 空間ウェイトコントロールレジスタ(CSnWCR)(n=0、1、3~6) | 9-12 |

| 9.4.4  | バス機能拡張レジスタ(BSCEHR)                      | 9-23 |

| 9.5    | 動作説明                                    | 9-25 |

| 9.5.1  | エンディアン/アクセスサイズとデータアライメント                | 9-25 |

| 9.5.2  | 通常空間インタフェース                             | 9-28 |

| 9.5.3  | アクセスウェイト制御                              | 9-32 |

| 9.5.4  | CSn アサート期間拡張                            | 9-34 |

| 9.5.5  | MPX-I/O インタフェース                         | 9-35 |

| 9.5.6  | アクセスサイクル間アイドル                           | 9-40 |

| 9.5.7  | バスアービトレーション                             | 9-45 |

| 9.5.8  | その他                                     | 9-47 |

| 9.6    | 使用上の注意事項                                | 9-52 |

| 9.6.1  | SRAM と ASIC 等外付け LSI を接続する場合の注意事項       | 9-52 |

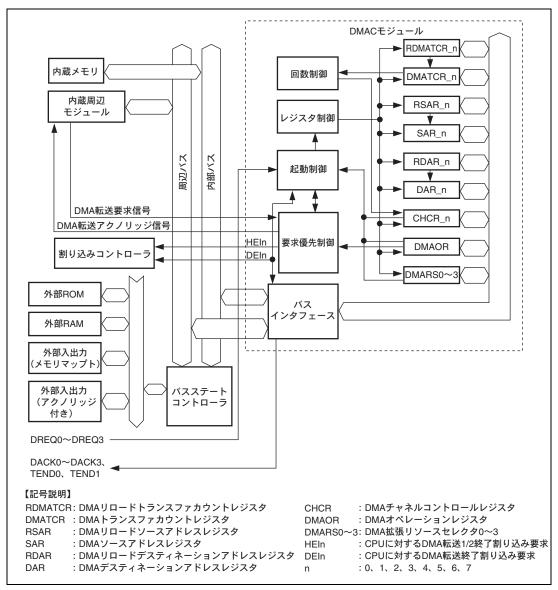

| 0. ダイ  | レクトメモリアクセスコントローラ(DMAC)                  | 10-1 |

|        | 特長                                      |      |

| 10.2   | 入出力端子                                   | 10-3 |

| 10.3   | レジスタの説明                                 | 10-4 |

| 10.3.1 | DMA ソースアドレスレジスタ(SAR)                    | 10-7 |

| 10.3.2  | DMA デスティネーションアドレスレジスタ(DAR)               | 10-8  |

|---------|------------------------------------------|-------|

| 10.3.3  | DMA トランスファカウントレジスタ(DMATCR)               | 10-8  |

| 10.3.4  | DMA チャネルコントロールレジスタ(CHCR)                 | 10-9  |

| 10.3.5  | DMA リロードソースアドレスレジスタ(RSAR)                | 10-15 |

| 10.3.6  | DMA リロードデスティネーションアドレスレジスタ(RDAR)          | 10-15 |

| 10.3.7  | DMA リロードトランスファカウントレジスタ(RDMATCR)          | 10-16 |

| 10.3.8  | DMA オペレーションレジスタ(DMAOR)                   | 10-16 |

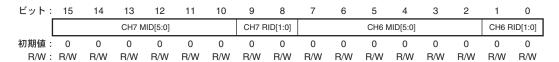

| 10.3.9  | DMA 拡張リソースセレクタ 0~3(DMARS0~DMARS3)        | 10-19 |

| 10.4    | 動作説明                                     | 10-21 |

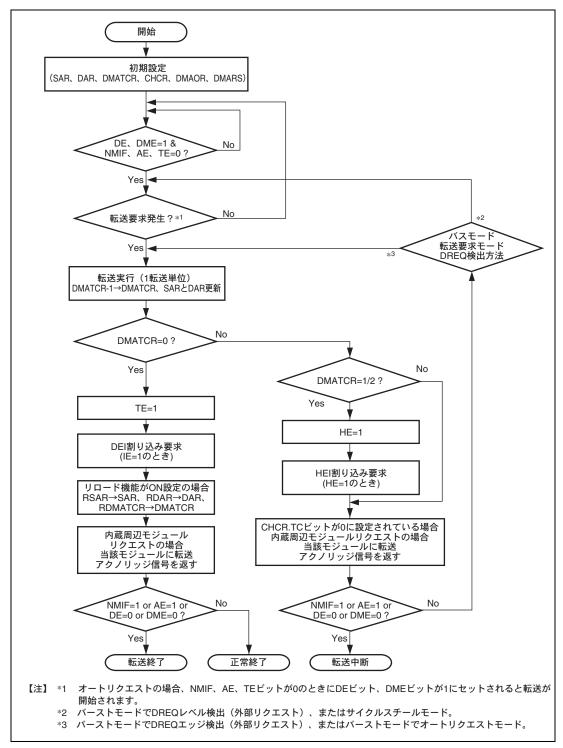

| 10.4.1  | 転送フロー                                    | 10-21 |

| 10.4.2  | DMA 転送要求                                 | 10-23 |

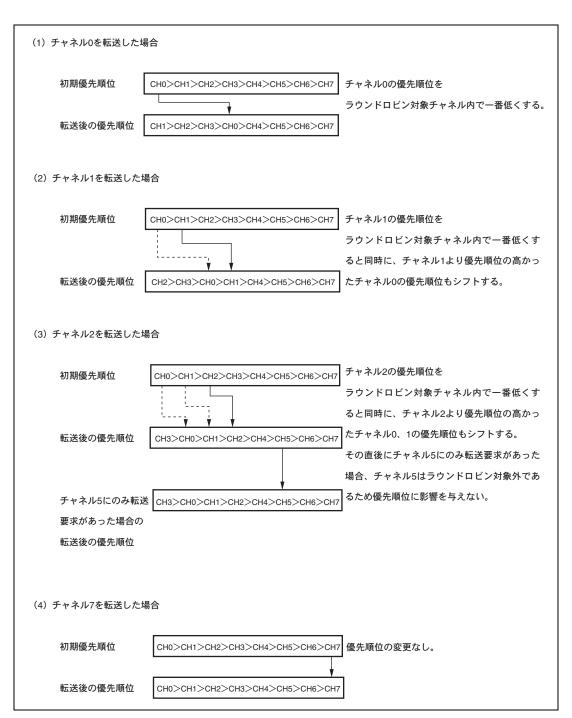

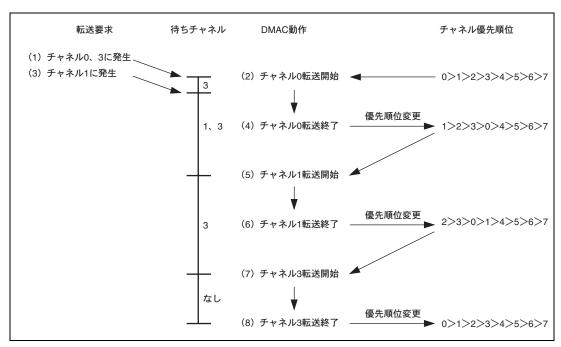

| 10.4.3  | チャネルの優先順位                                | 10-26 |

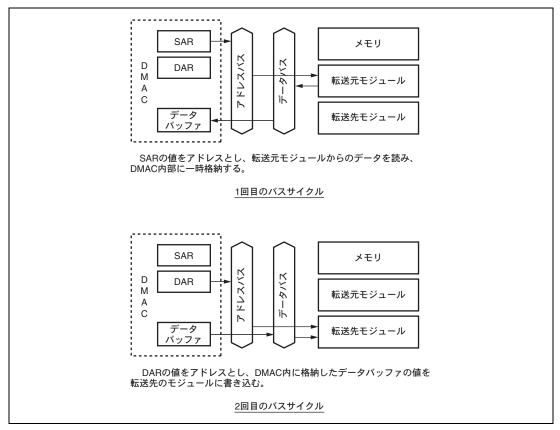

| 10.4.4  | DMA 転送の種類                                | 10-29 |

| 10.4.5  | バスサイクルのステート数と DREQ 端子のサンプリングタイミング        | 10-38 |

| 10.5    | 割り込み要因                                   | 10-41 |

| 10.5.1  | 割り込み要因と優先順位                              | 10-41 |

| 10.6    | 使用上の注意事項                                 |       |

| 10.6.1  | ハーフエンドフラグのセットおよびハーフエンド割り込み               | 10-42 |

| 10.6.2  | DACK 出力および TEND 出力のタイミング                 | 10-42 |

| 10.6.3  | CHCR の設定                                 | 10-42 |

| 10.6.4  | 複数チャネルの起動時の注意事項                          | 10-42 |

| 10.6.5  | 転送要求入力時の注意事項                             | 10-42 |

| 10.6.6  | NMI 割り込みと DMAC 起動の競合                     | 10-42 |

| 10.6.7  | DMAC からの内蔵 RAM アクセスサイクル数                 | 10-43 |

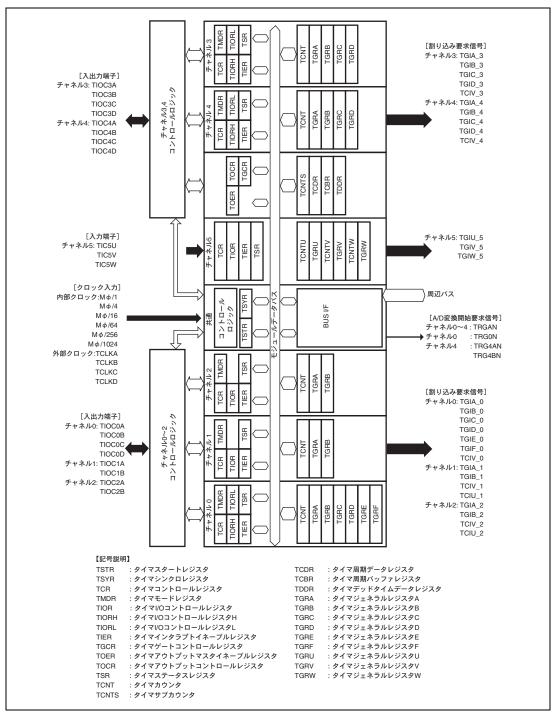

| 11. マル  | チファンクションタイマパルスユニット2 (MTU2)               | 11-1  |

| 11.1    | 特長                                       | 11-1  |

| 11.2    | 入出力端子                                    | 11-6  |

| 11.3    | レジスタの説明                                  | 11-8  |

| 11.3.1  | タイマコントロールレジスタ(TCR)                       | 11-11 |

| 11.3.2  | タイマモードレジスタ(TMDR)                         | 11-15 |

| 11.3.3  | タイマ I/O コントロールレジスタ(TIOR)                 |       |

| 11.3.4  | タイマコンペアマッチクリアレジスタ(TCNTCMPCLR)            | 11-36 |

| 11.3.5  | タイマインタラプトイネーブルレジスタ(TIER)                 | 11-37 |

| 11.3.6  | タイマステータスレジスタ(TSR)                        | 11-40 |

| 11.3.7  | タイマバッファ動作転送モードレジスタ(TBTM)                 | 11-45 |

| 11.3.8  | タイマインプットキャプチャコントロールレジスタ(TICCR)           | 11-46 |

| 11.3.9  | タイマシンクロクリアレジスタ S (TSYCRS)                | 11-47 |

| 11.3.10 | タイマ A/D 変換開始要求コントロールレジスタ(TADCR)          | 11-48 |

| 11.3.11 | タイマ A/D 変換開始要求周期設定レジスタ(TADCORA/B_4)      | 11-50 |

| 11.3.12 | タイマ A/D 変換開始要求周期設定バッファレジスタ(TADCOBRA/B_4) | 11-50 |

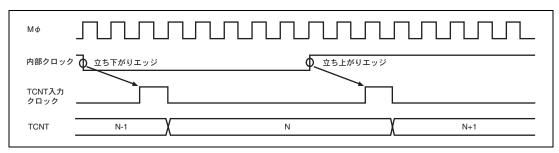

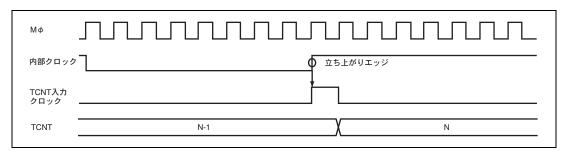

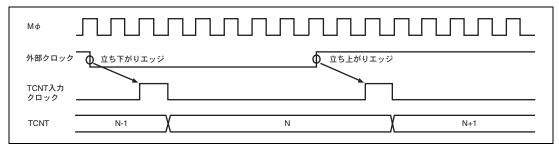

| 11.3.13 | タイマカウンタ(TCNT)                | 11-51  |

|---------|------------------------------|--------|

| 11.3.14 | タイマジェネラルレジスタ(TGR)            |        |

| 11.3.15 | タイマスタートレジスタ(TSTR)            | 11-52  |

| 11.3.16 | タイマシンクロレジスタ(TSYR)            |        |

| 11.3.17 | タイマカウンタシンクロスタートレジスタ(TCSYSTR) |        |

| 11.3.18 | タイマリードライトイネーブルレジスタ(TRWER)    |        |

| 11.3.19 | タイマアウトプットマスタイネーブルレジスタ(TOER)  |        |

| 11.3.20 | タイマアウトプットコントロールレジスタ 1(TOCR1) | 11-59  |

| 11.3.21 | タイマアウトプットコントロールレジスタ 2(TOCR2) | 11-61  |

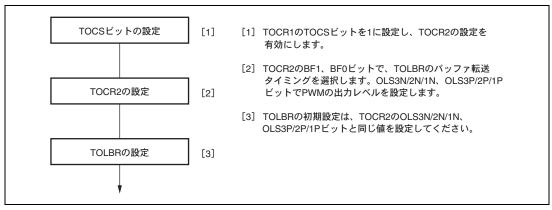

| 11.3.22 | タイマアウトプットレベルバッファレジスタ(TOLBR)  | 11-64  |

| 11.3.23 | タイマゲートコントロールレジスタ(TGCR)       | 11-65  |

| 11.3.24 | タイマサブカウンタ (TCNTS)            | 11-66  |

| 11.3.25 | タイマデッドタイムデータレジスタ(TDDR)       | 11-66  |

| 11.3.26 | タイマ周期データレジスタ(TCDR)           | 11-67  |

| 11.3.27 | タイマ周期バッファレジスタ(TCBR)          | 11-67  |

| 11.3.28 | タイマ割り込み間引き設定レジスタ(TITCR)      | 11-68  |

| 11.3.29 | タイマ割り込み間引き回数カウンタ(TITCNT)     | 11-69  |

| 11.3.30 | タイマバッファ転送設定レジスタ(TBTER)       | 11-70  |

| 11.3.31 | タイマデッドタイムイネーブルレジスタ(TDER)     | 11-71  |

| 11.3.32 | タイマ波形コントロールレジスタ(TWCR)        | 11-72  |

| 11.3.33 | バスマスタとのインタフェース               | 11-73  |

| 11.4 動  | 作説明                          | 11-74  |

| 11.4.1  | 基本動作                         | 11-74  |

| 11.4.2  | 同期動作                         | 11-80  |

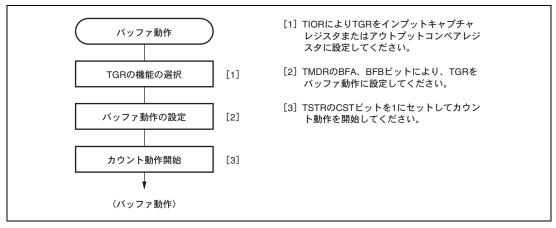

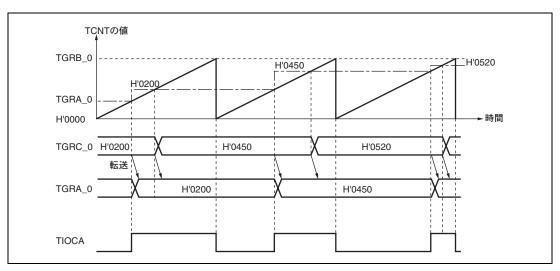

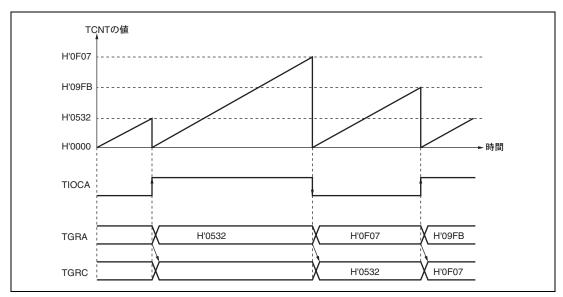

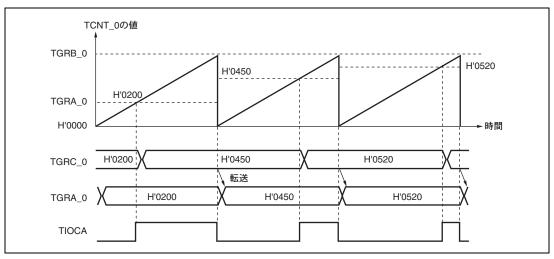

| 11.4.3  | バッファ動作                       | 11-82  |

| 11.4.4  | カスケード接続動作                    | 11-86  |

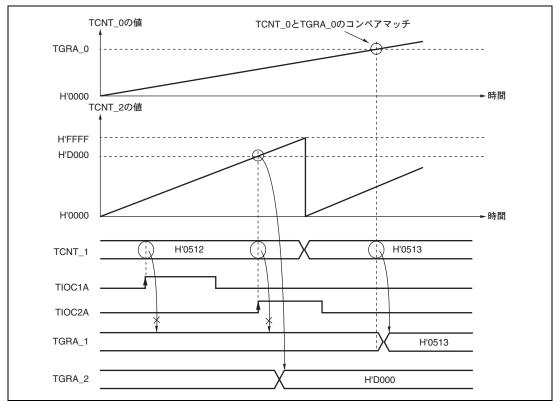

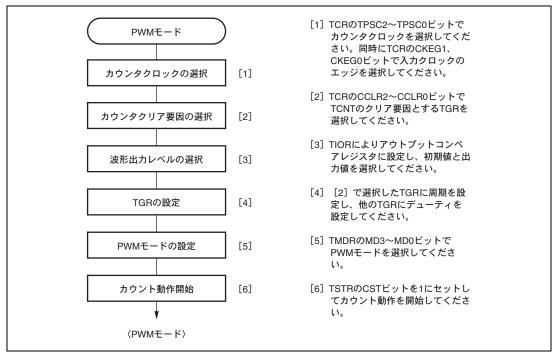

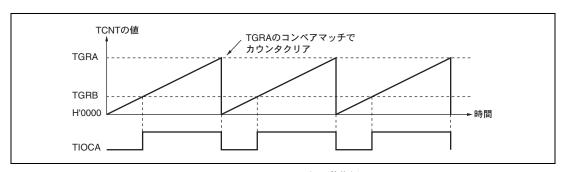

| 11.4.5  | PWM モード                      | 11-90  |

| 11.4.6  | 位相計数モード                      | 11-95  |

| 11.4.7  | リセット同期 PWM モード               | 11-101 |

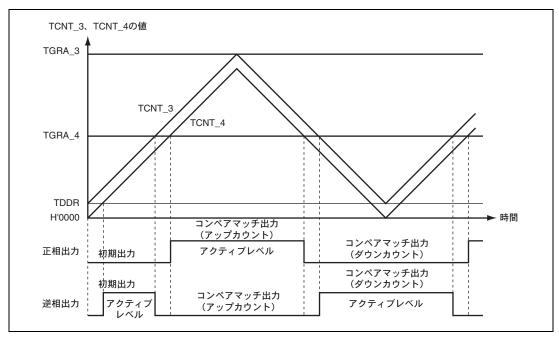

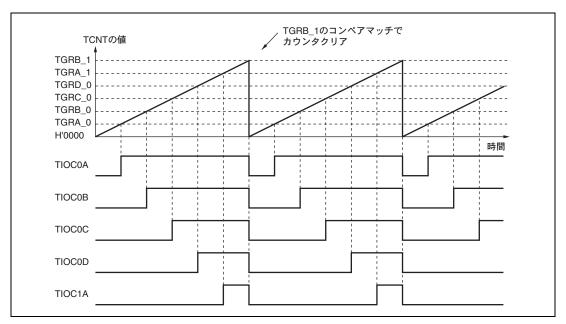

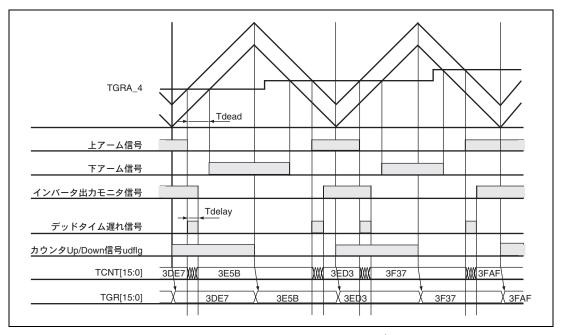

| 11.4.8  | 相補 PWM モード                   | 11-104 |

| 11.4.9  | A/D 変換開始要求ディレイド機能            | 11-141 |

| 11.4.10 | MTU2-MTU2S の同期動作             | 11-145 |

| 11.4.11 | 外部パルス幅測定機能                   | 11-148 |

| 11.4.12 | デッドタイム補償用機能                  | 11-149 |

| 11.4.13 | 相補 PWM の「山/谷」での TCNT キャプチャ動作 | 11-151 |

| 11.5 割  | り込み要因                        | 11-152 |

| 11.5.1  | 割込要因と優先順位                    | 11-152 |

| 11.5.2  | DTC/DMAC の起動                 |        |

| 11.5.3  | A/D 変換器の起動                   | 11-154 |

| 11.6 動  | 作タイミング                       | 11-156 |

| 11.6.1  | 入出力タイミング                     | 11-156 |

| 11.6.2  | 割り込み信号タイミング                                    | 11-163   |

|---------|------------------------------------------------|----------|

| 11.7    | 使用上の注意事項                                       | 11-169   |

| 11.7.1  | モジュールスタンバイモードの設定                               | 11-169   |

| 11.7.2  | 入力クロックの制限事項                                    | 11-169   |

| 11.7.3  | 周期設定上の注意事項                                     | 11-169   |

| 11.7.4  | TCNT のライトとクリアの競合                               | 11-170   |

| 11.7.5  | TCNT のライトとカウントアップの競合                           | 11-170   |

| 11.7.6  | TGR のライトとコンペアマッチの競合                            | 11-171   |

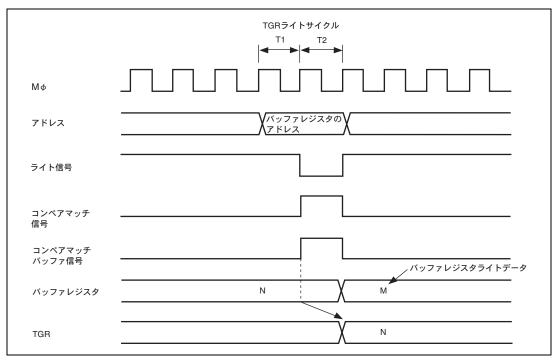

| 11.7.7  | バッファレジスタのライトとコンペアマッチの競合                        | 11-172   |

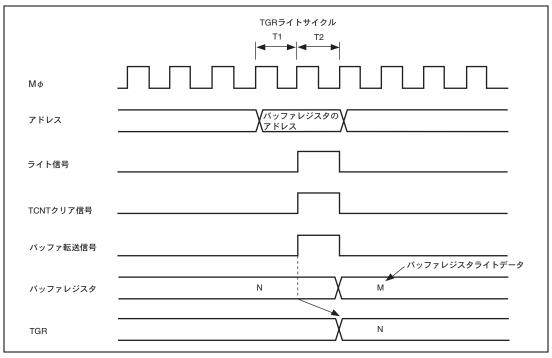

| 11.7.8  | バッファレジスタのライトと TCNT クリアの競合                      | 11-173   |

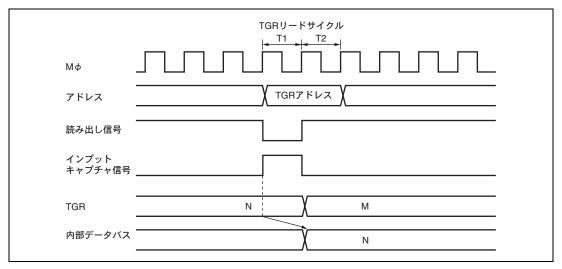

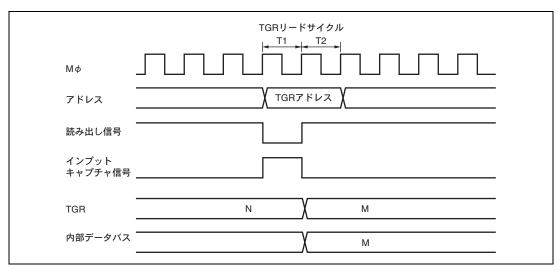

| 11.7.9  | TGR のリードとインプットキャプチャの競合                         | 11-174   |

| 11.7.10 | TGR のライトとインプットキャプチャの競合                         | 11-175   |

| 11.7.11 | バッファレジスタのライトとインプットキャプチャの競合                     | 11-176   |

| 11.7.12 | カスケード接続における TCNT_2 のライトとオーバフロー/アンダフローの 競合      | 11-176   |

| 11.7.13 | 相補 PWM モード停止時のカウンタ値                            | 11-178   |

| 11.7.14 | 相補 PWM モードでのバッファ動作の設定                          | 11-178   |

| 11.7.15 | ・・・リセット同期 PWM モードのバッファ動作とコンペアマッチフラグ            | 11-179   |

| 11.7.16 | 5 リセット同期 PWM モードのオーバフローフラグ                     | 11-180   |

| 11.7.17 | オーバフロー/アンダフローとカウンタクリアの競合                       | 11-181   |

| 11.7.18 | TCNT のライトとオーバフロー/アンダフローの競合                     | 11-181   |

| 11.7.19 | 通常動作または PWM モード 1 からリセット同期 PWM モードへ遷移する場合の注意事項 | . 11-182 |

| 11.7.20 | ー 相補 PWM モード、リセット同期 PWM モードの出力レベル              | 11-182   |

| 11.7.21 | モジュールスタンバイ時の割り込み                               | 11-182   |

| 11.7.22 | カスケード接続における TCNT_1、TCNT_2 同時インプットキャプチャ         | 11-182   |

| 11.7.23 | 相補 PWM モードでの同期カウンタクリア時出力波形制御における注意事項           | 11-183   |

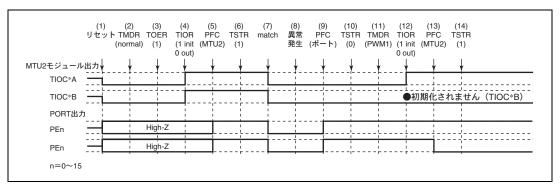

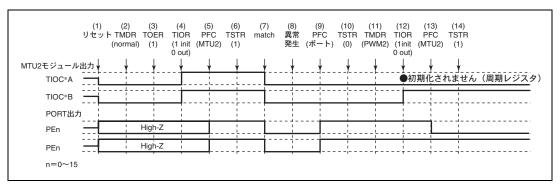

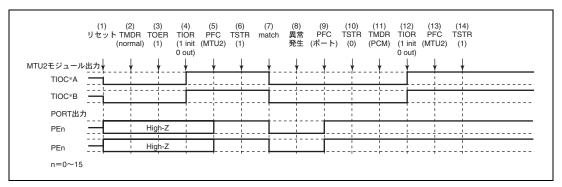

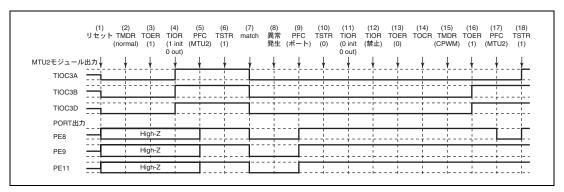

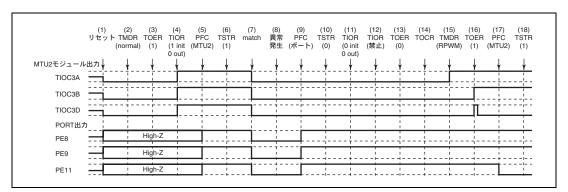

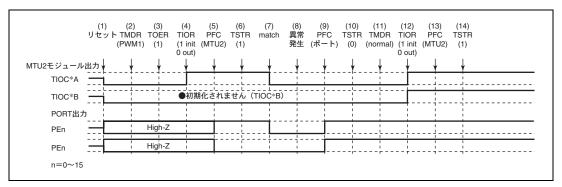

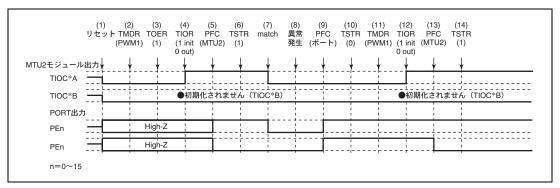

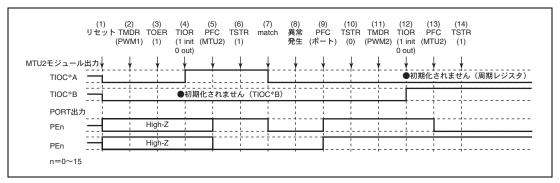

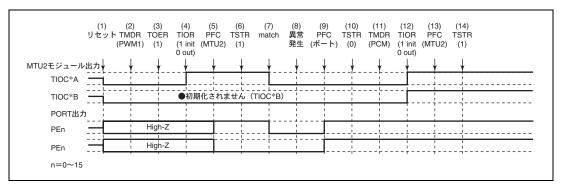

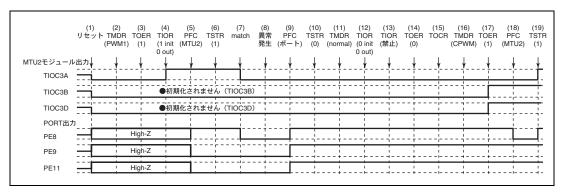

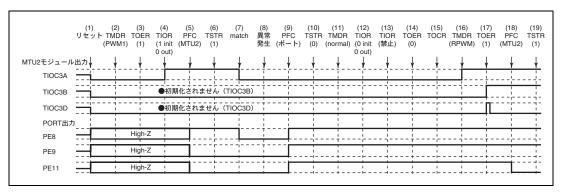

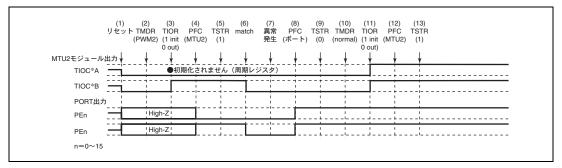

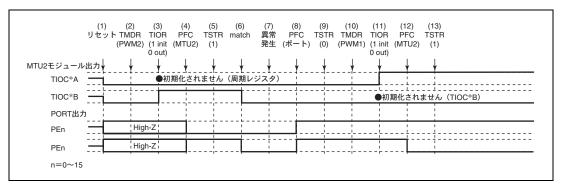

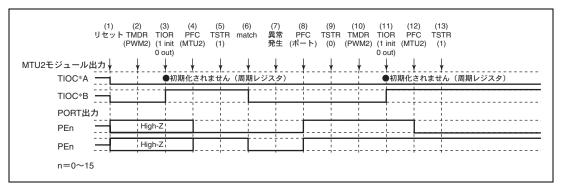

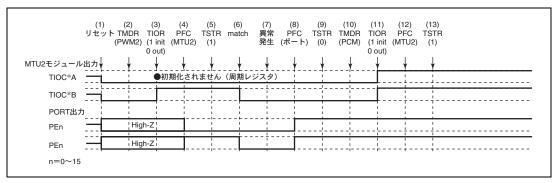

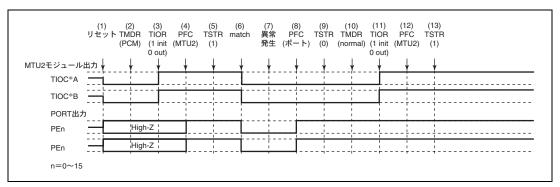

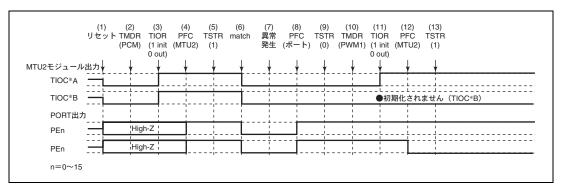

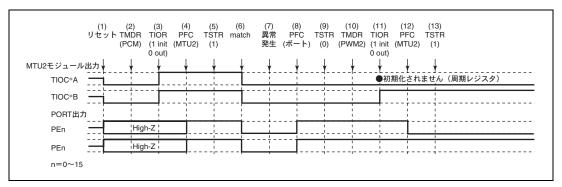

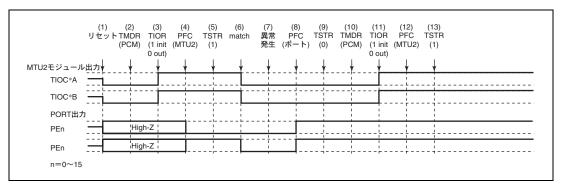

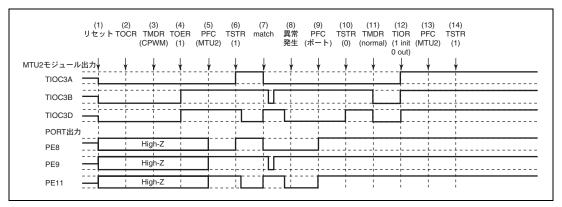

| 11.8    | MTU2出力端子の初期化方法                                 | 11-185   |

| 11.8.1  | 動作モード                                          | 11-185   |

| 11.8.2  | リセットスタート時の動作                                   | 11-185   |

| 11.8.3  | 動作中の異常などによる再設定時の動作                             | 11-186   |

| 11.8.4  | 動作中の異常などによる端子の初期化手順、モード遷移の概要                   | 11-186   |

| 12. マル  | ・チファンクションタイマパルスユニット 2S (MTU2S)                 | 12-1     |

| 12.1    | 入出力端子                                          | 12-3     |

| 12.2    | レジスタの説明                                        | 12-4     |

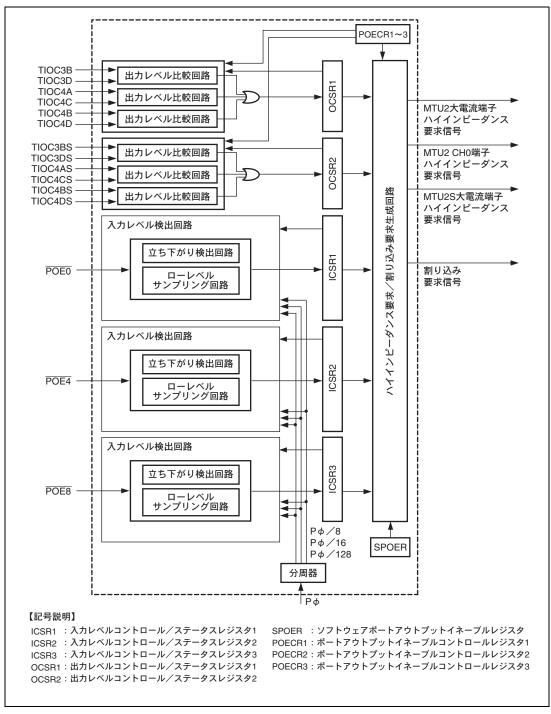

| 13. ポー  | ·トアウトプットイネーブル 2(POE2)                          | 13-1     |

| 13.1    | 特長                                             | 13-1     |

| 13.2    | 入出力端子                                          | 13-3     |

| 13.3    | レジスタの説明                                        | 13-4     |

| 13.3.1  | 入力レベルコントロール/ステータスレジスタ 1(ICSR1)                 | 13-5     |

| 13.3.2  | 出力レベルコントロール/ステータスレジスタ 1 (OCSR1)                | 13-7     |

| 13.3.3       | 入力レベルコントロール/ステータスレジスタ 2(ICSR2)     | 13-8  |

|--------------|------------------------------------|-------|

| 13.3.4       | 出力レベルコントロール/ステータスレジスタ 2 (OCSR2)    | 13-10 |

| 13.3.5       | 入力レベルコントロール/ステータスレジスタ 3(ICSR3)     | 13-11 |

| 13.3.6       | ソフトウェアポートアウトプットイネーブルレジスタ(SPOER)    | 13-12 |

| 13.3.7       | ポートアウトプットイネーブルコントロールレジスタ 1(POECR1) | 13-13 |

| 13.3.8       | ポートアウトプットイネーブルコントロールレジスタ 2(POECR2) | 13-15 |

| 13.3.9       | ポートアウトプットイネーブルコントロールレジスタ 3(POECR3) | 13-18 |

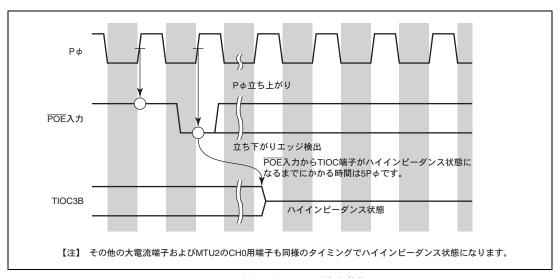

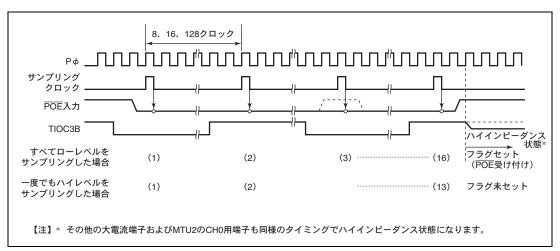

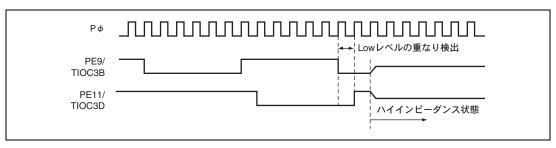

| 13.4         | 動作説明                               | 13-20 |

| 13.4.1       | 入力レベル検出動作                          | 13-21 |

| 13.4.2       | 出力レベル比較動作                          | 13-22 |

| 13.4.3       | ハイインピーダンス状態からの解除                   | 13-23 |

| 13.5         | 割り込み                               | 13-24 |

| 13.6         | 使用上の注意事項                           | 13-25 |

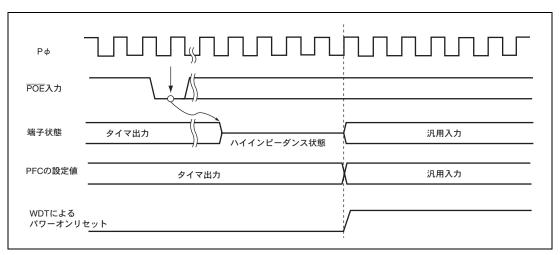

| 13.6.1       | ウォッチドッグタイマからパワーオンリセットが発行されたときの端子状態 | 13-25 |

| 13.6.2       | 入力端子について                           | 13-25 |

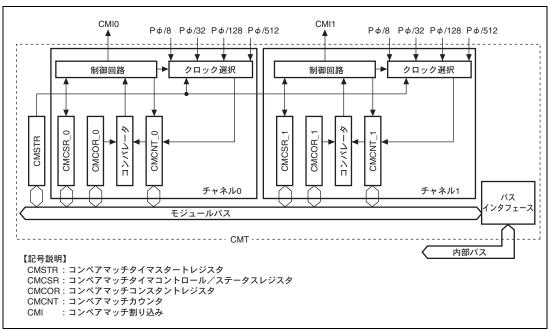

| 14. コン       | ·ペアマッチタイマ(CMT)                     | 14-1  |

| 14.1         | 特長                                 |       |

| 14.2         | レジスタの説明                            |       |

| 14.2.1       | コンペアマッチタイマスタートレジスタ (CMSTR)         |       |

| 14.2.2       | コンペアマッチタイマコントロール/ステータスレジスタ(CMCSR)  |       |

| 14.2.3       | コンペアマッチカウンタ (CMCNT)                |       |

| 14.2.4       | コンペアマッチコンスタントレジスタ (CMCOR)          |       |

| 14.3         | 動作説明                               |       |

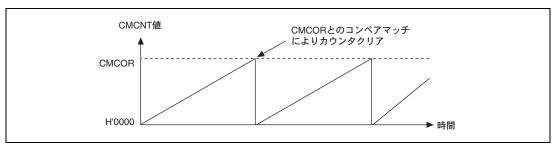

| 14.3.1       | 期間カウント動作                           |       |

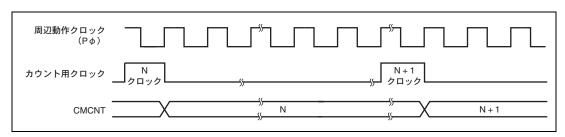

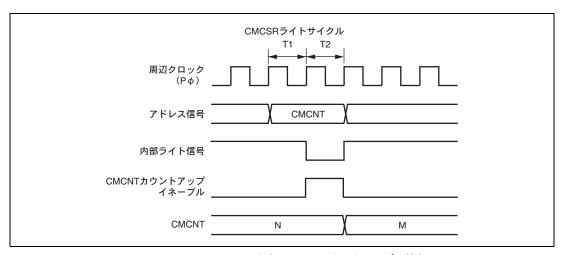

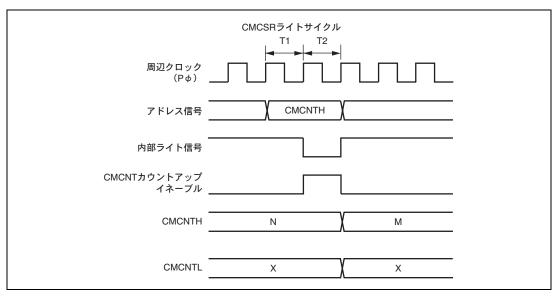

| 14.3.2       | CMCNT カウントタイミング                    | 14-5  |

| 14.4         | 割り込み                               |       |

| 14.4.1       | 割り込み要因と DTC/DMAC 転送要求              | 14-6  |

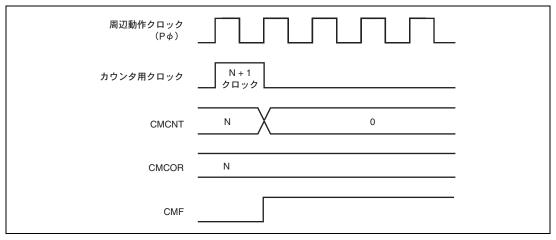

| 14.4.2       | コンペアマッチフラグのセットタイミング                | 14-7  |

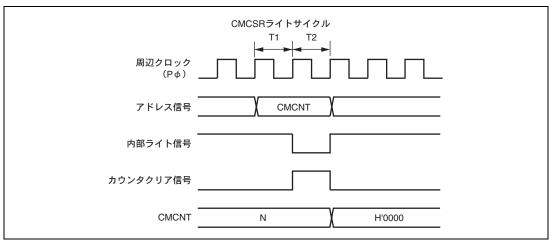

| 14.4.3       | コンペアマッチフラグのクリアタイミング                | 14-7  |

| 14.5         | 使用上の注意事項                           | 14-8  |

| 14.5.1       | CMCNT の書き込みとコンペアマッチの競合             | 14-8  |

| 14.5.2       | CMCNT のワード書き込みとカウントアップの競合          | 14-8  |

| 14.5.3       | CMCNT のバイト書き込みとカウントアップの競合          | 14-9  |

| 14.5.4       | CMCNT と CMCOR のコンペアマッチ             | 14-9  |

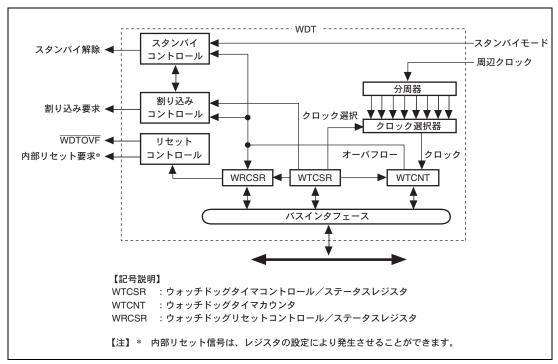

| 15. ウォ       | · ッチドッグタイマ(WDT)                    | 15_1  |

|              | 特長                                 |       |

| 15.1<br>15.2 | 入出力端子                              |       |

|              | 人 <b>ロ</b> 刀峏丁                     |       |

| 15.3         | レンスタの説明                            |       |

| 15.3.1       | フォラテドツクタイドガワマク(WICNI)              | 13-4  |

| 15.3.2  | ウォッチドッグタイマコントロール/ステータスレジスタ(WTCSR)  | 15-5  |

|---------|------------------------------------|-------|

| 15.3.3  | ウォッチドッグリセットコントロール/ステータスレジスタ(WRCSR) | 15-7  |

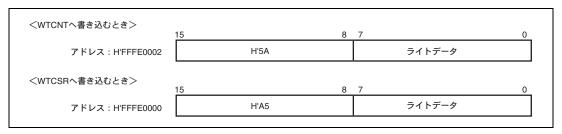

| 15.3.4  | レジスタアクセス時の注意                       | 15-8  |

| 15.4    | WDTの使用方法                           | 15-10 |

| 15.4.1  | ソフトウェアスタンバイモード解除の手順                | 15-10 |

| 15.4.2  | ウォッチドッグタイマモードの使用法                  | 15-11 |

| 15.4.3  | インターバルタイマモードの使用法                   | 15-13 |

| 15.5    | 割り込み要因                             | 15-14 |

| 15.6    | 使用上の注意事項                           | 15-15 |

| 15.6.1  | タイマ誤差                              | 15-15 |

| 15.6.2  | WTCNT の設定値として H'FF は設定禁止           | 15-15 |

| 15.6.3  | インターバルタイマオーバフローフラグ                 | 15-15 |

| 15.6.4  | WDTOVF 信号によるシステムリセット               | 15-15 |

| 15.6.5  | ウォッチドッグタイマモードのマニュアルリセット            | 15-16 |

| 15.6.6  | WDTOVF 信号の接続について                   | 15-16 |

| 40      | 1711-2                             | 10.1  |

| 16. ンり  | リアルコミュニケーションインタフェース (SCI)          |       |

| 16.1    | 特長                                 | 16-1  |

| 16.2    | 入出力端子                              |       |

| 16.3    | レジスタの説明                            | 16-5  |

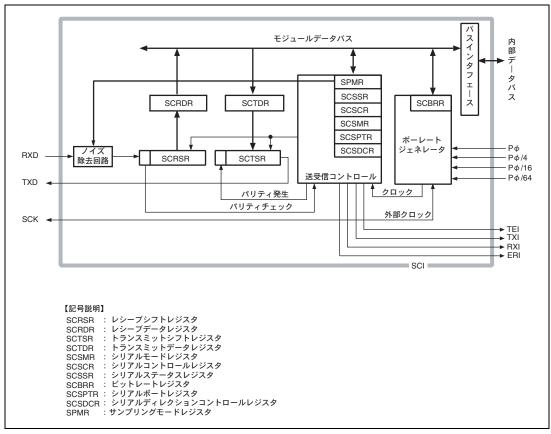

| 16.3.1  | レシーブシフトレジスタ(SCRSR)                 | 16-6  |

| 16.3.2  | レシーブデータレジスタ(SCRDR)                 | 16-6  |

| 16.3.3  | トランスミットシフトレジスタ(SCTSR)              | 16-6  |

| 16.3.4  | トランスミットデータレジスタ(SCTDR)              | 16-7  |

| 16.3.5  | シリアルモードレジスタ(SCSMR)                 | 16-7  |

| 16.3.6  | シリアルコントロールレジスタ(SCSCR)              | 16-9  |

| 16.3.7  | シリアルステータスレジスタ(SCSSR)               | 16-12 |

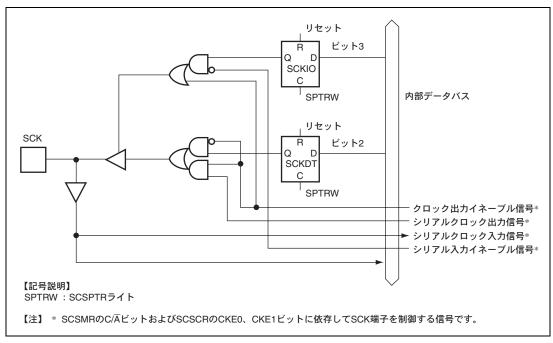

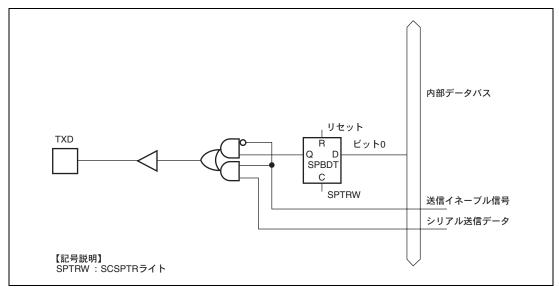

| 16.3.8  | シリアルポートレジスタ(SCSPTR)                | 16-16 |

| 16.3.9  | シリアルディレクションコントロールレジスタ(SCSDCR)      | 16-17 |

| 16.3.10 | ) ビットレートレジスタ(SCBRR)                | 16-18 |

| 16.3.1  |                                    |       |

| 16.4    | 動作説明                               | 16-28 |

| 16.4.1  | 概要                                 | 16-28 |

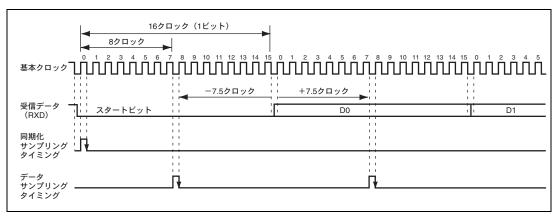

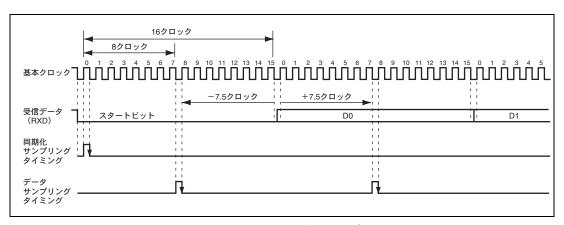

| 16.4.2  | 調歩同期式モード時の動作                       | 16-30 |

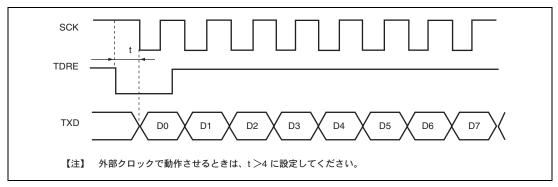

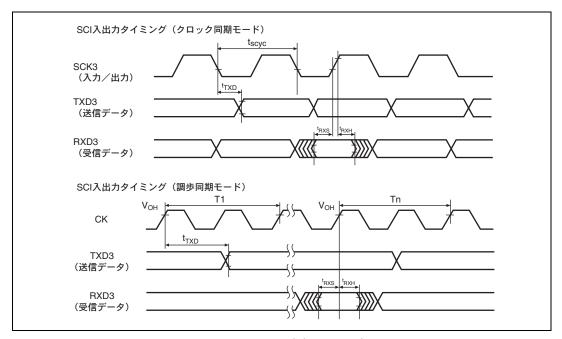

| 16.4.3  | クロック同期式モード時の動作                     | 16-39 |

| 16.4.4  | マルチプロセッサ通信機能                       |       |

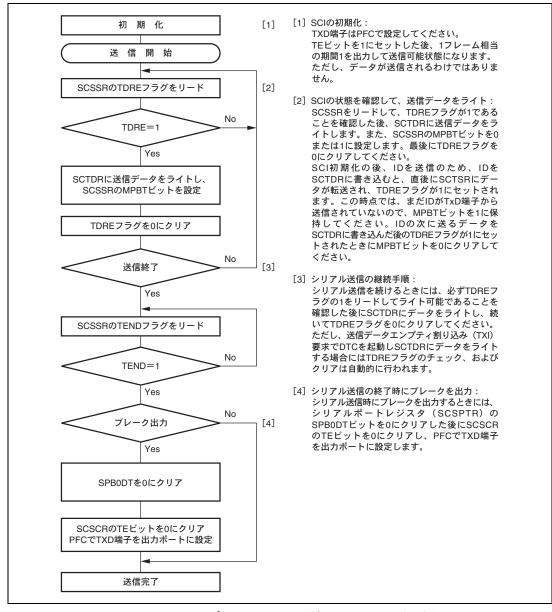

| 16.4.5  | マルチプロセッサシリアルデータ送信                  |       |

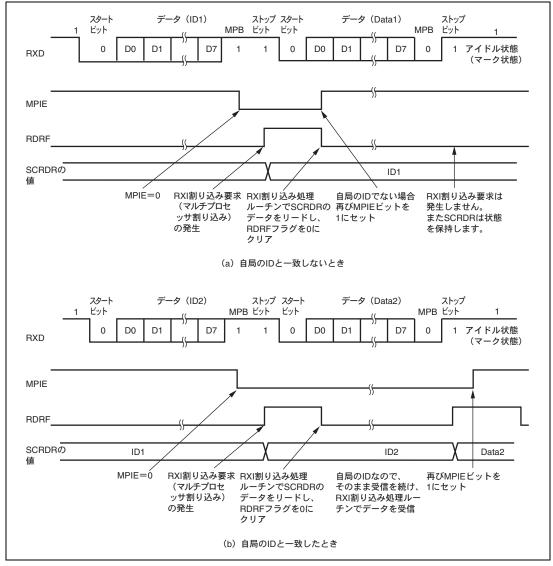

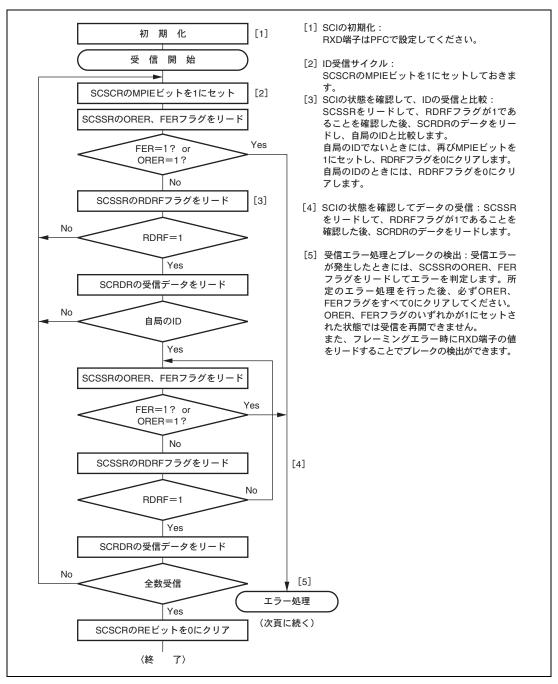

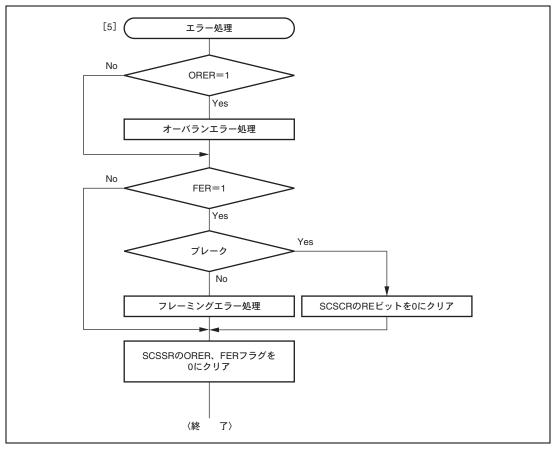

| 16.4.6  | マルチプロセッサシリアルデータ受信                  | 16-50 |

| 16.5    | SCIの割り込み要因とDTC                     | 16-53 |

| 16.6    | シリアルポートレジスタ(SCSPTR)とSCI端子との関係      | 16-54 |

| 16.7    | 使用上の注意事項                           | 16-55 |

| 16.7.1  | SCTDR への書き込みと TDRE フラグの関係について                | 16-55 |

|---------|----------------------------------------------|-------|

| 16.7.2  | 複数の受信エラーが同時に発生した場合の動作について                    | 16-55 |

| 16.7.3  | ブレークの検出と処理について                               | 16-56 |

| 16.7.4  | ブレークの送り出し                                    | 16-56 |

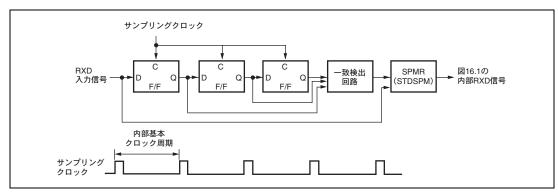

| 16.7.5  | 調歩同期式モードの受信データサンプリングタイミングと受信マージン             | 16-56 |

| 16.7.6  | DTC 使用上の注意事項                                 | 16-57 |

| 16.7.7  | クロック同期外部クロックモード時の注意事項                        | 16-58 |

| 16.7.8  | モジュールスタンバイモードの設定                             | 16-58 |

| 16.7.9  | RE ビットをセットする際の RXD 端子の状態についての注意事項            | 16-58 |

| 16.7.1  | 0 割り込みフラグのクリアについての注意事項                       | 16-58 |

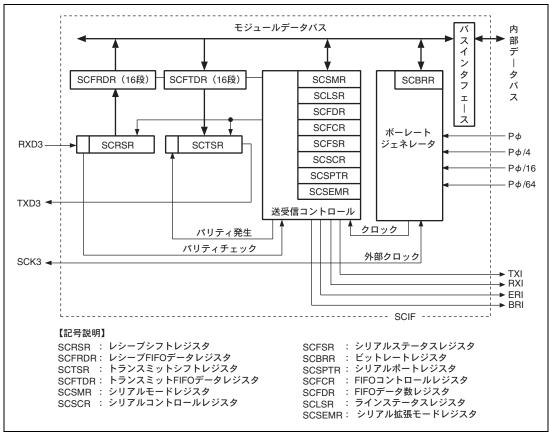

| 17. FIF | O 内蔵シリアルコミュニケーション インタフェース(SCIF)              | 17-1  |

| 17.1    | 特長                                           | 17-1  |

| 17.2    | 入出力端子                                        | 17-3  |

| 17.3    | レジスタの説明                                      | 17-3  |

| 17.3.1  | レシーブシフトレジスタ(SCRSR)                           | 17-4  |

| 17.3.2  | レシーブ FIFO データレジスタ(SCFRDR)                    | 17-4  |

| 17.3.3  | トランスミットシフトレジスタ(SCTSR)                        | 17-4  |

| 17.3.4  | トランスミット FIFO データレジスタ(SCFTDR)                 | 17-5  |

| 17.3.5  | シリアルモードレジスタ(SCSMR)                           | 17-5  |

| 17.3.6  | シリアルコントロールレジスタ(SCSCR)                        | 17-8  |

| 17.3.7  | シリアルステータスレジスタ(SCFSR)                         | 17-11 |

| 17.3.8  | ビットレートレジスタ (SCBRR)                           | 17-16 |

| 17.3.9  | FIFO コントロールレジスタ(SCFCR)                       | 17-25 |

| 17.3.1  | 0 FIFO データ数レジスタ(SCFDR)                       | 17-27 |

| 17.3.1  | 1 シリアルポートレジスタ(SCSPTR)                        | 17-28 |

| 17.3.1  | 2 ラインステータスレジスタ(SCLSR)                        | 17-29 |

| 17.3.1  | 3 シリアル拡張モードレジスタ(SCSEMR)                      | 17-30 |

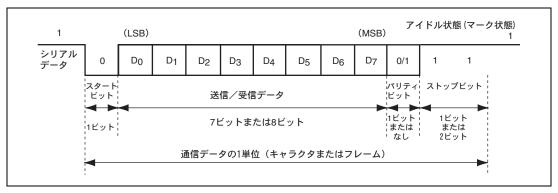

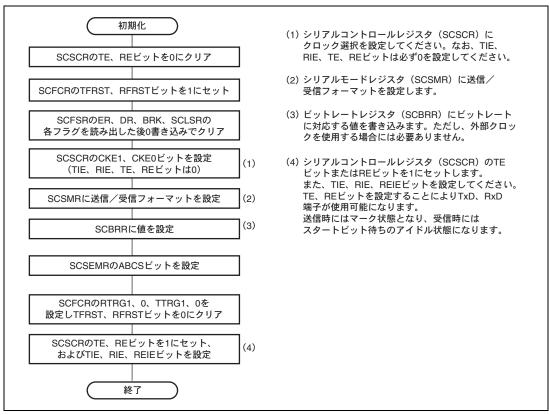

| 17.4    | 動作説明                                         | 17-31 |

| 17.4.1  | 概要                                           | 17-31 |

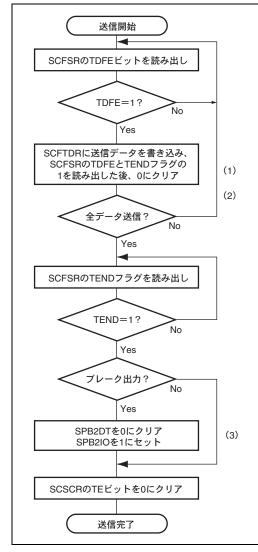

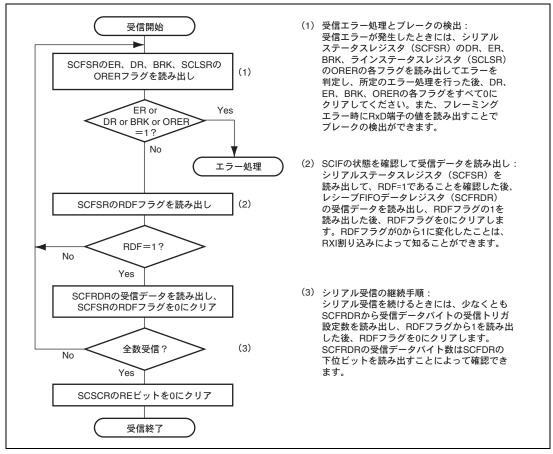

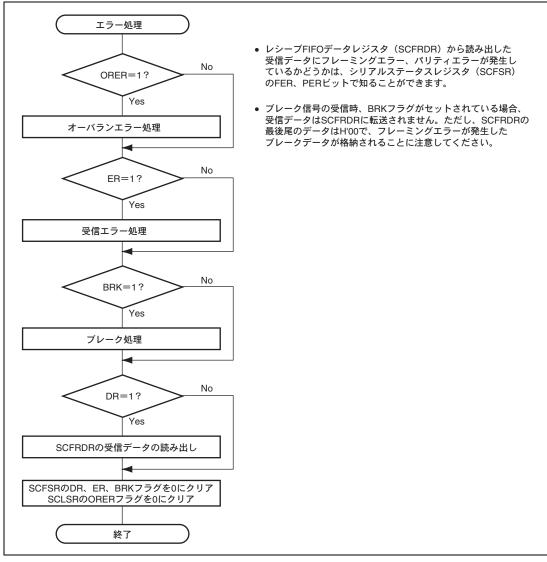

| 17.4.2  | 調歩同期式モード時の動作                                 | 17-33 |

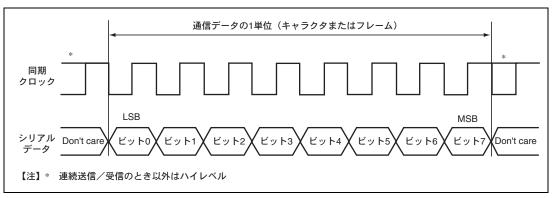

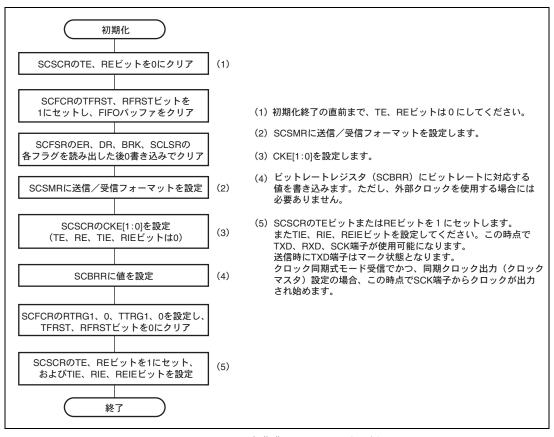

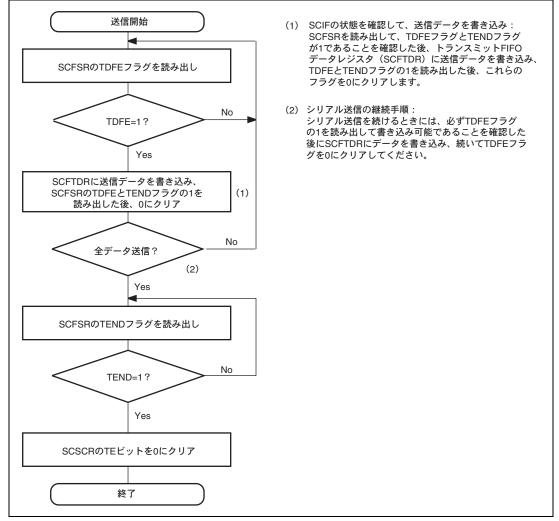

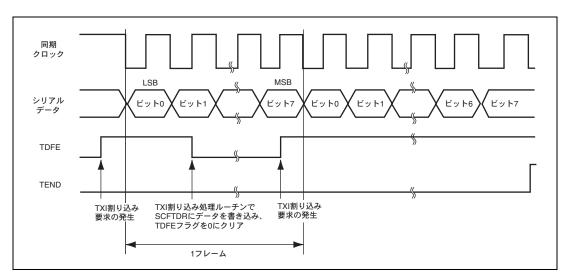

| 17.4.3  | クロック同期式モード時の動作                               | 17-41 |

| 17.5    | SCIFの割り込み                                    | 17-48 |

| 17.6    | 使用上の注意事項                                     | 17-49 |

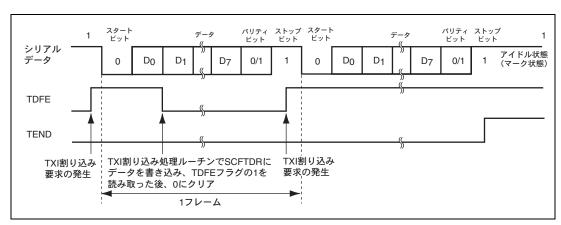

| 17.6.1  | SCFTDR への書き込みと TDFE フラグ                      | 17-49 |

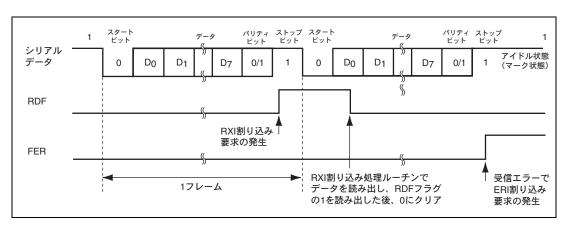

| 17.6.2  | SCFRDR の読み出しと RDF フラグ                        | 17-49 |

| 17.6.3  | DMAC/DTC 使用上の制約事項                            | 17-49 |

| 17.6.4  | ブレークの検出と処理                                   | 17-49 |

| 17.6.5  | ブレークの送り出し                                    | 17-50 |

| 17.6.6  | 調歩同期式モードの受信データサンプリングタイミングと受信マージン             | 17-50 |

| 17.6.7  | シリアルステータスレジスタ(SCFSR)の FER フラグおよび PER フラグについて | 17-51 |

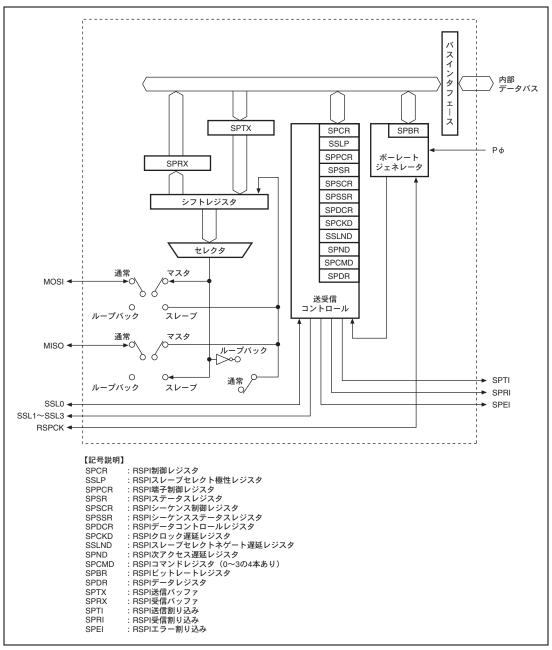

| 18. ルネサ | スシリアルペリフェラルインタフェース (RSPI)      | 18-1  |

|---------|--------------------------------|-------|

| 18.1 特  | ·E                             |       |

| 18.1.1  | 内部ブロック図                        |       |

| 18.2 入  | 、出力端子                          |       |

| 18.3 V  | · ジスタの説明                       | 18-5  |

| 18.3.1  | RSPI 制御レジスタ(SPCR)              | 18-6  |

| 18.3.2  | RSPI スレーブセレクト極性レジスタ(SSLP)      | 18-8  |

| 18.3.3  | RSPI 端子制御レジスタ(SPPCR)           | 18-9  |

| 18.3.4  | RSPI ステータスレジスタ(SPSR)           | 18-10 |

| 18.3.5  | RSPI データレジスタ(SPDR)             | 18-13 |

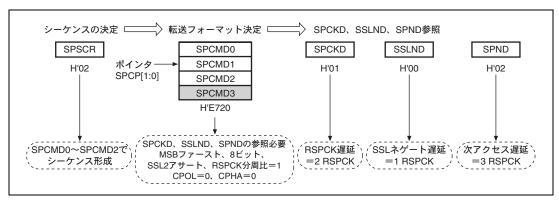

| 18.3.6  | RSPI シーケンス制御レジスタ(SPSCR)        | 18-14 |

| 18.3.7  | RSPI シーケンスステータスレジスタ(SPSSR)     | 18-15 |

| 18.3.8  | RSPI ビットレートレジスタ(SPBR)          | 18-16 |

| 18.3.9  | RSPI データコントロールレジスタ(SPDCR)      | 18-17 |

| 18.3.10 | RSPCK 遅延レジスタ(SPCKD)            | 18-20 |

| 18.3.11 | RSPI スレーブセレクトネゲート遅延レジスタ(SSLND) | 18-21 |

| 18.3.12 | RSPI 次アクセス遅延レジスタ(SPND)         | 18-22 |

| 18.3.13 | RSPI コマンドレジスタ(SPCMD)           | 18-23 |

| 18.4 動  | h作説明                           | 18-26 |

| 18.4.1  | RSPI 動作の概要                     | 18-26 |

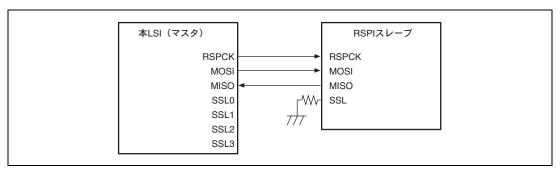

| 18.4.2  | RSPI 端子の制御                     | 18-27 |

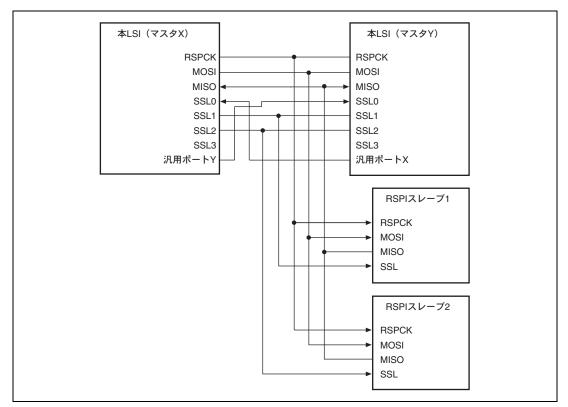

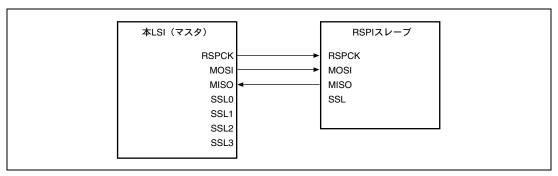

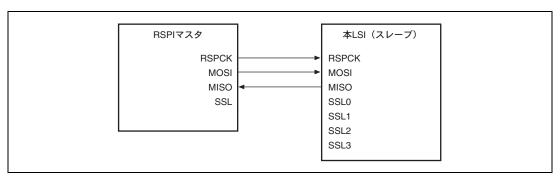

| 18.4.3  | RSPI システム構成例                   | 18-29 |

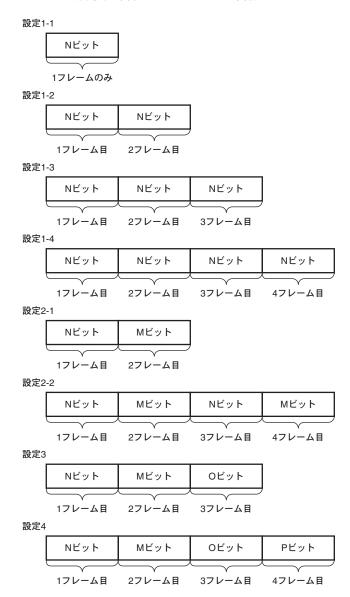

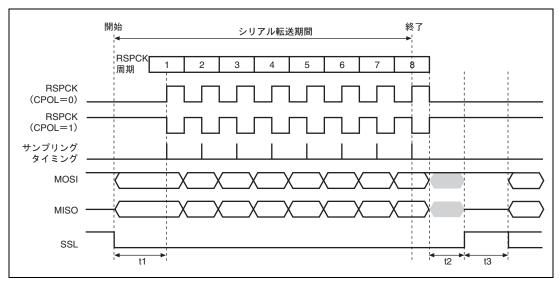

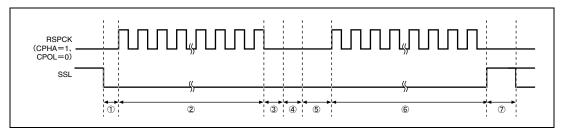

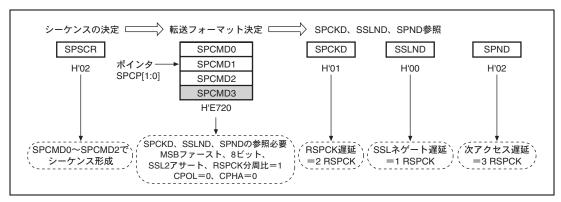

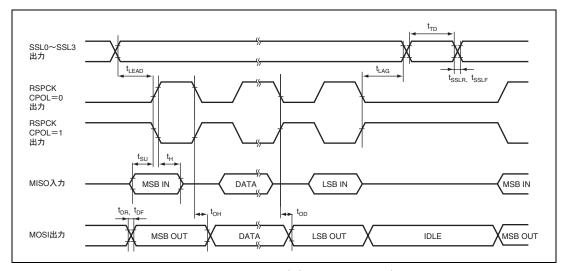

| 18.4.4  | 転送フォーマット                       | 18-35 |

| 18.4.5  | データフォーマット                      | 18-37 |

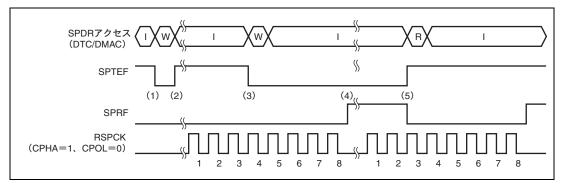

| 18.4.6  | 送信バッファエンプティ/受信バッファフルフラグ        | 18-41 |

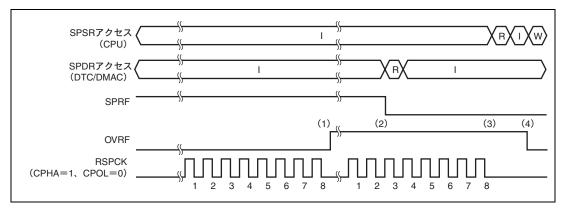

| 18.4.7  | エラー検出                          | 18-43 |

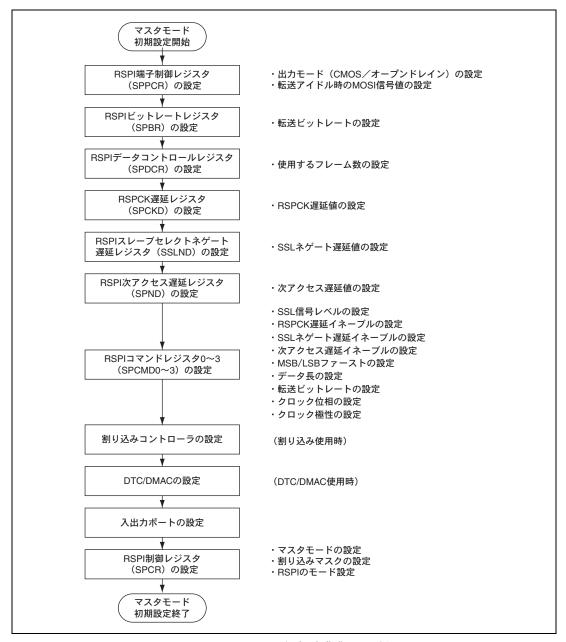

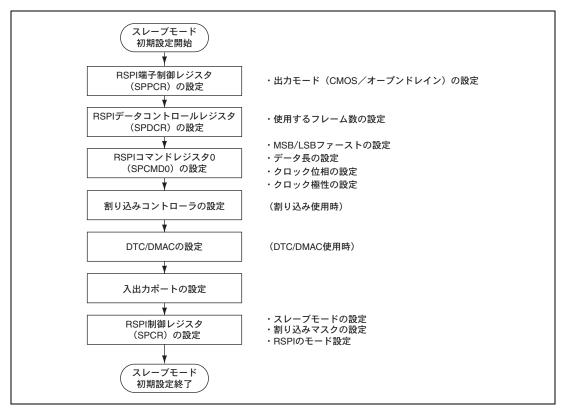

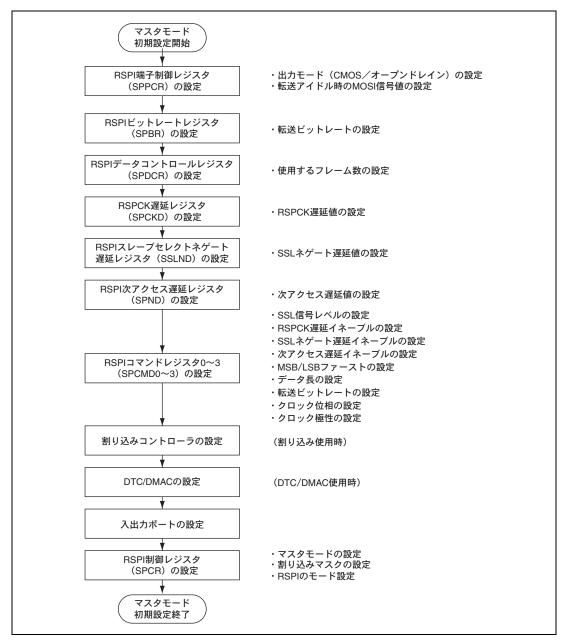

| 18.4.8  | RSPI の初期化                      | 18-46 |

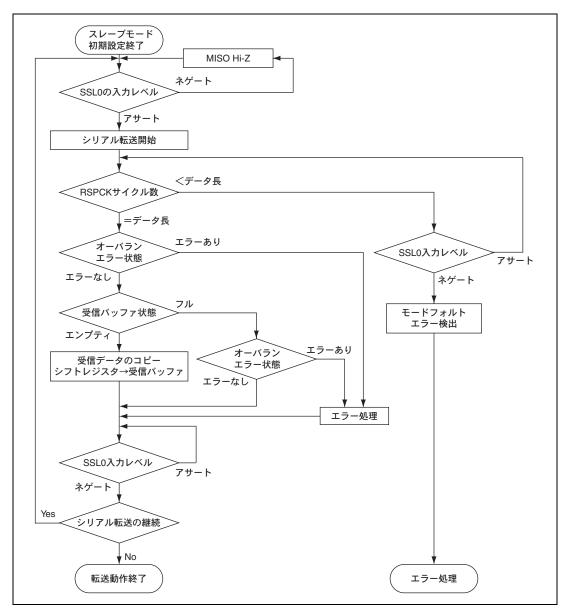

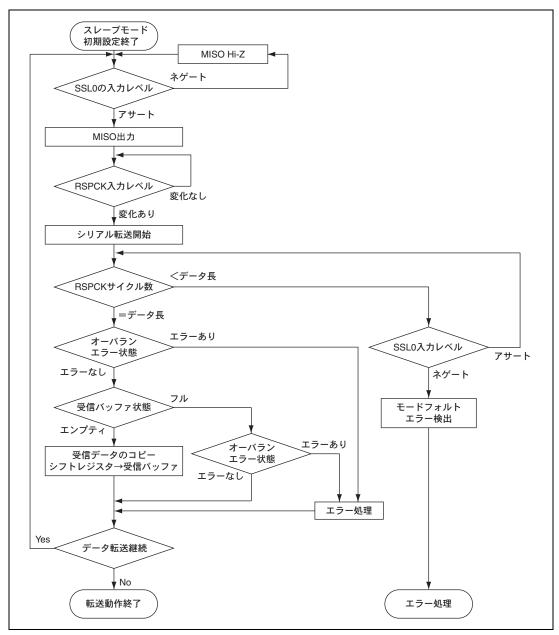

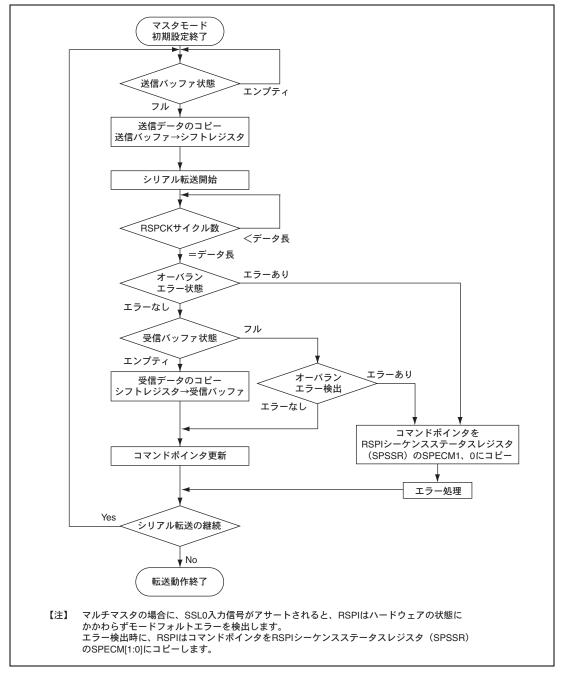

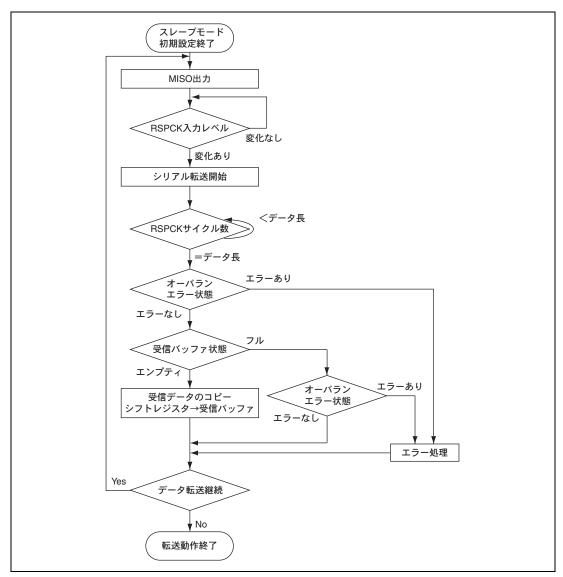

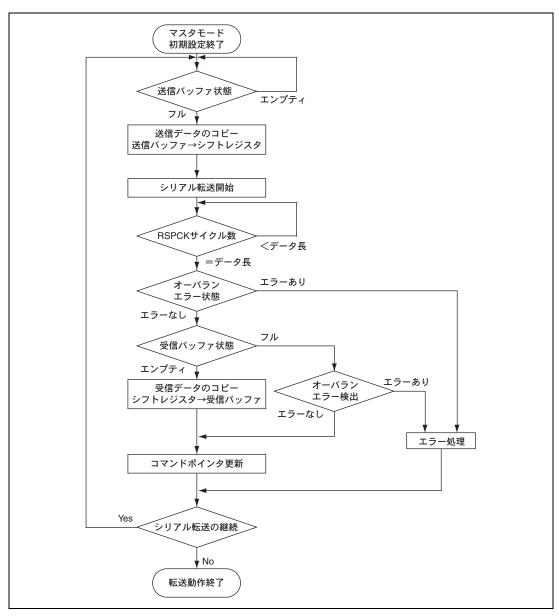

| 18.4.9  | SPI 動作                         | 18-47 |

| 18.4.10 | クロック同期式動作                      | 18-58 |

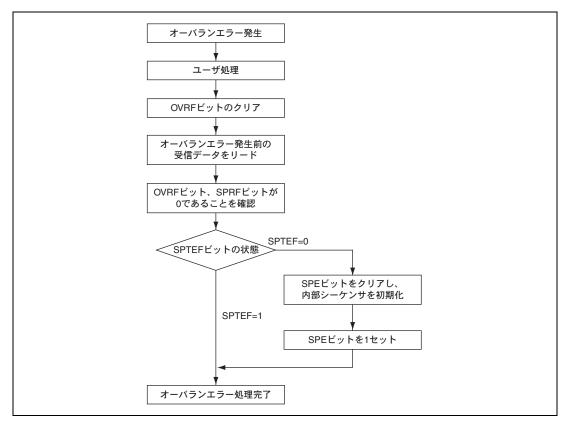

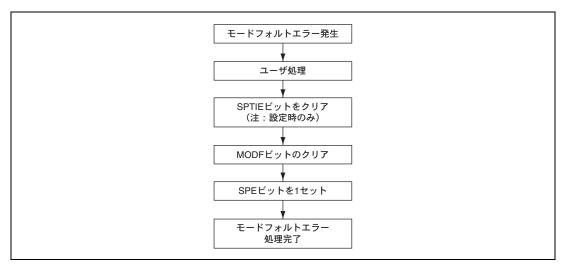

| 18.4.11 | エラー処理                          | 18-65 |

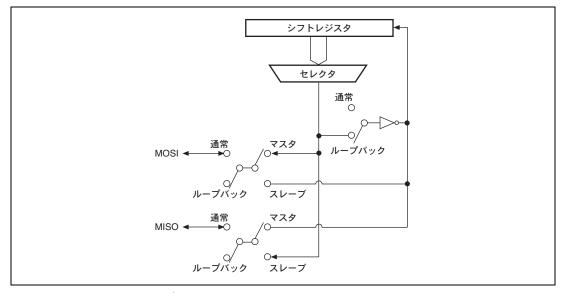

| 18.4.12 | ループバックモード                      | 18-67 |

| 18.4.13 | 割り込み要求                         | 18-68 |

| 18.5 使  | 5用上の注意                         |       |

| 18.5.1  | DTC ブロック転送                     | 18-69 |

| 18.5.2  | DMAC バースト転送                    | 18-69 |

| 18.5.3  | 受信データ読み出し                      |       |

| 18.5.4  | DTC/DMAC とモードフォルトエラーについて       | 18-69 |

| 18.5.5  | 出力をオープンドレインとして使用する場合           |       |

| 18.5.6  | スレーブモード時に端子を使用しない場合            | 18-69 |

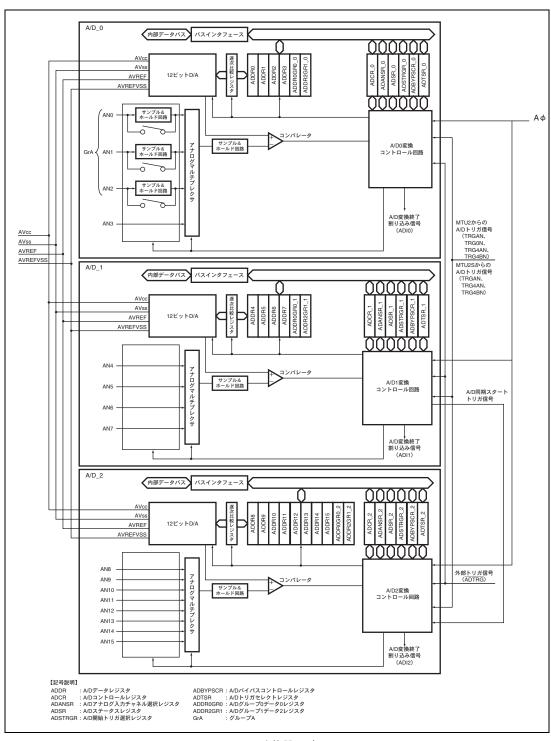

| 19. A/D | 変換器(ADC)                                     | 19-1  |

|---------|----------------------------------------------|-------|

| 19.1    | 特長                                           | 19-1  |

| 19.2    | 入出力端子                                        | 19-4  |

| 19.3    | レジスタの説明                                      | 19-5  |

| 19.3.1  | A/D コントロールレジスタ(ADCR_0~ADCR_2)                | 19-7  |

| 19.3.2  | A/D ステータスレジスタ(ADSR_0~ADSR_2)                 | 19-9  |

| 19.3.3  | A/D 開始トリガ選択レジスタ(ADSTRGR_0~ADSTRGR_2)         | 19-10 |

| 19.3.4  | A/D アナログ入力チャネル選択レジスタ(ADANSR_0~ADANSR_2)      | 19-11 |

| 19.3.5  | A/D バイパスコントロールレジスタ(ADBYPSCR_0~ADBYPSCR_2)    | 19-12 |

| 19.3.6  | A/D データレジスタ 0~15(ADDR0~ADDR15)               | 19-13 |

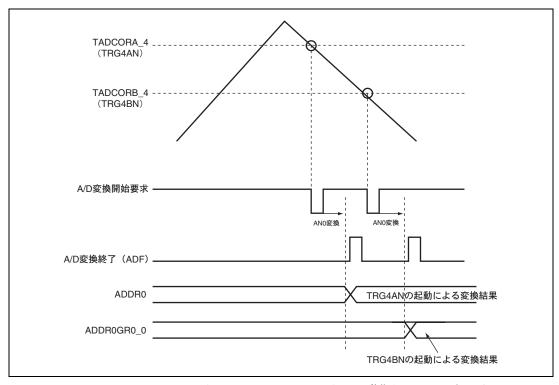

| 19.3.7  | A/D トリガセレクトレジスタ(ADTSR_0~ADTSR_2)             | 19-14 |

| 19.3.8  | A/D グループ 0 データ 0 レジスタ(ADDR0GR0_0~ADDR0GR0_2) | 19-17 |

| 19.3.9  | A/D グループ 1 データ 2 レジスタ(ADDR2GR1_0~ADDR2GR1_2) | 19-17 |

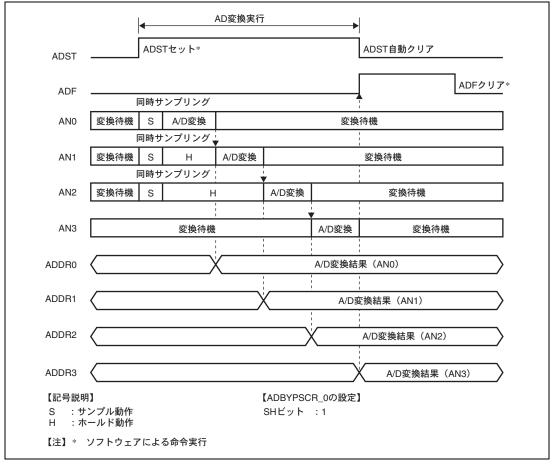

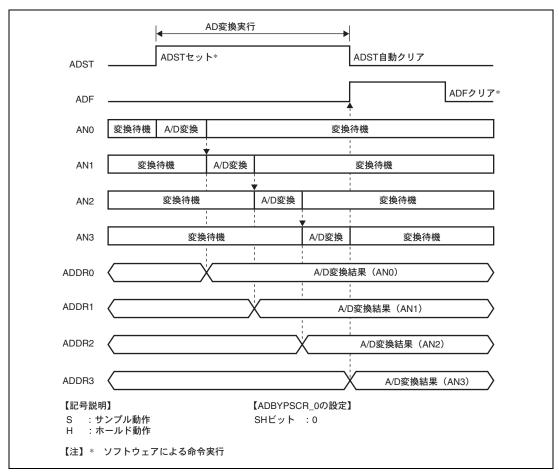

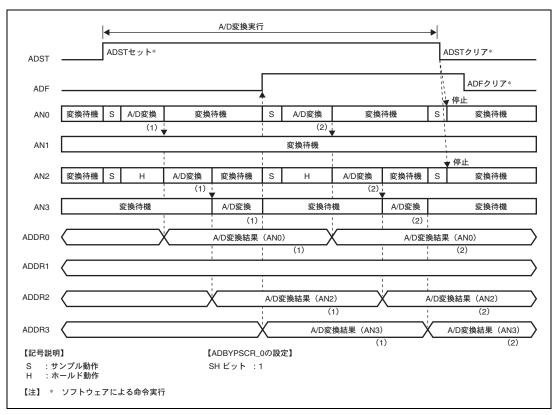

| 19.4    | 動作説明                                         | 19-18 |

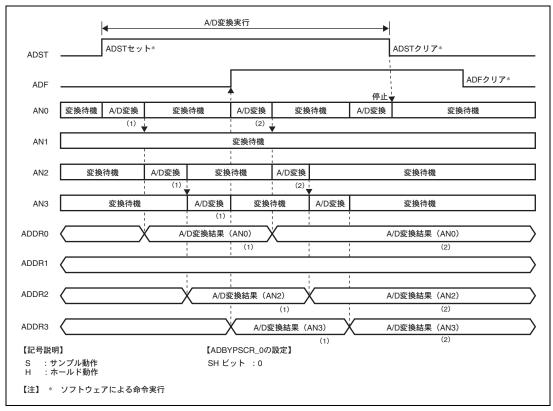

| 19.4.1  | 1 サイクルスキャンモード                                | 19-19 |

| 19.4.2  | 連続スキャンモード                                    | 19-22 |

| 19.4.3  | 2 チャネルスキャンモード                                | 19-25 |

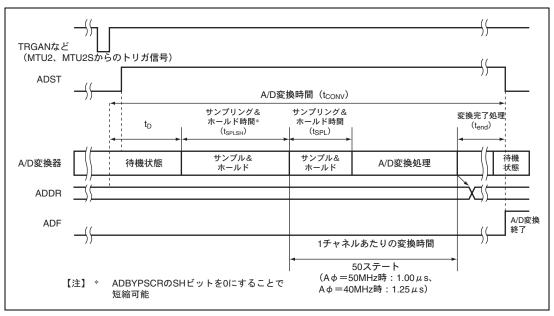

| 19.4.4  | 入力サンプリングと A/D 変換時間                           | 19-28 |

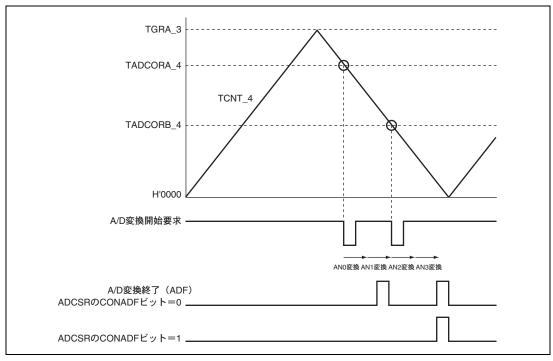

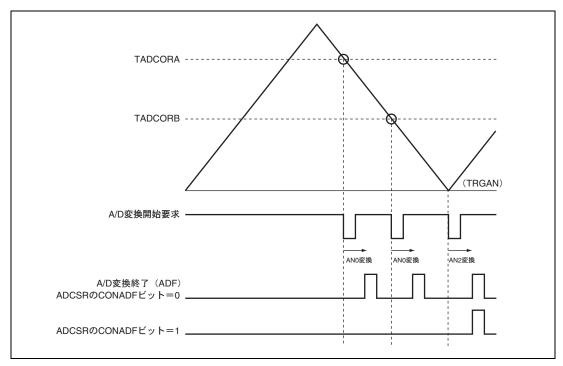

| 19.4.5  | MTU2、MTU2S による A/D 変換器の起動                    | 19-30 |

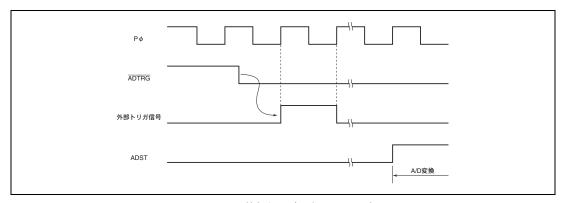

| 19.4.6  | 外部トリガ入カタイミング                                 | 19-30 |

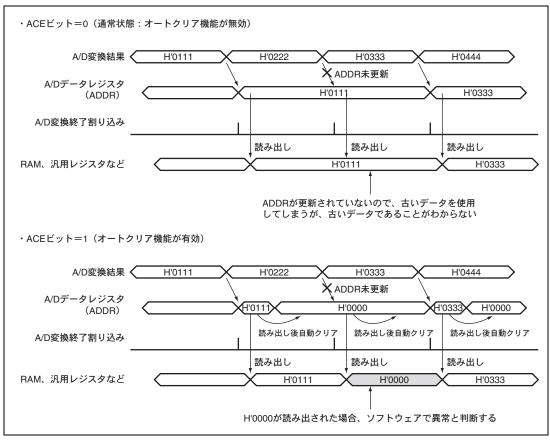

| 19.4.7  | ADDR レジスタのオートクリア機能の使用例                       | 19-31 |

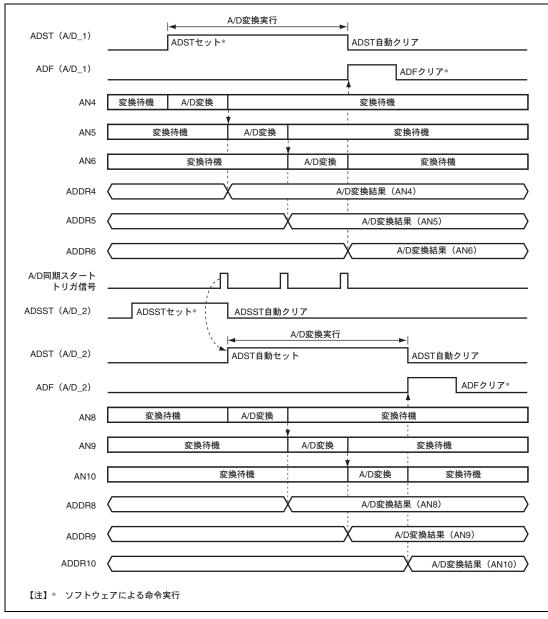

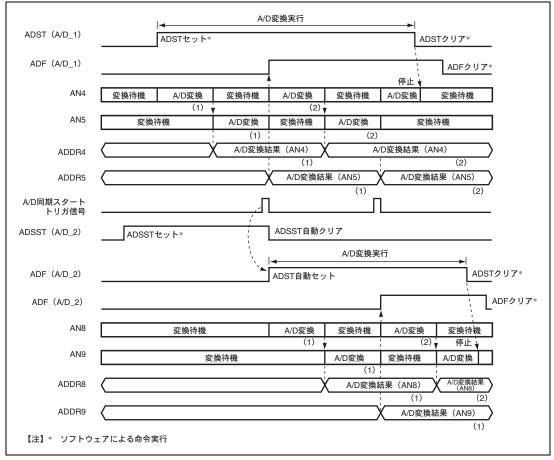

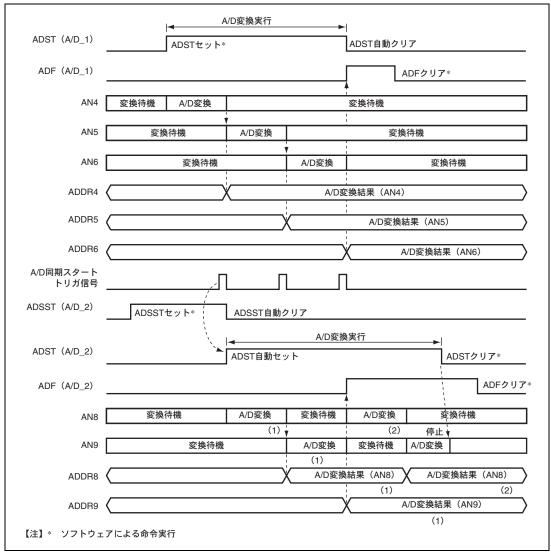

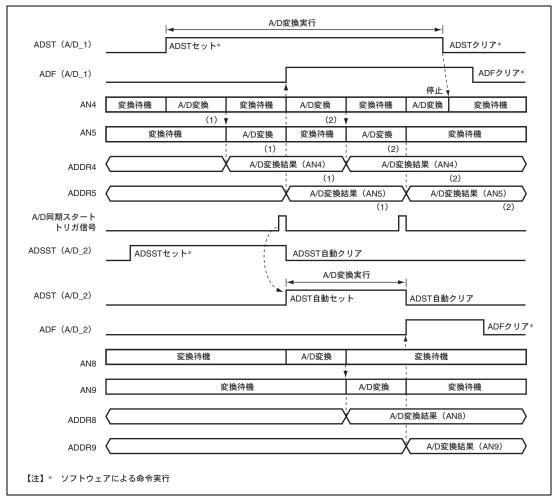

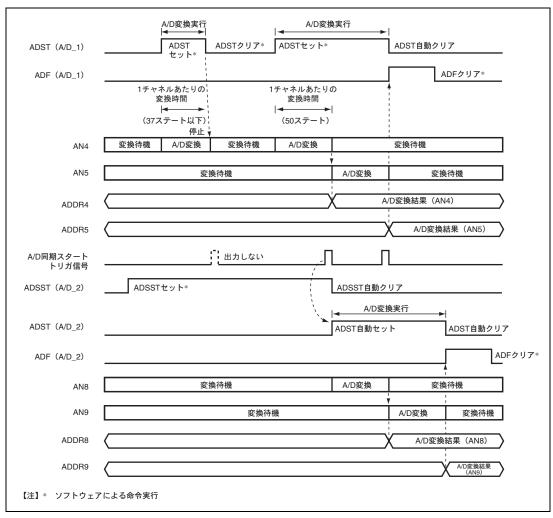

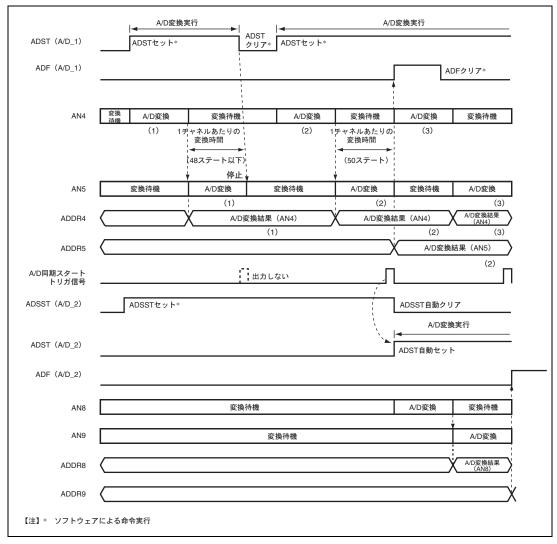

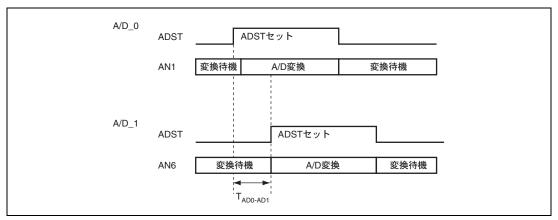

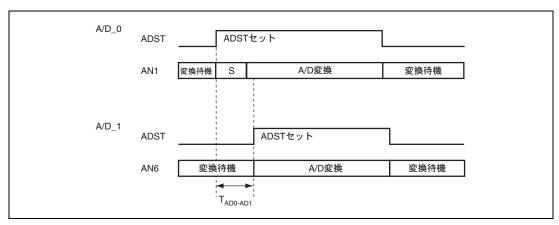

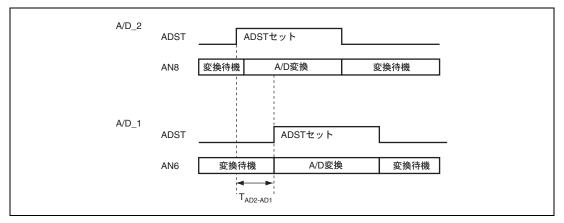

| 19.4.8  | A/D 変換同期化機能                                  | 19-33 |

| 19.5    | 割り込み要因とDMAC、DTC転送要求                          | 19-43 |

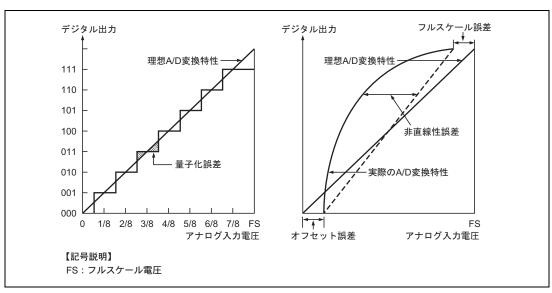

| 19.6    | A/D変換精度の定義                                   | 19-44 |

| 19.7    | 使用上の注意事項                                     | 19-45 |

| 19.7.1  | アナログ入力電圧の設定範囲                                | 19-45 |

| 19.7.2  | AVCC、AVSS と VCC、VSS の関係                      | 19-45 |

| 19.7.3  | AVREF 端子の設定範囲                                | 19-45 |

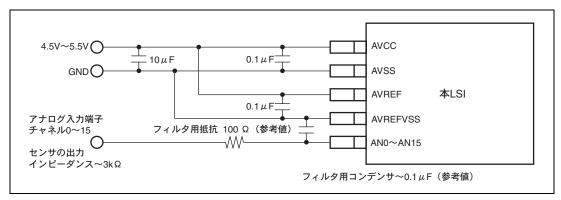

| 19.7.4  | ボード設計上の注意                                    | 19-45 |

| 19.7.5  | ノイズ対策上の注意                                    | 19-45 |

| 19.7.6  | レジスタ設定時の注意                                   | 19-46 |

| 19.7.7  | 許容信号源インピーダンスについて                             | 19-46 |

| 19.7.8  | 絶対精度への影響                                     | 19-46 |

| 19.7.9  | 2 つ以上の A/D モジュールを同時に動作させるときの注意               | 19-47 |

| 20. コン  | ・トローラエリアネットワーク(RCAN-ET)                      | 20-1  |

| 20.1    | 特長                                           | 20-1  |

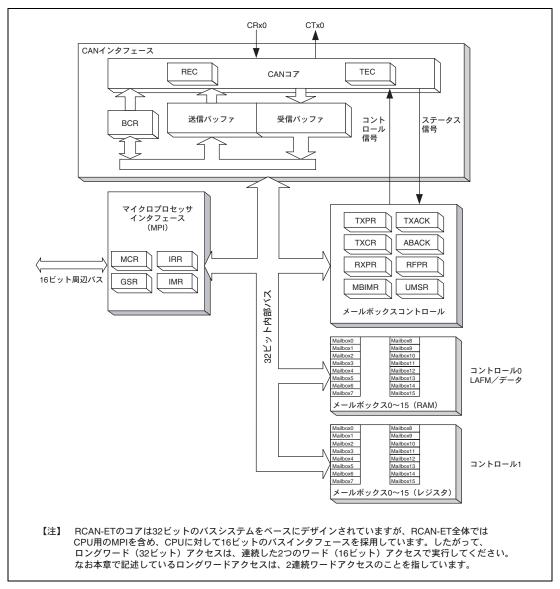

| 20.2    | 構成                                           | 20-2  |

| 20.2.1  | ブロック図                                        | 20-2  |

| 20.2.2  | 各ブロックの機能                                     | 20-3  |

| 20.2.3  | 端子構成                               | 20-4  |

|---------|------------------------------------|-------|

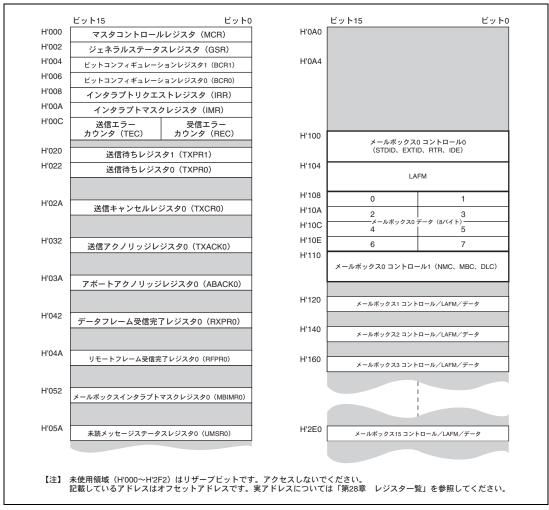

| 20.2.4  | メモリマップ                             | 20-5  |

| 20.3    | メールボックス                            | 20-6  |

| 20.3.1  | メールボックスの構成                         | 20-6  |

| 20.3.2  | メッセージコントロールフィールド                   | 20-8  |

| 20.3.3  | ローカルアクセプタンスフィルタマスク(LAFM)           | 20-13 |

| 20.3.4  | メッセージデータフィールド                      | 20-14 |

| 20.4    | RCAN-ETのコントロールレジスタ                 | 20-14 |

| 20.4.1  | マスタコントロールレジスタ(MCR)                 | 20-14 |

| 20.4.2  | ジェネラルステータスレジスタ(GSR)                | 20-20 |

| 20.4.3  | ビットコンフィギュレーションレジスタ 0、1 (BCR0、BCR1) | 20-22 |

| 20.4.4  | インタラプトリクエストレジスタ(IRR)               | 20-26 |

| 20.4.5  | インタラプトマスクレジスタ(IMR)                 | 20-31 |

| 20.4.6  | 送信エラーカウンタ(TEC)/受信エラーカウンタ(REC)      | 20-31 |

| 20.5    | RCAN-ETのメールボックスレジスタ                | 20-32 |

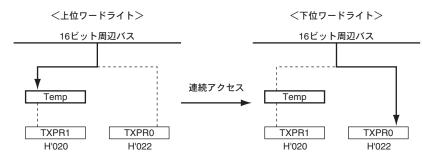

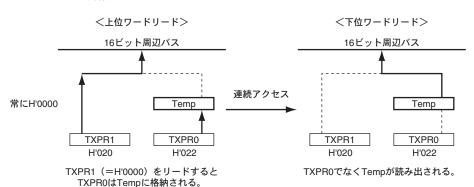

| 20.5.1  | 送信待ちレジスタ 1、0(TXPR1、TXPR0)          | 20-33 |

| 20.5.2  | 送信キャンセルレジスタ 0(TXCR0)               | 20-36 |

| 20.5.3  | 送信アクノリッジレジスタ 0(TXACK0)             | 20-37 |

| 20.5.4  | アボートアクノリッジレジスタ 0(ABACK0)           | 20-38 |

| 20.5.5  | データフレーム受信完了レジスタ 0(RXPRO)           | 20-39 |

| 20.5.6  | リモートフレーム受信完了レジスタ 0(RFPRO)          | 20-40 |

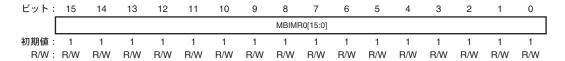

| 20.5.7  | メールボックスインタラプトマスクレジスタ 0(MBIMR0)     | 20-41 |

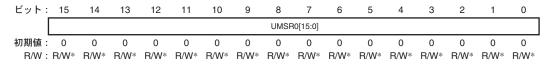

| 20.5.8  | 未読メッセージステータスレジスタ 0(UMSR0)          | 20-42 |

| 20.6    | 動作説明                               | 20-43 |

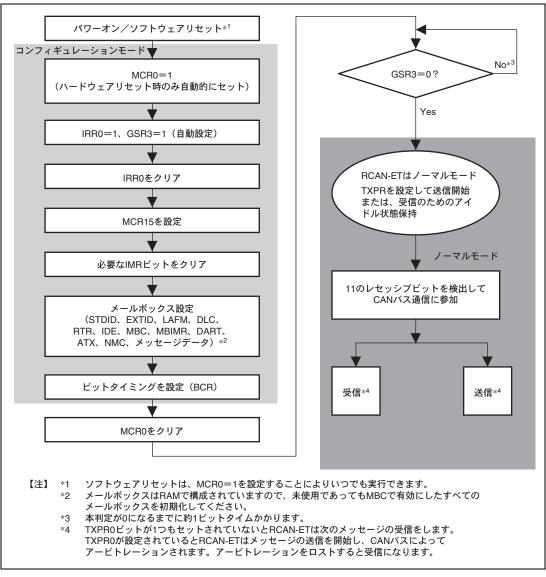

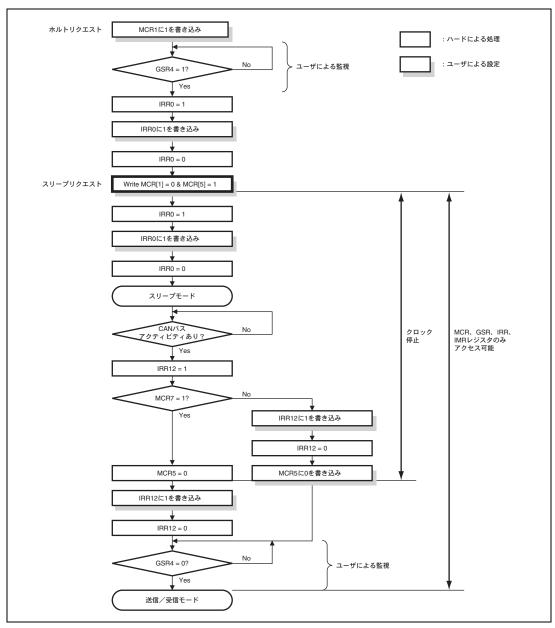

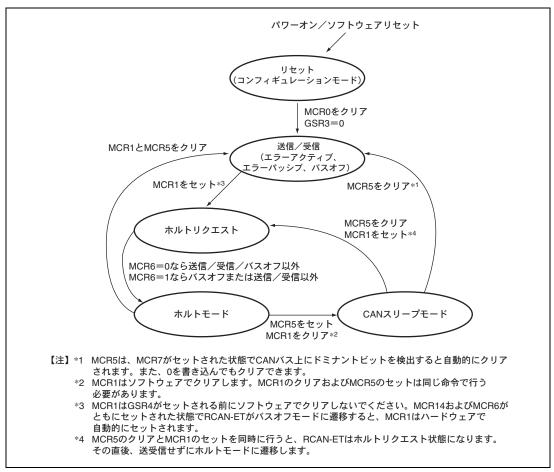

| 20.6.1  | RCAN-ET の設定                        | 20-43 |

| 20.6.2  | テストモードの設定                          | 20-48 |

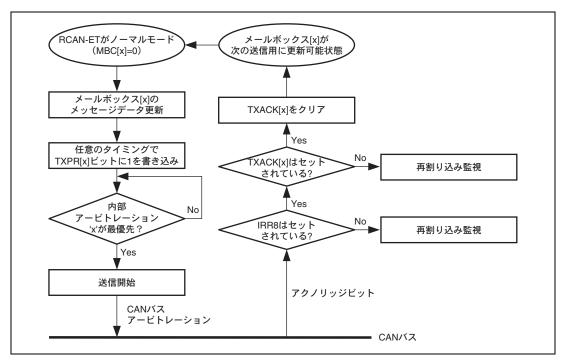

| 20.6.3  | メッセージ送信シーケンス                       | 20-50 |

| 20.6.4  | メッセージ受信シーケンス                       | 20-52 |

| 20.6.5  | メールボックスの再設定                        | 20-54 |

| 20.7    | 割り込み要因                             | 20-56 |

| 20.8    | DTCインタフェース                         | 20-57 |

| 20.9    | DMACインタフェース                        | 20-58 |

| 20.10   | CANバスインタフェース                       | 20-59 |

| 20.11   | 使用上の注意事項                           | 20-60 |

| 20.11.1 | モジュールスタンバイモード                      | 20-60 |

| 20.11.2 | リセット                               | 20-60 |

| 20.11.3 | CAN スリープモード                        | 20-60 |

| 20.11.4 |                                    |       |

| 20.11.5 | 割り込み                               | 20-60 |

| 21. ピンフ   | ファンクションコントローラ(PFC)                              | 21-1  |

|-----------|-------------------------------------------------|-------|

| 21.1 L    | ⁄ ジスタの説明                                        | 21-11 |

| 21.1.1    | ポート A・IO レジスタ H、L(PAIORH、PAIORL)                |       |

| 21.1.2    | ポートAコントロールレジスタH1、L1~L4(PACRH1、PACRL1~PACRL4)    |       |

| 21.1.3    | ポート A プルアップ MOS コントロールレジスタ H、L(PAPCRH、PAPCRL)   |       |

| 21.1.4    | ポートB・IO レジスタ H、L(PBIORH、PBIORL)                 |       |

| 21.1.5    | ポートBコントロールレジスタH1、H2、L1、L2(PBCRH1、PBCRH2、PBCRL1、 |       |

|           |                                                 | 21-20 |

| 21.1.6    | ポート B プルアップ MOS コントロールレジスタ H、L(PBPCRH、PBPCRL)   | 21-27 |

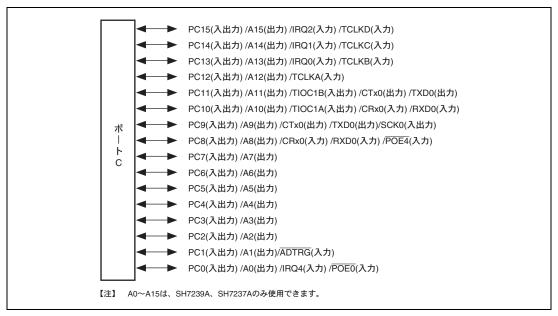

| 21.1.7    | ポート C・IO レジスタ L(PCIORL)                         | 21-28 |

| 21.1.8    | ポート C コントロールレジスタ L1~L4(PCCRL1~PCCRL4)           | 21-28 |

| 21.1.9    | ポート C プルアップ MOS コントロールレジスタ L(PCPCRL)            | 21-34 |

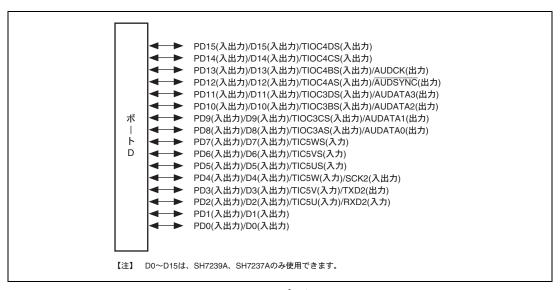

| 21.1.10   | ポート D・IO レジスタ L(PDIORL)                         | 21-35 |

| 21.1.11   | ポート D コントロールレジスタ L1~L4(PDCRL1~PDCRL4)           | 21-35 |

| 21.1.12   | ポート D プルアップ MOS コントロールレジスタ L(PDPCRL)            | 21-41 |

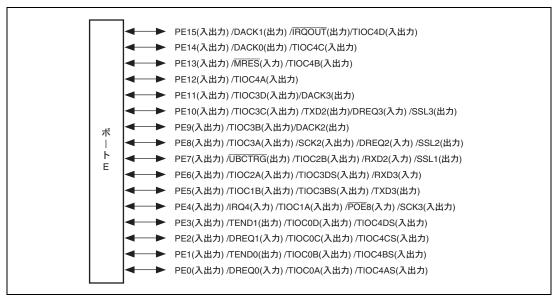

| 21.1.13   | ポートE・IO レジスタL(PEIORL)                           | 21-42 |

| 21.1.14   | ポート E コントロールレジスタ L1~L4(PECRL1~PECRL4)           | 21-42 |

| 21.1.15   | ポートEプルアップ MOS コントロールレジスタL(PEPCRL)               | 21-48 |

| 21.1.16   | 大電流ポートコントロールレジスタ(HCPCR)                         | 21-49 |

| 21.1.17   | DACK 出力タイミングコントロールレジスタ(PDACKCR)                 | 21-50 |

| 21.2 靖    | 端子機能によるプルアップMOS制御                               | 21-53 |

| 21.3 億    | <b></b>   E用上の注意事項                              | 21-55 |

|           |                                                 |       |

| 22. 1/0 木 | - h                                             | 22-1  |

| 22.1 য    | ∜− トA                                           | 22-2  |

| 22.1.1    | レジスタの説明                                         | 22-2  |

| 22.1.2    | ポート A データレジスタ H、L(PADRH、PADRL)                  | 22-3  |

| 22.1.3    | ポートAポートレジスタ H、L(PAPRH、PAPRL)                    | 22-5  |

| 22.2 최    | <sup>2</sup> √− トB                              | 22-6  |

| 22.2.1    | レジスタの説明                                         | 22-6  |

| 22.2.2    | ポートBデータレジスタH、L(PBDRH、PBDRL)                     | 22-7  |

| 22.2.3    | ポートBポートレジスタH、L(PBPRH、PBPRL)                     | 22-8  |

| 22.3 习    | <sup>8</sup> √−                                 | 22-10 |

| 22.3.1    | レジスタの説明                                         | 22-10 |

| 22.3.2    | ポート C データレジスタ L(PCDRL)                          | 22-11 |

| 22.3.3    | ポート C ポートレジスタ L(PCPRL)                          | 22-12 |

| 22.4 최    | <sup>2</sup> √− ∤D                              | 22-13 |

| 22.4.1    | レジスタの説明                                         |       |

| 22.4.2    | ポート D データレジスタ L(PDDRL)                          | 22-14 |

| 22.4.3    | ポートロポートレジスタI(PDPRI)                             | 22-15 |

| 22.5    | ポートE                           | 22-16 |

|---------|--------------------------------|-------|

| 22.5.1  | レジスタの説明                        | 22-16 |

| 22.5.2  | ポートEデータレジスタL(PEDRL)            | 22-17 |

| 22.5.3  | ポートEポートレジスタL(PEPRL)            | 22-18 |

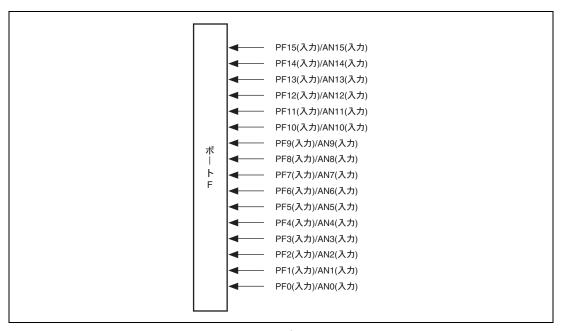

| 22.6    | ポートF                           | 22-19 |

| 22.6.1  | レジスタの説明                        | 22-19 |

| 22.6.2  | ポートFデータレジスタL(PFDRL)            | 22-20 |

| 22.7    | 使用上の注意事項                       | 22-21 |

| 22.7.1  | 未使用端子の処理について                   | 22-21 |

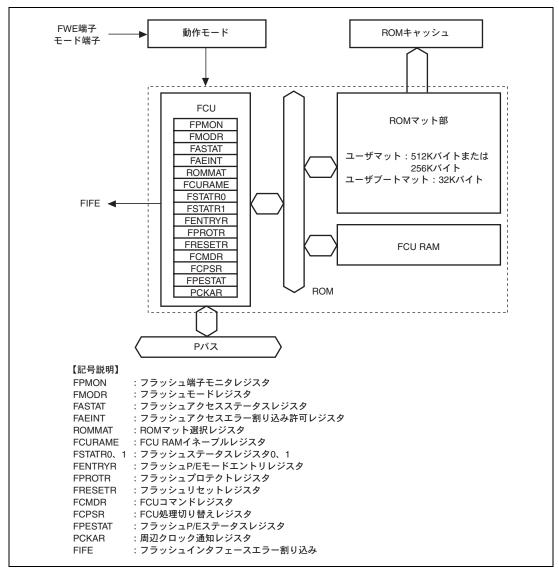

| 23. フラ  | ・ッシュメモリ(ROM)                   | 23-1  |

| 23.1    | 特長                             | 23-1  |

| 23.2    | 入出力端子                          | 23-4  |

| 23.3    | レジスタの説明                        | 23-5  |

| 23.3.1  | フラッシュ端子モニタレジスタ(FPMON)          | 23-6  |

| 23.3.2  | フラッシュモードレジスタ(FMODR)            | 23-7  |

| 23.3.3  | フラッシュアクセスステータスレジスタ(FASTAT)     | 23-8  |

| 23.3.4  | フラッシュアクセスエラー割り込み許可レジスタ(FAEINT) | 23-10 |

| 23.3.5  | ROM マット選択レジスタ(ROMMAT)          | 23-11 |

| 23.3.6  | FCU RAM イネーブルレジスタ(FCURAME)     | 23-12 |

| 23.3.7  | フラッシュステータスレジスタ 0(FSTATRO)      | 23-13 |

| 23.3.8  | フラッシュステータスレジスタ 1(FSTATR1)      | 23-15 |

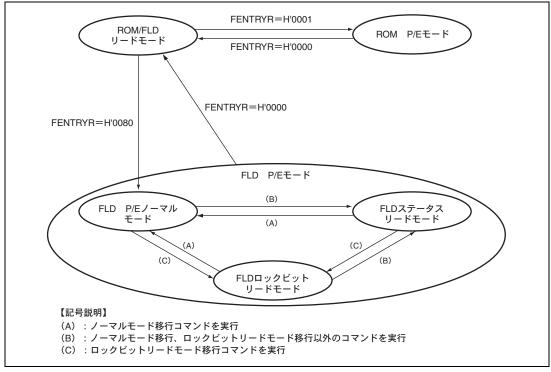

| 23.3.9  | フラッシュ P/E モードエントリレジスタ(FENTRYR) | 23-17 |

| 23.3.10 | ) フラッシュプロテクトレジスタ(FPROTR)       | 23-19 |

| 23.3.11 | フラッシュリセットレジスタ(FRESETR)         | 23-20 |

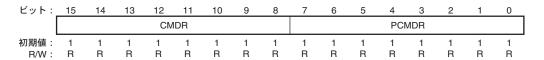

| 23.3.12 | PCU コマンドレジスタ(FCMDR)            | 23-21 |

| 23.3.13 | B FCU 処理切り替えレジスタ(FCPSR)        | 23-22 |

| 23.3.14 | 4 フラッシュ P/E ステータスレジスタ(FPESTAT) | 23-23 |

| 23.3.15 | 5 ROM キャッシュ制御レジスタ(RCCR)        | 23-24 |

| 23.3.16 | 5 周辺クロック通知レジスタ(PCKAR)          | 23-25 |

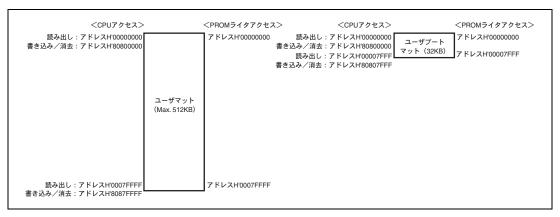

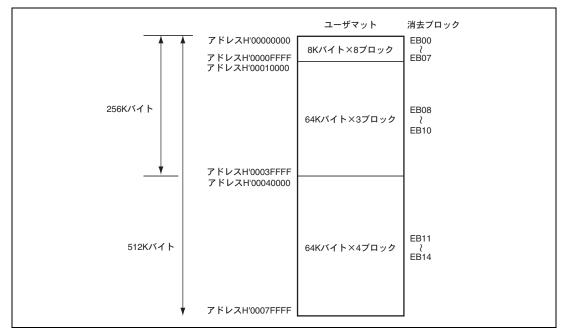

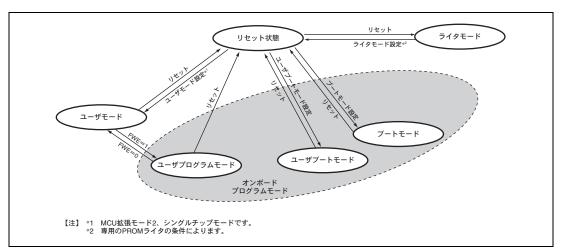

| 23.4    | ROM関連モード概要                     | 23-26 |

| 23.5    | ブートモード                         | 23-28 |

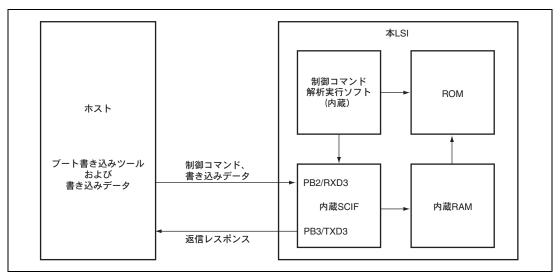

| 23.5.1  | システム構成                         | 23-28 |

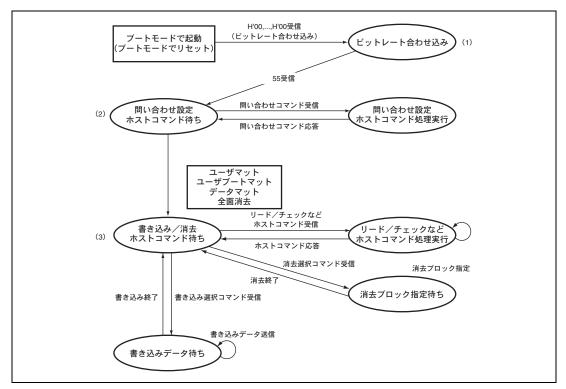

| 23.5.2  | ブートモードの状態遷移                    | 23-29 |

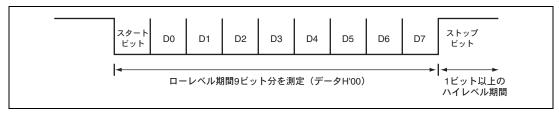

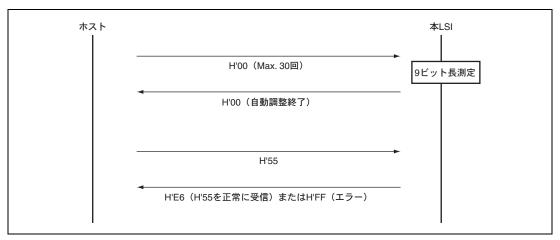

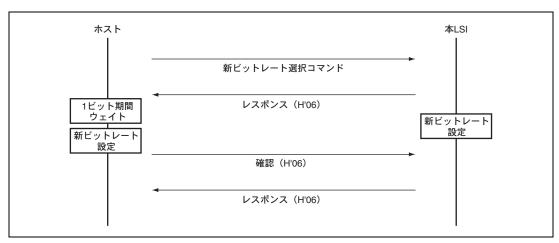

| 23.5.3  | ビットレートの自動調整                    | 23-31 |

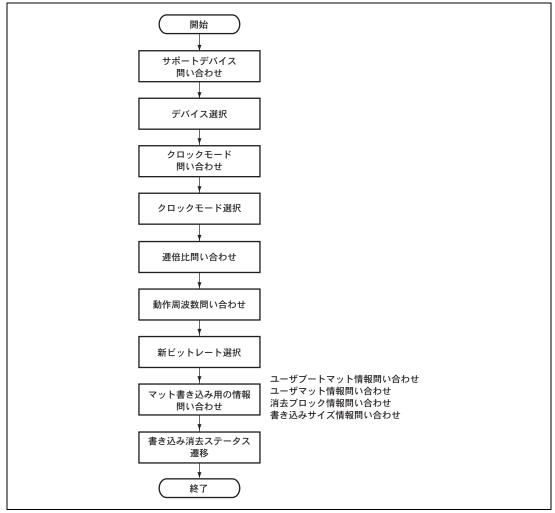

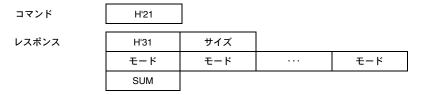

| 23.5.4  | 問い合わせ設定ホストコマンド待ち状態             | 23-32 |

| 23.5.5  | 書き込み/消去ホストコマンド待ち状態             | 23-44 |

| 23.6    | ユーザプログラムモード                    | 23-53 |

| 23.6.1  | FCU コマンド一覧                     | 23-53 |

| 23.6.2  | FCU コマンド受け付け条件                 | 23-55 |

| 23.6.3  | FCU コマンド使用方法                   | 23-59 |

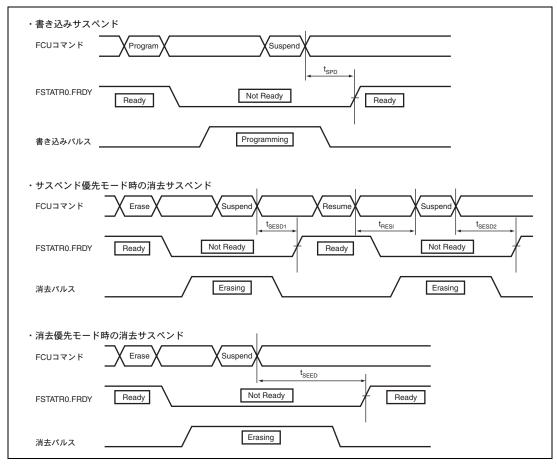

| 23.6.4                                          | サスペンド動作                                                                                              | 23-77                                     |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 23.7                                            | 1ーザブートモード                                                                                            | 23-80                                     |

| 23.7.1                                          | ユーザブートモードの起動シーケンス                                                                                    | 23-80                                     |

| 23.7.2                                          | ユーザマットのプログラミング方法                                                                                     | 23-81                                     |

| 23.8                                            | <del>5</del> イタモード                                                                                   | 23-82                                     |

| 23.9                                            | プロテクト                                                                                                | 23-82                                     |

| 23.9.1                                          | ハードウェアプロテクト                                                                                          | 23-82                                     |

| 23.9.2                                          | ソフトウェアプロテクト                                                                                          | 23-83                                     |

| 23.9.3                                          | エラープロテクト                                                                                             | 23-83                                     |

| 23.10                                           | <b></b>                                                                                              | 23-85                                     |

| 23.10.1                                         | ユーザマットとユーザブートマットの切り替え                                                                                | 23-85                                     |

| 23.10.2                                         | 割り込み無視状態                                                                                             | 23-87                                     |

| 23.10.3                                         | 書き込み/消去サスペンド対象領域                                                                                     | 23-87                                     |

| 23.10.4                                         | 従来の F-ZTAT SH マイコンとの書き込み/消去プログラムの互換性                                                                 | 23-87                                     |

| 23.10.5                                         | FWE 端子の状態                                                                                            | 23-87                                     |

| 23.10.6                                         | 書き込み/消去中のリセット                                                                                        | 23-88                                     |

| 23.10.7                                         | 書き込み/消去サスペンドによる中断                                                                                    | 23-88                                     |

| 23.10.8                                         | 追加書き込み禁止                                                                                             | 23-88                                     |

| 23.10.9                                         | 書き込み/消去中の割り込みベクタの配置                                                                                  | 23-88                                     |

| 23.10.10                                        | 書き込み/消去中の禁止事項                                                                                        | 23-89                                     |

| 23.10.11                                        | 書き込み/消去中の異常終了                                                                                        | 23-89                                     |

|                                                 |                                                                                                      |                                           |

| 24. データ                                         | プフラッシュ(FLD)                                                                                          | 24-1                                      |

| 24.1 特                                          | 持長                                                                                                   | 24-1                                      |

| 24.2                                            | \出力端子                                                                                                | 24-6                                      |

| 24.3 l                                          | ⁄ ジスタの説明                                                                                             | 24-7                                      |

| 24.3.1                                          | フラッシュモードレジスタ(FMODR)                                                                                  | 24-8                                      |

| 24.3.2                                          | フラッシュアクセスステータスレジスタ(FASTAT)                                                                           | 24-9                                      |

| 24.3.3                                          | フラッシュアクセスエラー割り込み許可レジスタ(FAEINT)                                                                       | 24-12                                     |

| 24.3.4                                          | FLD 読み出し許可レジスタ 0(EEPRE0)                                                                             | 24-14                                     |

| 24.3.5                                          | FLD 読み出し許可レジスタ 1(EEPRE1)                                                                             | 24-15                                     |

| 24.3.6                                          | FLD 書き込み/消去許可レジスタ 0(EEPWE0)                                                                          | 24-16                                     |

| 24.3.7                                          | FLD 書き込み/消去許可レジスタ 1(EEPWE1)                                                                          | 24-17                                     |

| 24.3.8                                          | フラッシュ P/E モードエントリレジスタ(FENTRYR)                                                                       | 24-18                                     |

|                                                 | J J J J J I I C   L J J J J J J J J J J J J J J J J J J                                              |                                           |

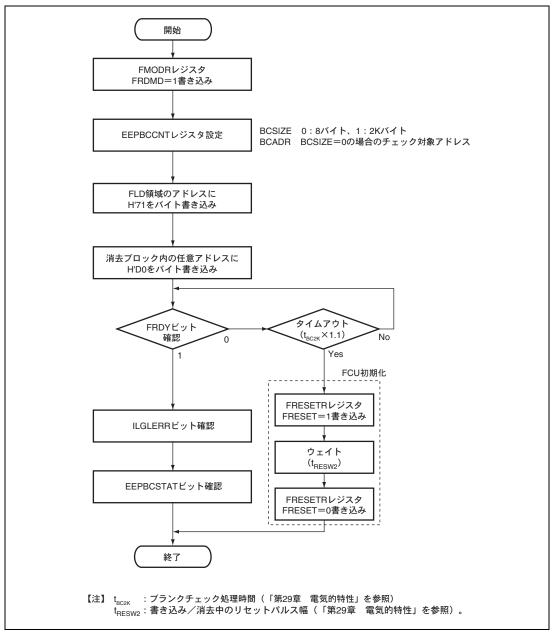

| 24.3.9                                          | FLD ブランクチェックレジスタ (EEPBCCNT)                                                                          | 24-19                                     |

| 24.3.9<br>24.3.10                               |                                                                                                      |                                           |

| 24.3.10                                         | FLD ブランクチェックレジスタ(EEPBCCNT)                                                                           | 24-20                                     |

| 24.3.10<br>24.4 F                               | FLD ブランクチェックレジスタ (EEPBCCNT)            FLD ブランクチェックステータスレジスタ (EEPBCSTAT)                             | 24-20                                     |

| 24.3.10<br>24.4 F                               | FLD ブランクチェックレジスタ(EEPBCCNT)                                                                           | 24-20<br>24-21<br>24-23                   |

| 24.3.10<br>24.4 F<br>24.5                       | FLD ブランクチェックレジスタ(EEPBCCNT)         FLD ブランクチェックステータスレジスタ(EEPBCSTAT)         LD関連モード概要         プートモード | 24-20<br>24-21<br>24-23<br>24-23          |

| 24.3.10<br>24.4 F<br>24.5 2<br>24.5.1<br>24.5.2 | FLD ブランクチェックレジスタ(EEPBCCNT)                                                                           | 24-20<br>24-21<br>24-23<br>24-23<br>24-25 |

|                                                                                                             | FCU コマンド一覧                                 | 24-21 |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------|

| 24.6.2                                                                                                      | FCU コマンド受け付け条件                             | 24-29 |

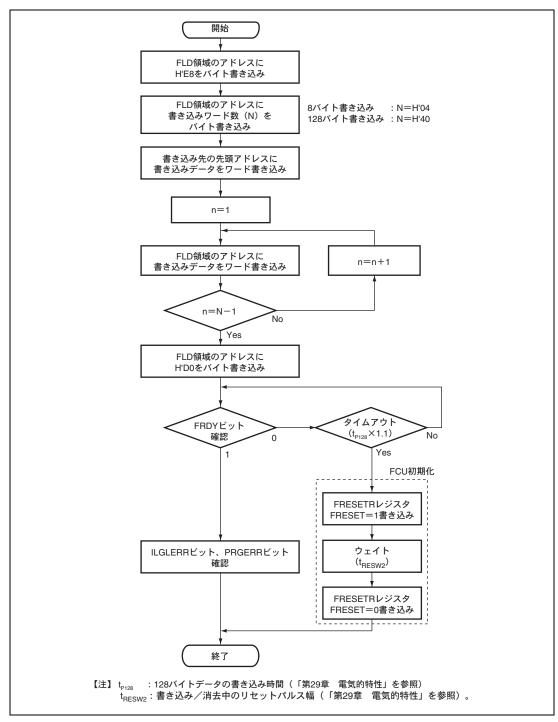

| 24.6.3                                                                                                      | FCU コマンド使用方法                               | 24-33 |

| 24.7                                                                                                        | プロテクト                                      | 24-37 |

| 24.7.1                                                                                                      | ハードウェアプロテクト                                | 24-37 |

| 24.7.2                                                                                                      | ソフトウェアプロテクト                                | 24-37 |

| 24.7.3                                                                                                      | エラープロテクト                                   | 24-38 |

| 24.8                                                                                                        | 使用上の注意事項                                   | 24-39 |

| 24.8.1                                                                                                      | リセット起動直後のデータマットプロテクト状態                     | 24-39 |

| 24.8.2                                                                                                      | 割り込み無視状態                                   | 24-39 |

| 24.8.3                                                                                                      | 書き込み/消去サスペンド対象領域                           | 24-39 |

| 24.8.4                                                                                                      | 従来の F-ZTAT SH マイコンとの書き込み/消去プログラムの互換性       | 24-39 |

| 24.8.5                                                                                                      | 書き込み/消去中のリセット                              | 24-39 |

| 24.8.6                                                                                                      | 書き込み/消去サスペンドによる中断                          | 24-40 |

| 24.8.7                                                                                                      | 追加書き込み禁止                                   | 24-40 |

| 24.8.8                                                                                                      | 読み出しプログラムについて                              | 24-40 |

| 24.8.9                                                                                                      | 書き込み/消去中の禁止事項                              | 24-40 |

| 24.8.10                                                                                                     | 書き込み/消去中の異常終了                              | 24-40 |

| 24.8.11                                                                                                     | 消去または書き込み中断時の対応について                        | 24-40 |

|                                                                                                             |                                            |       |

| 25. 内蔵                                                                                                      | RAM                                        | 25-1  |

| 25.1                                                                                                        | 特長                                         | 25-1  |

| 25.2                                                                                                        | レジスタの説明                                    | 25-4  |

| 25.2.1                                                                                                      | システムコントロールレジスタ 1(SYSCR1)                   | 25-4  |

|                                                                                                             | システムコントロールレジスタ 2(SYSCR2)                   |       |

| 25.2.2                                                                                                      | システムコントロールレシスタ 2 (SYSCR2)                  | 25-6  |

| 25.2.2<br>25.3                                                                                              | システムコントロールレンスタ 2 (SYSCR2)         使用上の注意事項 |       |

|                                                                                                             |                                            | 25-8  |

| 25.3<br>25.3.1                                                                                              | 使用上の注意事項ページ競合                              | 25-8  |

| 25.3<br>25.3.1                                                                                              | 使用上の注意事項                                   | 25-8  |

| 25.3<br>25.3.1                                                                                              | 使用上の注意事項ページ競合                              |       |

| 25.3<br>25.3.1<br>26. 低消                                                                                    | 使用上の注意事項ページ競合                              |       |

| 25.3。<br>25.3.1<br>26. 低消<br>26.1                                                                           | 使用上の注意事項ページ競合                              |       |

| 25.3<br>25.3.1<br>26. 低消<br>26.1<br>26.1.1                                                                  | 使用上の注意事項                                   |       |

| 25.3<br>25.3.1<br>26. 低消<br>26.1<br>26.1.1<br>26.1.2                                                        | 使用上の注意事項                                   |       |

| 25.3<br>25.3.1<br>26. 低消<br>26.1<br>26.1.1<br>26.1.2<br>26.2                                                | 使用上の注意事項                                   |       |

| 25.3<br>25.3.1<br>26. 低消<br>26.1.1<br>26.1.2<br>26.2<br>26.3                                                | 使用上の注意事項                                   |       |

| 25.3<br>25.3.1<br>26. 低消<br>26.1<br>26.1.1<br>26.1.2<br>26.2<br>26.3<br>26.3.1                              | 使用上の注意事項                                   |       |

| 25.3<br>25.3.1<br>26. 低消<br>26.1.1<br>26.1.2<br>26.2<br>26.3<br>26.3.1<br>26.3.2                            | 使用上の注意事項                                   |       |

| 25.3<br>25.3.1<br>26. 低消<br>26.1.1<br>26.1.2<br>26.2<br>26.3<br>26.3.1<br>26.3.2<br>26.3.3                  | 使用上の注意事項                                   |       |

| 25.3<br>25.3.1<br>26. <b>低消</b><br>26.1.1<br>26.1.2<br>26.2<br>26.3<br>26.3.1<br>26.3.2<br>26.3.3<br>26.3.4 | 使用上の注意事項ページ競合                              |       |

| 26.4.1 | スリープモード                             | 26-10 |

|--------|-------------------------------------|-------|

| 26.4.2 | ソフトウェアスタンバイモード                      | 26-10 |

| 26.4.3 | ソフトウェアスタンバイモードの応用例                  | 26-12 |

| 26.4.4 | モジュールスタンバイ機能                        | 26-13 |

| 26.5   | 使用上の注意事項                            | 26-14 |

| 26.5.1 | 発振安定待機中の消費電流                        | 26-14 |

| 26.5.2 | レジスタ書き込み時の注意                        | 26-14 |

| 26.5.3 | IRQx 割り込み要求によるソフトウェアスタンバイ解除に関する注意事項 | 26-14 |

| 27. ユー | -ザデバッグインタフェース(H-UDI)                | 27-1  |

| 27.1   | 特長                                  | 27-1  |

| 27.2   | 入出力端子                               | 27-2  |

| 27.3   | レジスタの説明                             | 27-3  |

| 27.3.1 | バイパスレジスタ(SDBPR)                     | 27-3  |

| 27.3.2 | インストラクションレジスタ(SDIR)                 | 27-3  |

| 27.4   | 動作説明                                | 27-5  |

| 27.4.1 | TAP コントローラ                          | 27-5  |

| 27.4.2 | リセット構成                              | 27-6  |

| 27.4.3 | TDO 出力タイミング                         | 27-6  |

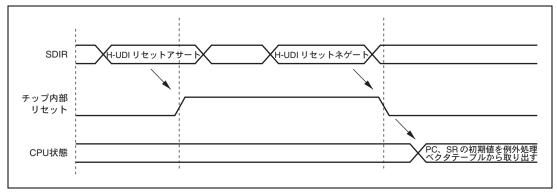

| 27.4.4 | H-UDI リセット                          | 27-7  |

| 27.4.5 | H-UDI 割り込み                          | 27-7  |

| 27.5   | 使用上の注意事項                            | 27-8  |

| 28. レシ | ジスター覧                               | 28-1  |

| 28.1   | レジスタアドレス一覧 (機能モジュールごと、マニュアル章番号順)    | 28-2  |

| 28.2   | レジスタビット一覧                           | 28-23 |

| 28.3   | 各動作モードにおけるレジスタの状態の一覧                | 28-53 |

| 29. 電気 | 5的特性                                | 29-1  |

| 29.1   | 絶対最大定格                              | 29-1  |

| 29.2   | DC特性                                |       |

| 29.3   | AC特性                                | 29-7  |

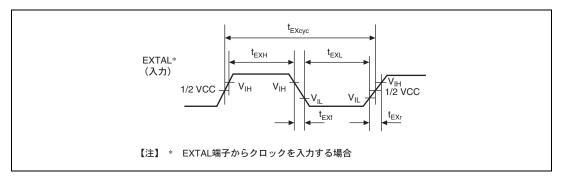

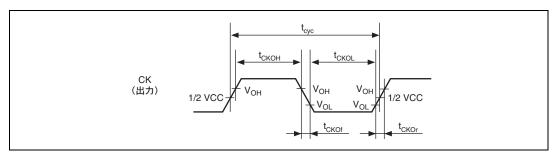

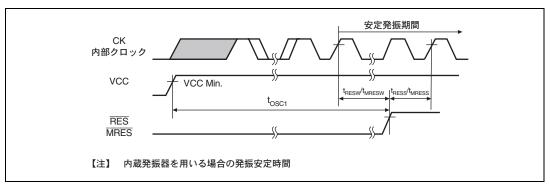

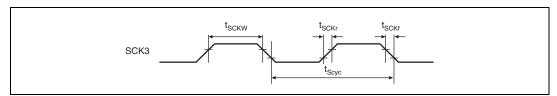

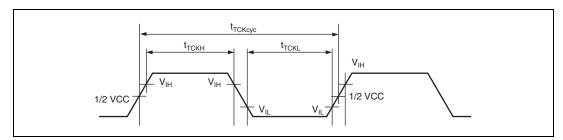

| 29.3.1 | クロックタイミング                           | 29-8  |

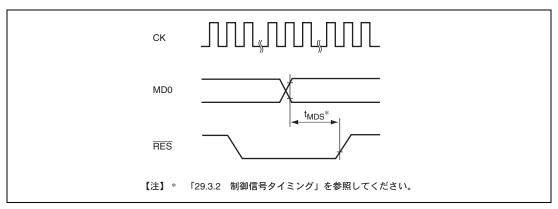

| 29.3.2 | 制御信号タイミング                           | 29-11 |

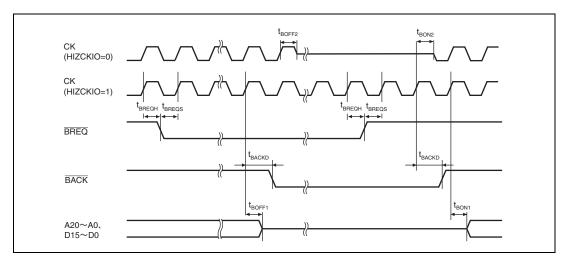

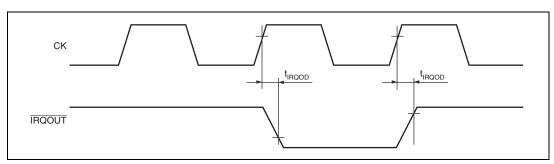

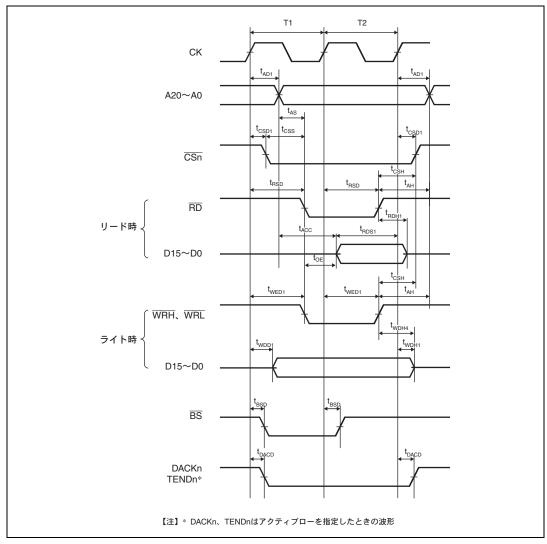

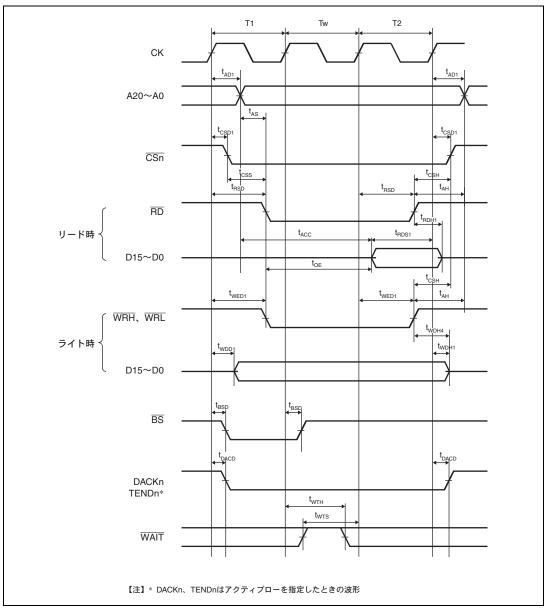

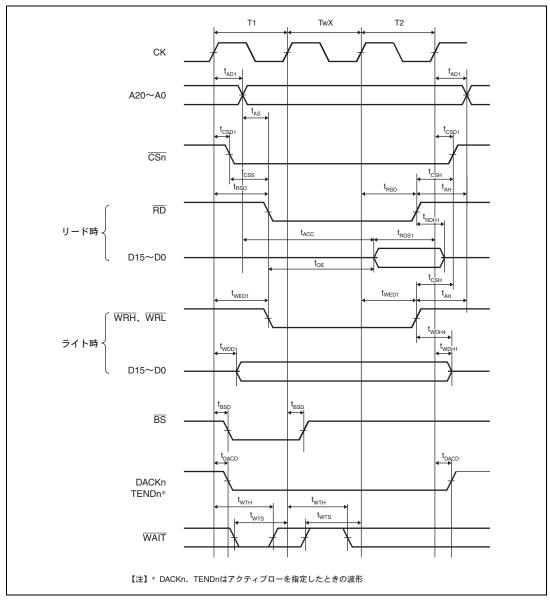

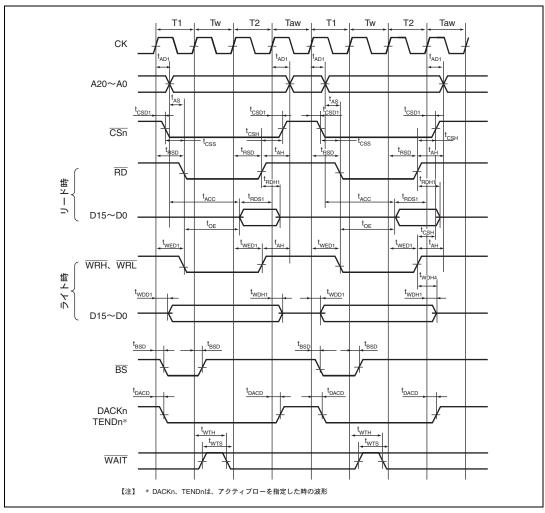

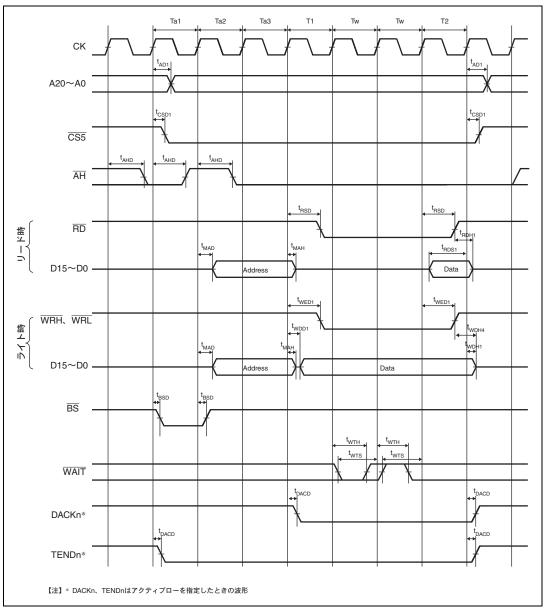

| 29.3.3 | バスタイミング(SH7239A、SH7237A のみ)         | 29-15 |

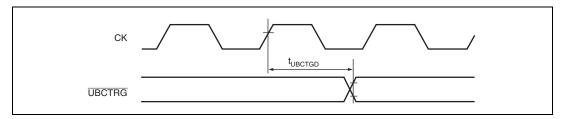

| 29.3.4 | UBC トリガタイミング                        | 29-21 |

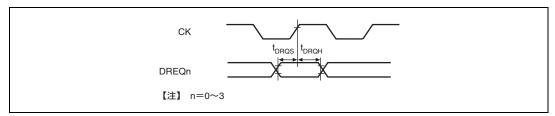

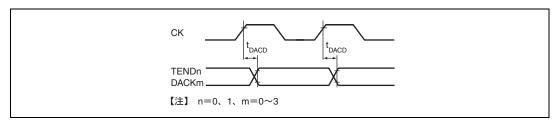

| 29.3.5 | DMAC モジュールタイミング                     | 29-22 |

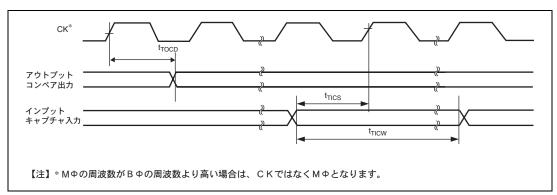

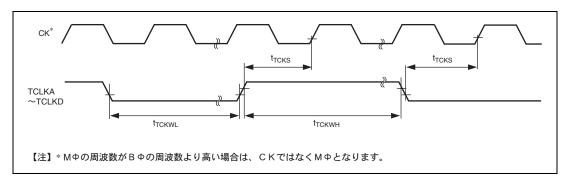

| 29.3.6 | MTU2、MTU2S モジュールタイミング               | 29-23 |

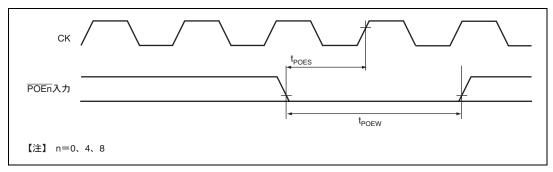

| 29.3.7 | POE2 モジュールタイミング                     | 29-24 |

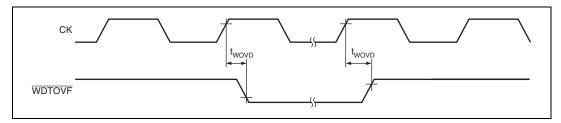

| 29.3.8 | ウォッチドッグタイマタイミング                     | 29-25 |

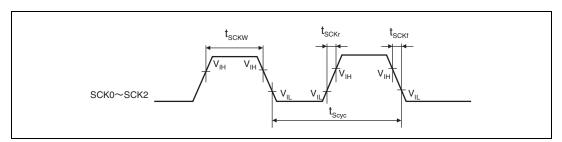

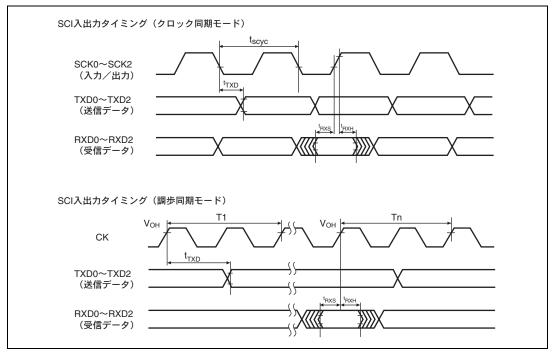

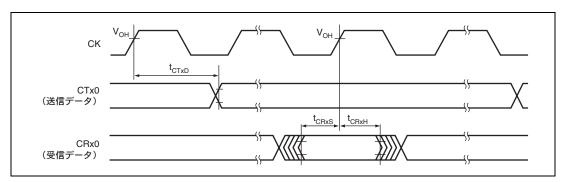

| 29.3.9 | シリアルコミュニケーションインタフェース (SCI) タイミング    | 29-26 |

|        |                                     |       |

| 29.3.10 | ) SCIF モジュールタイミング                 | 29-28 |

|---------|-----------------------------------|-------|

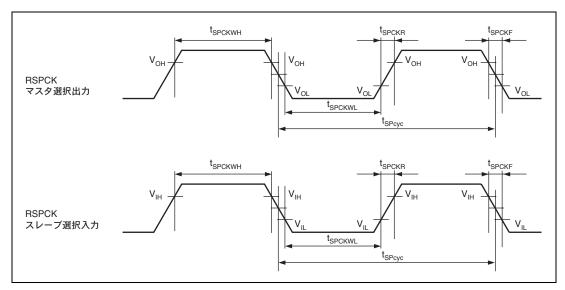

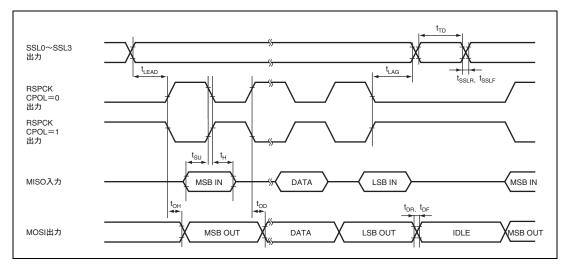

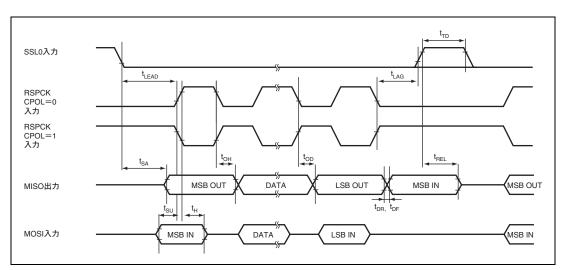

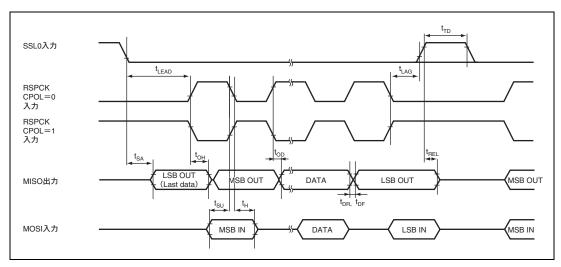

| 29.3.11 | RSPI タイミング                        | 29-30 |

| 29.3.12 | 2 コントローラエリアネットワーク (RCAN-ET) タイミング | 29-34 |

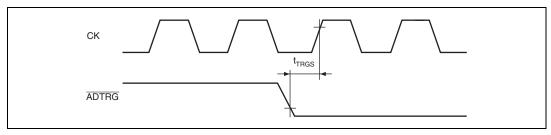

| 29.3.13 | 3 A/D トリガ入力タイミング                  | 29-35 |

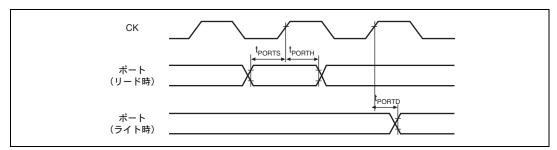

| 29.3.14 | I/O ポートタイミング                      | 29-36 |

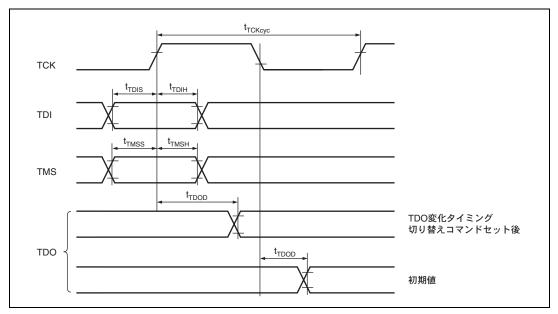

| 29.3.15 | 6 H-UDI 関連端子のタイミング                | 29-37 |

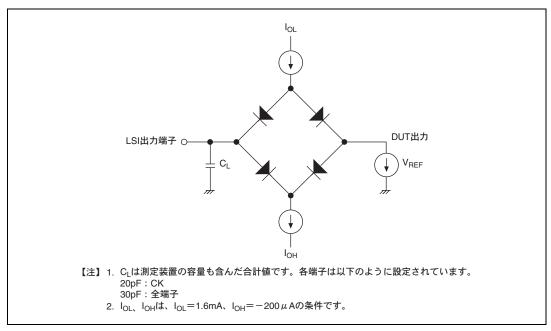

| 29.3.16 | 6 AC 特性測定条件                       | 29-39 |

| 29.4    | A/D変換器特性                          | 29-40 |

| 29.5    | フラッシュメモリ特性                        | 29-41 |

| 29.6    | FLD特性                             |       |

| 29.7    | 使用上の注意事項                          | 29-44 |

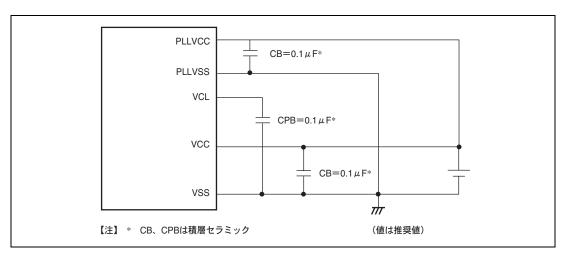

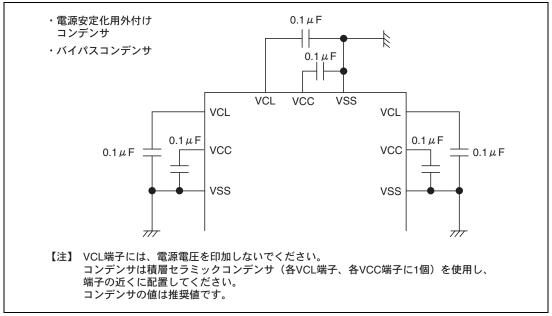

| 29.7.1  | コンデンサ接続方法                         | 29-44 |

| 付録      |                                   | 付録-1  |

| A.      | 端子状態                              | 付録-1  |

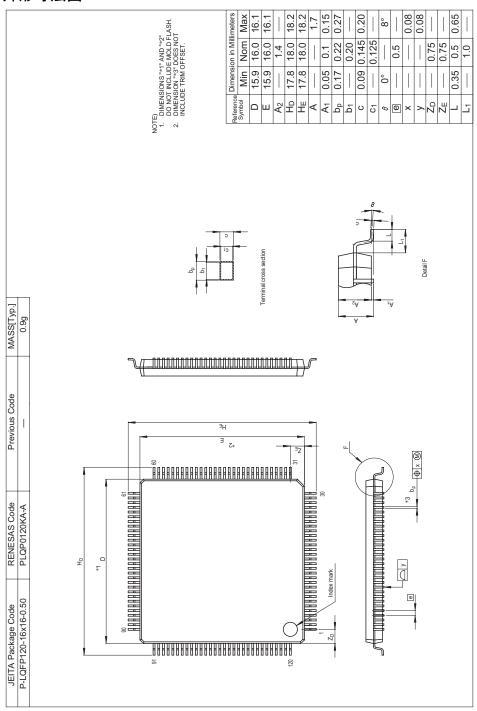

| B.      | 外形寸法図                             | 付録-8  |

| 本版で修    | 正または追加された箇所                       | 改訂-1  |

| 索引      |                                   | 索引-1  |

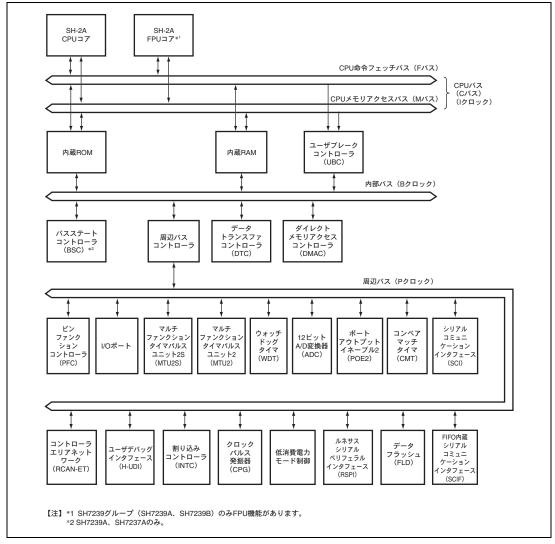

## 1. 概要

## 1.1 特長

SH7239 グループおよび SH7237 グループは、ルネサスオリジナルの RISC (Reduced Instruction Set Computer) 方式の CPU をコアにして、システム構成に必要な周辺機能を集積したシングルチップ RISC マイコンです。

SH7239 グループおよび SH7237 グループの CPU は、RISC 方式の命令セットを持っており、スーパースカラアーキテクチャやハーバードアーキテクチャを採用しているため、命令実行速度が飛躍的に向上しています。また内部 32 ビット構成を採用しており、データ処理能力を強化しています。SH7239 グループおよび SH7237 グループの CPU によって、従来のマイコンでは実現が不可能だった、高速性が要求されるリアルタイム制御等のアプリケーションでも、より低コストでかつ高性能/高機能なシステムを組むことができるようになります。また、SH7239 グループは浮動小数点ユニット (FPU) を内蔵しています。

さらに、SH7239 グループおよび SH7237 グループは、システム構成に必要な周辺機能として、大容量 ROM、ROM キャッシュ、RAM、ダイレクトメモリアクセスコントローラ (DMAC)、データトランスファコントローラ (DTC)、マルチファンクションタイマパルスユニット 2 (MTU2/MTU2S)、FIFO 内蔵シリアルコミュニケーションインタフェース (SCIF)、シリアルコミュニケーションインタフェース (SCI)、ルネサスシリアルペリフェラルインタフェース (RSPI)、A/D 変換器、割り込みコントローラ (INTC)、I/O ポート、コントローラエリアネットワーク (RCAN-ET)、データフラッシュ (FLD) などを内蔵しています。

また、SH7239 グループおよび SH7237 グループでは外部メモリアクセスサポート機能により、メモリや周辺 LSI と直接接続を行えます。これらにより、システムコストの大幅な低減が可能です。

表 1.1 に本 LSI の特長を示します。

表 1.1 特長

| 項目           | 特 長                                                |

|--------------|----------------------------------------------------|

| CPU          | • ルネサス独自の SuperH アーキテクチャ                           |

|              | ● SH-1、SH-2 とオブジェクトコードレベルで互換性あり                    |

|              | • 32 ビット内部データバス                                    |

|              | • 汎用レジスタアーキテクチャ                                    |

|              | 16 本の 32 ビット汎用レジスタ                                 |

|              | 4 本の 32 ビットコントロールレジスタ                              |

|              | 4 本の 32 ビットシステムレジスタ                                |

|              | 高速割り込み応答のためのレジスタバンク                                |

|              | • RISC タイプ命令セット(SH シリーズと上位互換性)                     |

|              | 命令長:コードの効率改善のための 16 ビット基本命令と性能、使い勝手向上のための 32 ビット命令 |

|              | ロードストアアーキテクチャ                                      |

|              | 遅延分岐命令                                             |

|              | C言語に基づく命令セット                                       |

|              | • 2 命令同時実行スーパースカラ                                  |

|              | • 命令実行時間:最大2命令/サイクル                                |

|              | • アドレス空間: 4G バイト                                   |

|              | • 乗算器内蔵                                            |

|              | • 5 段パイプライン                                        |

|              | • ハーバードアーキテクチャ                                     |

| FPU          | • 浮動小数点コプロセッサ内蔵                                    |

| (SH7239 グループ | ● 単精度(32 ビット)および倍精度(64 ビット)をサポート                   |

| のみ)          | ● IEEE754 に準拠したデータタイプおよび例外をサポート                    |

|              | ● 丸めモード: 近傍および 0 方向への丸め                            |

|              | ● 非正規化数の扱い:0 への切り捨て                                |

|              | ● 浮動小数点レジスタ                                        |

|              | 16 本の 32 ビット浮動小数点レジスタ                              |

|              | (単精度×16 ワードまたは倍精度×8 ワード)                           |

|              | 2 本の 32 ビット浮動小数点システムレジスタ                           |

|              | ● FMAC(乗算およびアキュムレート)命令をサポート                        |

|              | ● FDIV(除算)/FSQRT(平方根)命令をサポート                       |

|              | ● FLDI0/FLDI1(ロード定数 0/1)命令をサポート                    |

|              | ● 命令実行時間                                           |

|              | レイテンシ(FMAC/FADD/FSUB/FMUL):3 サイクル(単精度)、8 サイクル(倍精度) |

|              | ピッチ(FMAC/FADD/FSUB/FMUL):1 サイクル(単精度)、6 サイクル(倍精度)   |

|              | 【注】FMAC は単精度に対してのみサポートしています。                       |

|              | • 5 段パイプライン                                        |

| 項目          | 特 長                                              |

|-------------|--------------------------------------------------|

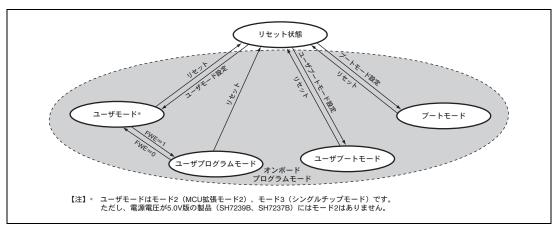

| 動作モード       | • 動作モード                                          |

|             | MCU 拡張モード 2(SH7239A、SH7237A のみ)                  |

|             | シングルチップモード                                       |

|             | ● 処理状態                                           |

|             | プログラム実行状態                                        |

|             | 例外処理状態                                           |

|             | バス権解放状態                                          |

|             | ● 低消費電力状態                                        |

|             | スリープモード                                          |

|             | ソフトウェアスタンバイモード                                   |

|             | モジュールスタンバイモード                                    |

| ROM キャッシュ   | • 命令/データ分離方式                                     |

|             | • 命令プリフェッチキャッシュ: フルセットアソシアティブ                    |

|             | • 命令プリフェッチミスキャッシュ: フルセットアソシアティブ                  |

|             | • データキャッシュ: フルセットアソシアティブ                         |

|             | • ラインサイズ 16 バイト                                  |

|             | • ハードウェアプリフェッチ機能(連続・分岐プリフェッチ)                    |

| 割り込みコントロー   | ● 8 本の外部割り込み端子(NMI、IRQ6~IRQ0)                    |

| ラ(INTC)     | • 内蔵周辺割り込み:モジュールごとに優先順位を設定                       |

|             | • 16 レベルの優先順位設定が可能                               |

|             | • レジスタバンクにより割り込み処理に伴うレジスタの退避/復帰を高速に行うことが可能       |

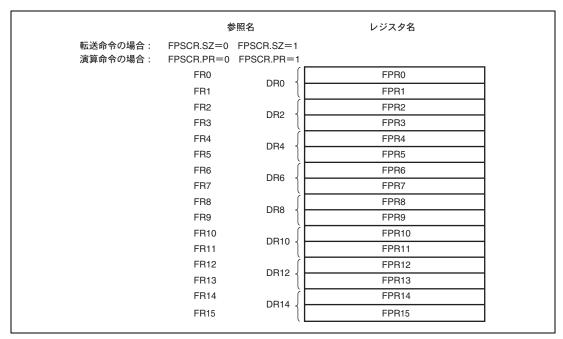

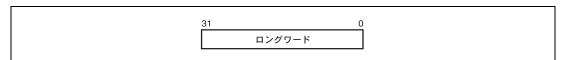

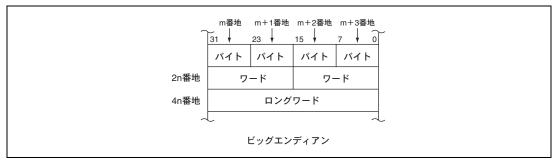

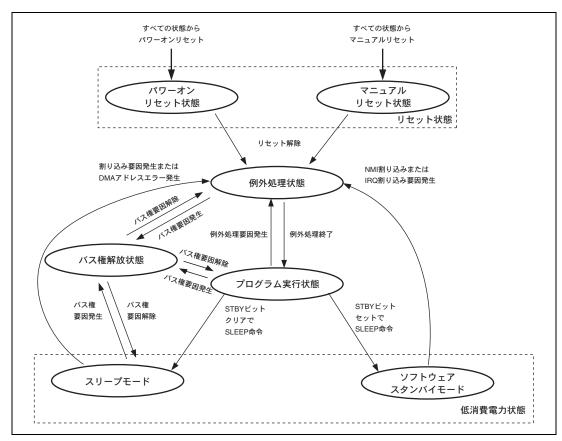

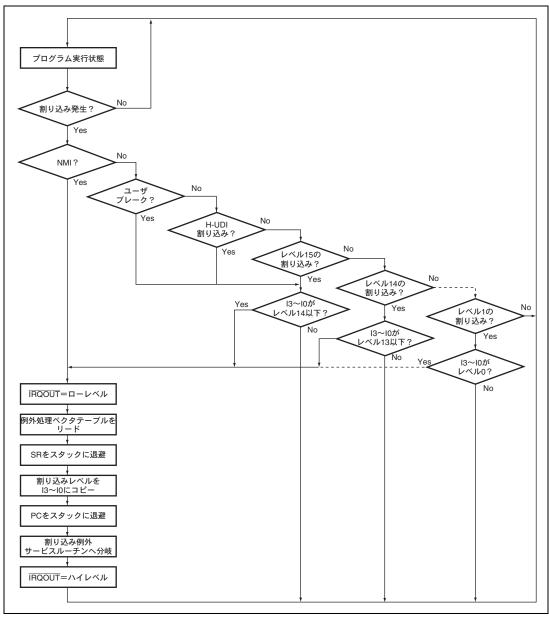

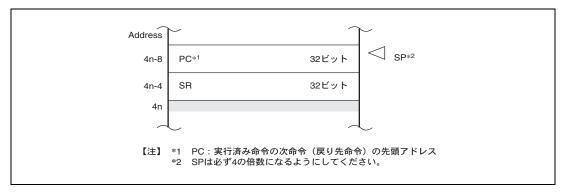

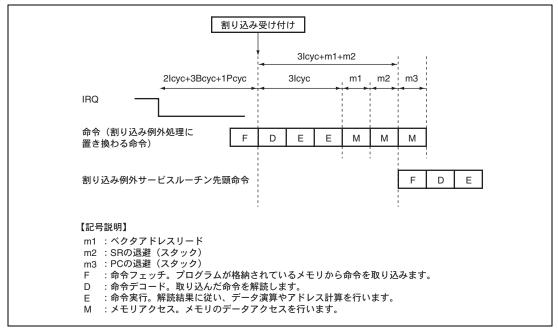

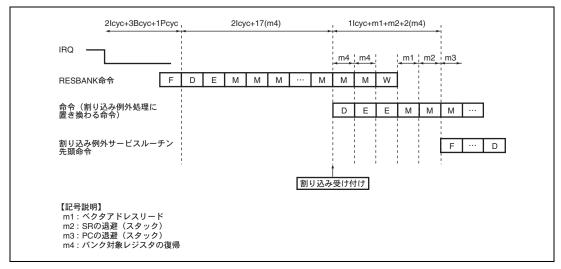

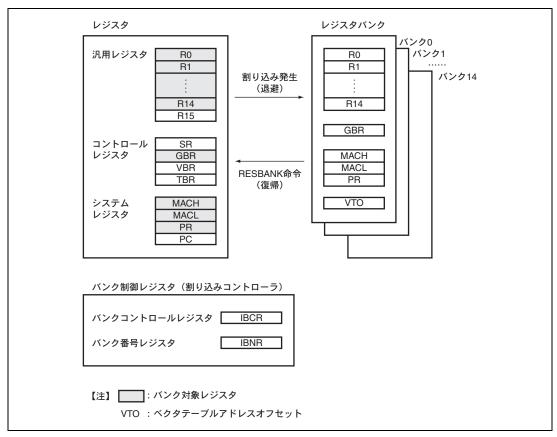

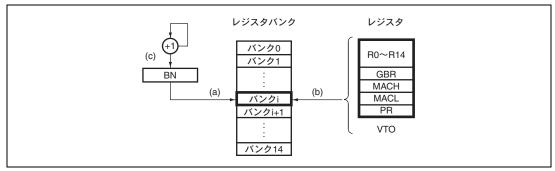

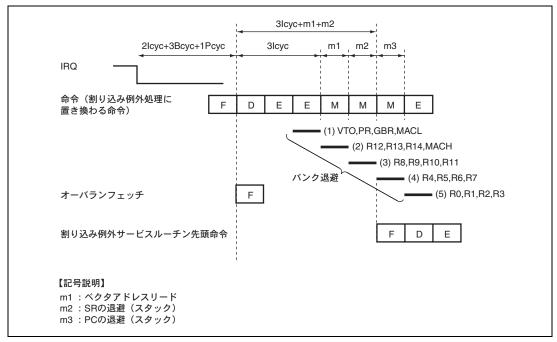

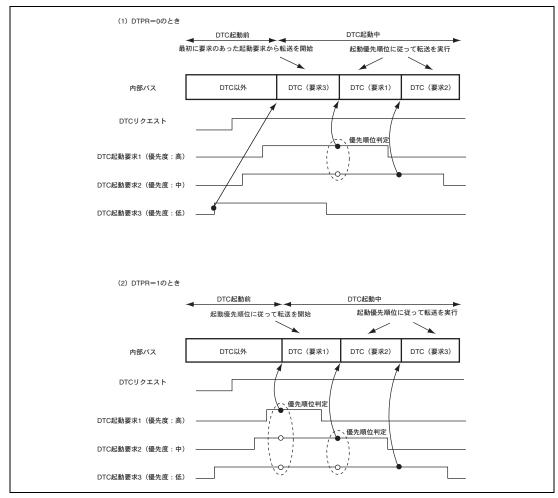

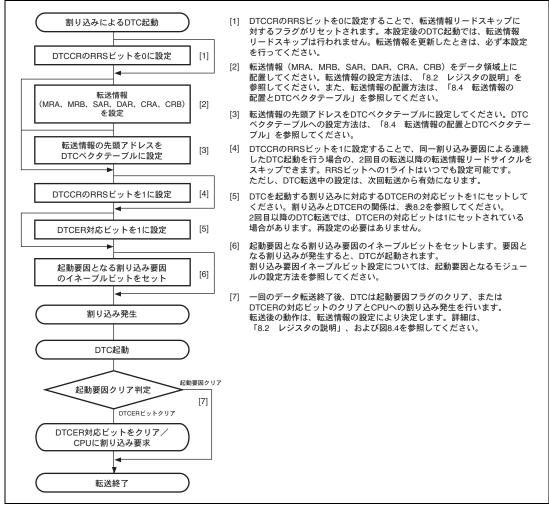

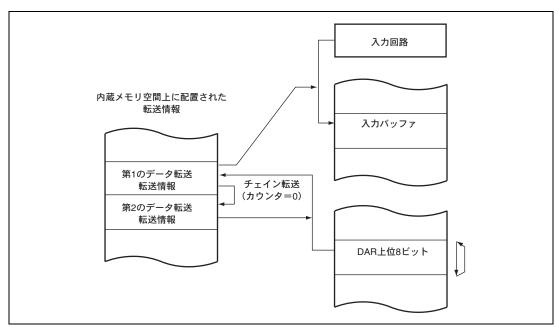

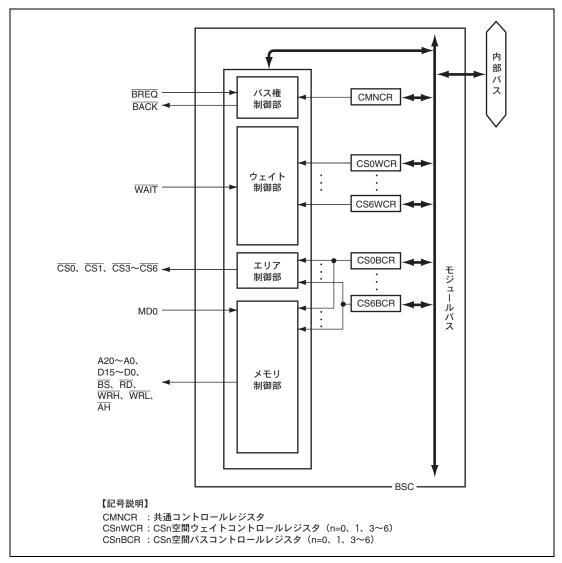

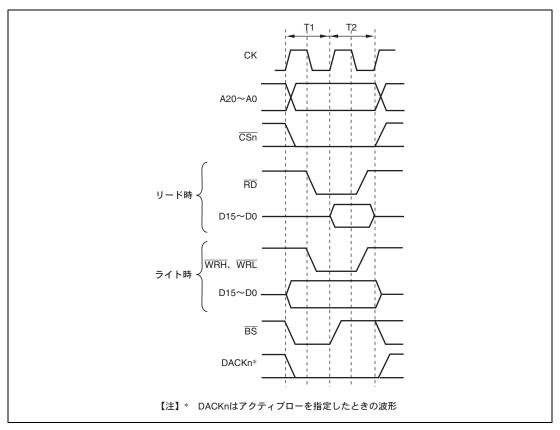

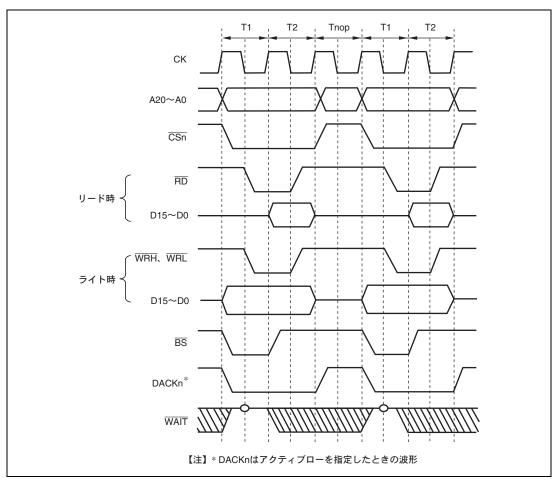

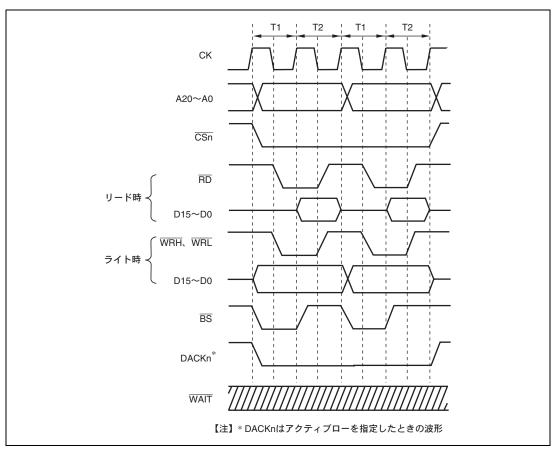

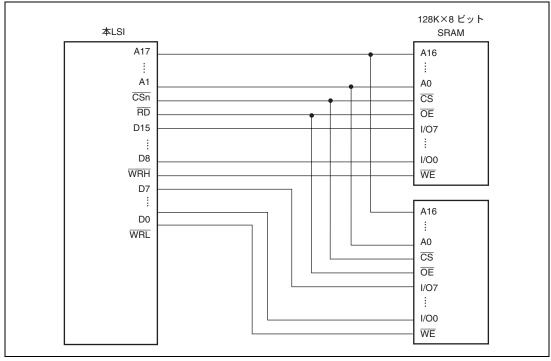

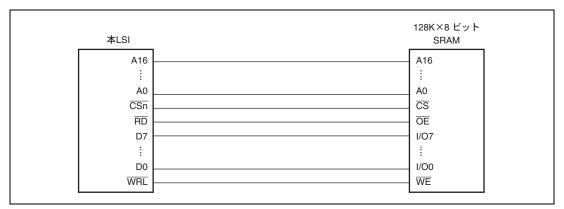

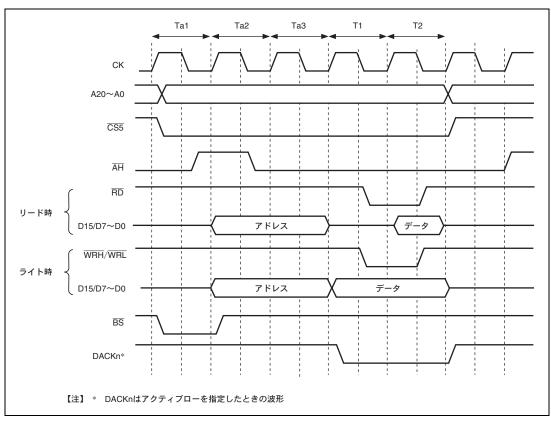

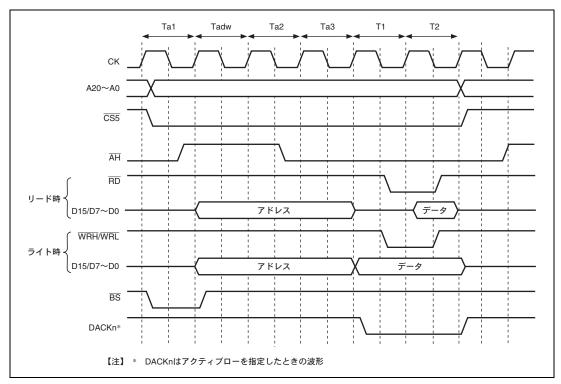

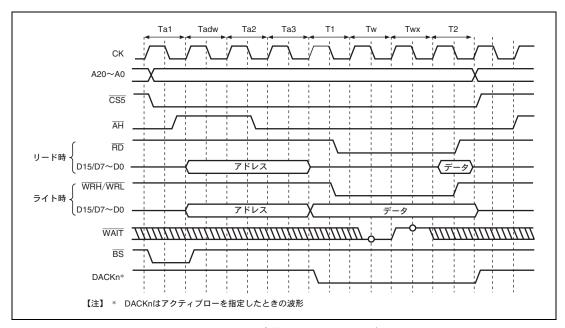

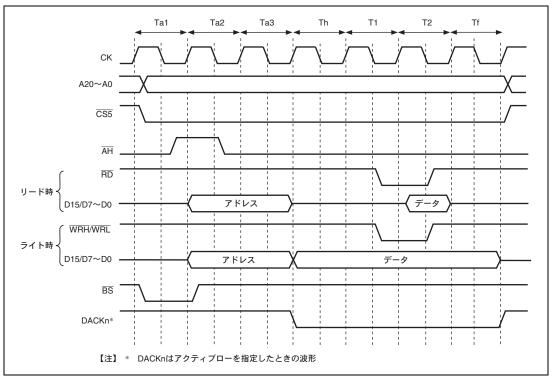

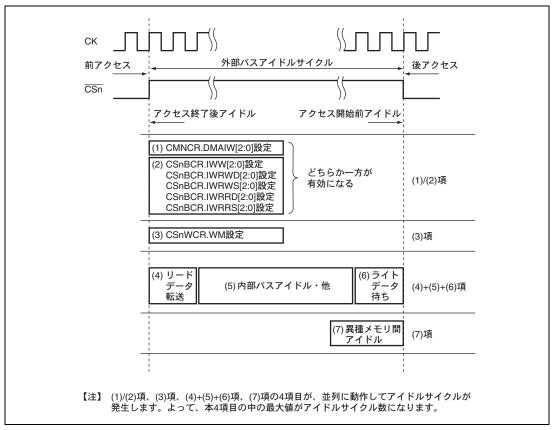

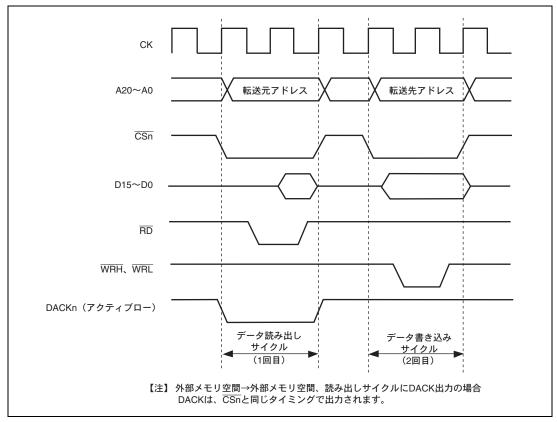

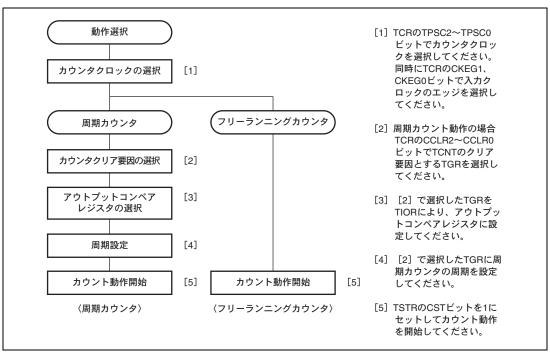

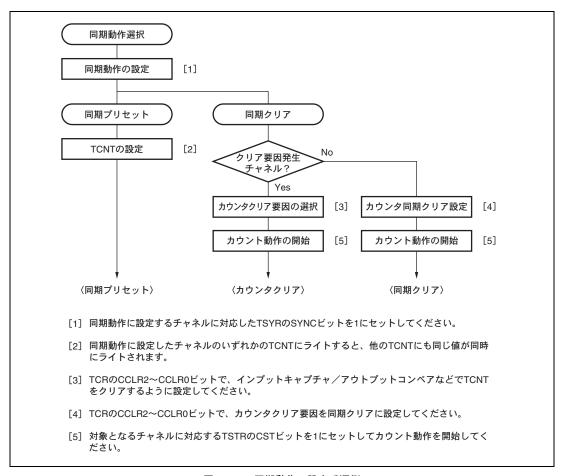

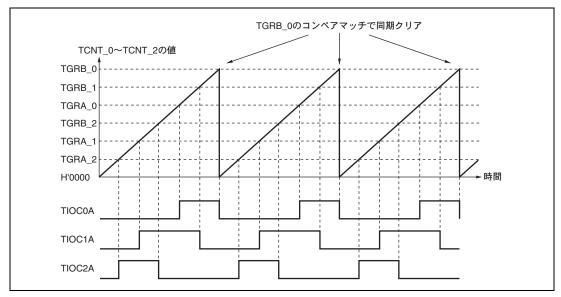

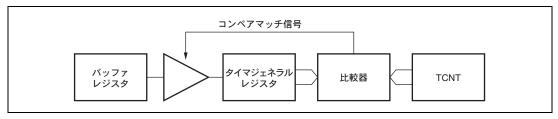

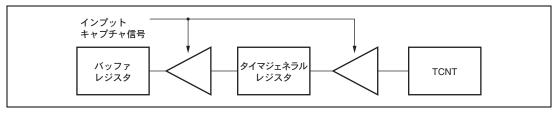

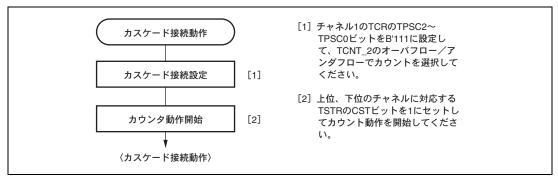

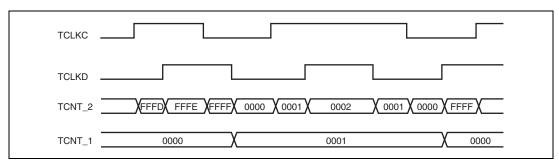

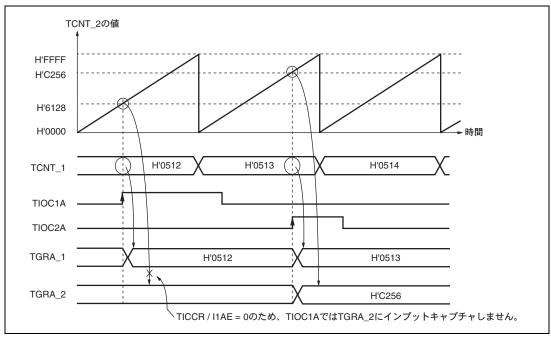

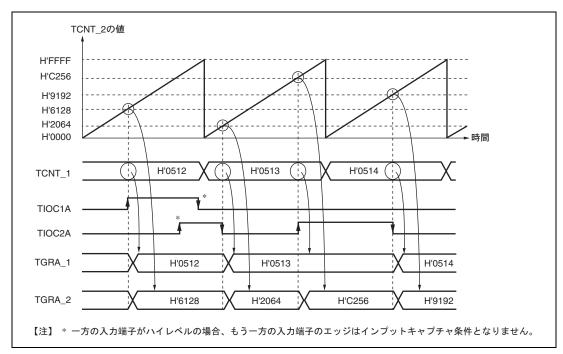

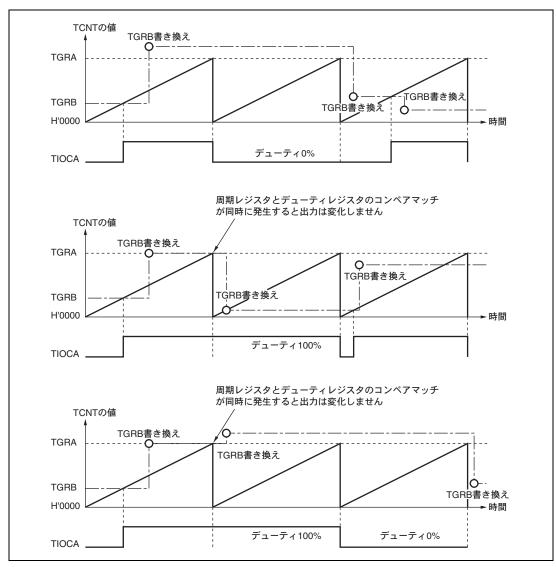

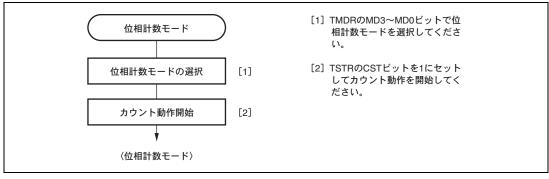

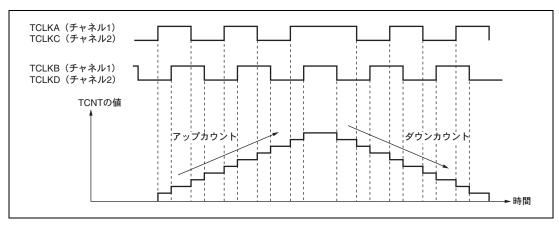

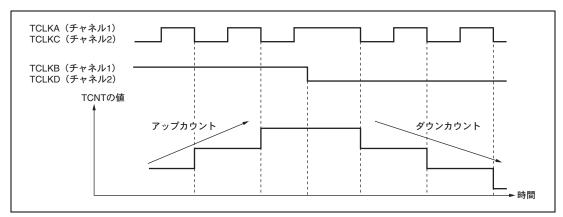

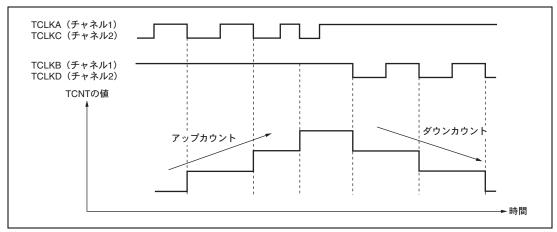

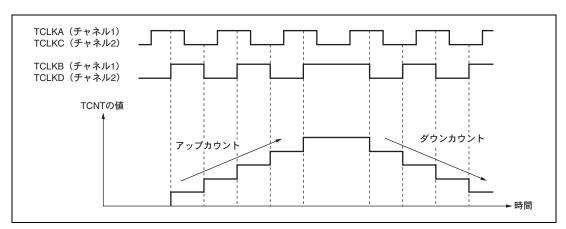

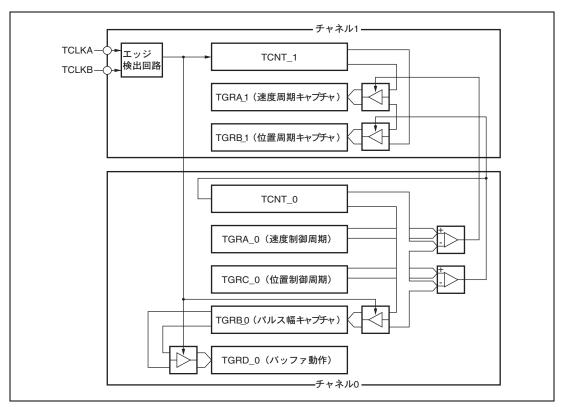

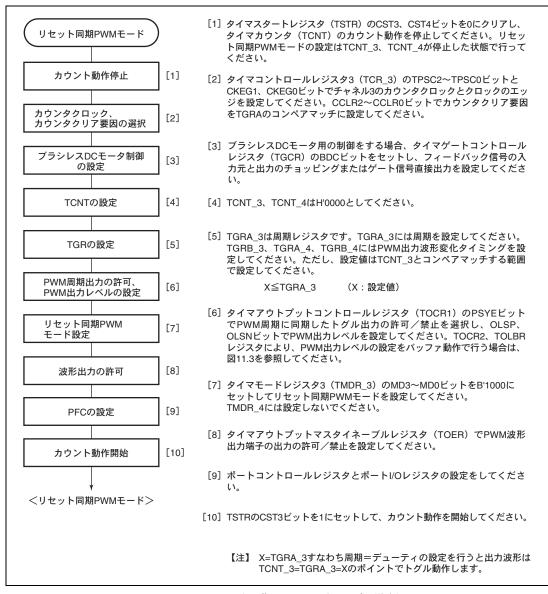

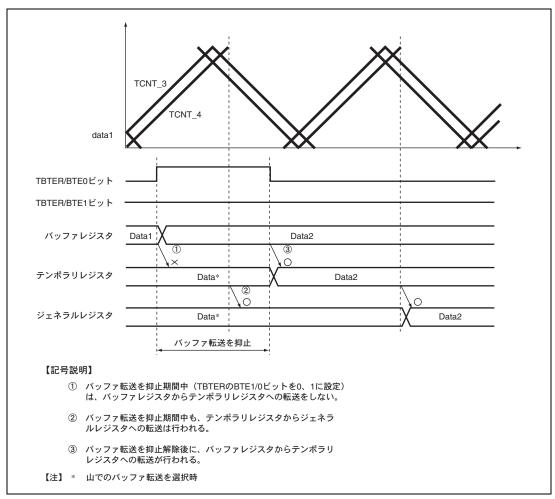

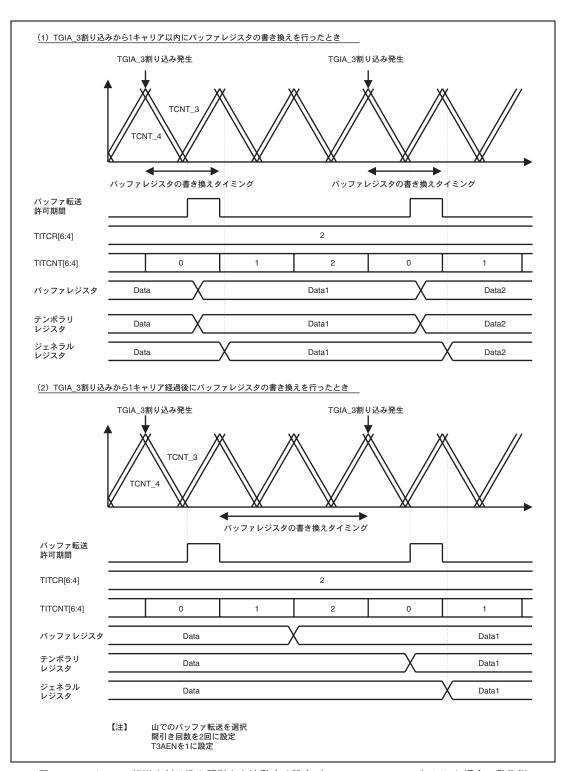

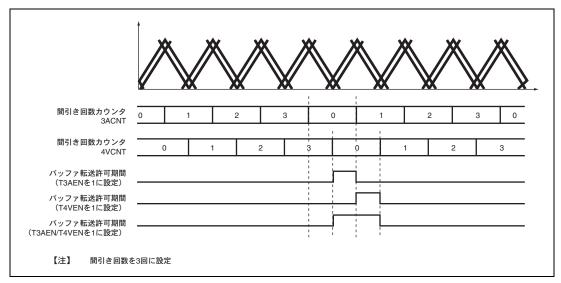

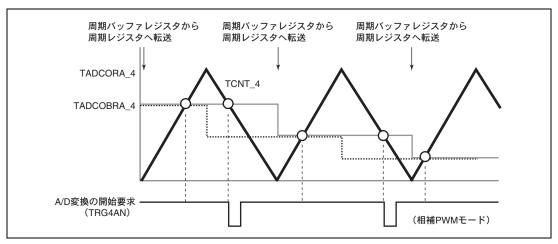

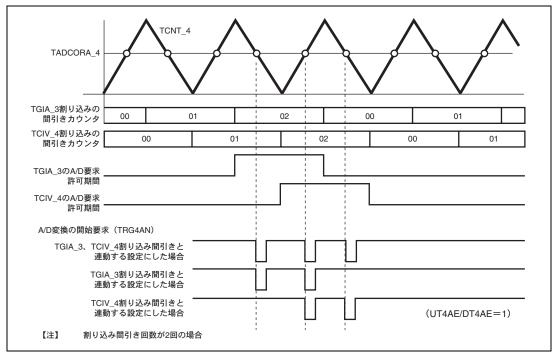

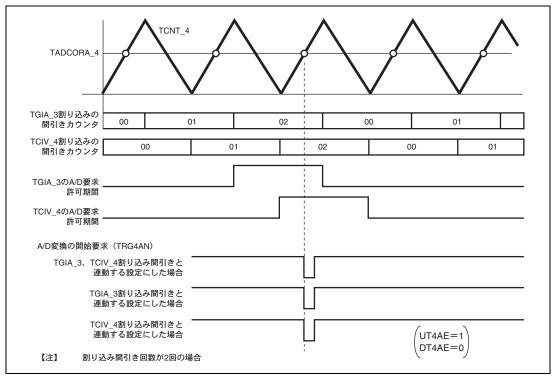

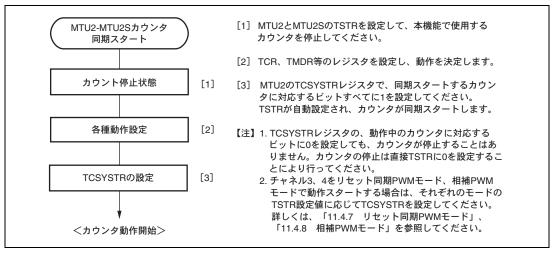

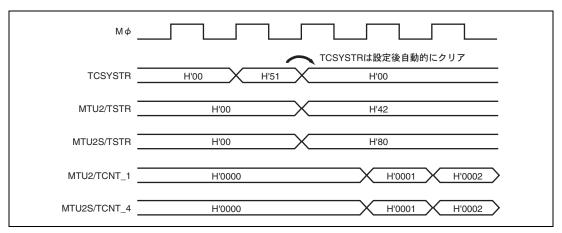

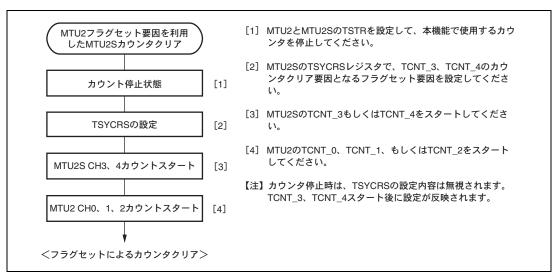

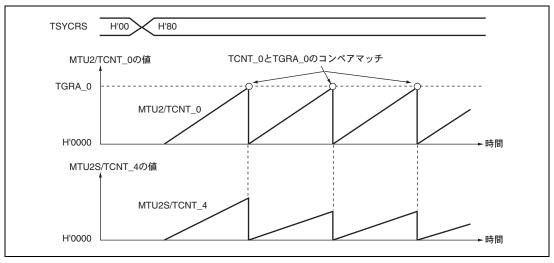

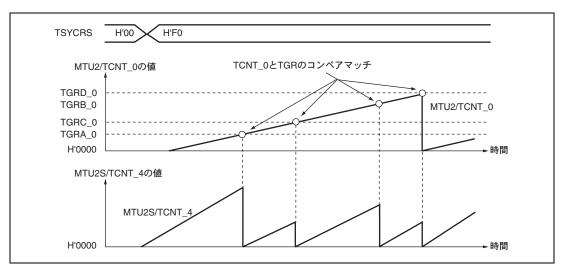

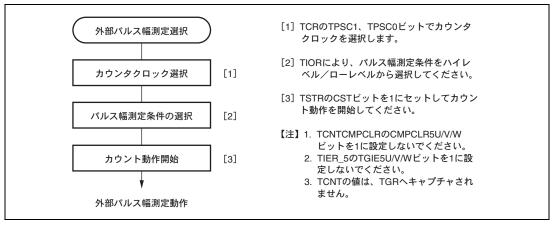

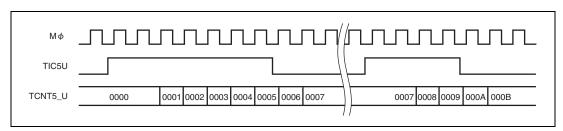

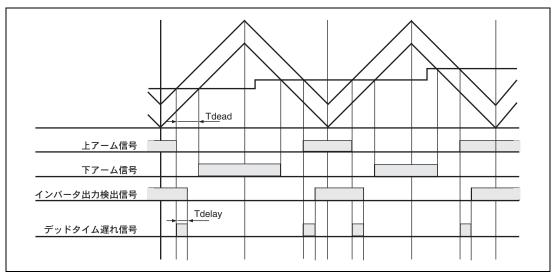

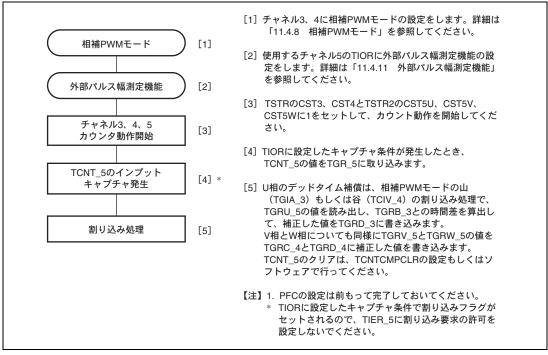

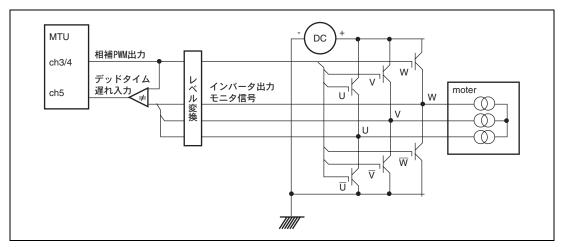

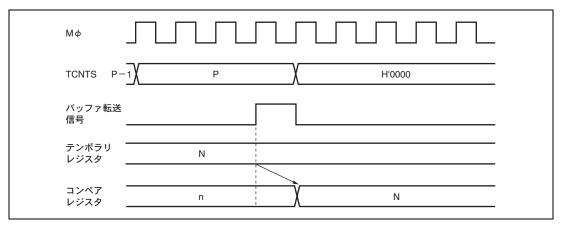

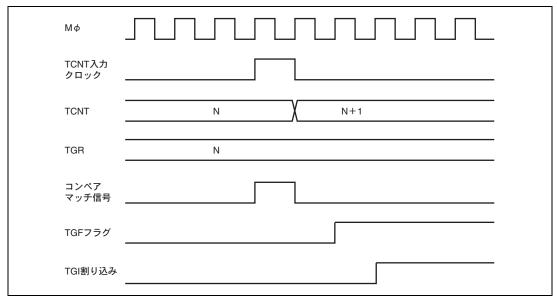

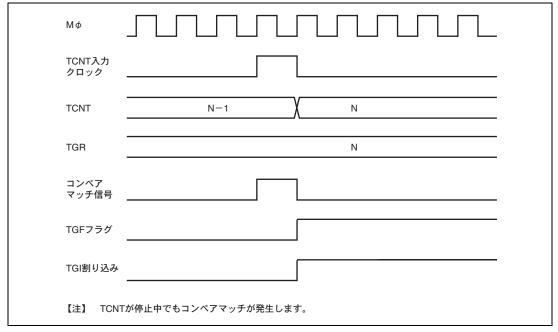

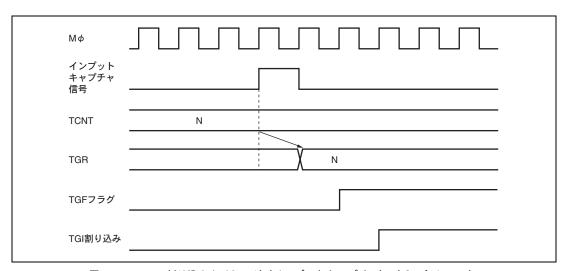

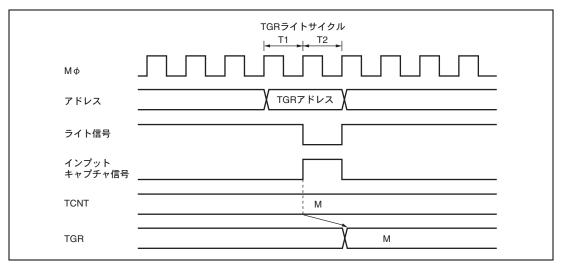

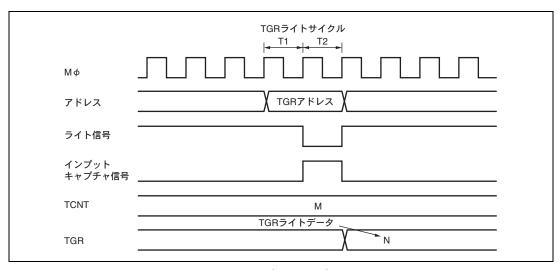

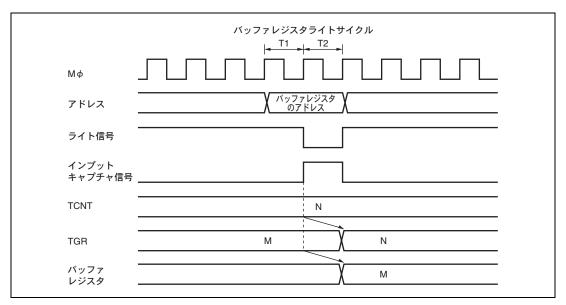

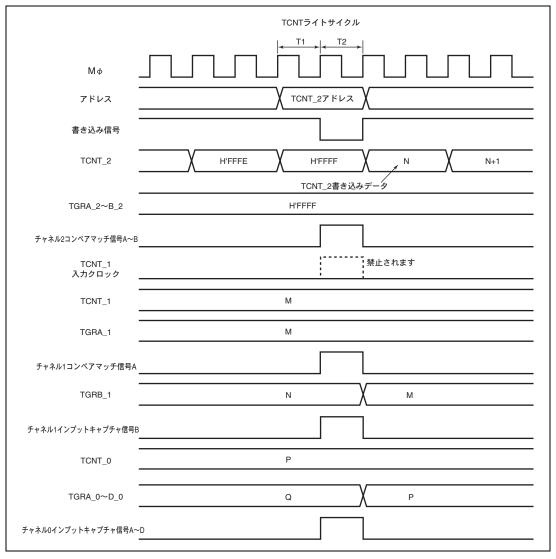

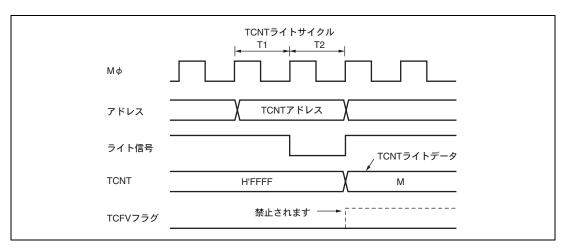

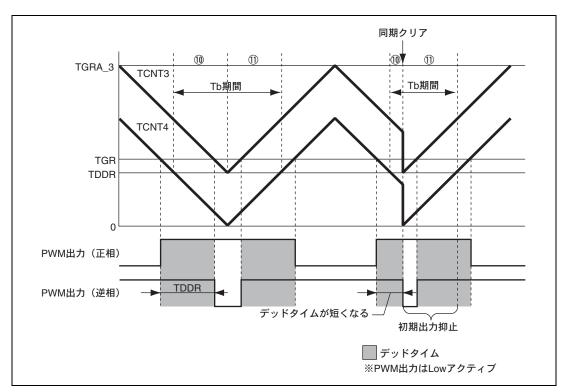

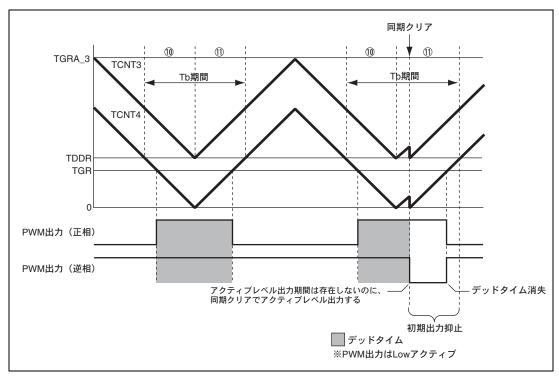

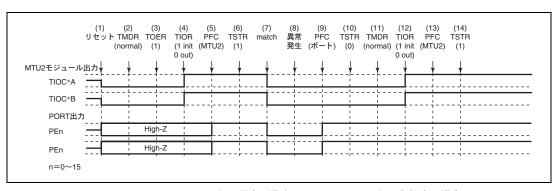

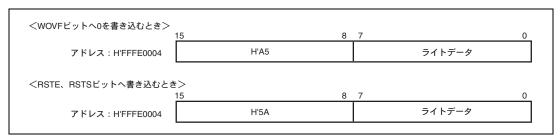

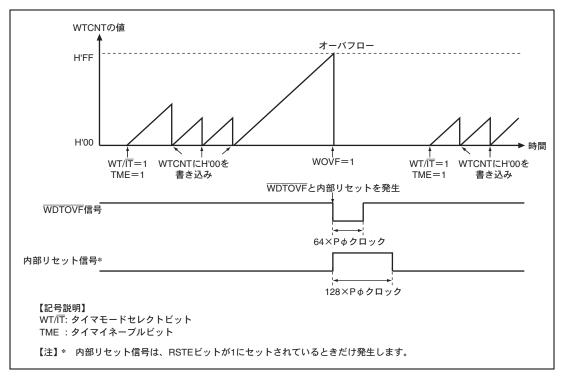

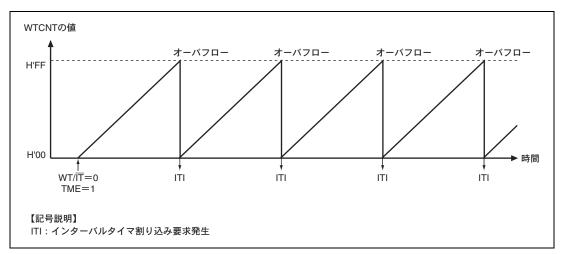

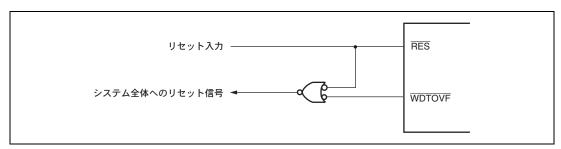

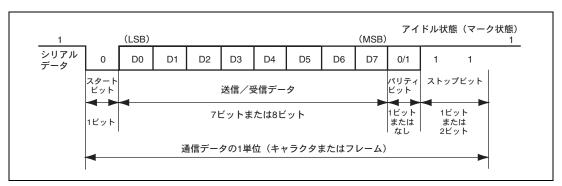

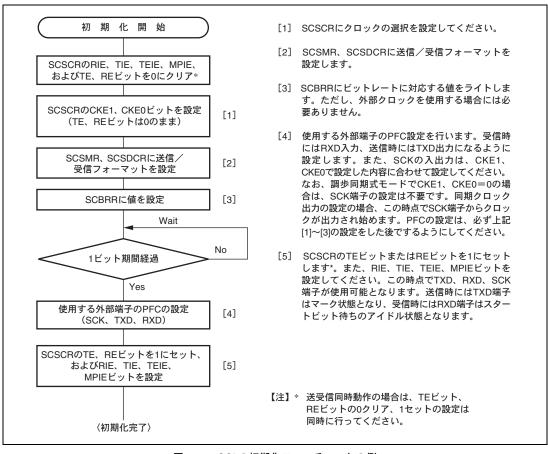

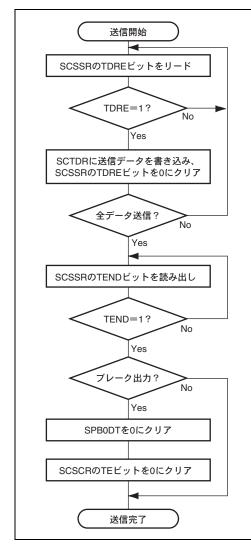

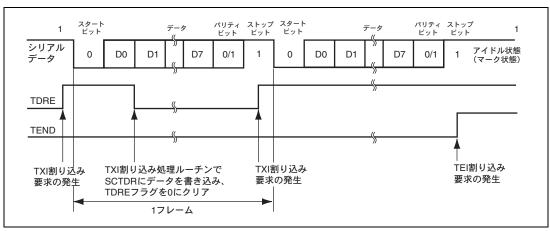

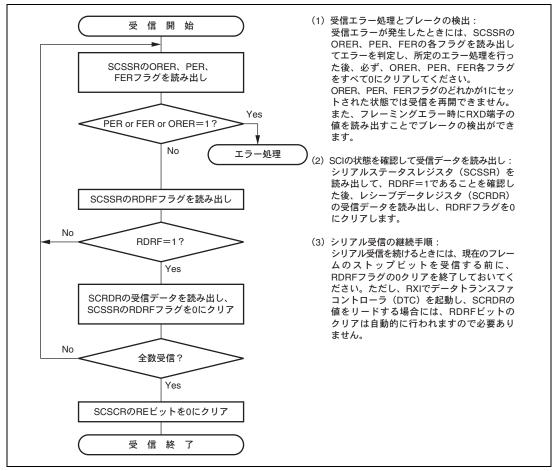

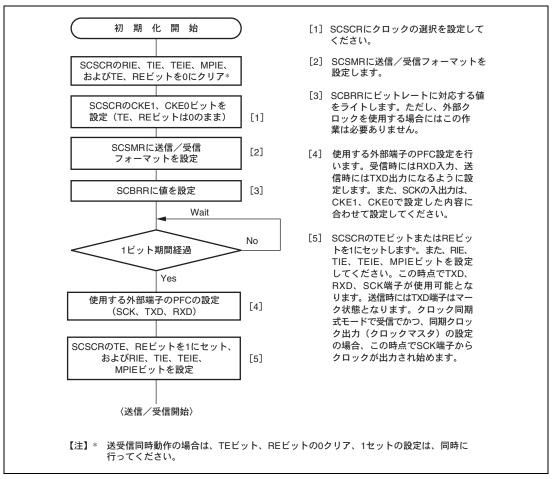

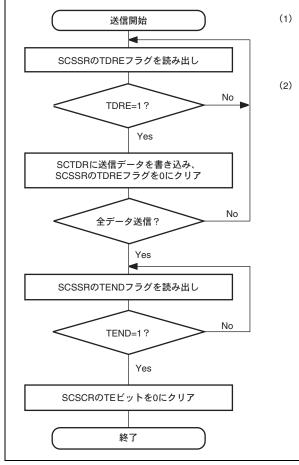

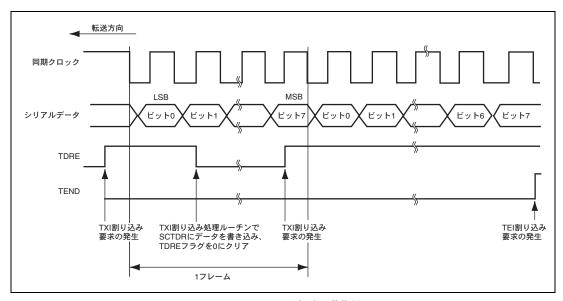

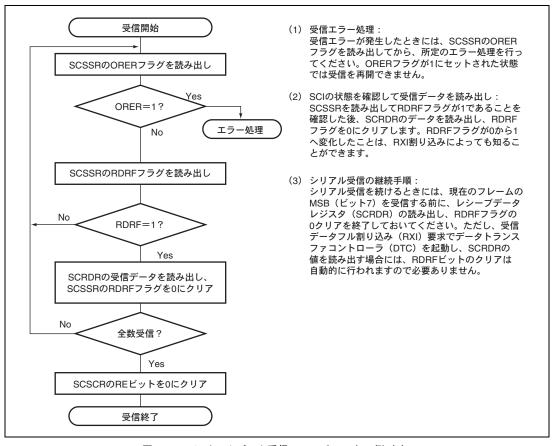

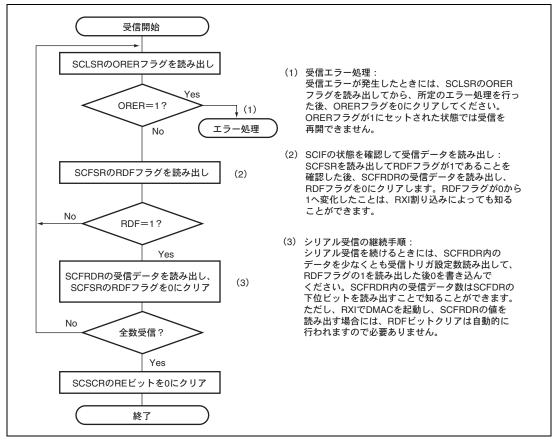

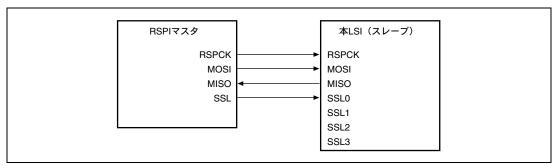

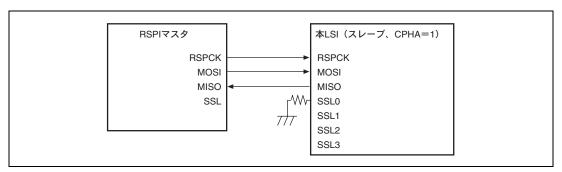

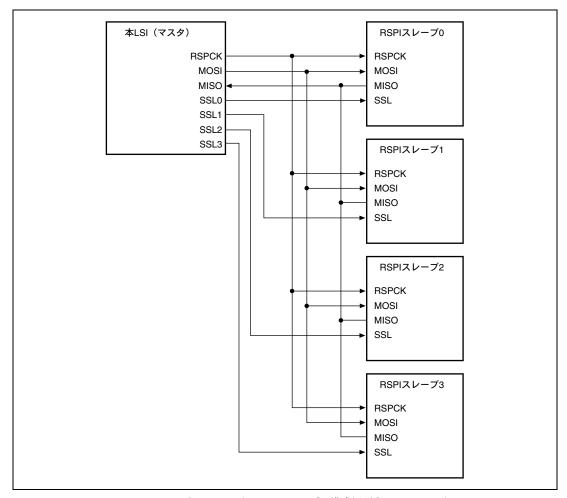

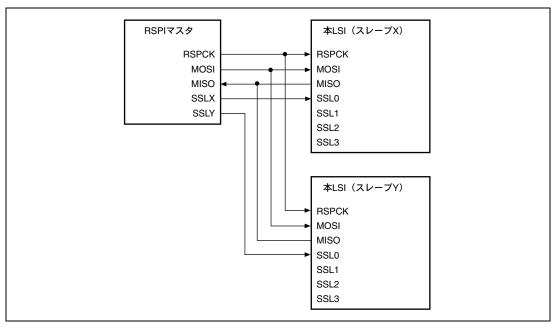

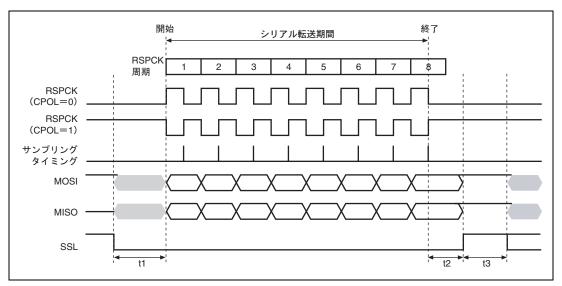

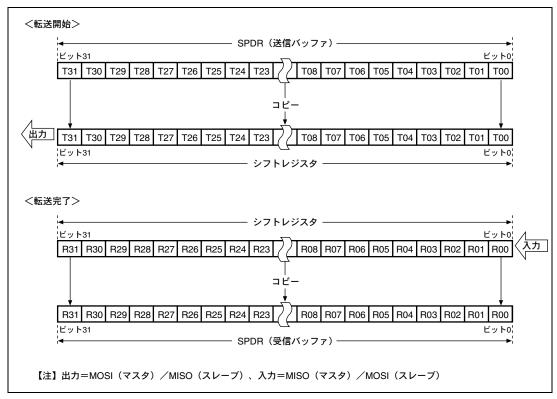

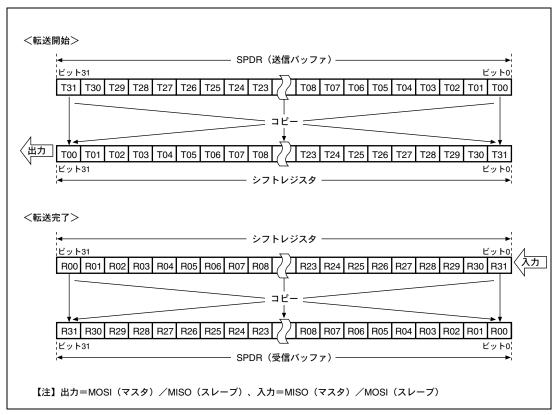

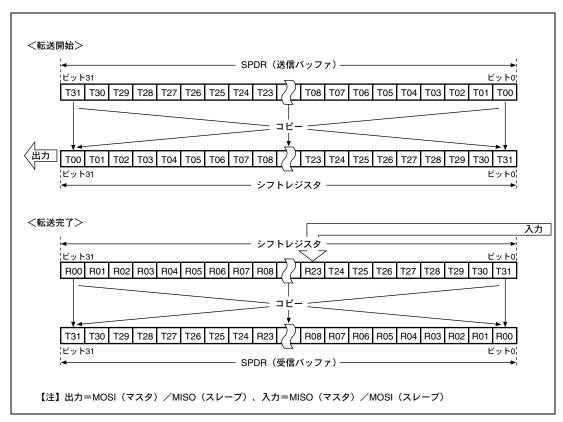

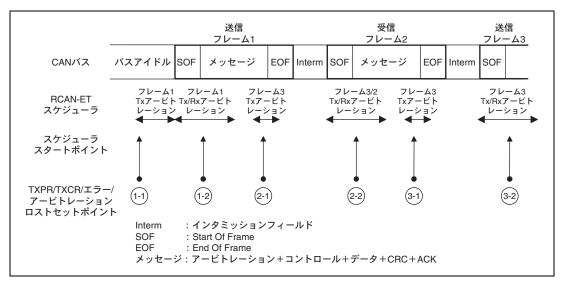

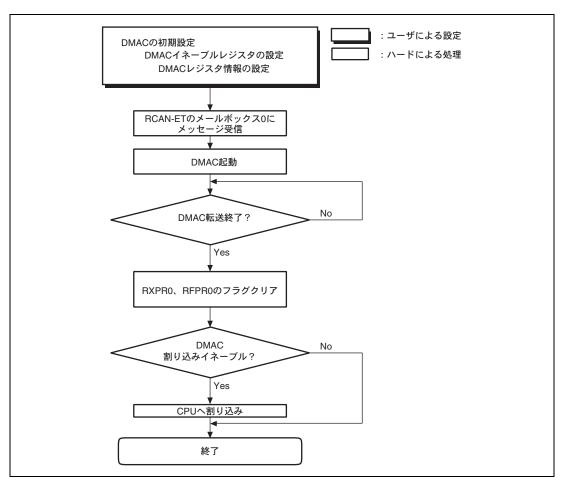

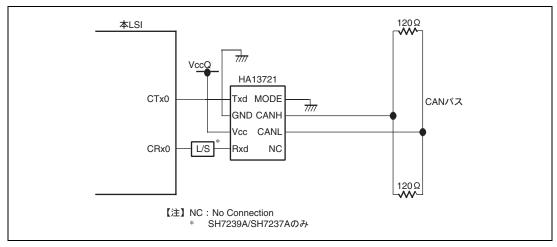

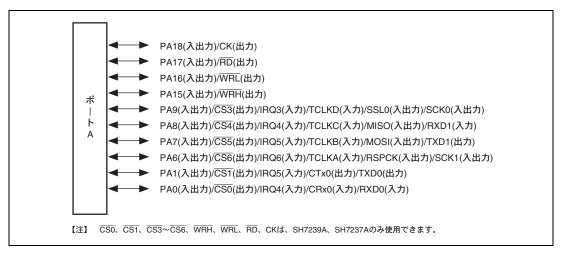

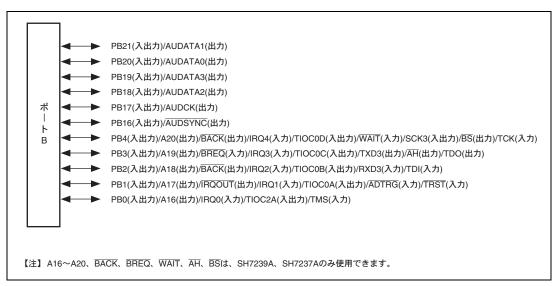

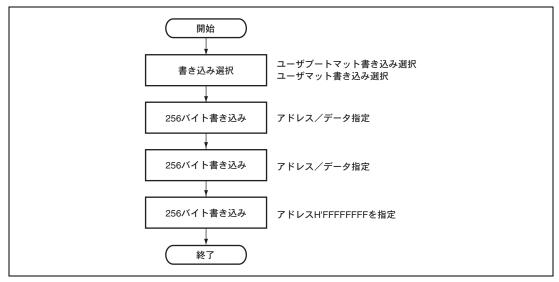

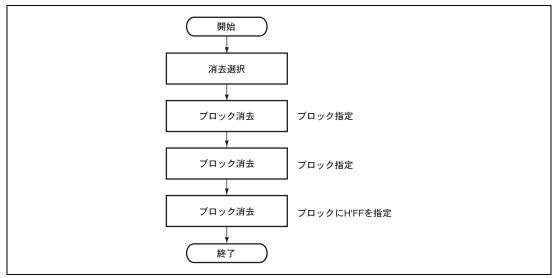

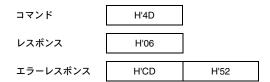

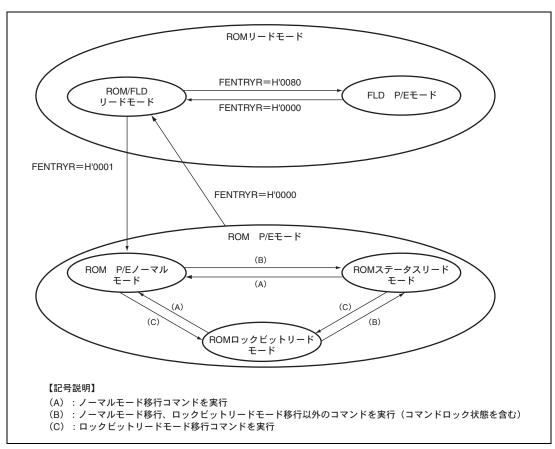

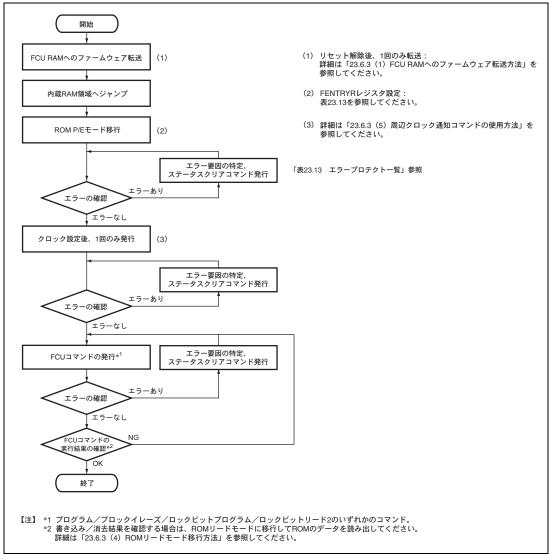

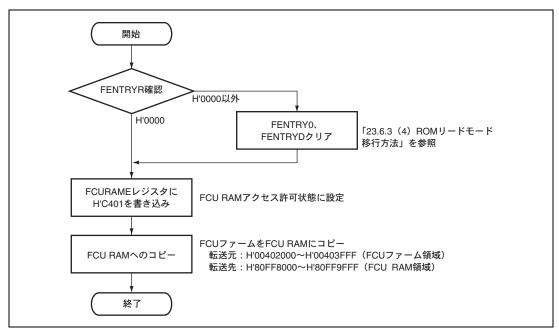

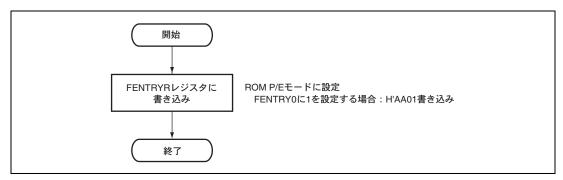

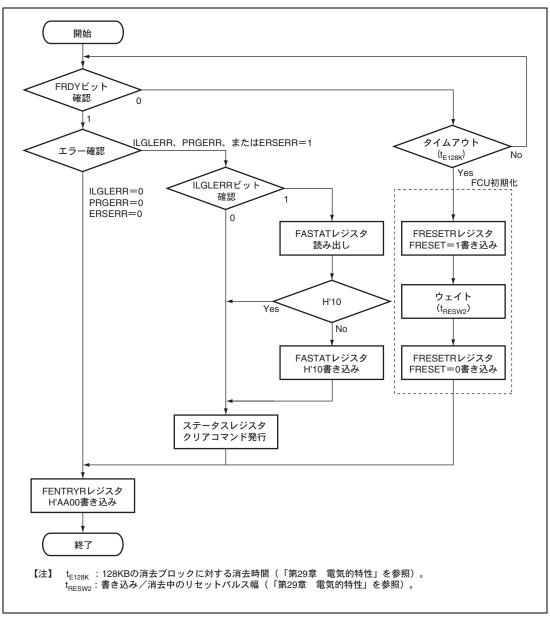

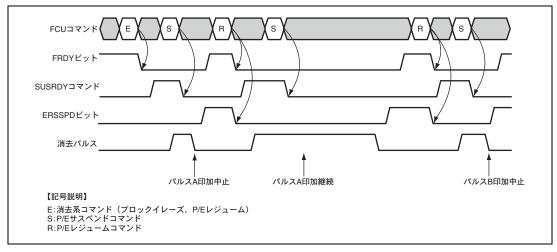

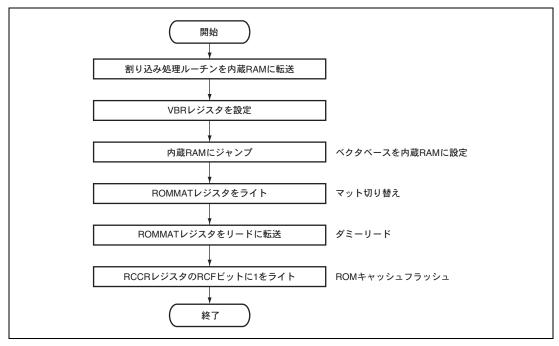

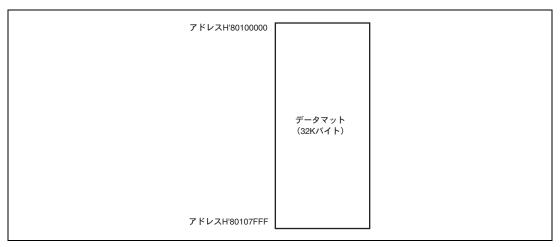

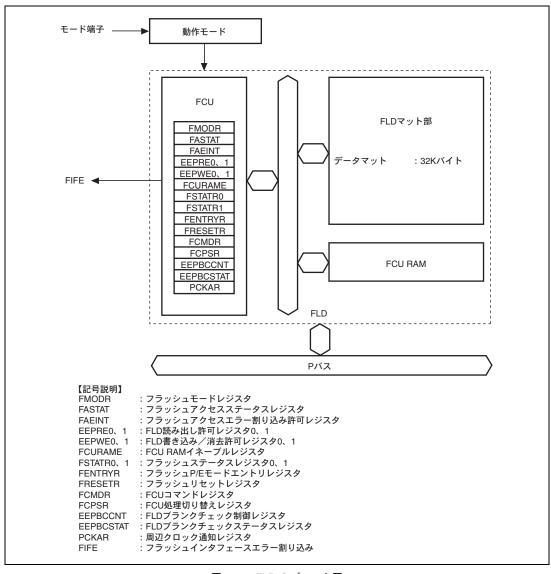

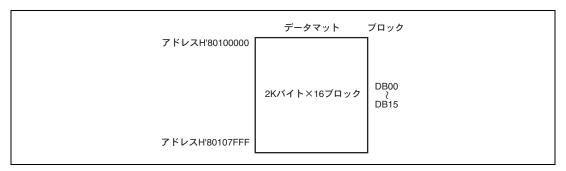

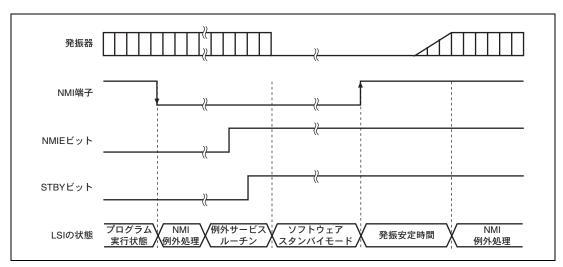

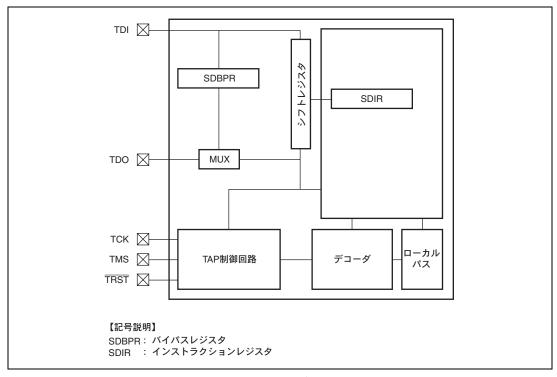

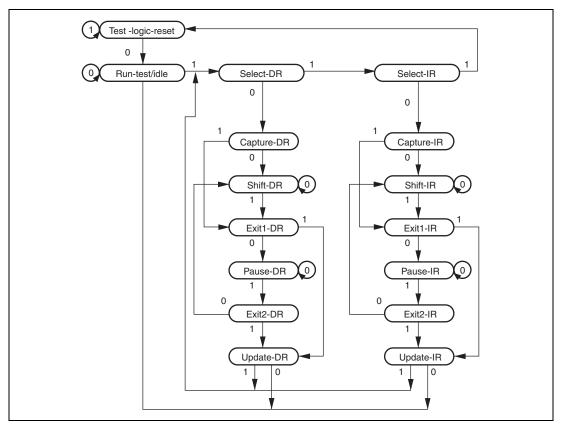

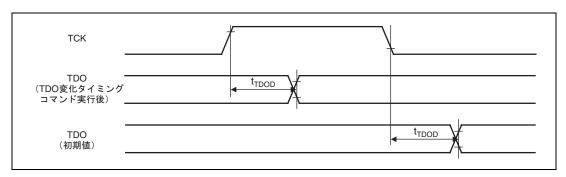

| バスステートコント   | ● アドレス空間はそれぞれ最大 2M バイトの 6 つの領域(エリア 0、1、3~6)をサポート |