# SH726A グループ、SH726B グループ

ユーザーズマニュアル ハードウェア編

ルネサス 32 ビット RISC マイクロコンピュータ SuperH<sup>™</sup> RISC engine ファミリ / SH7260 シリーズ

> SH726A R5S726A

> **SH726B** R5S726B

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、

産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命

維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用 に際しては、特定の物質の含有・使用を規制するRoHS指令等、適用される環境関連法令を十分調査のうえ、 かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお 断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

## 製品に関する一般的注意事項

### 1. NC 端子の処理

【注意】NC端子には、何も接続しないようにしてください。

NC(Non-Connection)端子は、内部回路に接続しない場合の他、テスト用端子やノイズ軽減などの目的で使用します。このため、NC端子には、何も接続しないようにしてください。

接続された場合については保証できません。

### 2. 未使用入力端子の処理

【注意】未使用の入力端子は、ハイまたはローレベルに固定してください。

CMOS製品の入力端子は、一般にハイインピーダンス入力となっています。未使用端子を開放状態で動作させると、周辺ノイズの誘導により中間レベルが発生し、内部で貫通電流が流れて誤動作を起こす恐れがあります。

未使用の入力端子は、ハイまたはローレベルに固定してください。

#### 3. 初期化前の処置

【注意】電源投入時は、製品の状態は不定です。

すべての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの間、内部回路は 不確定であり、レジスタの設定や各端子の出力状態は不定となります。この不定状態によってシ ステムが誤動作を起こさないようにシステム設計を行ってください。

リセット機能を持つ製品は、電源投入後は、まずリセット動作を実行してください。

4. 未定義・リザーブアドレスのアクセス禁止

【注意】未定義・リザーブアドレスのアクセスを禁止します。

未定義・リザーブアドレスは、将来の機能拡張用の他、テスト用レジスタなどが割り付けられている場合があります。

これらのレジスタをアクセスしたときの動作および継続する動作については、保証できませんので、アクセスしないようにしてください。

5. 各レジスタリザーブビットの読み出し/書き込み

各モジュールで使用されるレジスタのリザーブビットは、その説明記述中に読み出し/書き込み 値の指定が特にない限り以下のように取り扱ってください。

読み出すと常に0が読み出されます。書き込む場合は、0を書き込むか、直前に読み出した値を書き込むかいずれかにしてください。

直前に読み出した値を書き込むようにしておくと、将来このビットに拡張機能を割り当てることがある場合、その拡張機能に影響を与えない利点があります。

# 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品に関する一般的注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 目次

- 5. 概要

- 6. 各機能モジュールの説明

- · CPU およびシステム制御系

- ・内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュール毎に異なりますが、一般的には、 ①特長、②入出力端子、③レジスタの説明、④動作説明、⑤使用上の注意事項 等の節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認の上設計してください。 各章の本文中には説明に対する注意事項と、各章の最後には使用上の注意事項があります。 必ずお読みください(使用上の注意事項は必要により記載されます)。

- 7. レジスタ一覧

- 8. 電気的特性

- 9. 端子状態と処理方法

- 10. 付録

- 11. 本版で改訂または追加された主な箇所(改訂版のみ適用)

改定来歴は、前版の記載内容について訂正・追加された主な箇所についてまとめたものです。 改定内容の全てについて記載したものではありませんので、詳細については、本書の本文上で ご確認ください。

12. 索引

# はじめに

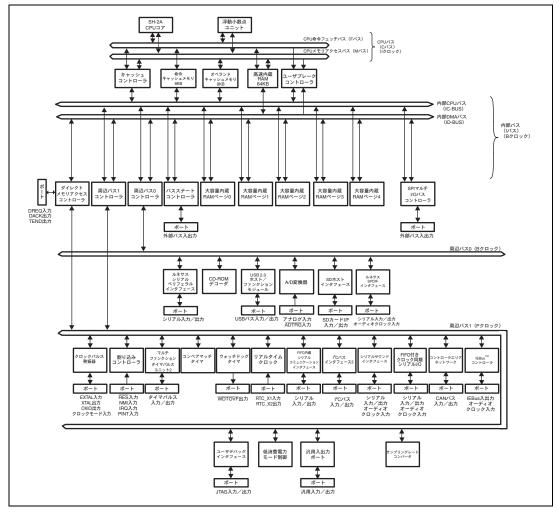

本 LSI は、ルネサスオリジナルの RISC 方式の CPU をコアにして、システム構成に必要な周辺機能を集積した RISC マイコンです。

- 対象者 本マニュアルは、本 LSI を用いた応用システムを設計するユーザを対象としています。本マニュアル を使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する基本的な知識を 必要とします。

- 目的 本マニュアルは、本 LSI のハードウェア機能と電気的特性をユーザに理解していただくことを目的に しています。

## 読み方

- 機能全体を理解しようとするとき

- → 目次に従って読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

- CPU機能の詳細を理解したいとき

- → 別冊の「SH-2A、SH2A-FPU ユーザーズマニュアル ソフトウェア編」を参照してください。

- レジスタ名がわかっていて、詳細機能を知りたいとき

- → 本書の後ろに、「**索引」**があります。索引からページ番号を検索してください。

「第34章 レジスター覧」にアドレス、ビット内容、初期化についてまとめています。

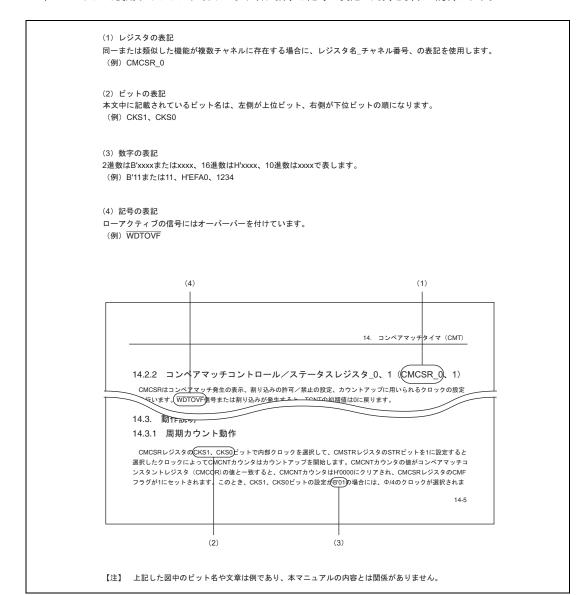

#### 凡例

本マニュアルで使用するレジスタ名やビット名、数字や記号の表記の凡例を以下に説明します。

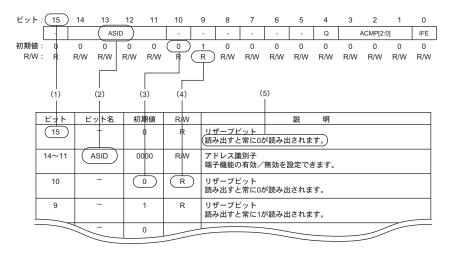

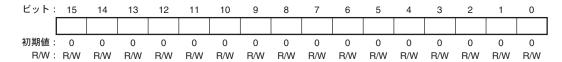

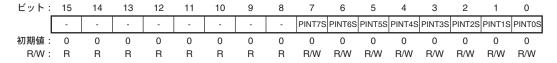

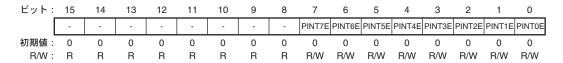

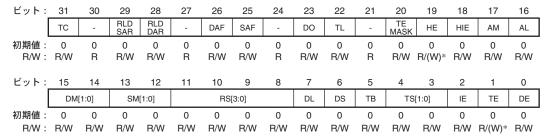

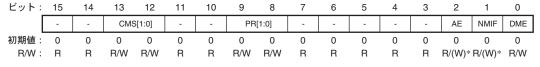

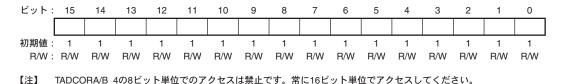

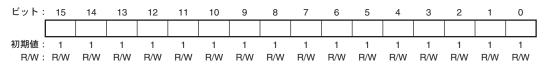

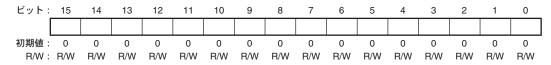

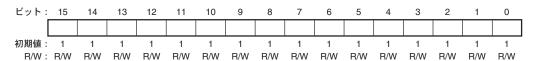

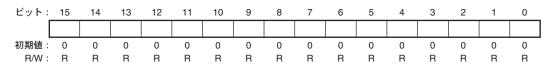

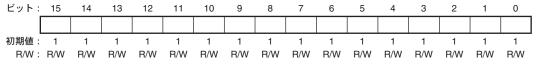

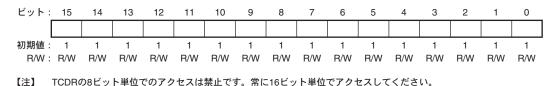

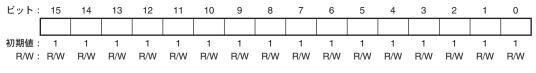

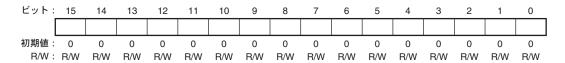

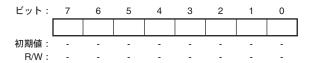

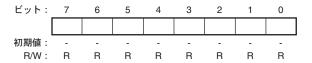

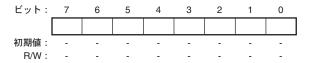

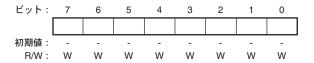

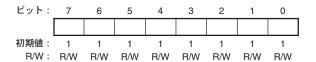

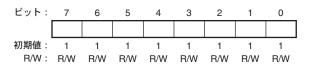

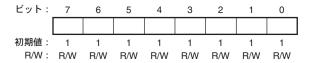

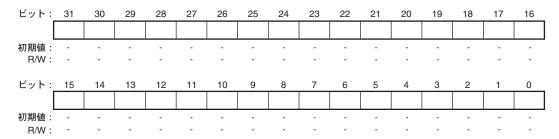

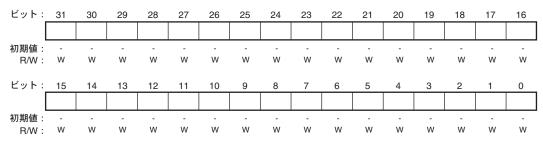

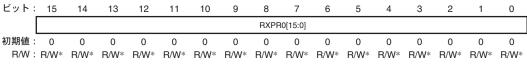

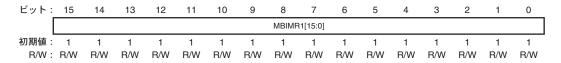

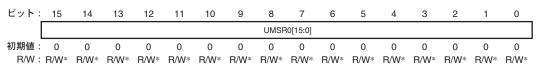

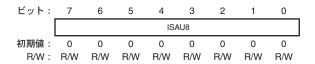

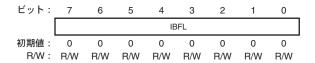

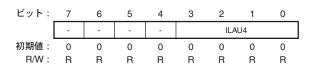

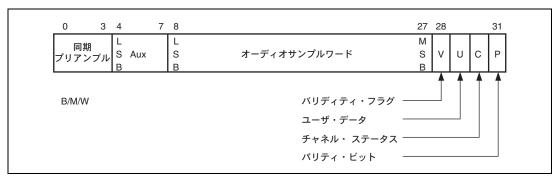

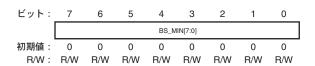

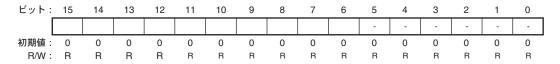

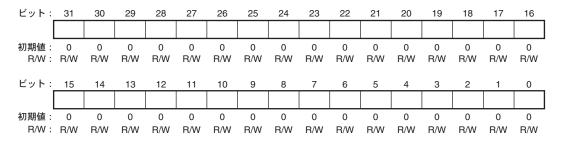

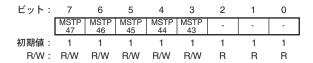

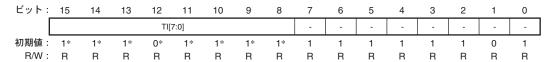

• ビット図とビット表の表記

各レジスタの説明には、ビットの並びを示すビット図とビットに設定する内容を説明するビット表があります。

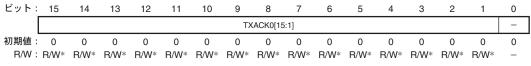

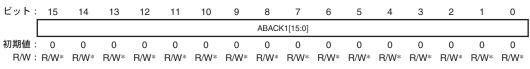

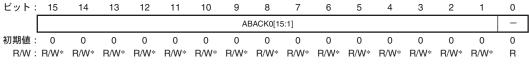

#### (1) ビット

ビット番号を示します。

32ビットレジスタの場合は31から0の順に、16ビットレジスタの場合は15から0の順に示します。

#### (2) ビット名

レジスタのビット名またはフィールド名を示します。

フィールドでビット桁数を明示する必要があるときは、ASID[3:0]というように桁数の表記を追加します。

また、リザーブビットの場合は「-」と表記します。

ただし、タイムカウンタなどをはじめとして、ビット名の記載をせずに空白のままとしているものもあります。

#### (3) 初期値

各ビットのパワーオンリセット後の値を初期値として示します。

0 : 初期値は0であることを示します。

1 : 初期値は1であることを示します。

- : 初期値は不定であることを示します。

#### (4) R/W

各ビットが読み出し可能か、書き込み可能か、または書き込みも読み出しも不可であるかを示します。 使用する表記を以下に説明します。

R/W:読み出しおよび書き込みが可能なビットまたはフィールドです。

R/(W) : 読み出しおよび書き込みが可能なビットまたはフィールドです。

ただし書き込みは、フラグをクリアするための書き込みのみ可能です。

R:読み出しが可能なビットまたはフィールドです。

ただし、リザーブビットはすべて「R」と表記します。書き込む必要がある場合は、

ビット表で指定された値または初期値を書き込んでください。

W:書き込みが可能なビットまたはフィールドです。

ただし、読み出すときの値は、ビット表に記載してある場合以外は保証されません。

#### (5) 説明

ビットを設定することで可能となる機能について説明しています。

【注】 上記した図中のビット名や文章は例であり、本マニュアルの内容とは関係がありません。

# 目次

| 1. 櫻  | 现要                      | 1-1  |

|-------|-------------------------|------|

| 1.1   | SH726A/726Bの特長          | 1-1  |

| 1.2   | 製品一覧                    | 1-9  |

| 1.3   | ブロック図                   | 1-10 |

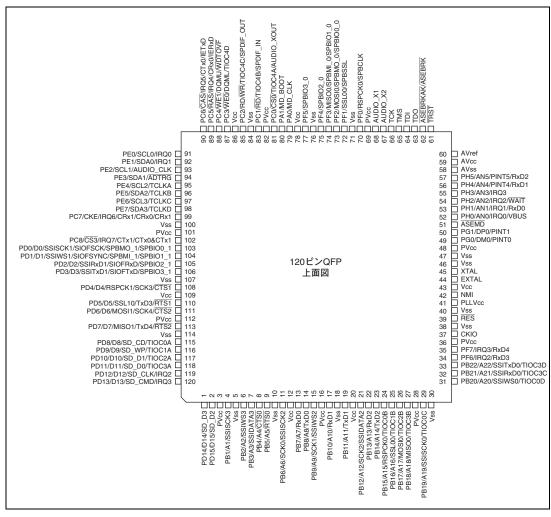

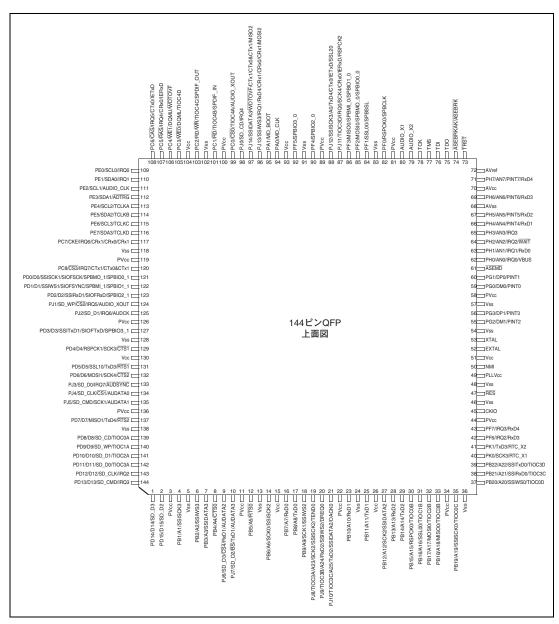

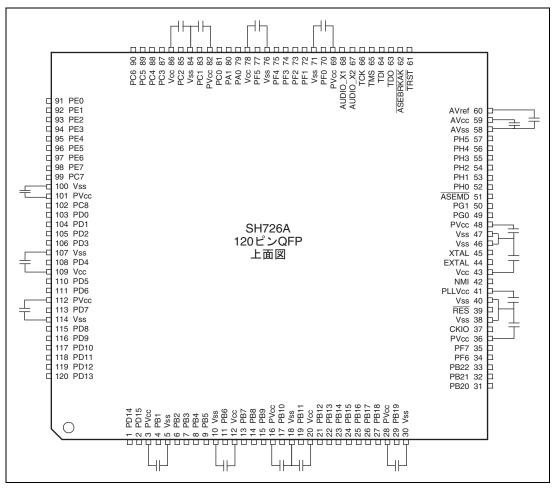

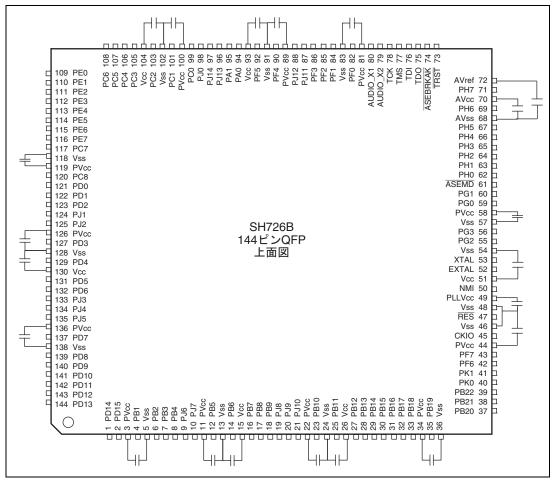

| 1.4   | ピン配置図                   | 1-11 |

| 1.5   | 端子機能                    | 1-13 |

| 1.6   | 端子一覧                    | 1-19 |

| 2. C  | CPU                     | 2-1  |

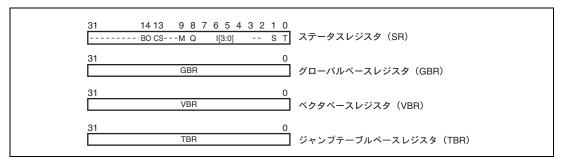

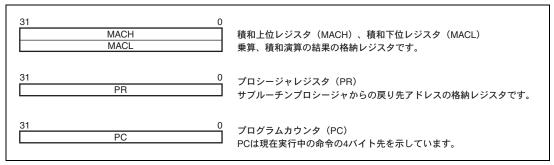

| 2.1   | レジスタ構成                  | 2-1  |

| 2.1.1 | 1 汎用レジスタ                | 2-1  |

| 2.1.2 | 2 コントロールレジスタ            | 2-2  |

| 2.1.3 | 3 システムレジスタ              | 2-3  |

| 2.1.4 | 4 レジスタバンク               | 2-4  |

| 2.1.5 | 5 レジスタの初期値              | 2-4  |

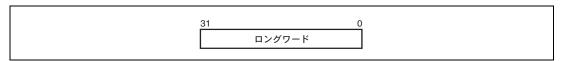

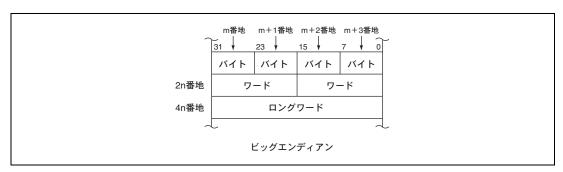

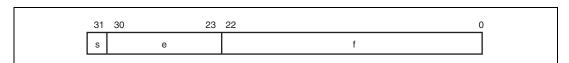

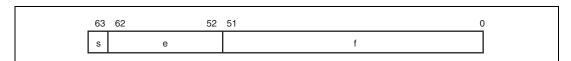

| 2.2   | データ形式                   | 2-5  |

| 2.2.1 | 1 レジスタのデータ形式            | 2-5  |

| 2.2.2 | _ , _ , . , . , . , . , |      |

| 2.2.3 | 3 イミディエイトデータのデータ形式      | 2-6  |

| 2.3   | 命令の特長                   | 2-7  |

| 2.3.1 |                         |      |

| 2.3.2 | 2 アドレッシングモード            | 2-11 |

| 2.3.3 | 3 命令形式                  | 2-15 |

| 2.4   | 命令セット                   | 2-19 |

| 2.4.1 | 2 /2//// 1/ 2 / 1       |      |

| 2.4.2 | 2 データ転送命令               | 2-24 |

| 2.4.3 | 3 算術演算命令                | 2-27 |

| 2.4.4 | 4 論理演算命令                | 2-29 |

| 2.4.5 |                         |      |

| 2.4.6 | 6 分岐命令                  | 2-31 |

| 2.4.7 |                         |      |

| 2.4.8 |                         |      |

| 2.4.9 |                         |      |

| 2.4.1 |                         |      |

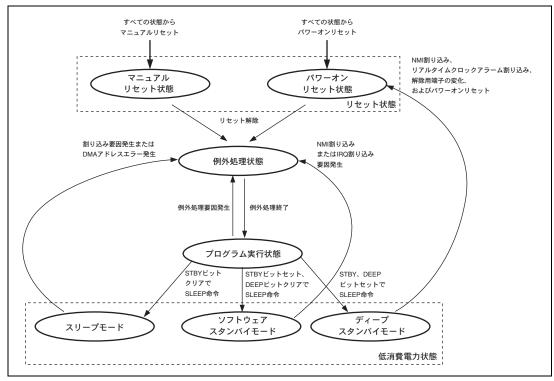

| 2.5   | 処理状態                    | 2-38 |

| 3. 浮  | 動小数点ユニット(FPU)                | 3-1  |

|-------|------------------------------|------|

| 3.1   | 特長                           | 3-1  |

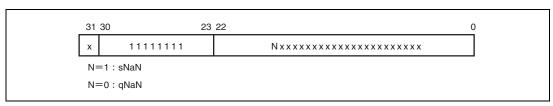

| 3.2   | データフォーマット                    | 3-2  |

| 3.2.1 | 浮動小数点フォーマット                  | 3-2  |

| 3.2.2 | 非数(NaN)                      | 3-4  |

| 3.2.3 | 非正規化数                        | 3-4  |

| 3.3   | レジスタの説明                      | 3-5  |

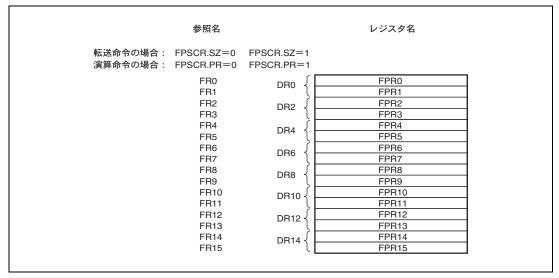

| 3.3.1 | 浮動小数点レジスタ                    | 3-5  |

| 3.3.2 | 浮動小数点ステータス/コントロールレジスタ(FPSCR) | 3-6  |

| 3.3.3 | 浮動小数点通信レジスタ(FPUL)            | 3-7  |

| 3.4   | 丸め                           | 3-8  |

| 3.5   | FPU例外                        | 3-9  |

| 3.5.1 | FPU 例外要因                     | 3-9  |

| 3.5.2 | FPU 例外処理                     | 3-9  |

|       |                              |      |

| 4. ブ- | ートモード                        |      |

| 4.1   | 特長                           |      |

| 4.2   | ブートモードと端子機能設定                | 4-1  |

| 4.3   | 動作説明                         | 4-2  |

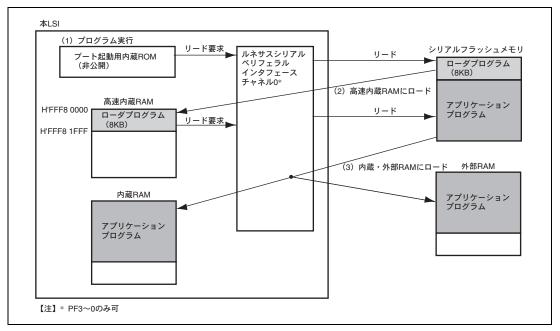

| 4.3.1 | ブートモード 0                     | 4-2  |

| 4.3.2 | ブートモード 1                     |      |

| 4.4   | 注意事項                         | 4-4  |

| 4.4.1 | ブート関連端子                      | 4-4  |

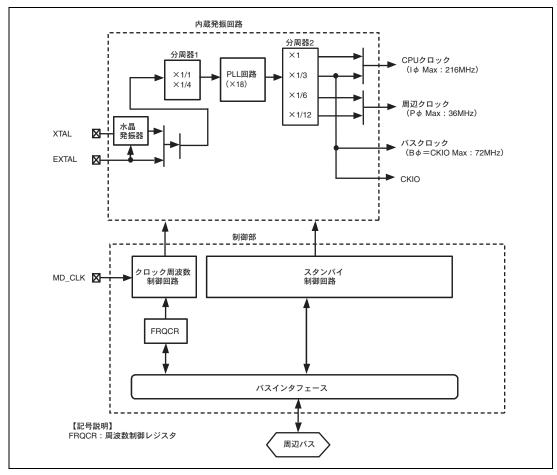

| 5. クロ | ロックパルス発振器                    | 5-1  |

| 5.1   | 特長                           | 5-1  |

| 5.2   | 入出力端子                        | 5-4  |

| 5.3   | クロック動作モード                    | 5-5  |

| 5.4   | レジスタの説明                      | 5-7  |

| 5.4.1 | 周波数制御レジスタ(FRQCR)             | 5-7  |

| 5.5   | 周波数変更方法                      | 5-9  |

| 5.5.1 | 分周率の変更                       | 5-9  |

| 5.6   | クロック端子の使用方法                  | 5-10 |

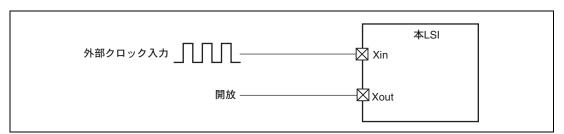

| 5.6.1 | 外部クロック入力時                    | 5-10 |

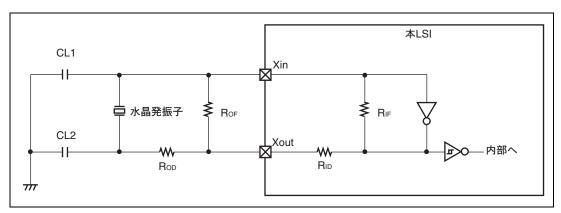

| 5.6.2 | 水晶発振子使用時                     | 5-11 |

| 5.6.3 | 未使用時                         | 5-11 |

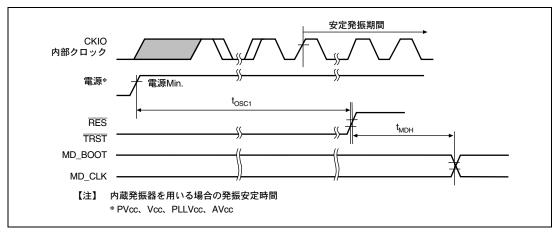

| 5.7   | 発振安定時間                       | 5-12 |

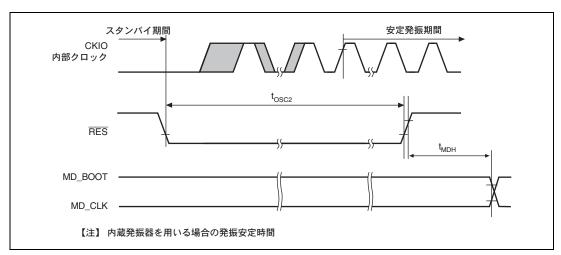

| 5.7.1 | 内蔵水晶発振器の発振安定時間               | 5-12 |

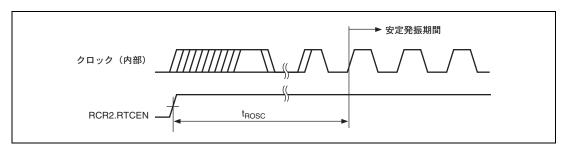

| 5.7.2 | PLL 回路の発振安定時間                | 5-12 |

| 5.8   | ボード設計上の注意事項                  | 5-13 |

|       |                              |      |

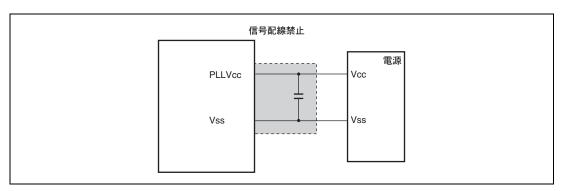

| 5.8.1 | PLL 発振回路使用時の注意                 | 5-13 |

|-------|--------------------------------|------|

| 6. 例名 | 外処理                            | 6-1  |

| 6.1   | 概要                             | 6-1  |

| 6.1.1 | 例外処理の種類と優先順位                   |      |

| 6.1.2 | 例外処理の動作                        | 6-2  |

| 6.1.3 | 例外処理ベクタテーブル                    | 6-4  |

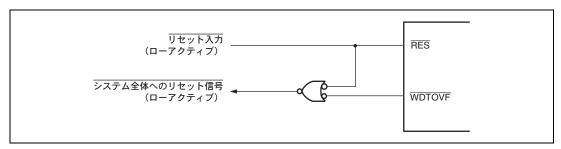

| 6.2   | リセット                           | 6-6  |

| 6.2.1 | 入出力端子                          | 6-6  |

| 6.2.2 | リセットの種類                        | 6-6  |

| 6.2.3 | パワーオンリセット                      | 6-7  |

| 6.2.4 | マニュアルリセット                      | 6-8  |

| 6.3   | アドレスエラー                        | 6-9  |

| 6.3.1 | アドレスエラー発生要因                    | 6-9  |

| 6.3.2 | アドレスエラー例外処理                    | 6-10 |

| 6.4   | レジスタバンクエラー                     | 6-11 |

| 6.4.1 | レジスタバンクエラー発生要因                 | 6-11 |

| 6.4.2 | レジスタバンクエラー例外処理                 | 6-11 |

| 6.5   | 割り込み                           | 6-12 |

| 6.5.1 | 割り込み要因                         | 6-12 |

| 6.5.2 | 割り込み優先順位                       | 6-12 |

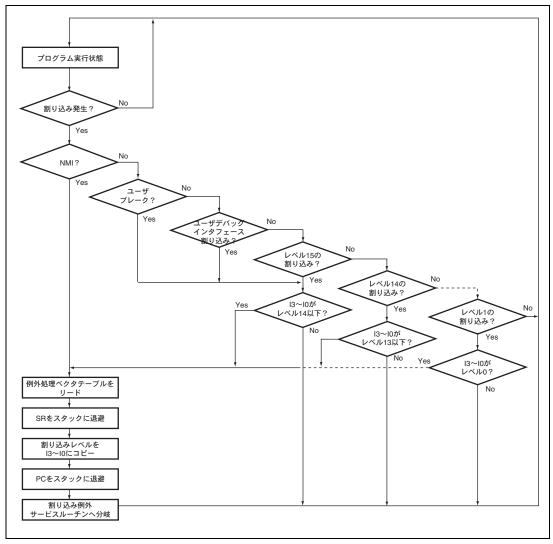

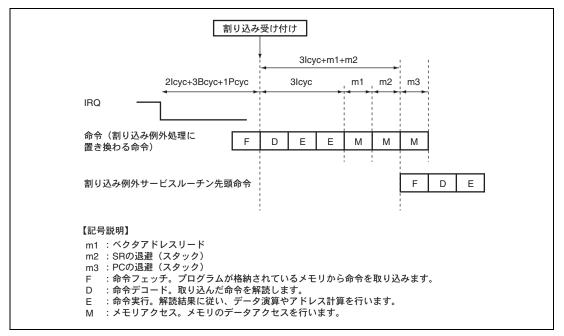

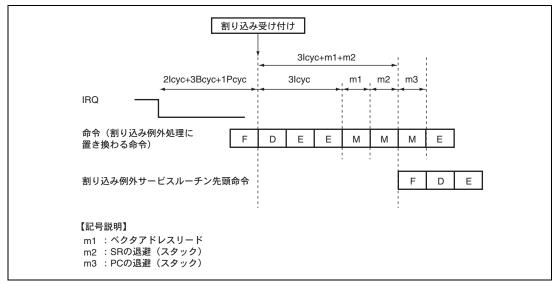

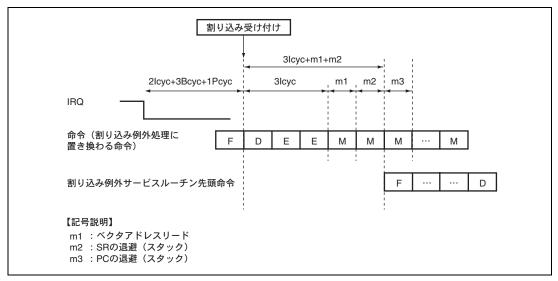

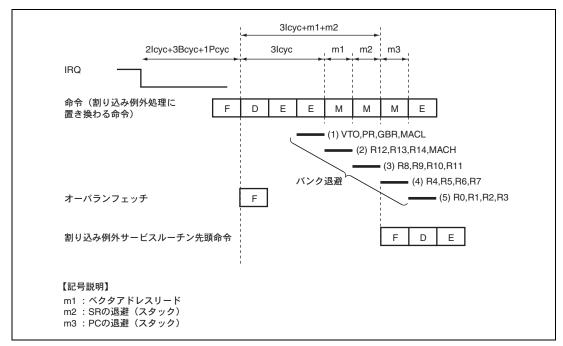

| 6.5.3 | 割り込み例外処理                       | 6-13 |

| 6.6   | 命令による例外                        | 6-14 |

| 6.6.1 | 命令による例外の種類                     | 6-14 |

| 6.6.2 | トラップ命令                         | 6-14 |

| 6.6.3 | スロット不当命令                       | 6-15 |

| 6.6.4 | 一般不当命令                         | 6-15 |

| 6.6.5 | 整数除算例外                         | 6-16 |

| 6.6.6 | FPU 例外                         | 6-16 |

| 6.7   | 例外処理が受け付けられない場合                | 6-17 |

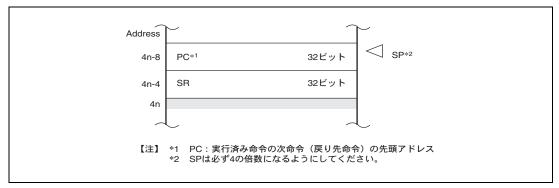

| 6.8   | 例外処理後のスタックの状態                  | 6-18 |

| 6.9   | 使用上の注意事項                       | 6-19 |

| 6.9.1 | スタックポインタ(SP)の値                 |      |

| 6.9.2 | ベクタベースレジスタ(VBR)の値              |      |

| 6.9.3 | アドレスエラー例外処理のスタッキングで発生するアドレスエラー | 6-19 |

| 6.9.4 | 例外処理実行前の注意事項                   | 6-20 |

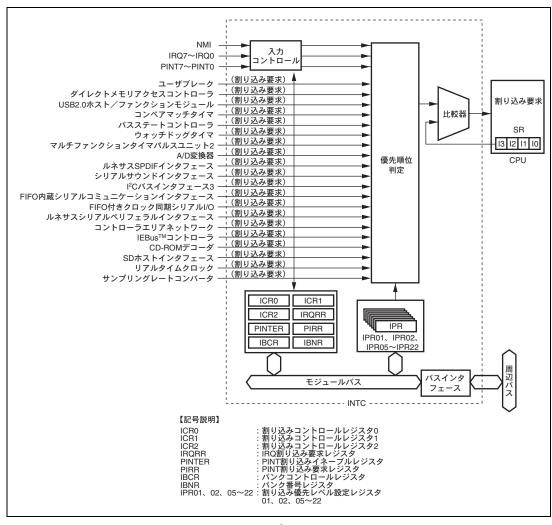

| 7. 割  | り込みコントローラ                      | 7-1  |

| 7.1   | 特長                             | 7-1  |

| 7.2   | 入出力端子                          | 7-3  |

| 7.3   | レジスタの説明                        | 7-4  |

| 7.3.1  | 割り込み優先レベル設定レジスタ 01、02、05~22 (IPR01、IPR02、IPR05~IPR22)     | 7-5  |

|--------|-----------------------------------------------------------|------|

| 7.3.2  | 割り込みコントロールレジスタ 0(ICRO)                                    | 7-7  |

| 7.3.3  | 割り込みコントロールレジスタ 1(ICR1)                                    | 7-8  |

| 7.3.4  | 割り込みコントロールレジスタ 2(ICR2)                                    | 7-9  |

| 7.3.5  | IRQ 割り込み要求レジスタ(IRQRR)                                     | 7-10 |

| 7.3.6  | PINT 割り込みイネーブルレジスタ(PINTER)                                | 7-11 |

| 7.3.7  | PINT 割り込み要求レジスタ(PIRR)                                     | 7-12 |

| 7.3.8  | バンクコントロールレジスタ(IBCR)                                       | 7-13 |

| 7.3.9  | バンク番号レジスタ(IBNR)                                           | 7-14 |

| 7.4    | 割り込み要因                                                    | 7-15 |

| 7.4.1  | NMI 割り込み                                                  | 7-15 |

| 7.4.2  | ユーザブレーク割り込み                                               | 7-16 |

| 7.4.3  | ユーザデバッグインタフェース割り込み                                        | 7-16 |

| 7.4.4  | IRQ 割り込み                                                  | 7-16 |

| 7.4.5  | PINT 割り込み                                                 | 7-17 |

| 7.4.6  | 内蔵周辺モジュール割り込み                                             | 7-18 |

| 7.5    | 割り込み例外処理ベクタテーブルと優先順位                                      | 7-19 |

| 7.6    | 動作説明                                                      | 7-27 |

| 7.6.1  | 割り込み動作の流れ                                                 | 7-27 |

| 7.6.2  | 割り込み例外処理終了後のスタックの状態                                       | 7-29 |

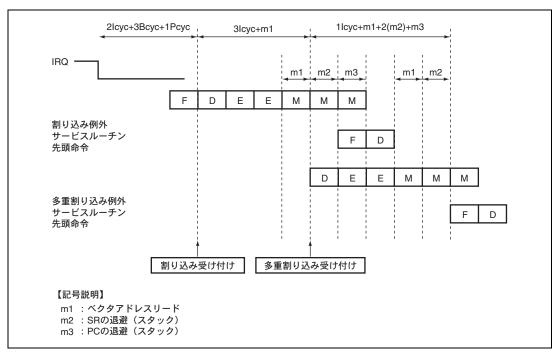

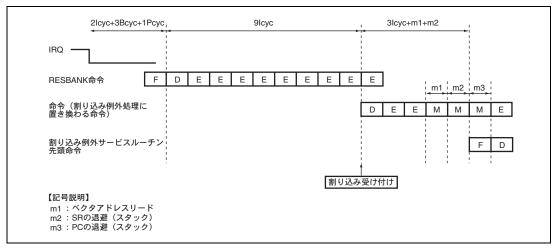

| 7.7    | 割り込み応答時間                                                  | 7-30 |

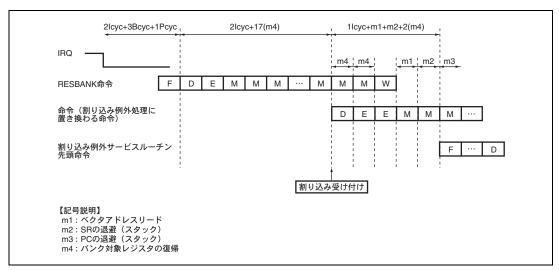

| 7.8    | レジスタバンク                                                   | 7-35 |

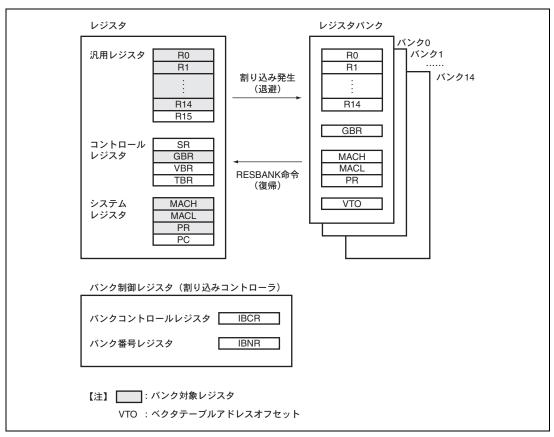

| 7.8.1  | バンクの対象レジスタと入出力方式                                          | 7-35 |

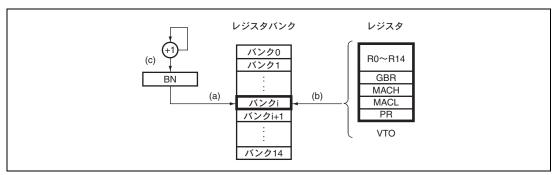

| 7.8.2  | バンク退避、復帰の動作                                               | 7-36 |

| 7.8.3  | すべてのバンクに退避が行われた状態での退避、復帰                                  | 7-38 |

| 7.8.4  | レジスタバンクの例外                                                | 7-39 |

| 7.8.5  | レジスタバンクエラー例外処理                                            | 7-39 |

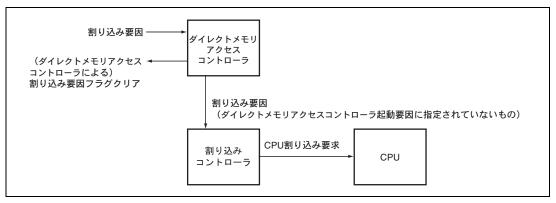

| 7.9    | 割り込み要求信号によるデータ転送                                          | 7-40 |

| 7.9.1  | 割り込み要求信号を CPU の割り込み要因とし、ダイレクトメモリアクセスコントローラの<br>起動要因としない場合 | 7-40 |

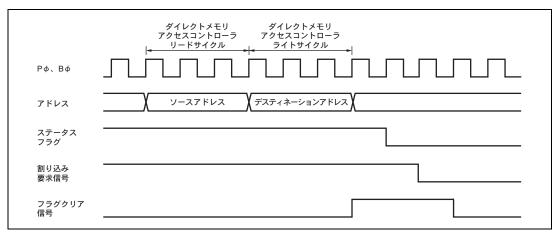

| 7.9.2  | 割り込み要求信号をダイレクトメモリアクセスコントローラの起動要因とし、CPU の<br>割り込み要因としない場合  | 7-41 |

| 7.10   | 使用上の注意事項                                                  | 7-42 |

| 7.10.1 | 割り込み要因クリアのタイミング                                           | 7-42 |

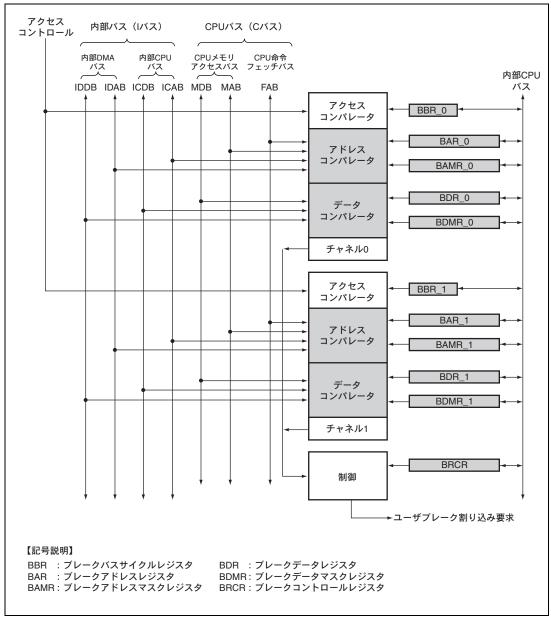

| 8. ユー  | ザブレークコントローラ                                               | 8-1  |

| 8.1    | 特長                                                        | 8-1  |

| 8.2    | レジスタの説明                                                   | 8-3  |

| 8.2.1  | ブレークアドレスレジスタ(BAR)                                         | 8-3  |

| 8.2.2  | ブレークアドレスマスクレジスタ(BAMR)                                     | 8-4  |

| 8.2.3  | ブレークデータレジスタ (BDR)                                         | 8-5  |

| 8.2.4         | ブレークデータマスクレジスタ(BDMR)                  | 8-6   |

|---------------|---------------------------------------|-------|

| 8.2.5         | ブレークバスサイクルレジスタ(BBR)                   | 8-7   |

| 8.2.6         | ブレークコントロールレジスタ(BRCR)                  | 8-9   |

| 8.3           | 動作説明                                  | 8-11  |

| 8.3.1         | ユーザブレーク動作の流れ                          | 8-11  |

| 8.3.2         | 命令フェッチサイクルでのブレーク                      | 8-12  |

| 8.3.3         | データアクセスサイクルでのブレーク                     | 8-13  |

| 8.3.4         | 退避されるプログラムカウンタの値                      | 8-14  |

| 8.3.5         | 使用例                                   | 8-14  |

| 8.4           | 使用上の注意事項                              | 8-17  |

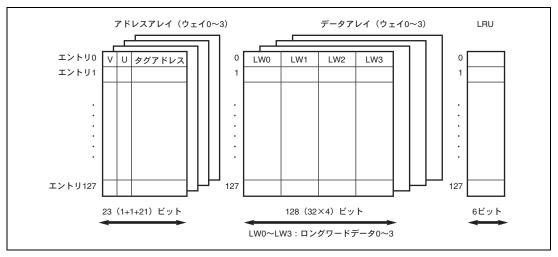

| 9. <b>+</b> † | ッシュ                                   | 9-1   |

| 9.1           | 特長                                    | 9-1   |

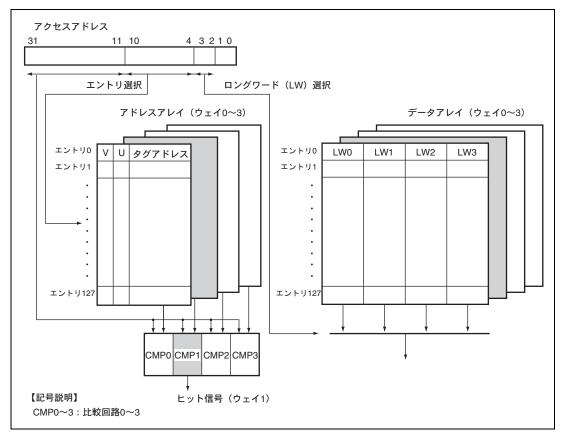

| 9.1.1         | キャッシュの構成                              | 9-1   |

| 9.2           | レジスタの説明                               | 9-4   |

| 9.2.1         | キャッシュ制御レジスタ1(CCR1)                    | 9-4   |

| 9.2.2         | キャッシュ制御レジスタ 2 (CCR2)                  | 9-6   |

| 9.3           | 動作説明                                  | 9-9   |

| 9.3.1         | キャッシュの検索                              | 9-9   |

| 9.3.2         | リード動作                                 | 9-10  |

| 9.3.3         | プリフェッチ動作(オペランドキャッシュのみ)                | 9-10  |

| 9.3.4         | ライト動作(オペランドキャッシュのみ)                   | 9-10  |

| 9.3.5         | ライトバックバッファ(オペランドキャッシュのみ)              | 9-11  |

| 9.3.6         | キャッシュと外部メモリ/大容量内蔵 RAM とのコヒーレンシ        | 9-13  |

| 9.4           | メモリ割り付けキャッシュの構成                       | 9-14  |

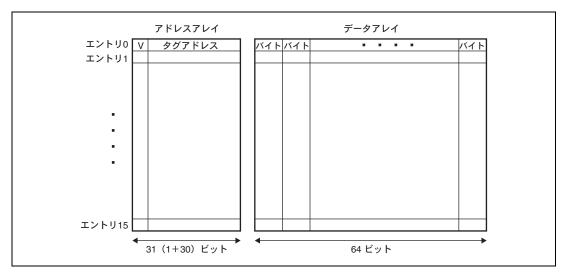

| 9.4.1         | アドレスアレイ                               | 9-14  |

| 9.4.2         | データアレイ                                | 9-15  |

| 9.4.3         | 使用例                                   | 9-17  |

| 9.4.4         | 注意事項                                  | 9-17  |

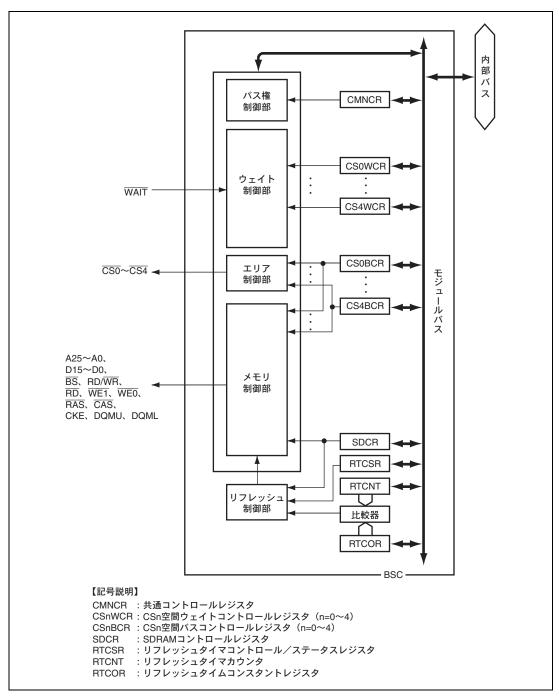

| 10. バス        | ステートコントローラ                            | 10-1  |

| 10.1          | 特長                                    | 10-1  |

| 10.2          | 入出力端子                                 | 10-4  |

| 10.3          | エリアの概要                                | 10-5  |

| 10.3.1        | アドレスマップ                               |       |

| 10.3.2        | ブートモードと各エリアのデータバス幅およびエンディアン指定と関連端子設定  | 10-6  |

| 10.4          | レジスタの説明                               | 10-7  |

| 10.4.1        | 共通コントロールレジスタ (CMNCR)                  | 10-8  |

| 10.4.2        | CSn 空間バスコントロールレジスタ (CSnBCR) (n=0~4)   | 10-10 |

| 10.4.3        | CSn 空間ウェイトコントロールレジスタ (CSnWCR) (n=0~4) | 10-14 |

| 10.4.4        | SDRAM コントロールレジスタ(SDCR)                | 10-31 |

| 10.4.5    | リフレッシュタイマコントロール/ステータスレジスタ(RTCSR)  | 10-34 |

|-----------|-----------------------------------|-------|

| 10.4.6    | リフレッシュタイマカウンタ(RTCNT)              | 10-36 |

| 10.4.7    | リフレッシュタイムコンスタントレジスタ(RTCOR)        | 10-37 |

| 10.5      | 動作説明                              | 10-38 |

| 10.5.1    | エンディアン/アクセスサイズとデータアライメント          | 10-38 |

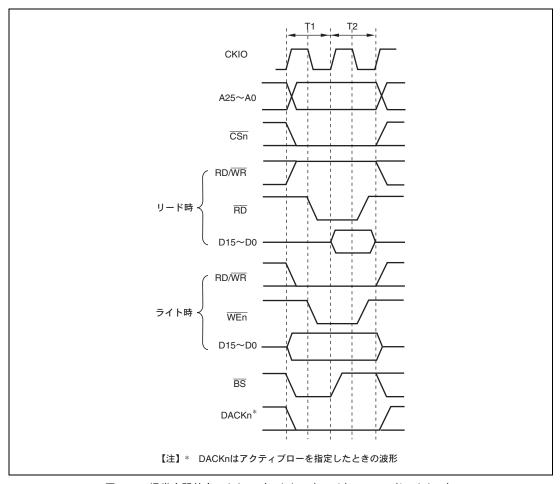

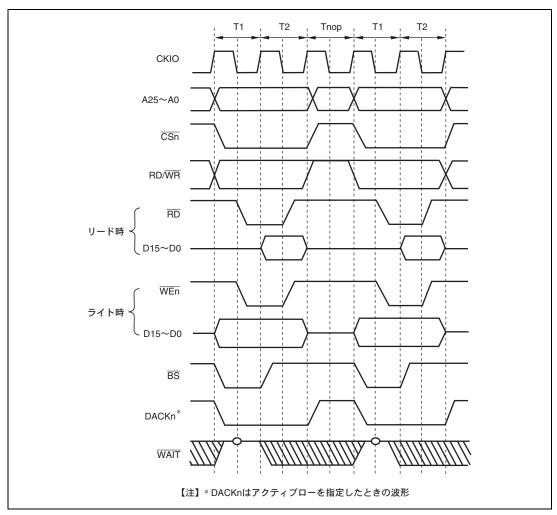

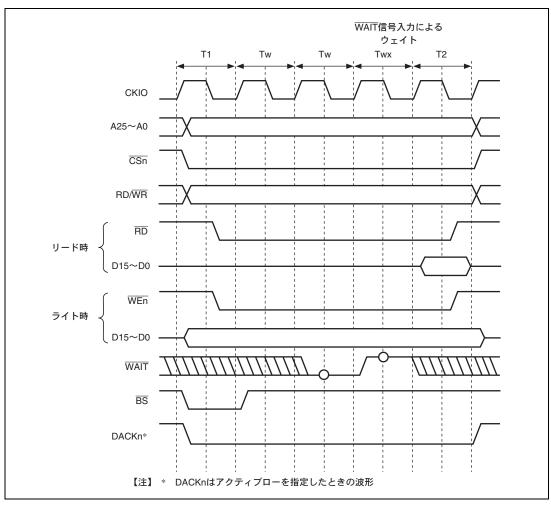

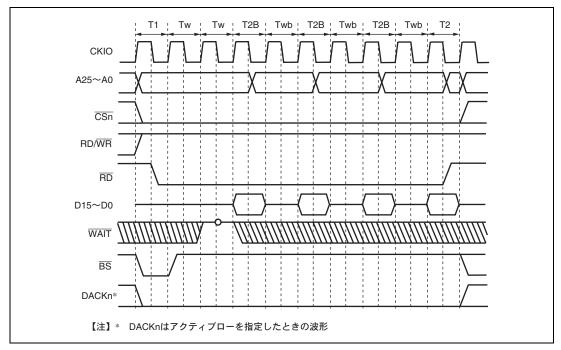

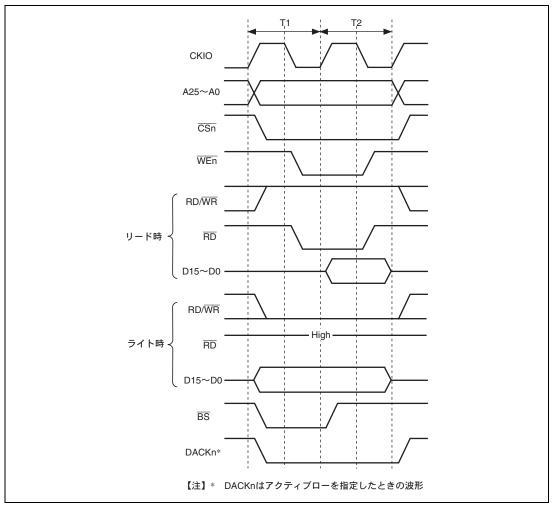

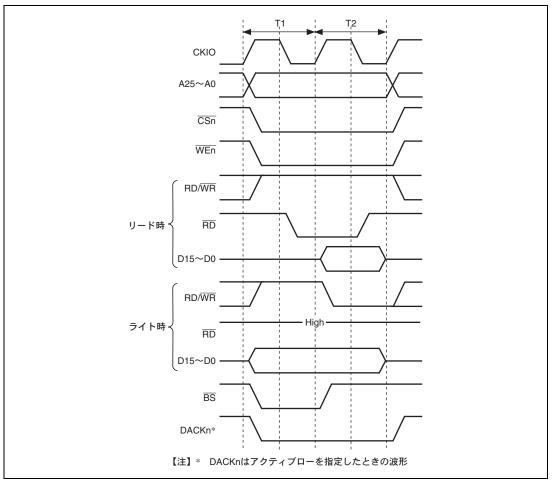

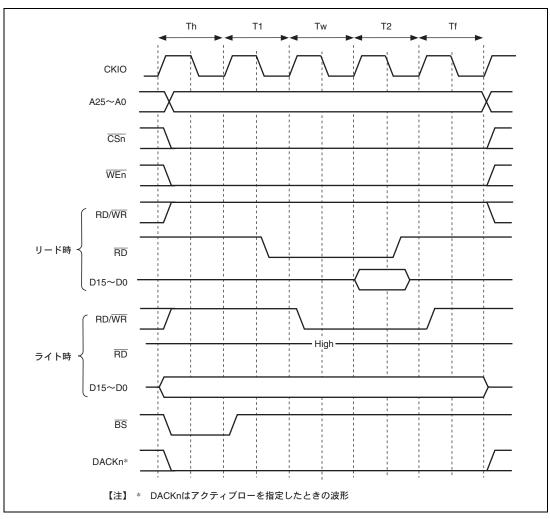

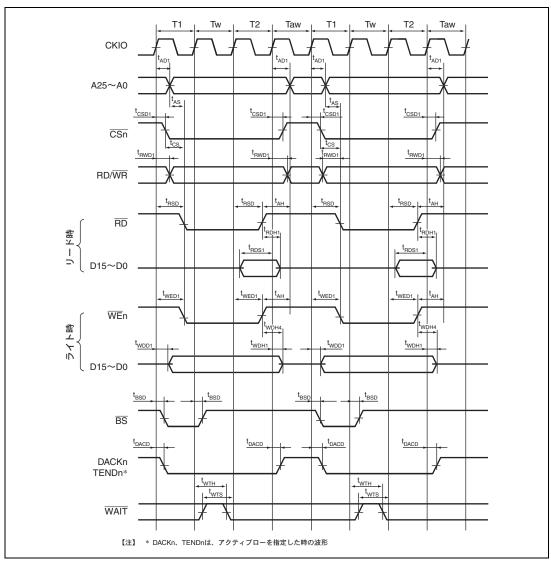

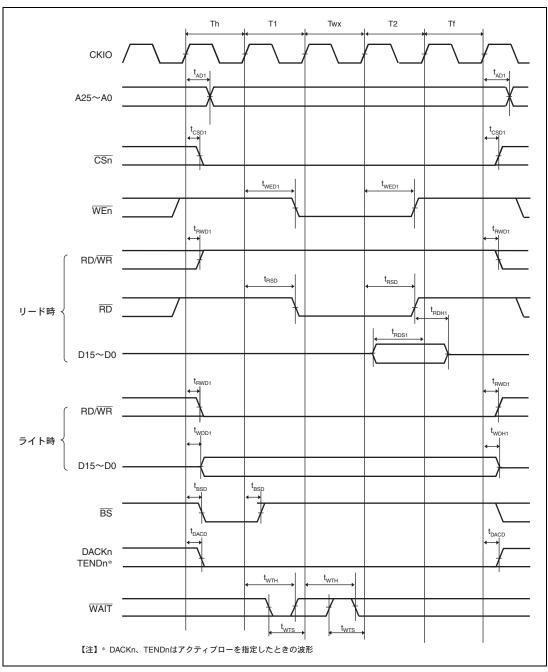

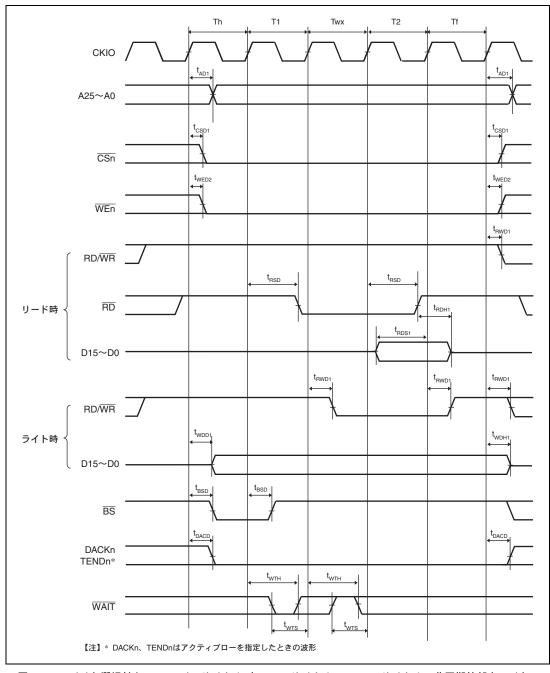

| 10.5.2    | 通常空間インタフェース                       | 10-41 |

| 10.5.3    | アクセスウェイト制御                        | 10-45 |

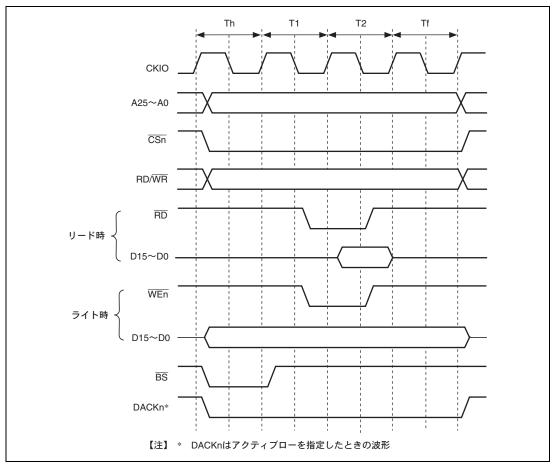

| 10.5.4    | <u>CSn</u> アサート期間拡張               | 10-47 |

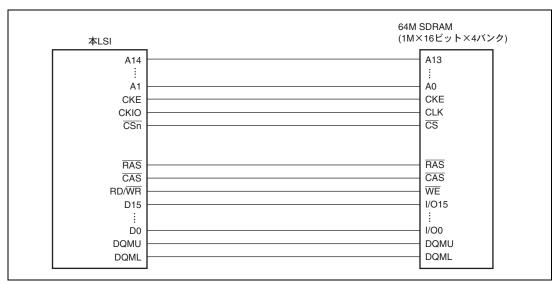

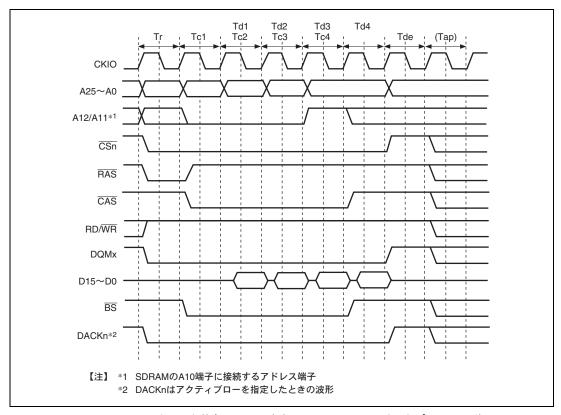

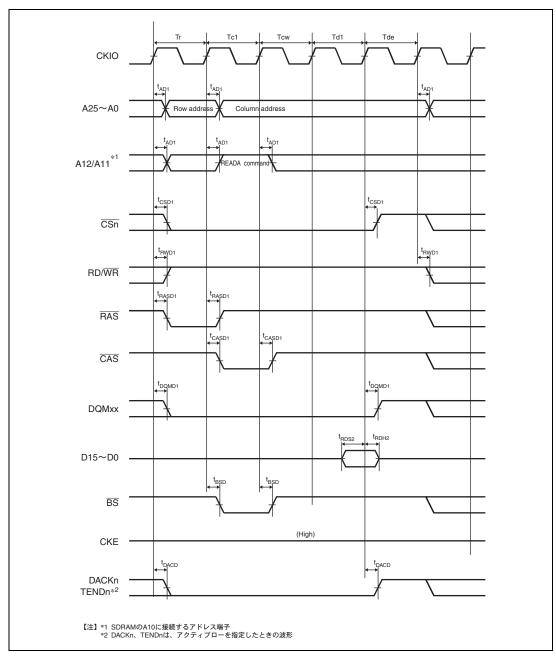

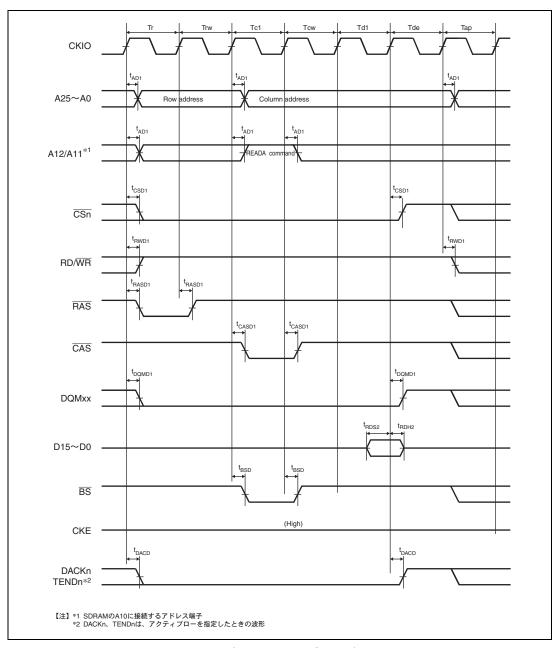

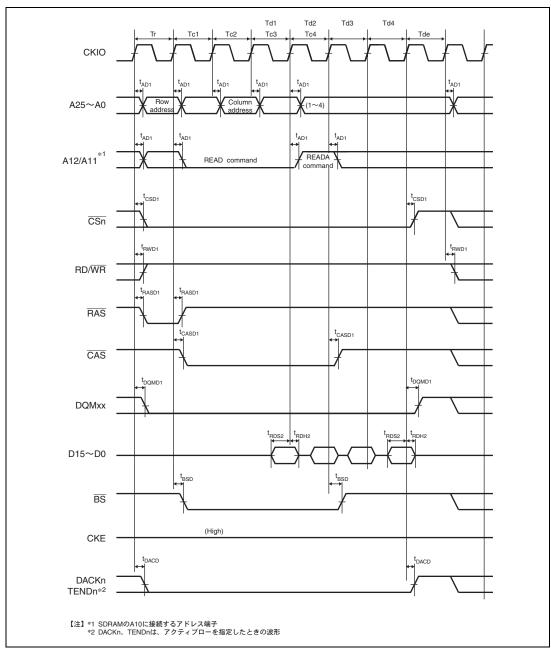

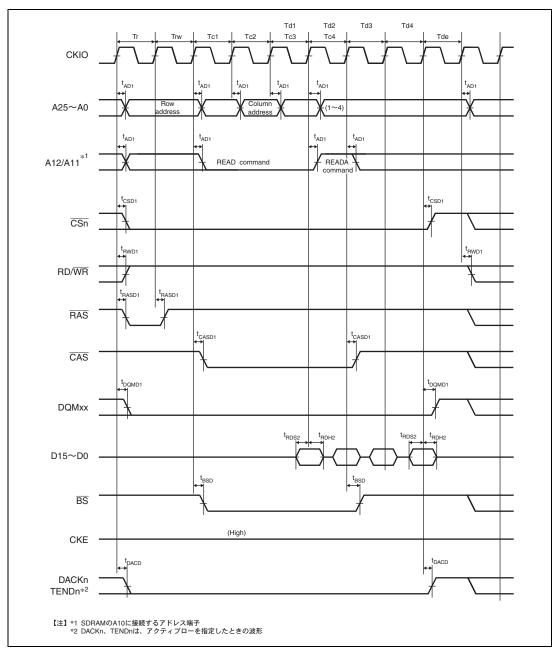

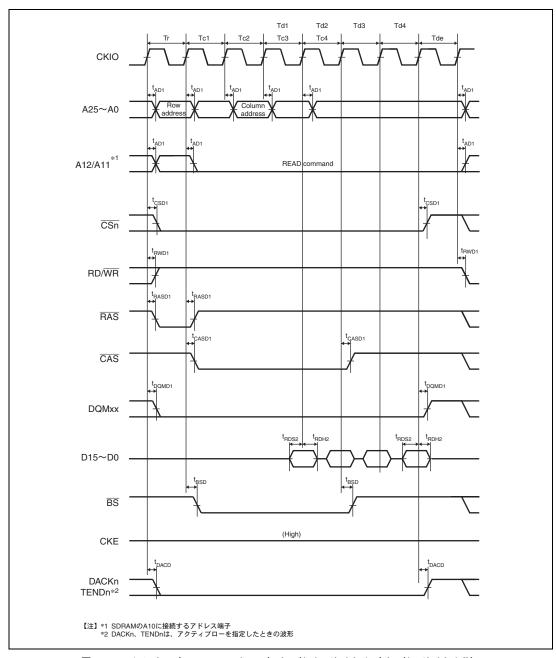

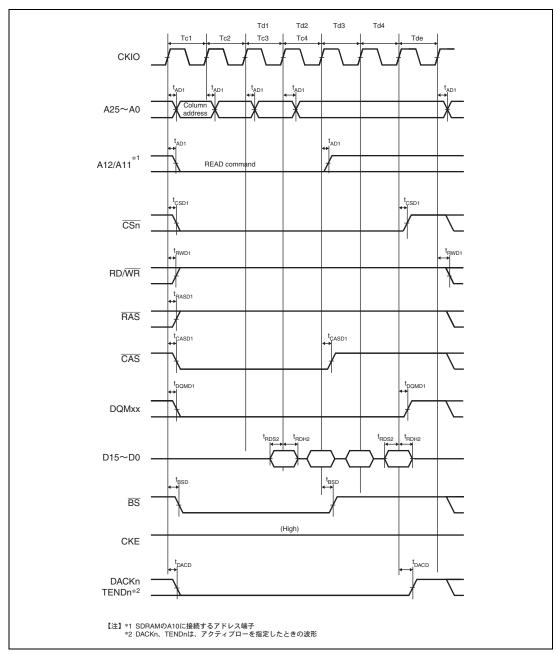

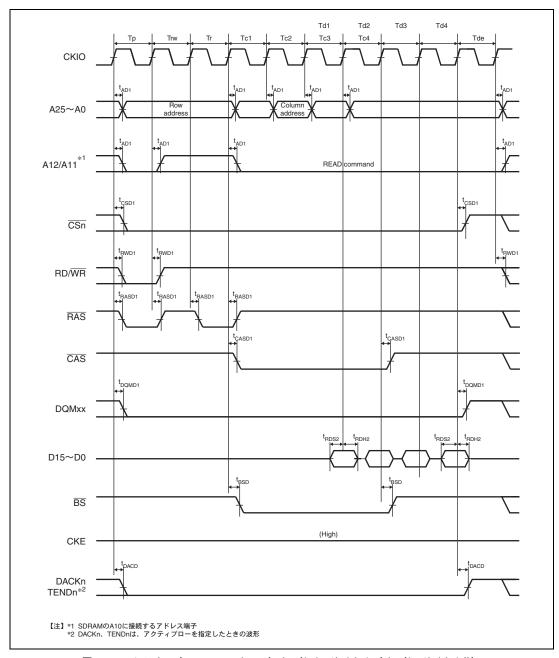

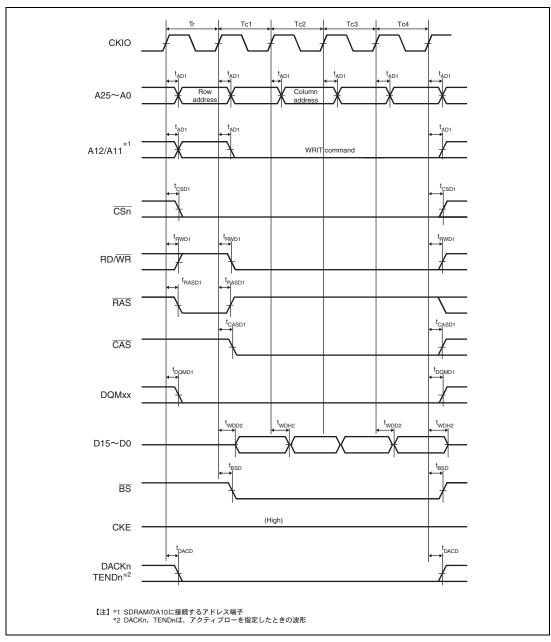

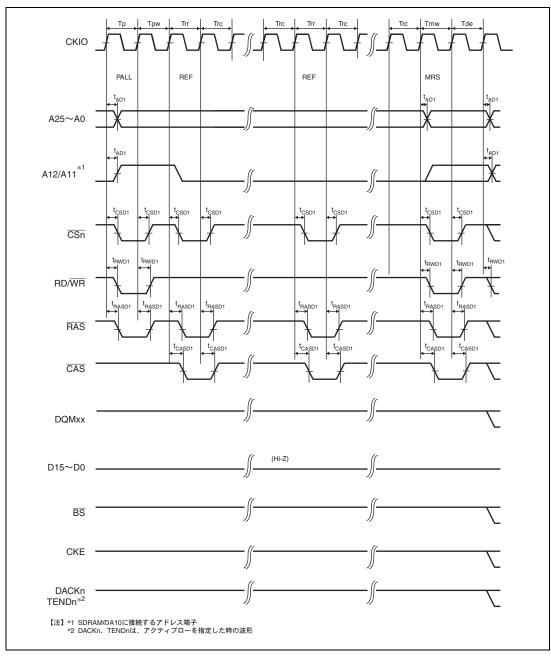

| 10.5.5    | SDRAM インタフェース                     | 10-48 |

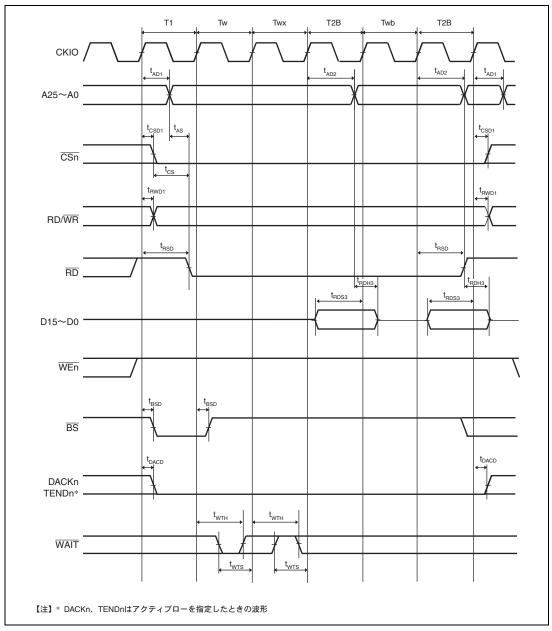

| 10.5.6    | バースト ROM(クロック非同期)インタフェース          | 10-75 |

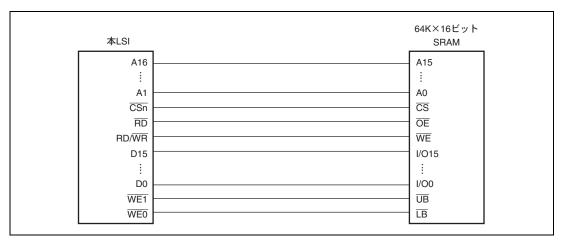

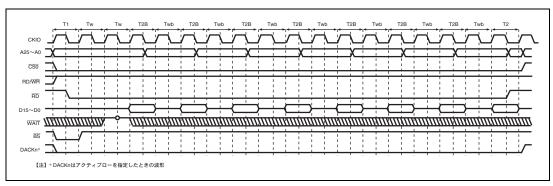

| 10.5.7    | バイト選択付き SRAM インタフェース              | 10-76 |

| 10.5.8    | バースト ROM(クロック同期)インタフェース           | 10-81 |

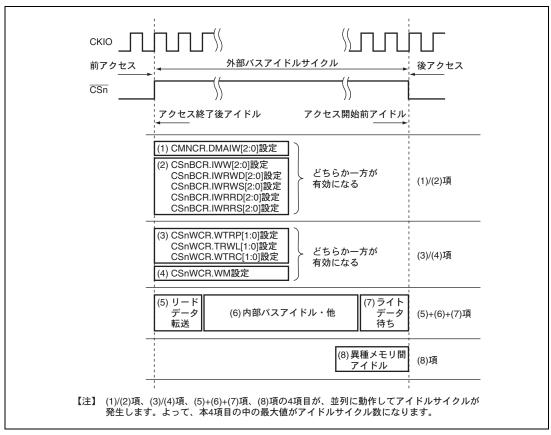

| 10.5.9    | アクセスサイクル間アイドル                     | 10-82 |

| 10.5.10   | 0 その他                             | 10-88 |

| . جيو د د | /I 61 / TURK                      |       |

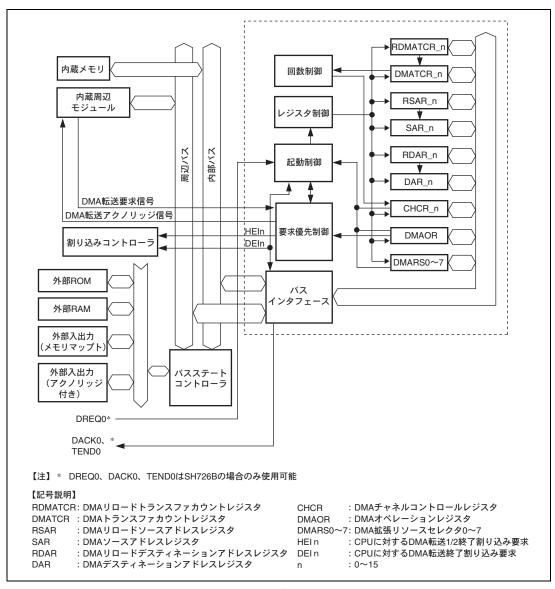

| 11. タイ    | (レクトメモリアクセスコントローラ                 |       |

| 11.1      | 特長                                |       |

| 11.2      | 入出力端子                             |       |

| 11.3      | レジスタの説明                           |       |

| 11.3.1    |                                   |       |

| 11.3.2    |                                   |       |

| 11.3.3    |                                   |       |

| 11.3.4    |                                   |       |

| 11.3.5    |                                   |       |

| 11.3.6    |                                   |       |

| 11.3.7    | DMA リロードトランスファカウントレジスタ(RDMATCR)   | 11-21 |

| 11.3.8    |                                   |       |

| 11.3.9    | DMA 拡張リソースセレクタ 0~7(DMARS0~DMARS7) | 11-24 |

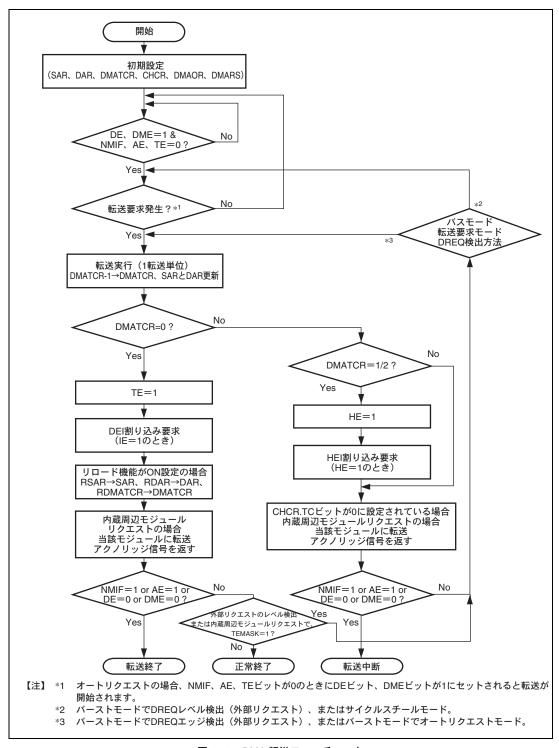

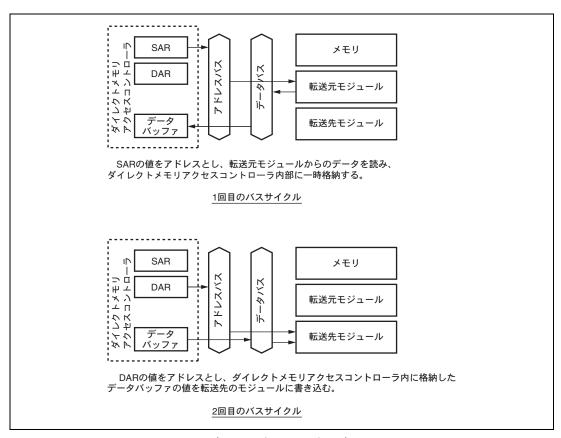

| 11.4      | 動作説明                              | 11-28 |

| 11.4.1    | 転送フロー                             | 11-28 |

| 11.4.2    |                                   |       |

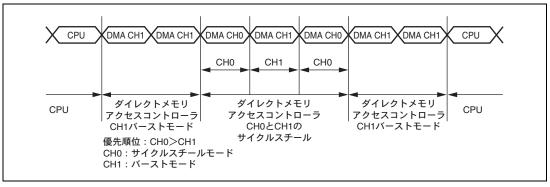

| 11.4.3    | チャネルの優先順位                         | 11-36 |

| 11.4.4    |                                   |       |

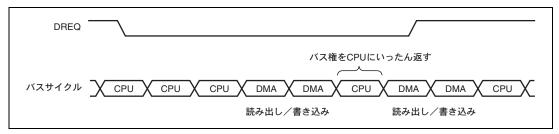

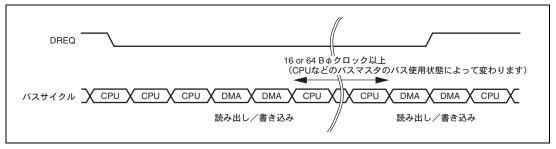

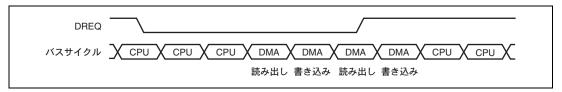

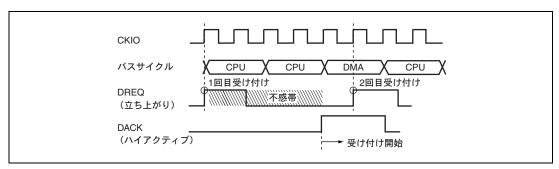

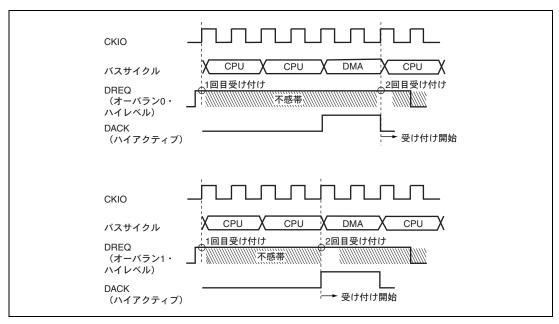

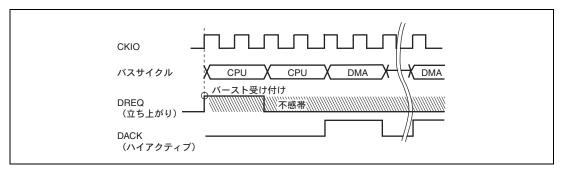

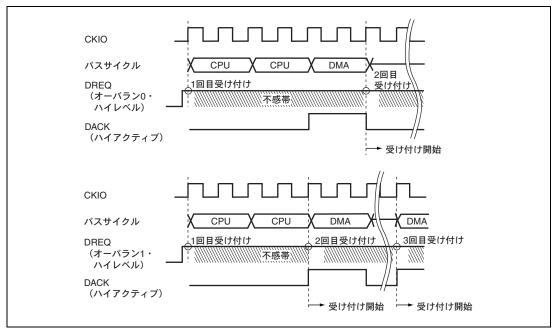

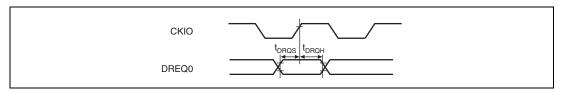

| 11.4.5    | バスサイクルのステート数と DREQ 端子のサンプリングタイミング |       |

| 11.5      | 使用上の注意事項                          |       |

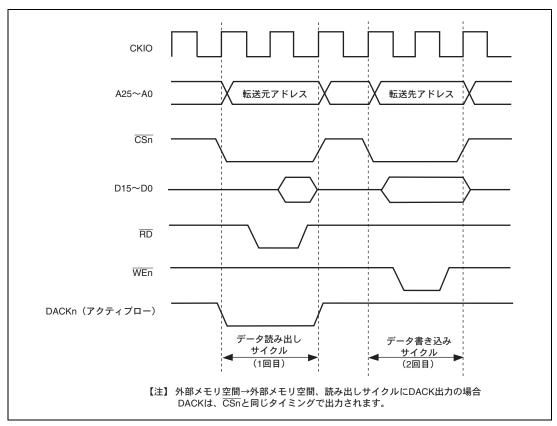

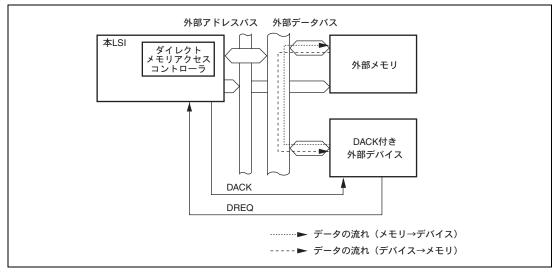

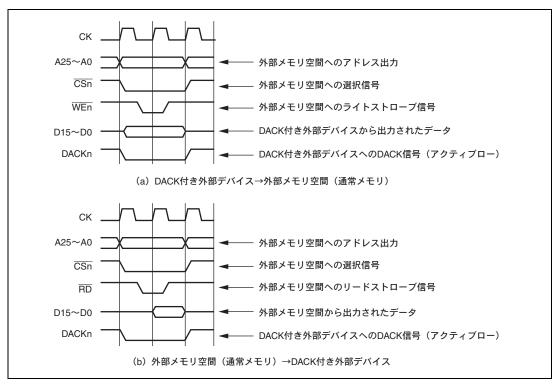

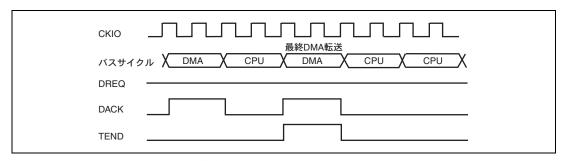

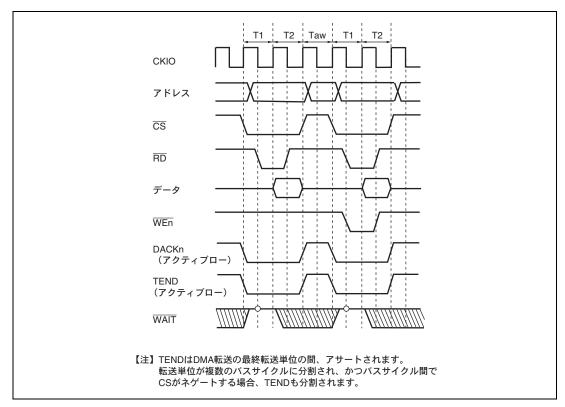

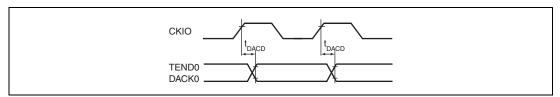

| 11.5.1    | DACK 出力および TEND 出力のタイミング          | 11-48 |

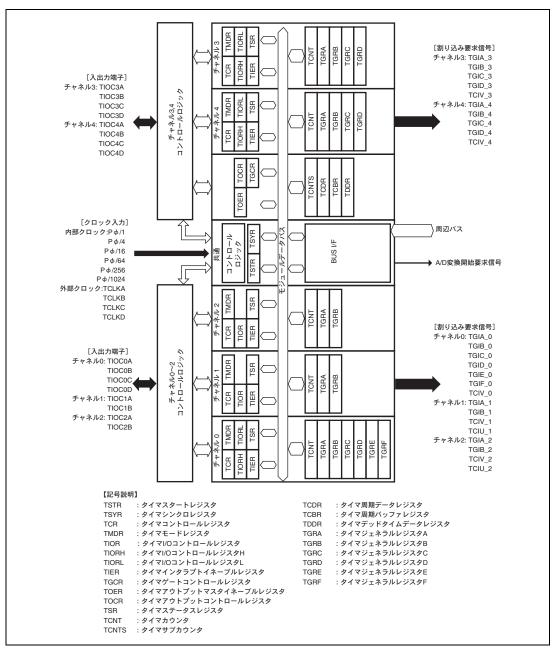

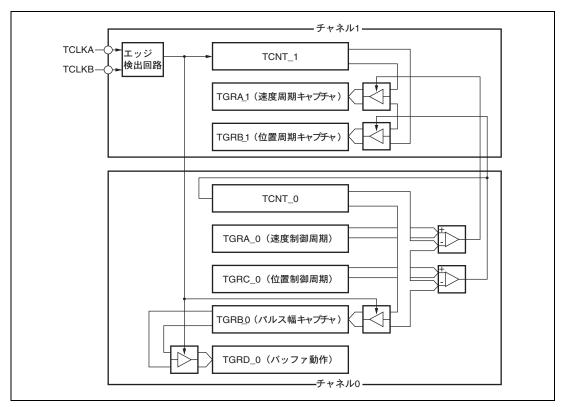

| 12. マル    | レチファンクションタイマパルスユニット 2             | 12-1  |

| 12.1      | 特長                                | 12-1  |

| 12.2      | 入出力端子                             | 12-6  |

| 12.3      | レジスタの説明                           | 12-8  |

| 12.3.1  | タイマコントロールレジスタ(TCR)                       | 12-11  |

|---------|------------------------------------------|--------|

| 12.3.2  | タイマモードレジスタ(TMDR)                         | 12-14  |

| 12.3.3  | タイマ I/O コントロールレジスタ(TIOR)                 | 12-16  |

| 12.3.4  | タイマインタラプトイネーブルレジスタ(TIER)                 | 12-34  |

| 12.3.5  | タイマステータスレジスタ(TSR)                        | 12-37  |

| 12.3.6  | タイマバッファ動作転送モードレジスタ(TBTM)                 | 12-41  |

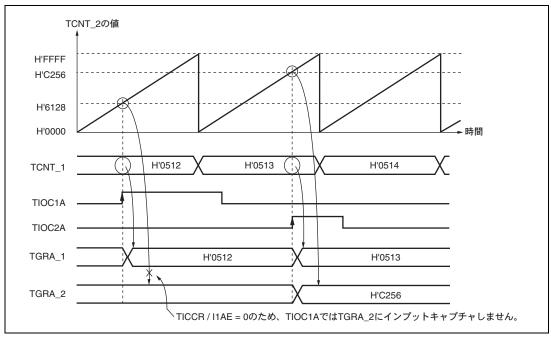

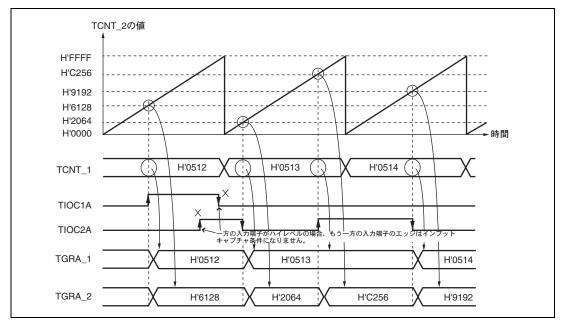

| 12.3.7  | タイマインプットキャプチャコントロールレジスタ(TICCR)           | 12-42  |

| 12.3.8  | タイマ A/D 変換開始要求コントロールレジスタ(TADCR)          | 12-43  |

| 12.3.9  | タイマ A/D 変換開始要求周期設定レジスタ(TADCORA/B_4)      | 12-45  |

| 12.3.10 | タイマ A/D 変換開始要求周期設定バッファレジスタ(TADCOBRA/B_4) | 12-45  |

| 12.3.11 | タイマカウンタ(TCNT)                            | 12-46  |

| 12.3.12 | タイマジェネラルレジスタ(TGR)                        | 12-46  |

| 12.3.13 | タイマスタートレジスタ(TSTR)                        | 12-47  |

| 12.3.14 | タイマシンクロレジスタ(TSYR)                        | 12-48  |

| 12.3.15 | タイマリードライトイネーブルレジスタ(TRWER)                | 12-49  |

| 12.3.16 | タイマアウトプットマスタイネーブルレジスタ(TOER)              | 12-50  |

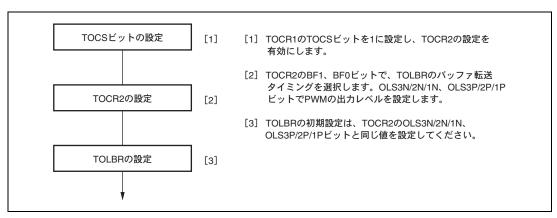

| 12.3.17 | タイマアウトプットコントロールレジスタ 1(TOCR1)             | 12-51  |

| 12.3.18 | タイマアウトプットコントロールレジスタ 2(TOCR2)             | 12-53  |

| 12.3.19 | タイマアウトプットレベルバッファレジスタ(TOLBR)              | 12-56  |

| 12.3.20 | タイマゲートコントロールレジスタ(TGCR)                   | 12-57  |

| 12.3.21 | タイマサブカウンタ(TCNTS)                         | 12-58  |

| 12.3.22 | タイマデッドタイムデータレジスタ(TDDR)                   | 12-58  |

| 12.3.23 | タイマ周期データレジスタ(TCDR)                       | 12-59  |

| 12.3.24 | タイマ周期バッファレジスタ(TCBR)                      | 12-59  |

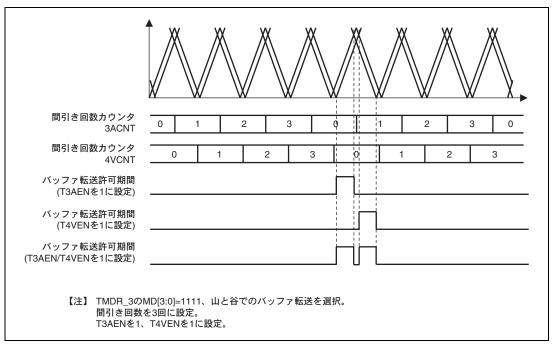

| 12.3.25 | タイマ割り込み間引き設定レジスタ(TITCR)                  | 12-60  |

| 12.3.26 | タイマ割り込み間引き回数カウンタ(TITCNT)                 | 12-61  |

| 12.3.27 | タイマバッファ転送設定レジスタ(TBTER)                   | 12-62  |

| 12.3.28 | タイマデッドタイムイネーブルレジスタ(TDER)                 | 12-63  |

| 12.3.29 | タイマ波形コントロールレジスタ(TWCR)                    | 12-64  |

| 12.3.30 | バスマスタとのインタフェース                           | 12-65  |

| 12.4 重  | 动作説明                                     | 12-66  |

| 12.4.1  | 基本動作                                     | 12-66  |

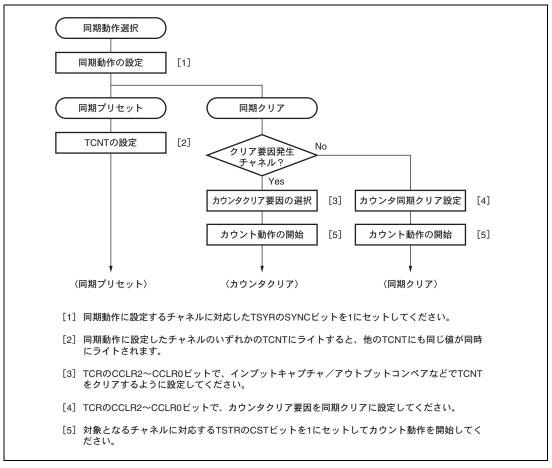

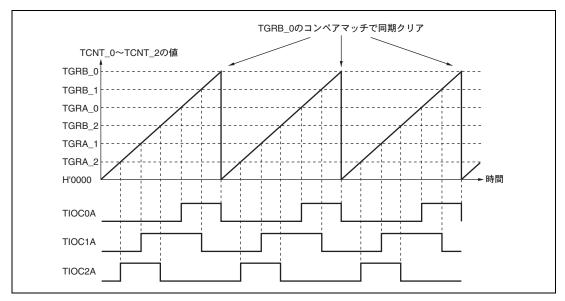

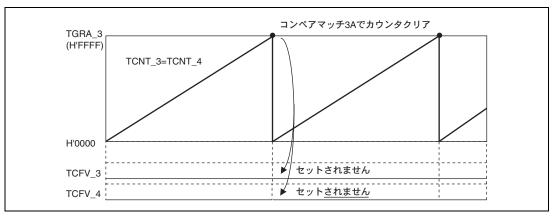

| 12.4.2  | 同期動作                                     | 12-72  |

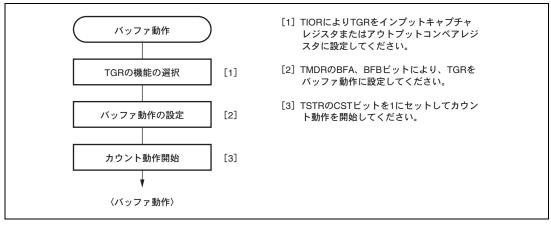

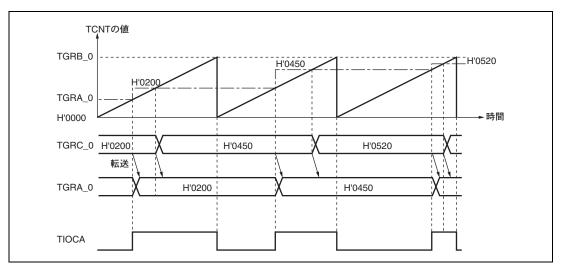

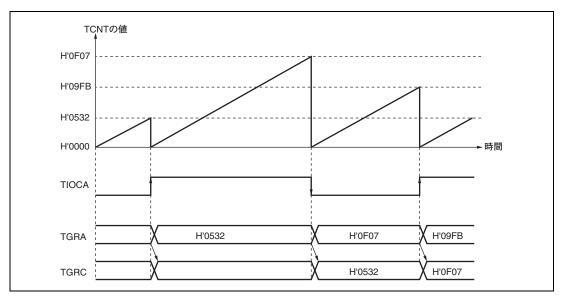

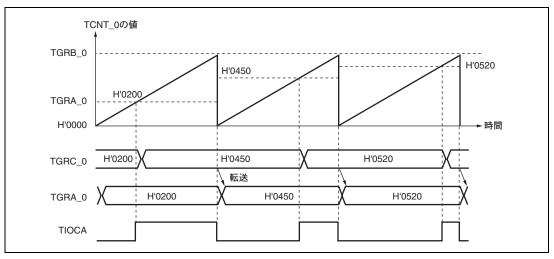

| 12.4.3  | バッファ動作                                   | 12-74  |

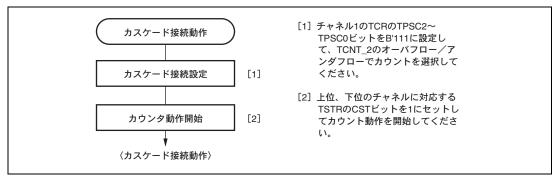

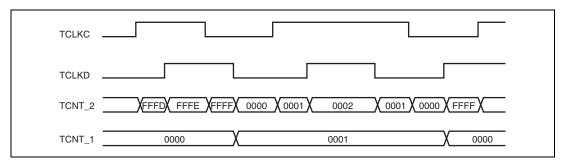

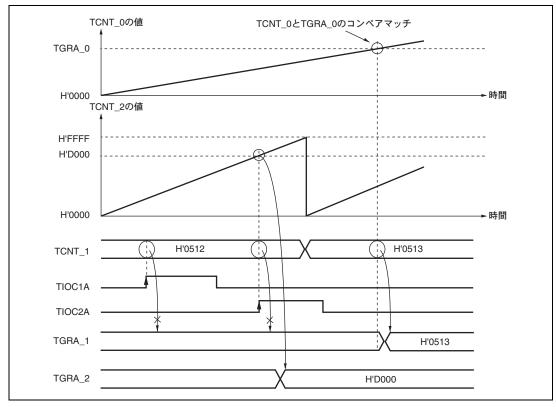

| 12.4.4  | カスケード接続動作                                | 12-78  |

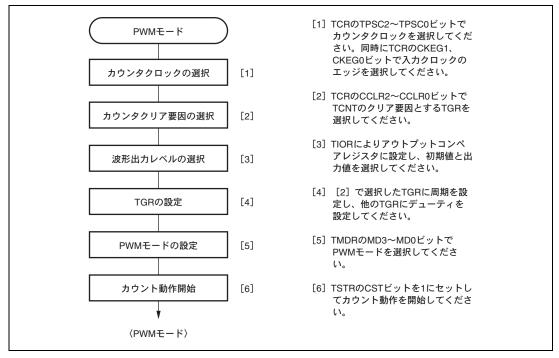

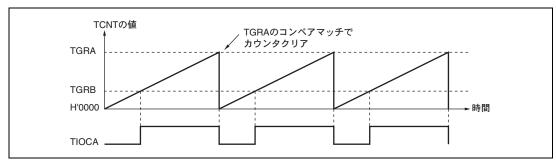

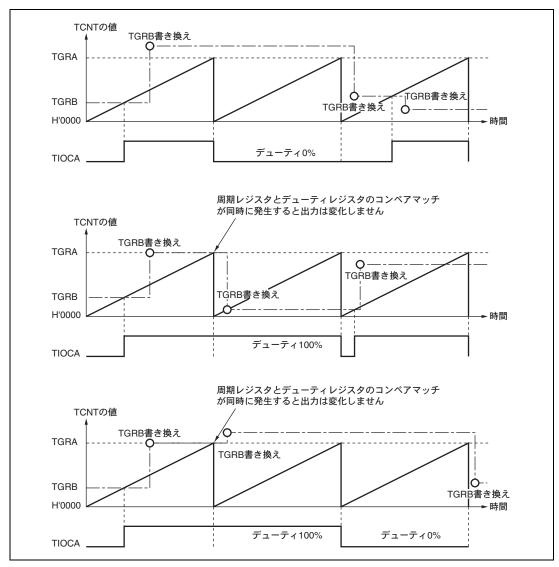

| 12.4.5  | PWM モード                                  | 12-82  |

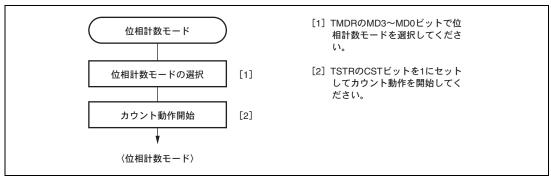

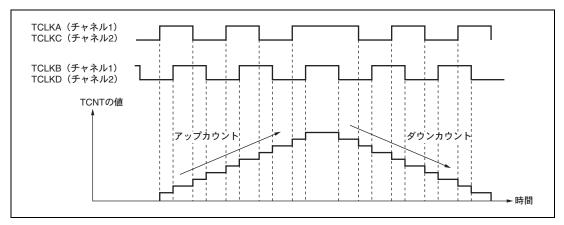

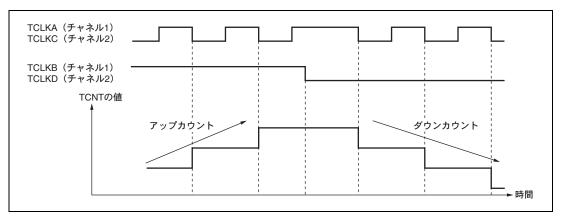

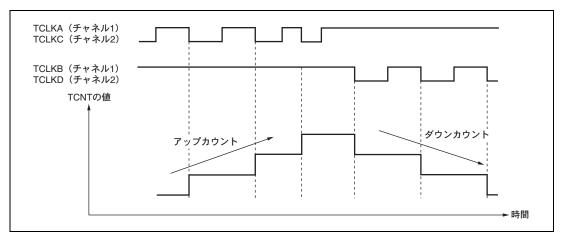

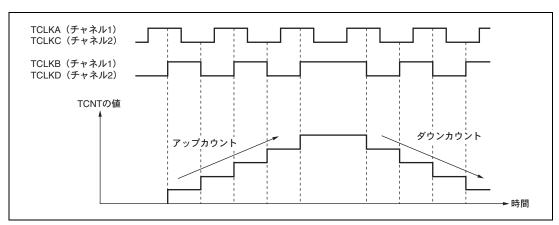

| 12.4.6  | 位相計数モード                                  | 12-87  |

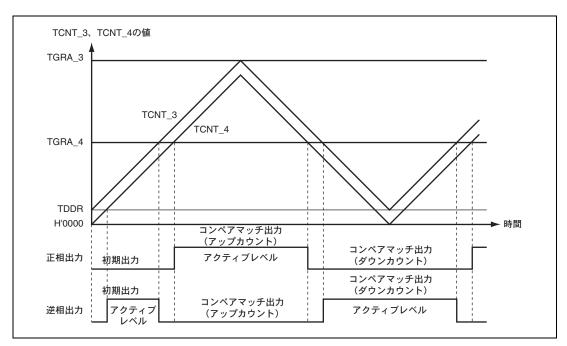

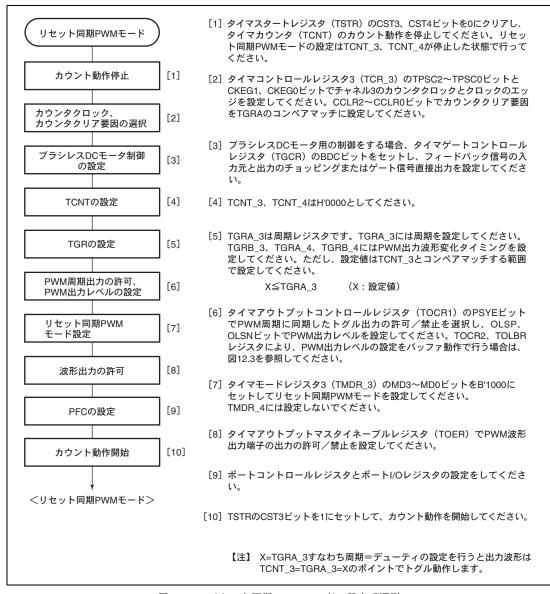

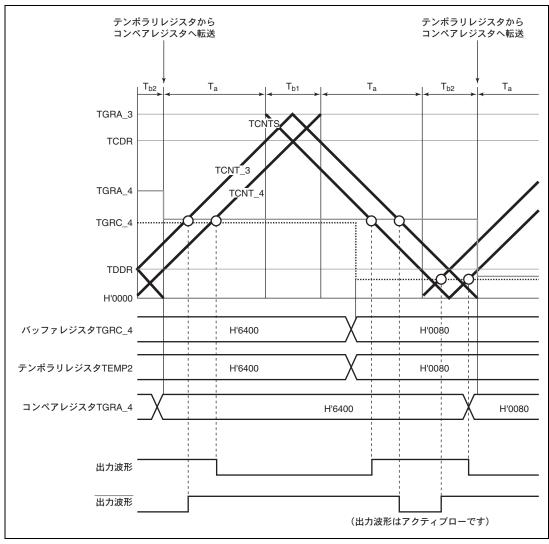

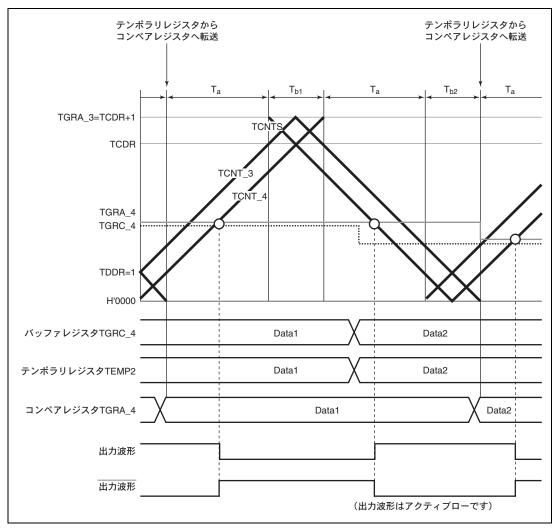

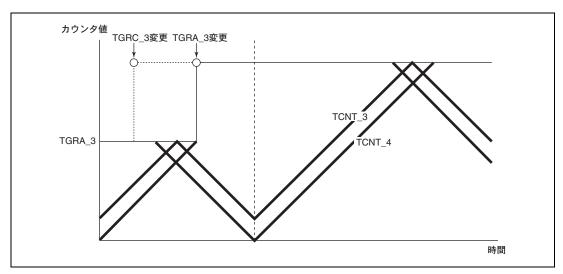

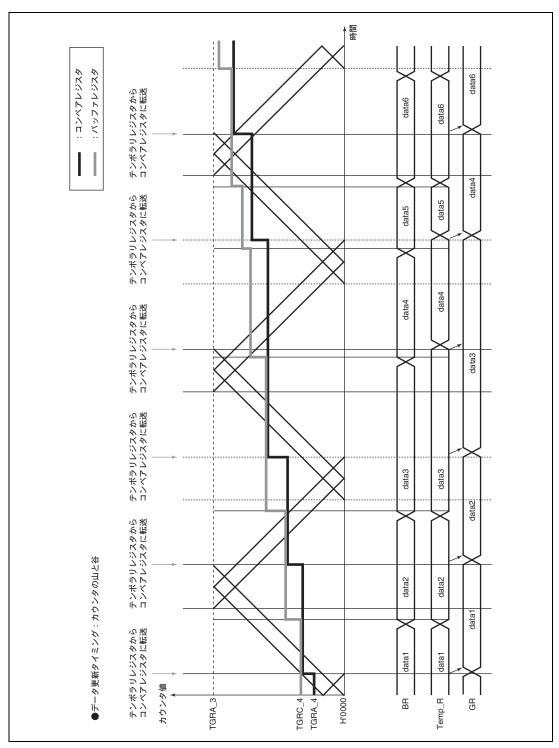

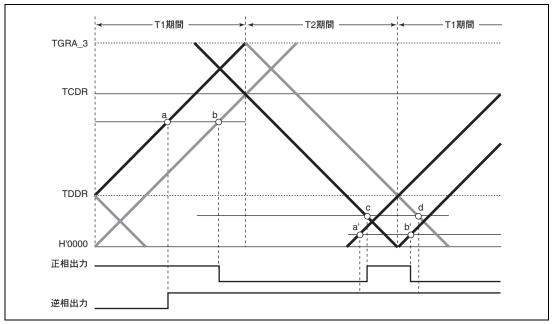

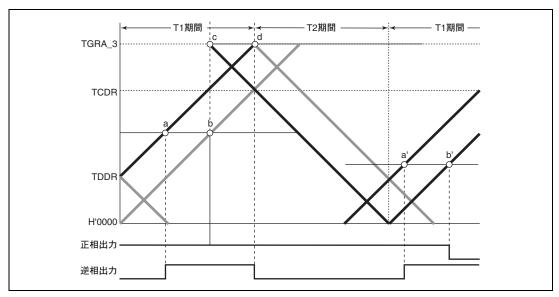

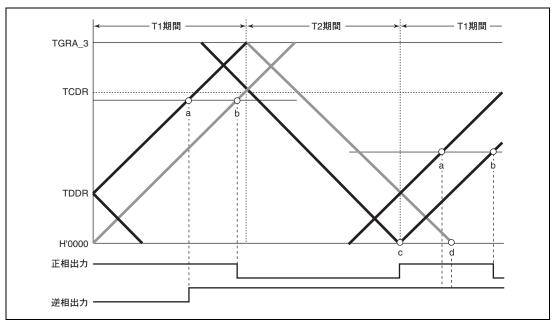

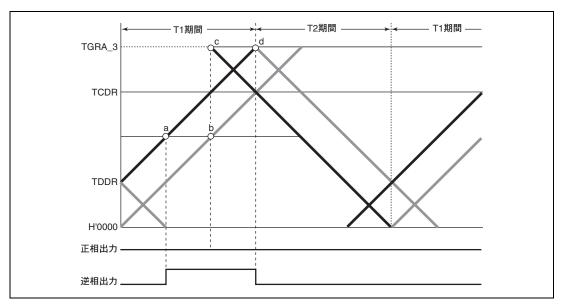

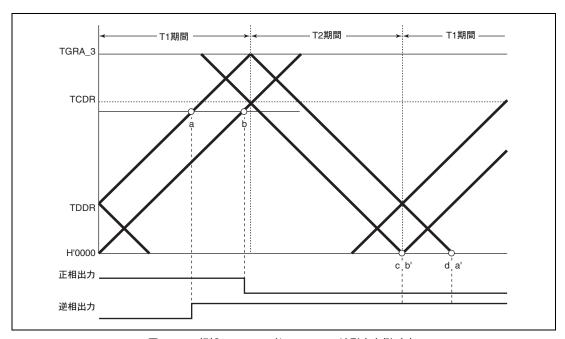

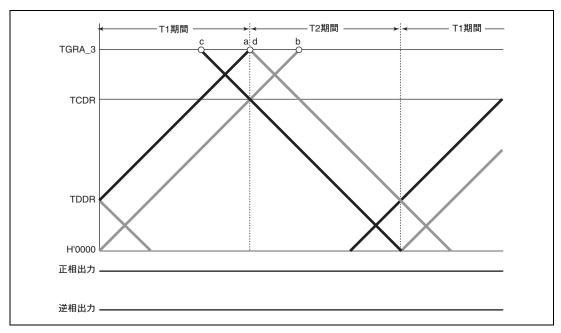

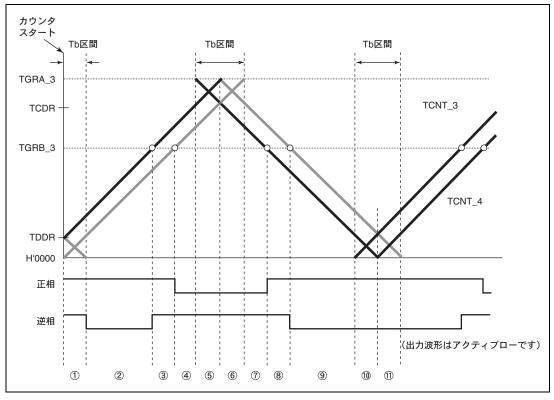

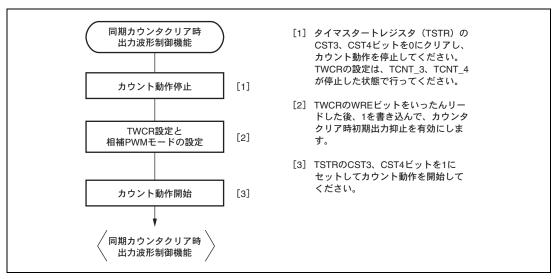

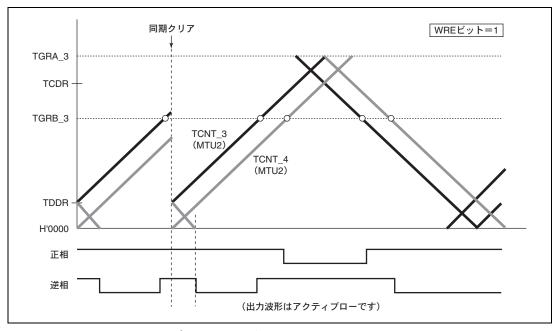

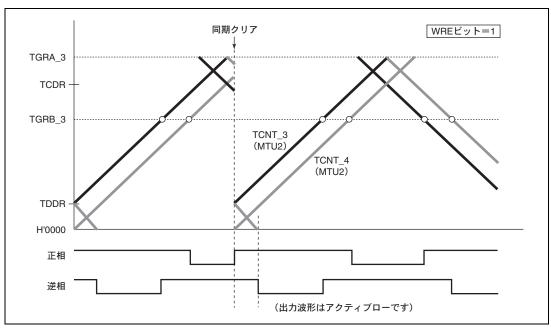

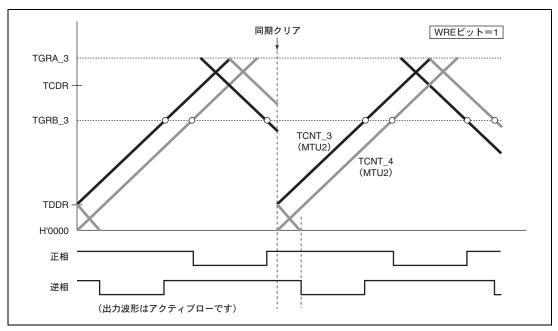

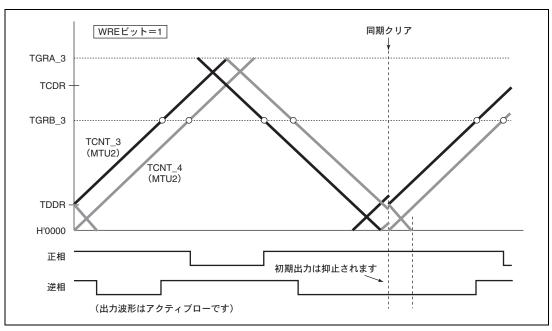

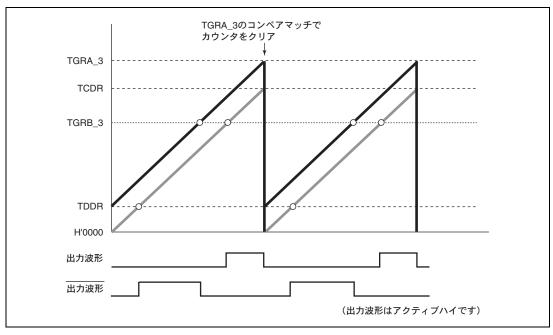

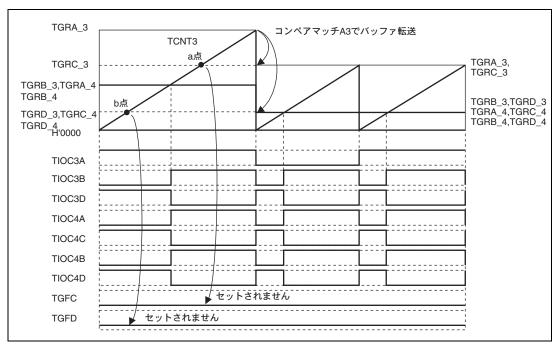

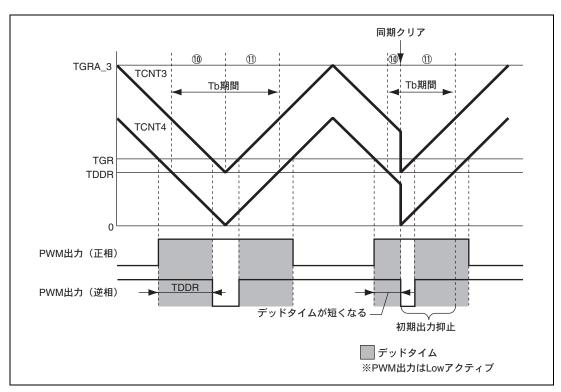

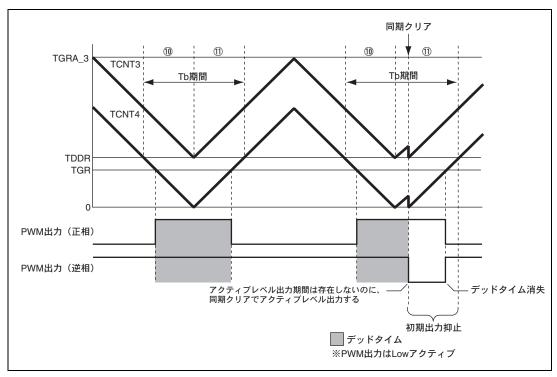

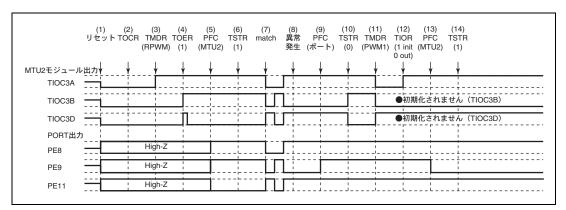

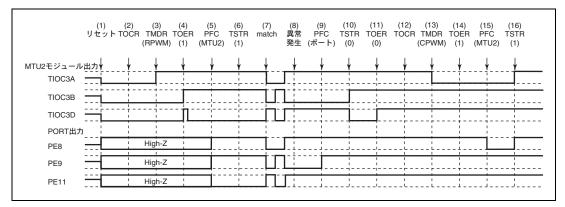

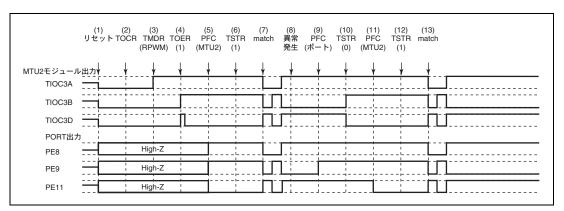

| 12.4.7  | リセット同期 PWM モード                           | 12-93  |

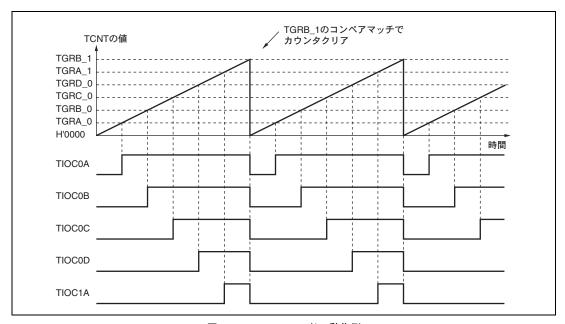

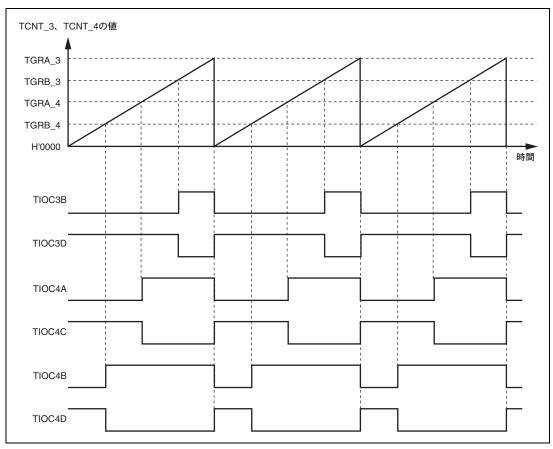

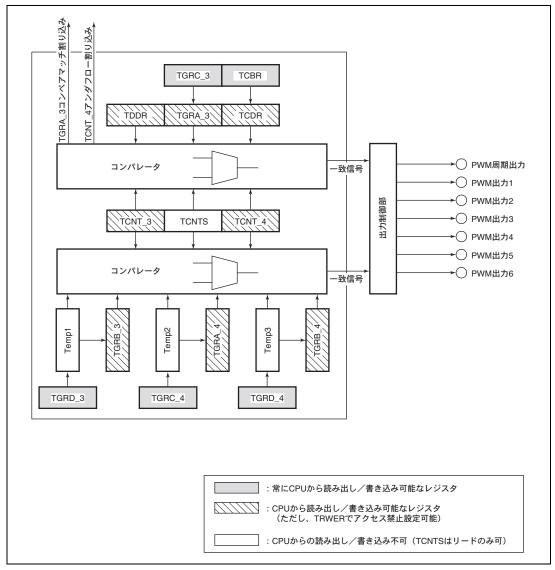

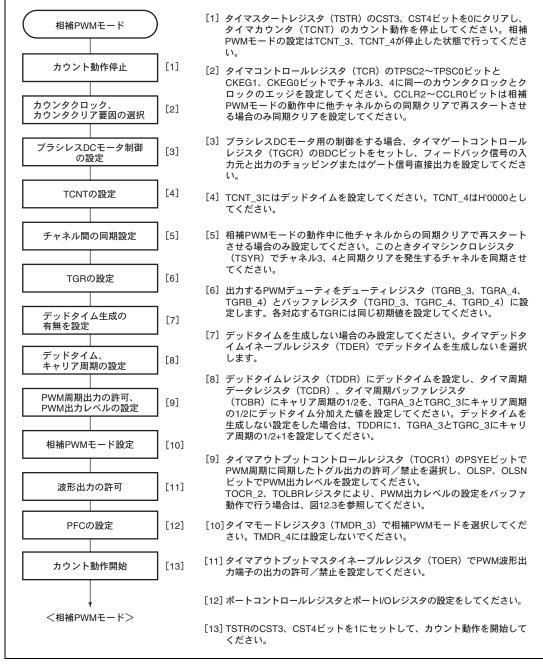

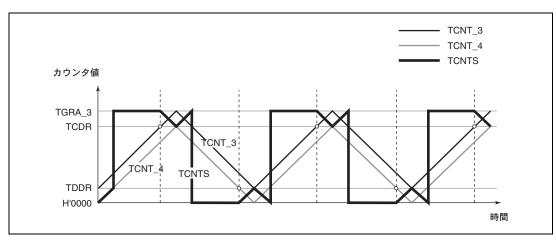

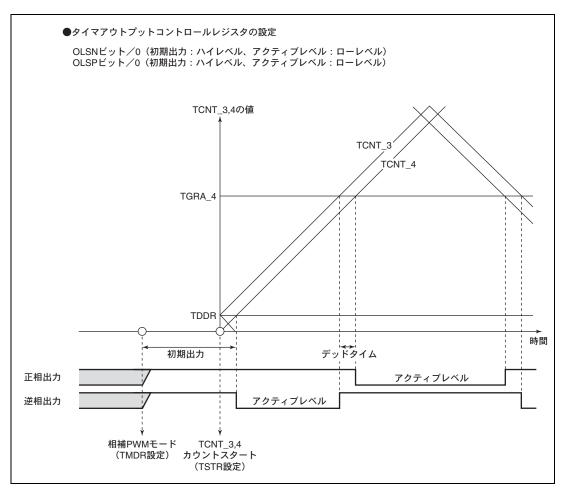

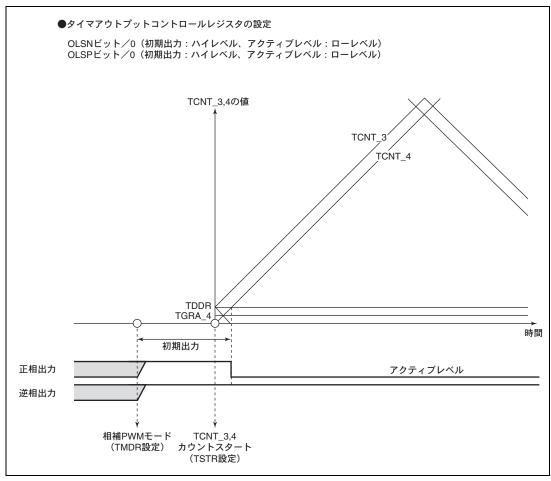

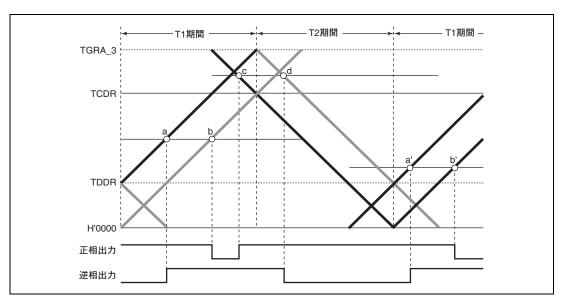

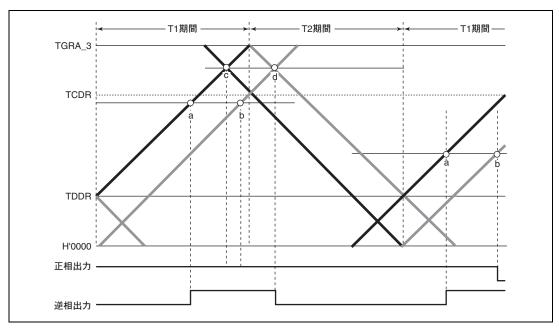

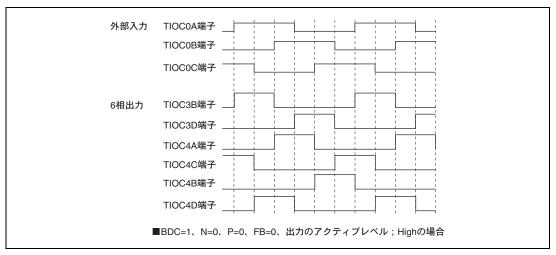

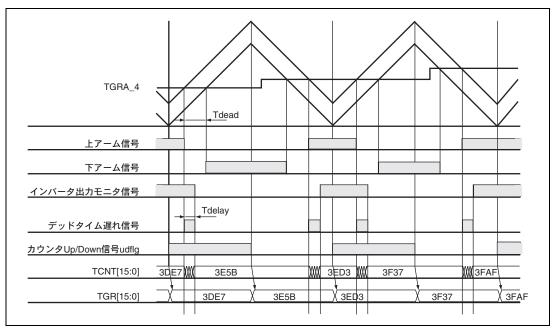

| 12.4.8  | 相補 PWM モード                               | 12-96  |

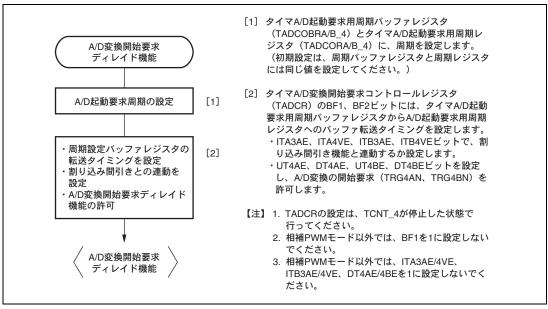

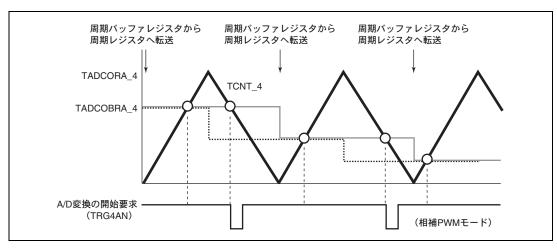

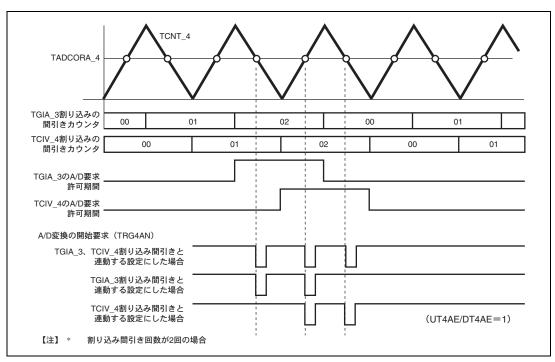

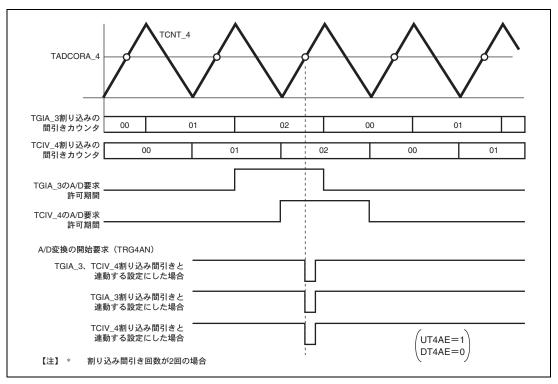

| 12.4.9  | A/D 変換開始要求ディレイド機能                        | 12-128 |

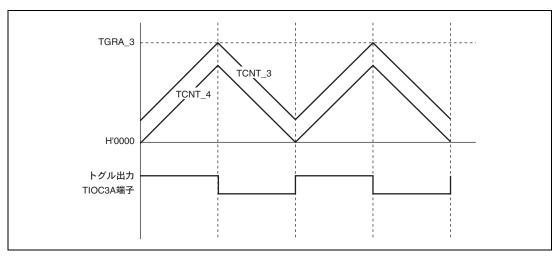

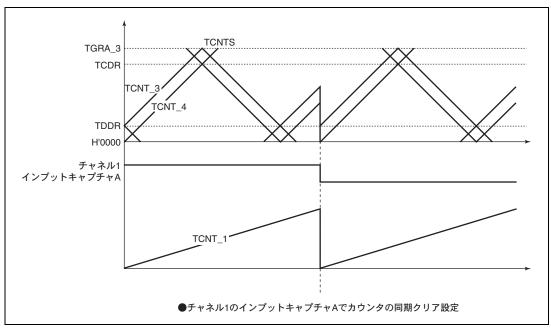

| 12.4.10 | 相補 PWM の「山/谷」での TCNT キャプチャ動作             | 12-132 |

| 12.5    | 割り込み要因                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12-133 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 12.5.1  | 割り込み要因と優先順位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12-133 |

| 12.5.2  | ダイレクトメモリアクセスコントローラの起動                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12-135 |

| 12.5.3  | A/D 変換器の起動                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12-135 |

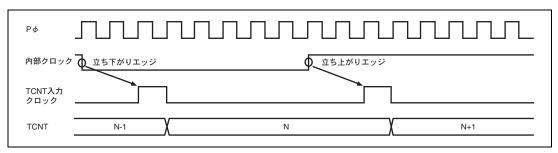

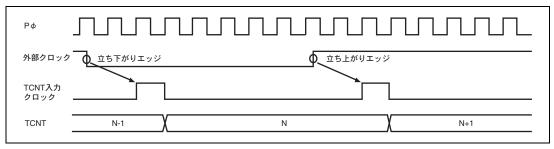

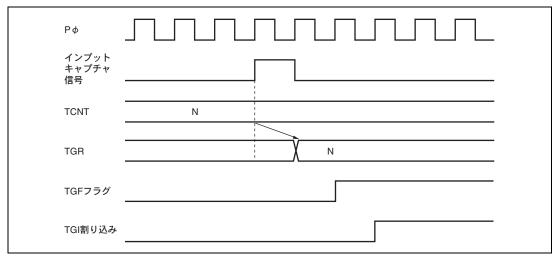

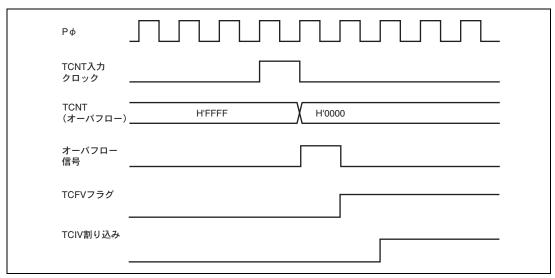

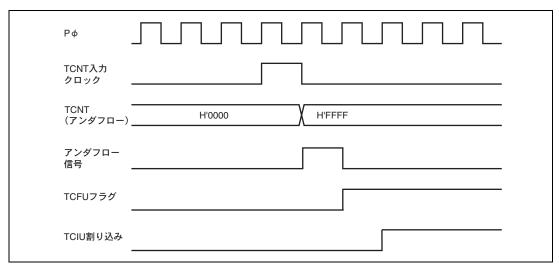

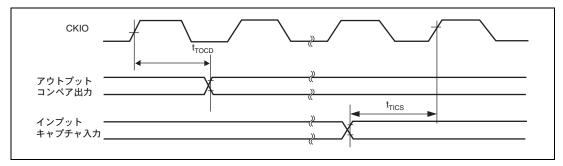

| 12.6    | 動作タイミング                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-137 |

| 12.6.1  | 入出力タイミング                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12-137 |

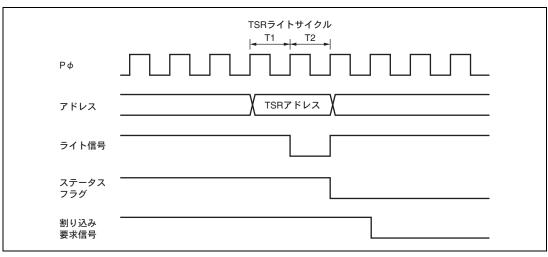

| 12.6.2  | 割り込み信号タイミング                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12-144 |

| 12.7    | 使用上の注意事項                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12-148 |

| 12.7.1  | モジュールスタンバイモードの設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12-148 |

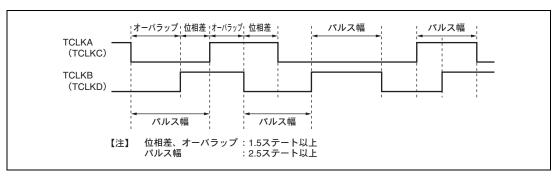

| 12.7.2  | 入力クロックの制限事項                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12-148 |

| 12.7.3  | 周期設定上の注意事項                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12-148 |

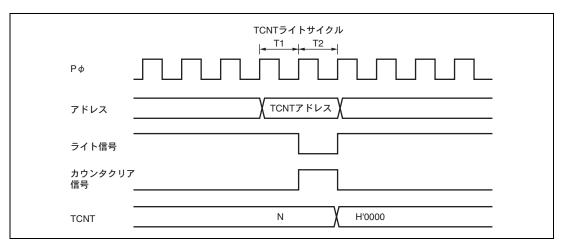

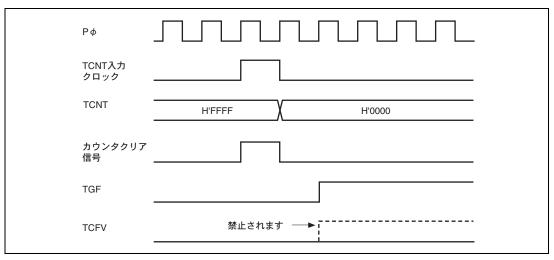

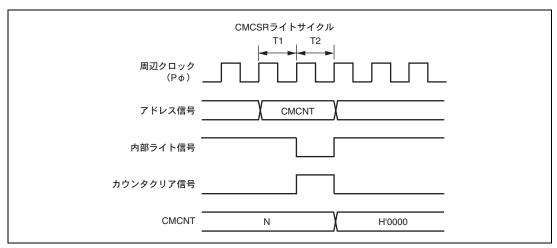

| 12.7.4  | TCNT のライトとクリアの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12-149 |

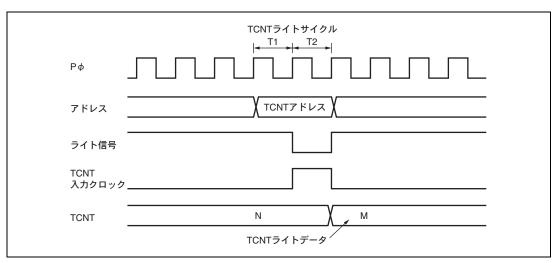

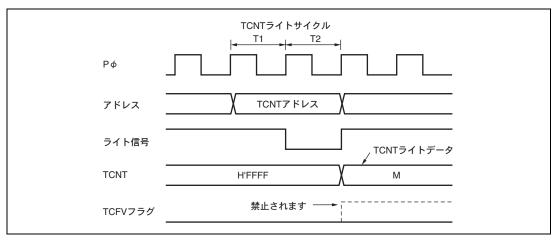

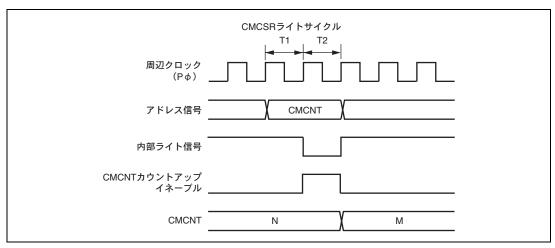

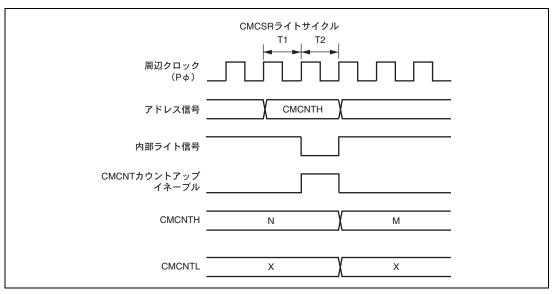

| 12.7.5  | TCNT のライトとカウントアップの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12-149 |

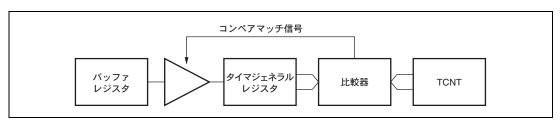

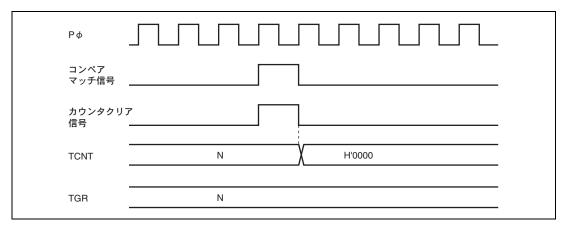

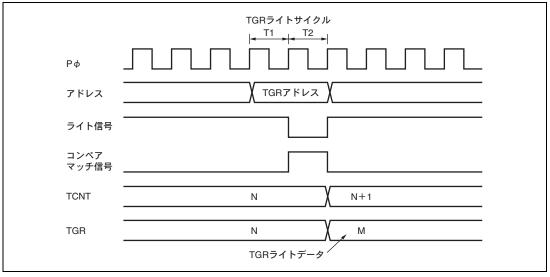

| 12.7.6  | TGR のライトとコンペアマッチの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12-150 |

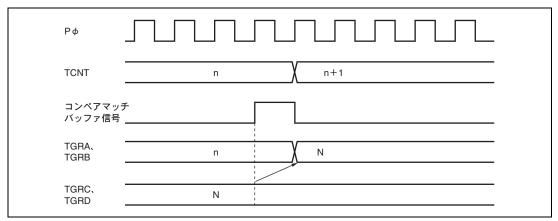

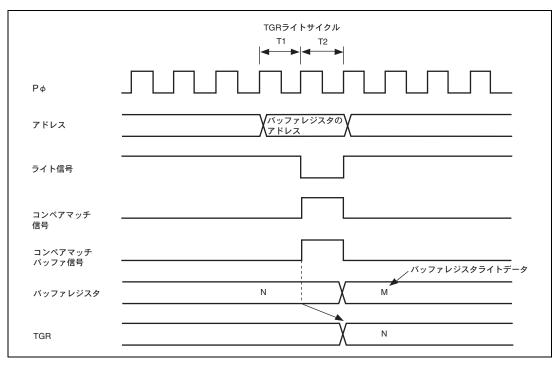

| 12.7.7  | バッファレジスタのライトとコンペアマッチの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-151 |

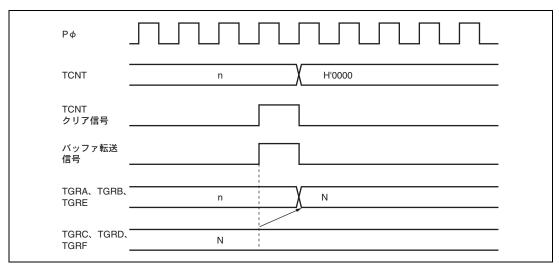

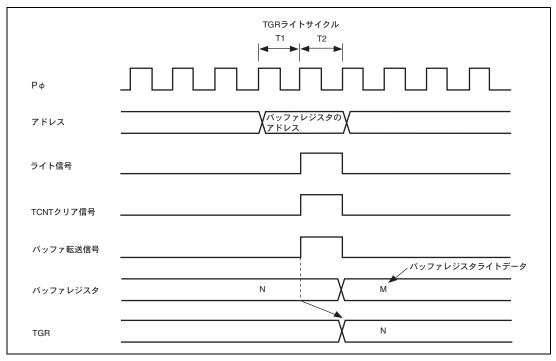

| 12.7.8  | バッファレジスタのライトと TCNT クリアの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12-152 |

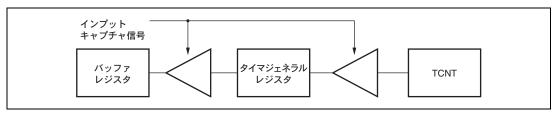

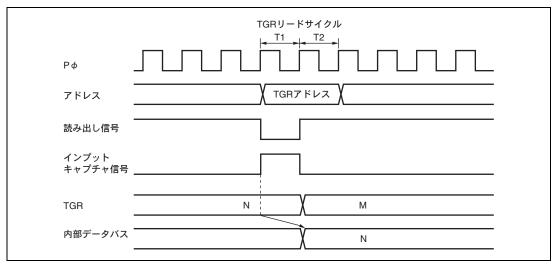

| 12.7.9  | TGR のリードとインプットキャプチャの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12-153 |

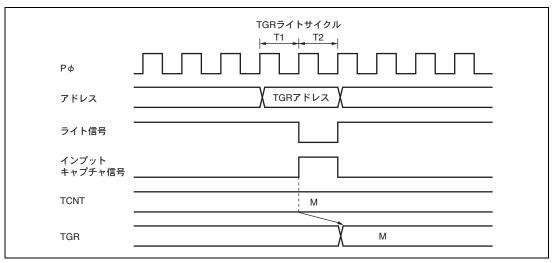

| 12.7.10 | TGR のライトとインプットキャプチャの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12-154 |

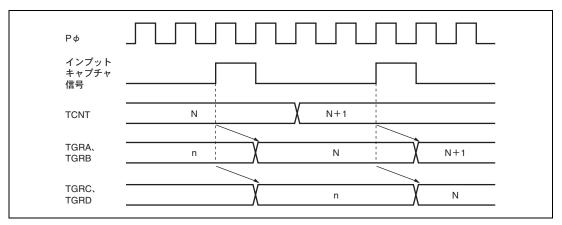

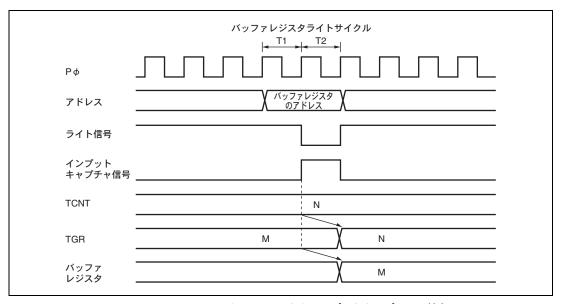

| 12.7.11 | バッファレジスタのライトとインプットキャプチャの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12-155 |

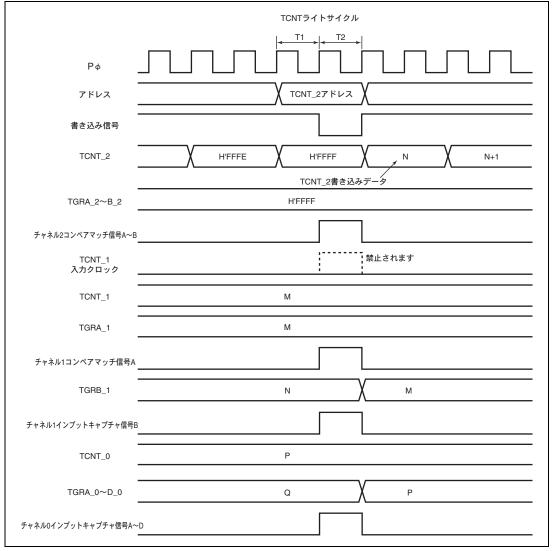

| 12.7.12 | カスケード接続における TCNT_2 のライトとオーバフロー/アンダフローの 競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12-155 |

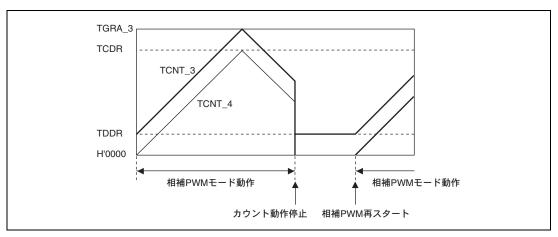

| 12.7.13 | 相補 PWM モード停止時のカウンタ値                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12-157 |

| 12.7.14 | 相補 PWM モードでのバッファ動作の設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12-157 |

| 12.7.15 | リセット同期 PWM モードのバッファ動作とコンペアマッチフラグ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12-158 |

| 12.7.16 | リセット同期 PWM モードのオーバフローフラグ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12-159 |

| 12.7.17 | オーバフロー/アンダフローとカウンタクリアの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12-160 |

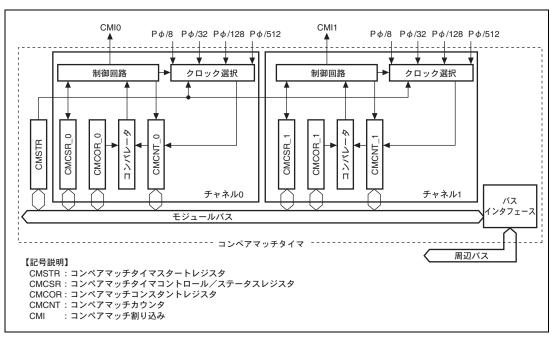

| 12.7.18 | TCNT のライトとオーバフロー/アンダフローの競合                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12-160 |