概要

説明

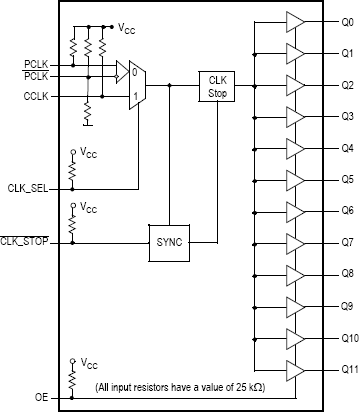

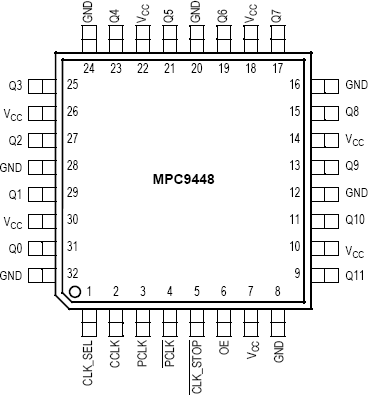

The MPC9448 is specifically designed to distribute LVCMOS compatible clock signals up to a frequency of 350 MHz. Each output provides a precise copy of the input signal with a near zero skew. The outputs buffers support driving of 50Ω terminated transmission lines on the incident edge. Each output is capable of driving either one parallel terminated or two series terminated transmission lines. Two selectable, independent clock inputs are available, providing support of LVCMOS and differential LVPECL clock distribution systems. The MPC9448 CLK_STOP control is synchronous to the falling edge of the input clock. It allows the start and stop of the output clock signal only in a logic low state, thus eliminating potential output runt pulses. Applying the OE control will force the outputs into high-impedance mode. All inputs have an internal pull-up or pull-down resistor preventing unused and open inputs from floating. The device supports a 2.5 V or 3.3 V power supply and an ambient temperature range of -40°C to +85°C. The MPC9448 is pin and function compatible but performance-enhanced to the MPC948.

特長

- 12 LVCMOS compatible clock outputs

- Selectable LVCMOS and differential LVPECL compatible clock inputs

- Maximum clock frequency of 350 MHz

- Maximum clock skew of 150 ps

- Synchronous output stop in logic low state eliminates output runt pulses

- High-impedance output control

- 3.3 V or 2.5 V power supply

- Drives up to 24 series terminated clock lines

- Ambient temperature range -40°C to +85°C

- 32-Lead LQFP packaging

- 32-lead Pb-free package available

- Supports clock distribution in networking, telecommunication and computing applications

- Pin and function compatible to MPC948

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。