# ForgeFPGA Workshop User Guide v6.42

This user guide will help you navigate the ForgeFPGA Workshop and understand the different features inbuilt in the software in detail.

### Contents

| 1. | Softv | vare Ove | rview                                | 5  |

|----|-------|----------|--------------------------------------|----|

| 2. | Forg  | e FPGA   | Norkshop                             | 7  |

|    | 2.1   | FPGA E   | ditor                                | 7  |

|    |       | 2.1.1    | Flowchart                            | 7  |

|    |       | 2.1.2    | Main Menu                            | 9  |

|    |       | 2.1.3    | Toolbar                              | 11 |

|    |       | 2.1.4    | Work Area                            | 11 |

|    |       | 2.1.5    | Logger Panel                         | 12 |

|    |       | 2.1.6    | Control Panel                        | 12 |

|    |       | 2.1.7    | Settings                             | 13 |

|    | 2.2   | Writing  | HDL Code                             | 14 |

|    | 2.3   | Modules  | s Library                            | 15 |

|    | 2.4   | RTL Syı  | nthesis                              | 17 |

|    |       | 2.4.1    | Post-Synth RTL                       | 17 |

|    |       | 2.4.2    | Netlist                              | 17 |

|    | 2.5   | Generat  | ing the Bitstream                    | 18 |

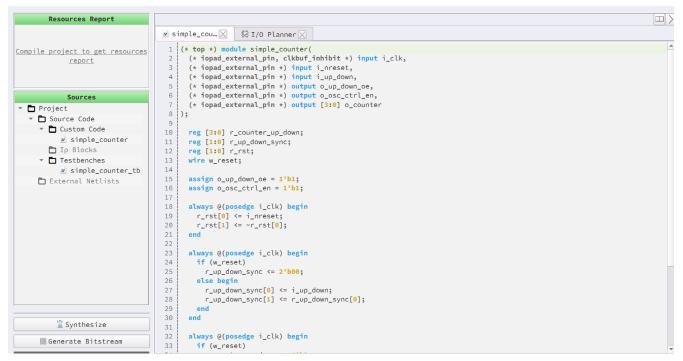

|    |       | 2.5.1    | I/O Planner                          | 19 |

|    | 2.6   | Floorpla | n                                    | 20 |

|    | 2.7   | Resourc  | ces Utilization Report               | 20 |

|    | 2.8   | Timing / | Analysis                             | 21 |

|    | 2.9   | PLL Cal  | culator                              | 22 |

|    | 2.10  | Build Fo | lder                                 | 22 |

|    | 2.11  | Simulati | on                                   | 23 |

|    |       | 2.11.1   | Writing a Testbench                  | 23 |

|    |       | 2.11.2   | Simulating a Testbench               | 25 |

|    | 2.12  | Macroce  | ell Editor                           | 25 |

| 3. | Debu  | ıa       |                                      | 26 |

|    | 3.1   | -        | re Platforms                         |    |

|    |       | 3.1.1    | ForgeFPGA Advanced Development Board |    |

|    |       | 3.1.2    | ForgeFPGA Evaluation Board           |    |

|    | 3.2   | Platform | o Configuration Guide                |    |

|    | 3.3   |          | с<br>Гооls                           |    |

|    |       | 3.3.1    | Configuration Button:                |    |

|    |       | 3.3.2    | Synchronous Logic Generator          |    |

|    |       | 3.3.3    | Parametric Generator                 |    |

|    | 3.4   |          | nalyzer                              |    |

|    |       | 3.4.1    | Operational Controls                 |    |

|    |       |          |                                      |    |

| Α. | Appendix: Warnings |                |                          |    |  |  |

|----|--------------------|----------------|--------------------------|----|--|--|

| 7. | Revis              | ion Histo      | ory                      | 46 |  |  |

| 6. | IO Pla             | anner Sig      | gnals                    | 45 |  |  |

| 5. | NVM                | Viewer         |                          | 43 |  |  |

|    | 4.6                | General        | Purpose Input Output Pin | 43 |  |  |

|    | 4.5                | EN (nSL        | EEP) & PWR (nRST)        | 43 |  |  |

|    | 4.4                | Block Re       | ead Access Memory (BRAM) | 42 |  |  |

|    | 4.3                | Oscillato      | r (OSC)                  | 42 |  |  |

|    | 4.2                | Phase Lo       | ocked Loop (PLL)         | 42 |  |  |

|    | 4.1                | FPGA C         | ore                      | 41 |  |  |

| 4. | Block              | <b>Propert</b> | ies                      | 41 |  |  |

|    |                    | 3.4.11         | UART Terminal            | 40 |  |  |

|    |                    | 3.4.10         | Markers                  | 39 |  |  |

|    |                    | 3.4.9          | Cursors                  | 38 |  |  |

|    |                    | 3.4.8          | Plot Widget              | 37 |  |  |

|    |                    | 3.4.7          | Import/Export            | 37 |  |  |

|    |                    | 3.4.6          | Protocol Analyzer        |    |  |  |

|    |                    | 3.4.5          | Presets                  | 36 |  |  |

|    |                    | 3.4.4          | Debugging Controls       |    |  |  |

|    |                    | 3.4.3          | Triggers                 |    |  |  |

|    |                    | 3.4.2          | Mode                     | 35 |  |  |

# Figures

| Figure 1. Go Configure Software Hub User Interface                   |    |

|----------------------------------------------------------------------|----|

| Figure 2. ForgeFPGA Workshop                                         | 7  |

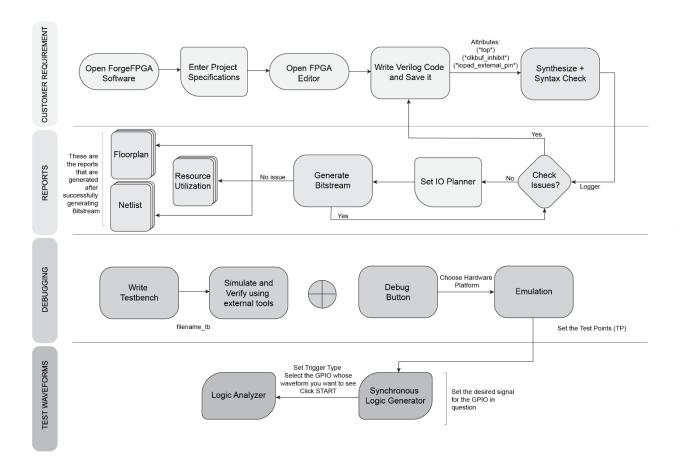

| Figure 3. ToolChain Flowchart                                        | 8  |

| Figure 4. ForgeFPGA Workshop User Interface                          | 9  |

| Figure 5. ForgeFPGA Workshop Toolbar                                 | 11 |

| Figure 6. Work Area                                                  | 11 |

| Figure 7. Logger Panel                                               | 12 |

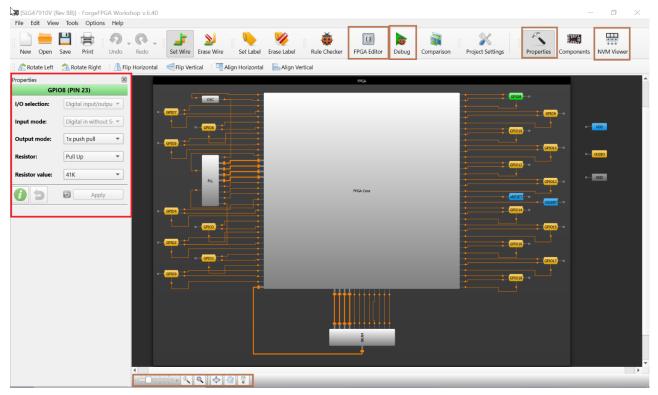

| Figure 8. Control Panel                                              | 13 |

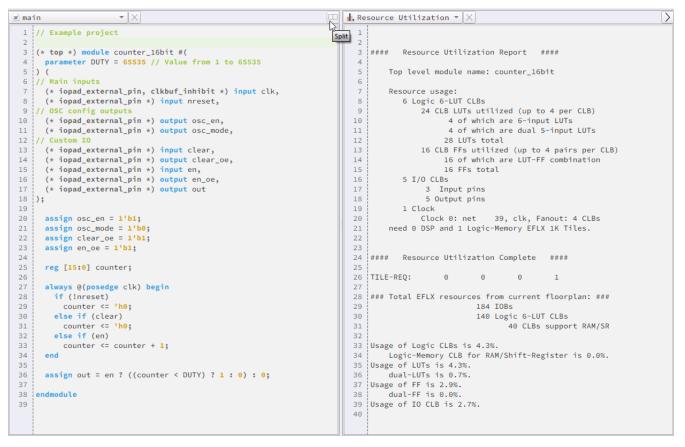

| Figure 9. Working with Verilog example                               | 15 |

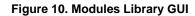

| Figure 10. Modules Library GUI                                       | 16 |

| Figure 11. Module Library GUI with Parameters                        | 16 |

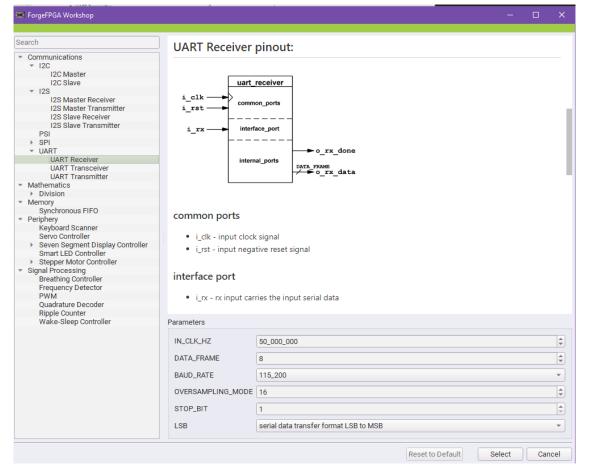

| Figure 12. Post-Synth RTL                                            | 17 |

| Figure 13. Netlist                                                   | 18 |

| Figure 14. Mapping I/O Ports                                         | 19 |

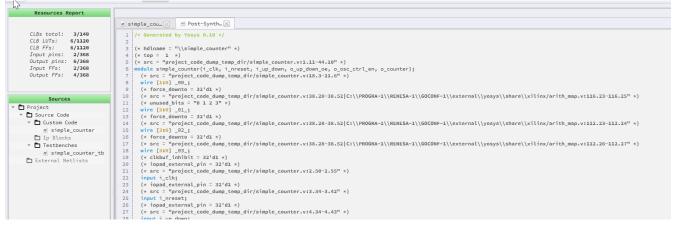

| Figure 15. Place and Route Results                                   | 20 |

| Figure 16. Place and Route Results                                   | 20 |

| Figure 17. Resources Utilized Report                                 | 21 |

| Figure 18. Timing Analysis                                           | 22 |

| Figure 19. PLL Calculator                                            | 22 |

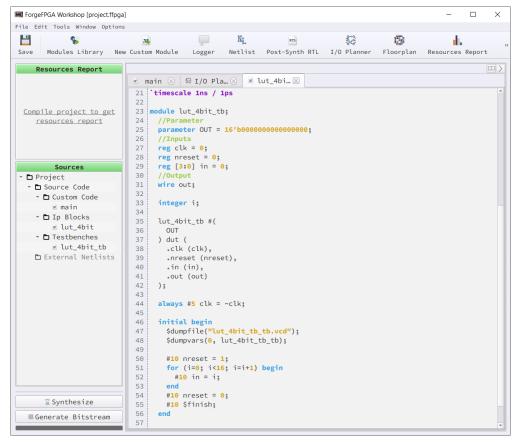

| Figure 20. Custom Testbench example                                  | 24 |

| Figure 21. 4-bit LUT Testbench example from Modules Library          | 24 |

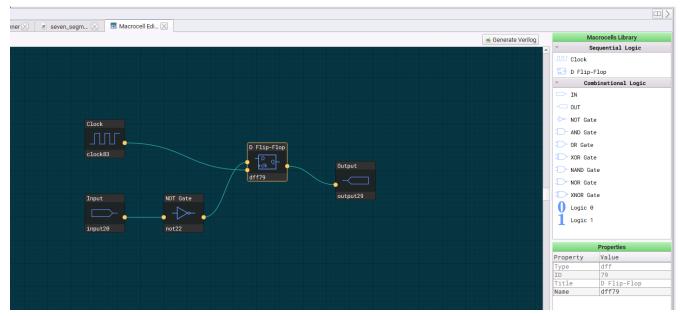

| Figure 22. Macrocell Editor                                          | 25 |

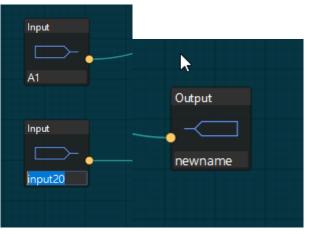

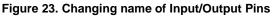

| Figure 23. Changing name of Input/Output Pins                        | 25 |

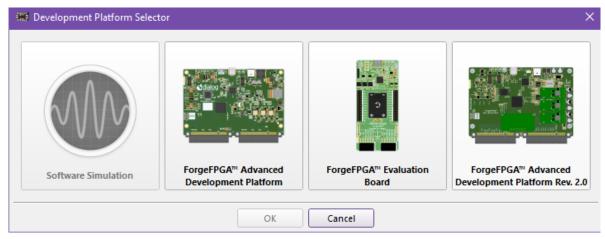

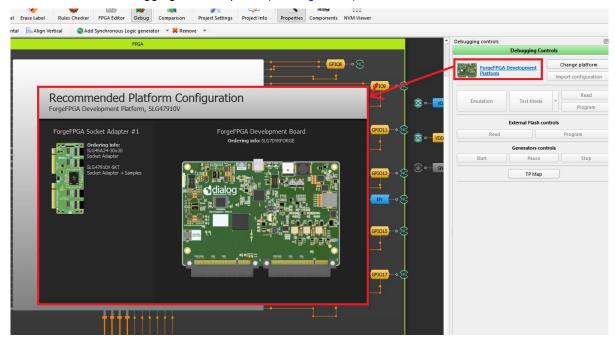

| Figure 24. Development Platform Selector                             | 26 |

| Figure 25. Development Platform Selector                             | 26 |

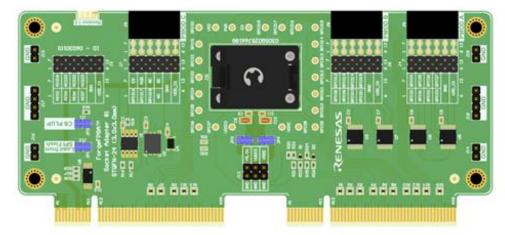

| Figure 26. Assembled equipment for working with a chip in the socket | 27 |

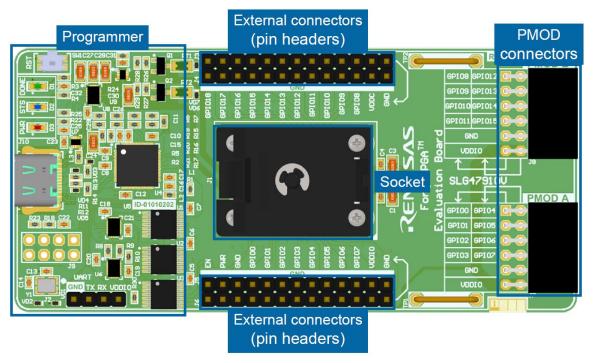

| Figure 27. ForgeFPGA Evaluation Board v2.0                           | 28 |

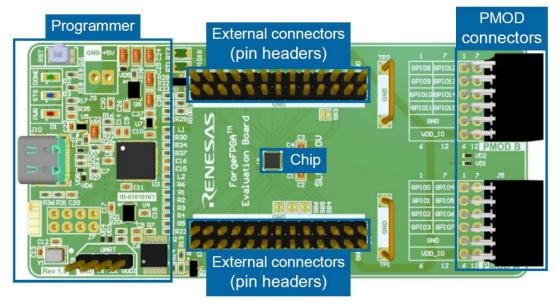

| Figure 28. ForgeFPGA Evaluation Board v1.0                           | 28 |

| Figure 29. Platform Configuration Guide                              | 29 |

| Figure 30. Debugging Controls                                        | 29 |

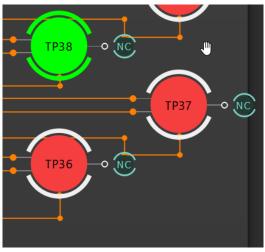

| Figure 31. TP Map                                                    | 30 |

| Figure 32. Debug Tool                                                | 31 |

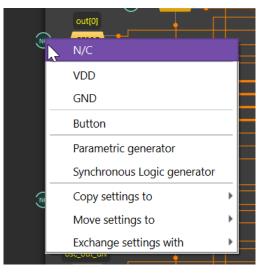

| Figure 33. NC (not connected)                                        | 31 |

| Figure 34. Set to VDD                                                | 31 |

| Figure 35. Set to GND                                                | 31 |

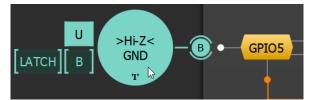

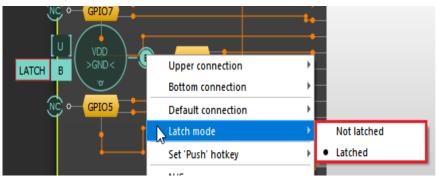

| Figure 36. Latched Button with Upper Connection as VDD               | 32 |

| Figure 37. Unlatched Button with Upper Connection as Hi-Z            | 32 |

| Figure 38. Context menu options for Configurable Button              | 32 |

| Figure 39. Synchronous Logic Generator                               | 32 |

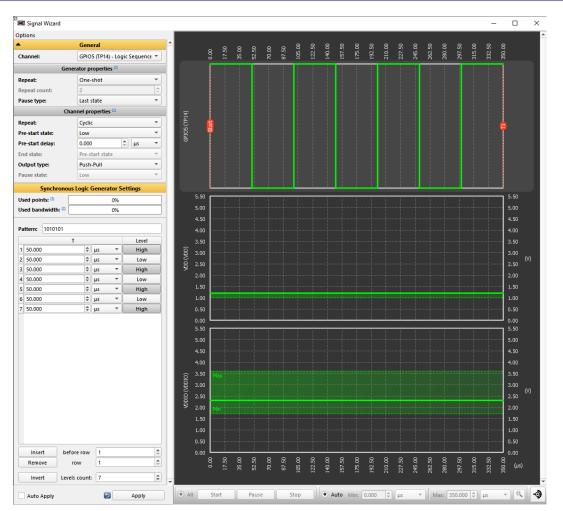

| Figure 40. Signal Wizard for Synchronous Logic Generator             |    |

| Figure 41. Parametric Generator Command Editor                       |    |

| Figure 42. PWM Command Editor                                        |    |

| Figure 43. Clock Command Editor                                      |    |

| Figure 44. Clock Command Editor                                      |    |

|                                                                      |    |

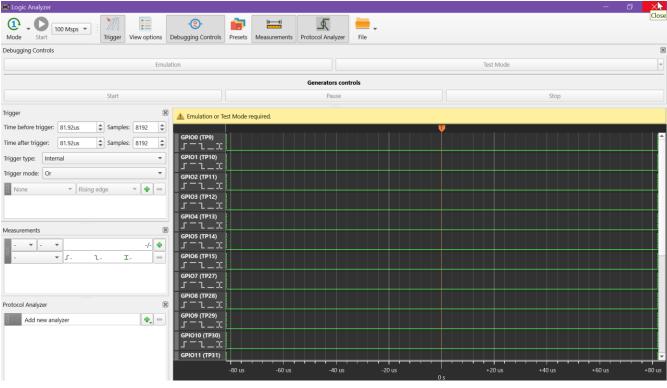

| Figure 45. Logic Analyzer                                         | 35 |

|-------------------------------------------------------------------|----|

| Figure 46. Trigger Parameters                                     | 36 |

| Figure 47. Trigger Conditions                                     | 36 |

| Figure 48. View Options                                           | 36 |

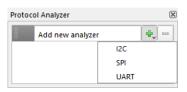

| Figure 49. Protocol Analyzer Decode Options                       | 37 |

| Figure 50. Protocol Analyzer Options                              | 37 |

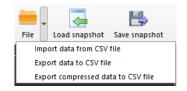

| Figure 51. Import/Export from/to CSV format                       | 37 |

| Figure 52. Plot Widget                                            | 37 |

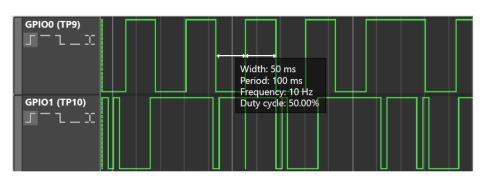

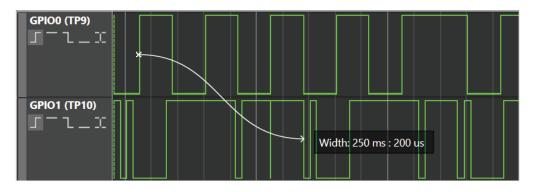

| Figure 53. Half Period Cursor                                     | 38 |

| Figure 54. Period Cursor                                          | 38 |

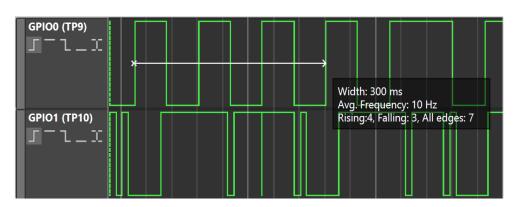

| Figure 55. Adjustable Period Cursor for Measurement               | 39 |

| Figure 56. Adjustable Period Cursor Measurement between waveforms | 39 |

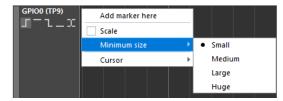

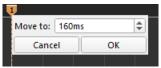

| Figure 57. Moving markers with context menu                       | 39 |

| Figure 58. Marker Measurements                                    | 40 |

| Figure 59. UART Terminal Tool                                     | 40 |

| Figure 60. UART Terminal Window                                   | 40 |

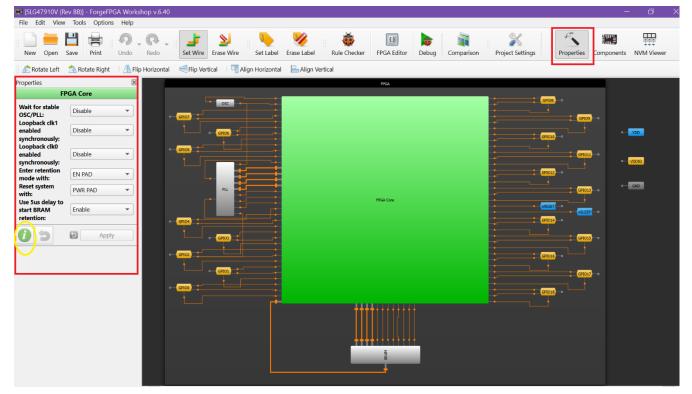

| Figure 61. Block Property Editing                                 | 41 |

| Figure 62. FPGA Core's Properties                                 | 42 |

| Figure 63. GPIO Properties                                        | 43 |

| Figure 64. NVM Bits for GPIO7                                     | 44 |

| Figure 65. NVM Bits 0011 after the property has been modified     | 44 |

# Reference

For related documents and software, please visit our website:

Download our free ForgeFPGA Designer software [1] and follow the steps in this user guide. User can reference [2] for the datasheet. Use Configuration Document to understand the different modes of configuration [3]. Renesas Electronics provides a complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the Renesas IC. Please visit the <u>product page</u> to download the following :

- [1] Go Configure Software Hub, Software Download, Renesas Electronics

- [2] ForgeFPGA SLG47910 Datasheet, Renesas Electronics

- [3] SLG47910, Configuration Document, Renesas Electronics

- [4] Application Notes, ForgeFPGA Application Notes & Design Files, Renesas Electronics

- [5] ForgeFPGA Development Board User Manual, Renesas Electronics

- [6] ForgeFPGA Socket Adapter User Manual, Renesas Electronics

- [7] ForgeFPGA Evaluation Board User Manual, Renesas Electronics

- [8] ForgeFPGA Software Simulation User Manual, Renesas Electronics

### 1. Software Overview

Go Configure Software Hub is a product, created to design a specific device configuration. The software gives a direct access to all GreenPAK, ADCPAK and ForgeFPGA device features and complete control over the routing and configuration options.

The software contains the tools that allow you to:

- Creating FPGA Project in HDL

- Program a chip with the created design

- Read a programmed part and import its data to the software

- Simulate with external components

#### Getting Started:

1. Download and install Go Configure Software Hub from <a href="https://www.renesas.com/us/en/software-tool/go-configure-software-hub">https://www.renesas.com/us/en/software-tool/go-configure-software-hub</a>

|                                                               | Software Tool         | Part Family    |                                                                                                                                                                                                                                                                                |                                                                                                                                                   |                                                                                              |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                |                                              |

|---------------------------------------------------------------|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------|

| elcome                                                        | All                   | All            | SLG4                                                                                                                                                                                                                                                                           | 1/910                                                                                                                                             | V (Rev B                                                                                     | B)                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                | Filter                                       |

|                                                               |                       |                | Part Number                                                                                                                                                                                                                                                                    | DS                                                                                                                                                | VDD (V)                                                                                      | VDD2 (V)                                                                                           | GPI GPO GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AEC-Q100                                                       | Special Fea                                  |

|                                                               |                       | GreenPAK       | SLG47004-AP                                                                                                                                                                                                                                                                    | Contact us                                                                                                                                        | 2.40 to 5.50                                                                                 | -                                                                                                  | 1 0 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Grade 1                                                        | 2x Op Amp or 1x In-Amp; 2x Rheostat          |

| ecent                                                         |                       |                | SLG51003V                                                                                                                                                                                                                                                                      | Contact us                                                                                                                                        | 2.80 to 5.00                                                                                 | 1.20 to 5.00                                                                                       | 1 0 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | 3x LDO (1x HP 475 mA; 1x HV 500 mA; 1x LV    |

| files                                                         |                       | AnalogPAK      | SLG47003V                                                                                                                                                                                                                                                                      | Contact us                                                                                                                                        | 2.30 to 5.50                                                                                 | -                                                                                                  | 5 0 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                              | 2x Op Amp; 2x Rheos                          |

|                                                               |                       |                | K SLG47011V                                                                                                                                                                                                                                                                    | Contact us                                                                                                                                        | 1.71 to 3.60                                                                                 | -                                                                                                  | 1 0 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                              | ADC (14-bit; SAR), DAC (12-bit), PGA 1x-64x, |

|                                                               | GreenPAK              | 1000414        | SLG51000C                                                                                                                                                                                                                                                                      | PDF                                                                                                                                               | 2.80 to 5.00                                                                                 | 2                                                                                                  | 1 0 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                | Synchronized; 7x LDO (2x HP 475 mA; 3x HV 5  |

|                                                               | Designer              | HVPAK          | SLG51001C                                                                                                                                                                                                                                                                      | PDF                                                                                                                                               | 2.80 to 5.00                                                                                 | -                                                                                                  | 1 0 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                              | Synchronized; 6x LDO (1x HP 475 mA; 4x HV 5  |

|                                                               |                       |                | SLG47910V (Rev AA)                                                                                                                                                                                                                                                             | Contact us                                                                                                                                        | 0.99 to 1.21                                                                                 | 1.71 to 3.60                                                                                       | 0 0 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                              | Dense Logic Array;                           |

| elop                                                          |                       | Power GreenPAK | SLG47910V (Rev BB)                                                                                                                                                                                                                                                             | Contact us                                                                                                                                        | 0.99 to 1.21                                                                                 | 1.71 to 3.60                                                                                       | 0 0 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                              | Dense Logic Array;                           |

|                                                               |                       |                | SLG51002C                                                                                                                                                                                                                                                                      | PDF                                                                                                                                               | 2.80 to 5.00                                                                                 | 1.20 to 5.00                                                                                       | 1 0 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                | 8x LDO (3x HV 500 mA; 2x HC 500 mA;          |

|                                                               |                       |                | SLG47004V                                                                                                                                                                                                                                                                      | PDF                                                                                                                                               | 2.40 to 5.50                                                                                 | 2                                                                                                  | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                | 2x Op Amp or 1x In-Amp; 2x Rheostat; 2x A    |

|                                                               |                       | AutomotivePAK  | SLG47115V                                                                                                                                                                                                                                                                      | PDF                                                                                                                                               | 2.30 to 5.50                                                                                 | 4.50 to 26.40                                                                                      | 1 2 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                              | 1x H-/2x Half- Bridge; 2x PWM                |

|                                                               | ForgeFPGA<br>Workshop | ForgeFPGA      | ICM SLG47105V                                                                                                                                                                                                                                                                  | PDF                                                                                                                                               | 2.30 to 5.50                                                                                 | 3.00 to 13.20                                                                                      | 1 4 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ~                                                              | 2x H-/4x Half- Bridge; 2x PWM;               |

|                                                               |                       |                |                                                                                                                                                                                                                                                                                |                                                                                                                                                   |                                                                                              |                                                                                                    | anne de la                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                |                                              |

|                                                               |                       |                | Details                                                                                                                                                                                                                                                                        |                                                                                                                                                   |                                                                                              |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                |                                              |

|                                                               | Tronibiliop           |                |                                                                                                                                                                                                                                                                                |                                                                                                                                                   |                                                                                              |                                                                                                    | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |                                              |

|                                                               | Troncinop             |                |                                                                                                                                                                                                                                                                                | [                                                                                                                                                 | ontact us for Datash                                                                         | eet   Product page   Ar                                                                            | oplication notes   Resource                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | tes   Get samples   Cor                                        | ntact us ]                                   |

|                                                               | nononop               |                | Package:                                                                                                                                                                                                                                                                       | [0                                                                                                                                                | ontact us for Datash                                                                         | eet   Product page   Ap                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tes   <u>Get samples   Cor</u>                                 | atact us ]                                   |

| cation                                                        | Tononop               |                | Package:<br>QFN-24                                                                                                                                                                                                                                                             | [0                                                                                                                                                | ontact us for Datash                                                                         | eet   Product page   Ap                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tes   Get samples   Cor                                        | tact us ]                                    |

| cation                                                        |                       |                | QFN-24                                                                                                                                                                                                                                                                         |                                                                                                                                                   | ontact us for Datash                                                                         | eet   Product page   Ar                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tes   Get samples   Cor                                        | tact us ] 🔺                                  |