改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

# SH7265 グループ

ユーザーズマニュアル ハードウェア編 ルネサス 32 ビット RISC マイクロコンピュータ SuperH™RISC engine ファミリ / SH7260 シリーズ

SH7265

R5S72650P200BG R5S72651P200BG R5S72652P200BG R5S72653P200BG

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、 応用例を説明するものです。お客様の機器・システムの設計において、回路、ソフトウェアお よびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これ らの使用に起因して、お客様または第三者に生じた損害に関し、当社は、一切その責任を負い ません。

- 2. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

3. 本資料に記載された製品デ-タ、図、表、プログラム、アルゴリズム、応用回路例等の情報の

- 3. 本資料に記載された製品デ・タ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権に対する侵害に関し、当社は、何らの責任を負うものではありません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4 . 当社製品を改造、改変、複製等しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、 各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、

家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準: 輸送機器(自動車、電車、船舶等) 交通用信号機器、

防災・防犯装置、各種安全装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(原子力制御システム、軍事機器等)に使用されることを意図しておらず、使用することはできません。 たとえ、意図しない用途に当社製品を使用したことによりお客様または第三者に損害が生じても、当社は一切その責任を負いません。 なお、ご不明点がある場合は、当社営業にお問い合わせください。

- 6. 当社製品をご使用の際は、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件 その他の保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の 故障および事故につきましては、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。で使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようで使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 9. 本資料に記載されている当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。また、当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途に使用しないでください。当社製品または技術を輸出する場合は、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。

- 10. お客様の転売等により、本ご注意書き記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は何らの責任も負わず、お客様にてご負担して頂きますのでご了承ください。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネ サス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する 会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は,製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザープアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。 プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

### 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品ご使用上の注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 目次

- 5. 概要

- 6. 各機能モジュールの説明

- CPUおよびシステム制御系

- 内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュールごとに異なりますが、一般的には、 特長、 入出力端子、 レジスタの説明、 動作説明、 使用上の注意事項、 等の節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認のうえ設計してください。 各章の本文中には説明に対する注意事項、各章の最後には使用上の注意事項があります。 必ずお読みください(使用上の注意事項は必要により記載されます)。

- 7. レジスター覧

- 8. 電気的特性

- 9. 付録

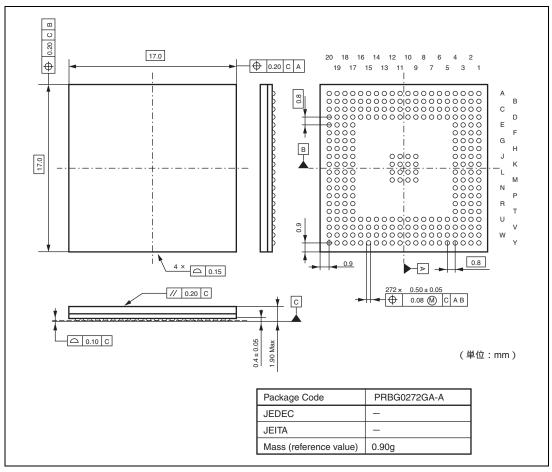

- 製品型名、外形寸法図など

- 10. 本版で改訂された箇所(改訂版のみ適用)

改訂来歴は、前版の記載内容について訂正・追加された主な箇所についてまとめたものです。 改訂内容のすべてについて記載したものではありませんので、詳細については、本書の本文上 でご確認ください。

11. 索引

## はじめに

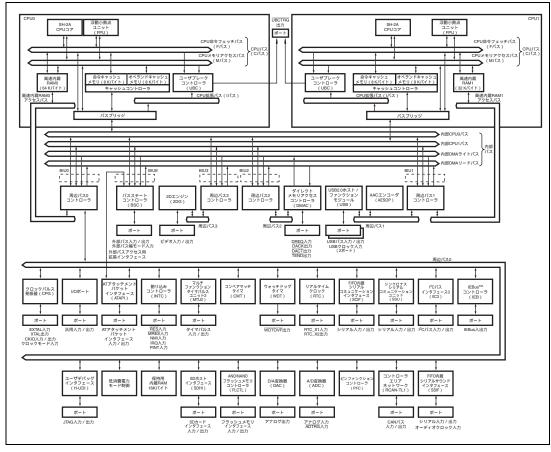

本 LSI は、ルネサスオリジナルの RISC 方式の CPU をコアにして、システム構成に必要な周辺機能を集積した RISC マイコンです。

対象者 本マニュアルは、本 LSI を用いた応用システムを設計するユーザを対象としています。本マニュアル を使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する基本的な知識を 必要とします。

目的 本マニュアルは、本 LSI のハードウェア機能と電気的特性をユーザに理解していただくことを目的に しています。

#### 読み方

• 機能全体を理解しようとするとき

目次に従って読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

• CPU機能の詳細を理解したいとき

別冊の「SH-2A、SH2A-FPU ソフトウェアマニュアル」を参照してください。

• レジスタ名がわかっていて、詳細機能を知りたいとき

本書の後ろに、「索引」があります。索引からページ番号を検索してください。

「第35章 レジスター覧」にアドレス、ビット内容、初期化についてまとめています。

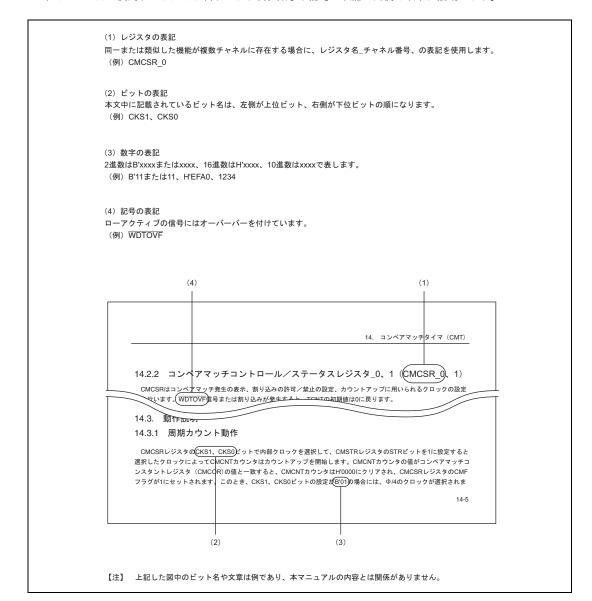

#### • 凡例

本マニュアルで使用するレジスタ名やビット名、数字や記号の表記の凡例を以下に説明します。

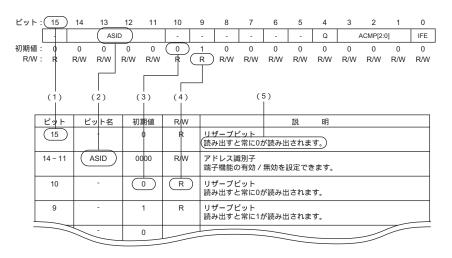

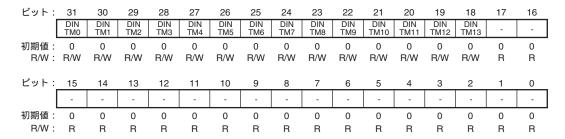

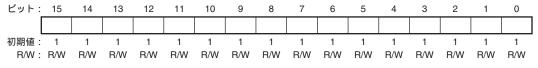

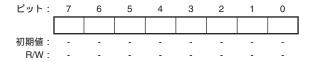

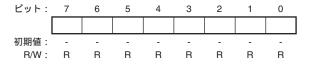

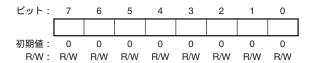

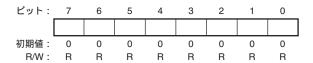

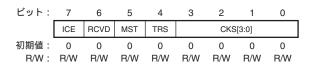

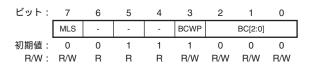

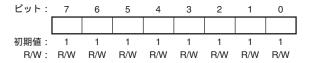

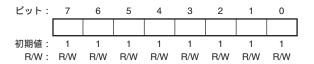

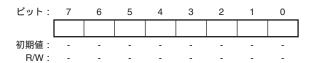

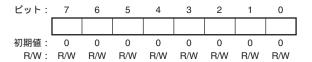

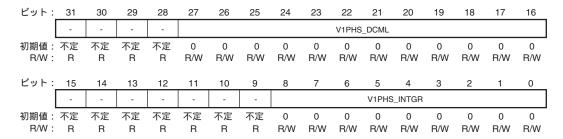

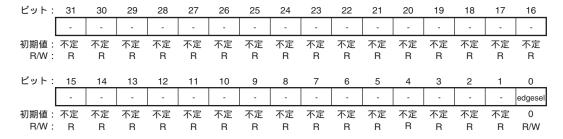

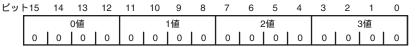

#### • ビット図とビット表の表記

各レジスタの説明には、ビットの並びを示すビット図とビットに設定する内容を説明するビット表があります。

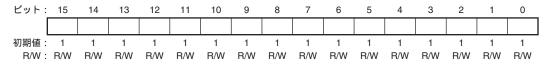

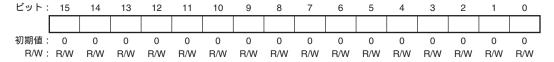

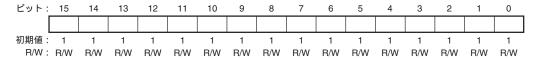

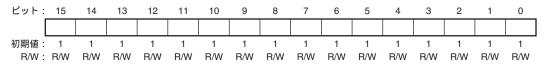

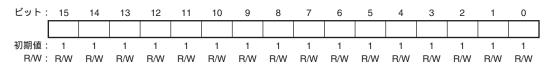

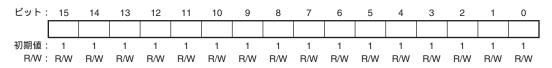

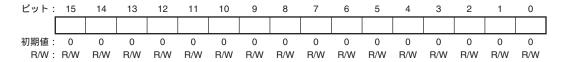

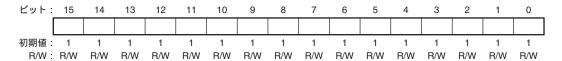

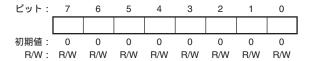

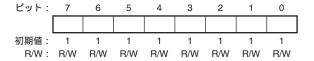

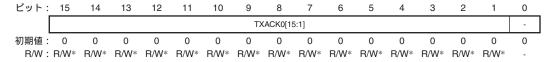

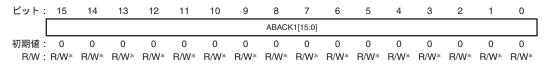

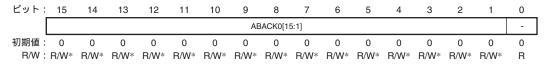

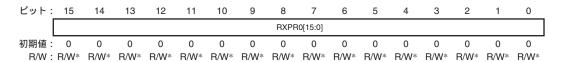

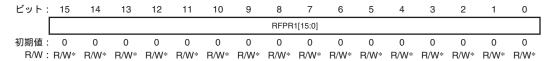

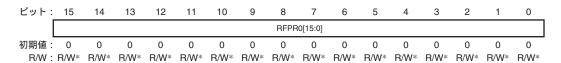

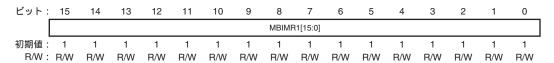

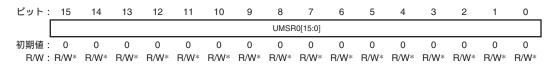

#### (1) ビット

ビット番号を示します。

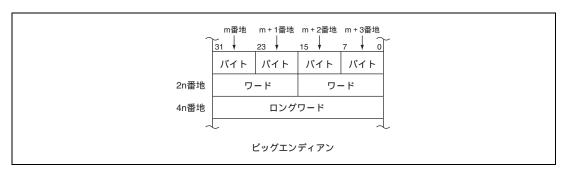

32ビットレジスタの場合は31から0の順に、16ビットレジスタの場合は15から0の順に示します。

#### (2)ビット名

レジスタのビット名またはフィールド名を示します。

フィールドでビット桁数を明示する必要があるときは、ASID[3:0]というように桁数の表記を追加します。

また、リザーブビットの場合は「 - 」と表記します。

ただし、タイムカウンタなどをはじめとして、ビット名の記載をせずに空白のままとしているものもあります。

#### (3)初期値

各ビットのパワーオンリセット後の値を初期値として示します。

0 : 初期値は0であることを示します。1 : 初期値は1であることを示します。

: 初期値は不定であることを示します。

#### (4) R/W

各ピットが読み出し可能か、書き込み可能か、または書き込みも読み出しも不可であるかを示します。 使用する表記を以下に説明します。

R/W: 読み出しおよび書き込みが可能なビットまたはフィールドです。

R/(W) : 読み出しおよび書き込みが可能なビットまたはフィールドです。

ただし書き込みは、フラグをクリアするための書き込みのみ可能です。

R : 読み出しが可能なビットまたはフィールドです。

ただし、リザーブビットはすべて「R」と表記します。書き込む必要がある場合は、

ビット表で指定された値または初期値を書き込んでください。

W : 書き込みが可能なビットまたはフィールドです。

ただし、読み出すときの値は、ビット表に記載してある場合以外は保証されません。

#### (5)説明

ビットを設定することで可能となる機能について説明しています。

【注】 上記した図中のビット名や文章は例であり、本マニュアルの内容とは関係がありません。

## 目次

| 1.  | 概要   |                  | 1-1  |

|-----|------|------------------|------|

| 1.1 |      | SH7265の特長        | 1-1  |

| 1.2 |      | 製品一覧             | 1-9  |

| 1.3 |      | プロック図            | 1-10 |

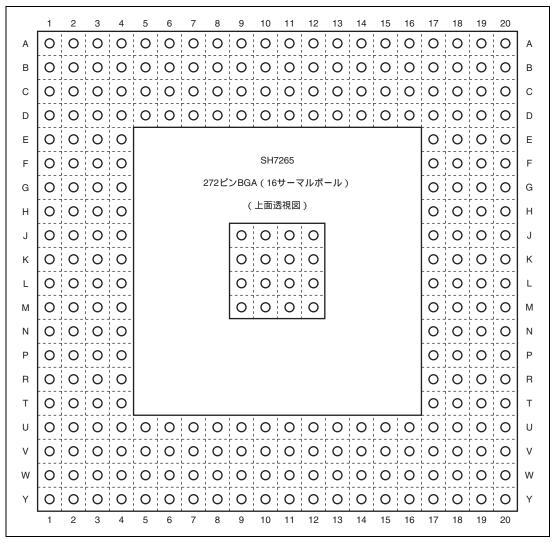

| 1.4 |      | ピン配置図            | 1-11 |

| 1.5 |      | 端子機能             | 1-36 |

| 1.6 |      | バス構成             | 1-43 |

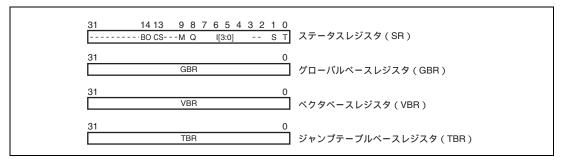

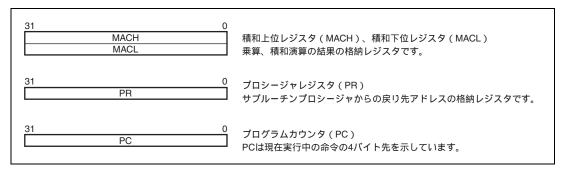

| 2.  | CPL  | J                | 2-1  |

| 2.1 |      | レジスタ構成           | 2-1  |

| 2.  | .1.1 | 汎用レジスタ           | 2-1  |

| 2.  | .1.2 | コントロールレジスタ       | 2-2  |

| 2.  | .1.3 | システムレジスタ         | 2-3  |

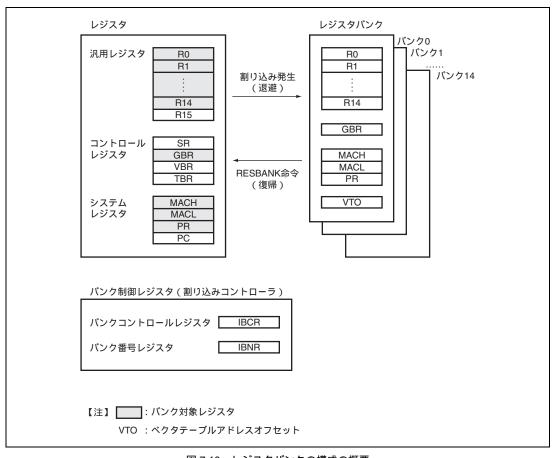

| 2.  | .1.4 | レジスタバンク          | 2-4  |

| 2.  | .1.5 | レジスタの初期値         | 2-4  |

| 2.2 |      | データ形式            | 2-5  |

| 2.  | .2.1 | レジスタのデータ形式       | 2-5  |

| 2.  | .2.2 | メモリのデータ形式        | 2-5  |

| 2.  | .2.3 | イミディエイトデータのデータ形式 | 2-6  |

| 2.3 |      | 命令の特長            | 2-7  |

| 2.  | .3.1 | RISC 方式          | 2-7  |

| 2.  | .3.2 | アドレッシングモード       | 2-11 |

| 2.  | .3.3 | 命令形式             | 2-15 |

| 2.4 |      | 命令セット            | 2-19 |

| 2.  | .4.1 | 分類順命令セット         | 2-19 |

| 2.  | .4.2 | データ転送命令          | 2-24 |

| 2.  | .4.3 | 算術演算命令           | 2-27 |

| 2.  | .4.4 | 論理演算命令           | 2-29 |

| 2.  | .4.5 | シフト命令            | 2-30 |

| 2   | 4.6  | 分岐命令             | 2-31 |

| 2.  | .4.7 | システム制御命令         | 2-32 |

| 2   | .4.8 | 浮動小数点演算命令        |      |

|     | 4.9  | FPU に関する CPU 命令  |      |

|     |      |                  |      |

| 2.5   | 処理状態                              | 2-38 |

|-------|-----------------------------------|------|

| 3. 浮動 | 動小数点ユニット(FPU)                     | 3-1  |

| 3.1   | 特長                                | 3-1  |

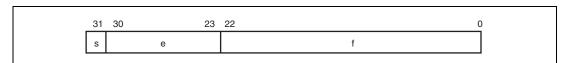

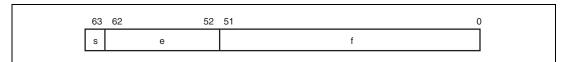

| 3.2   | データフォーマット                         |      |

| 3.2.1 | 浮動小数点フォーマット                       |      |

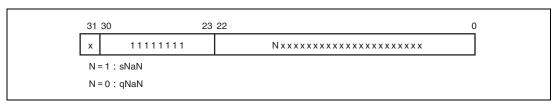

| 3.2.2 | 非数(NaN)                           | 3-4  |

| 3.2.3 | 非正規化数                             | 3-4  |

| 3.3   | レジスタの説明                           | 3-5  |

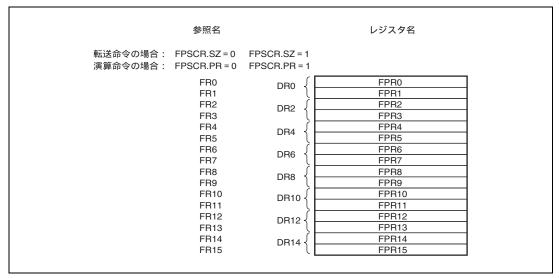

| 3.3.1 | 浮動小数点レジスタ                         | 3-5  |

| 3.3.2 | 浮動小数点ステータス / コントロールレジスタ ( FPSCR ) | 3-6  |

| 3.3.3 | 浮動小数点通信レジスタ(FPUL)                 | 3-7  |

| 3.4   | 丸め                                | 3-8  |

| 3.5   | FPU例外                             | 3-9  |

| 3.5.1 | FPU 例外要因                          | 3-9  |

| 3.5.2 | FPU 例外処理                          | 3-9  |

| 4. マノ | ルチコアプロセッサ                         | 4-1  |

| 4.1   | 特長                                | 4-1  |

| 4.2   | レジスタの説明                           | 4-2  |

| 4.2.1 | CPU ID レジスタ(CPUIDR)               | 4-4  |

| 4.2.2 | セマフォレジスタ 0 ~ 31 ( SEMR0 ~ 31 )    | 4-5  |

| 4.3   | 動作説明                              | 4-6  |

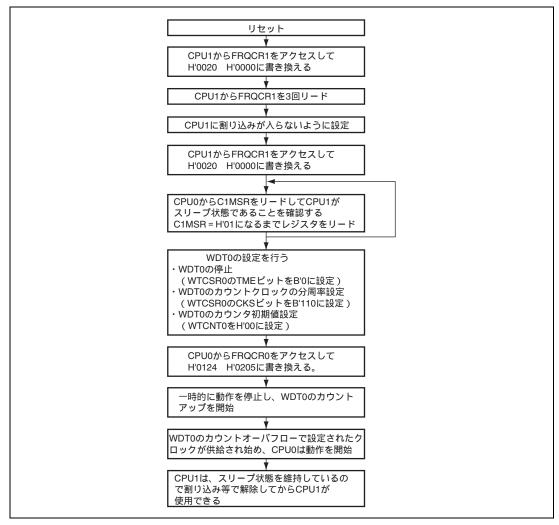

| 4.3.1 | 本 LSI の初期化手順                      | 4-6  |

| 4.3.2 | CPU 間の排他制御                        | 4-7  |

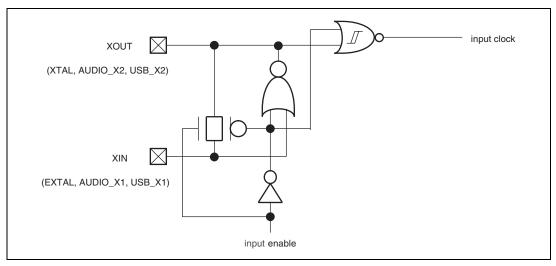

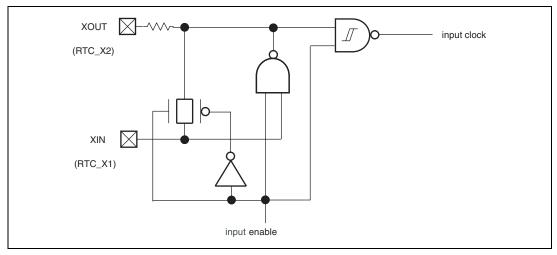

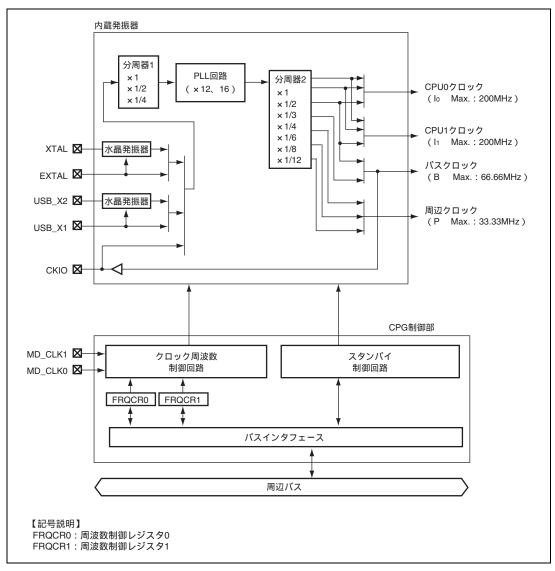

| 5. ク[ | コックパルス発振器(CPG)                    | 5-1  |

| 5.1   | 特長                                | 5-1  |

| 5.2   | 入出力端子                             | 5-4  |

| 5.3   | クロック動作モード                         | 5-5  |

| 5.4   | レジスタの説明                           | 5-10 |

| 5.4.1 | 周波数制御レジスタ 0、1 (FRQCR0、FRQCR1)     | 5-10 |

| 5.5   | 周波数变更方法                           | 5-14 |

| 5.5.1 | 逓倍率の変更                            | 5-14 |

| 5.5.2 | 分周率の変更                            | 5-16 |

| 5.5.3 | 逓倍率・分周率変更時の注意事項                   | 5-16 |

| 5.6   | クロック端子の使用方法                       | 5-17 |

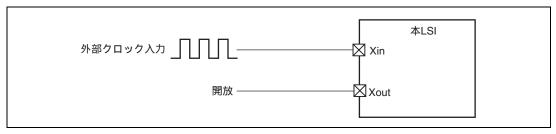

| 5.6.1 | 外部クロック入力時                         | 5-17 |

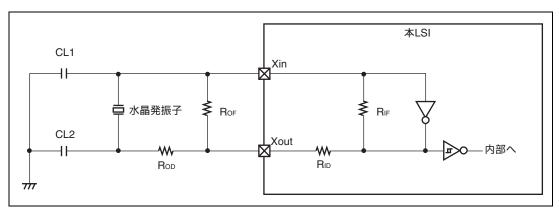

| 5.6.2 | 水晶発振子使用時                          | 5-18 |

| 5.6.3 | 未使用時                              | 5-18 |

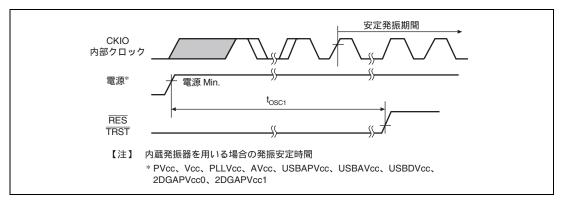

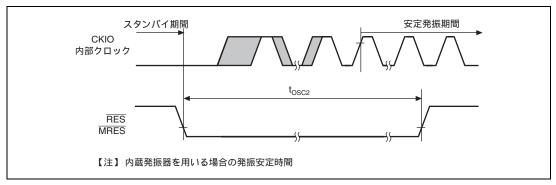

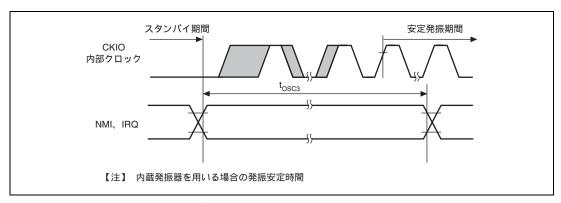

| 5.7    | 発振安定時間          | 5-19 |

|--------|-----------------|------|

| 5.7.1  | 内蔵水晶発振器の発振安定時間  | 5-19 |

| 5.7.2  | PLL 回路の発振安定時間   | 5-19 |

| 5.8    | ボード設計上の注意事項     | 5-20 |

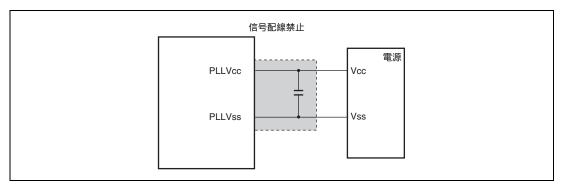

| 5.8.1  | PLL 発振回路使用時の注意  | 5-20 |

| 6. 例夕  | 卜処理             | 6-1  |

| 6.1    | 概要              | 6-1  |

| 6.1.1  | 例外処理の種類と優先順位    | 6-1  |

| 6.1.2  | 例外処理の動作         | 6-2  |

| 6.1.3  | 例外処理ベクタテーブル     | 6-4  |

| 6.2    | リセット            | 6-6  |

| 6.2.1  | 入出力端子           | 6-6  |

| 6.2.2  | リセットの種類         | 6-6  |

| 6.2.3  | パワーオンリセット       | 6-7  |

| 6.2.4  | マニュアルリセット       | 6-8  |

| 6.3    | アドレスエラー         | 6-9  |

| 6.3.1  | アドレスエラー発生要因     | 6-9  |

| 6.3.2  | アドレスエラー例外処理     | 6-10 |

| 6.4    | レジスタパンクエラー      | 6-11 |

| 6.4.1  | レジスタバンクエラー発生要因  |      |

| 6.4.2  | レジスタバンクエラー例外処理  | 6-11 |

| 6.5    | スリープエラー         | 6-12 |

| 6.5.1  | スリープエラー発生要因     | 6-12 |

| 6.5.2  | スリープエラー例外処理     | 6-12 |

| 6.6    | 割り込み            | 6-13 |

| 6.6.1  | 割り込み要因          | 6-13 |

| 6.6.2  | 割り込み優先順位        | 6-13 |

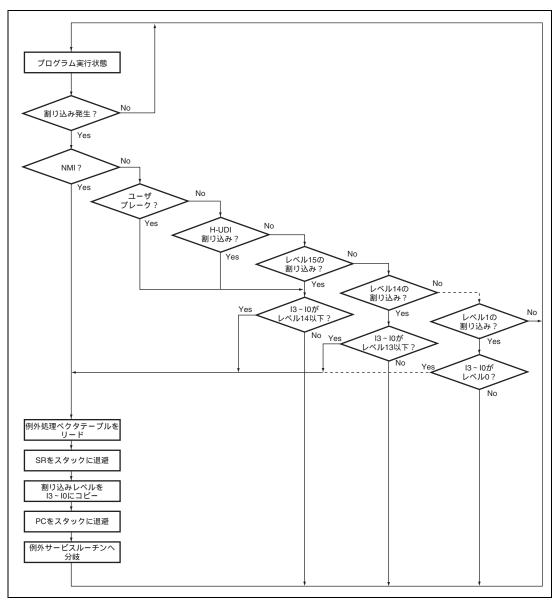

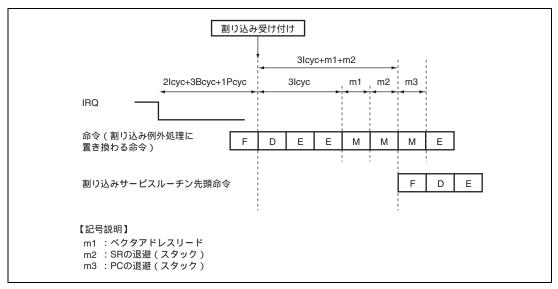

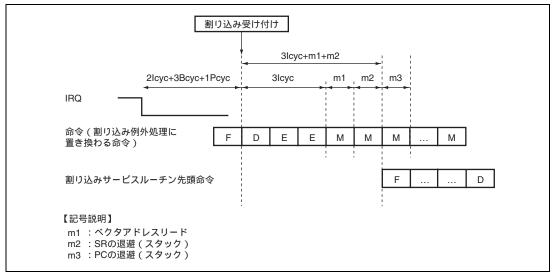

| 6.6.3  | 割り込み例外処理        | 6-14 |

| 6.7    | 命令による例外         | 6-15 |

| 6.7.1  | 命令による例外の種類      | 6-15 |

| 6.7.2  | トラップ命令          |      |

| 6.7.3  | スロット不当命令        |      |

| 6.7.4  | 一般不当命令          | 6-16 |

| 6.7.5  | 整数除算例外          |      |

| 6.7.6  | FPU 例外          |      |

| 6.8    | 例外処理が受け付けられない場合 |      |

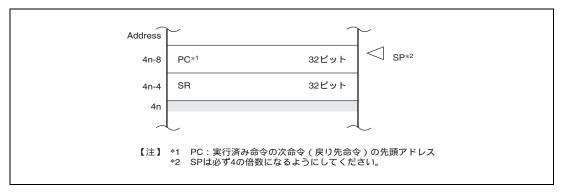

| 6.9    | 例外処理後のスタックの状態   |      |

| 6.10   | 使用上の注意事項        |      |

| 6.10.1 |                 |      |

|        |                 |      |

| 6.10.2 | ベクタベースレジスタ(VBR)の値                                                  | 6-20 |

|--------|--------------------------------------------------------------------|------|

| 6.10.3 | アドレスエラー例外処理のスタッキングで発生するアドレスエラー                                     | 6-20 |

| 6.10.4 | 割り込みマスクビット変更による割り込み制御                                              | 6-20 |

| 6.10.5 | 例外処理実行前の注意事項                                                       | 6-20 |

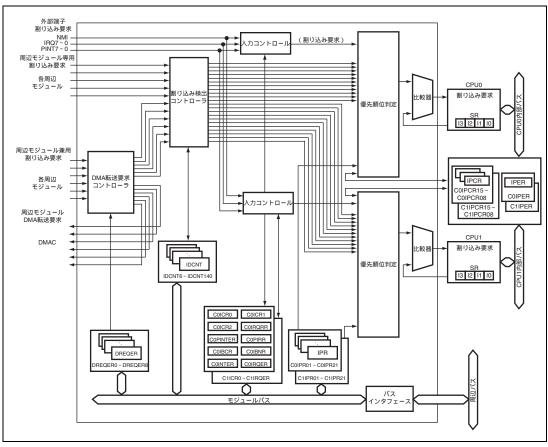

| 7. 割じ  | <br> 込みコントローラ(INTC)                                                | 7-1  |

| 7.1    | 特長                                                                 | 7-1  |

| 7.2    | 入出力端子                                                              | 7-3  |

| 7.3    | レジスタの説明                                                            | 7-3  |

| 7.3.1  | 割り込み優先レベル設定レジスタ 01、02、05~21<br>(COIPR01、02、05~21、C1IPR01、02、05~21) | 7-12 |

| 7.3.2  | 割り込みコントロールレジスタ 0 ( COICRO、C1ICRO )                                 | 7-13 |

| 7.3.3  | 割り込みコントロールレジスタ1(C0ICR1、C1ICR1)                                     | 7-14 |

| 7.3.4  | 割り込みコントロールレジスタ 2 ( COICR2、C1ICR2 )                                 | 7-15 |

| 7.3.5  | IRQ 割り込み要求レジスタ(C0IRQRR、C1IRQRR)                                    | 7-16 |

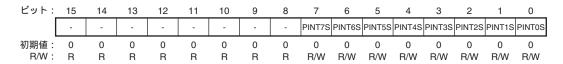

| 7.3.6  | PINT 割り込みイネーブルレジスタ ( COPINTER、C1PINTER )                           | 7-17 |

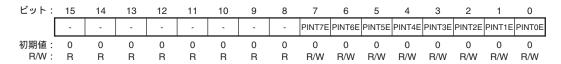

| 7.3.7  | PINT 割り込み要求レジスタ ( COPIRR、C1PIRR )                                  | 7-18 |

| 7.3.8  | バンクコントロールレジスタ ( COIBCR、C1IBCR )                                    | 7-19 |

| 7.3.9  | バンク番号レジスタ(COIBNR、C1IBNR)                                           | 7-20 |

| 7.3.10 | プロセッサ間割り込み制御レジスタ 15~08 ( COIPCR15~08、C1IPCR15~08 )                 | 7-21 |

| 7.3.11 | プロセッサ間割り込みイネーブルレジスタ(COIPER、C1IPER)                                 | 7-22 |

| 7.3.12 | 割り込みイネーブル制御レジスタ(COINTER、C1INTER)                                   | 7-23 |

| 7.3.13 | IRQ 割り込みイネーブル制御レジスタ ( COIRQER、C1IRQER )                            | 7-24 |

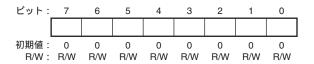

| 7.3.14 | 割り込み検出制御レジスタ(IDCNT6~140)                                           | 7-25 |

| 7.3.15 | DMA 転送要求イネーブルレジスタ 0~8 ( DREQER0~8 )                                | 7-28 |

| 7.4    | 割り込み要因                                                             | 7-31 |

| 7.4.1  | NMI 割り込み                                                           | 7-31 |

| 7.4.2  | ユーザブレーク割り込み                                                        | 7-31 |

| 7.4.3  | H-UDI 割り込み                                                         | 7-31 |

| 7.4.4  | IRQ 割り込み                                                           | 7-32 |

| 7.4.5  | PINT 割り込み                                                          | 7-32 |

| 7.4.6  | 内蔵周辺モジュール割り込み                                                      | 7-33 |

| 7.4.7  | プロセッサ間割り込み                                                         |      |

| 7.5    | 割り込み例外処理ベクタテーブルと優先順位                                               | 7-34 |

| 7.6    | 動作説明                                                               |      |

| 7.6.1  | 割り込み動作の流れ                                                          |      |

| 7.6.2  | 割り込み例外処理終了後のスタックの状態                                                |      |

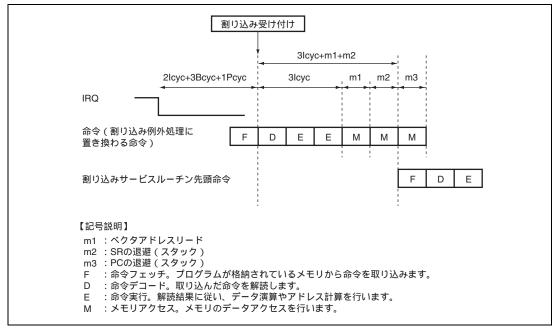

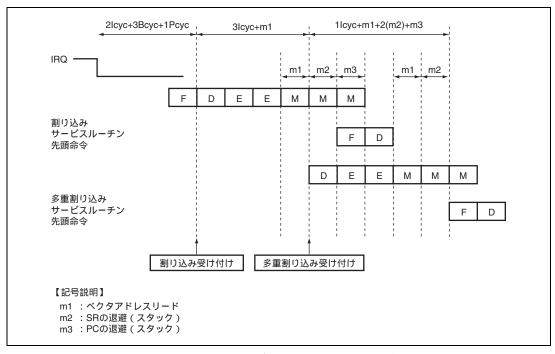

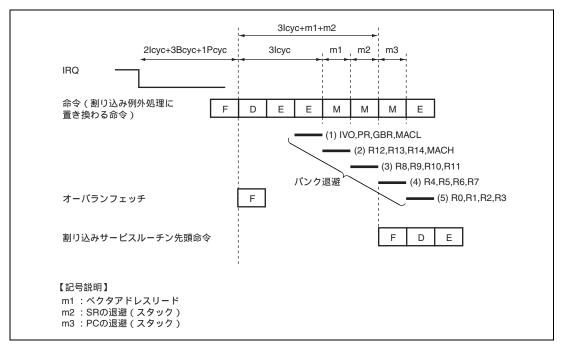

| 7.7    | 割り込み応答時間                                                           |      |

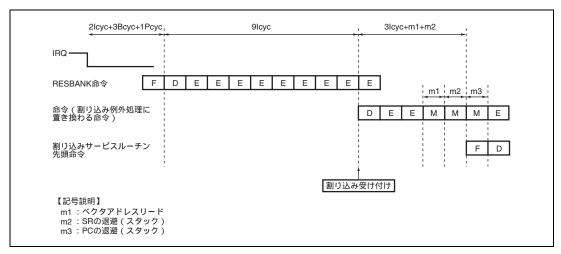

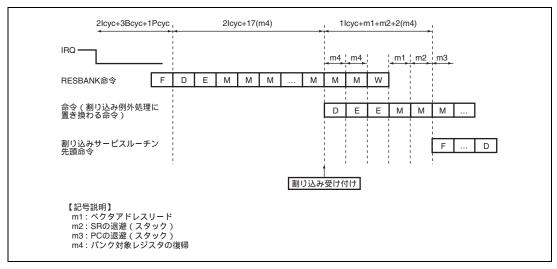

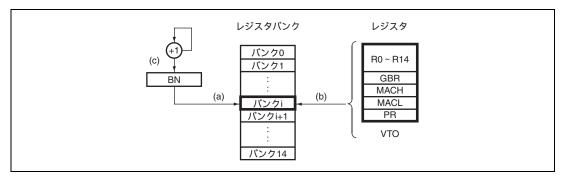

| 7.8    | レジスタバンク                                                            |      |

| 7.9    | レジスタバンクとバンク制御レジスタ                                                  |      |

| 7.9.1  | バンク退避、復帰の動作                                                        | 7-49 |

| 7   | 7.9.2  | すべてのバンクに退避が行われた状態での退避、復帰      | 7-51 |

|-----|--------|-------------------------------|------|

| 7   | 7.9.3  | レジスタバンクの例外                    | 7-51 |

| 7.1 | 10     | レジスタバンクエラー例外処理                | 7-52 |

| 7.1 | 11     | 割り込み要求信号によるデータ転送              | 7-52 |

| 7.1 | 12     | 使用上の注意事項                      | 7-52 |

| 7   | 7.12.1 | 割り込み要因クリアのタイミング               | 7-52 |

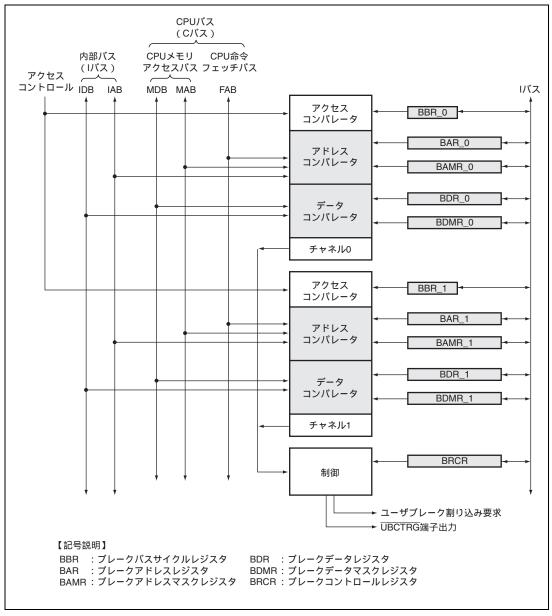

| 8.  | ュー     | -ザブレークコントローラ(UBC)             | 8-1  |

| 8.1 | 1      | 特長                            | 8-2  |

| 8.2 | 2      | 入出力端子                         | 8-4  |

| 8.3 | 3      | レジスタの説明                       | 8-4  |

| 8   | 3.3.1  | プレークアドレスレジスタ(BAR)             | 8-5  |

| 8   | 3.3.2  | プレークアドレスマスクレジスタ ( BAMR )      | 8-6  |

| 8   | 3.3.3  | プレークデータレジスタ(BDR)              | 8-7  |

| 8   | 3.3.4  | プレークデータマスクレジスタ ( BDMR )       | 8-8  |

| 8   | 3.3.5  | プレークバスサイクルレジスタ ( BBR )        | 8-9  |

| 8   | 3.3.6  | プレークコントロールレジスタ ( BRCR )       | 8-11 |

| 8.4 | 1      | 動作説明                          | 8-13 |

| 8   | 3.4.1  | ユーザブレーク動作の流れ                  | 8-13 |

| 8   | 3.4.2  | 命令フェッチサイクルでのプレーク              | 8-14 |

| 8   | 3.4.3  | データアクセスサイクルでのプレーク             | 8-15 |

| 8   | 3.4.4  | 退避されるプログラムカウンタの値              | 8-16 |

| 8   | 3.4.5  | 使用例                           | 8-16 |

| 8.5 | 5      | 使用上の注意事項                      | 8-19 |

| 9.  | ++     | <b>7</b> ツシュ                  | 9-1  |

| 9.1 | 1      | 特長                            | 9-1  |

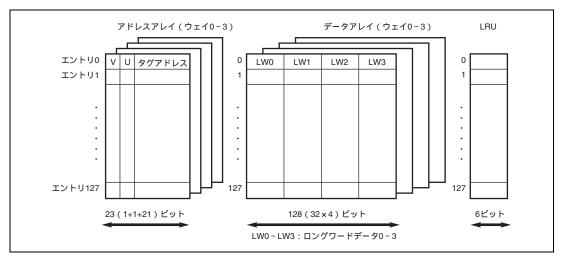

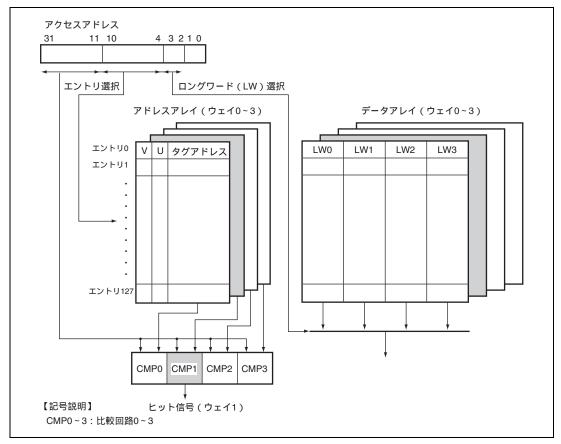

| 9   | 9.1.1  | キャッシュの構成                      | 9-1  |

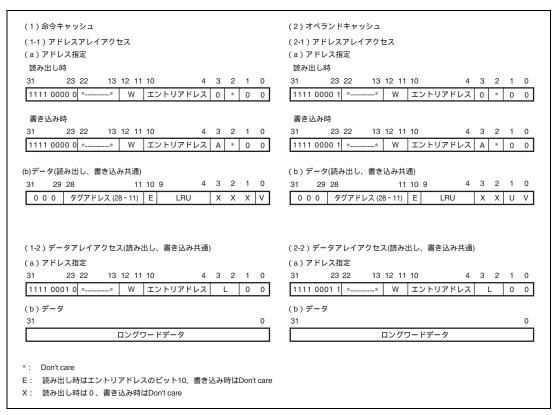

| 9.2 | 2      | レジスタの説明                       | 9-4  |

| 9   | 9.2.1  | キャッシュ制御レジスタ1(CCR1)            | 9-4  |

| 9   | 9.2.2  | キャッシュ制御レジスタ 2 ( CCR2 )        | 9-6  |

| 9.3 | 3      | 動作説明                          | 9-9  |

|     | 9.3.1  | キャッシュの検索                      |      |

| 9   | 9.3.2  | リード動作                         | 9-10 |

| 9   | 9.3.3  | プリフェッチ動作(オペランドキャッシュのみ )       | 9-10 |

| 9   | 9.3.4  | ライト動作(オペランドキャッシュのみ)           |      |

| 9   | 9.3.5  | -<br>ライトバックバッファ(オペランドキャッシュのみ) |      |

| 9   | 9.3.6  | キャッシュと外部メモリとのコヒーレンシ           |      |

| 9.4 | 4      | メモリ割り付けキャッシュの構成               | 9-13 |

| 9   | 9.4.1  | アドレスアレイ                       | 9-13 |

| 9.4.2  | データアレイ                                      | 9-14  |

|--------|---------------------------------------------|-------|

| 9.4.3  | 使用例                                         | 9-16  |

| 9.4.4  | 注意事項                                        | 9-16  |

|        |                                             |       |

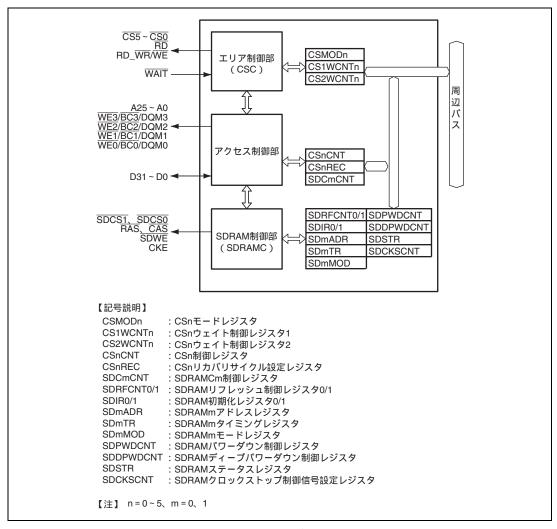

| 10. バフ | スステートコントローラ(BSC)                            | 10-1  |

| 10.1   | 特長                                          | 10-1  |

| 10.2   | 入出力端子                                       | 10-3  |

| 10.3   | エリアの概要                                      | 10-4  |

| 10.3.1 | アドレスマップ                                     | 10-4  |

| 10.3.2 | 各エリアのデータバス幅と関連端子設定                          | 10-6  |

| 10.4   | レジスタの説明                                     | 10-7  |

| 10.4.1 | CSn 制御レジスタ(CSnCNT)(n = 0 ~ 5)               | 10-9  |

| 10.4.2 | CSn リカバリサイクル設定レジスタ(CSnREC)(n = 0 ~ 5)       | 10-10 |

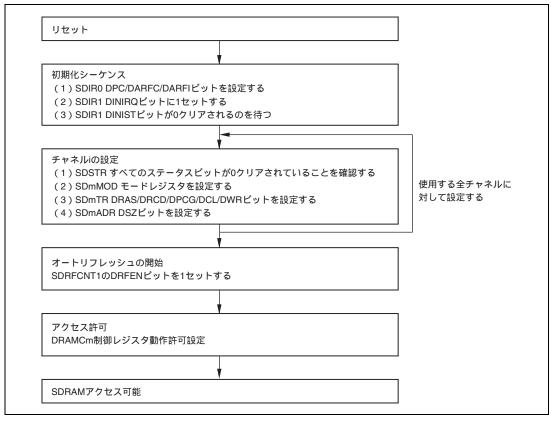

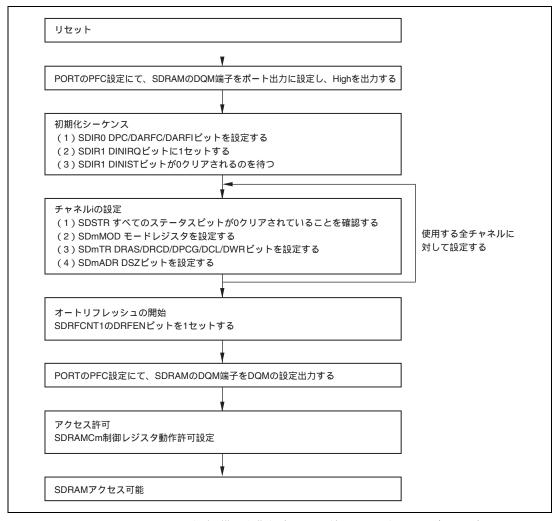

| 10.4.3 | SDRAMCm 制御レジスタ(SDCmCNT)(m=0、1)              | 10-12 |

| 10.4.4 | CSn モードレジスタ (CSMODn) (n=0~5)                | 10-13 |

| 10.4.5 | CSn ウェイト制御レジスタ 1 ( CS1WCNTn ) ( n = 0 ~ 5 ) | 10-15 |

| 10.4.6 | CSn ウェイト制御レジスタ 2 (CS2WCNTn) (n=0~5)         | 10-17 |

| 10.4.7 | SDRAM リフレッシュ制御レジスタ 0 ( SDRFCNT0 )           | 10-20 |

| 10.4.8 | SDRAM リフレッシュ制御レジスタ 1(SDRFCNT1)              | 10-21 |

| 10.4.9 | SDRAM 初期化レジスタ 0(SDIR0)                      | 10-23 |

| 10.4.1 | 0 SDRAM 初期化レジスタ 1(SDIR1)                    | 10-24 |

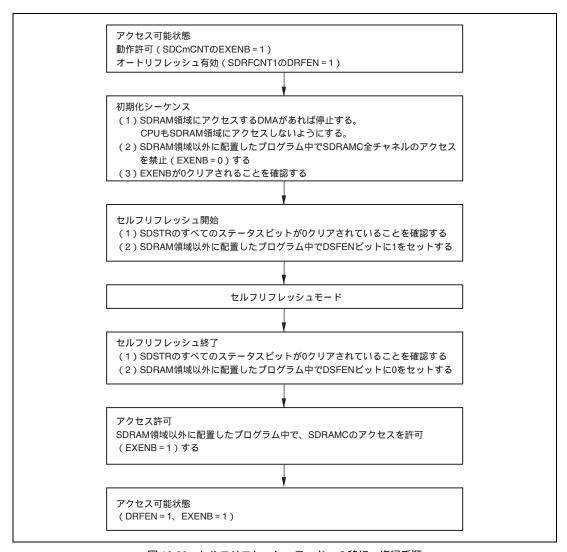

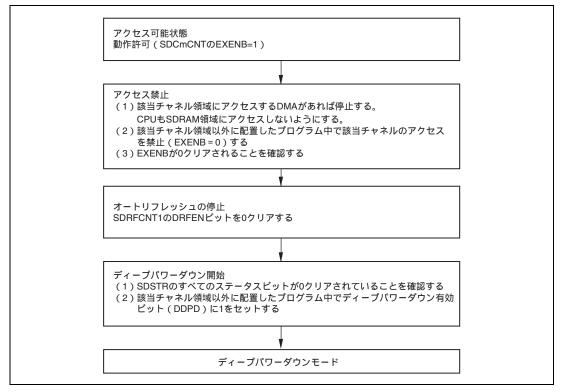

| 10.4.1 | 1 SDRAM パワーダウン制御レジスタ(SDPWDCNT)              | 10-25 |

| 10.4.1 | 2 SDRAM ディープパワーダウン制御レジスタ(SDDPWDCNT)         | 10-26 |

| 10.4.1 | 3 SDRAMm アドレスレジスタ (SDmADR) (m=0、1)          | 10-27 |

| 10.4.1 | 4 SDRAMm タイミングレジスタ (SDmTR) (m=0、1)          | 10-28 |

| 10.4.1 | 5 SDRAMm モードレジスタ (SDmMOD) (m=0、1)           | 10-30 |

| 10.4.1 | 6 SDRAM ステータスレジスタ(SDSTR)                    | 10-31 |

| 10.4.1 | 7 SDRAM クロックストップ制御信号設定レジスタ(SDCKSCNT)        | 10-33 |

| 10.5   | 動作説明                                        | 10-34 |

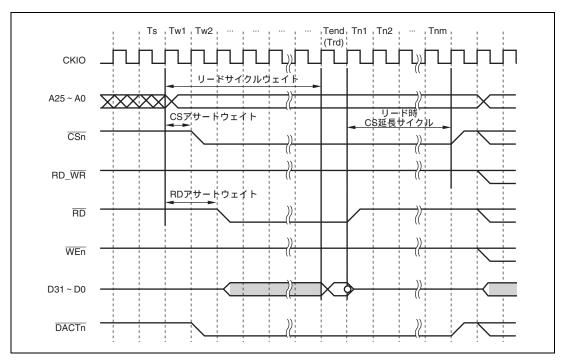

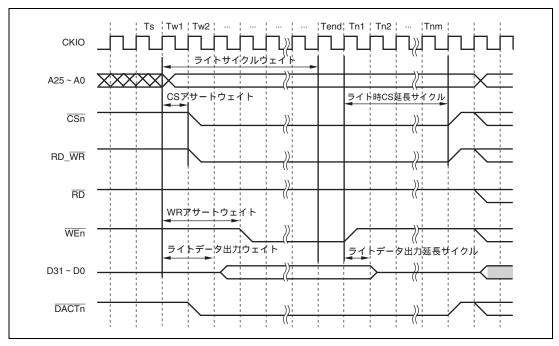

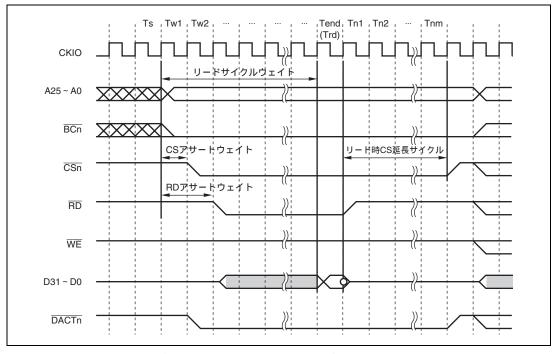

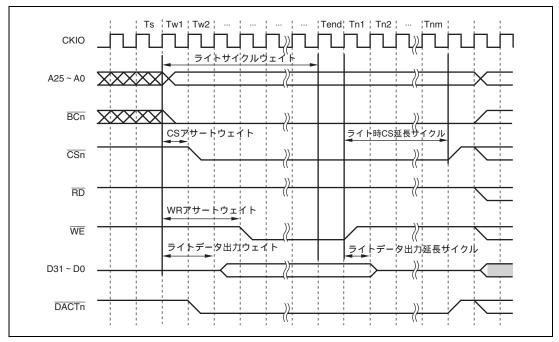

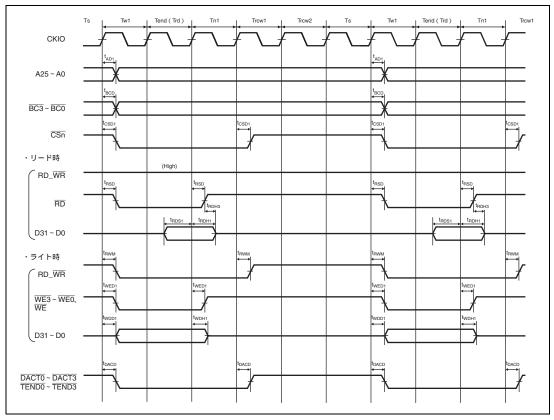

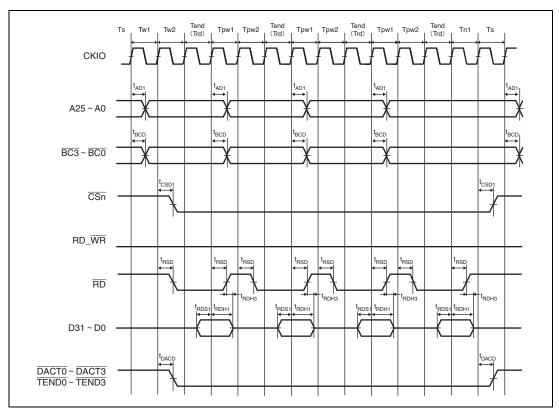

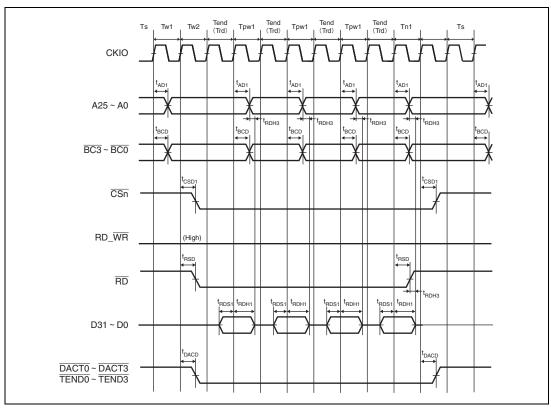

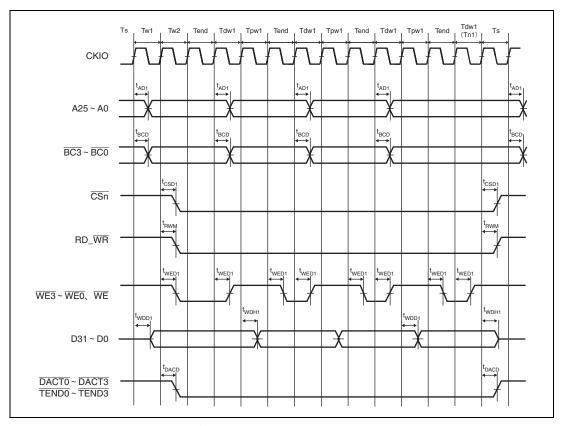

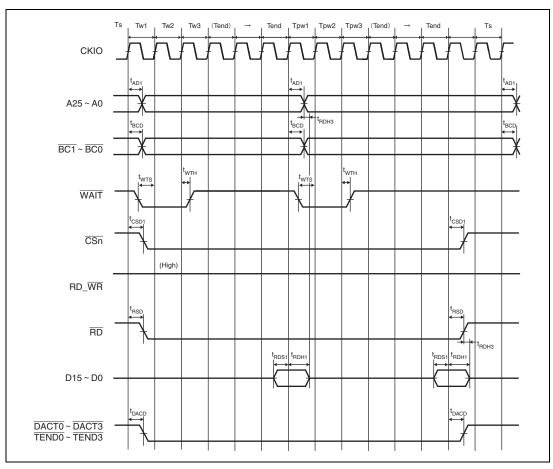

| 10.5.1 | CS 空間アクセス                                   | 10-34 |

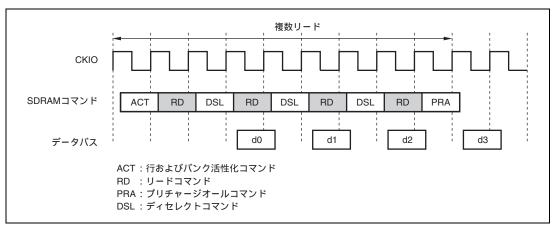

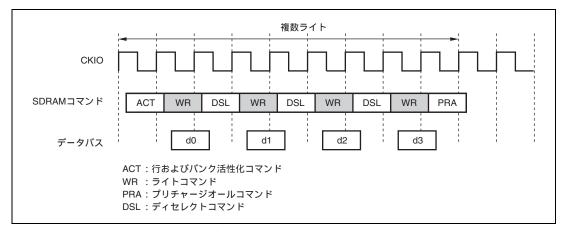

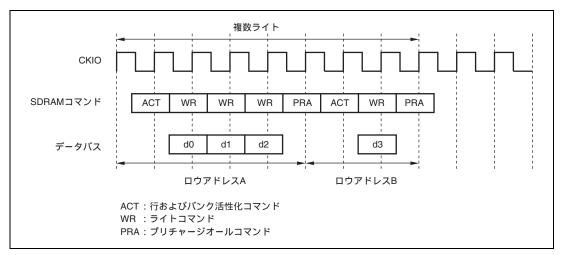

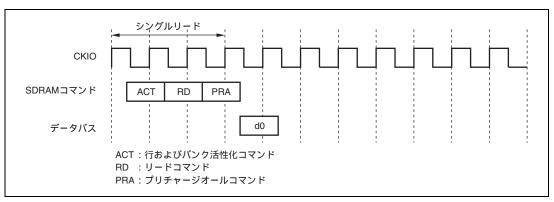

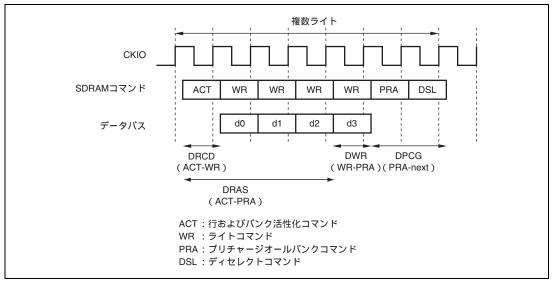

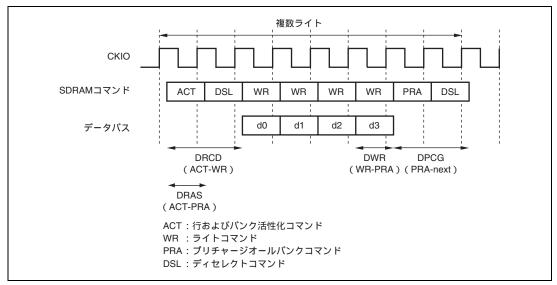

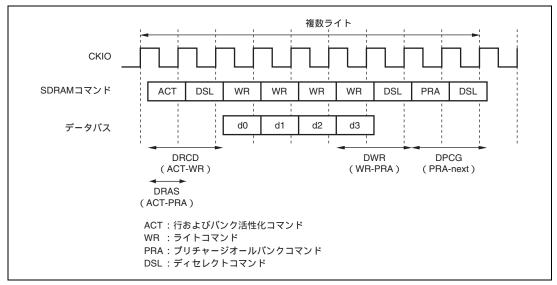

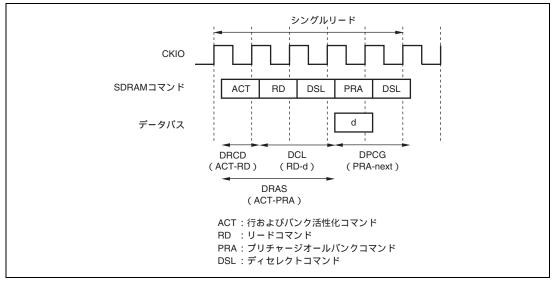

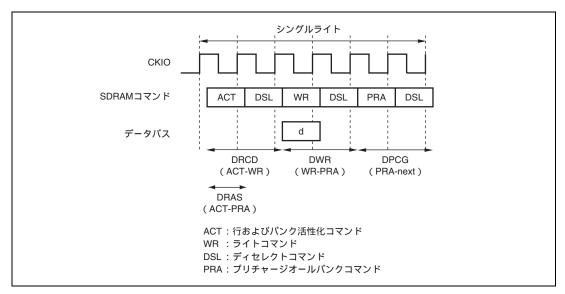

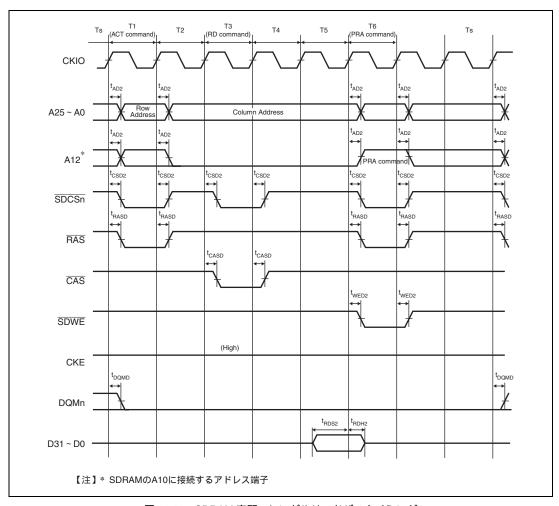

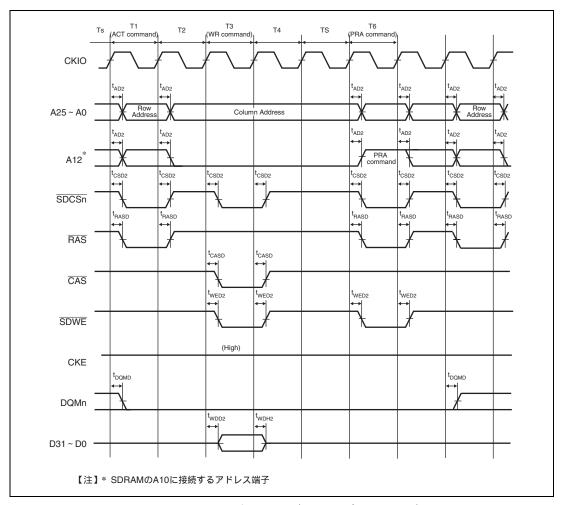

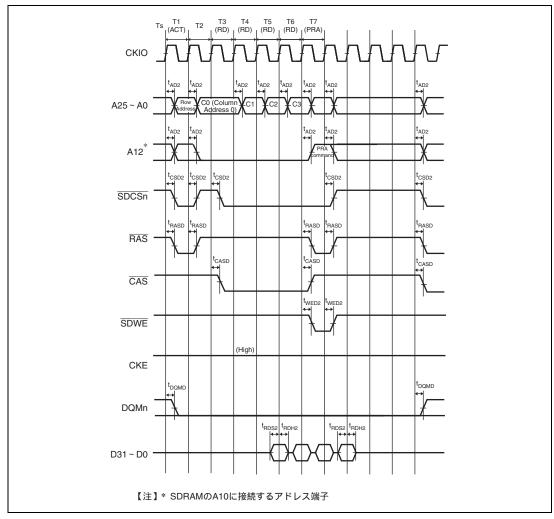

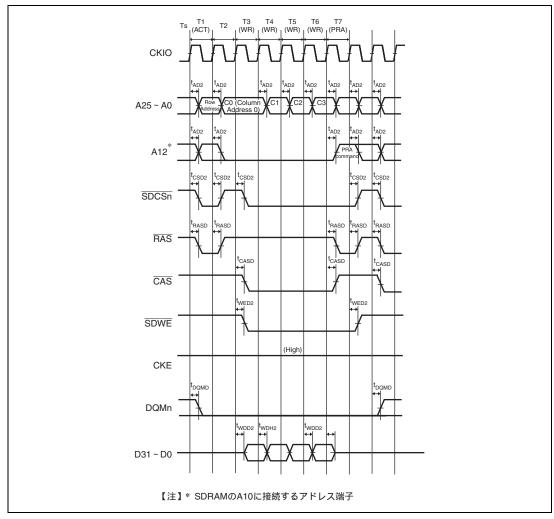

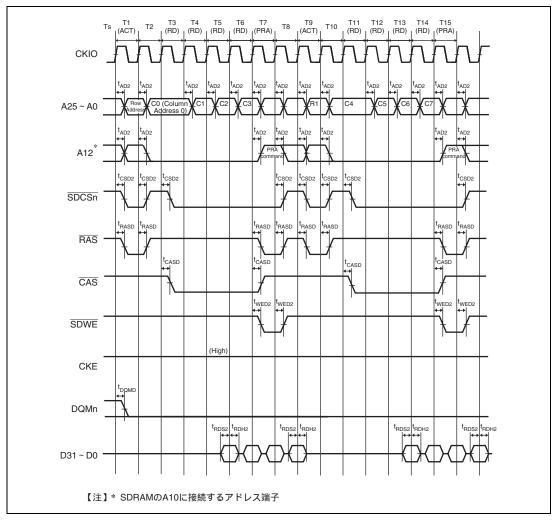

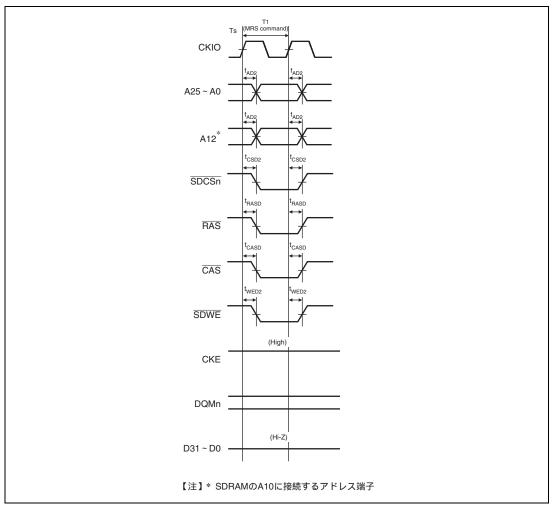

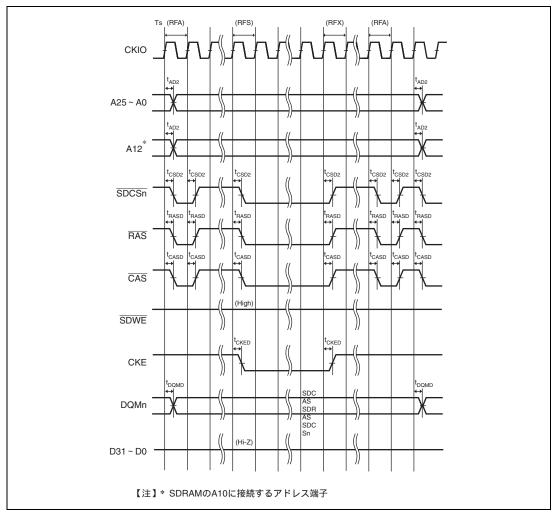

| 10.5.2 | SDRAM アクセス                                  | 10-46 |

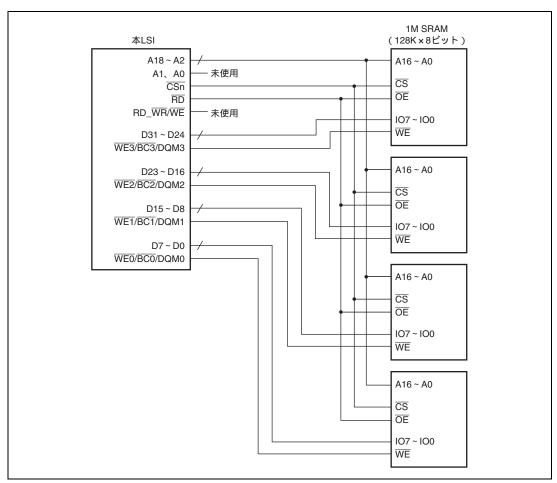

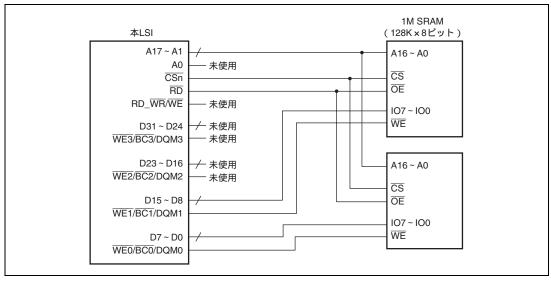

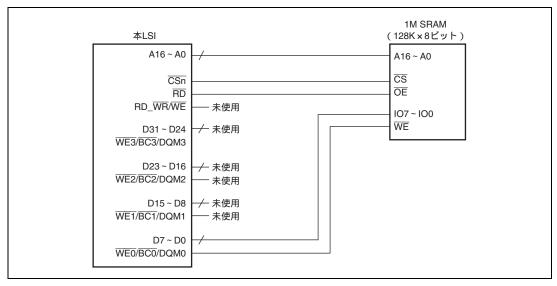

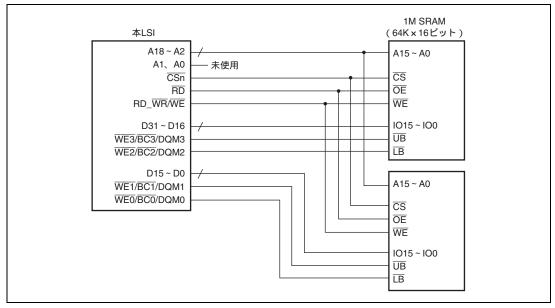

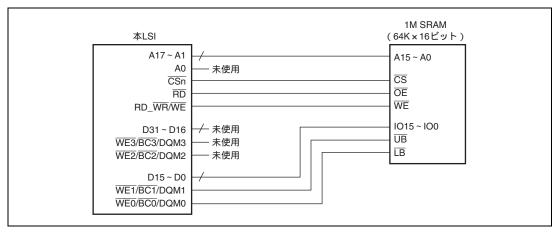

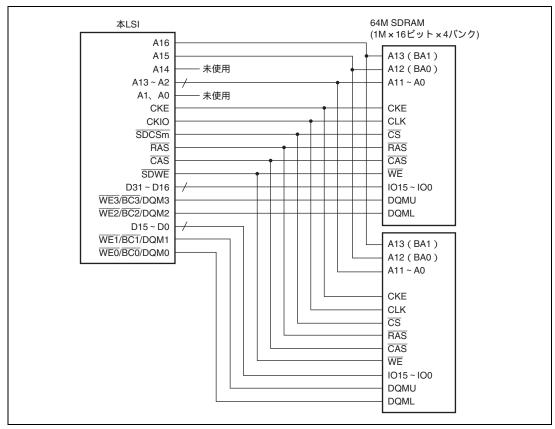

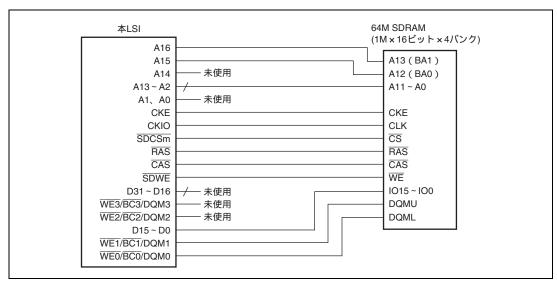

| 10.6   | 接続例                                         | 10-79 |

| 10.7   | 使用上の注意事項                                    | 10-83 |

| 10.7.1 | ライトバッファ                                     | 10-83 |

| 10.7.2 | ソフトウェアスタンバイモードまたはディープスタンバイモード遷移時の注意事項       | 10-83 |

|        | (1 EL 1-11-EL> L (D.110)                    |       |

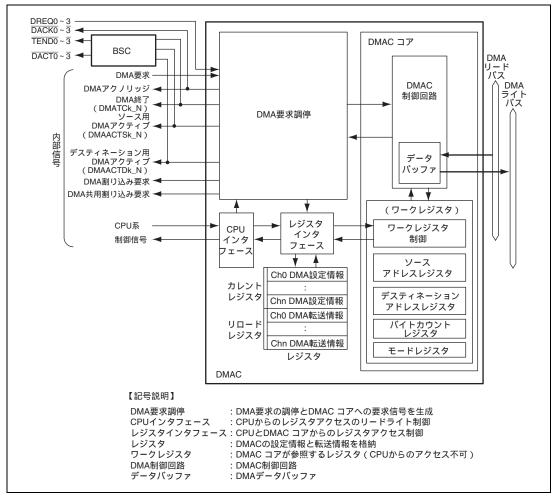

| 11. ダイ | イレクトメモリアクセスコントローラ(DMAC)                     |       |

| 11.1   | 特長                                          |       |

| 11.2   | 入出力端子                                       | 11-4  |

| 11.3   | レジスタの説明                                     | 11-5  |

| 11.3.1  | DMA カレントソースアドレスレジスタ(DMCSADRn)               | 11-14 |

|---------|---------------------------------------------|-------|

| 11.3.2  | DMA カレントデスティネーションアドレスレジスタ(DMCDADRn)         | 11-15 |

| 11.3.3  | DMA カレントバイトカウントレジスタ(DMCBCTn)                | 11-16 |

| 11.3.4  | DMA リロードソースアドレスレジスタ(DMRSADRn)               | 11-17 |

| 11.3.5  | DMA リロードデスティネーションアドレスレジスタ ( DMRDADRn )      | 11-18 |

| 11.3.6  | DMA リロードバイトカウントレジスタ(DMRBCTn)                | 11-19 |

| 11.3.7  | DMA モードレジスタ ( DMMODn )                      | 11-20 |

| 11.3.8  | DMA 制御レジスタ A(DMCNTAn)                       | 11-28 |

| 11.3.9  | DMA 制御レジスタ B ( DMCNTBn )                    | 11-33 |

| 11.3.10 | DMA 起動制御レジスタ(DMSCNT)                        | 11-36 |

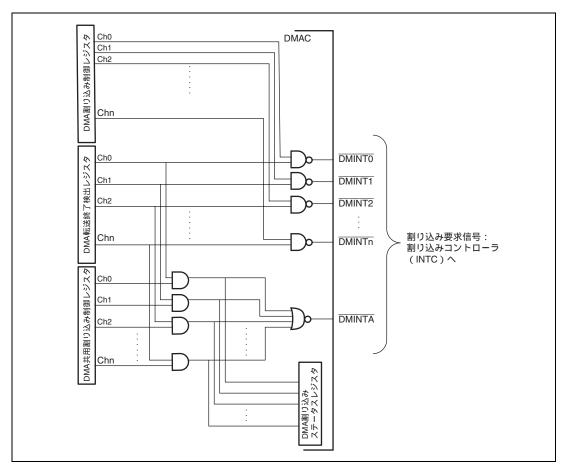

| 11.3.11 | DMA 割り込み制御レジスタ(DMICNT)                      | 11-37 |

| 11.3.12 | DMA 共用割り込み制御レジスタ(DMICNTA)                   | 11-38 |

| 11.3.13 | DMA 割り込みステータスレジスタ(DMISTS)                   | 11-39 |

| 11.3.14 | DMA 転送終了検出レジスタ(DMEDET)                      | 11-40 |

| 11.3.15 | DMA アービトレーションステータスレジスタ ( DMASTS )           | 11-41 |

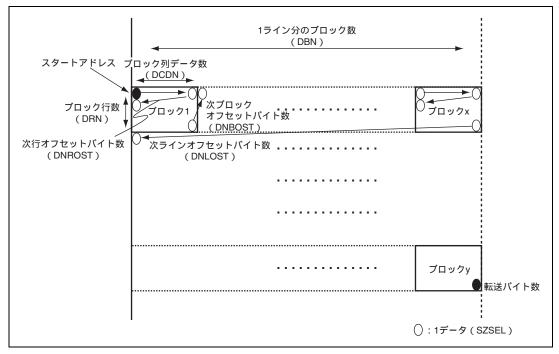

| 11.3.16 | DMA2 次元列設定レジスタ ( DM2DCLMm )                 | 11-42 |

| 11.3.17 | DMA2 次元行設定レジスタ ( DM2DROWm )                 | 11-44 |

| 11.3.18 | DMA2 次元ブロック設定レジスタ(DM2DBLKm)                 | 11-45 |

| 11.3.19 | DMA2 次元次行オフセットレジスタ ( DM2DNROSTm )           |       |

| 11.3.20 | DMA2 次元次ブロックオフセットレジスタ(DM2DNBOSTm )          | 11-47 |

| 11.3.21 | DMA2 次元次ラインオフセットレジスタ ( DM2DNLOSTm )         |       |

| 11.3.22 | DMA リロード 2 次元列設定レジスタ ( DMR2DCLMm )          | 11-49 |

| 11.3.23 | DMA リロード 2 次元行設定レジスタ ( DMR2DROWm )          | 11-50 |

| 11.3.24 | DMA リロード 2 次元プロック設定レジスタ ( DMR2DBLKm )       |       |

| 11.3.25 | DMA リロード 2 次元次行オフセットレジスタ ( DMR2DNROSTm )    | 11-52 |

| 11.3.26 | DMA リロード 2 次元次ブロックオフセットレジスタ ( DMR2DNBOSTm ) |       |

| 11.3.27 | DMA リロード 2 次元次ラインオフセットレジスタ ( DMR2DNLOSTm )  | 11-54 |

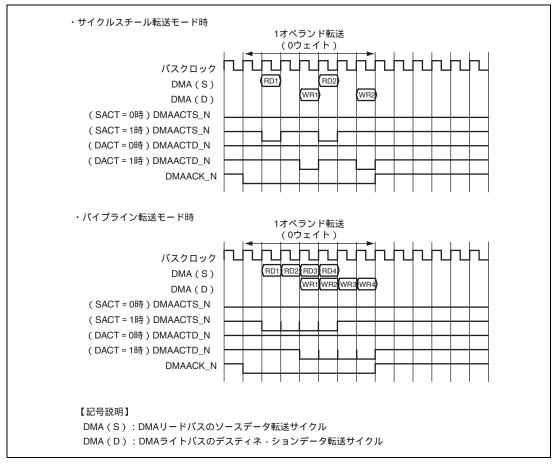

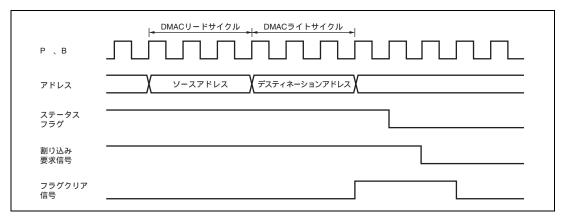

| 11.4 動  | 作説明作                                        | 11-55 |

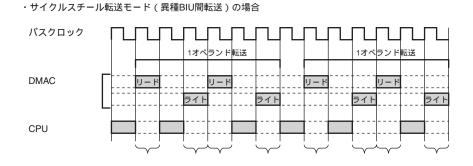

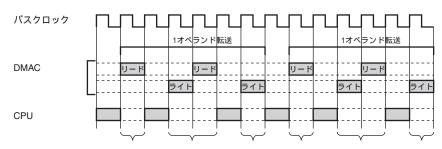

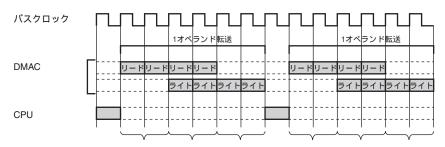

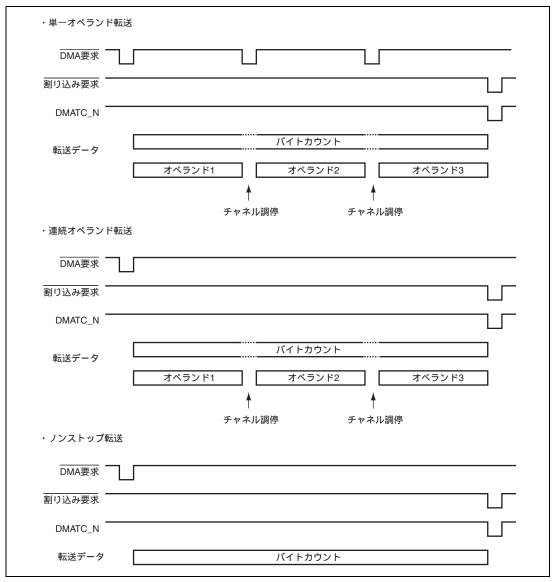

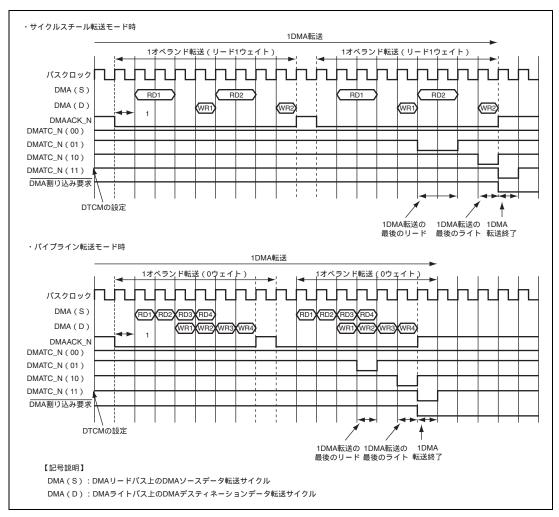

| 11.4.1  | DMA 転送モード                                   | 11-55 |

| 11.4.2  | DMA 転送条件                                    |       |

| 11.4.3  | DMA の起動                                     |       |

| 11.5 DI | MAの終了と割り込み                                  |       |

| 11.5.1  | DMA 転送の終了                                   |       |

| 11.5.2  | DMA 割り込み要求                                  |       |

| 11.5.3  | DMA 終了信号の出力                                 |       |

|         | MA転送の一時停止と再開、中止                             |       |

| 11.6.1  | DMA 転送の一時停止と再開                              |       |

| 11.6.2  | 各チャネルの DMA 転送の中止                            |       |

|         | MA要求                                        |       |

| 11.7.1  | DMA 要求要因                                    |       |

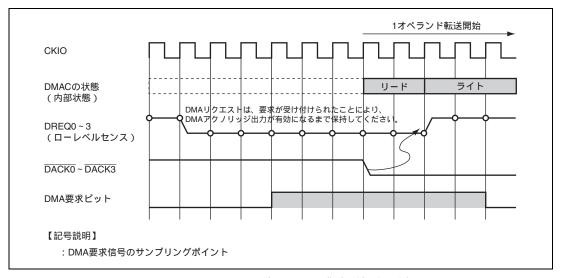

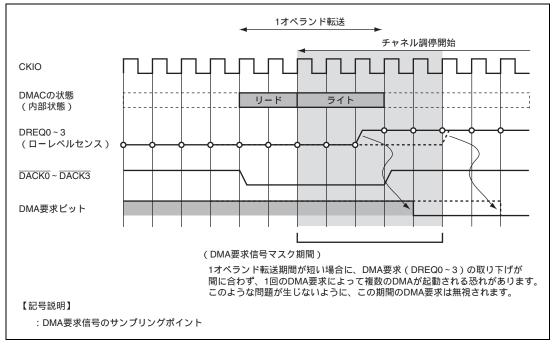

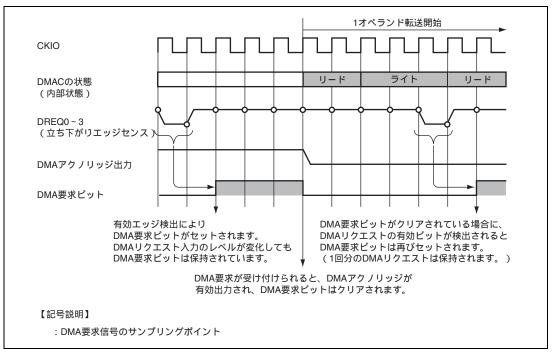

| 11.7.2  | DMA 要求信号入力の同期回路                             | 11-70 |

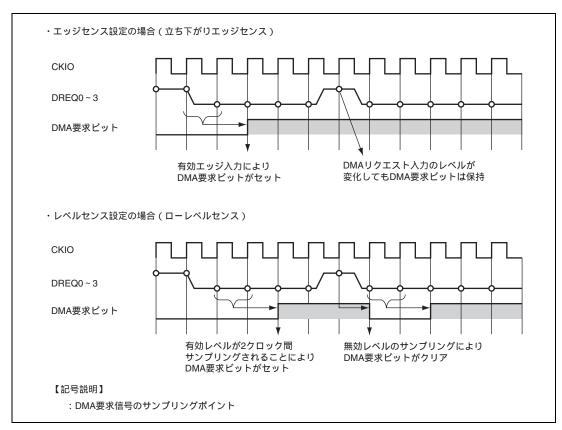

| 11.7.3  | DMA 要求のセンスモード                              | 11-71 |

|---------|--------------------------------------------|-------|

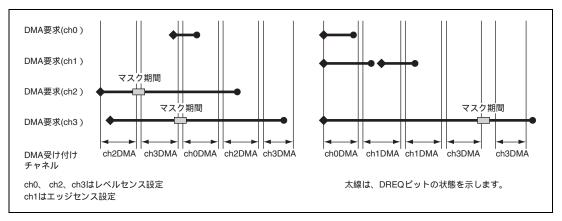

| 11.8    | DMAチャネルの優先順位判断                             | 11-74 |

| 11.8.1  | チャネル優先順位                                   | 11-74 |

| 11.8.2  | 多重 DMA 要求時の動作                              | 11-74 |

| 11.9    | DMAアクノリッジ信号出力とDMAアクティブ信号出力                 | 11-76 |

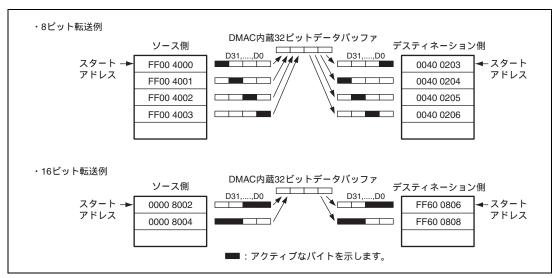

| 11.10   | 転送単位と転送バイト位置                               | 11-79 |

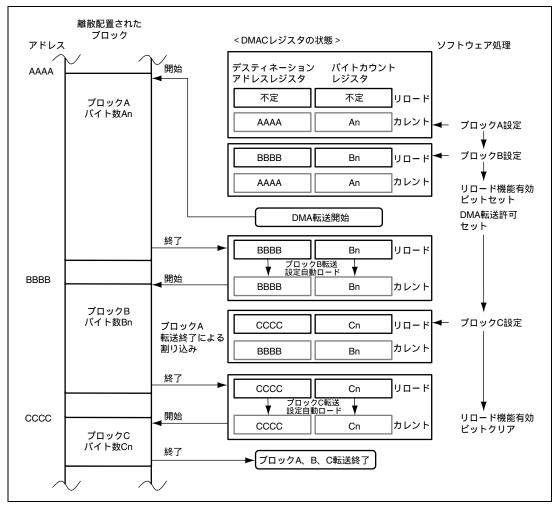

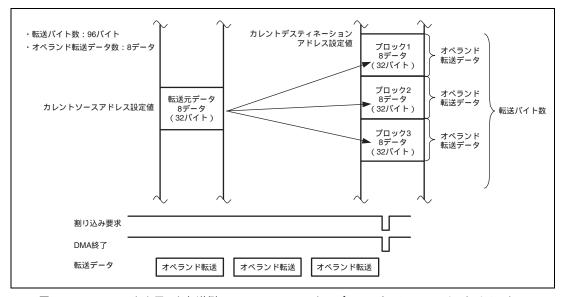

| 11.11   | リロード機能                                     | 11-80 |

| 11.12   | ローテート機能                                    | 11-82 |

| 11.13   | 使用上の注意事項                                   | 11-83 |

| 11.13.  | 1 ソフトウェアスタンバイモードまたはディープスタンバイモード遷移時の注意事項    | 11-83 |

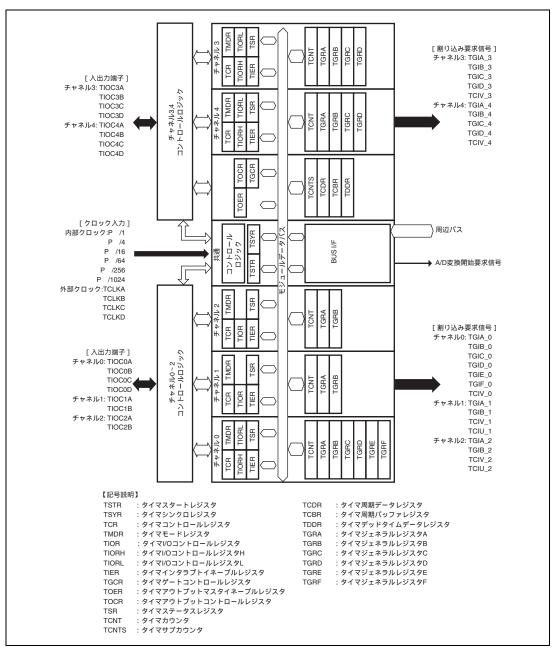

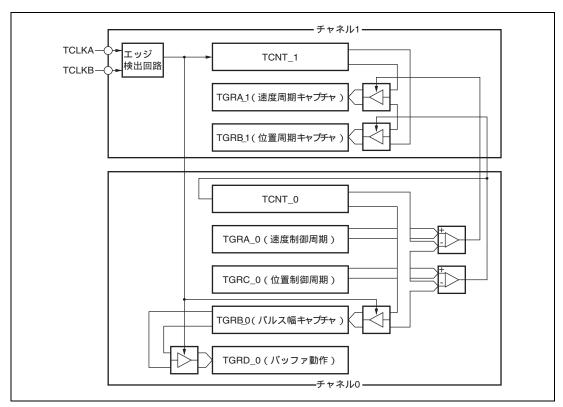

| 12. マル  | ・チファンクションタイマパルスユニット 2(MTU2)                | 12-1  |

| 12.1    | 特長                                         | 12-1  |

| 12.2    | 入出力端子                                      | 12-6  |

| 12.3    | レジスタの説明                                    | 12-7  |

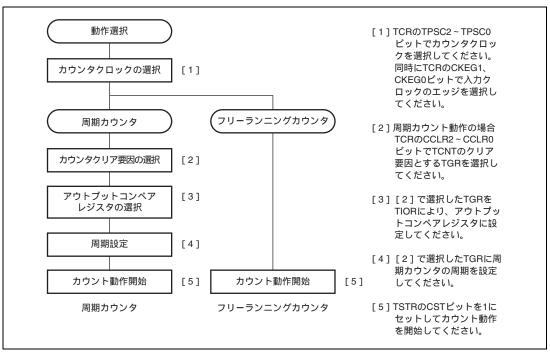

| 12.3.1  | タイマコントロールレジスタ(TCR)                         | 12-10 |

| 12.3.2  | タイマモードレジスタ(TMDR)                           | 12-13 |

| 12.3.3  | タイマ I/O コントロールレジスタ(TIOR)                   | 12-15 |

| 12.3.4  | タイマインタラプトイネーブルレジスタ(TIER)                   | 12-33 |

| 12.3.5  | タイマステータスレジスタ ( TSR )                       | 12-36 |

| 12.3.6  | タイマバッファ動作転送モードレジスタ(TBTM)                   | 12-40 |

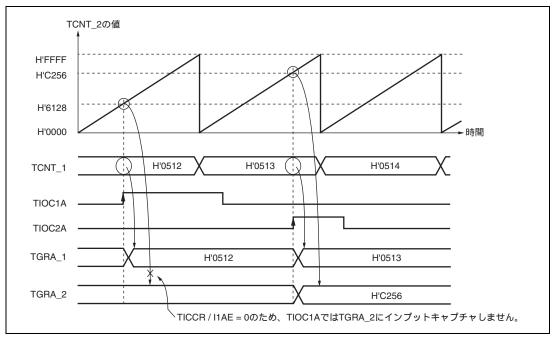

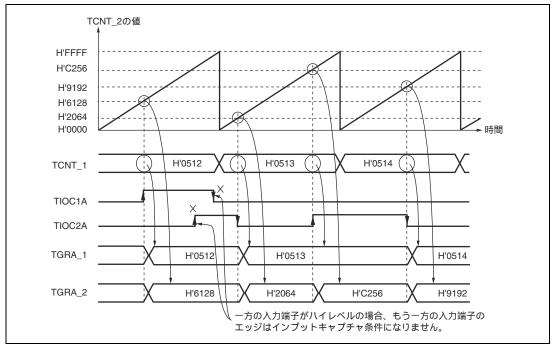

| 12.3.7  | タイマインプットキャプチャコントロールレジスタ(TICCR)             | 12-41 |

| 12.3.8  | タイマ A/D 変換開始要求コントロールレジスタ(TADCR )           | 12-42 |

| 12.3.9  | タイマ A/D 変換開始要求周期設定レジスタ(TADCORA/B_4)        | 12-44 |

| 12.3.10 | ) タイマ A/D 変換開始要求周期設定バッファレジスタ(TADCOBRA/B_4) | 12-44 |

| 12.3.1  | 1 タイマカウンタ(TCNT)                            | 12-45 |

| 12.3.1  | 2 タイマジェネラルレジスタ ( TGR )                     | 12-45 |

| 12.3.13 | 3 タイマスタートレジスタ ( TSTR )                     | 12-46 |

| 12.3.14 | 4 タイマシンクロレジスタ(TSYR)                        | 12-47 |

| 12.3.1  | 5 タイマリードライトイネーブルレジスタ(TRWER)                | 12-48 |

| 12.3.10 | 5 タイマアウトプットマスタイネーブルレジスタ ( TOER )           | 12-49 |

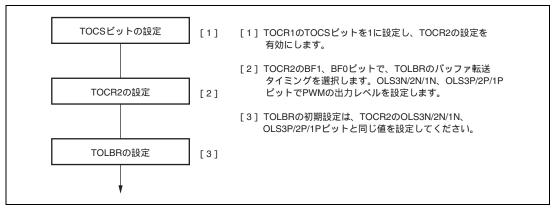

| 12.3.1  | 7 タイマアウトプットコントロールレジスタ 1(TOCR1)             | 12-50 |

| 12.3.1  | 8 タイマアウトプットコントロールレジスタ 2 ( TOCR2 )          | 12-52 |

| 12.3.19 | 9 タイマアウトプットレベルバッファレジスタ(TOLBR)              | 12-55 |

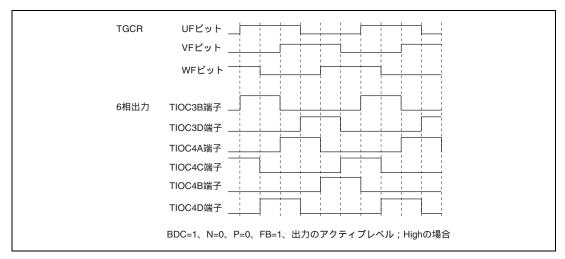

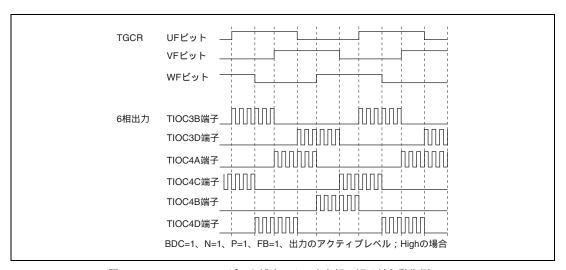

| 12.3.20 | ) タイマゲートコントロールレジスタ(TGCR)                   | 12-56 |

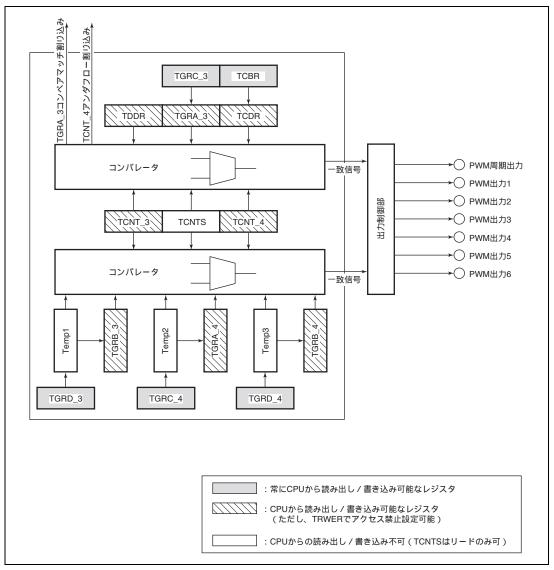

| 12.3.2  | 1 タイマサブカウンタ(TCNTS)                         | 12-57 |

| 12.3.2  | 2 タイマデッドタイムデータレジスタ(TDDR)                   | 12-57 |

| 12.3.2  | 3 タイマ周期データレジスタ(TCDR)                       | 12-58 |

| 12.3.2  | 4 タイマ周期バッファレジスタ(TCBR)                      | 12-58 |

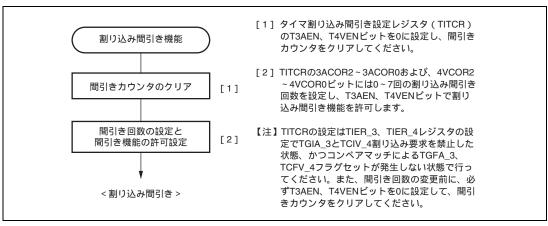

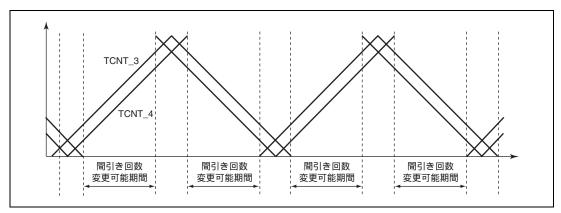

| 12.3.2  | 5 タイマ割り込み間引き設定レジスタ(TITCR)                  | 12-59 |

| 12.3.26 | 5 タイマ割り込み間引き回数カウンタ(TITCNT)                    | 12-60  |

|---------|-----------------------------------------------|--------|

| 12.3.27 | タイマバッファ転送設定レジスタ(TBTER)                        | 12-61  |

| 12.3.28 | タイマデッドタイムイネーブルレジスタ(TDER)                      | 12-62  |

| 12.3.29 | ) タイマ波形コントロールレジスタ(TWCR)                       | 12-63  |

| 12.3.30 | ) バスマスタとのインタフェース                              | 12-64  |

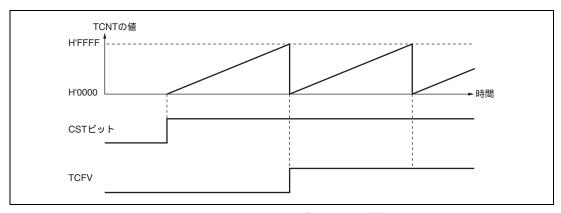

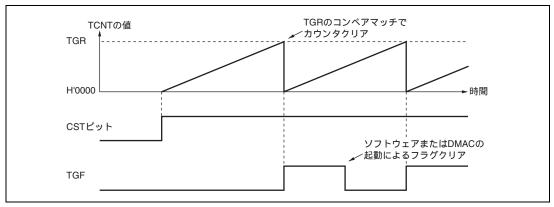

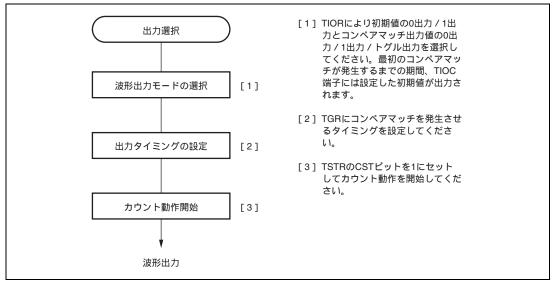

| 12.4    | 動作説明                                          | 12-65  |

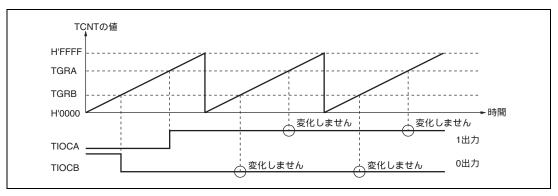

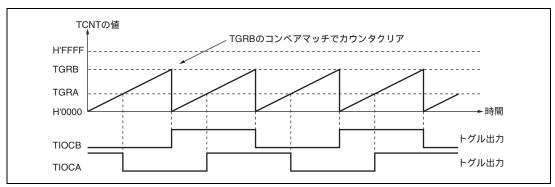

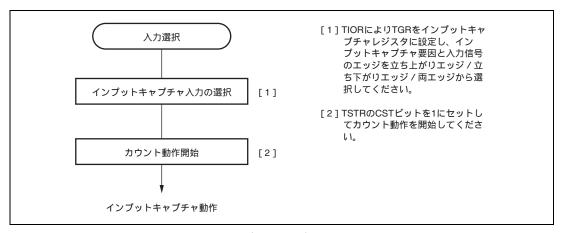

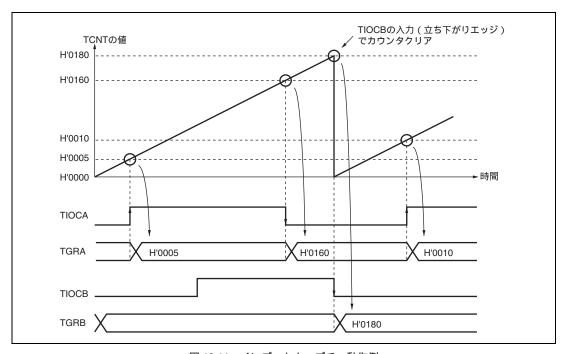

| 12.4.1  | 基本動作                                          | 12-65  |

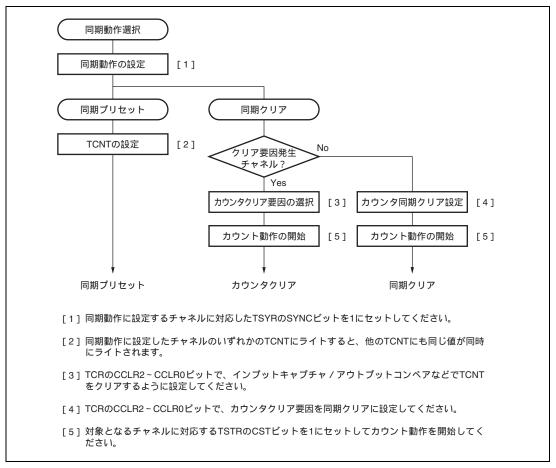

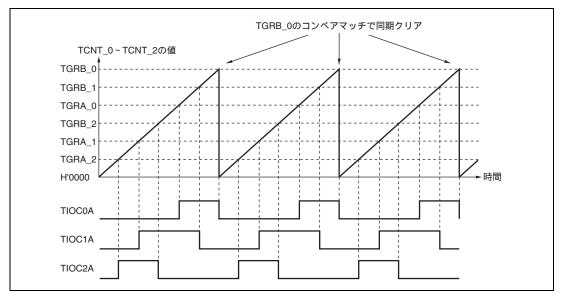

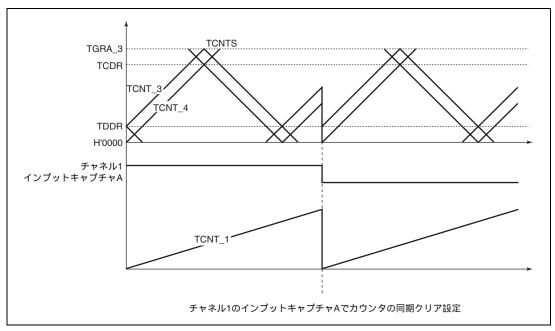

| 12.4.2  | 同期動作                                          | 12-71  |

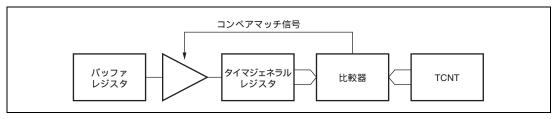

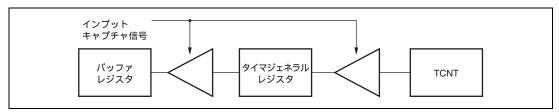

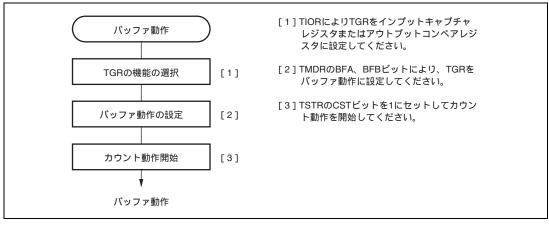

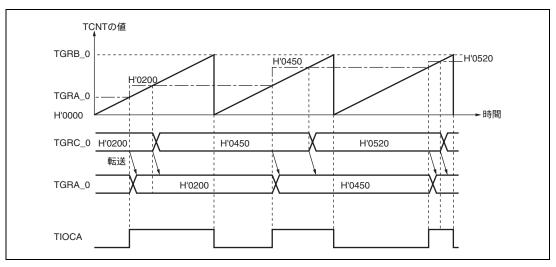

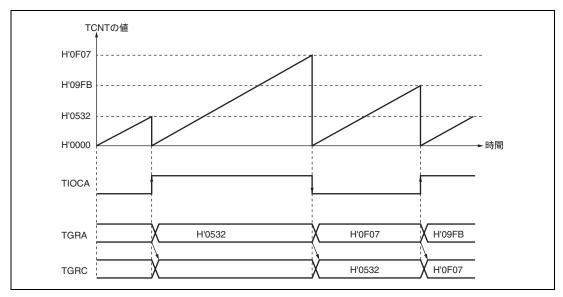

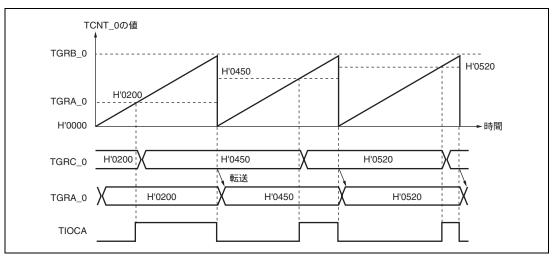

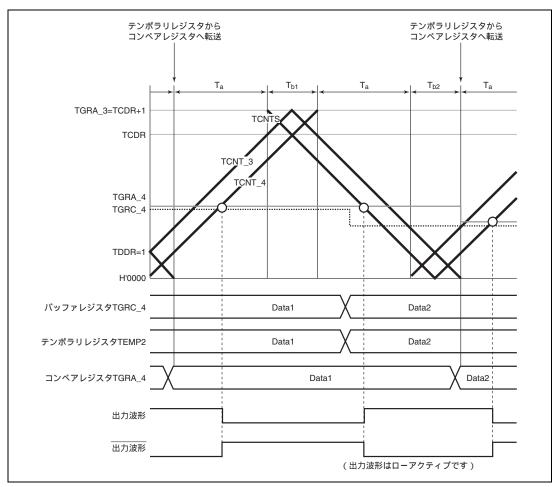

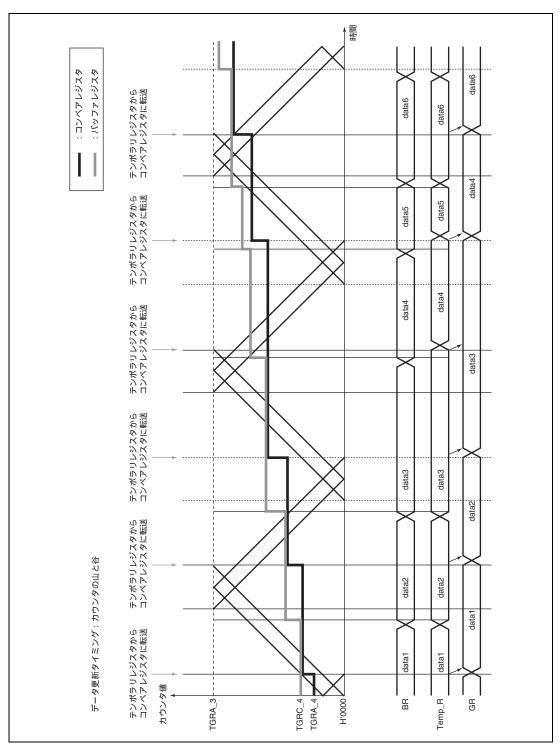

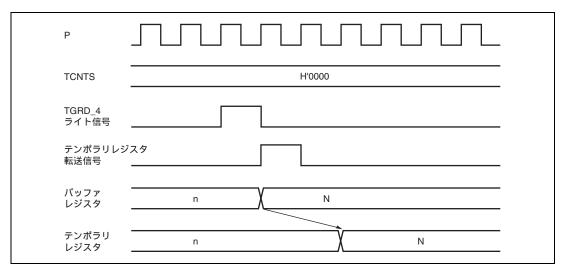

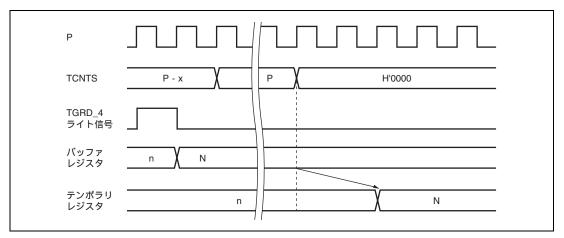

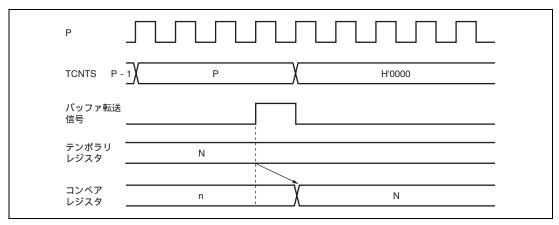

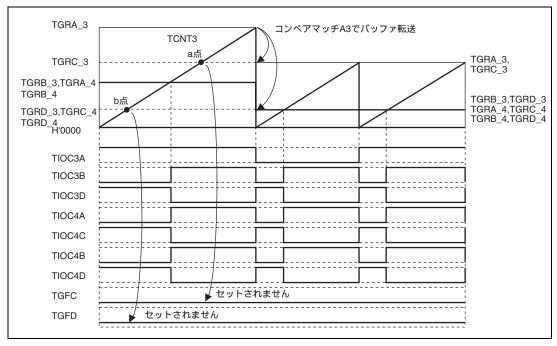

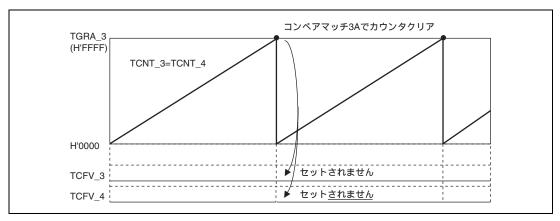

| 12.4.3  | バッファ動作                                        | 12-73  |

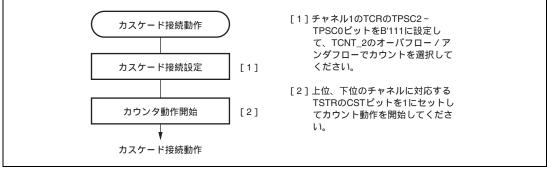

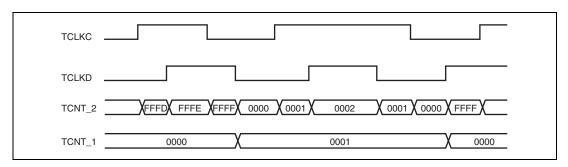

| 12.4.4  | カスケード接続動作                                     | 12-77  |

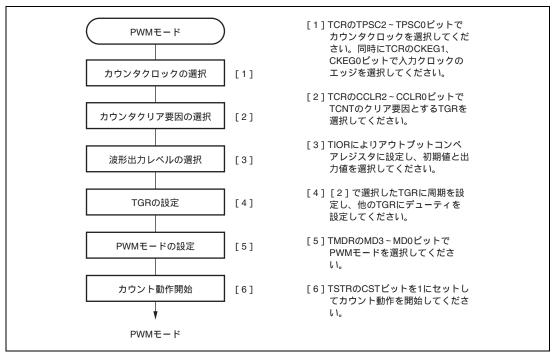

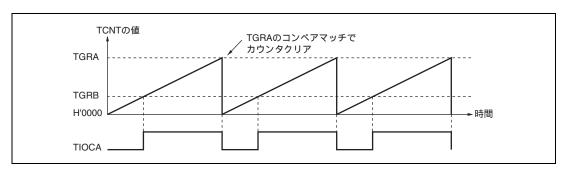

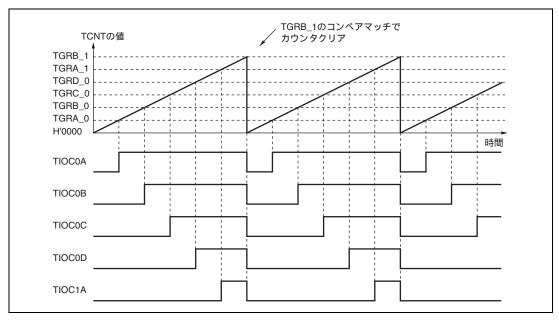

| 12.4.5  | PWM モード                                       | 12-81  |

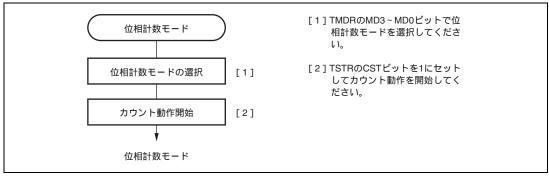

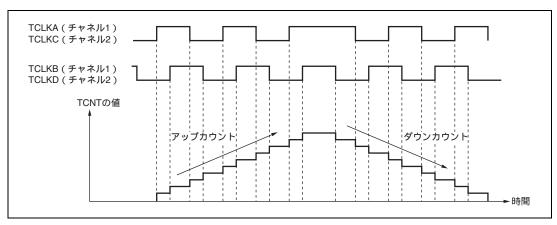

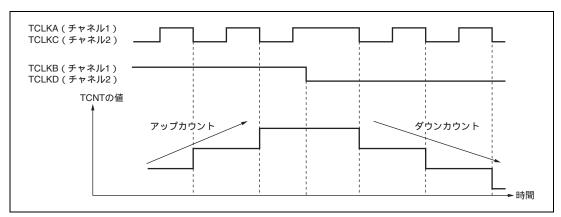

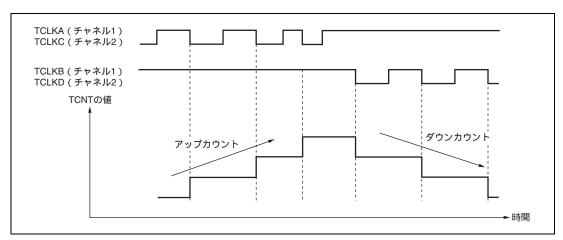

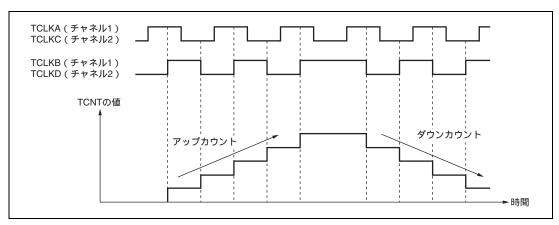

| 12.4.6  | 位相計数モード                                       | 12-86  |

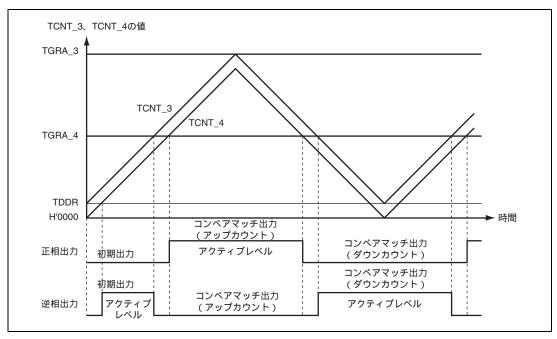

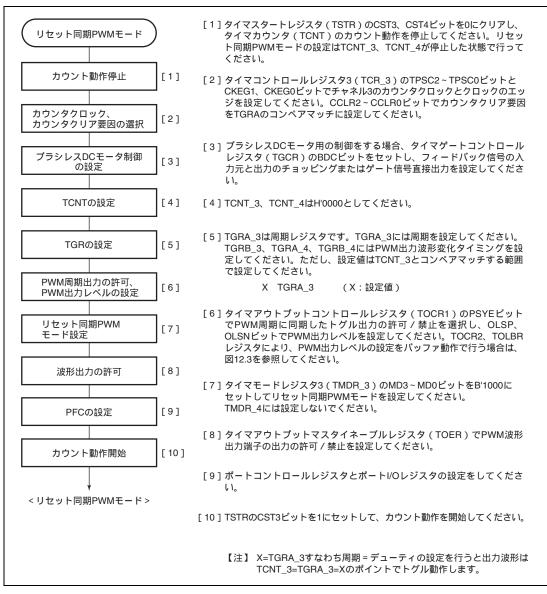

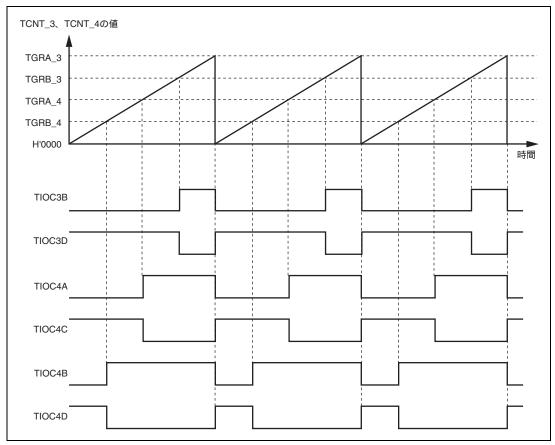

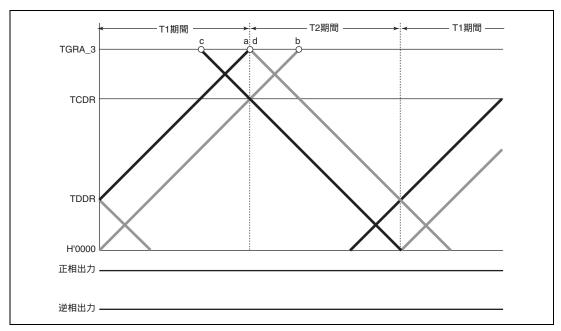

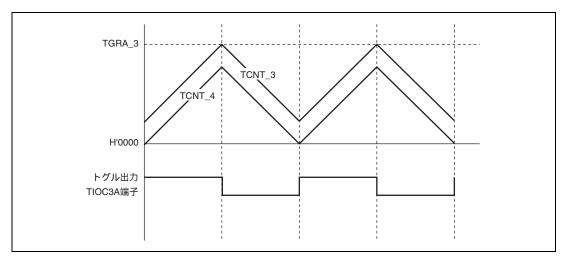

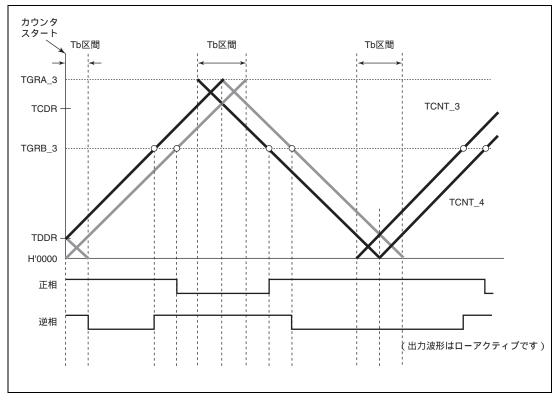

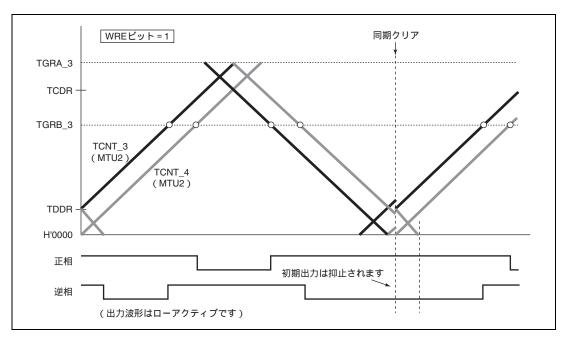

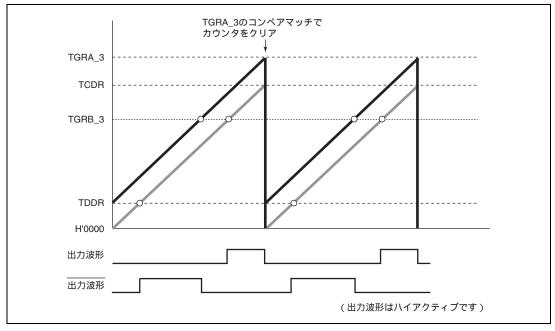

| 12.4.7  | リセット同期 PWM モード                                | 12-92  |

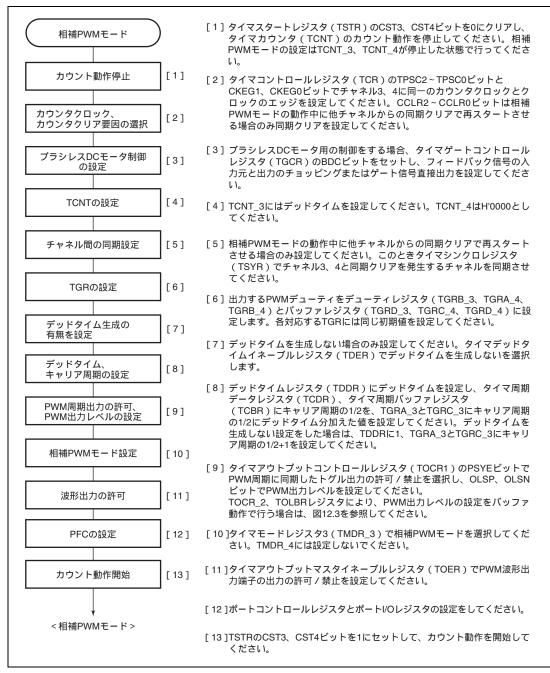

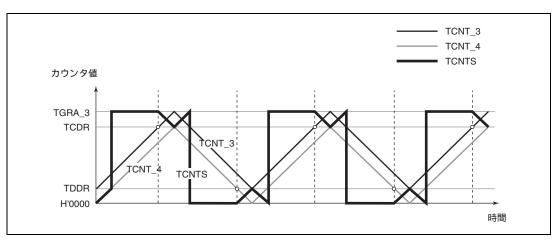

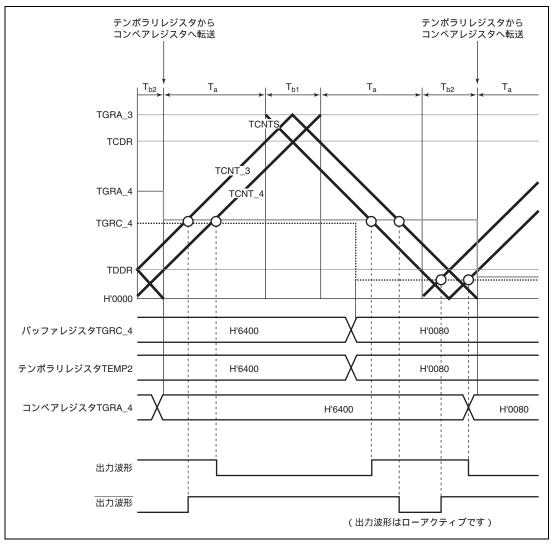

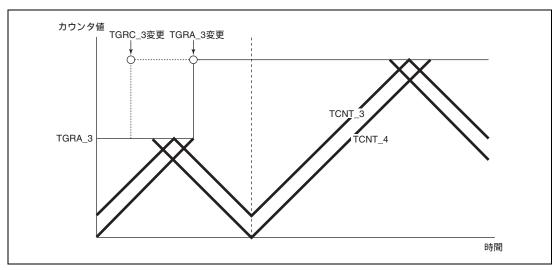

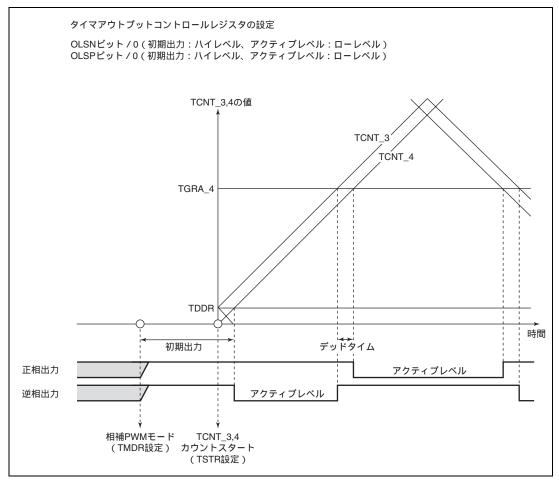

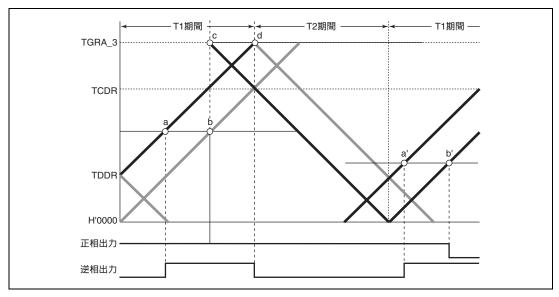

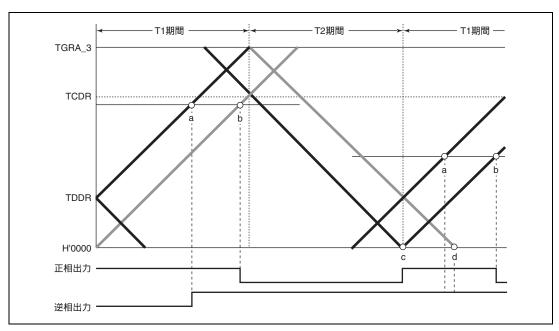

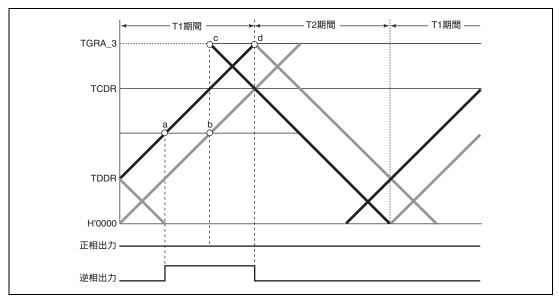

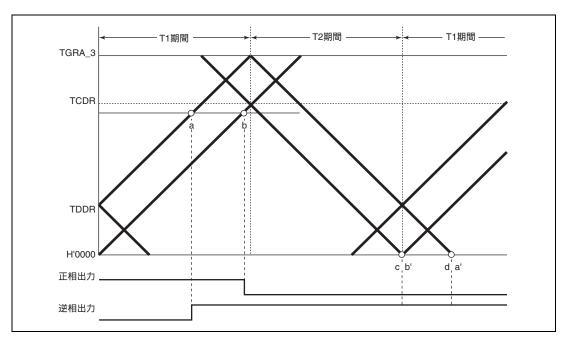

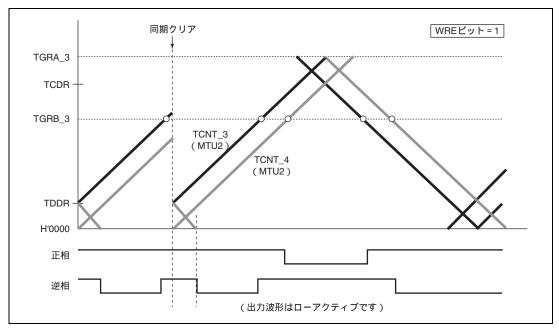

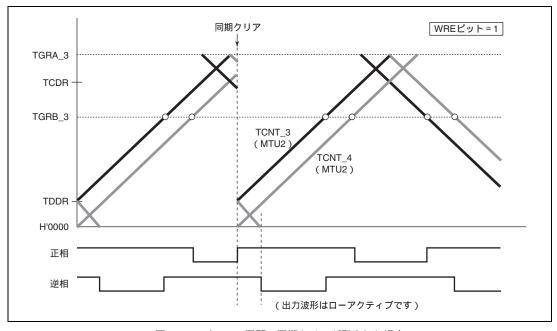

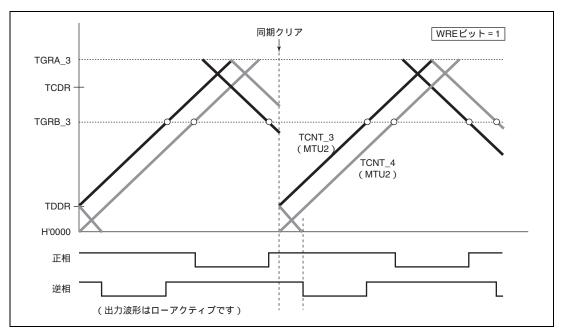

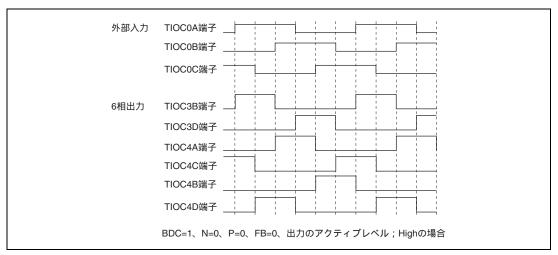

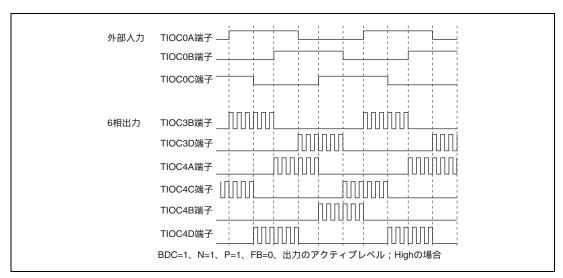

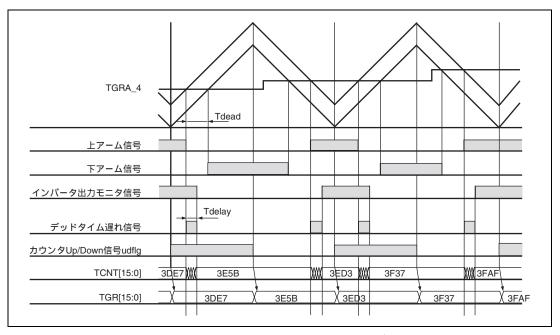

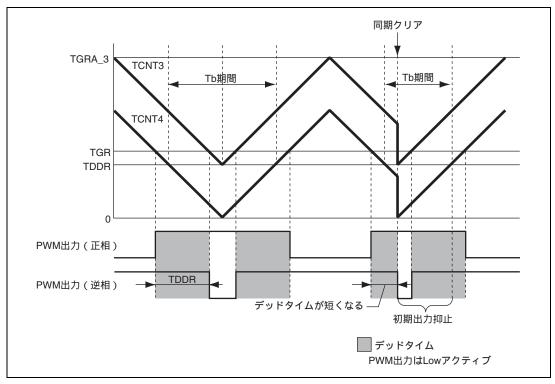

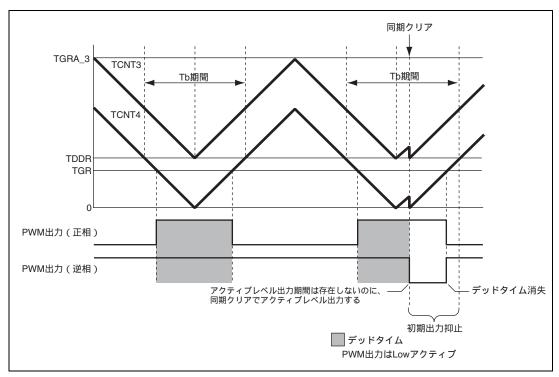

| 12.4.8  | 相補 PWM モード                                    | 12-95  |

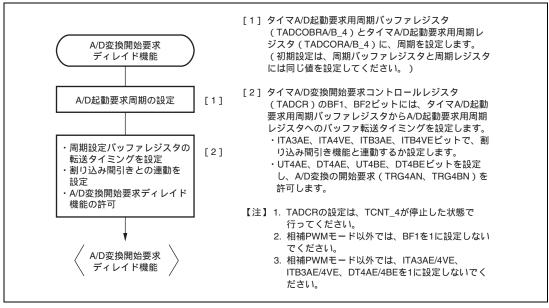

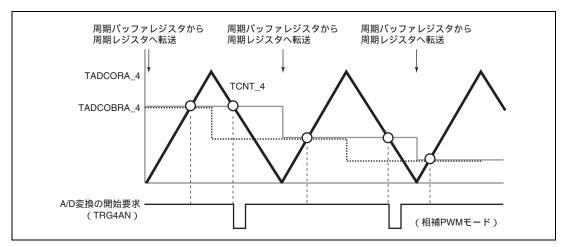

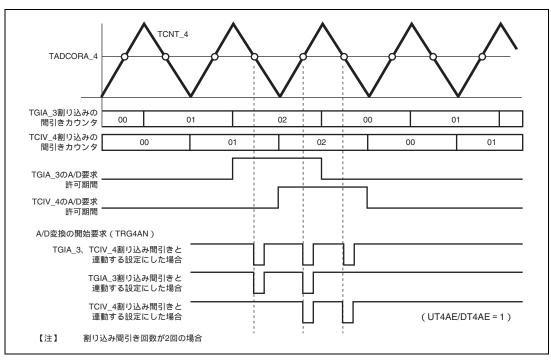

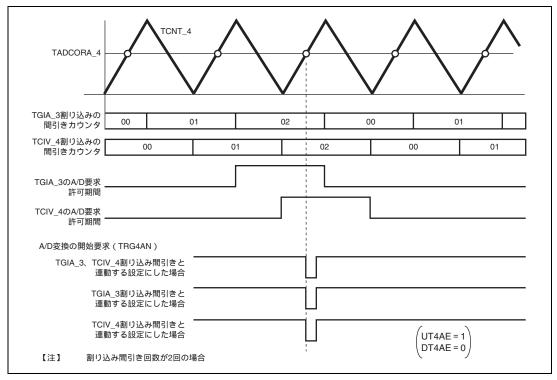

| 12.4.9  | A/D 変換開始要求ディレイド機能                             | 12-126 |

| 12.4.10 | ) 相補 PWM の「山/谷」での TCNT キャプチャ動作                | 12-130 |

| 12.5    | 割り込み要因                                        | 12-131 |

| 12.5.1  | 割り込み要因と優先順位                                   | 12-131 |

| 12.5.2  | DMAC の起動                                      | 12-133 |

| 12.5.3  | A/D 変換器の起動                                    | 12-133 |

| 12.6    | 動作タイミング                                       | 12-135 |

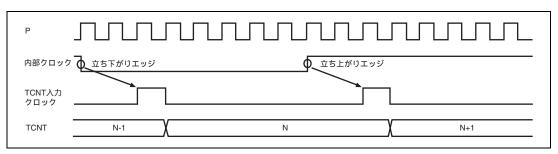

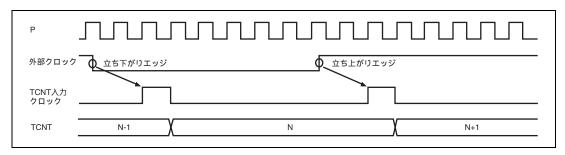

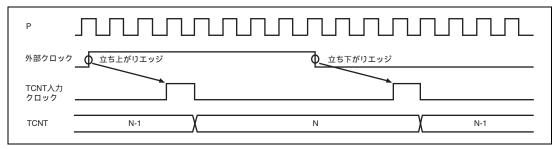

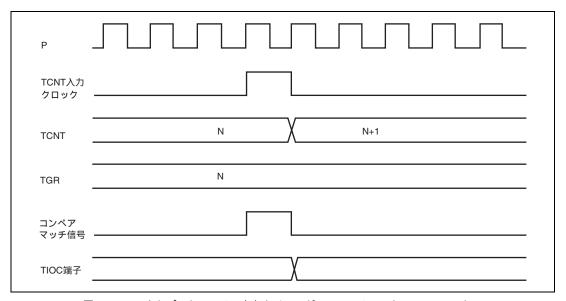

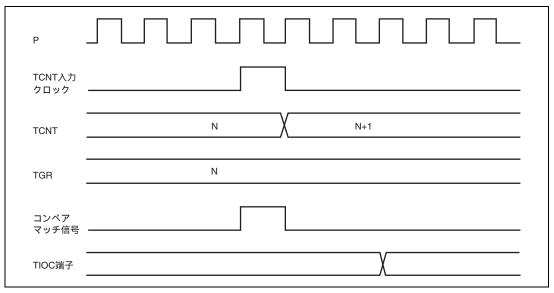

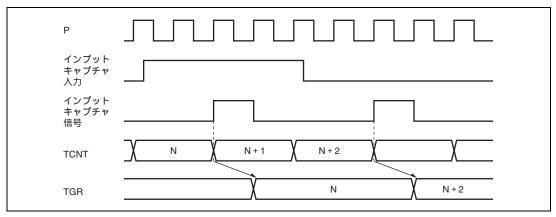

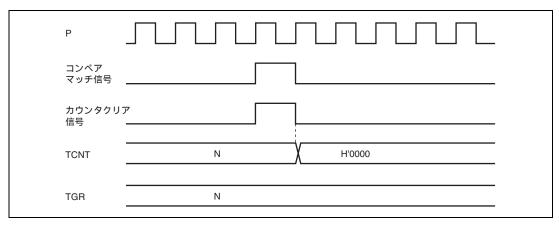

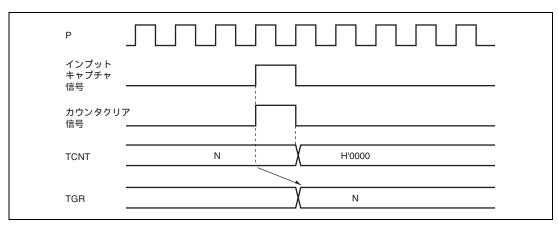

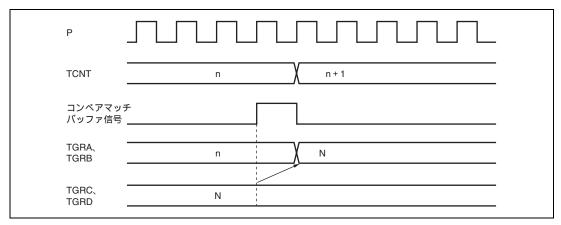

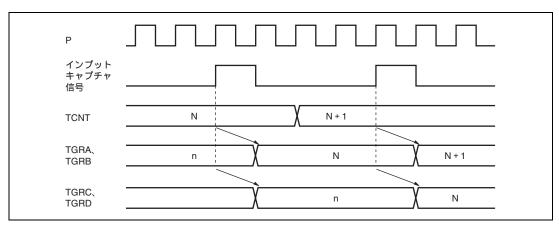

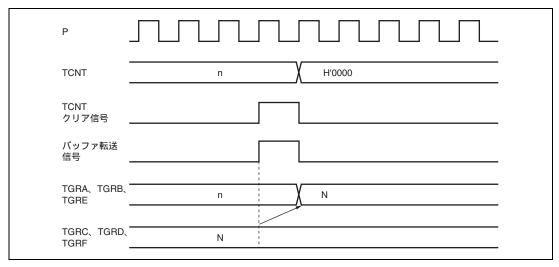

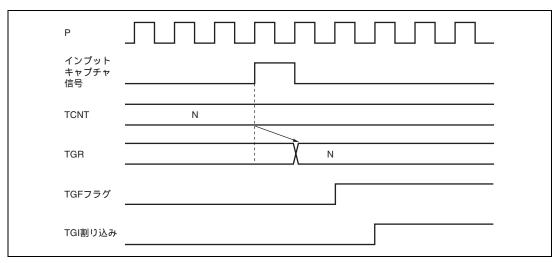

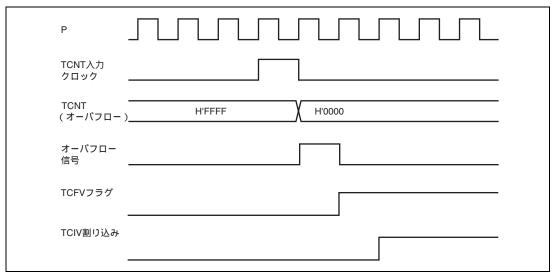

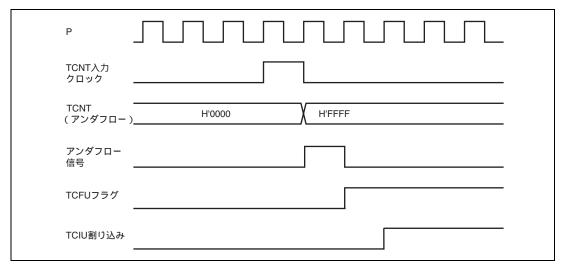

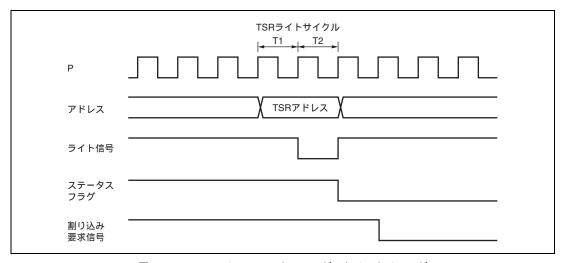

| 12.6.1  | 入出力タイミング                                      | 12-135 |

| 12.6.2  | 割り込み信号タイミング                                   | 12-142 |

| 12.7    | 使用上の注意事項                                      | 12-146 |

| 12.7.1  | モジュールスタンバイモードの設定                              | 12-146 |

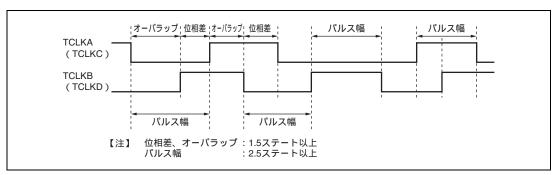

| 12.7.2  | 入力クロックの制限事項                                   | 12-146 |

| 12.7.3  | 周期設定上の注意事項                                    | 12-146 |

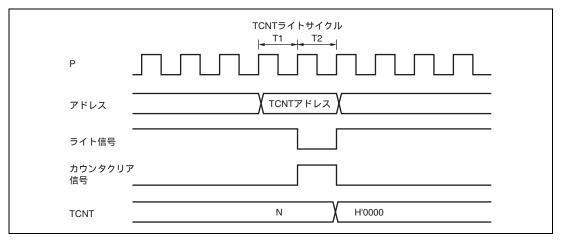

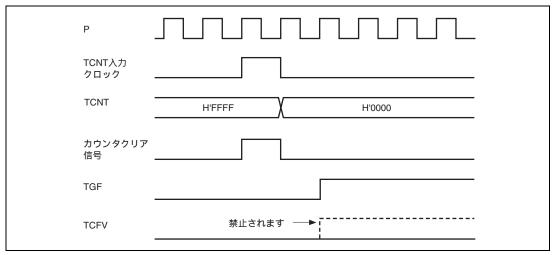

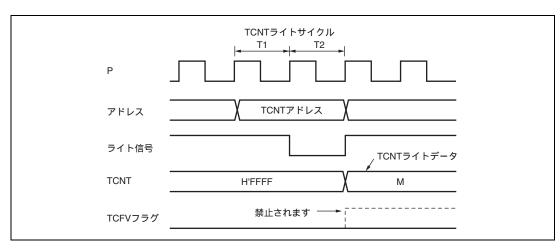

| 12.7.4  | TCNT のライトとクリアの競合                              | 12-147 |

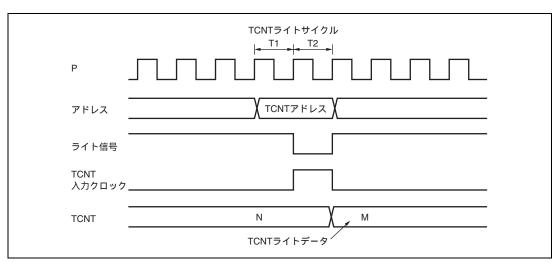

| 12.7.5  | TCNT のライトとカウントアップの競合                          | 12-147 |

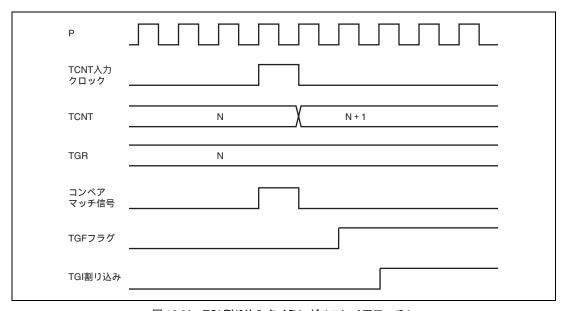

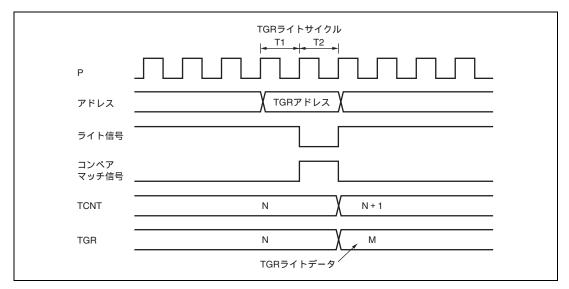

| 12.7.6  | TGR のライトとコンペアマッチの競合                           | 12-148 |

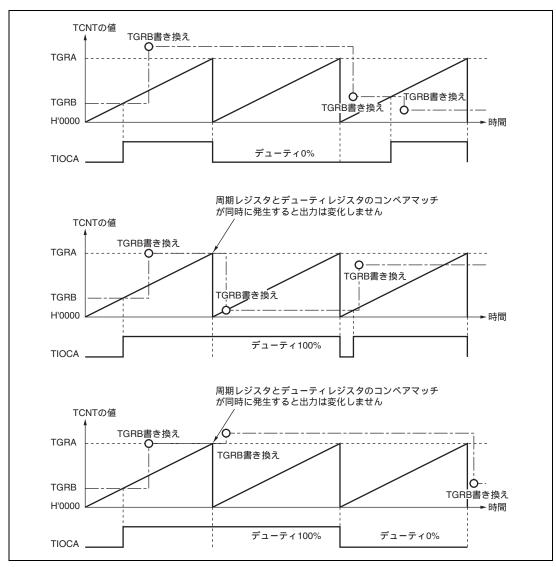

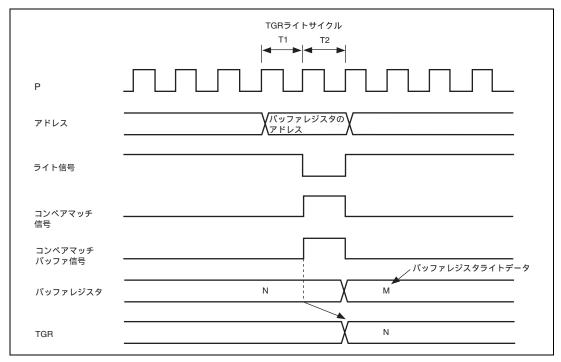

| 12.7.7  | バッファレジスタのライトとコンペアマッチの競合                       | 12-149 |

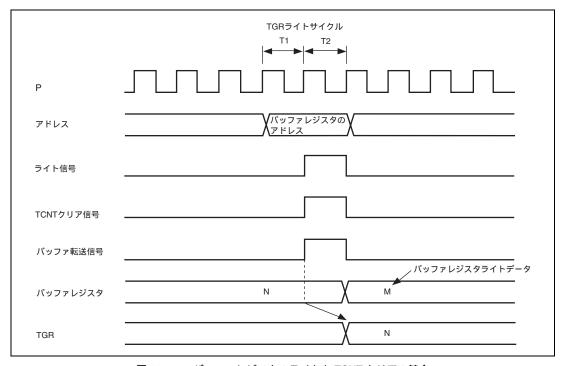

| 12.7.8  | バッファレジスタのライトと TCNT クリアの競合                     | 12-150 |

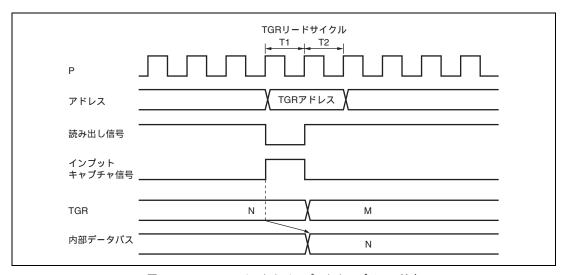

| 12.7.9  | TGR のリードとインプットキャプチャの競合                        | 12-151 |

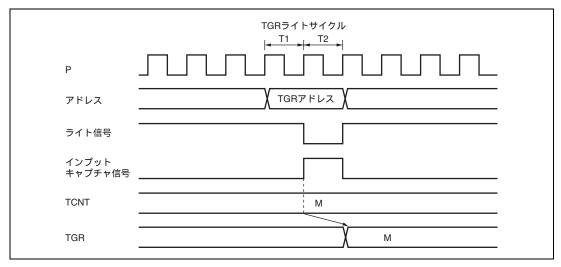

| 12.7.10 | ) TGR のライトとインプットキャプチャの競合                      | 12-152 |

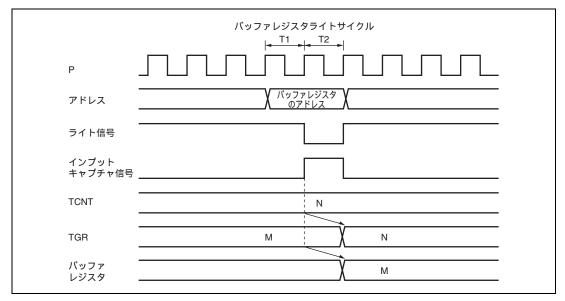

| 12.7.11 | バッファレジスタのライトとインプットキャプチャの競合                    | 12-153 |

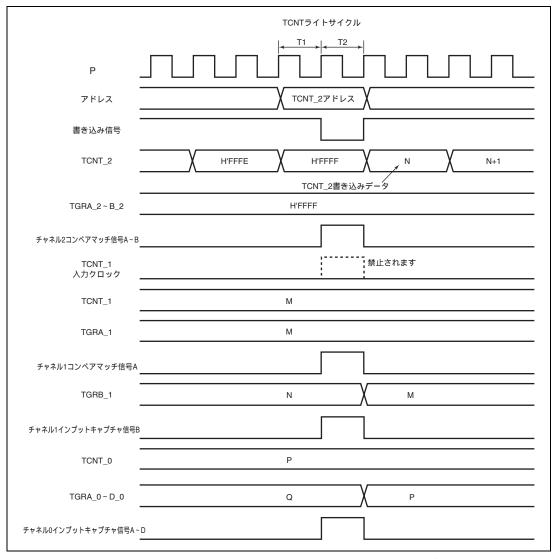

| 12.7.12 | 2 カスケード接続における TCNT_2 のライトとオーバフロー / アンダフローの 競合 | 12-153 |

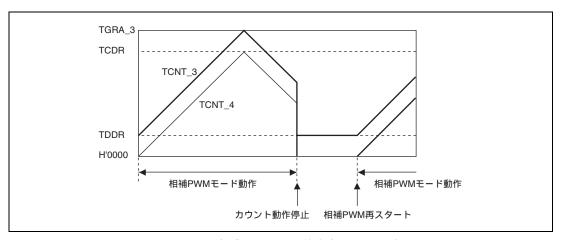

| 12.7.13 | 3 相補 PWM モード停止時のカウンタ値                         | 12-155 |

| 12.7.14 | 4 相補 PWM モードでのバッファ動作の設定                       | 12-155 |

| 12.7.15 | 5 リセット同期 PWM モードのバッファ動作とコンペアマッチフラグ            | 12-156 |

| 12.7.16 | う リセット同期 PWM モードのオーバフローフラグ                    | 12-157 |

| 12.7.17 | オーバフロー / アンダフローとカウンタクリアの競合                    | 12-158 |

|         |                                               |        |

| 12.7.18 | 3 TCNT のライトとオーバフロー / アンダフローの競合                  | .12-158 |

|---------|-------------------------------------------------|---------|

| 12.7.19 | 通常動作または PWM モード 1 からリセット同期 PWM モードへ遷移する場合の注意事項. | .12-159 |

| 12.7.20 | ) 相補 PWM モード、リセット同期 PWM モードの出力レベル               | .12-159 |

| 12.7.21 | モジュールスタンバイ時の割り込み                                | .12-159 |

| 12.7.22 | カスケード接続における TCNT_1、TCNT_2 同時インプットキャプチャ          | .12-159 |

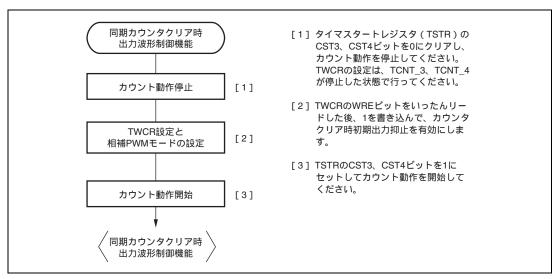

| 12.7.23 | は 相補 PWM モードでの同期カウンタクリア時出力波形制御における注意事項          | .12-160 |

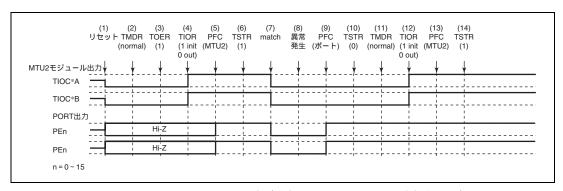

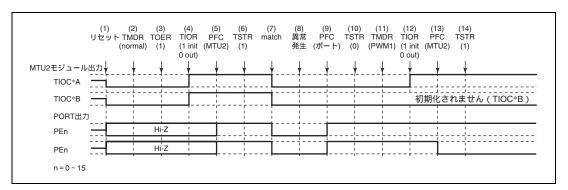

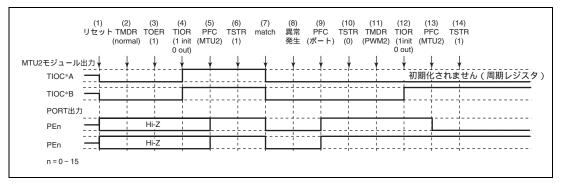

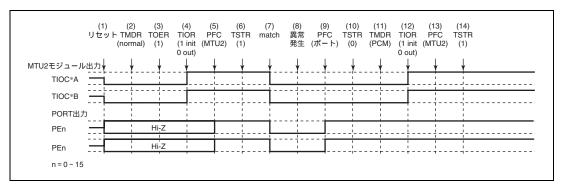

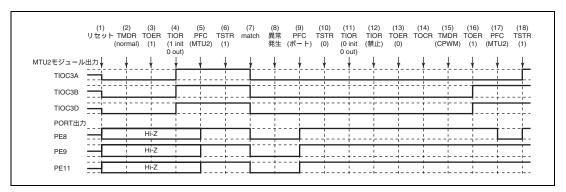

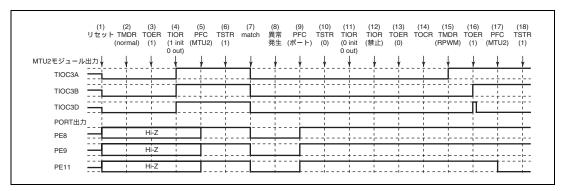

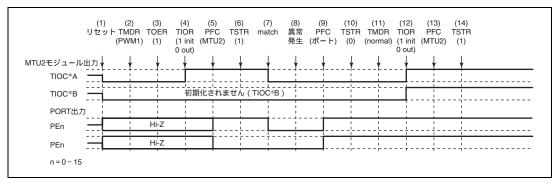

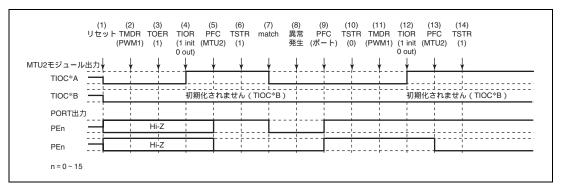

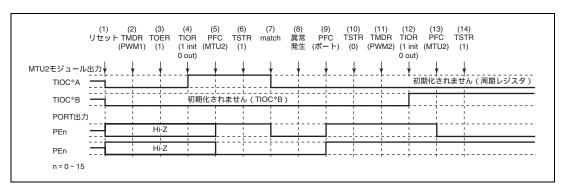

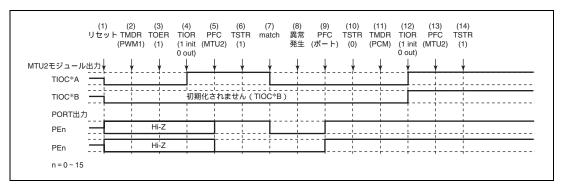

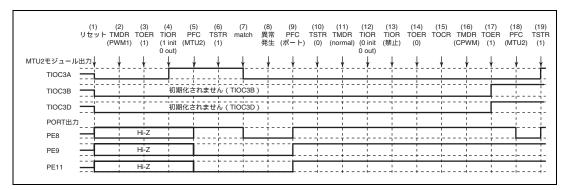

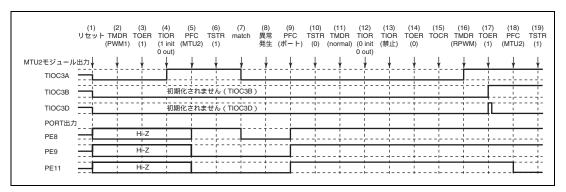

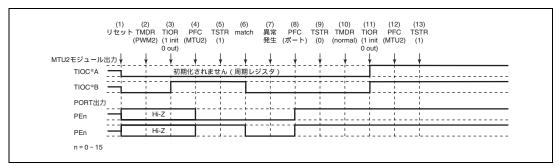

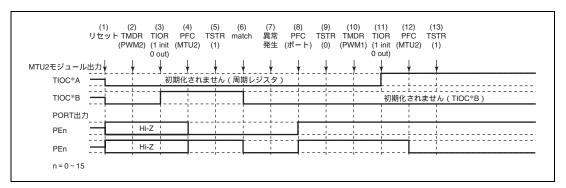

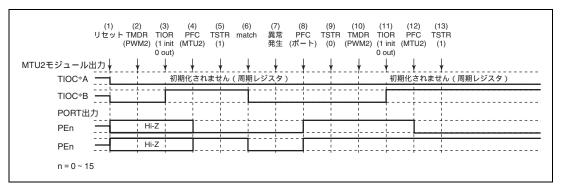

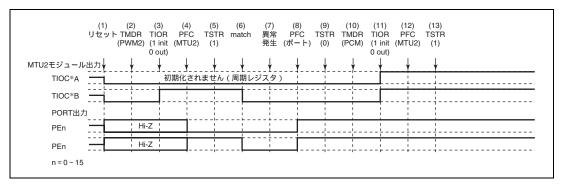

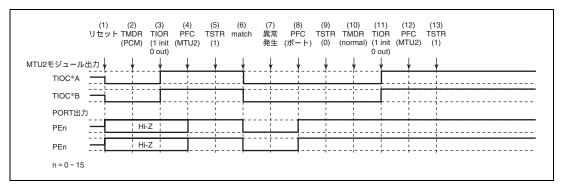

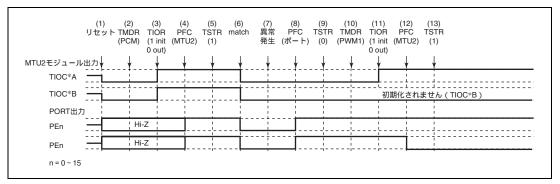

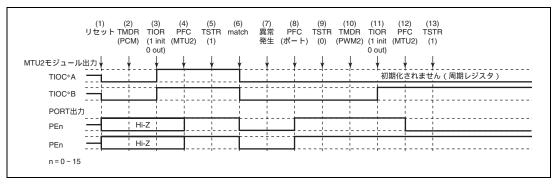

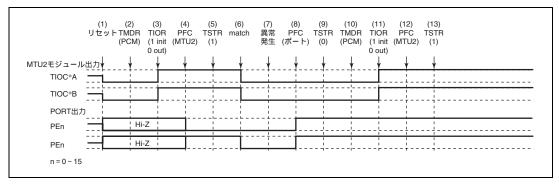

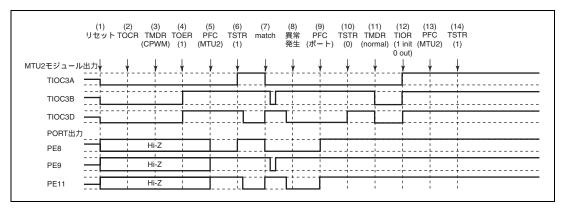

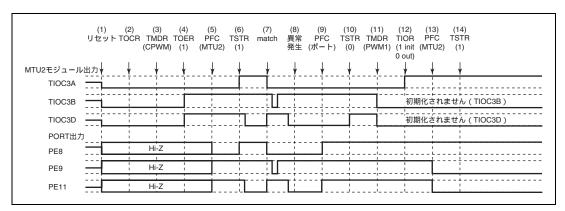

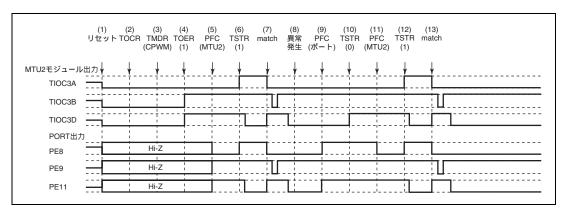

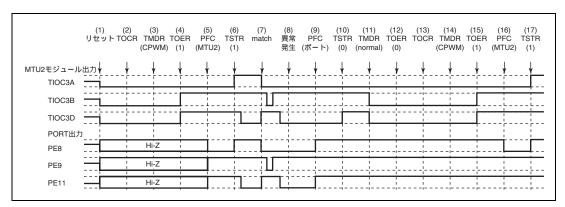

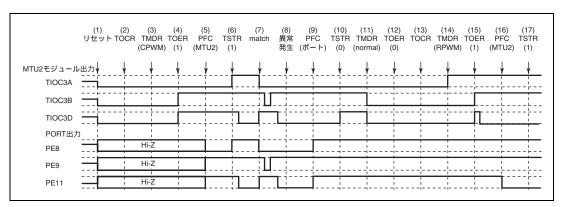

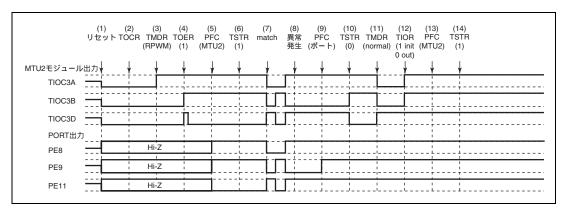

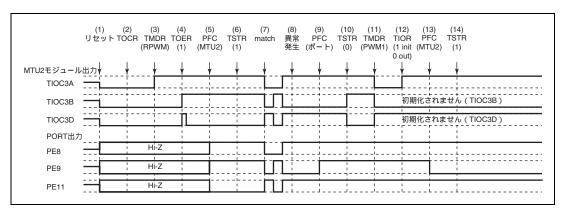

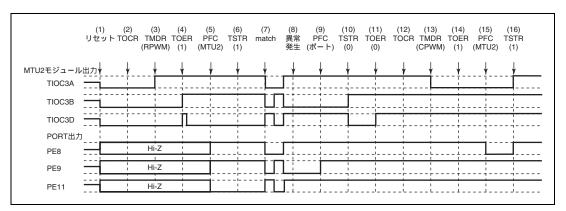

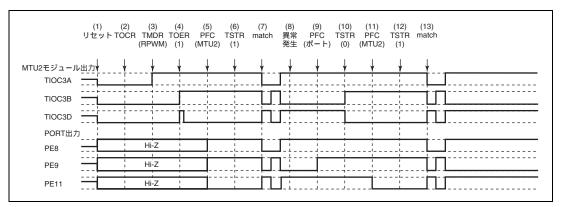

| 12.8    | MTU2出力端子の初期化方法                                  | .12-162 |

| 12.8.1  | 動作モード                                           | .12-162 |

| 12.8.2  | リセットスタート時の動作                                    | .12-162 |

| 12.8.3  | 動作中の異常などによる再設定時の動作                              | .12-163 |

| 12.8.4  | 動作中の異常などによる端子の初期化手順、モード遷移の概要                    | .12-163 |

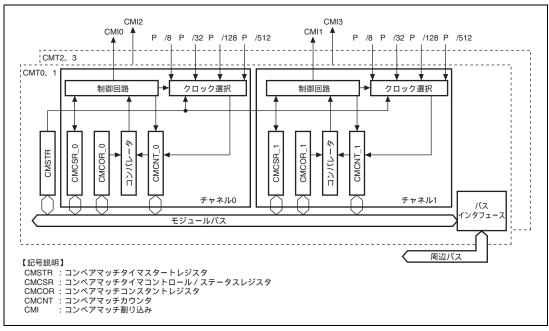

| 13. コン  | ペアマッチタイマ(CMT)                                   | 13-1    |

| 13.1    | 特長                                              | 13-1    |

| 13.2    | レジスタの説明                                         | 13-2    |

| 13.2.1  | コンペアマッチタイマスタートレジスタ (CMSTR)                      | 13-3    |

| 13.2.2  | コンペアマッチタイマコントロール / ステータスレジスタ(CMCSR)             | 13-4    |

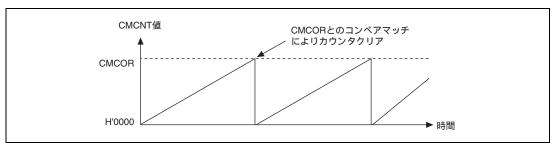

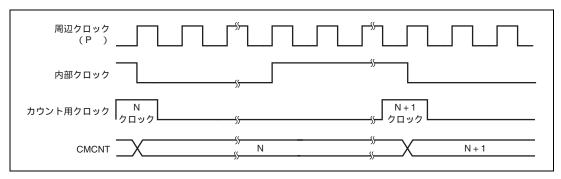

| 13.2.3  | コンペアマッチカウンタ(CMCNT)                              | 13-5    |

| 13.2.4  | コンペアマッチコンスタントレジスタ(CMCOR)                        | 13-5    |

| 13.3    | 動作説明                                            | 13-6    |

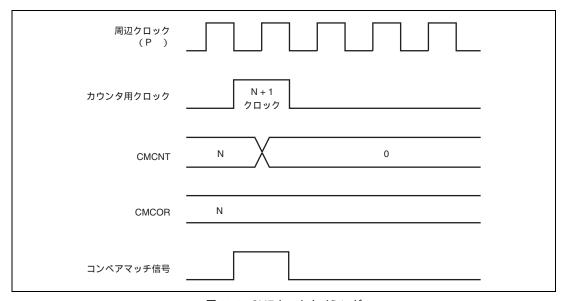

| 13.3.1  | 期間カウント動作                                        | 13-6    |

| 13.3.2  | CMCNT カウントタイミング                                 | 13-6    |

| 13.4    | 割り込み                                            | 13-7    |

| 13.4.1  | 割り込み要因と DMA 転送要求                                | 13-7    |

| 13.4.2  | コンペアマッチフラグのセットタイミング                             | 13-7    |

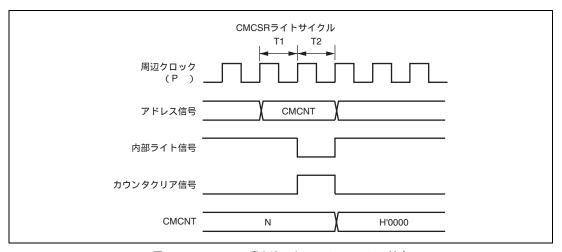

| 13.4.3  | コンペアマッチフラグのクリアタイミング                             | 13-8    |

| 13.5    | 使用上の注意事項                                        | 13-9    |

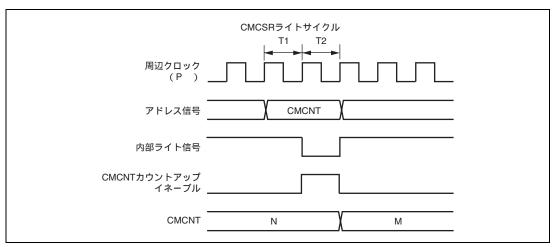

| 13.5.1  | CMCNT の書き込みとコンペアマッチの競合                          | 13-9    |

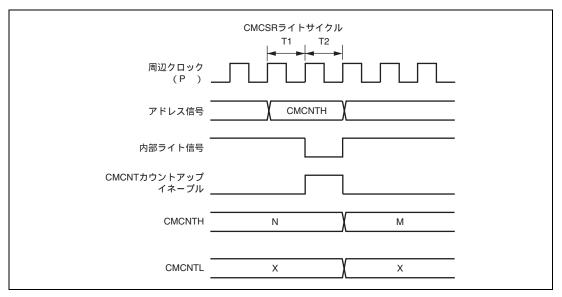

| 13.5.2  | CMCNT のワード書き込みとカウントアップの競合                       | 13-9    |

| 13.5.3  | CMCNT のバイト書き込みとカウントアップの競合                       | 13-10   |

| 13.5.4  | CMCNT と CMCOR のコンペアマッチ                          | 13-10   |

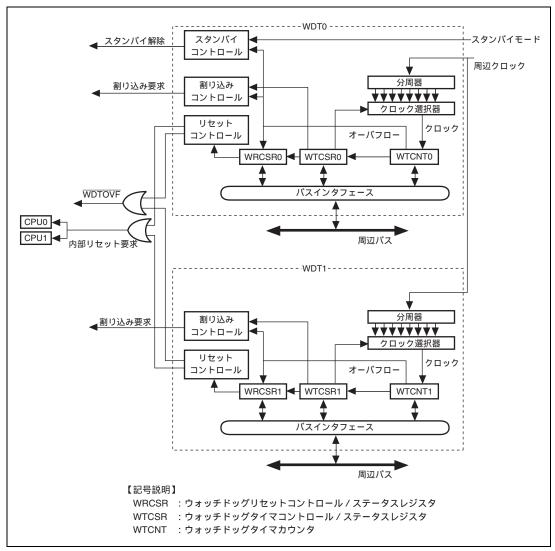

| 14. ウォ  | ッチドッグタイマ(WDT)                                   | 14-1    |

| 14.1    | 特長                                              | 14-1    |

| 14.2    | 入出力端子                                           | 14-3    |

| 14.3    | レジスタの説明                                         | 14-4    |

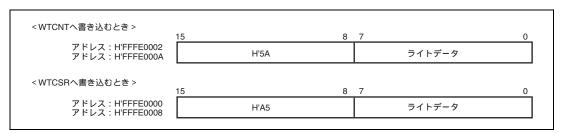

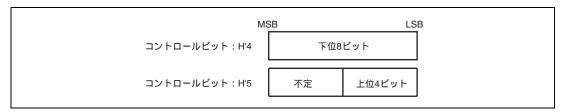

| 14.3.1  | ウォッチドッグタイマカウンタ ( WTCNT0、 WTCNT1 )               | 14-4    |

| 14.3.2  | ウォッチドッグタイマコントロール/ステータスレジスタ (WTCSR0、WTCSR1)      | 14-5    |

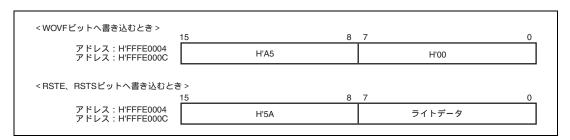

| 14.3.3  | ウォッチドッグリセットコントロール/ステータスレジスタ (WRCSR0、WRCSR1)     | 14-7    |

| 14.3.4  | レジスタアクセス時の注意                                    | 14-8    |

| 14.4    | WDTの使用方法                    | 14-10 |

|---------|-----------------------------|-------|

| 14.4.1  | ソフトウェアスタンバイモード解除の手順         | 14-10 |

| 14.4.2  | PLL の逓倍率変更の手順               | 14-10 |

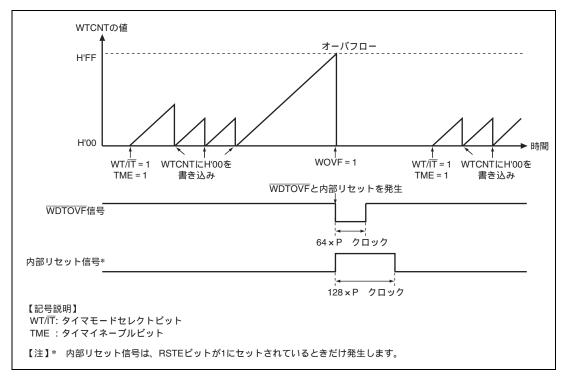

| 14.4.3  | ウォッチドッグタイマモードの使用法           | 14-10 |

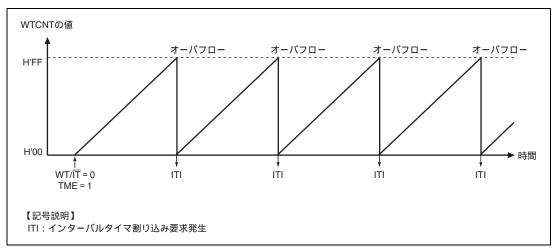

| 14.4.4  | インターバルタイマモードの使用法            | 14-12 |

| 14.5    | 使用上の注意事項                    | 14-13 |

| 14.5.1  | タイマ誤差                       | 14-13 |

| 14.5.2  | WTCNT の設定値として H'FF は設定禁止    | 14-13 |

| 14.5.3  | インターバルタイマオーバフローフラグ          | 14-13 |

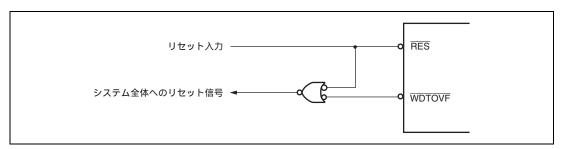

| 14.5.4  | WDTOVF 信号によるシステムリセット        | 14-13 |

| 14.5.5  | ウォッチドッグタイマモードのマニュアルリセット     | 14-14 |

| 14.5.6  | ディープスタンバイモードへの遷移について        | 14-14 |

| 14.5.7  | ウォッチドッグタイマモードでの内部リセット       | 14-14 |

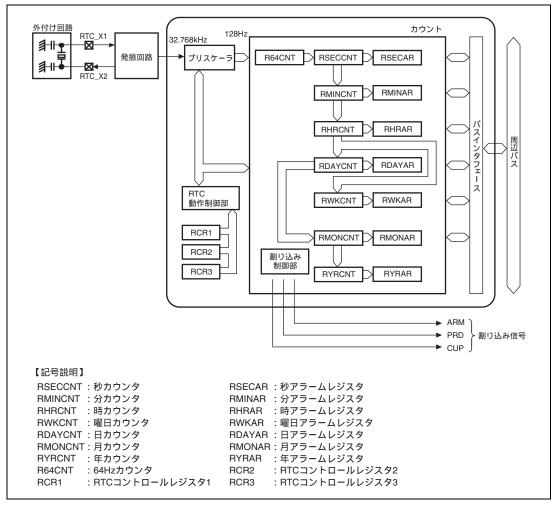

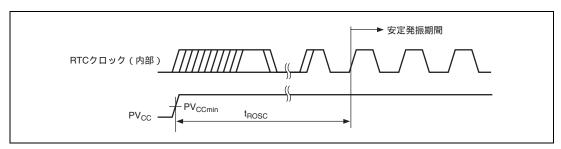

| 15. リア  | プルタイムクロック(RTC)              | 15-1  |

| 15.1    | 特長                          |       |

| 15.2    | 入出力端子                       |       |

| 15.3    | レジスタの説明                     |       |

| 15.3.1  | 64Hz カウンタ(R64CNT)           | 15-4  |

| 15.3.2  | 秒カウンタ ( RSECCNT )           |       |

| 15.3.3  | 分カウンタ(RMINCNT)              | 15-6  |

| 15.3.4  | 時カウンタ(RHRCNT)               | 15-7  |

| 15.3.5  | 曜日カウンタ(RWKCNT)              |       |

| 15.3.6  | 日カウンタ ( RDAYCNT )           | 15-9  |

| 15.3.7  | 月カウンタ ( RMONCNT )           |       |

| 15.3.8  | 年カウンタ(RYRCNT)               |       |

| 15.3.9  | 秒アラームレジスタ (RSECAR )         | 15-12 |

| 15.3.10 | ) 分アラームレジスタ(RMINAR)         | 15-13 |

| 15.3.11 | 時アラームレジスタ(RHRAR)            | 15-14 |

| 15.3.12 | 2 曜日アラームレジスタ(RWKAR)         | 15-15 |

| 15.3.13 | 3 日アラームレジスタ(RDAYAR)         | 15-16 |

| 15.3.14 | 4 月アラームレジスタ(RMONAR)         | 15-17 |

| 15.3.15 | 5 年アラームレジスタ(RYRAR)          | 15-18 |

| 15.3.16 | 6 RTC コントロールレジスタ 1 (RCR1)   | 15-18 |

| 15.3.17 | 7 RTC コントロールレジスタ 2 ( RCR2 ) | 15-20 |

| 15.3.18 |                             |       |

| 15.4    | 動作説明                        |       |

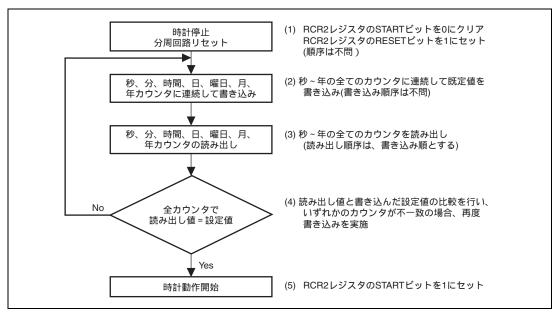

| 15.4.1  | 電源投入後のレジスタの初期設定             | 15-22 |

| 15.4.2  | 時刻設定手順                      | 15-22 |

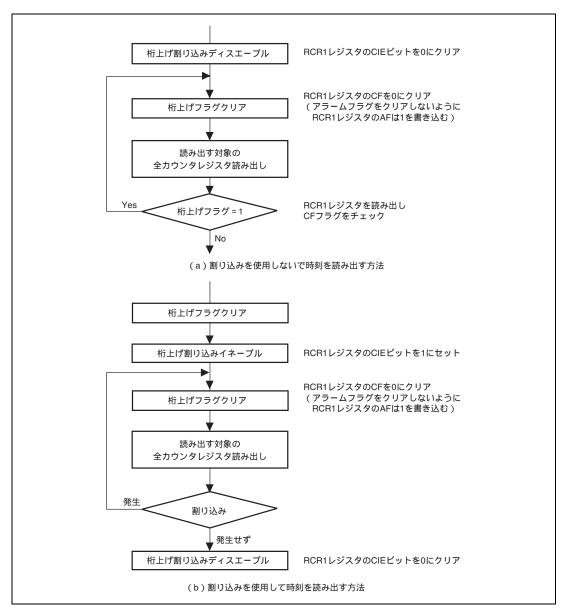

| 15.4.3  | 時刻読み出し手順                    | 15-23 |

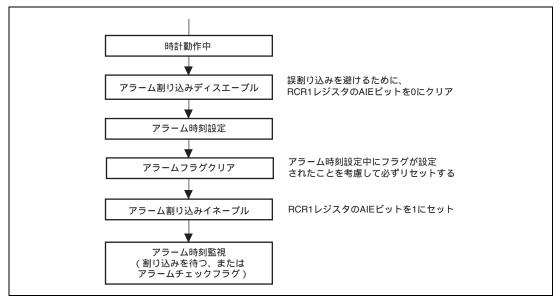

| 15.4.4   | アラーム機能                                | 15-24 |

|----------|---------------------------------------|-------|

| 15.5     | 使用上の注意事項                              | 15-25 |

| 15.5.1   | RTC カウント動作時のレジスタ書き込みについて              | 15-25 |

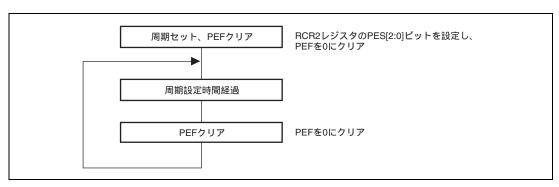

| 15.5.2   | リアルタイムクロック(RTC)の周期割り込みの使用について         | 15-25 |

| 15.5.3   | レジスタ設定後のスタンバイ遷移について                   | 15-25 |

| 15.5.4   | レジスタ書き込み/読み出し時の注意事項                   | 15-25 |

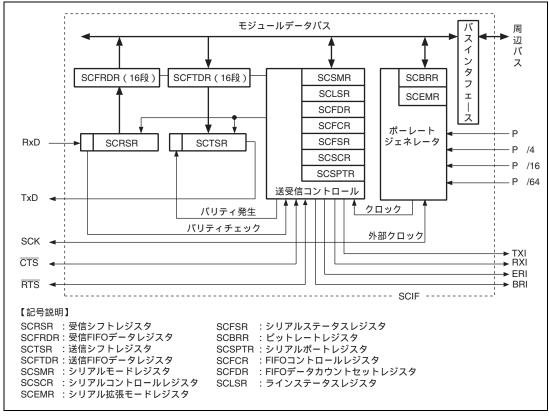

| 16. FIF0 | )内蔵シリアルコミュニケーションインタフェース(SCIF)         | 16-1  |

| 16.1     | 特長                                    | 16-1  |

| 16.2     | 入出力端子                                 |       |

| 16.3     | レジスタの説明                               | 16-4  |

| 16.3.1   | 受信シフトレジスタ(SCRSR )                     |       |

| 16.3.2   | 受信 FIFO データレジスタ(SCFRDR)               | 16-6  |

| 16.3.3   | · · · · · · · · · · · · · · · · · · · |       |

| 16.3.4   | 送信 FIFO データレジスタ(SCFTDR )              |       |

| 16.3.5   | シリアルモードレジスタ(SCSMR )                   |       |

| 16.3.6   | シリアルコントロールレジスタ ( SCSCR )              |       |

| 16.3.7   | シリアルステータスレジスタ ( SCFSR )               | 16-12 |

| 16.3.8   | ビットレートレジスタ ( SCBRR )                  |       |

| 16.3.9   | FIFO コントロールレジスタ ( SCFCR )             |       |

| 16.3.10  |                                       |       |

| 16.3.11  | シリアルポートレジスタ ( SCSPTR )                | 16-28 |

| 16.3.12  | ラインステータスレジスタ(SCLSR)                   | 16-30 |

| 16.3.13  | シリアル拡張モードレジスタ(SCEMR )                 | 16-31 |

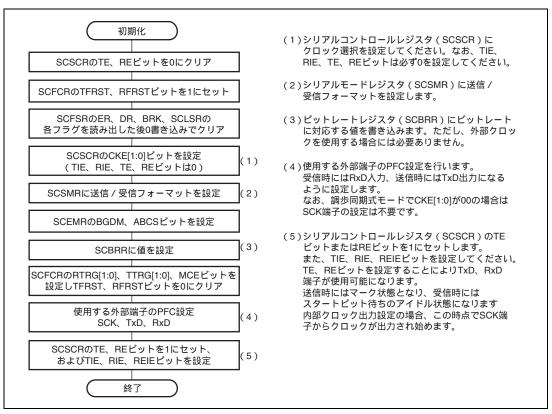

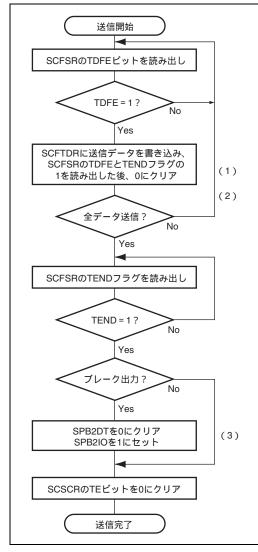

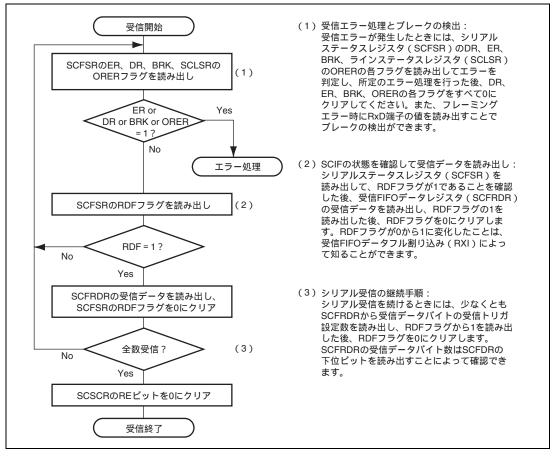

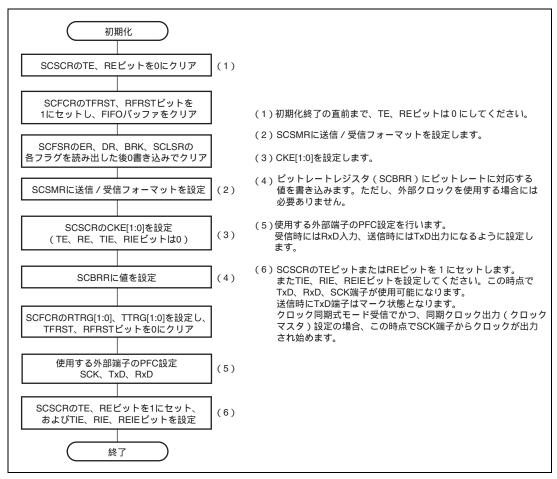

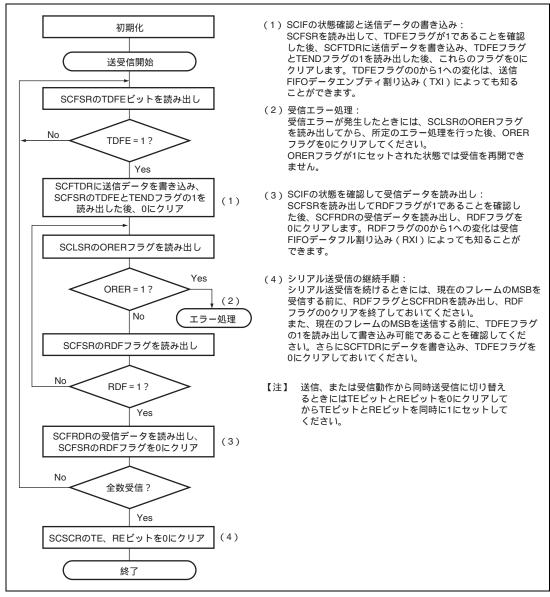

| 16.4     | 動作説明                                  | 16-32 |

| 16.4.1   | 概要                                    | 16-32 |

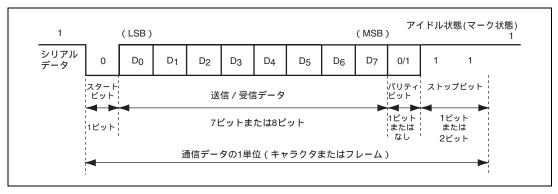

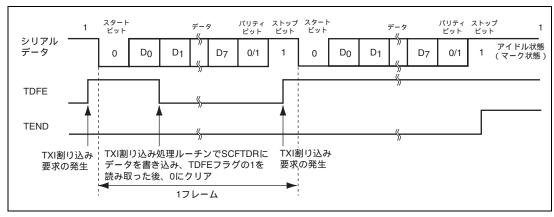

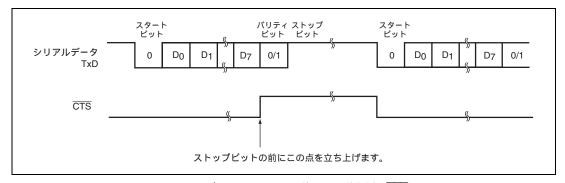

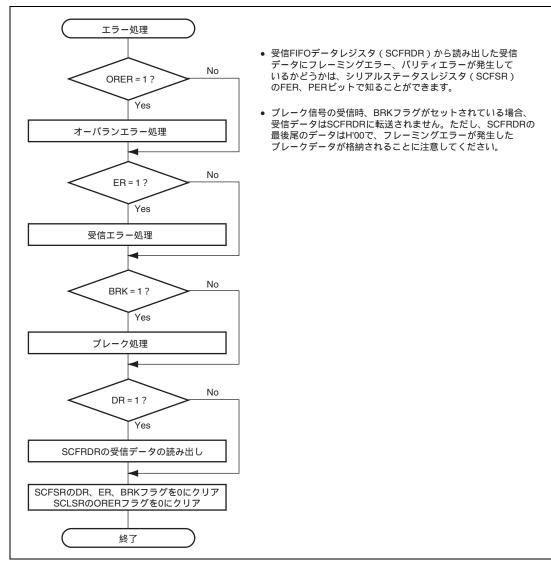

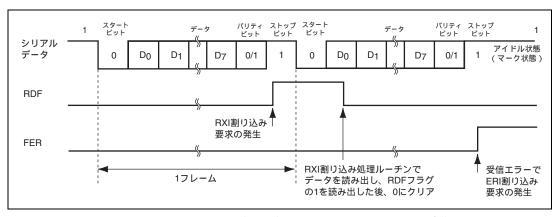

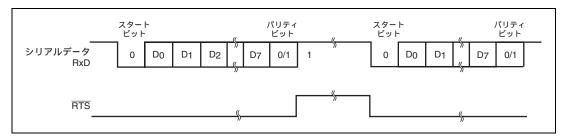

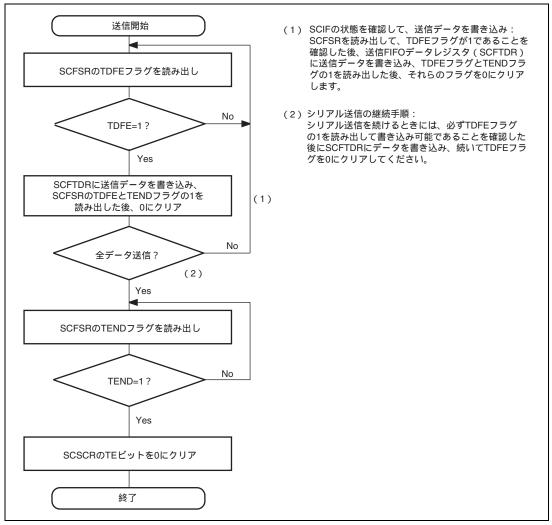

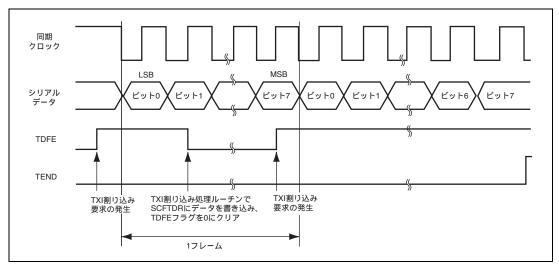

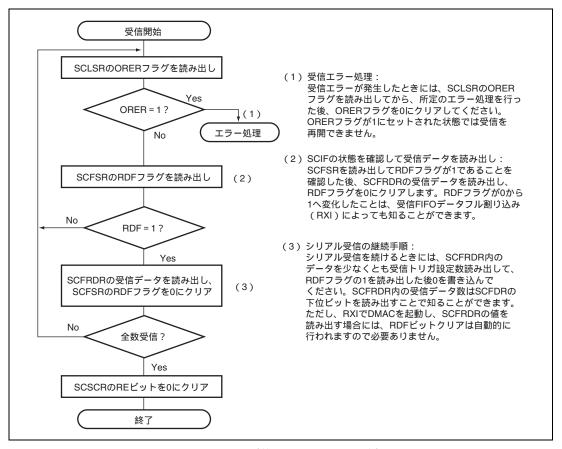

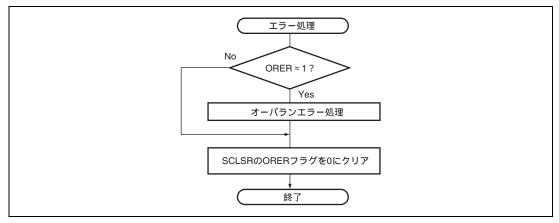

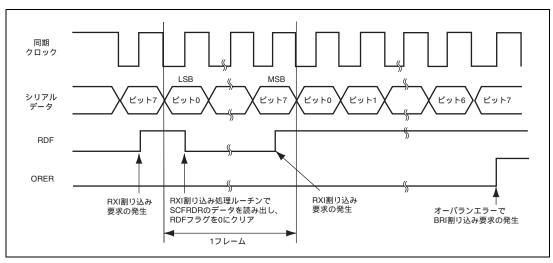

| 16.4.2   | 調歩同期式モード時の動作                          | 16-34 |

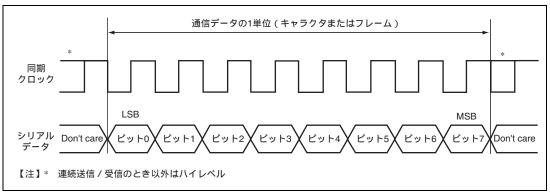

| 16.4.3   | クロック同期式モード時の動作                        | 16-43 |

| 16.5     | SCIFの割り込み                             | 16-51 |

| 16.6     | 使用上の注意事項                              | 16-52 |

| 16.6.1   | SCFTDR への書き込みと TDFE フラグ               | 16-52 |

| 16.6.2   | SCFRDR の読み出しと RDF フラグ                 | 16-52 |

| 16.6.3   | DMAC 使用上の制約事項                         |       |

| 16.6.4   | ブレークの検出と処理                            | 16-52 |

| 16.6.5   | ブレークの送り出し                             |       |

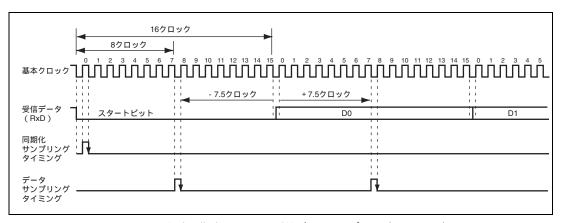

| 16.6.6   | 調歩同期式モードの受信データサンプリングタイミングと受信マージン      | 16-53 |

| 16.6.7   | 調歩同期式基本クロックセレクト                       |       |

|          |                                       |       |

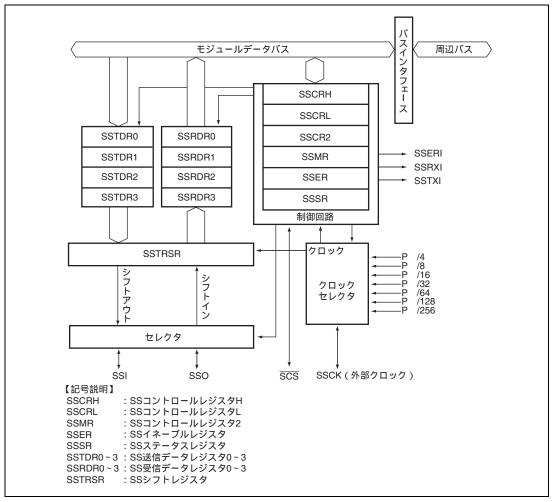

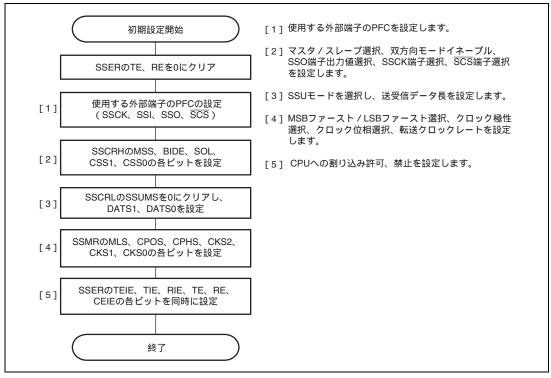

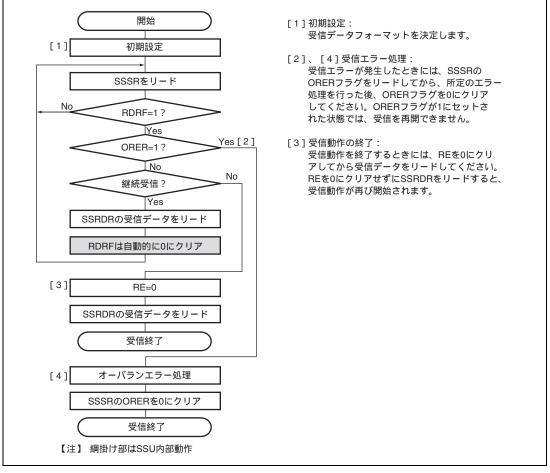

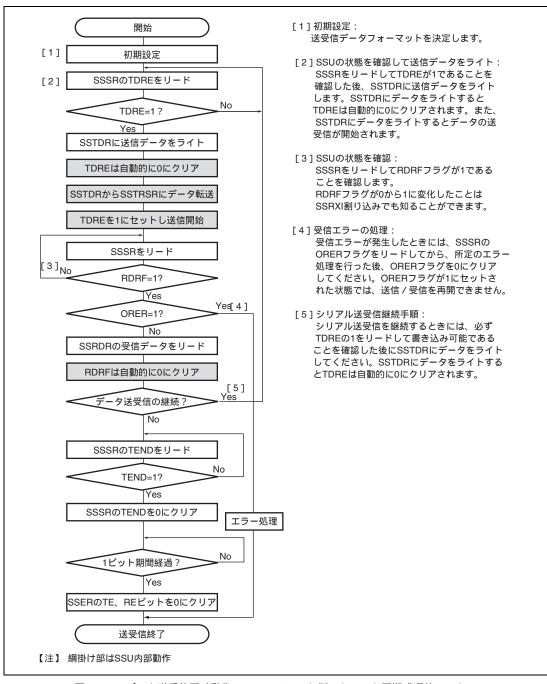

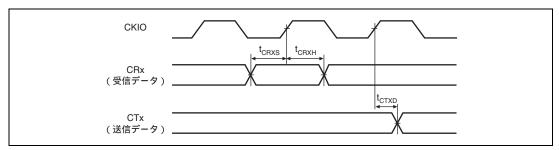

| 17. シン   | クロナスシリアルコミュニケーションユニット(SSU)            | 17-1  |

| 17.1     | 特長                                    | 17-1  |

| 17.2                   | 入出力端子                                     | 17-3  |

|------------------------|-------------------------------------------|-------|

| 17.3                   | レジスタの説明                                   | 17-4  |

| 17.3.1                 | SS コントロールレジスタ H ( SSCRH )                 | 17-5  |

| 17.3.2                 | SS コントロールレジスタ L ( SSCRL )                 | 17-6  |

| 17.3.3                 | SS モードレジスタ ( SSMR )                       | 17-7  |

| 17.3.4                 | SS イネーブルレジスタ ( SSER )                     | 17-8  |

| 17.3.5                 | SS ステータスレジスタ ( SSSR )                     | 17-9  |

| 17.3.6                 | SS コントロールレジスタ 2 ( SSCR2 )                 | 17-12 |

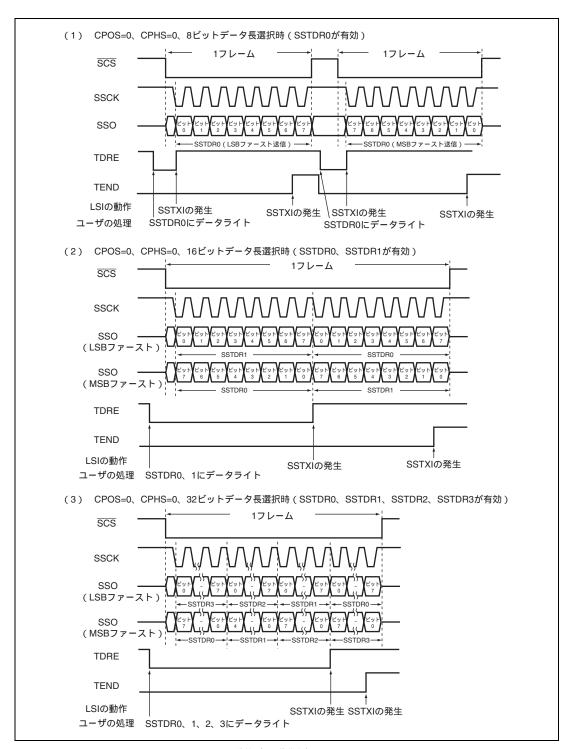

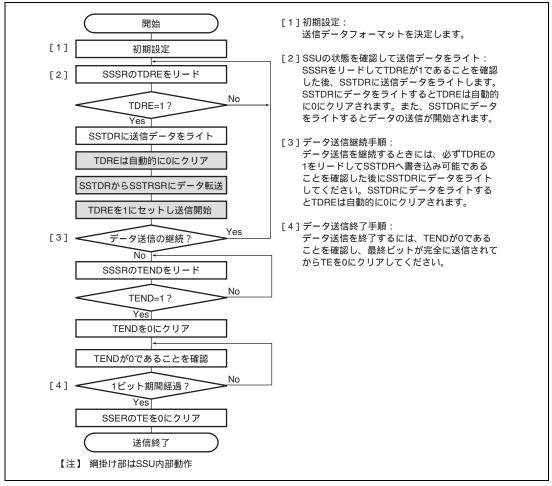

| 17.3.7                 | SS 送信データレジスタ 0~3 (SSTDR0~SSTDR3)          | 17-13 |

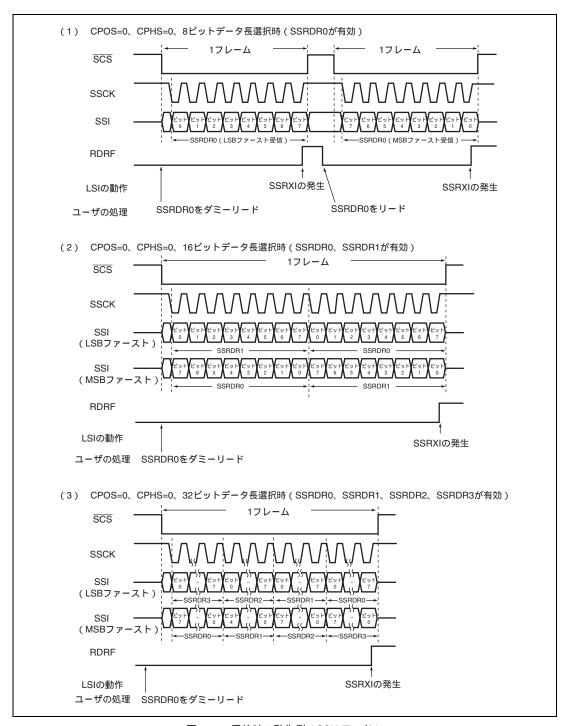

| 17.3.8                 | SS 受信データレジスタ 0~3 ( SSRDR0 ~ SSRDR3 )      | 17-14 |

| 17.3.9                 | SS シフトレジスタ ( SSTRSR )                     | 17-15 |

| 17.4                   | 動作説明                                      | 17-16 |

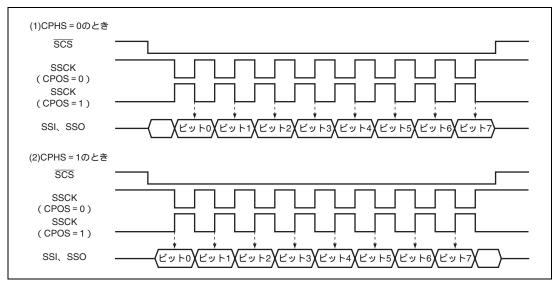

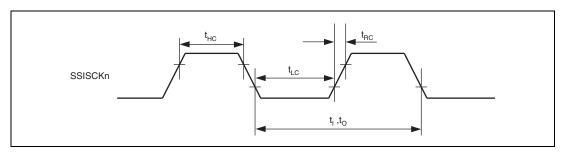

| 17.4.1                 | 転送クロック                                    | 17-16 |

| 17.4.2                 | クロックの位相、極性とデータの関係                         | 17-16 |

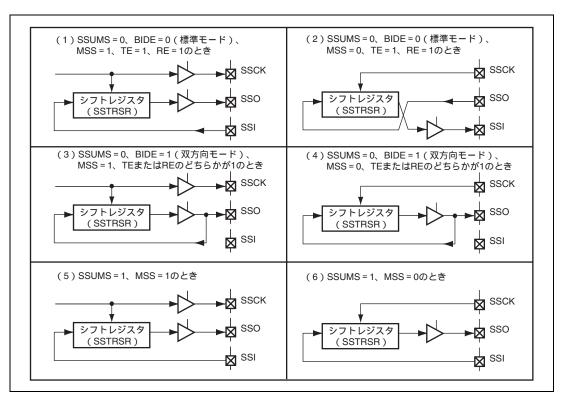

| 17.4.3                 | データ入出力端子とシフトレジスタの関係                       | 17-17 |

| 17.4.4                 | 各通信モードと端子機能                               | 17-18 |

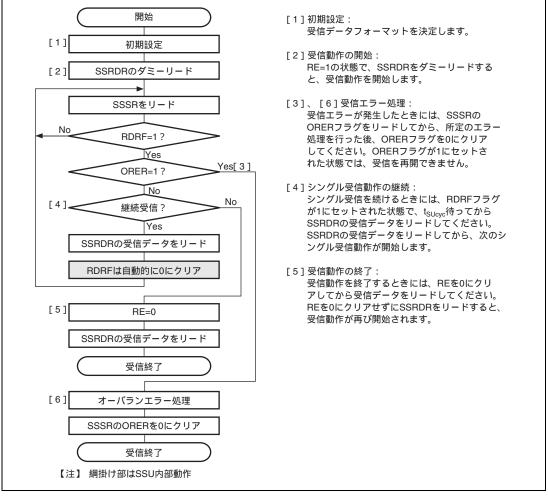

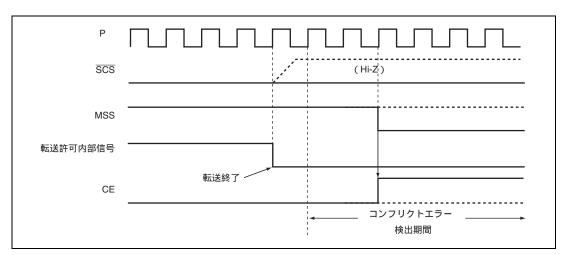

| 17.4.5                 | SSU モード                                   | 17-19 |

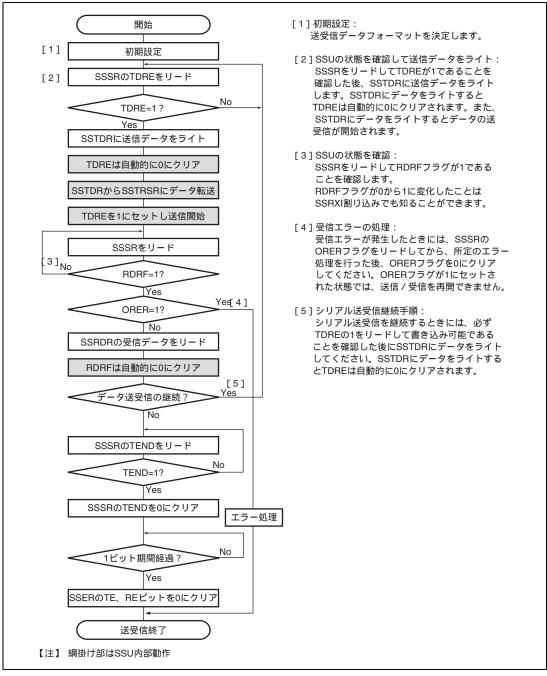

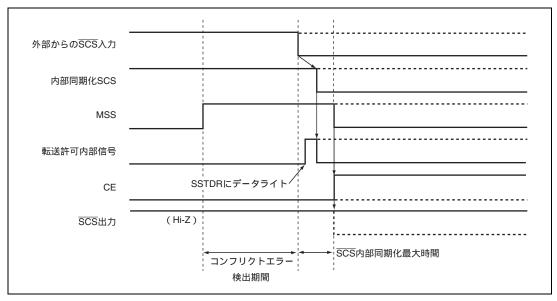

| 17.4.6                 | SCS 端子制御とコンフリクトエラー                        | 17-27 |

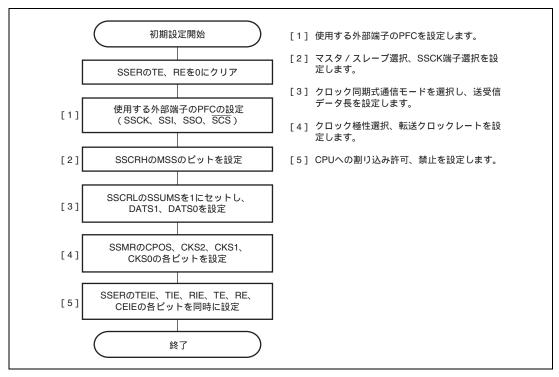

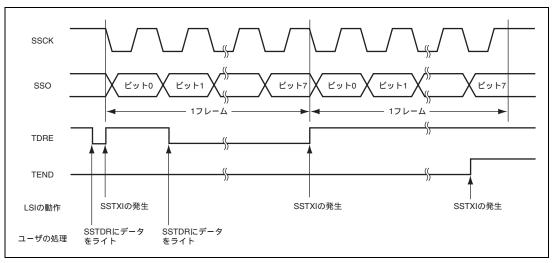

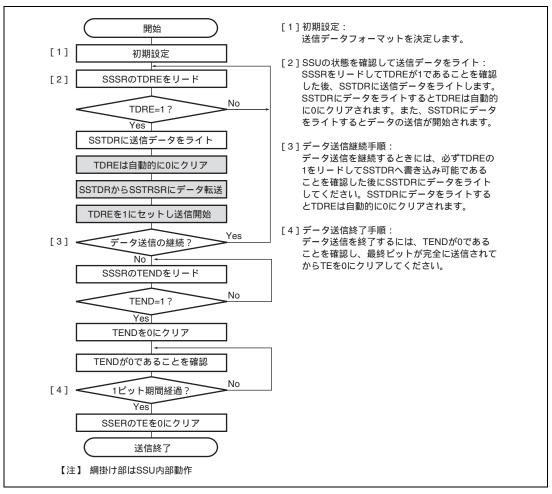

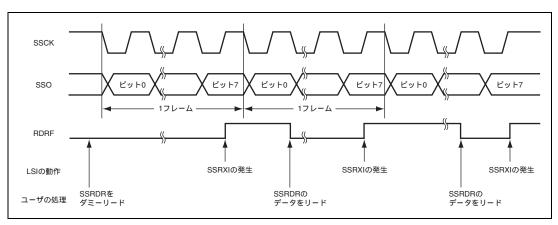

| 17.4.7                 | クロック同期式通信モード                              | 17-28 |

| 17.5                   | SSUの割り込み要因とDMAC                           | 17-34 |

| 17.6                   | 使用上の注意事項                                  | 17-35 |

| 17.6.1                 | モジュールスタンパイモードの設定                          | 17-35 |

| 17.6.2                 | SSU スレープモードにおける連続送受信時の注意事項                | 17-35 |

| 17.6.3                 | SSU モードのマスタ送信動作またはマスタ送受信動作における注意事項        | 17-35 |

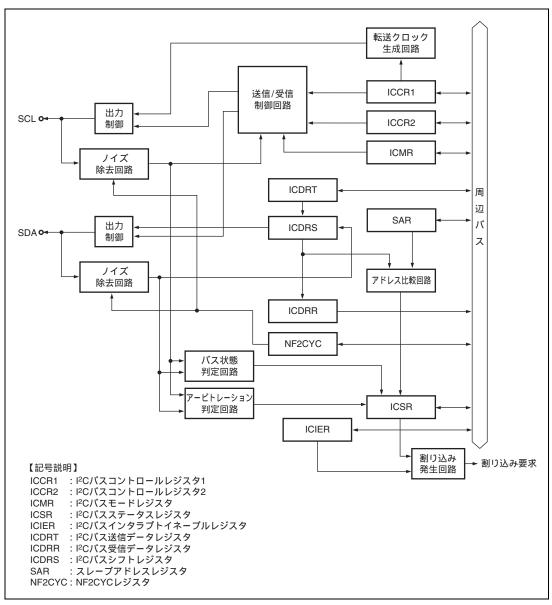

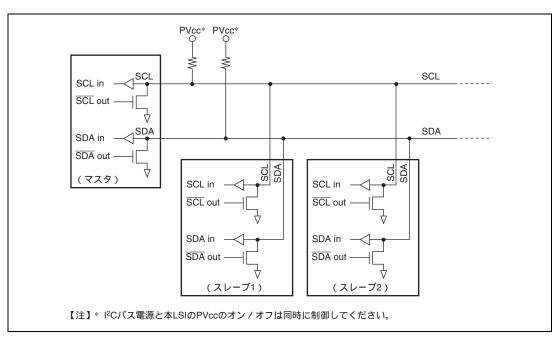

| 18. I <sup>2</sup> C / | パスインタフェース 3 ( IIC3 )                      | 18-1  |

| 18.1                   | 特長                                        | 18-1  |

| 18.2                   | 入出力端子                                     | 18-3  |

| 18.3                   | レジスタの説明                                   | 18-4  |

| 18.3.1                 | I <sup>2</sup> C バスコントロールレジスタ 1 ( ICCR1 ) | 18-5  |

| 18.3.2                 | I <sup>2</sup> C バスコントロールレジスタ 2 ( ICCR2 ) | 18-8  |

| 18.3.3                 | I <sup>2</sup> C バスモードレジスタ ( ICMR )       | 18-9  |

| 18.3.4                 | I¹C バスインタラプトイネーブルレジスタ(ICIER)              | 18-11 |

| 18.3.5                 | I <sup>2</sup> C バスステータスレジスタ ( ICSR )     | 18-13 |

| 18.3.6                 | スレープアドレスレジスタ(SAR)                         | 18-15 |

| 18.3.7                 | I <sup>2</sup> C バス送信データレジスタ(ICDRT)       | 18-15 |

| 18.3.8                 | I <sup>2</sup> C バス受信データレジスタ(ICDRR)       | 18-16 |

| 18.3.9                 | I <sup>2</sup> C バスシフトレジスタ(ICDRS)         | 18-16 |

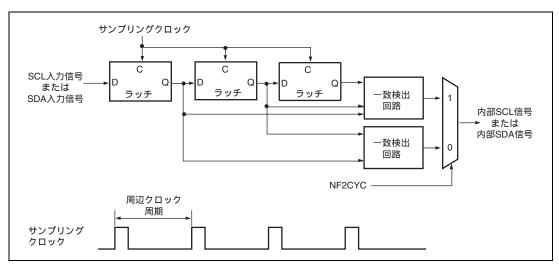

| 18.3.10                | NF2CYC レジスタ(NF2CYC)                       | 18-16 |

| 18.4                   | 動作説明                                      | 18-17 |

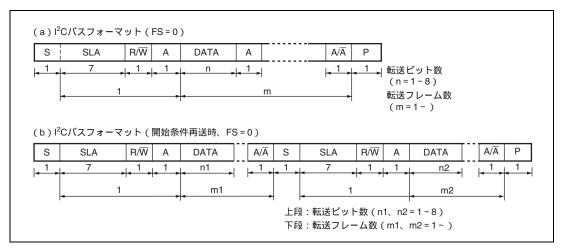

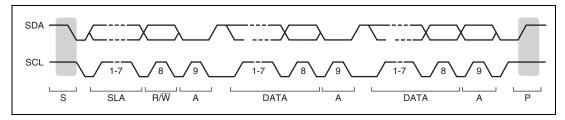

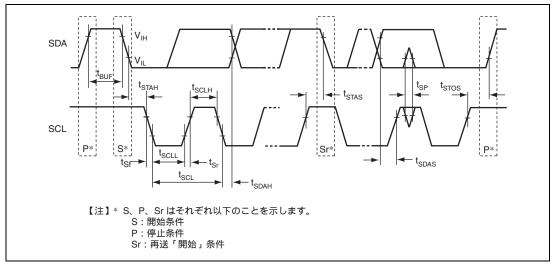

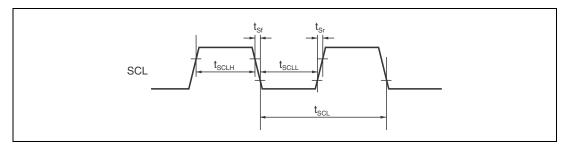

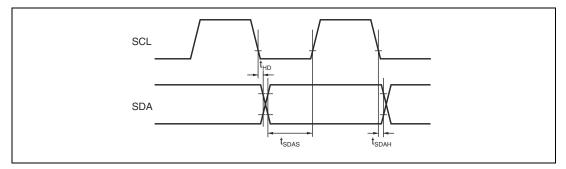

| 18.4.1  | I <sup>2</sup> C バスフォーマット                    | 18-17 |

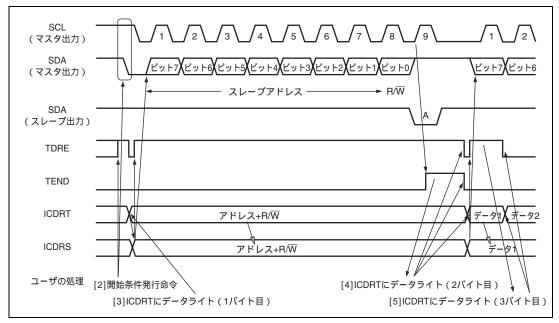

|---------|----------------------------------------------|-------|

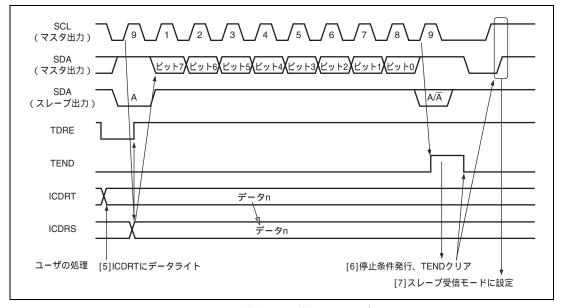

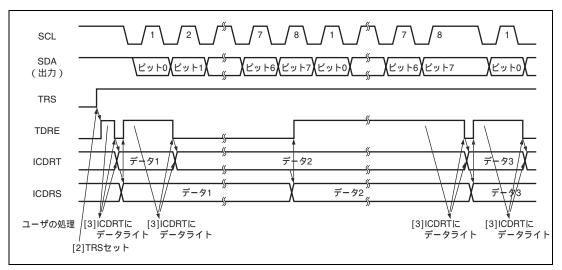

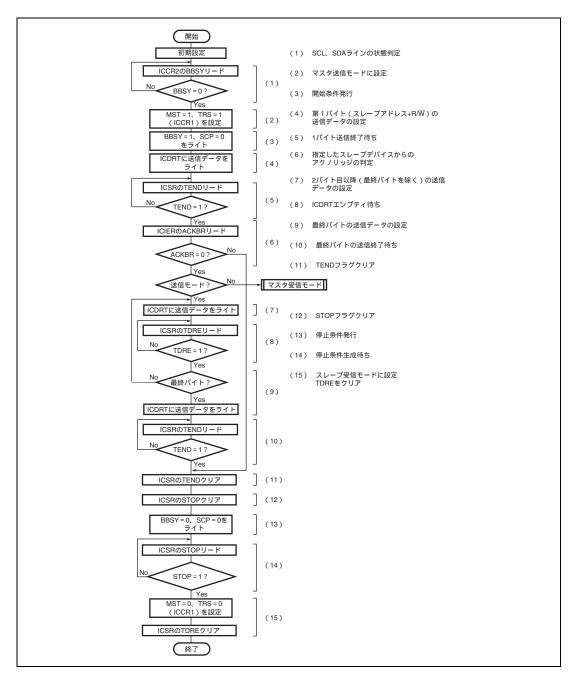

| 18.4.2  | マスタ送信動作                                      | 18-18 |

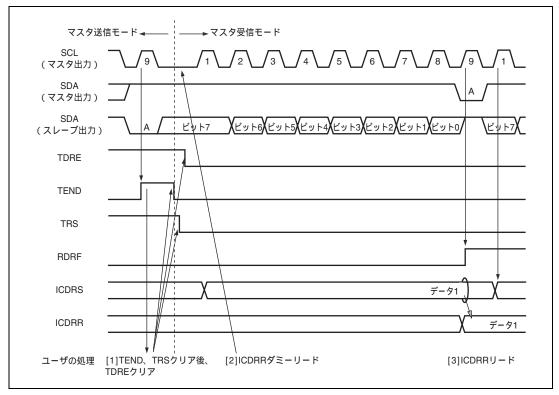

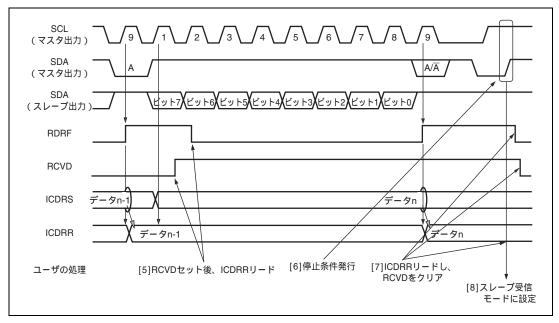

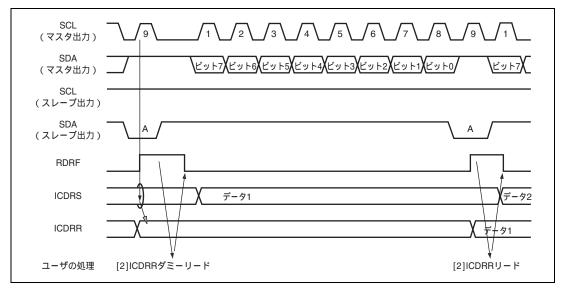

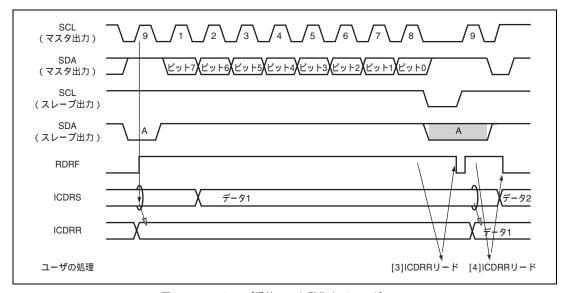

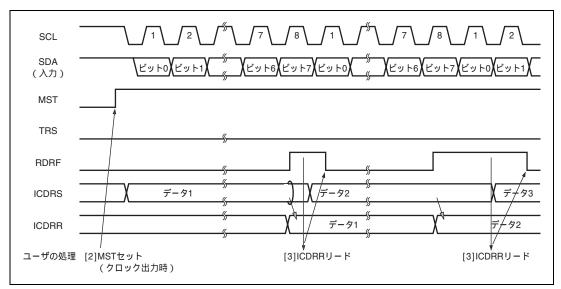

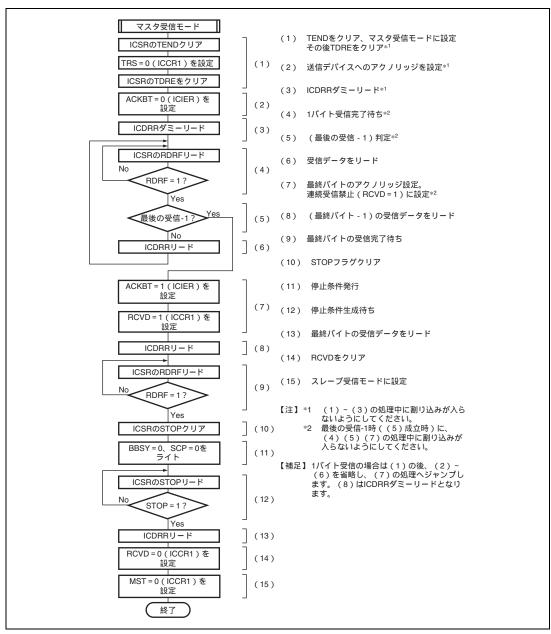

| 18.4.3  | マスタ受信動作                                      | 18-20 |

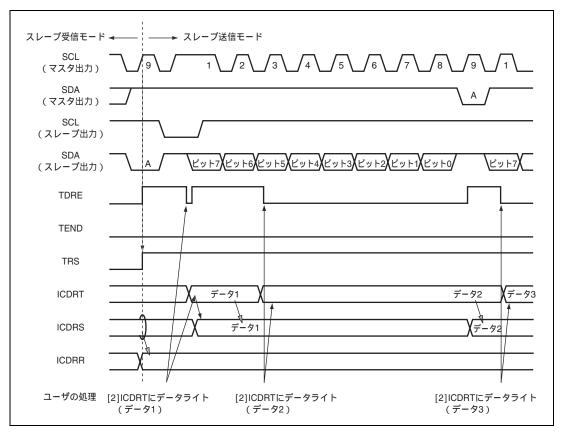

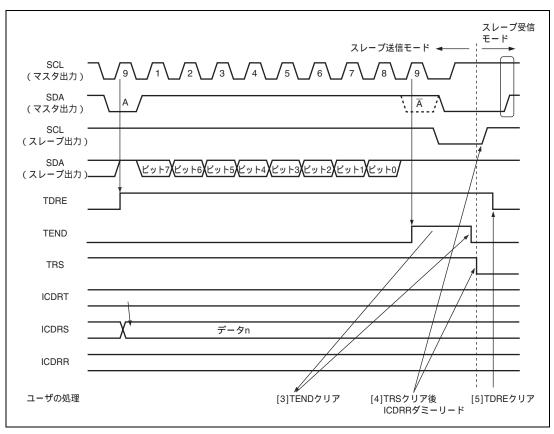

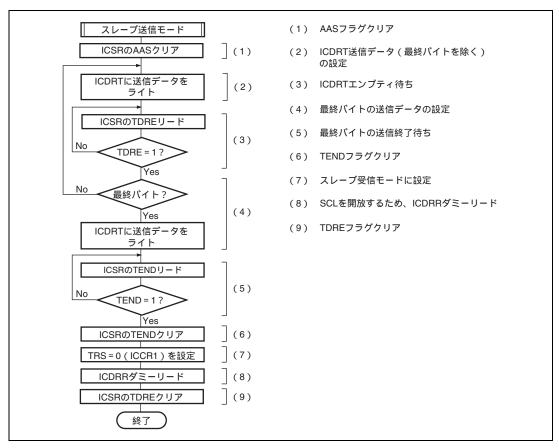

| 18.4.4  | スレーブ送信動作                                     | 18-22 |

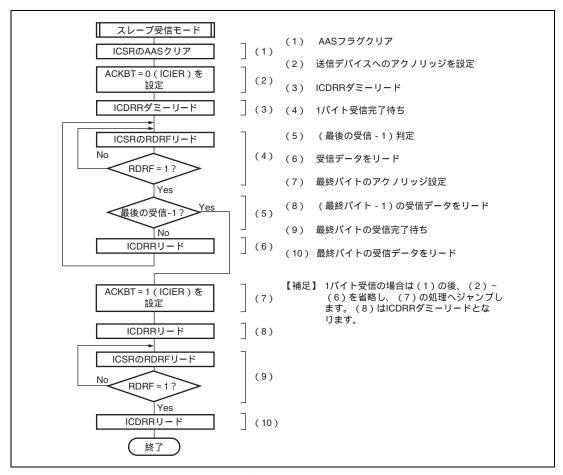

| 18.4.5  | スレープ受信動作                                     | 18-24 |

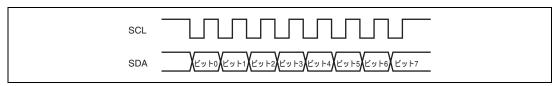

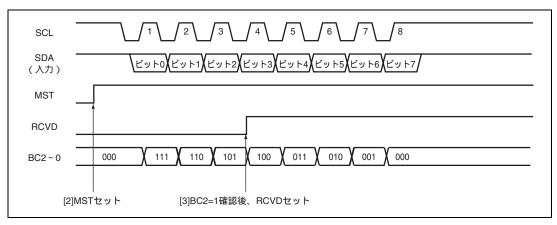

| 18.4.6  | クロック同期式シリアルフォーマット                            | 18-26 |

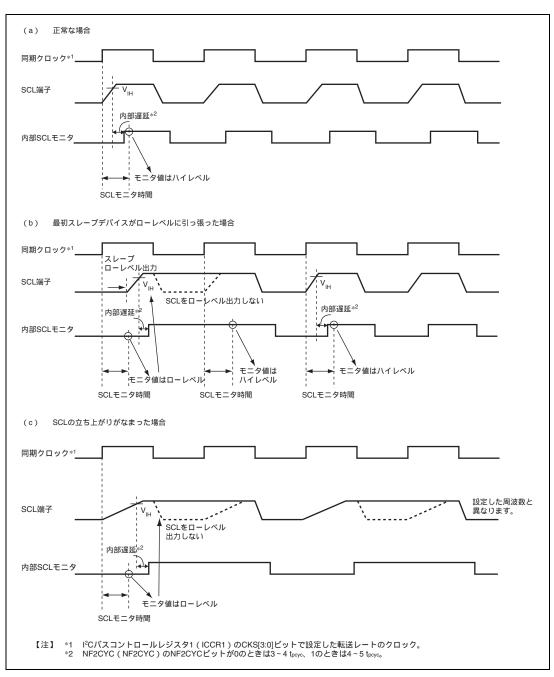

| 18.4.7  | ノイズ除去回路                                      | 18-29 |

| 18.4.8  | 使用例                                          | 18-30 |

| 18.5    | 割り込み要求                                       | 18-34 |

| 18.6    | ビット同期回路                                      | 18-35 |

| 18.7    | 使用上の注意事項                                     | 18-38 |

| 18.7.1  | マルチマスタで使用時の注意                                | 18-38 |

| 18.7.2  | マスタ受信モード時の注意                                 | 18-38 |

| 18.7.3  | マスタ受信モード、ACKBT 設定時の注意                        | 18-38 |

| 18.7.4  | アービトレーションロスト時の MST と TRN ビットの状態についての注意       | 18-38 |

| 18.7.5  | I <sup>2</sup> C バスインタフェースモードのマスタ受信モード時の注意事項 | 18-38 |

| 18.7.6  | IICRST、BBSY ビットに関する注意事項                      | 18-38 |

| 18.7.7  | マスタ送信モード、ACKE ビット = 1 設定時における停止条件発行の注意       | 18-39 |

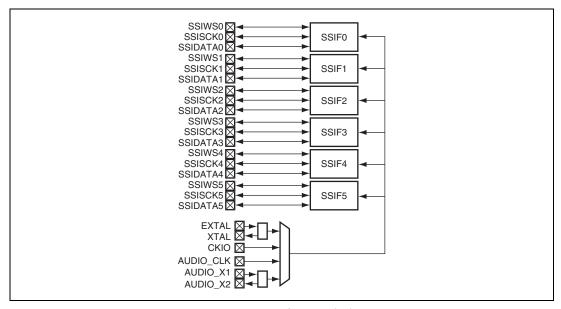

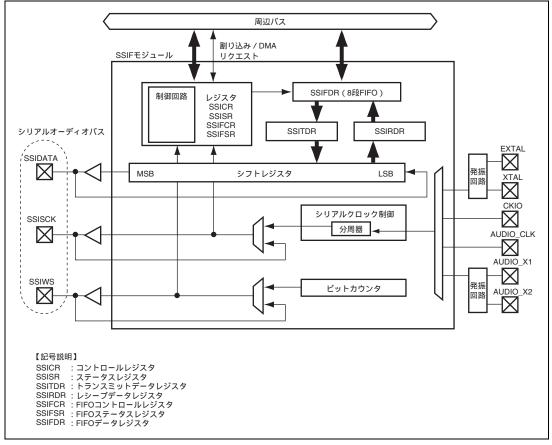

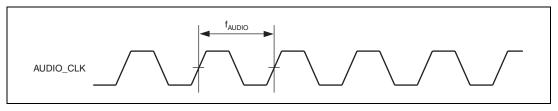

| 19. FIF | O 内蔵シリアルサウンドインタフェース(SSIF )                   | 19-1  |

| 19.1    | 特長                                           |       |

| 19.2    | 入出力端子                                        | 19-4  |

| 19.3    | レジスタの説明                                      | 19-5  |

| 19.3.1  | コントロールレジスタ ( SSICR )                         | 19-6  |

| 19.3.2  | ステータスレジスタ (SSISR)                            |       |

| 19.3.3  | トランスミットデータレジスタ(SSITDR)                       |       |

| 19.3.4  | レシープデータレジスタ ( SSIRDR )                       |       |

| 19.3.5  | FIFO コントロールレジスタ ( SSIFCR )                   |       |

| 19.3.6  |                                              |       |

| 19.3.7  |                                              |       |

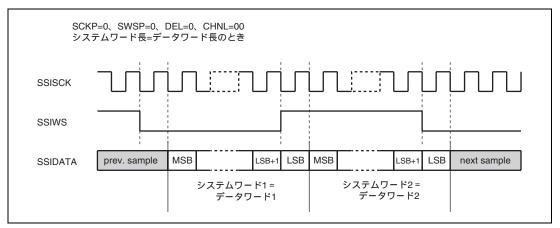

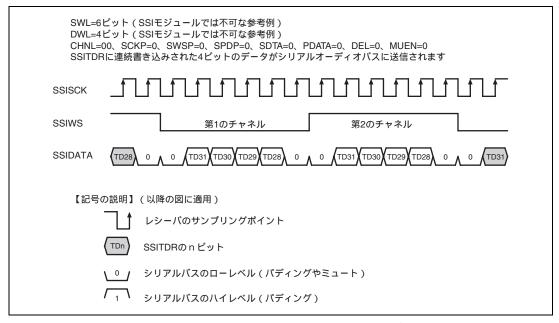

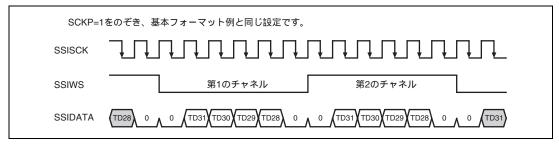

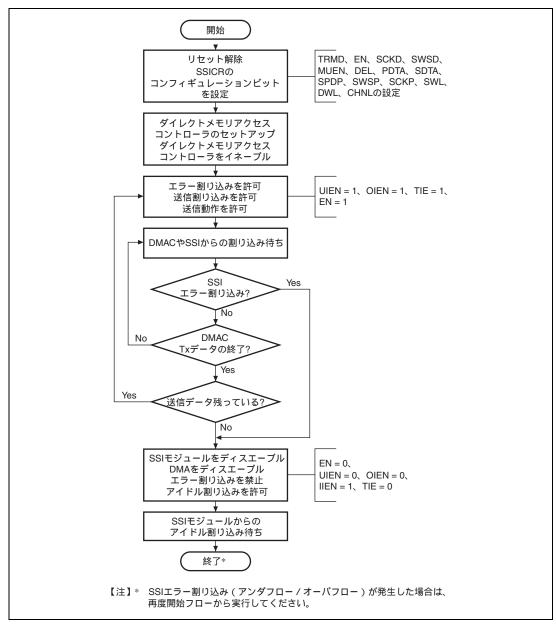

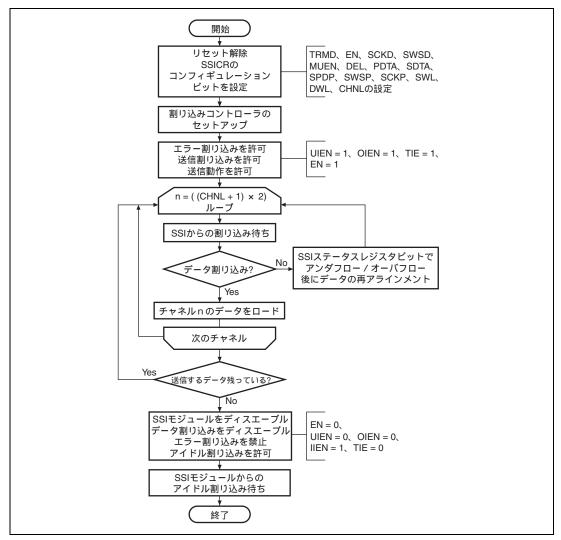

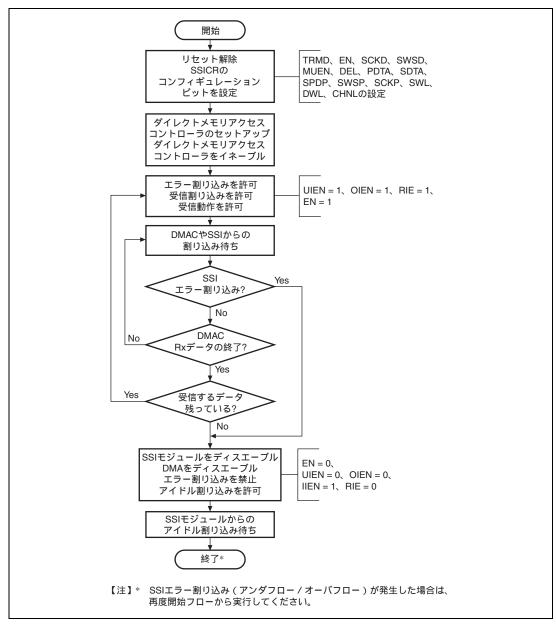

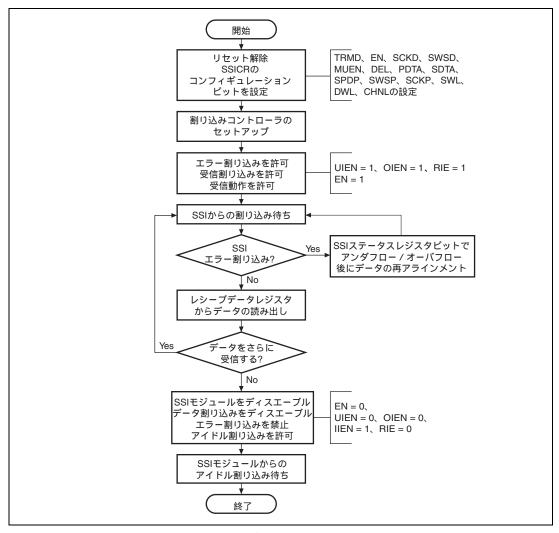

| 19.4    | 動作説明                                         | 19-20 |

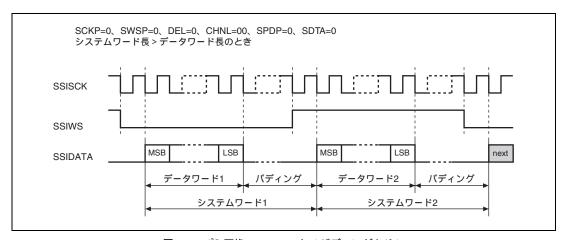

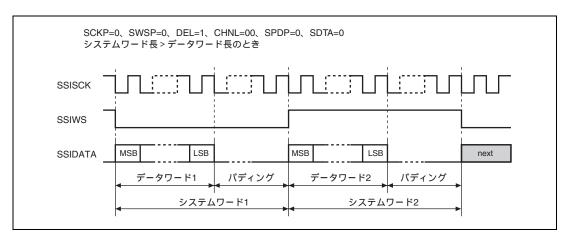

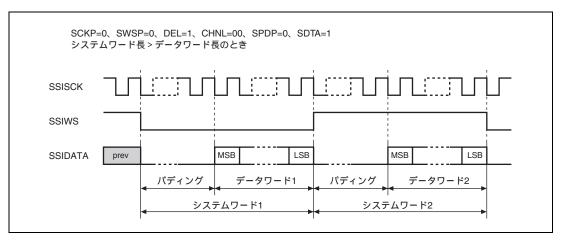

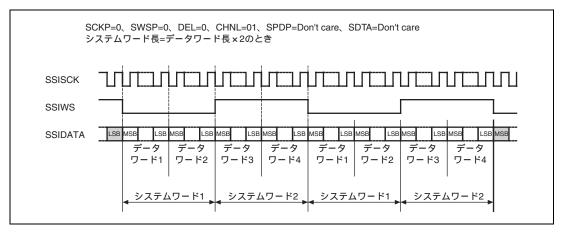

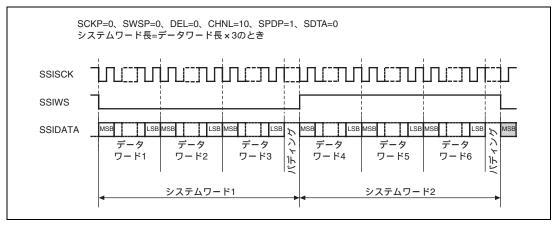

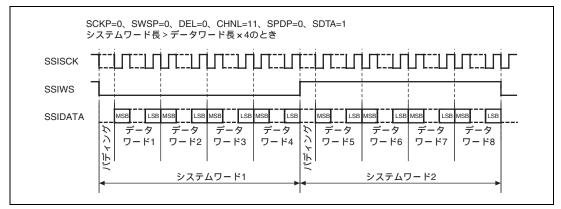

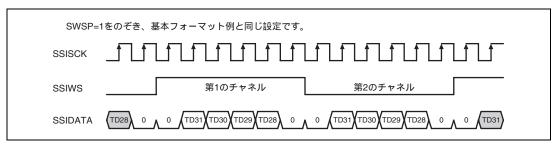

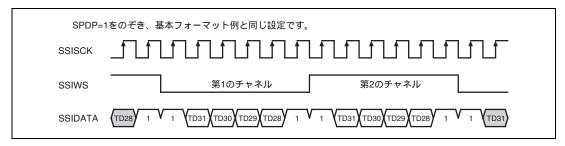

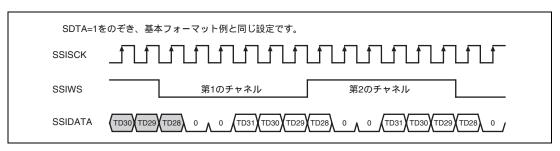

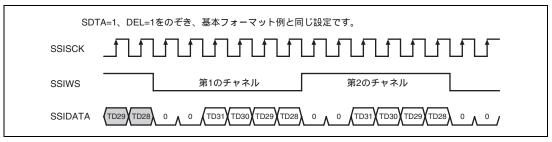

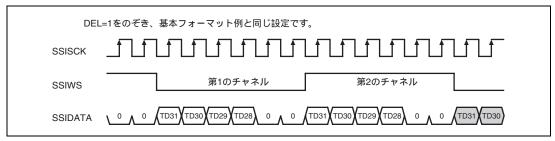

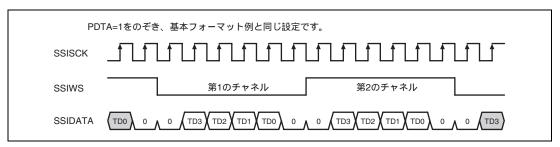

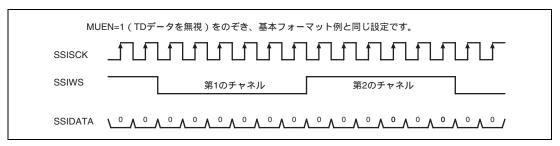

| 19.4.1  | バスフォーマット                                     | 19-20 |

| 19.4.2  | 非圧縮モード                                       | 19-20 |

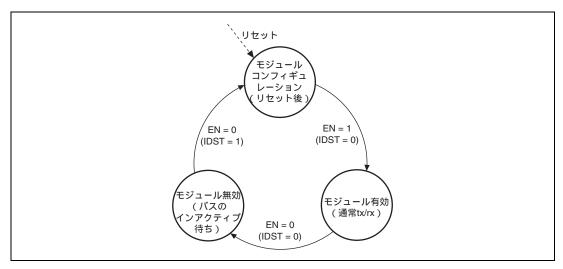

| 19.4.3  | 動作モード                                        | 19-28 |

| 19.4.4  |                                              |       |

| 19.4.5  | 受信動作                                         | 19-31 |

| 19.4.6  | シリアルビットクロックコントロール                            | 19-34 |

| 19.5    | 使用上の注意事項                                     | 19-34 |

| 19.5.1  | DMA 動作中にアンダフローまたはオーバフローが起こった場合の制限事項          |       |

| 20. 🗆  | ソトローラエリアネットワーク(RCAN-TL1)                       | 20-1  |

|--------|------------------------------------------------|-------|

| 20.1   | 特長                                             | 20-2  |

| 20.1.1 | RCAN-TL1 の特長                                   | 20-2  |

| 20.1.2 | 本マイコンにおける特長                                    | 20-2  |

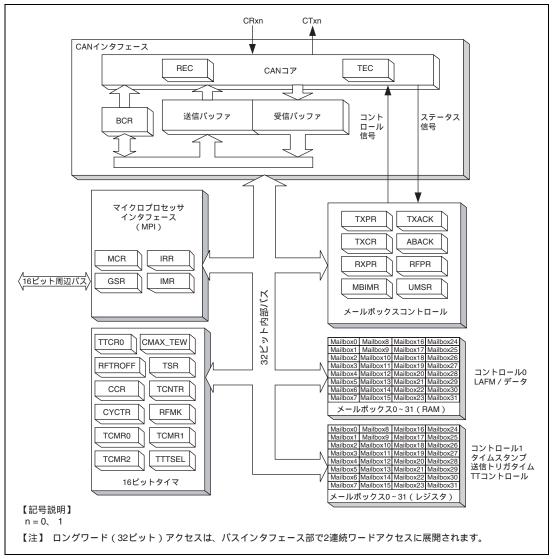

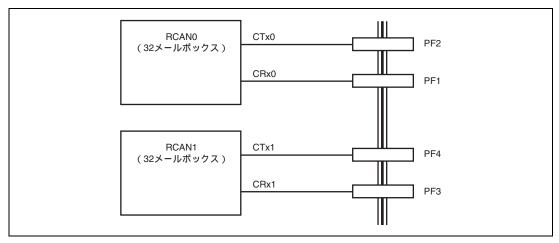

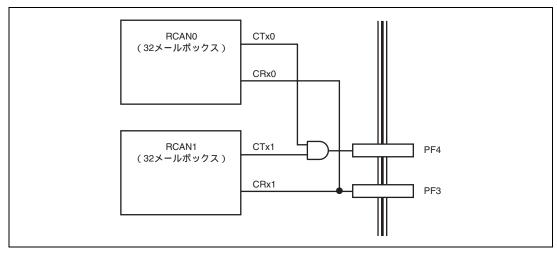

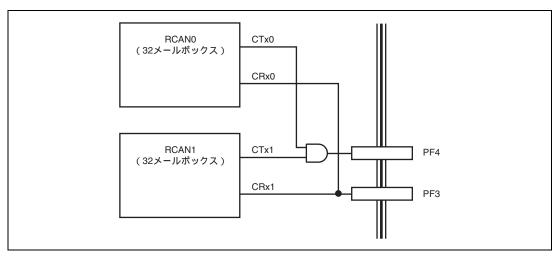

| 20.2   | 構成                                             | 20-3  |

| 20.2.1 | ブロック図                                          | 20-3  |

| 20.2.2 | 各ブロックの機能                                       | 20-4  |

| 20.2.3 | 端子構成                                           | 20-5  |

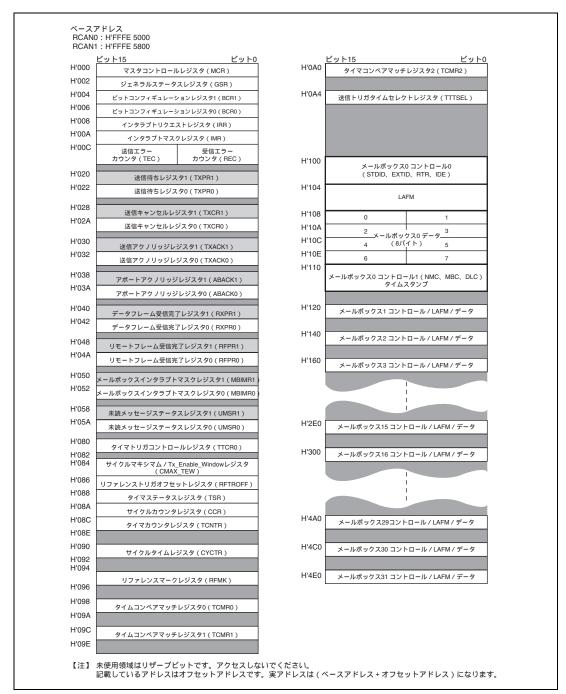

| 20.2.4 | メモリマップ                                         | 20-6  |

| 20.3   | メールボックス                                        | 20-7  |

| 20.3.1 | メールボックスの構成                                     | 20-7  |

| 20.3.2 | メッセージコントロールフィールド                               | 20-12 |

| 20.3.3 | ローカルアクセプタンスフィルタマスク(LAFM)                       | 20-17 |

| 20.3.4 | メッセージデータフィールド                                  | 20-18 |

| 20.3.5 | タイムスタンプ                                        | 20-19 |

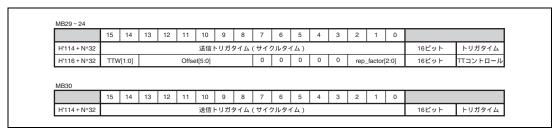

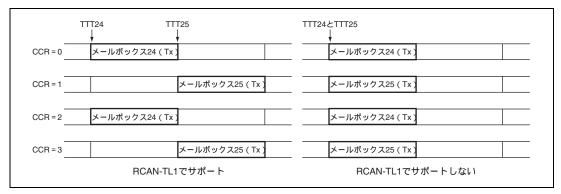

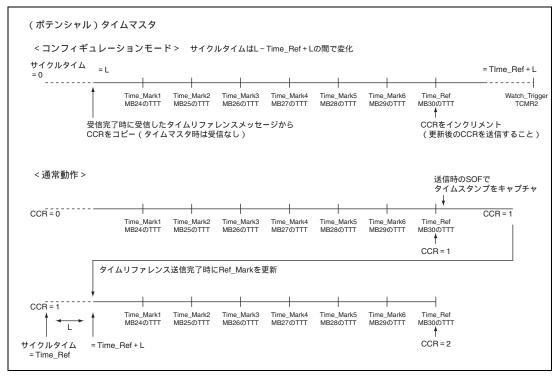

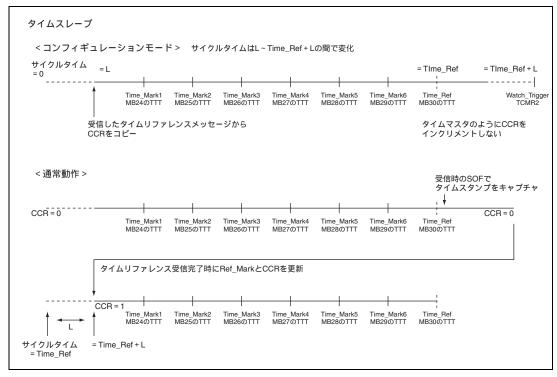

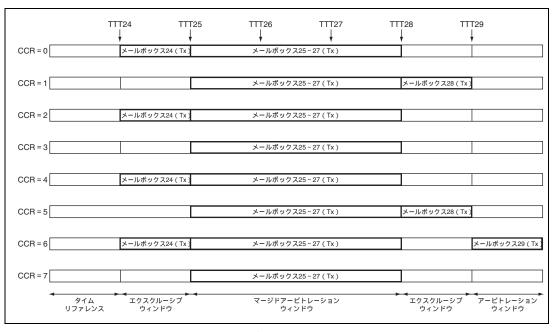

| 20.3.6 | 送信トリガタイム(TTT)とタイムトリガコントロール                     | 20-20 |

| 20.4   | RCAN-TL1のコントロールレジスタ                            | 20-24 |

| 20.4.1 | マスタコントロールレジスタ(MCR)                             | 20-24 |

| 20.4.2 | ジェネラルステータスレジスタ ( GSR )                         | 20-30 |

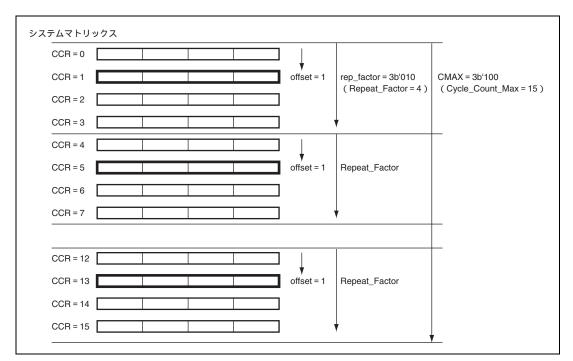

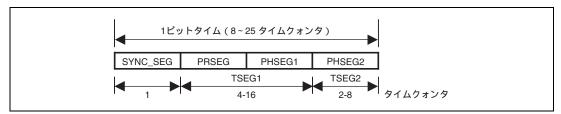

| 20.4.3 | ビットコンフィギュレーションレジスタ 0、1 (BCR0、BCR1)             | 20-32 |

| 20.4.4 | インタラプトリクエストレジスタ(IRR)                           | 20-36 |

| 20.4.5 | インタラプトマスクレジスタ(IMR)                             | 20-43 |

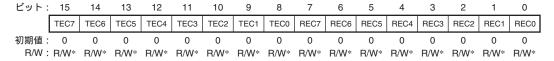

| 20.4.6 | 送信エラーカウンタ(TEC) / 受信エラーカウンタ(REC)                | 20-43 |

| 20.5   | RCAN-TL1のメールボックスレジスタ                           | 20-44 |

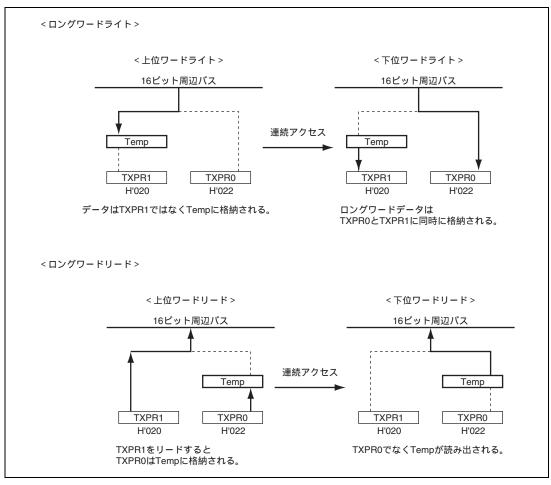

| 20.5.1 | 送信待ちレジスタ 1、0 ( TXPR1、TXPR0 )                   | 20-45 |

| 20.5.2 | 送信キャンセルレジスタ 1、0 ( TXCR1、TXCR0 )                | 20-48 |

| 20.5.3 | 送信アクノリッジレジスタ 1、0 (TXACK1、TXACK0)               | 20-50 |

| 20.5.4 | アボートアクノリッジレジスタ 1、0 ( ABACK1、ABACK0 )           | 20-51 |

| 20.5.5 | データフレーム受信完了レジスタ 1、0(RXPR1、RXPR0)               | 20-52 |

| 20.5.6 | リモートフレーム受信完了レジスタ 1、0(RFPR1、RFPR0)              | 20-53 |

| 20.5.7 | メールボックスインタラプトマスクレジスタ 1、0(MBIMR1、MBIMR0)        | 20-54 |

| 20.5.8 | 未読メッセージステータスレジスタ 1、0(UMSR1、UMSR0)              | 20-55 |

| 20.6   | タイマレジスタ                                        |       |

| 20.6.1 |                                                |       |

| 20.6.2 | サイクルマキシマム / Tx_Enable_Window レジスタ ( CMAX_TEW ) | 20-59 |

| 20.6.3 | リファレンストリガオフセットレジスタ(RFTROFF)                    | 20-60 |

| 20.6.4 | ,                                              |       |

| 20.6.5 |                                                |       |

| 20.6.6 | ,                                              |       |

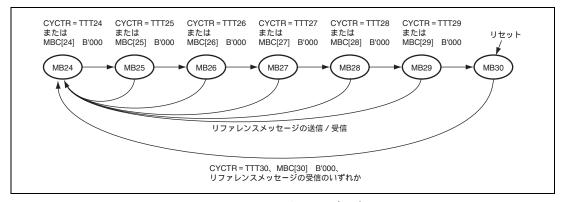

| 20.6.7 | サイクルタイムレジスタ(CYCTR)                             | 20-65 |

| 20.6.8  | リファレンスマークレジスタ(RFMK)                 | 20-65 |

|---------|-------------------------------------|-------|

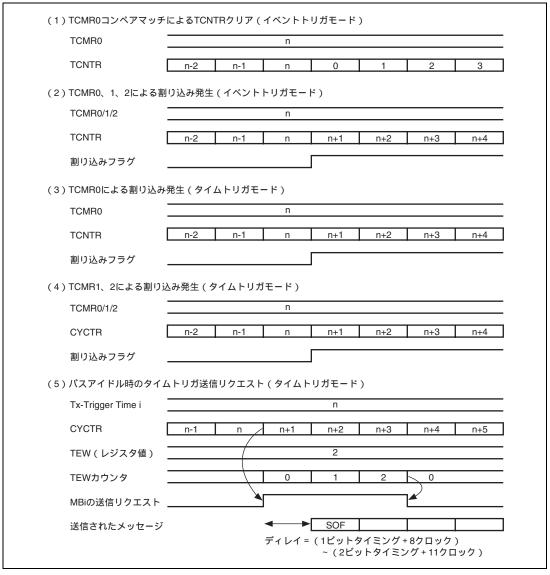

| 20.6.9  | タイマコンペアマッチレジスタ 0~2 ( TCMR0~2 )      | 20-66 |

| 20.6.1  | 0 送信トリガタイムセレクトレジスタ(TTTSEL)          | 20-68 |

| 20.7    | 動作説明                                | 20-69 |

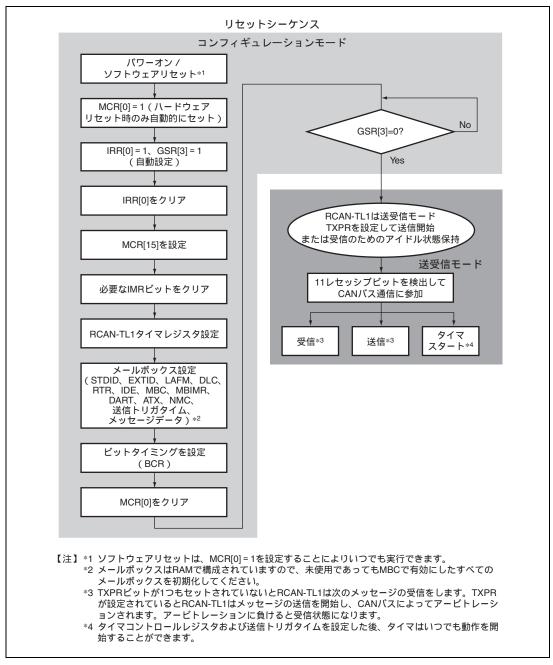

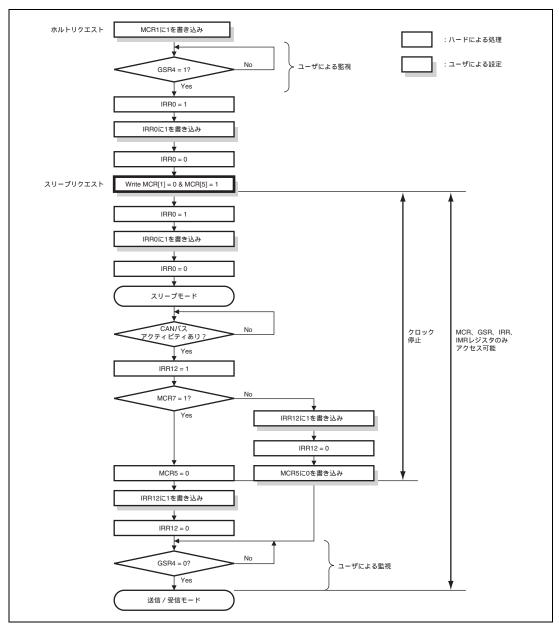

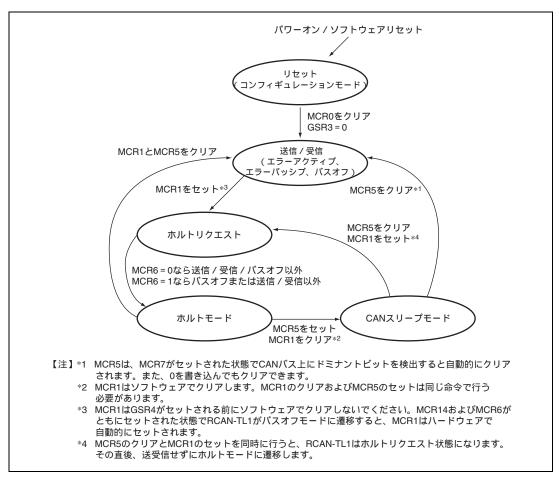

| 20.7.1  | RCAN-TL1 の設定                        | 20-69 |

| 20.7.2  | テストモードの設定                           | 20-75 |

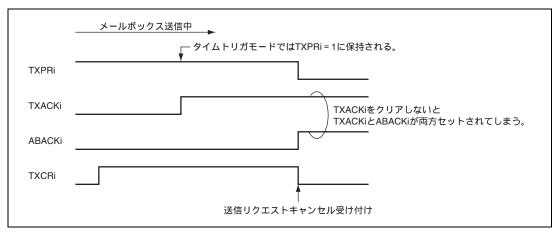

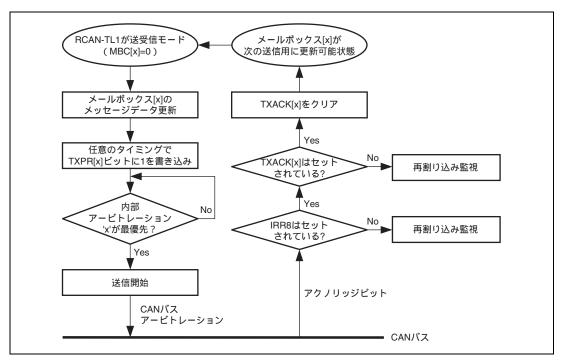

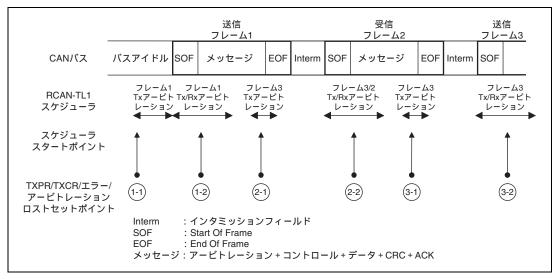

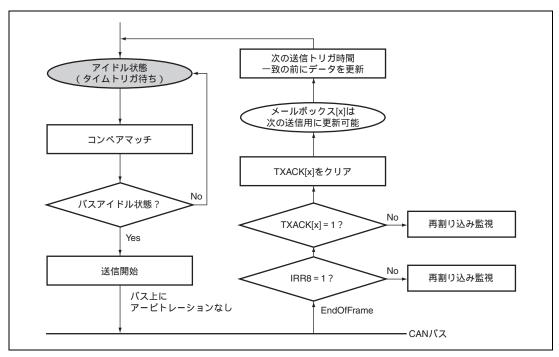

| 20.7.3  | メッセージ送信シーケンス                        | 20-77 |

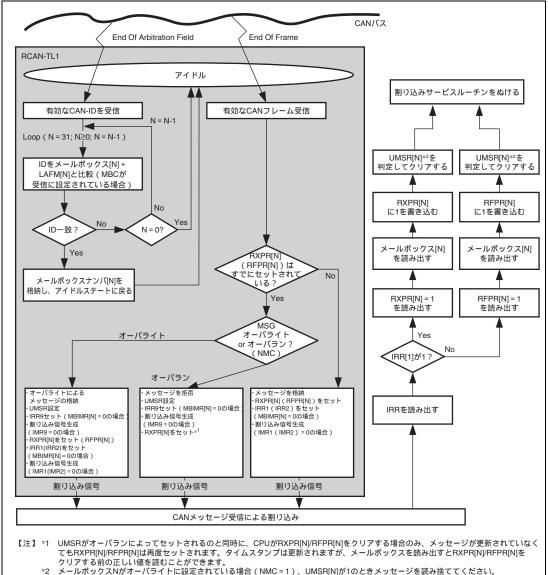

| 20.7.4  | メッセージ受信シーケンス                        | 20-89 |

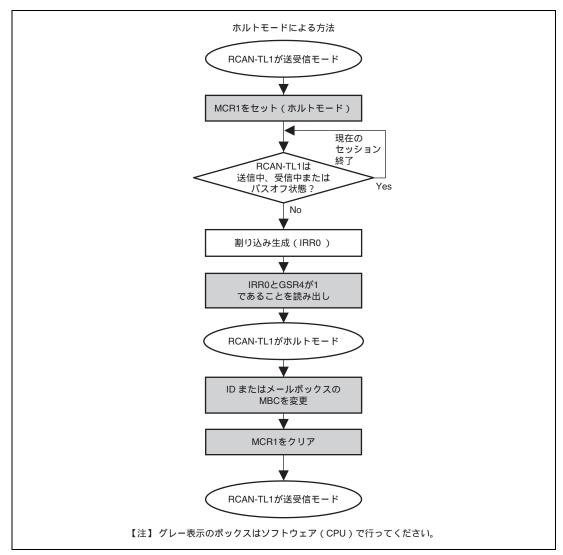

| 20.7.5  | メールボックスの再設定                         | 20-91 |

| 20.8    | 割り込み要因                              | 20-93 |

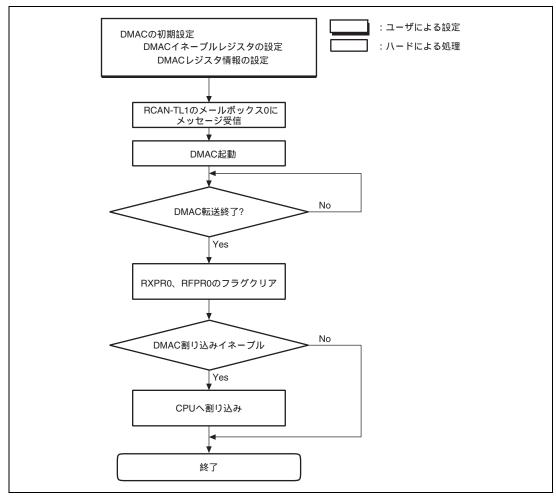

| 20.9    | DMACインタフェース                         | 20-94 |

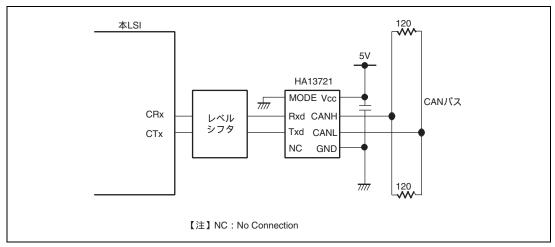

| 20.10   | CANバスインタフェース                        | 20-95 |

| 20.11   | RCAN-TL1端子ポート設定                     | 20-96 |

| 20.12   | 使用上の注意事項                            |       |

| 20.12.  | 1 1 チャネル 64 メールボックスでのポート設定についての注意事項 | 20-97 |

| 21. IEE | Bus <sup>™</sup> コントローラ(IEB)        | 21-1  |

| 21.1    | 特長                                  | 21-1  |

| 21.1.1  | IEBus 通信プロトコル                       | 21-2  |

| 21.1.2  | 伝送プロトコル                             | 21-4  |

| 21.1.3  | 伝送データ(データフィールドの内容)                  | 21-10 |

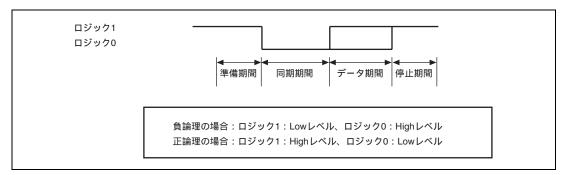

| 21.1.4  | ビットフォーマット                           | 21-13 |

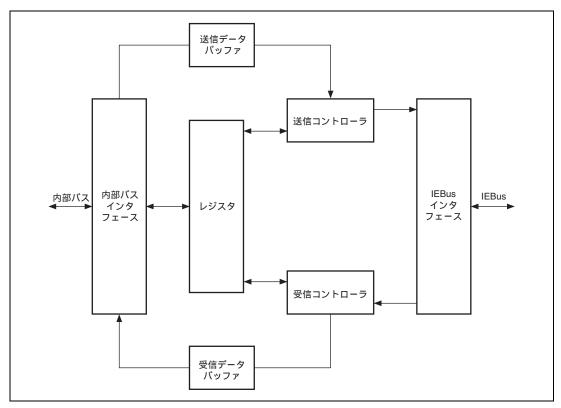

| 21.1.5  | 構成                                  | 21-14 |

| 21.2    | 入出力端子                               | 21-15 |

| 21.3    | レジスタの説明                             | 21-16 |

| 21.3.1  | IEBus コントロールレジスタ(IECTR)             | 21-17 |

| 21.3.2  | IEBus コマンドレジスタ(IECMR)               | 21-18 |

| 21.3.3  | IEBus マスタコントロールレジスタ(IEMCR)          | 21-19 |

| 21.3.4  | IEBus 自局アドレスレジスタ 1(IEAR1)           | 21-21 |

| 21.3.5  | IEBus 自局アドレスレジスタ 2 ( IEAR2 )        | 21-22 |

| 21.3.6  | IEBus スレープアドレス設定レジスタ 1(IESA1)       | 21-22 |

| 21.3.7  | IEBus スレープアドレス設定レジスタ 2(IESA2)       | 21-23 |

| 21.3.8  | IEBus 送信電文長レジスタ(IETBFL)             | 21-23 |

| 21.3.9  | IEBus 受信マスタアドレスレジスタ 1(IEMA1)        | 21-24 |

| 21.3.1  | 0 IEBus 受信マスタアドレスレジスタ 2(IEMA2)      | 21-24 |

| 21.3.1  | 1 IEBus 受信コントロールフィールドレジスタ(IERCTL)   | 21-25 |

| 21.3.1  | 2 IEBus 受信電文長レジスタ(IERBFL)           | 21-25 |

| 21.3.1  | 3 IEBus ロックアドレスレジスタ 1 ( IELA1 )     | 21-26 |

| 21.3.1  | 4 IEBus ロックアドレスレジスタ 2(IELA2)        | 21-26 |

| 21.3.1  | 5 IEBus ゼネラルフラグレジスタ(IEFLG)          | 21-27 |

| 21.3.16 | iEBus 送信ステータスレジスタ(IETSR)                 | 21-29 |

|---------|------------------------------------------|-------|

| 21.3.17 | 「IEBus 送信割り込み許可レジスタ(IEIET)               | 21-31 |

| 21.3.18 | IEBus 受信ステータスレジスタ(IERSR)                 | 21-32 |

| 21.3.19 | IEBus 受信割り込み許可レジスタ(IEIER)                | 21-35 |

| 21.3.20 | IEBus クロック選択レジスタ(IECKSR)                 | 21-36 |

| 21.3.21 | IEBus 送信データバッファ 001~128(IETB001~IETB128) | 21-37 |

| 21.3.22 | IEBus 受信データバッファ 001~128(IERB001~IERB128) | 21-37 |

| 21.4    | データフォーマット                                | 21-38 |

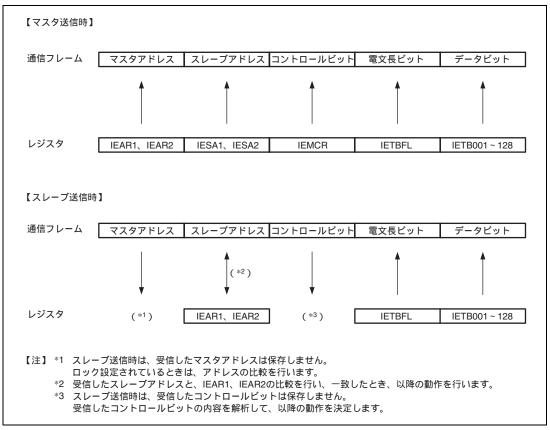

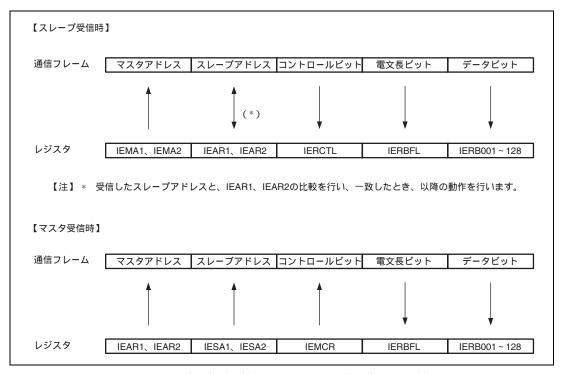

| 21.4.1  | 送信フォーマット                                 | 21-38 |

| 21.4.2  | 受信フォーマット                                 | 21-39 |

| 21.5    | ソフト制御フロー                                 | 21-40 |

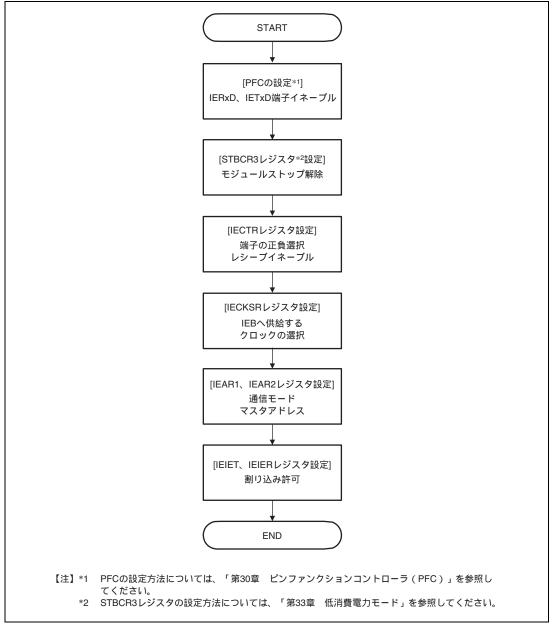

| 21.5.1  | 初期設定                                     | 21-40 |

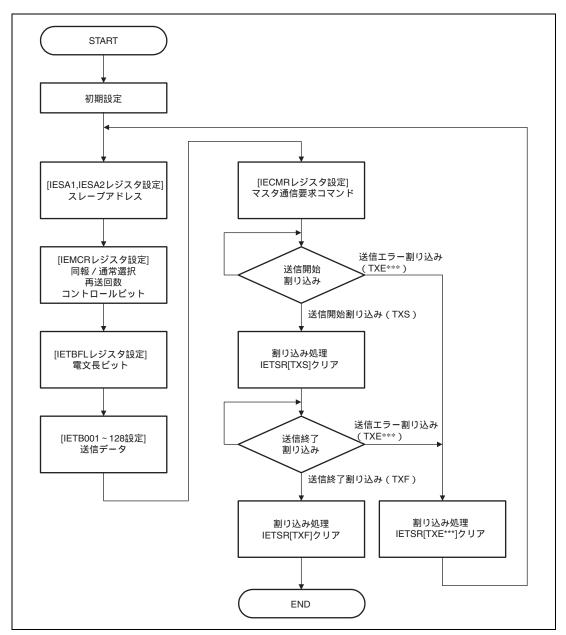

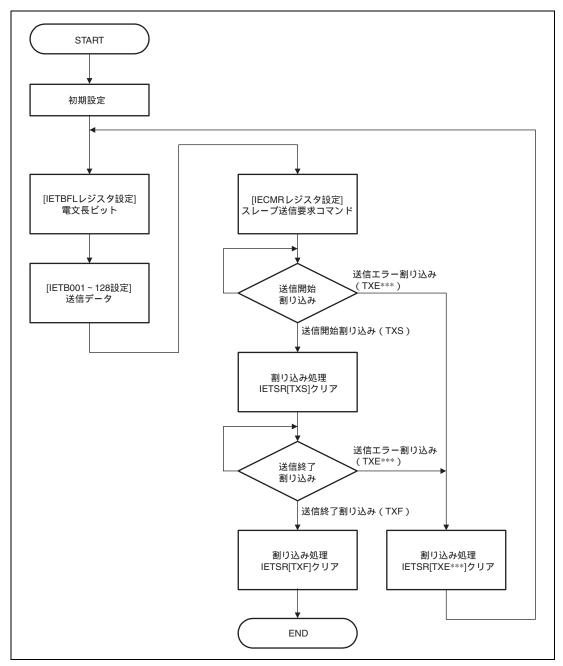

| 21.5.2  | マスタ送信                                    | 21-41 |

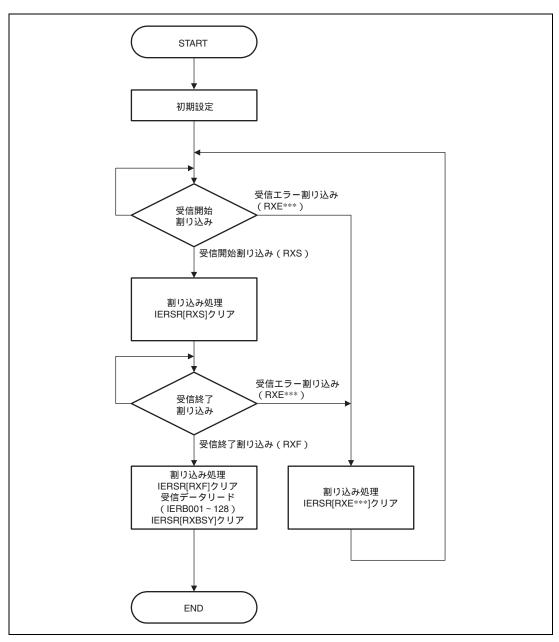

| 21.5.3  | スレープ受信                                   | 21-42 |

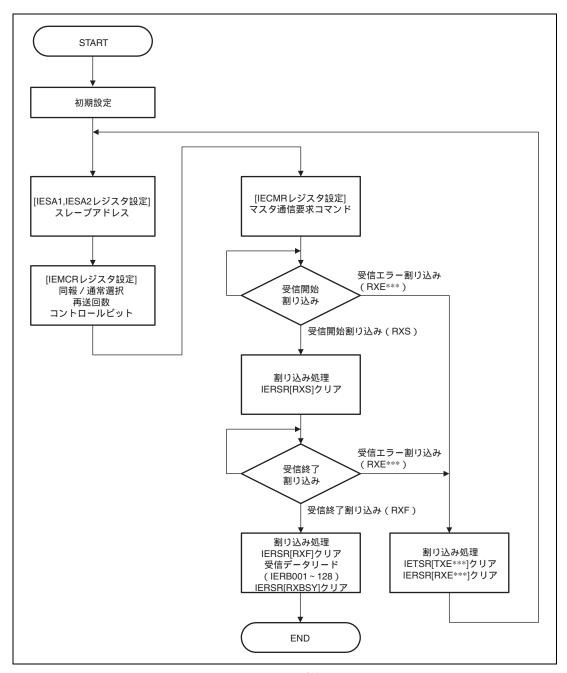

| 21.5.4  | マスタ受信                                    | 21-43 |

| 21.5.5  | スレーブ送信                                   | 21-44 |

| 21.6    | 動作タイミング                                  | 21-45 |

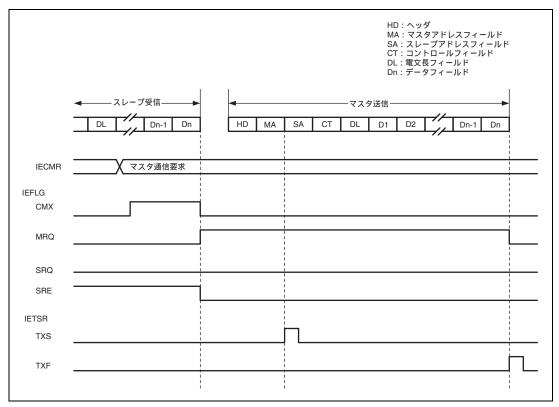

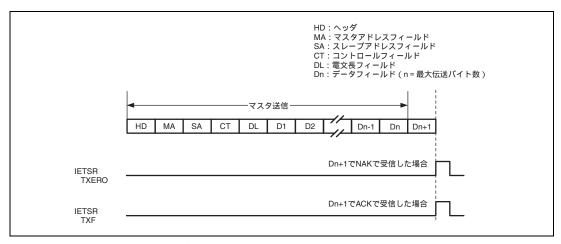

| 21.6.1  | マスタ送信                                    | 21-45 |

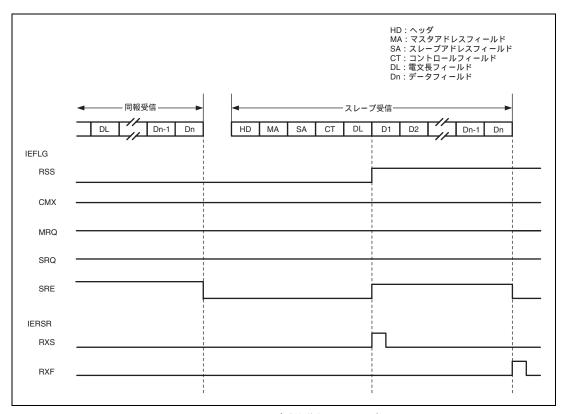

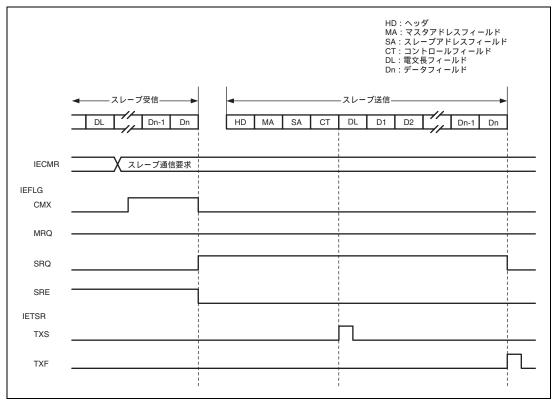

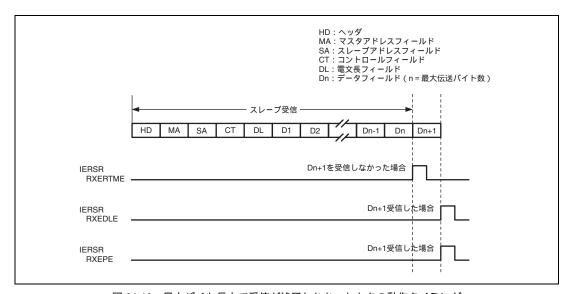

| 21.6.2  | スレープ受信                                   | 21-46 |

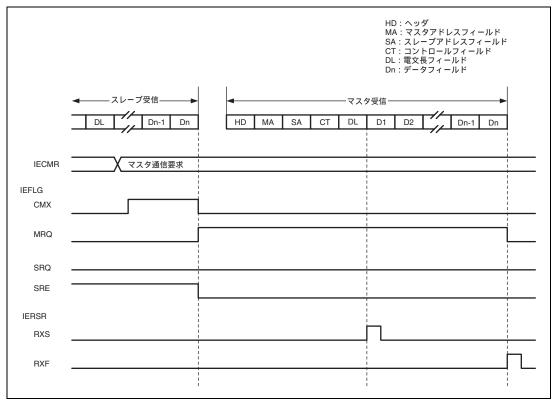

| 21.6.3  | マスタ受信                                    | 21-47 |

| 21.6.4  | スレーブ送信                                   | 21-48 |

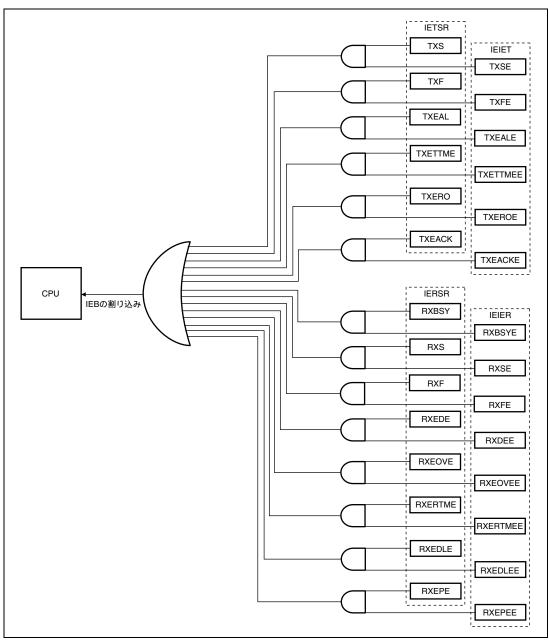

| 21.7    | 割り込み要因                                   | 21-49 |

| 21.8    | 使用上の注意事項                                 | 21-51 |

| 21.8.1  | 最大伝送バイト長内で通信が終了しなかったときの注意事項              | 21-51 |

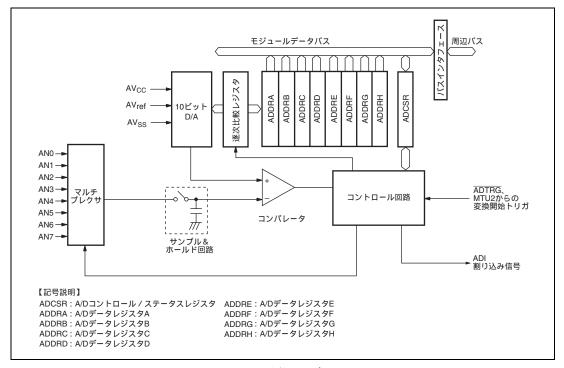

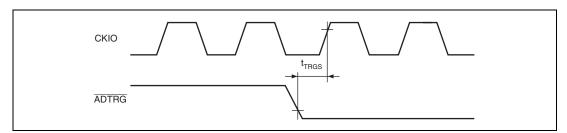

| 22. A/D | 变換器(ADC)                                 | 22-1  |

| 22.1    | 特長                                       | 22-1  |

| 22.2    | 入出力端子                                    | 22-3  |

| 22.3    | レジスタの説明                                  | 22-3  |

| 22.3.1  | A/D データレジスタ A~H(ADDRA~ADDRH)             | 22-4  |

| 22.3.2  | A/D コントロール / ステータスレジスタ ( ADCSR )         | 22-4  |

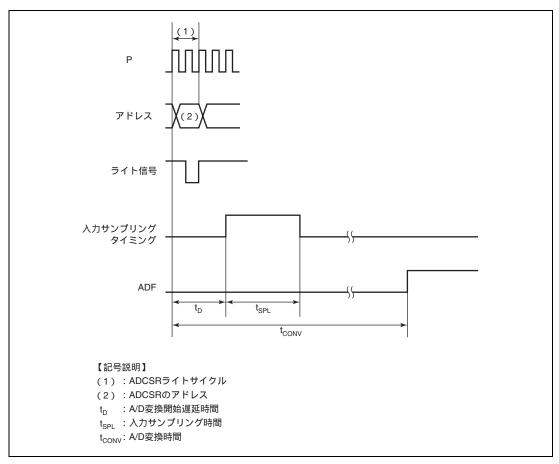

| 22.4    | 動作説明                                     | 22-7  |

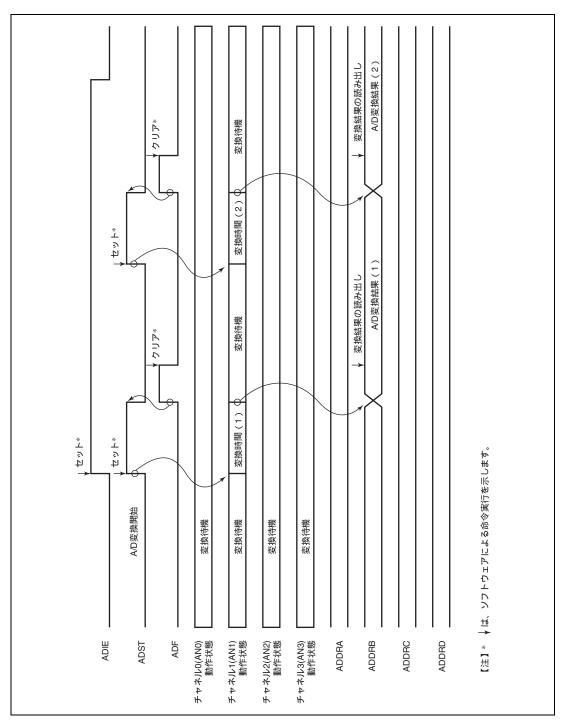

| 22.4.1  | シングルモード                                  | 22-7  |

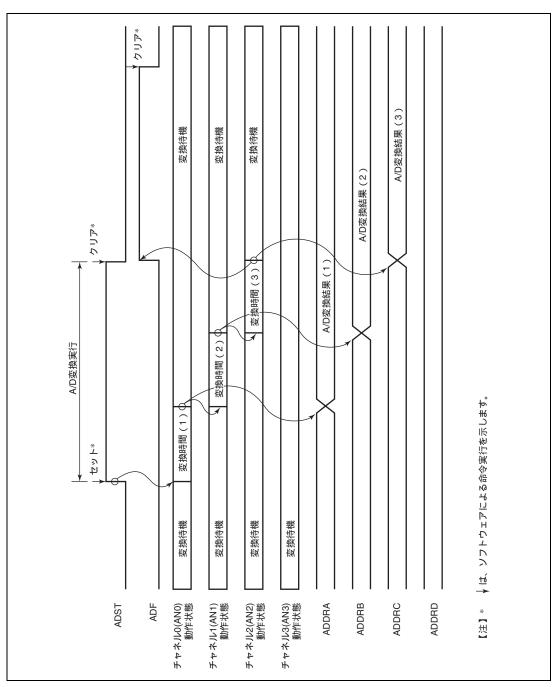

| 22.4.2  | マルチモード                                   | 22-9  |

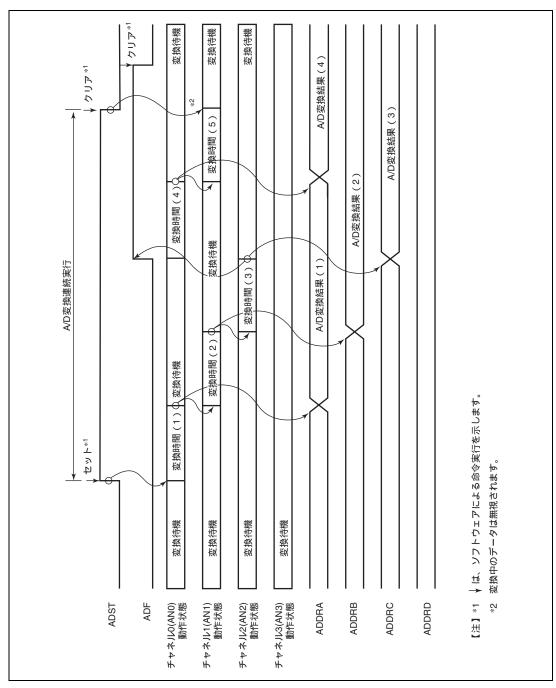

| 22.4.3  | スキャンモード                                  |       |

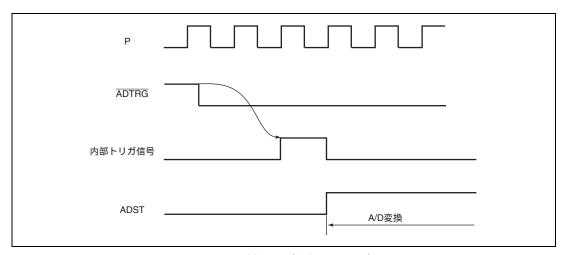

| 22.4.4  | 外部トリガ、MTU2 による A/D 変換器の起動                | 22-13 |

| 22.4.5  | 入力サンプリングと A/D 変換時間                       | 22-13 |

| 22.5    | 割り込み要因とDMAC転送要求                          | 22-16 |

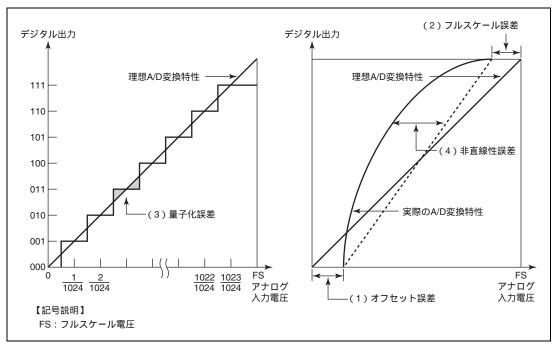

| 22.6    | A/D変換精度の定義                               | 22-17 |

| 22.7    | 使用上の注意事項                                 | 22-18 |

| 22.7.1         | モジュールスタンバイモードの設定                 | 22-18 |

|----------------|----------------------------------|-------|

| 22.7.2         | アナログ電圧の設定                        | 22-18 |

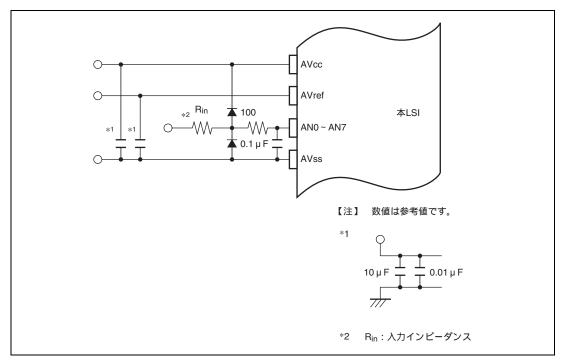

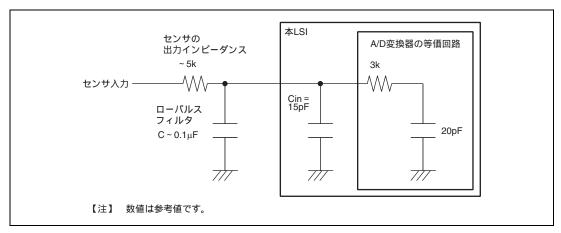

| 22.7.3         | ボード設計上の注意                        | 22-18 |

| 22.7.4         | アナログ入力端子の取り扱い                    | 22-18 |

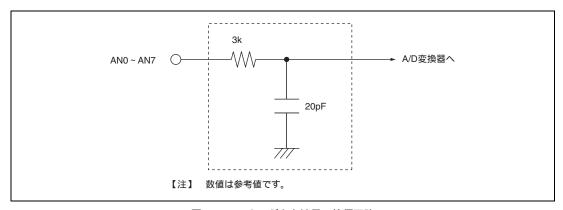

| 22.7.5         | 許容信号源インピーダンス                     | 22-20 |

| 22.7.6         | 絶対精度への影響                         | 22-20 |

| 22.7.7         | スキャンモードおよびマルチモード使用時の注意           | 22-20 |

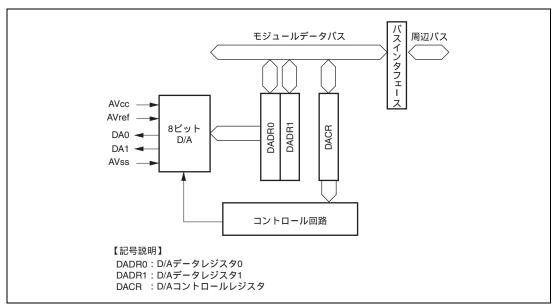

| 23. D/A        | 变换器(DAC)                         | 23-1  |

| 23.1           | 特長                               | 23-1  |

| 23.2           | 入出力端子                            | 23-2  |

| 23.3           | レジスタの説明                          | 23-3  |

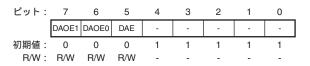

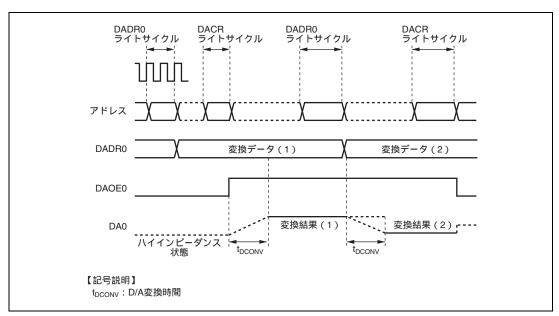

| 23.3.1         | D/A データレジスタ 0、1 ( DADR0、DADR1 )  | 23-3  |

| 23.3.2         | D/A コントロールレジスタ ( DACR )          | 23-3  |

| 23.4           | 動作説明                             | 23-5  |

| 23.5           | 使用上の注意事項                         | 23-6  |

| 23.5.1         | モジュールスタンバイモードの設定                 | 23-6  |

| 23.5.2         | ソフトウェアスタンバイモード時の D/A 出力保持機能      | 23-6  |

| 23.5.3         | アナログ電圧の設定                        | 23-6  |

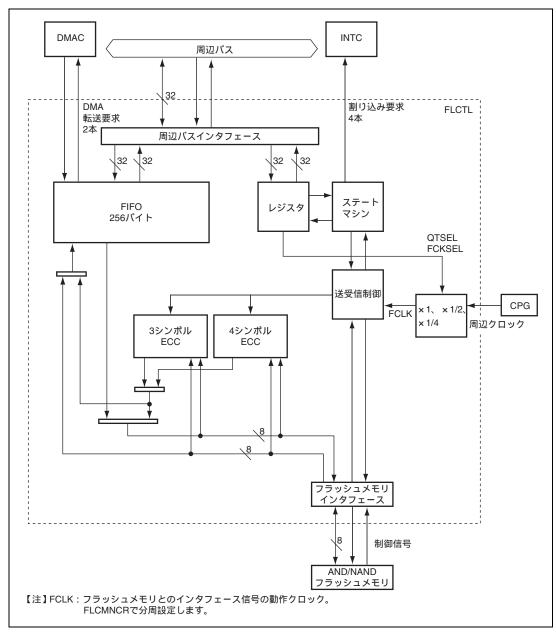

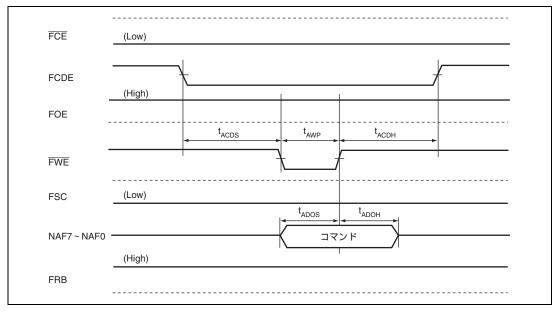

| 24.1           | 特長                               |       |

| 24.2           | 入出力端子                            |       |

| 24.3<br>24.3.1 | レジスタの説明<br>共通コントロールレジスタ(FLCMNCR) |       |

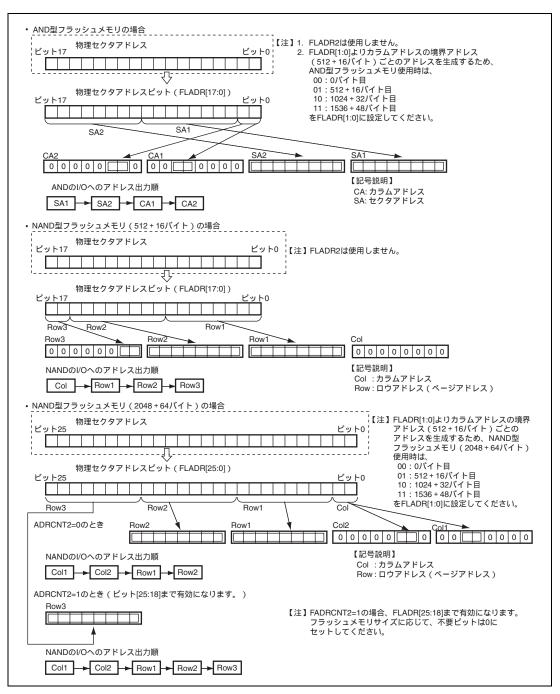

| 24.3.1         | スプトロールレシスタ (FLCMINCR)            |       |

| 24.3.3         | コマンドコードレジスタ (FLCMCDR )           |       |

| 24.3.4         | フドレスレジスタ(FLADR)                  |       |

| 24.3.4         | アドレスレジスタ 2 ( FLADR )             |       |

| 24.3.6         | データカウンタレジスタ(FLDTCNTR)            |       |

| 24.3.7         | データレジスタ(FLDATAR)                 |       |

| 24.3.8         | 割り込み DMA 制御レジスタ (FLINTDMACR )    |       |

| 24.3.9         | レディビジータイムアウト設定レジスタ (FLBSYTMR)    |       |

| 24.3.10        |                                  |       |

| 24.3.11        |                                  |       |

| 24.3.12        |                                  |       |

| 24.3.13        |                                  |       |

| 24.3.14        |                                  |       |

| 24.3.15        |                                  |       |

| 24.3.16        |                                  |       |

|                |                                  |       |

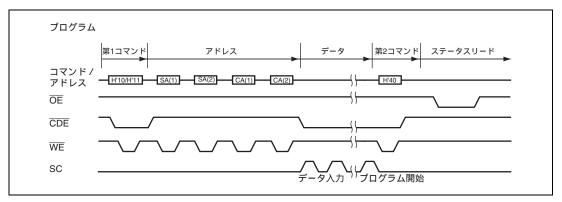

| 24.4    | 動作説明                                                    | 24-29 |

|---------|---------------------------------------------------------|-------|

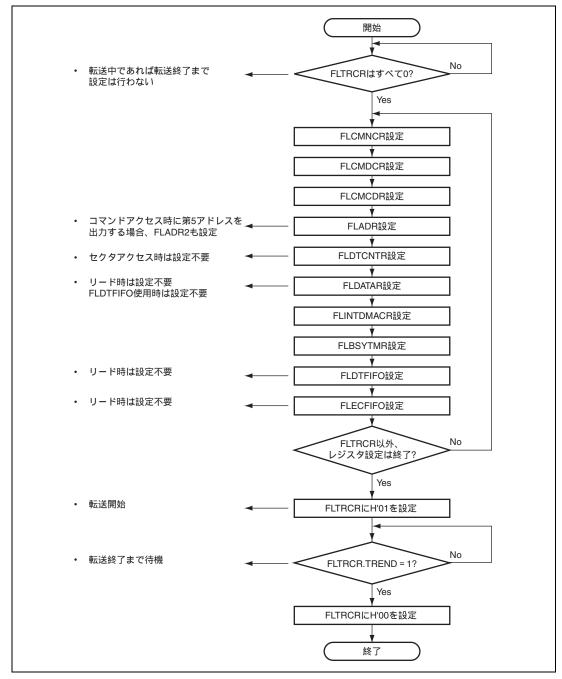

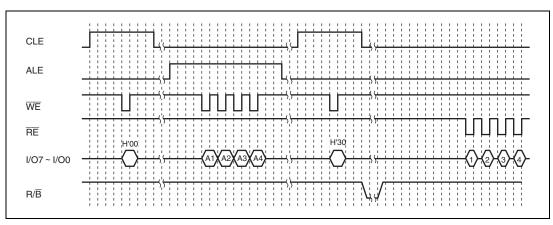

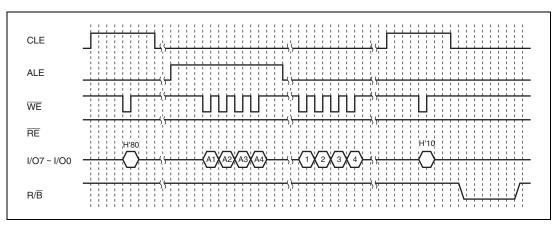

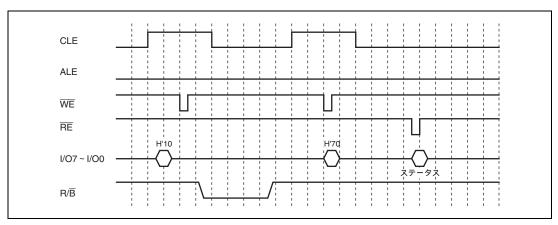

| 24.4.1  | アクセス手順                                                  | 24-29 |

| 24.4.2  | 動作モード                                                   | 24-29 |

| 24.4.3  | レジスタ設定手順                                                | 24-30 |

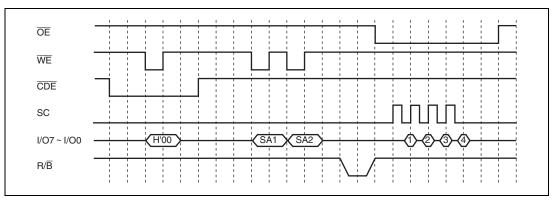

| 24.4.4  | コマンドアクセスモード                                             | 24-31 |

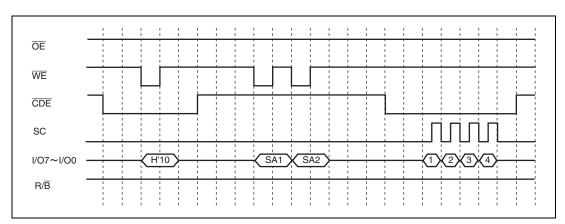

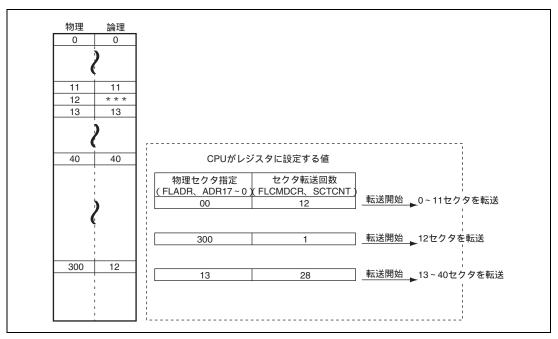

| 24.4.5  | セクタアクセスモード                                              | 24-36 |

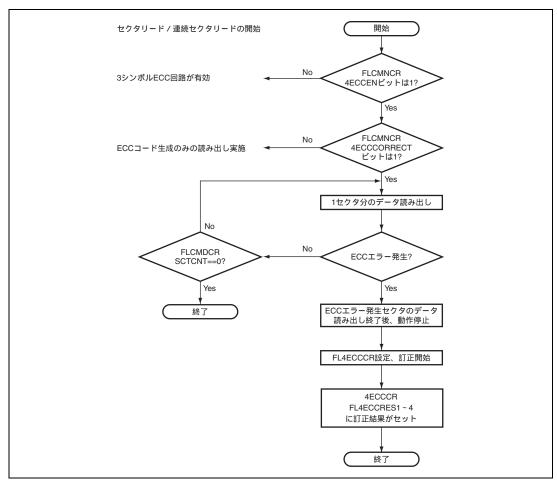

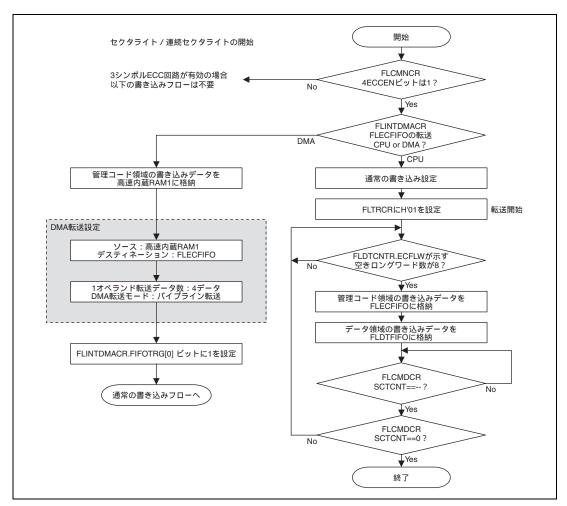

| 24.4.6  | ECC のエラー修正                                              | 24-38 |

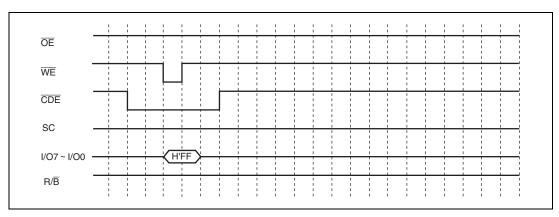

| 24.4.7  | ステータスリード                                                | 24-41 |

| 24.5    | 割り込み処理                                                  | 24-43 |

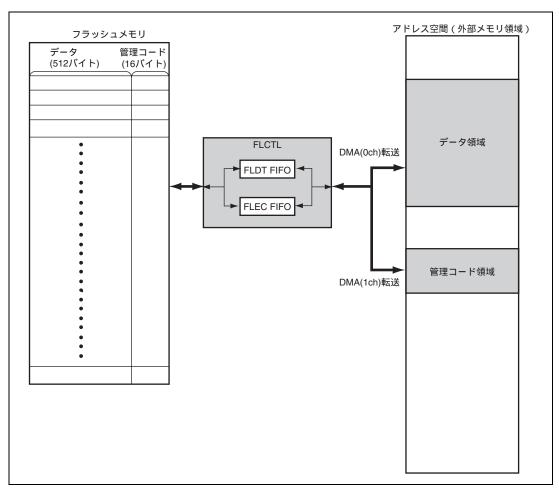

| 24.6    | DMA転送の設定                                                | 24-43 |

| 24.7    | 使用上の注意事項                                                | 24-44 |

| 24.7.1  | 4 シンボル ECC 回路使用時の管理コード領域書き込み                            | 24-44 |

| 24.7.2  | SNAND ビットに関する注意事項                                       | 24-44 |

| 05 1105 | 20.0 + 7   ( 7 - 2)   7   2   4   ( 110   2             | 05.4  |

| 25. USE | 32.0 ホスト / ファンクションモジュール(USB )                           | 25-1  |

| 25.1    | 特長                                                      |       |

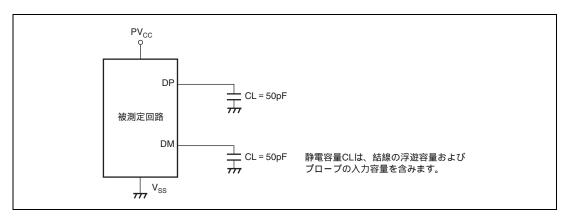

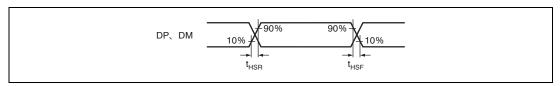

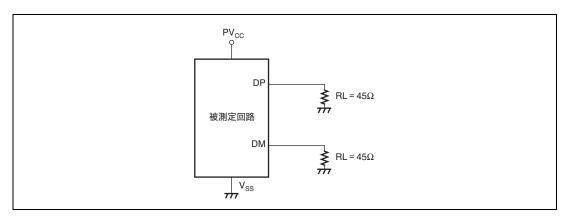

| 25.2    | 入出力端子                                                   |       |

| 25.3    | レジスタの説明                                                 |       |

| 25.3.1  | システムコンフィギュレーションコントロールレジスタ 0(SYSCFG0)                    |       |

| 25.3.2  | システムコンフィギュレーションコントロールレジスタ 1(SYSCFG1)                    | 25-11 |

| 25.3.3  | システムコンフィギュレーションステータスレジスタ 0(SYSSTS0)                     | 25-12 |

| 25.3.4  | システムコンフィギュレーションステータスレジスタ 1 ( SYSSTS1 )                  | 25-13 |

| 25.3.5  | デバイスステートコントロールレジスタ 0 ( DVSTCTR0 )                       | 25-14 |

| 25.3.6  | デバイスステートコントロールレジスタ 1 ( DVSTCTR1 )                       | 25-18 |

| 25.3.7  | テストモードレジスタ(TESTMODE)                                    | 25-21 |

| 25.3.8  | DMA-FIFO バスコンフィギュレーションレジスタ ( D0FBCFG、D1FBCFG )          | 25-24 |

| 25.3.9  | FIFO ポートレジスタ (CFIFO、D0FIFO、D1FIFO)                      | 25-25 |

| 25.3.10 | ) FIFO ポート選択レジスタ ( CFIFOSEL、 D0FIFOSEL、 D1FIFOSEL )     | 25-27 |

| 25.3.11 | I FIFO ポートコントロールレジスタ ( CFIFOCTR、 D0FIFOCTR、 D1FIFOCTR ) | 25-33 |

| 25.3.12 | 2 割り込み許可レジスタ 0(INTENB0)                                 | 25-36 |

| 25.3.13 | 3 割り込み許可レジスタ 1(INTENB1)                                 | 25-38 |

| 25.3.14 | 4 割り込み許可レジスタ 2(INTENB2)                                 | 25-40 |

| 25.3.15 | 5 BRDY 割り込み許可レジスタ(BRDYENB)                              | 25-41 |

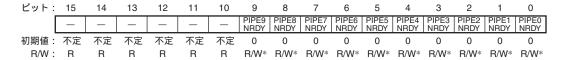

| 25.3.16 | 6 NRDY 割り込み許可レジスタ(NRDYENB)                              | 25-43 |

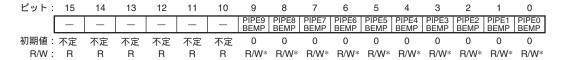

| 25.3.17 | 7 BEMP 割り込み許可レジスタ(BEMPENB)                              | 25-45 |

| 25.3.18 | 8 SOF 出力コンフィグレーションレジスタ(SOFCFG)                          | 25-47 |

| 25.3.19 |                                                         |       |

| 25.3.20 |                                                         |       |

| 25.3.21 |                                                         |       |

| 25.3.22 |                                                         |       |

| 25.3.2  | 3 NRDY 割り込みステータスレジスタ(NRDYSTS)                   | 25-59  |

|---------|-------------------------------------------------|--------|

| 25.3.2  | 4 BEMP 割り込みステータスレジスタ(BEMPSTS)                   | 25-63  |

| 25.3.2  | 5 フレームナンバーレジスタ(FRMNUM)                          | 25-65  |

| 25.3.20 | 6 μフレームナンバーレジスタ(UFRMNUM)                        | 25-67  |

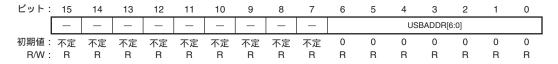

| 25.3.2  | 7 USB アドレスレジスタ(USBADDR)                         | 25-67  |

| 25.3.2  | 8 USB リクエストタイプレジスタ ( USBREQ )                   | 25-68  |

| 25.3.29 | 9 USB リクエストバリューレジスタ ( USBVAL )                  | 25-68  |

| 25.3.30 | 0 USB リクエストインデックスレジスタ ( USBINDX )               | 25-69  |

| 25.3.3  | 1 USB リクエストレングスレジスタ ( USBLENG )                 | 25-69  |

| 25.3.3  | 2 DCP コンフィギュレーションレジスタ ( DCPCFG )                | 25-70  |

| 25.3.3  | 3 DCP マックスパケットサイズレジスタ ( DCPMAXP )               | 25-72  |

| 25.3.3  | 4 DCP コントロールレジスタ ( DCPCTR )                     | 25-73  |

| 25.3.3  | 5 パイプウィンドウ選択レジスタ(PIPESEL)                       | 25-79  |

| 25.3.3  |                                                 |        |

| 25.3.3  | 7 パイプバッファ指定レジスタ(PIPEBUF)                        | 25-84  |

| 25.3.3  | 8 パイプマックスパケットサイズレジスタ(PIPEMAXP)                  | 25-86  |

| 25.3.3  | 9 パイプ周期制御レジスタ(PIPEPERI)                         | 25-88  |

| 25.3.40 | 0 パイプ n コントロールレジスタ ( PIPEnCTR ) ( n = 1 ~ 5 )   | 25-93  |

| 25.3.4  | 1 パイプ n コントロールレジスタ ( PIPEnCTR ) ( n = 6~9 )     | 25-100 |

| 25.3.4  | 2 トランザクションカウンタ許可レジスタ ( PIPEnTRE ) ( n = 1 ~ 5 ) | 25-105 |

| 25.3.4  | 3 トランザクションカウンタレジスタ ( PIPEnTRN ) ( n = 1 ~ 5 )   | 25-106 |

| 25.3.4  | 4 デバイスアドレスコンフィグレーションレジスタ(DEVADDn)(n=0~9、A)      | 25-108 |

| 25.3.4  | 5 USB AC 特性切り替えレジスタ 0(USBACSWR0)                | 25-110 |

| 25.3.4  | 6 USB AC 特性切り替えレジスタ 1(USBACSWR1)                | 25-111 |

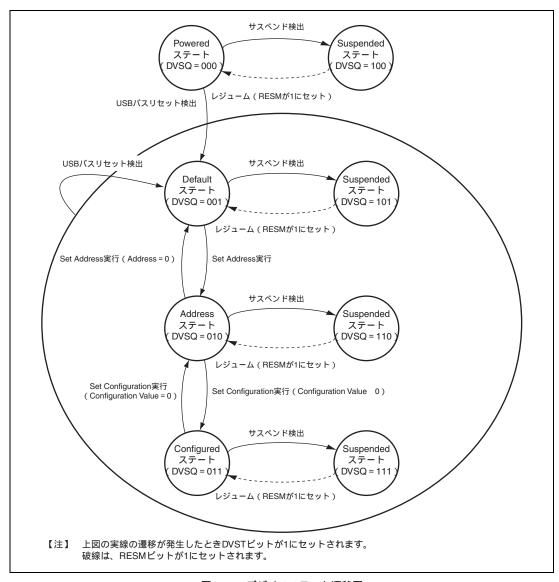

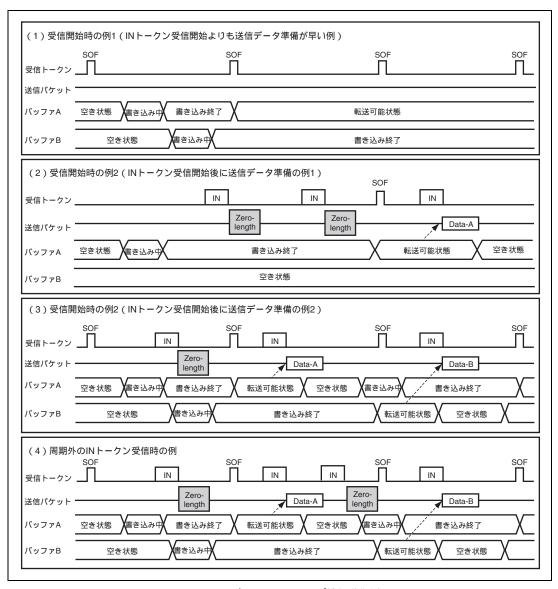

| 25.4    | 動作説明                                            | 25-112 |

| 25.4.1  | システム制御                                          | 25-112 |

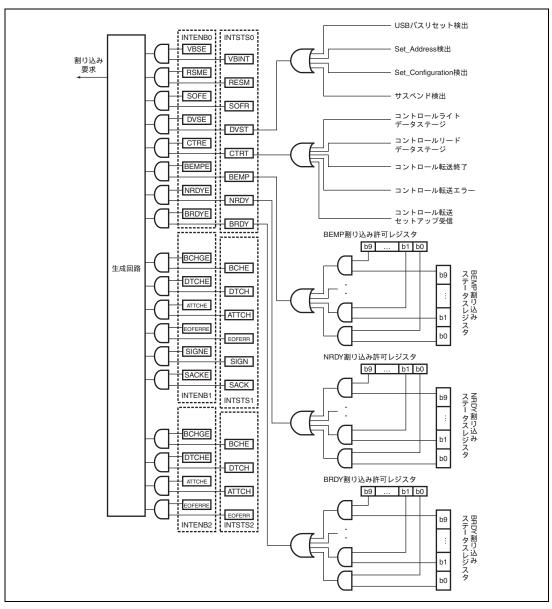

| 25.4.2  | 割り込み機能                                          | 25-114 |

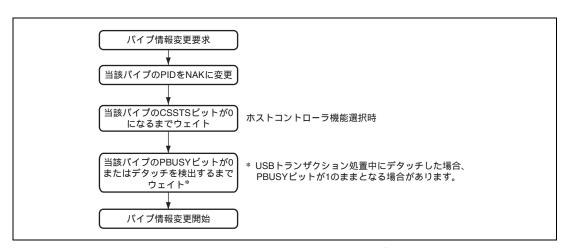

| 25.4.3  | パイプコントロール                                       | 25-121 |

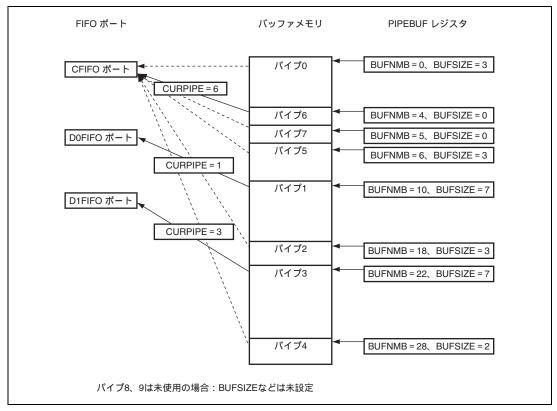

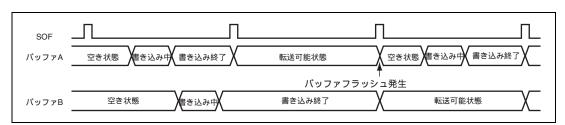

| 25.4.4  | FIFO バッファ                                       | 25-126 |

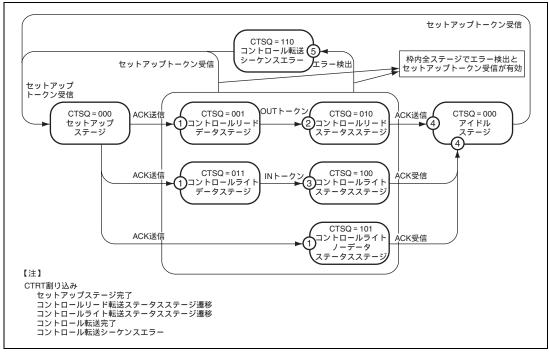

| 25.4.5  | コントロール転送(DCP)                                   | 25-135 |

| 25.4.6  | バルク転送(パイプ 1~5)                                  | 25-138 |

| 25.4.7  | インタラプト転送(パイプ 6~9)                               | 25-140 |

| 25.4.8  | アイソクロナス転送 (パイプ 1、2)                             | 25-141 |

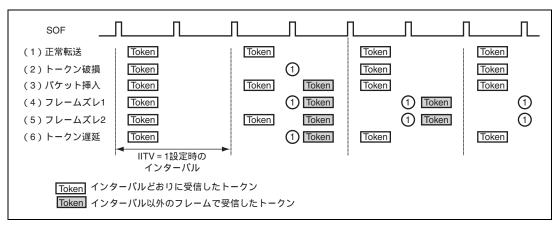

| 25.4.9  | SOF 補間機能                                        | 25-148 |

| 25.5    | 使用上の注意事項                                        | 25-149 |

| 25.5.1  | USB トランシーバの設定手順                                 | 25-149 |

| 26. SD         | ホストインタフェース(SDHI)                           | 26-1  |

|----------------|--------------------------------------------|-------|

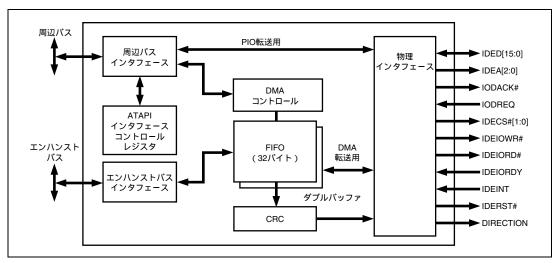

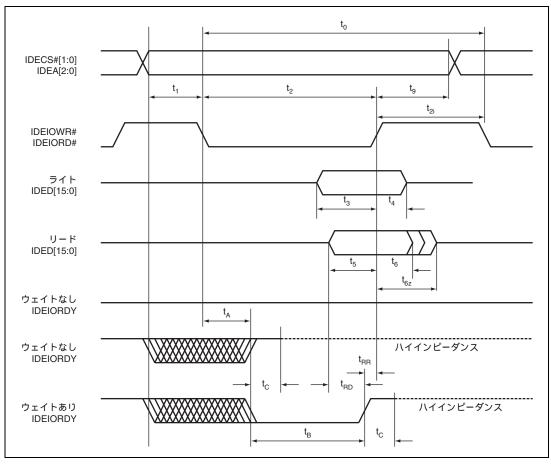

| 27. AT         | アタッチメントパケットインタフェース(ATAPI)                  | 27-1  |

| 27.1           | 特長                                         | 27-1  |

| 27.2           | 入出力端子                                      |       |

| 27.3           | レジスタの説明                                    |       |

| 27.3.1         |                                            |       |

| 27.3.2         |                                            |       |

| 27.4           | 動作説明                                       |       |

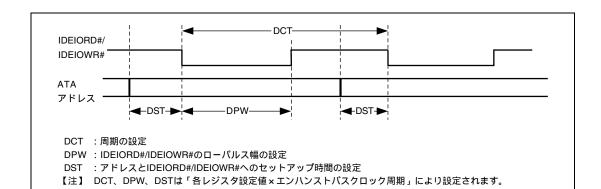

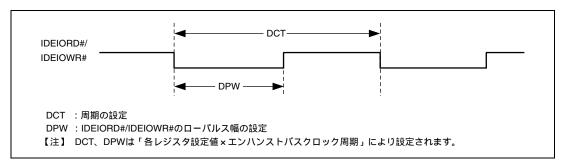

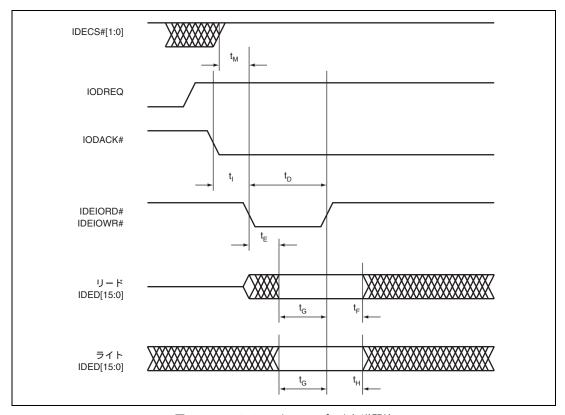

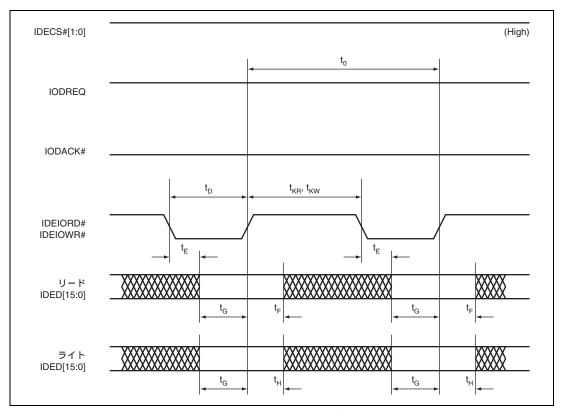

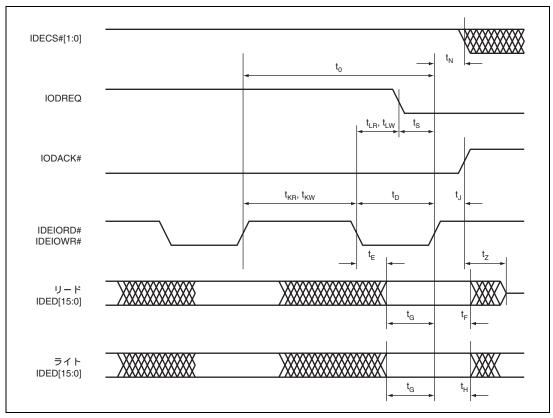

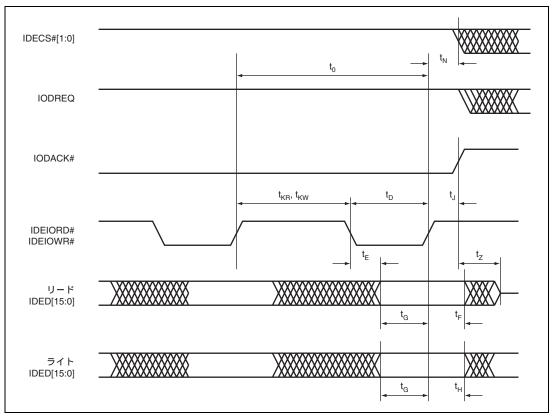

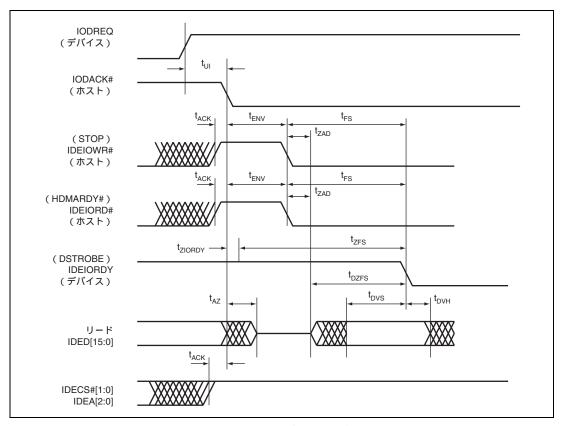

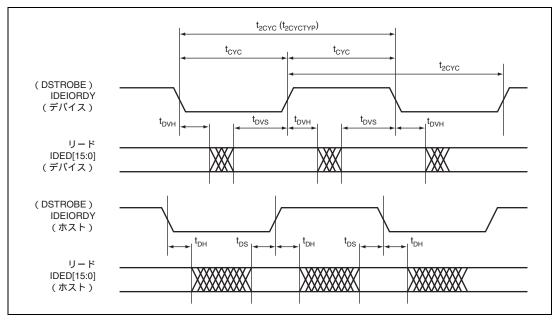

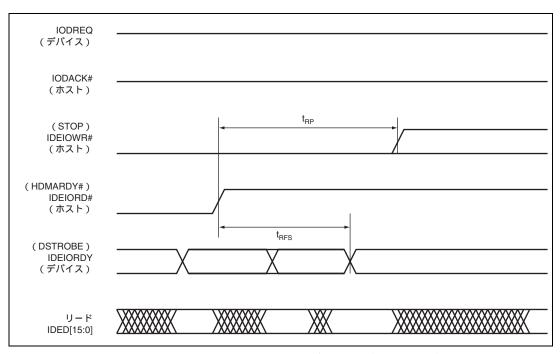

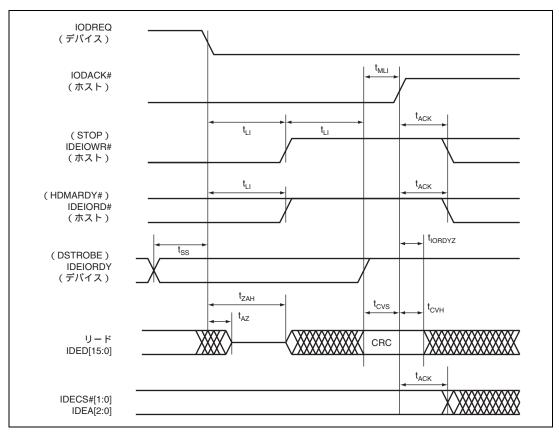

| 27.4.1         | データ転送モード                                   | 27-17 |

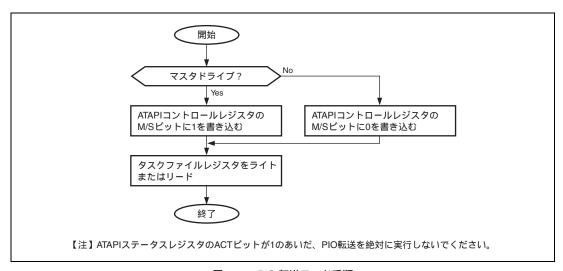

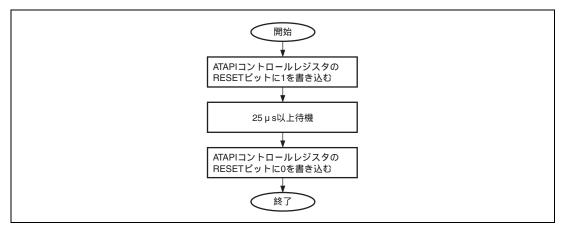

| 27.4.2         | 初期化手順                                      | 27-18 |

| 27.4.3         | PIO 転送モード手順                                | 27-18 |

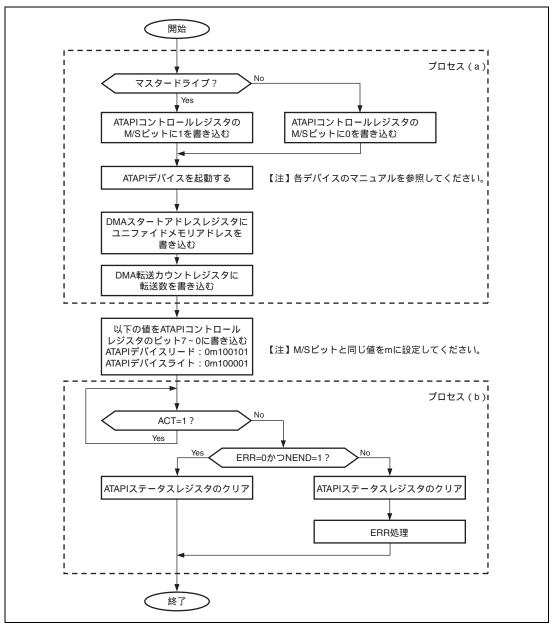

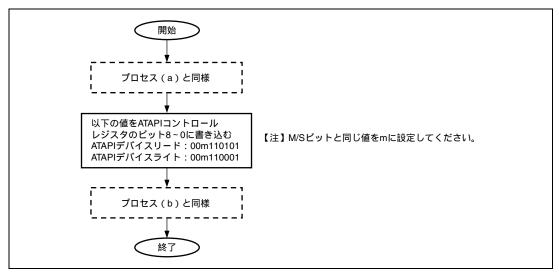

| 27.4.4         | マルチワード DMA 転送モード手順                         | 27-19 |

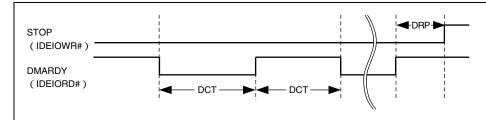

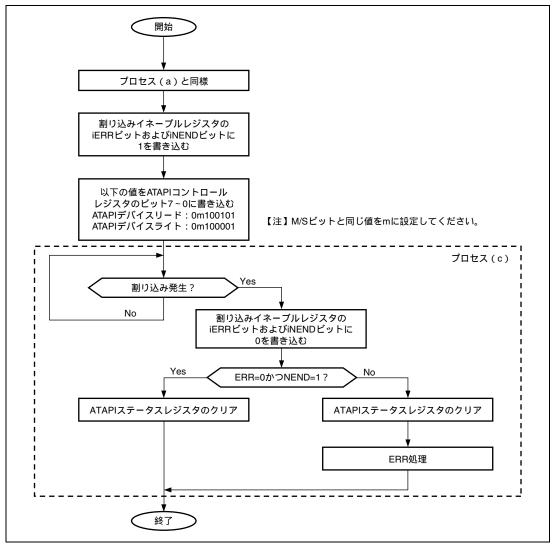

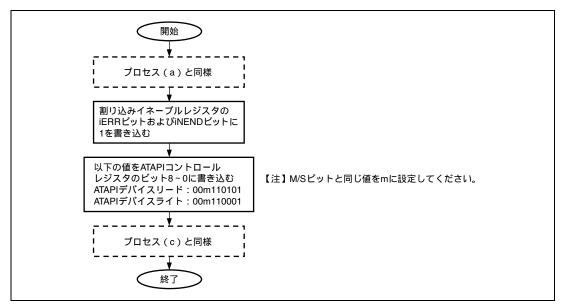

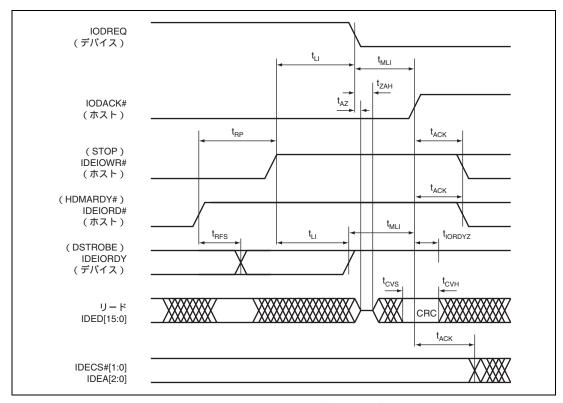

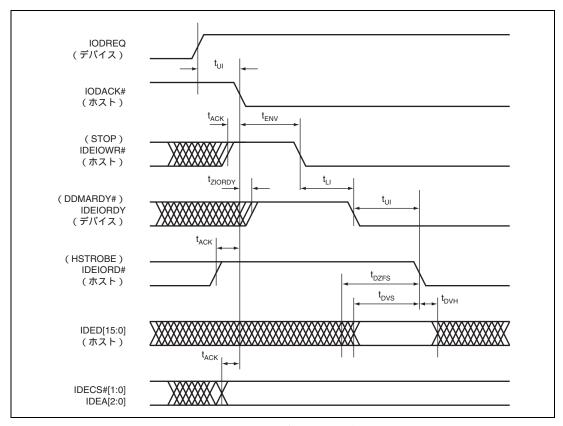

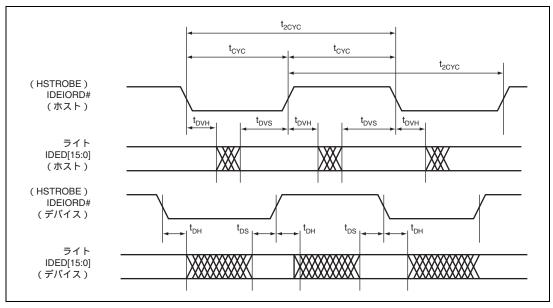

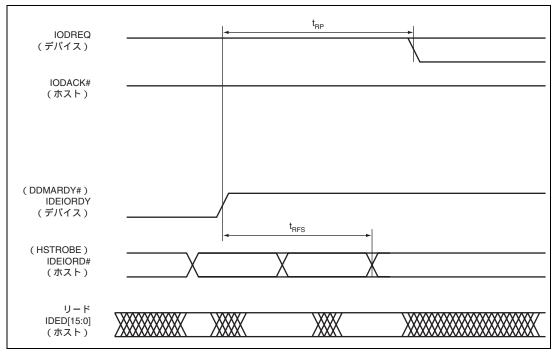

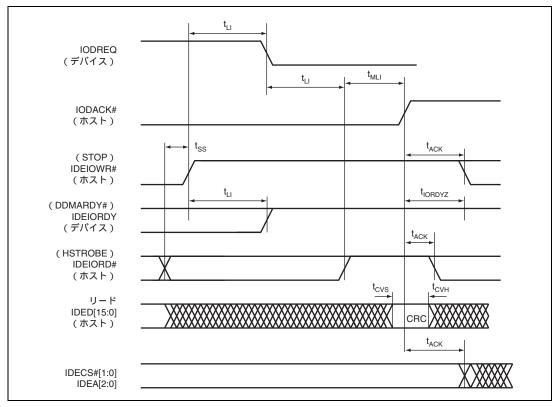

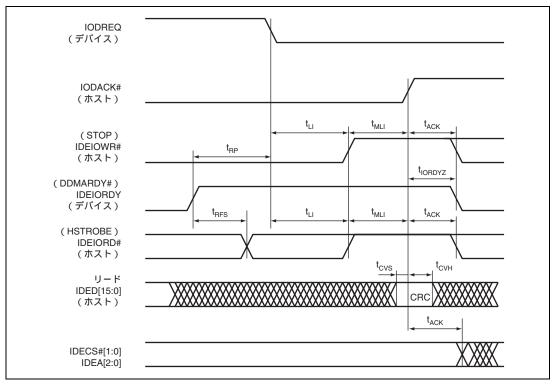

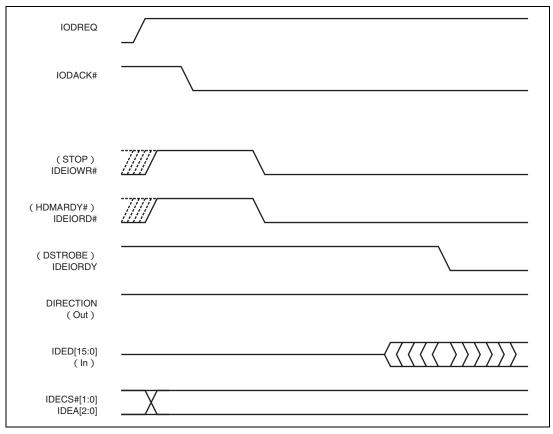

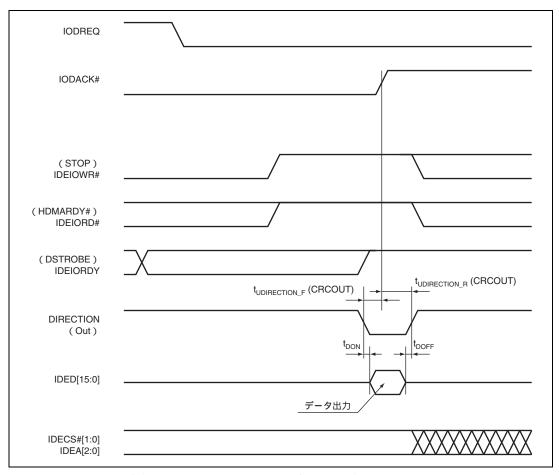

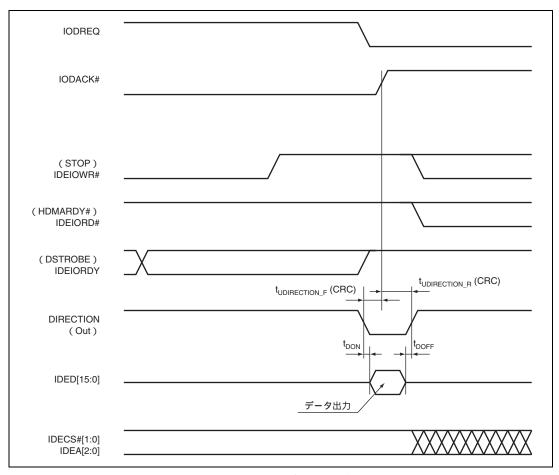

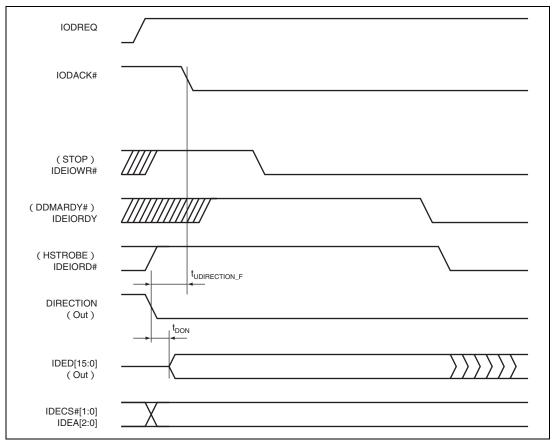

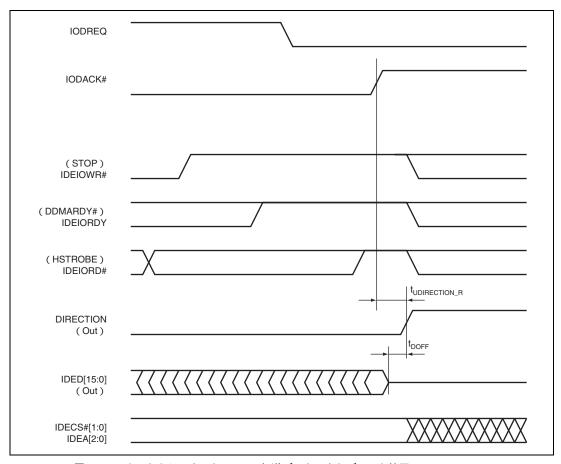

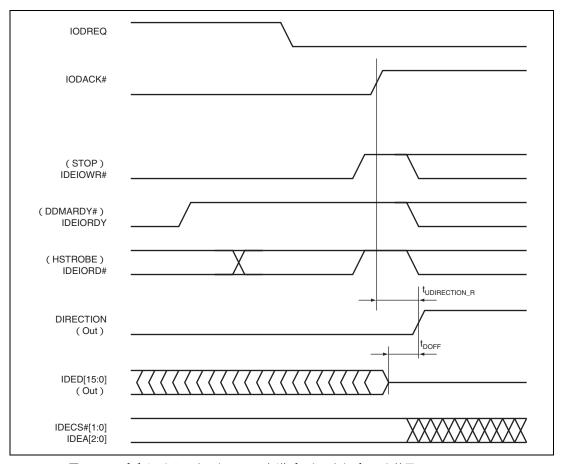

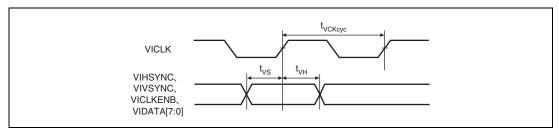

| 27.4.5         | ウルトラ DMA 転送モード手順                           | 27-21 |

| 27.4.6         | ATAPI デバイスのハードウェアリセット手順                    | 27-22 |

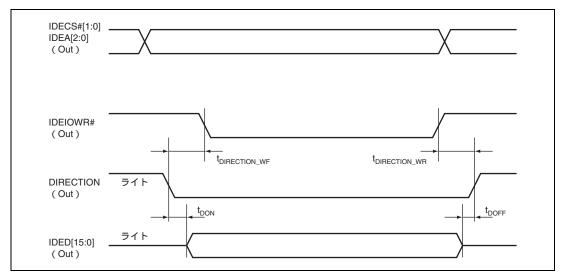

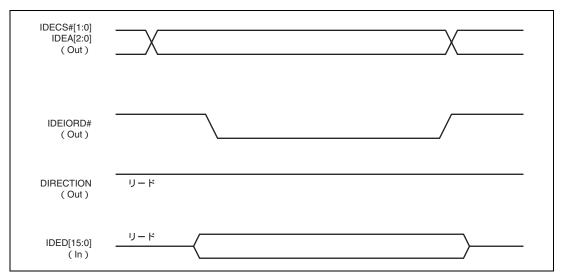

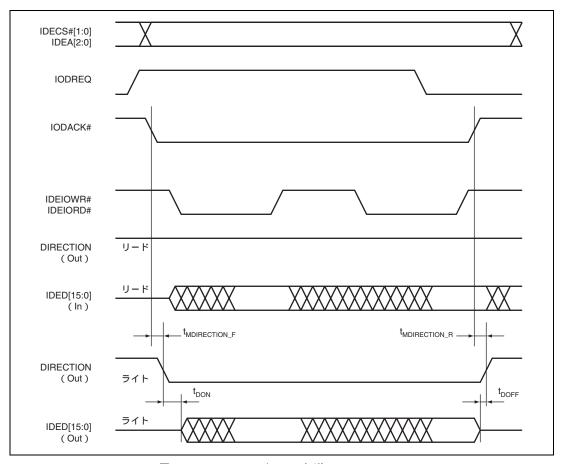

| 27.5           | DIRECTION端子                                | 27-22 |

| 27.6           | 使用上の注意事項                                   | 27-22 |

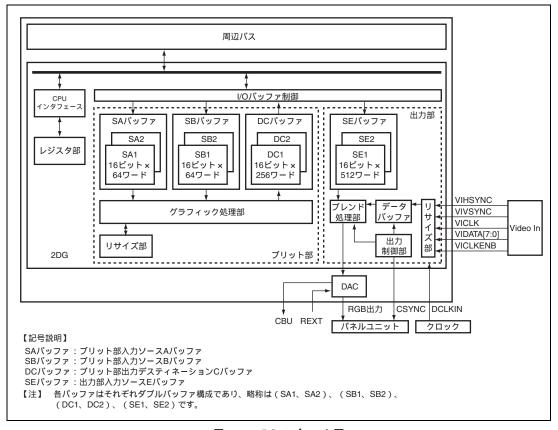

| 28. 2D<br>28.1 | エンジン(2DG)特長                                |       |

| 28.2           | 入出力端子                                      | 28-3  |

| 28.3           | レジスタの説明                                    | 28-4  |

| 28.3.1         | グラフィック部 BLT 機能指定実行レジスタ(GR_BLTPLY)          | 28-6  |

| 28.3.2         | グラフィック部 MIX 機能指定実行レジスタ(GR_MIXPLY )         | 28-7  |

| 28.3.3         | グラフィック部動作ステータスレジスタ(GR_DOSTAT)              | 28-8  |

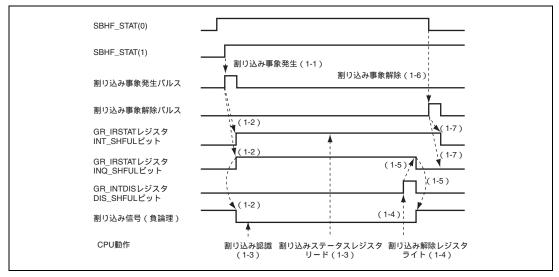

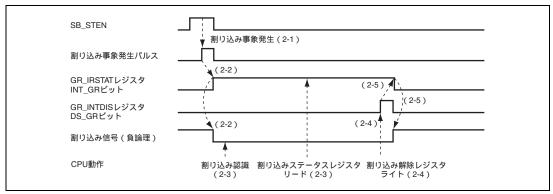

| 28.3.4         | グラフィック部割り込みステータスレジスタ(GR_IRSTAT)            | 28-11 |

| 28.3.5         | グラフィック部割り込みマスク制御レジスタ(GR_INTMSK)            | 28-15 |

| 28.3.6         | グラフィック部割り込み解除制御レジスタ ( GR_INTDIS )          | 28-17 |

| 28.3.7         | グラフィック部 DMAC 要求制御レジスタ(GR_DMAC)             | 28-19 |

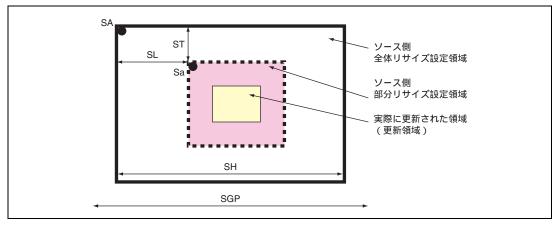

| 28.3.8         | BLT 用ソース AB 読み込み領域設定レジスタ(GR_SABSET)        | 28-21 |

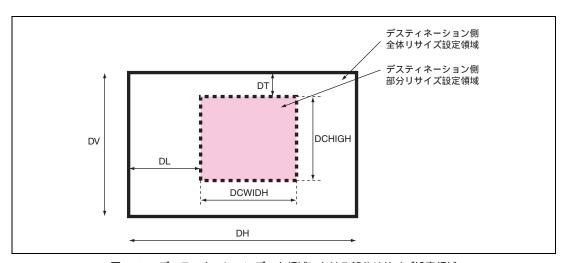

| 28.3.9         | BLT 用デスティネーション C 書き込み領域設定レジスタ ( GR_DCSET ) | 28-22 |

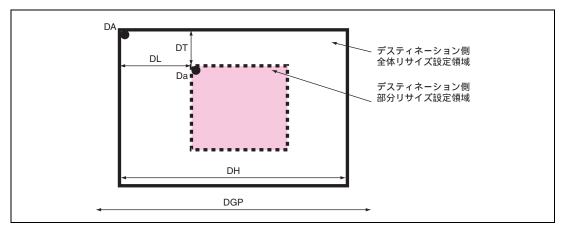

| 28.3.1         | 0 出力部用ソース E 読み込み領域設定レジスタ ( MGR_SESET )     | 28-23 |

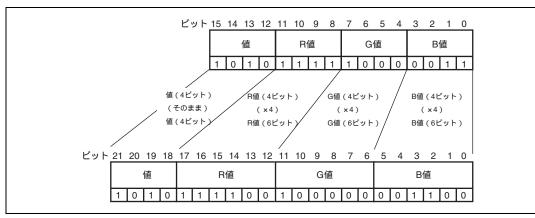

| 28.3.1         | 1 グラフィック部用画素フォーマット設定レジスタ(GR_PIXLFMT)       | 28-24 |

| 28.3.1         | 2 BLT 用動作モード設定レジスタ(GR_BLTMODE)             | 28-25 |

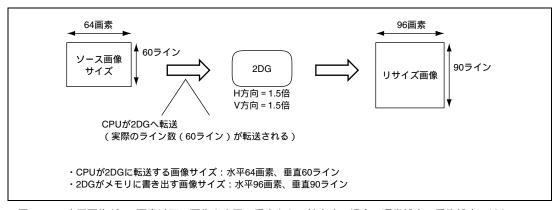

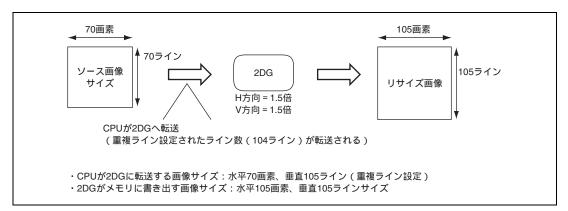

| 28.3.1         | 3 グラフィック用リサイズ画面設定レジスタ(GR_RISZSET)          | 28-27 |

| 28.3.1         | 4 BLT 用リサイズモード選択レジスタ(GR_RISZMOD)           | 28-28 |

| 28.3.1         | 5 BLT 用リサイズデルタ設定レジスタ(GR_DELT)              | 28-29 |

| 28.3.1         | 6 BLT 用リサイズ水平先頭位相設定レジスタ(GR_HSPHAS )        | 28-30 |

| 28.3.1         | 7 BLT 用リサイズ垂直先頭位相設定レジスタ(GR_VSPHAS)         | 28-31 |

| 28 3 1         | 8 出力部用リサイズ水平デルタ設定レジスタ(MGR HDFLT)           | 28-32 |

| 28.3.19                                 | 出力部用リサイズ水平先頭位相設定レジスタ(MGR_HPHAS)       | 28-32  |

|-----------------------------------------|---------------------------------------|--------|

| 28.3.20                                 | BLT 用論理演算入力データレジスタ(GR_LGDAT)          | 28-33  |

| 28.3.21                                 | BLT 用クロマキー対象色データレジスタ(GR_DETCOL)       | 28-34  |

| 28.3.22                                 | BLT 用ブレンド処理用置換色データレジスタ ( GR_BRDCOL )  | 28-35  |

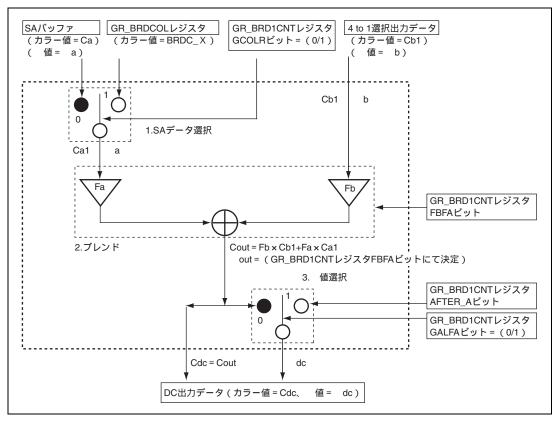

| 28.3.23                                 | BLT 用ブレンド 1 コントロールレジスタ ( GR_BRD1CNT ) | 28-36  |

| 28.3.24                                 | 出力部動作モード設定レジスタ(MGR_MIXMODE)           | 28-38  |

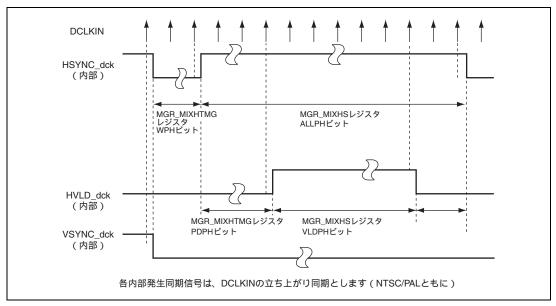

| 28.3.25                                 | 出力部パネル出力水平タイミング設定レジスタ(MGR_MIXHTMG)    | 28-40  |

| 28.3.26                                 | 出力部パネル出力水平有効領域設定レジスタ(MGR_MIXHS)       | 28-41  |

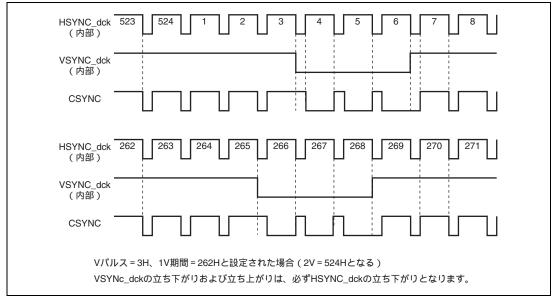

| 28.3.27                                 | 出力部パネル出力垂直タイミング設定レジスタ(MGR_MIXVTMG)    | 28-42  |

| 28.3.28                                 | 出力部パネル出力垂直有効領域設定レジスタ ( MGR_MIXVS )    | 28-43  |

| 28.3.29                                 | グラフィック部出力 SYNC 位置設定レジスタ(GR_VSDLY)     | 28-44  |

| 28.3.30                                 | VideoDAC タイミング設定レジスタ(VDAC_TMC)        | 28-45  |

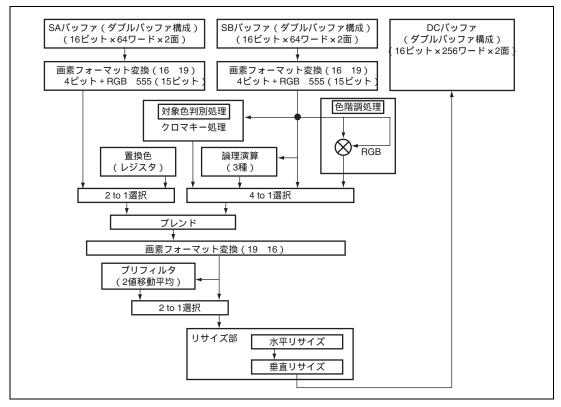

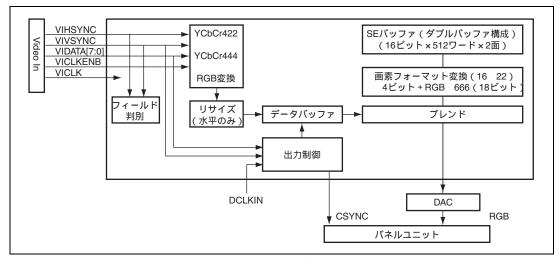

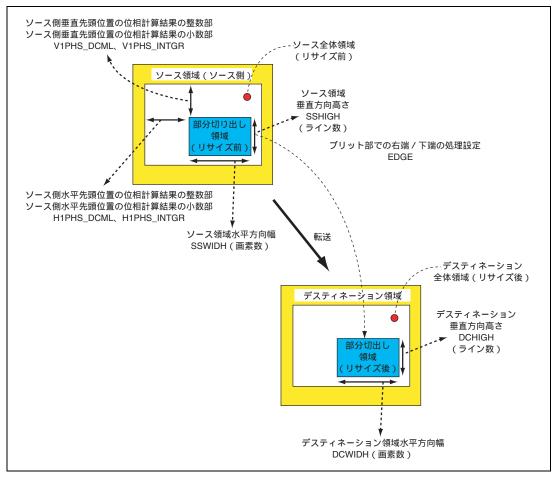

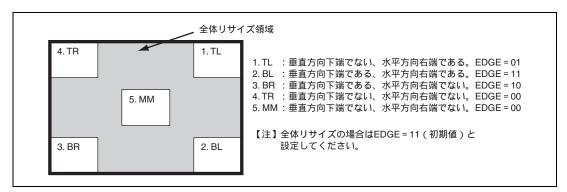

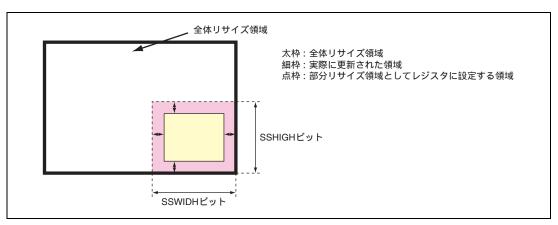

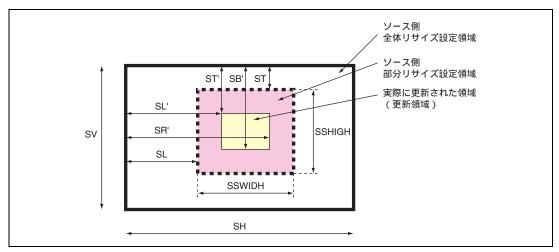

| 28.4 重                                  | 加作説明                                  | 28-46  |

| 28.4.1                                  | 入出力                                   | 28-47  |

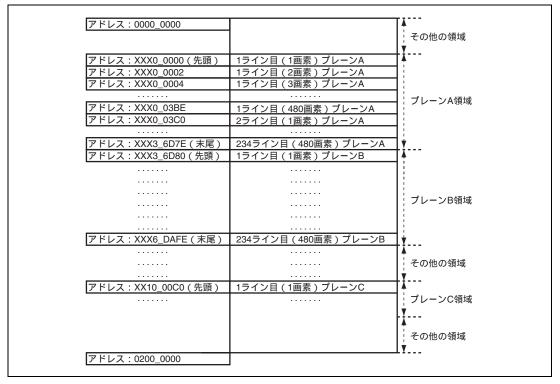

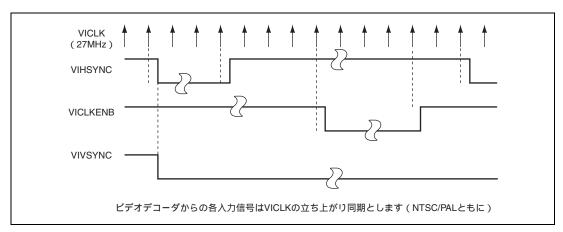

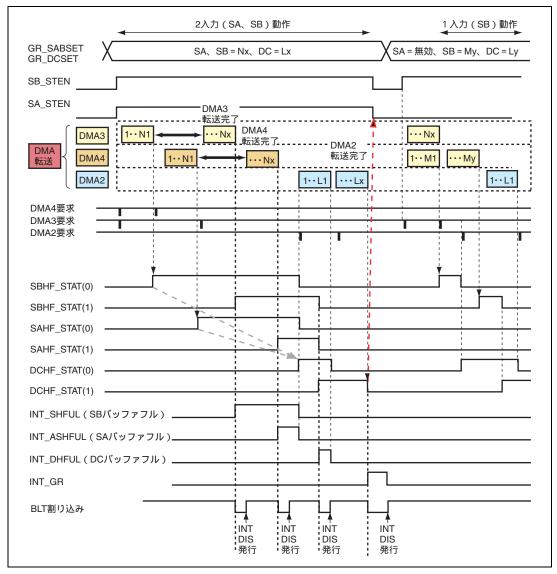

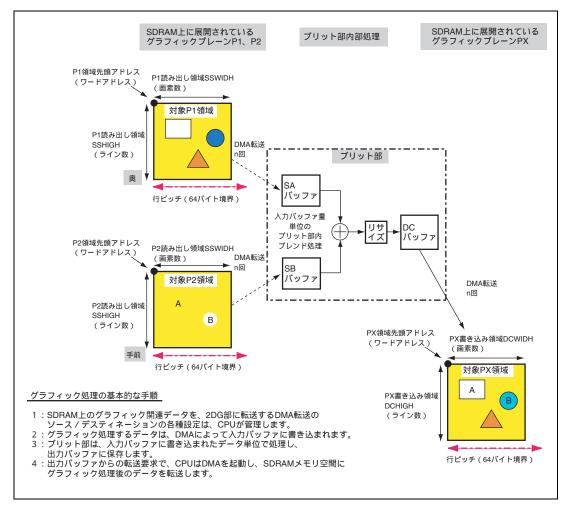

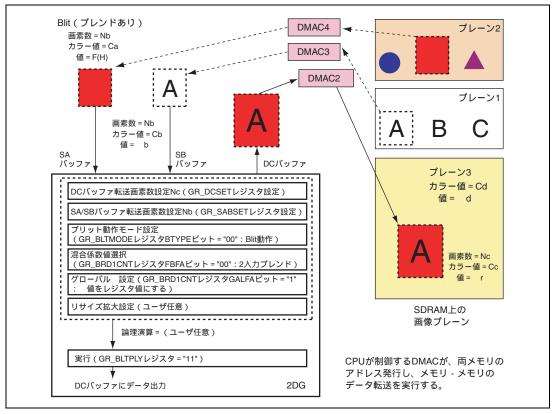

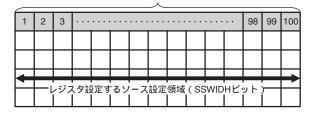

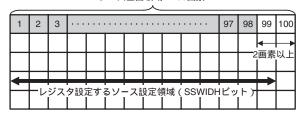

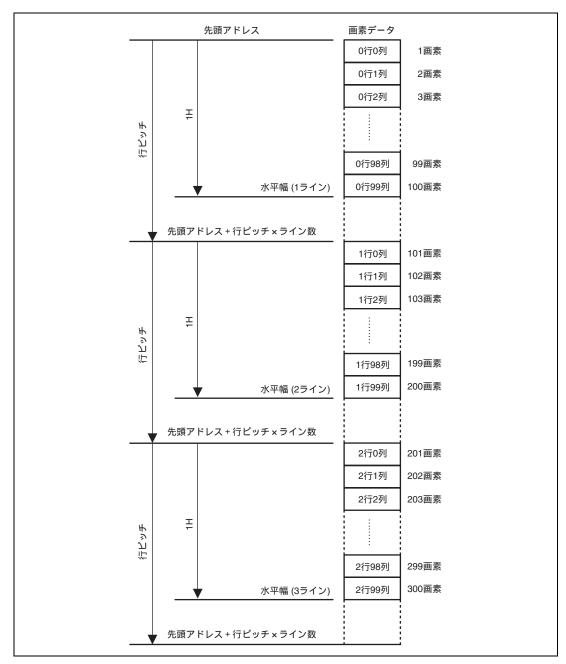

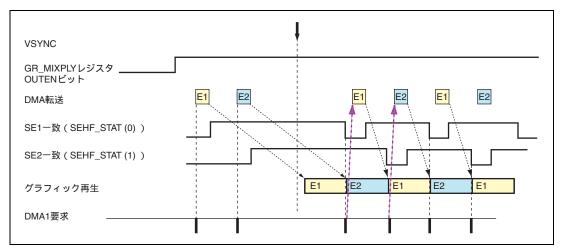

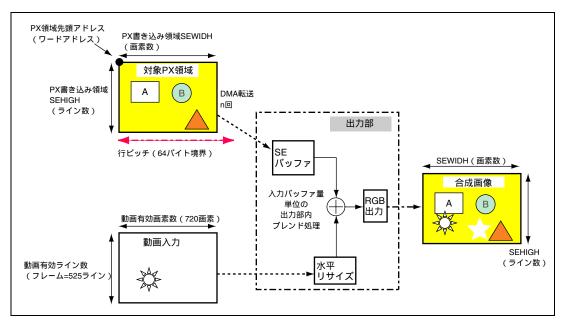

| 28.4.2                                  | DMA 使用方法                              | 28-57  |

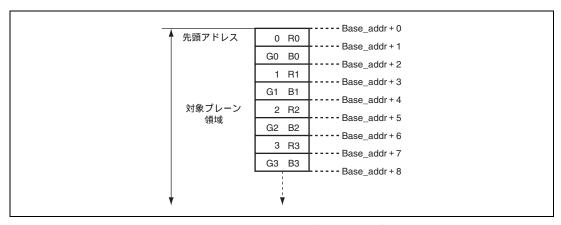

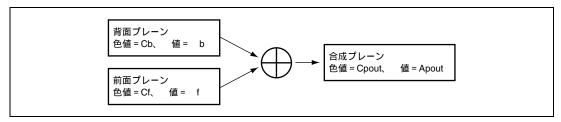

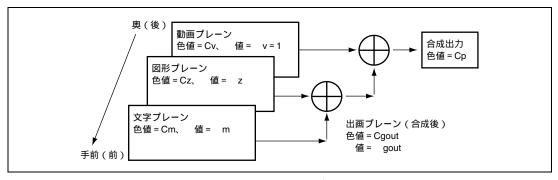

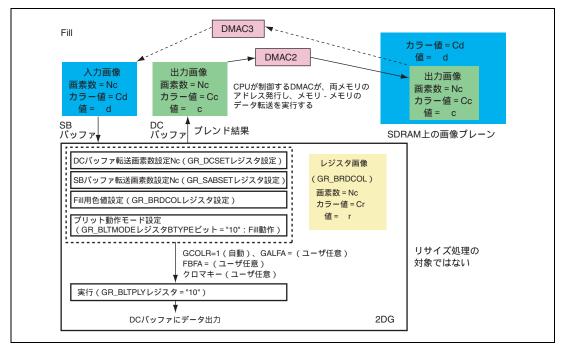

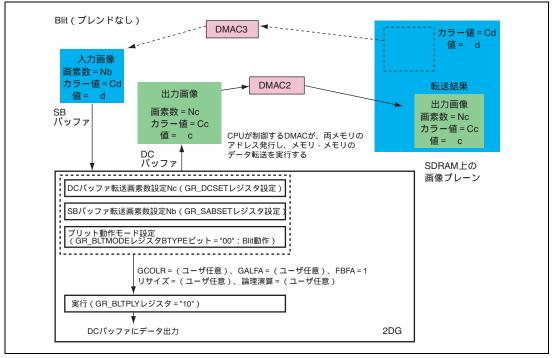

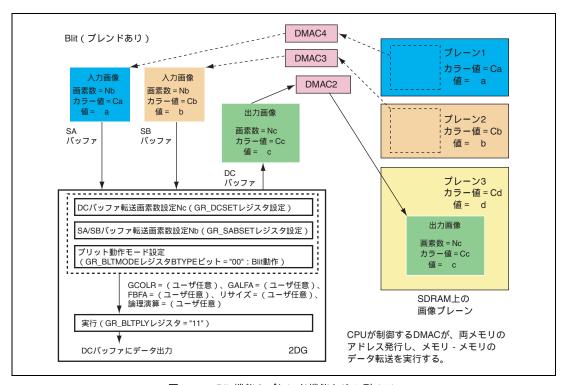

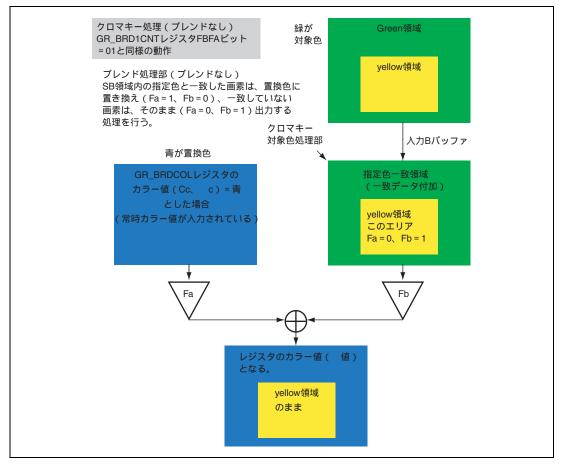

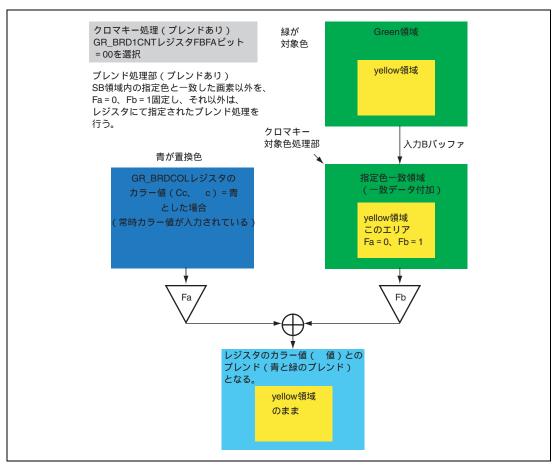

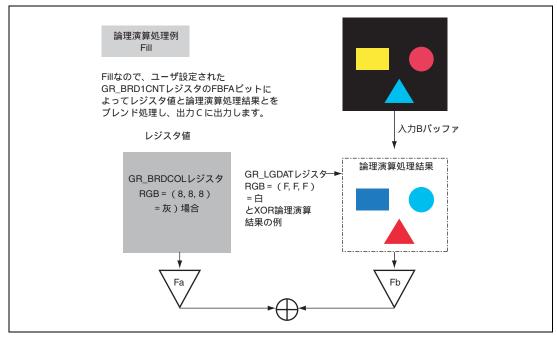

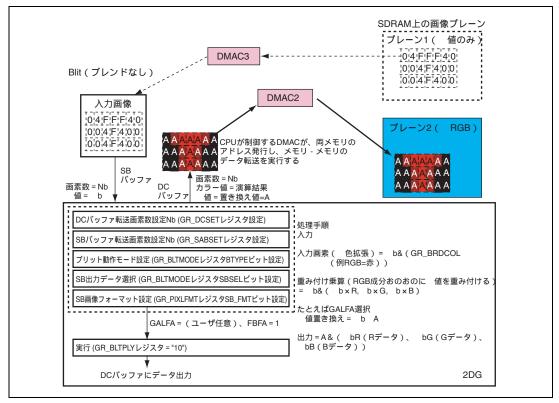

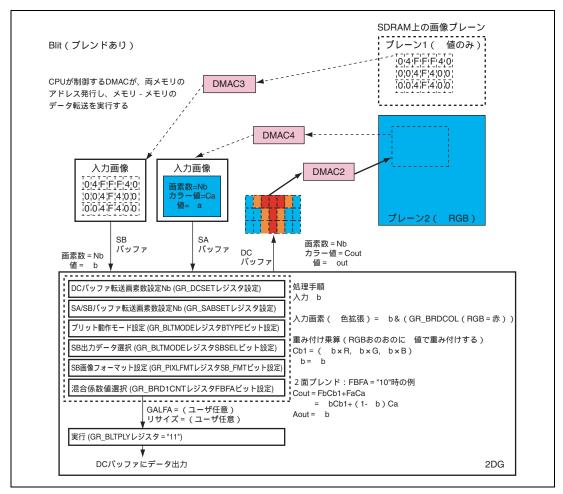

| 28.4.3                                  | ブリット部動作                               | 28-60  |

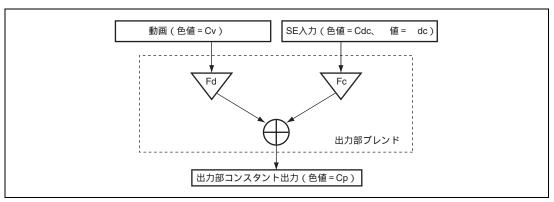

| 28.4.4                                  | 出力動作                                  | 28-105 |

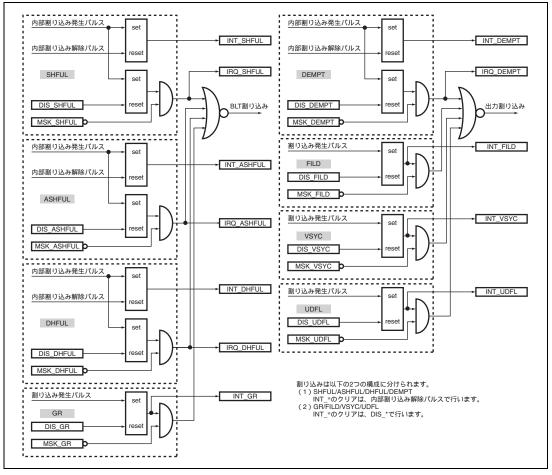

| 28.4.5                                  | 割り込み                                  | 28-110 |

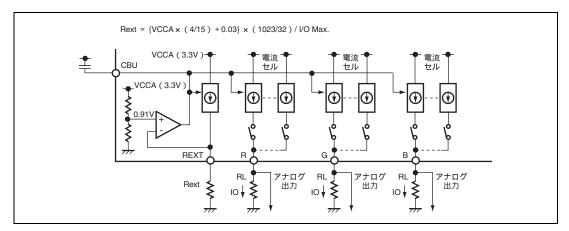

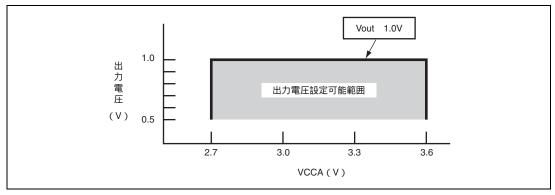

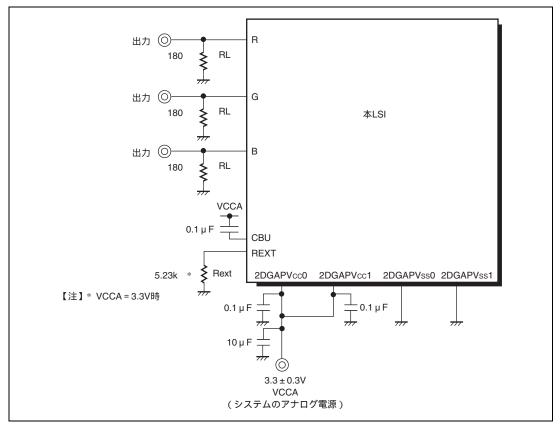

| 28.5 亿                                  | †録 VIDEO OUT ( D/A変換器 )               | 28-114 |

| 28.5.1                                  | アナログ出力電流                              | 28-114 |

| 28.5.2                                  | 使用上の注意                                | 28-116 |

| 28.5.3                                  | 使用例                                   | 28-117 |

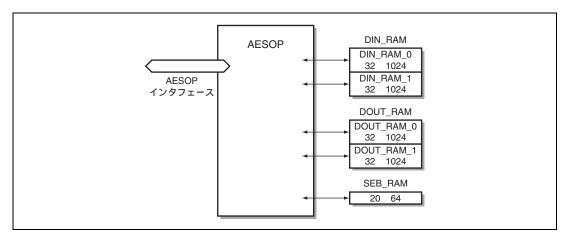

| 20 440 =                                | Lンコーダ(AESOP)                          | 00.1   |

|                                         |                                       |        |

| • • • • • • • • • • • • • • • • • • • • | 持長                                    |        |

|                                         | 、                                     |        |

|                                         | ·ジスタの説明                               |        |

| 29.3.1                                  | ソフトウェアリセットレジスタ(SWRSR)                 |        |

| 29.3.2                                  | エンコード処理初期化レジスタ ( RPRSR )              |        |

| 29.3.3                                  | DMA コントロールレジスタ ( DMACR )              |        |

| 29.3.4                                  | DIN_RAM バッファライト用 DMA 転送レジスタ(DMADI)    |        |

| 29.3.5                                  | DOUT_RAM バッファリード用 DMA 転送レジスタ(DMADO)   |        |

| 29.3.6                                  | イベントマスクレジスタ(EVMSR)                    |        |

| 29.3.7                                  | イベントクリアレジスタ ( EVCLR )                 |        |

| 29.3.8                                  | 設定指定レジスタ 1 (MBOTR )                   |        |

| 29.3.9                                  | 設定指定レジスタ 2 (BACCR )                   |        |

| 29.3.10                                 | 設定指定レジスタ 3 ( ACESR )                  |        |

| 29.3.11                                 | オーディオ処理情報設定レジスタ(ADIFR)                |        |

| 29.3.12                                 | 設定指定レジスタ 4(TBRSR)                     |        |

| 29.3.13                                 | ヘッダ設定レジスタ(HEADR)                      | 29-12  |

| 29.3.14 | ADTS 形式ヘッダ情報設定レジスタ(ADTSR)                                     | 29-13 |

|---------|---------------------------------------------------------------|-------|

| 29.3.15 | 設定指定レジスタ 5(MSS1R)                                             | 29-15 |

| 29.3.16 | 設定指定レジスタ 6 ( MSS2R )                                          | 29-15 |

| 29.3.17 | 設定指定レジスタ7(QLMDR)                                              | 29-15 |

| 29.3.18 | 設定指定レジスタ 8 ( QCHAR )                                          | 29-15 |

| 29.3.19 | 設定指定レジスタ 9 ( QGGAR )                                          | 29-15 |

| 29.3.20 | 設定指定レジスタ 10 ( SDTRR )                                         | 29-15 |

| 29.3.21 | ストリームデータ強制転送設定レジスタ(SDFOR)                                     | 29-16 |

| 29.3.22 | ストリームデータ強制転送バイト量表示レジスタ(SDBTR )                                | 29-16 |

| 29.3.23 | フレームバイト量表示レジスタ(FBYTR )                                        | 29-17 |

| 29.4 重  | 协作説明                                                          | 29-18 |

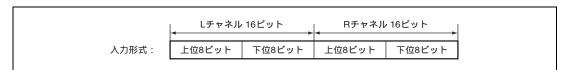

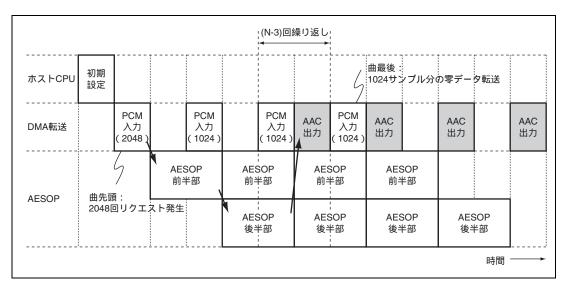

| 29.4.1  | DMA 転送による動作                                                   | 29-18 |

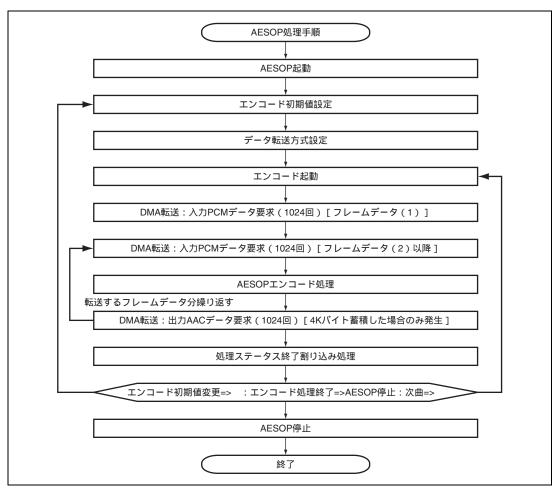

| 29.4.2  | AESOP 処理手順                                                    | 29-19 |

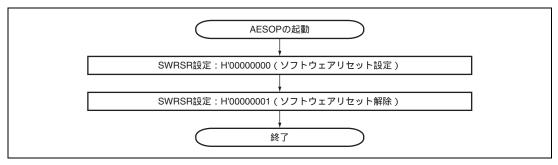

| 29.4.3  | AESOP 起動                                                      | 29-20 |

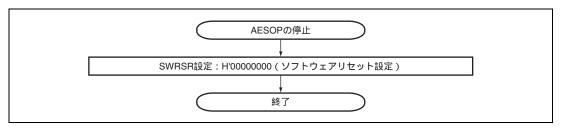

| 29.4.4  | AESOP 停止                                                      | 29-20 |

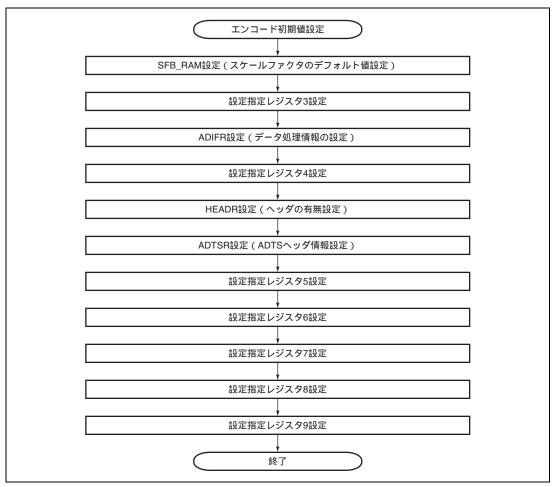

| 29.4.5  | エンコード初期値設定                                                    | 29-21 |

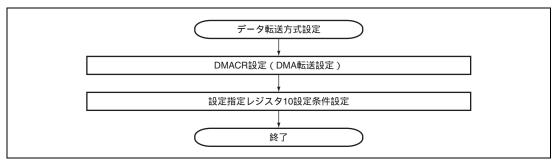

| 29.4.6  | データ転送方式設定                                                     | 29-22 |

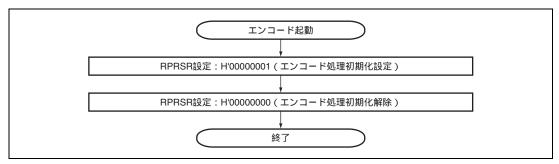

| 29.4.7  | エンコード起動                                                       | 29-22 |

| 29.4.8  | DMA 転送(AESOP へのデータ入力転送用 DMA)                                  | 29-23 |

| 29.4.9  | DMA 転送(AESOP からのデータ出力転送用 DMA)                                 | 29-23 |

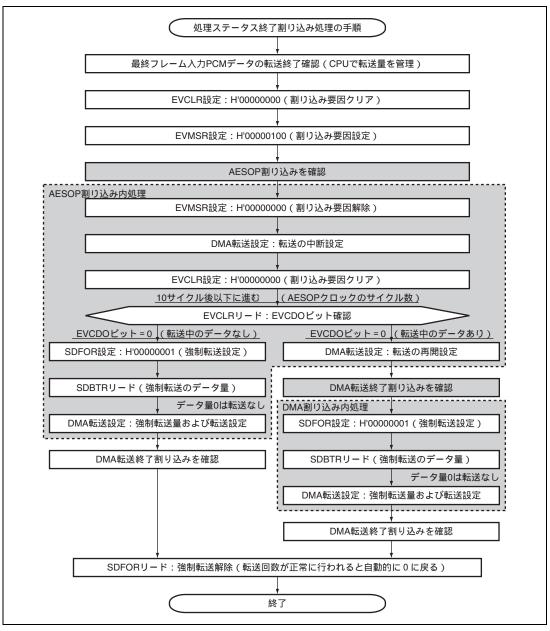

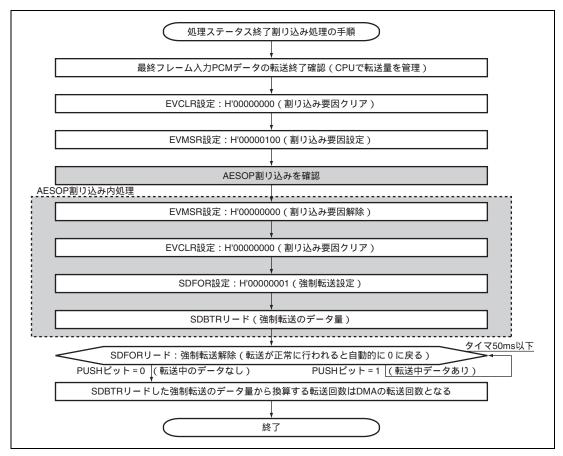

| 29.4.10 | 処理ステータス終了割り込み処理                                               | 29-24 |

| 29.4.11 | SFB_RAM 係数デフォルト値                                              | 29-28 |

| 30 ピン-  | ファンクションコントローラ(PFC)                                            | 30-1  |

|         |                                                               |       |

|         | 寺長                                                            |       |

|         | ノジスタの説明                                                       |       |

| 30.2.1  | ポート A・IO レジスタ L ( PAIORL )                                    |       |

| 30.2.2  | ポート A コントロールレジスタ L1 ~ L4 ( PACRL1 ~ PACRL4 )                  |       |

| 30.2.3  | ポートB・IO レジスタ H(PBIORH)                                        |       |

| 30.2.4  | ポートB・IO レジスタL ( PBIORL )                                      | 30-14 |

| 30.2.5  | ポート B コントロールレジスタ H1、H2、L1~L4<br>(PBCRH1、PBCRH2、PBCRL1~PBCRL4) | 30.14 |

| 30.2.6  | ポート C・IO レジスタ L ( PCIORL )                                    |       |

| 30.2.7  | ポート C コントロールレジスタ L1 ~ L3 ( PCCRL1 ~ PCCRL3 )                  |       |

| 30.2.7  | ポート D・IO レジスタ L ( PDIORL )                                    |       |

| 30.2.9  | ポート D コントロールレジスタ L1 ( PDCRL1 )                                |       |

| 30.2.9  | ポートE・IO レジスタL(PEIORL)                                         |       |

|         | ポート E コントロールレジスタ L1 ~ L4 ( PECRL1 ~ PECRL4 )                  |       |

| 30.2.11 | ホート E コフトロールレシスタ L1 ~ L4 ( PECRL1 ~ PECRL4 )                  |       |

| 30.2.12 | ポートFコントロールレジスタ L1、L2(PFCRL1、PFCRL2)                           |       |

| 30.2.13 |                                                               |       |

| 30.2.14 | ポート G コントロールレジスタ L1~L2 ( PGCRL1~PGCRL2 )                      | 30-24 |

| 30.2.15    | ポートH・IO レジスタL(PHIORL)                        | 30-25 |

|------------|----------------------------------------------|-------|

| 30.2.16    | ポート H コントロールレジスタ L1 ~ L4 ( PHCRL1 ~ PHCRL4 ) | 30-26 |

| 30.2.17    | ポート J・IO レジスタ L ( PJIORL )                   | 30-28 |

| 30.2.18    | ポート J コントロールレジスタ L1 ~ L4 ( PJCRL1 ~ PJCRL4 ) | 30-28 |

| 30.2.19    | ポート K・IO レジスタ L ( PKIORL )                   | 30-30 |

| 30.2.20    | ポート K コントロールレジスタ L1 ( PKCRL1 )               | 30-31 |

| 30.3 使     | 用上の注意事項                                      | 30-32 |

| 31. I/O ポ- | - h                                          | 31-1  |

| 31.1 特     | 長                                            | 31-1  |

| 31.2 L     | デジスタの説明                                      | 31-3  |

| 31.2.1     | ポート A データレジスタ L ( PADRL )                    | 31-4  |

| 31.2.2     | ポート A ポートレジスタ L ( PAPRL )                    | 31-5  |

| 31.2.3     | ポート B データレジスタ H、L ( PBDRH、 PBDRL )           | 31-6  |

| 31.2.4     | ポート B ポートレジスタ H、L ( PBPRH、 PBPRL )           | 31-8  |

| 31.2.5     | ポート C データレジスタ L ( PCDRL )                    | 31-9  |

| 31.2.6     | ポート C ポートレジスタ L ( PCPRL )                    | 31-10 |

| 31.2.7     | ポート D データレジスタ L ( PDDRL )                    | 31-11 |

| 31.2.8     | ポート D ポートレジスタL ( PDPRL )                     | 31-12 |

| 31.2.9     | ポートEデータレジスタL(PEDRL)                          | 31-13 |

| 31.2.10    | ポートEポートレジスタL(PEPRL)                          | 31-14 |

| 31.2.11    | ポートFデータレジスタL(PFDRL)                          | 31-15 |

| 31.2.12    | ポートFポートレジスタL(PFPRL)                          | 31-16 |

| 31.2.13    | ポート G データレジスタ L ( PGDRL )                    | 31-17 |

| 31.2.14    | ポート H データレジスタ L ( PHDRL )                    | 31-18 |

| 31.2.15    | ポート H ポートレジスタL ( PHPRL )                     | 31-19 |

| 31.2.16    | ポート J データレジスタ L ( PJDRL )                    | 31-20 |

| 31.2.17    | ポート J ポートレジスタ L ( PJPRL )                    | 31-21 |

| 31.2.18    | ポート K データレジスタ L ( PKDRL )                    | 31-22 |

| 31.2.19    | ポート K ポートレジスタ L ( PKPRL )                    | 31-23 |

| 31.3 使     | F用上の注意事項                                     | 31-24 |

| 32. 内蔵 R   | AM                                           | 32-1  |

| 32.1 特     | ·長                                           | 32-1  |

| 32.2 使     | <br>  用上の注意事項                                | 32-3  |

| 32.2.1     | ページ競合                                        |       |

| 32.2.2     | RAME ビット、RAMWE ビットについて                       |       |

| 32.2.3     | データ保持について                                    |       |

|            |                                              |       |

| 33.  | 低消    | <b>i</b> 費電力モード                       | 33-1  |

|------|-------|---------------------------------------|-------|

| 33.1 |       | 低消費電力モードの種類                           | 33-1  |

| 33.2 |       | レジスタ説明                                | 33-3  |

| 33.  | .2.1  | スタンバイコントロールレジスタ 1(STBCR1)             | 33-4  |

| 33.  | .2.2  | スタンバイコントロールレジスタ 2(STBCR2)             | 33-5  |

| 33.  | .2.3  | スタンバイコントロールレジスタ 3(STBCR3)             | 33-6  |

| 33.  | .2.4  | スタンバイコントロールレジスタ 4(STBCR4)             | 33-8  |

| 33.  | .2.5  | スタンバイコントロールレジスタ 5(STBCR5)             | 33-9  |

| 33.  | .2.6  | スタンバイコントロールレジスタ 6 ( STBCR6 )          | 33-10 |

| 33.  | .2.7  | スタンバイコントロールレジスタ 7(STBCR7)             | 33-11 |

| 33.  | .2.8  | システムコントロールレジスタ 1(SYSCR1)              | 33-12 |

| 33.  | .2.9  | システムコントロールレジスタ 2(SYSCR2)              | 33-13 |

| 33.  | .2.10 | ) システムコントロールレジスタ 3(SYSCR3)            | 33-14 |

| 33.  | .2.11 | 1 システムコントロールレジスタ 4(SYSCR4)            | 33-14 |

| 33.  | .2.12 | 2 システムコントロールレジスタ 5(SYSCR5)            | 33-14 |

| 33.  | .2.13 | 3 システムコントロールレジスタ 6(SYSCR6)            | 33-14 |

| 33.  | .2.14 | 4 システムコントロールレジスタ 7(SYSCR7)            | 33-15 |

| 33.  | .2.15 | 5 システムコントロールレジスタ 8(SYSCR8)            | 33-16 |

| 33.  | .2.16 | 5 システムコントロールレジスタ 9 ( SYSCR9 )         | 33-17 |

| 33.  | .2.17 | 7 システムコントロールレジスタ 10 ( SYSCR10 )       | 33-17 |

| 33.  | .2.18 | 8 システムコントロールレジスタ 11(SYSCR11)          | 33-17 |

| 33.  | .2.19 | シーシステムコントロールレジスタ 12(SYSCR12)          | 33-17 |

| 33.  | .2.20 | ) ソフトウェアリセットコントロールレジスタ ( SWRSTCR )    | 33-18 |

| 33.  | .2.21 | 1 ハイインピーダンスコントロールレジスタ(HIZCR)          | 33-19 |

| 33.  | .2.22 | 2 CPU0、1 モードステータスレジスタ ( COMSR、C1MSR ) | 33-20 |

| 33.  | .2.23 | 3 保持用内蔵 RAM 保持エリア指定レジスタ(RRAMKP)       | 33-21 |

| 33.  | .2.24 | 4 ディープスタンバイコントロールレジスタ ( DSCTR )       | 33-22 |

| 33.  | .2.25 | 5 ディープスタンバイ解除要因セレクトレジスタ(DSSSR)        | 33-23 |

| 33.  | .2.26 | 5 ディープスタンバイ解除要因フラグレジスタ(DSFR)          | 33-24 |

| 33.3 |       | 動作説明                                  | 33-26 |

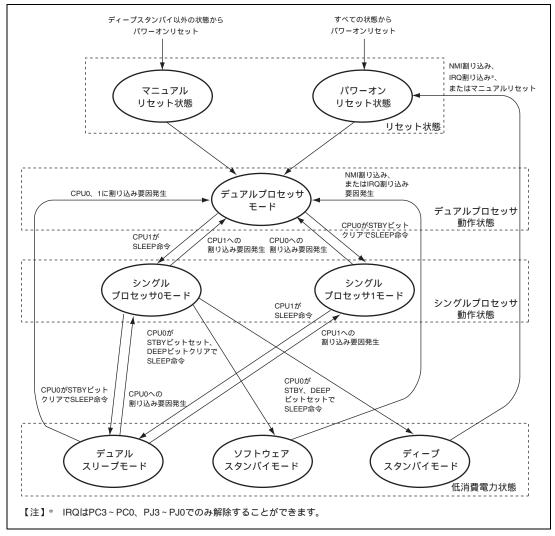

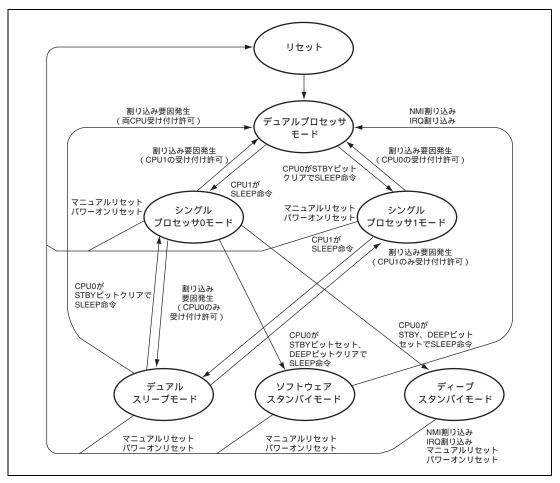

| 33.  | .3.1  | 低消費電力モードでの状態遷移                        | 33-26 |

| 33.  | .3.2  | デュアルプロセッサモード                          | 33-26 |

| 33.  | .3.3  | シングルプロセッサモード                          | 33-27 |

| 33.  | .3.4  | デュアルスリープモード                           | 33-27 |

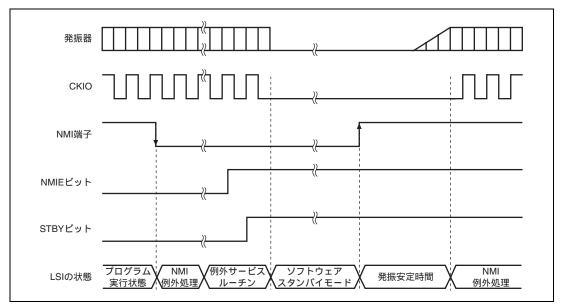

| 33.  | .3.5  | ソフトウェアスタンパイモード                        | 33-28 |

| 33.  | .3.6  | ソフトウェアスタンバイモードの応用例                    | 33-31 |

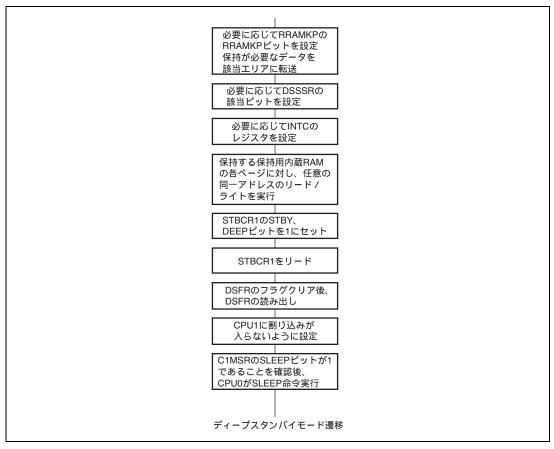

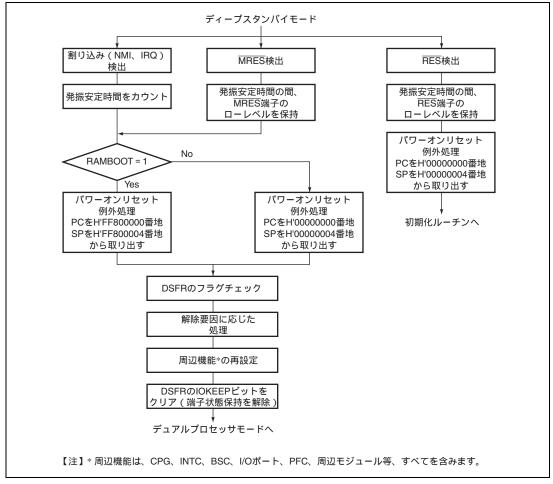

| 33.  | .3.7  | ディープスタンバイモード                          | 33-32 |

| 33.  | .3.8  | モジュールスタンバイ機能                          | 33-37 |

| 33.4 |       | 使用上の注意事項                              | 33-38 |

| 33   | 4.1   | レジスタ書き込みに関する注意事項                      | 33-38 |

| 33.4.2 | ディープスタンバイコントロールレジスタ ( DSCTR ) に関する注意事項 | 33-38  |

|--------|----------------------------------------|--------|

| 33.4.3 | パワーオンリセット例外処理に関する注意事項                  | 33-38  |

|        |                                        |        |

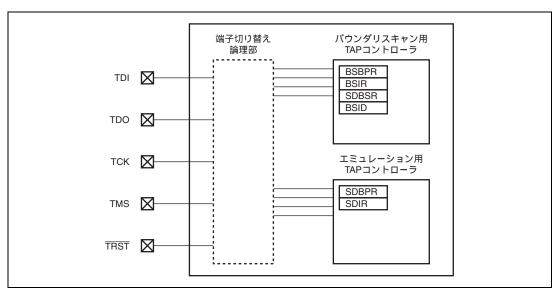

| 34. ユー | -ザデバッグインタフェース(H-UDI)                   | 34-1   |

| 34.1   | 特長                                     | 34-1   |

| 34.2   | 入出力端子                                  | 34-2   |

| 34.3   | バウンダリスキャン用TAPコントローラのレジスタの説明            | 34-3   |

| 34.3.1 | バイパスレジスタ ( BSBPR )                     | 34-3   |

| 34.3.2 | インストラクションレジスタ(BSIR)                    | 34-3   |

| 34.3.3 | バウンダリスキャンレジスタ ( SDBSR )                | 34-4   |

| 34.3.4 | ID レジスタ ( BSID )                       | 34-9   |

| 34.4   | エミュレーション用TAPコントローラのレジスタの説明             | 34-10  |

| 34.4.1 | バイパスレジスタ(SDBPR)                        | 34-10  |

| 34.4.2 | インストラクションレジスタ(SDIR)                    | 34-10  |

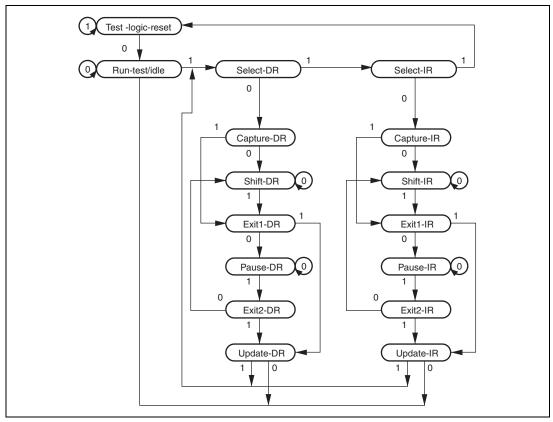

| 34.5   | 動作説明                                   | 34-12  |

| 34.5.1 | TAP コントローラ                             | 34-12  |

| 34.5.2 | リセット構成                                 | 34-13  |

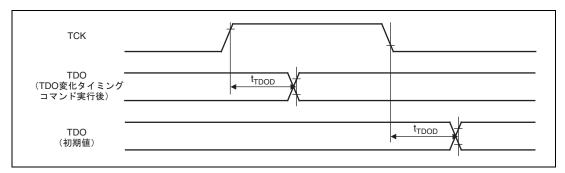

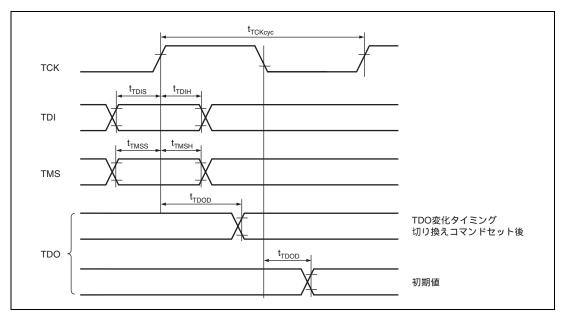

| 34.5.3 | TDO 出力タイミング                            | 34-13  |

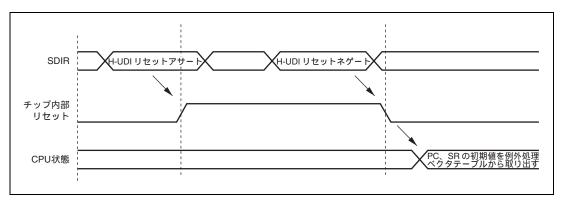

| 34.5.4 | H-UDI リセット                             | 34-14  |

| 34.5.5 | H-UDI 割り込み                             | 34-14  |

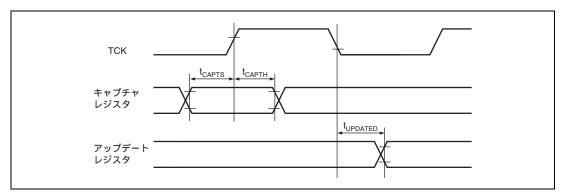

| 34.6   | バウンダリスキャン                              | 34-15  |

| 34.6.1 | サポートする命令                               | 34-15  |

| 34.6.2 | 注意事項                                   | 34-16  |

| 34.7   | 使用上の注意事項                               | 34-17  |

|        |                                        |        |

| 35. レシ | 『スター覧                                  | 35-1   |

| 35.1   | レジスタアドレス一覧 (機能モジュールごと、マニュアル章番号順)       | 35-2   |

| 35.2   | レジスタビット一覧                              | 35-37  |

| 35.3   | 各動作モードにおけるレジスタの状態の一覧                   | 35-121 |

|        |                                        |        |

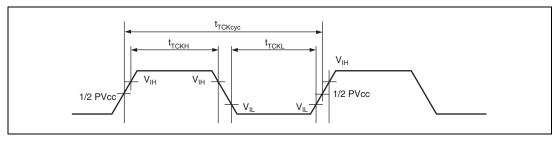

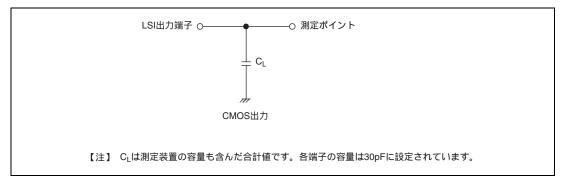

| 36. 電気 | 5的特性                                   | 36-1   |

| 36.1   | 絶対最大定格                                 | 36-1   |