# Go Configure<sup>™</sup> Software Hub User Guide

# Contents

| 1 | Intro | Introduction       |                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|---|-------|--------------------|-----------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

|   | 1.1   | Quick              | start 5                           |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 1.1.1              | System requirements               |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 1.1.2              | Getting started                   |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 1.1.3              | Support                           |  |  |  |  |  |  |  |  |  |  |  |  |

| 2 | Soft  | oftware overview 6 |                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1   | Design tools       |                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.1              | Interface overview                |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.2              | Working with project files        |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.3              | NVM viewer                        |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.4              | Components                        |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.5              | Connections                       |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.6              | Keyboard commands                 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.7              | Settings                          |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.8              | Legend box                        |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.9              | Help window                       |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       |                    | Snipping tool                     |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       |                    | Rule checker                      |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       |                    | Comparison tool                   |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       |                    | Power Dissipation Calculator      |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       |                    | Acceleration Profile Configurator |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       |                    | Reg File Configurator             |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2   |                    | tools                             |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2   | 2.2.1              | Hardware sources                  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.2.2              | Generators                        |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.2.3              | Signal Wizard                     |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.2.4              | Custom Signal Wizard              |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.2.5              | Hardware configurations           |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.2.6              | Debugging Controls                |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.2.7              | Project data window               |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.2.7              | Demo Board and Demo mode          |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.2.9              | I2C Tools                         |  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | ۷.۷.۶              | 120 10015                         |  |  |  |  |  |  |  |  |  |  |  |  |

|     | 2.2.10 I2C I/O Tool                                    | 94       |

|-----|--------------------------------------------------------|----------|

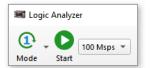

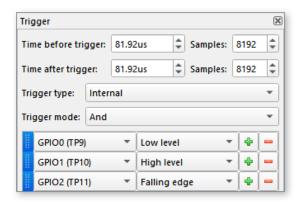

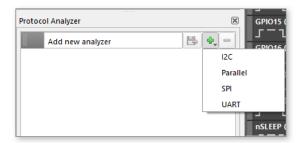

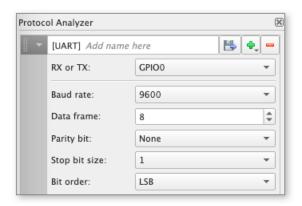

|     | 2.2.11 Logic Analyzer                                  | 96       |

|     |                                                        | )4       |

|     |                                                        | )5       |

|     |                                                        | 70       |

|     | 5                                                      | )9       |

|     | · •                                                    | 10       |

|     | 2.2.17 Go Configure Driver Tool                        | _        |

| 2.3 |                                                        | 14       |

| 2.3 |                                                        | 14<br>14 |

|     |                                                        |          |

|     |                                                        | 18       |

|     |                                                        | 22       |

|     | - , , , , , , , , , , , , , , , , , , ,                | 24       |

|     |                                                        | 28       |

| 2.4 |                                                        | 30       |

|     | ,                                                      | 31       |

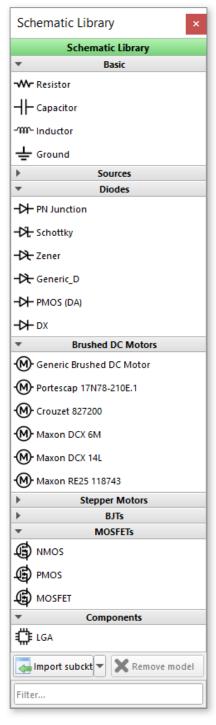

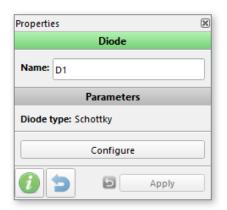

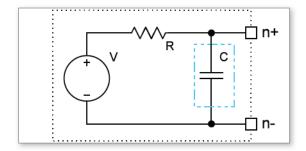

|     | 2.4.2 External components                              | 32       |

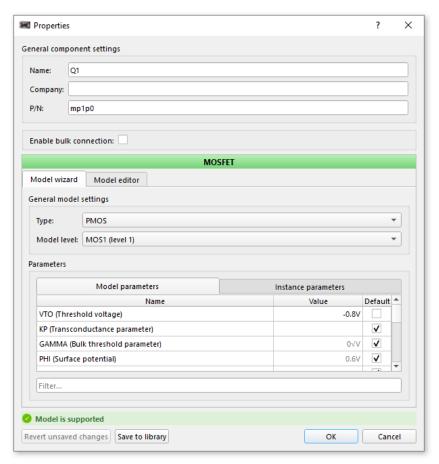

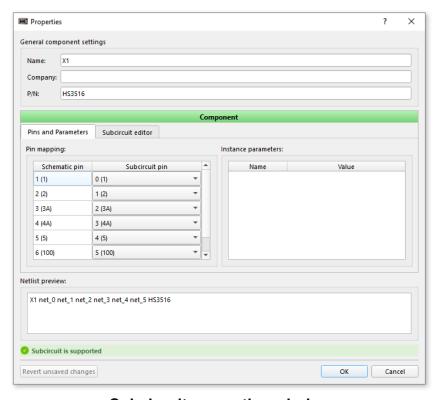

|     | 2.4.3 Working with models and subcircuits              | 33       |

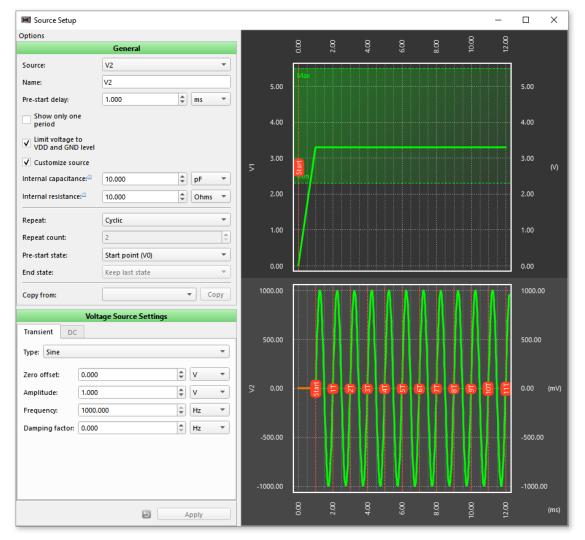

|     | 2.4.4 Source Setup                                     | 37       |

|     |                                                        | 40       |

|     |                                                        | 41       |

|     |                                                        | 43       |

|     |                                                        | 45       |

|     | 1 3                                                    | 46       |

| 2.5 |                                                        | 52       |

| 0   |                                                        | 52       |

|     |                                                        | 53       |

|     |                                                        | 57       |

|     | 5 1                                                    | 30       |

|     | 5 5                                                    | 30<br>31 |

|     | ,                                                      | 33       |

|     | ,                                                      |          |

|     | <b>3</b>                                               | 36       |

|     | , , , , , , , , , , , , , , , , , ,                    | 70       |

|     |                                                        | 72       |

|     |                                                        | 73       |

|     | <del>g</del>                                           | 74       |

|     | 2.5.12 Settings                                        | 77       |

| _   | <b>.</b> -                                             |          |

| Dev |                                                        | -        |

| 3.1 |                                                        | 30       |

|     | '                                                      | 30       |

|     | · ·                                                    | 32       |

|     | ·                                                      | 34       |

|     | 33                                                     | 37       |

|     |                                                        | 39       |

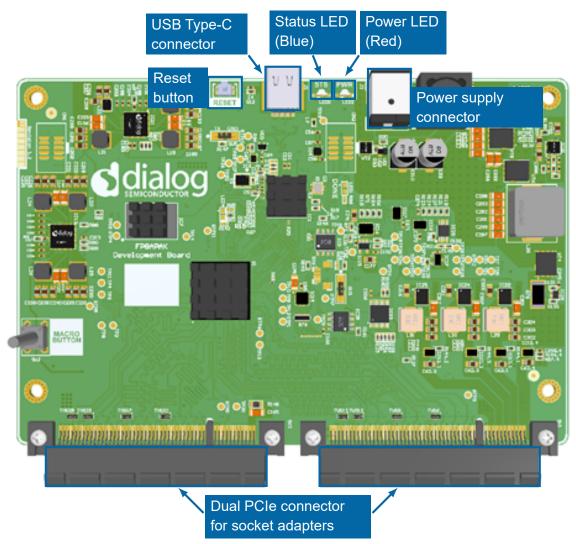

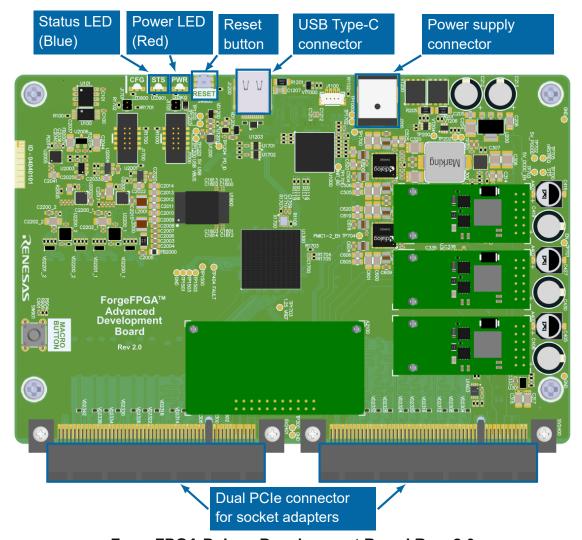

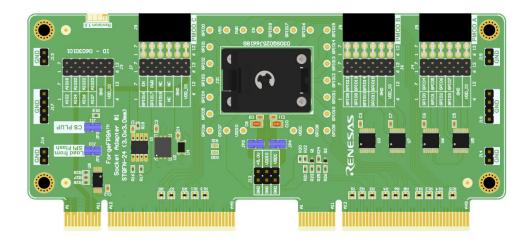

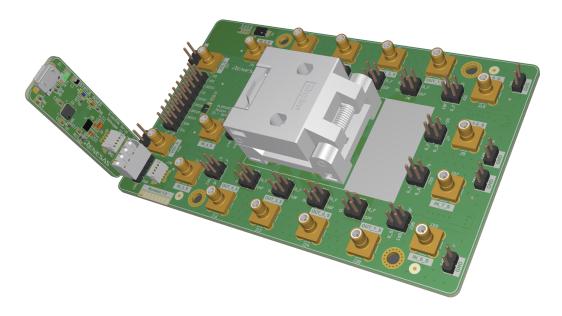

| 3.2 | <b>o</b>                                               | 91       |

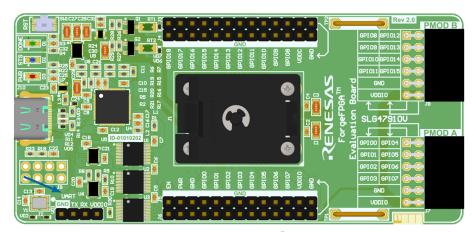

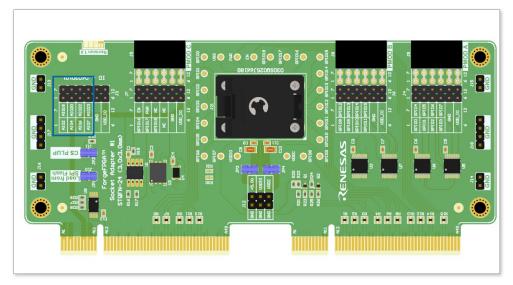

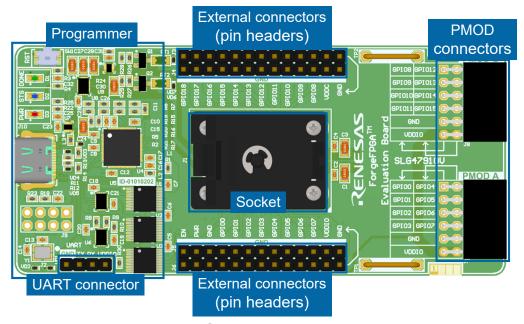

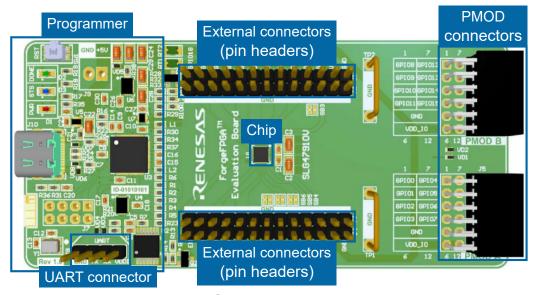

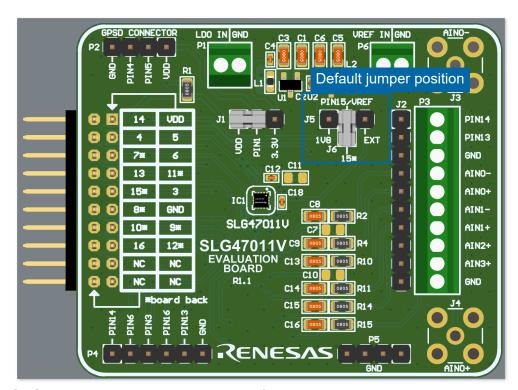

|     | 3.2.1 ForgeFPGA <sup>™</sup> Deluxe Development Boards | 91       |

|     | <b></b>                                                | 96       |

| 3 3 | · · · · · · · · · · · · · · · · · · ·                  | วล       |

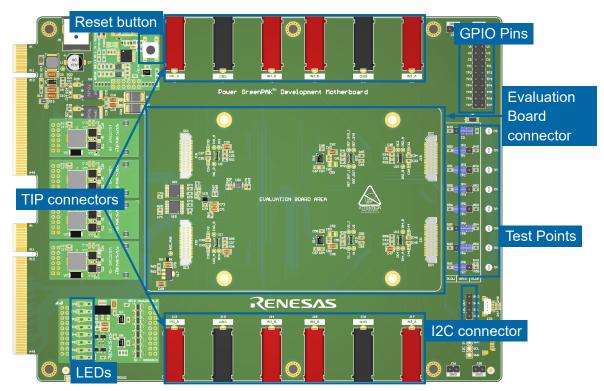

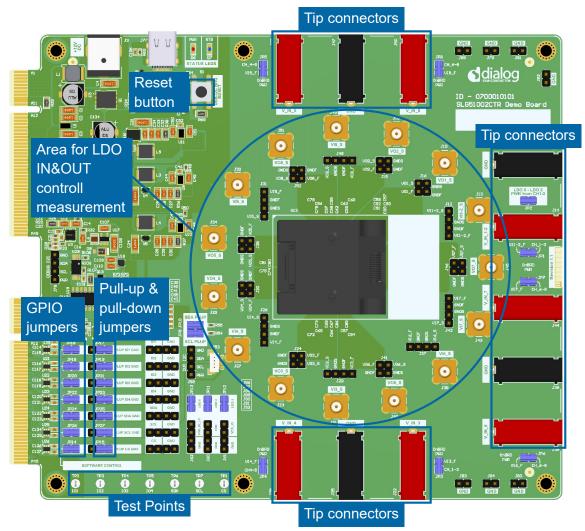

|   |      | 3.3.1   | Power GreenPAK     | Developm    | nent M | othe | erbo | oard | ١. |  |  |  | <br> |   | <br> |       | 198 |

|---|------|---------|--------------------|-------------|--------|------|------|------|----|--|--|--|------|---|------|-------|-----|

|   |      | 3.3.2   | Power GreenPAK     | -           |        |      |      |      |    |  |  |  |      |   |      |       |     |

|   |      | 3.3.3   | Connecting exteri  |             |        |      |      |      |    |  |  |  |      |   |      |       |     |

| 4 | How  | / to    |                    |             |        |      |      |      |    |  |  |  |      |   |      |       | 205 |

|   | 4.1  | Softwa  | re update          |             |        |      |      |      |    |  |  |  | <br> | _ |      | <br>_ | 206 |

|   |      |         | g                  |             |        |      |      |      |    |  |  |  |      |   |      |       |     |

|   |      |         | Print              |             |        |      |      |      |    |  |  |  |      |   |      |       |     |

|   |      |         | Print Editor (obso |             |        |      |      |      |    |  |  |  |      |   |      |       |     |

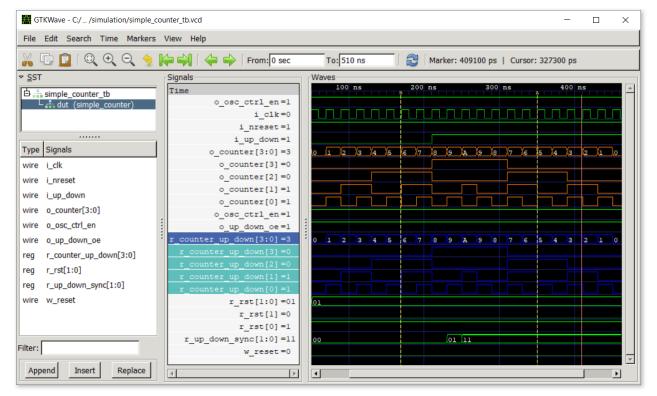

|   | 4.3  |         | Verilog and GTKV   | -           |        |      |      |      |    |  |  |  |      |   |      |       |     |

|   |      | 4.3.1   | Installation       | -           |        |      |      |      |    |  |  |  |      |   |      |       |     |

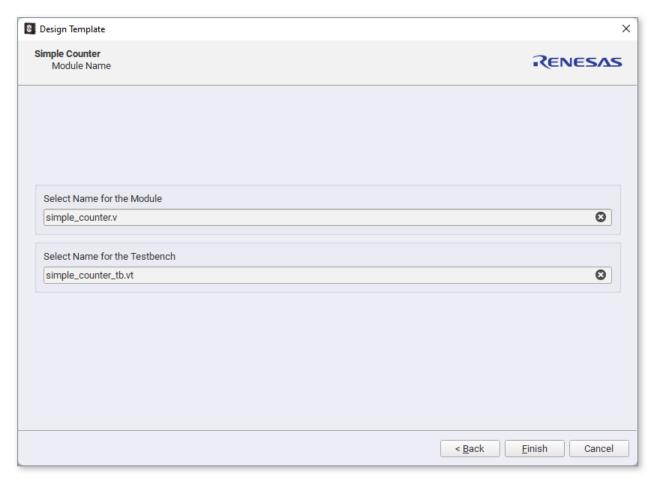

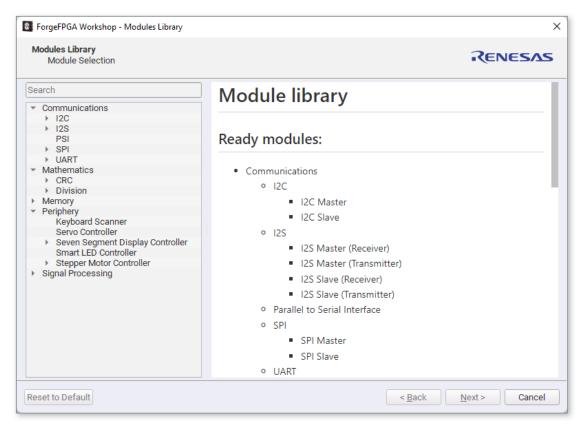

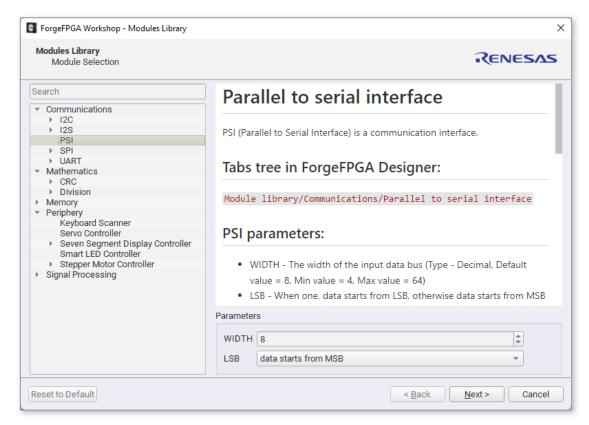

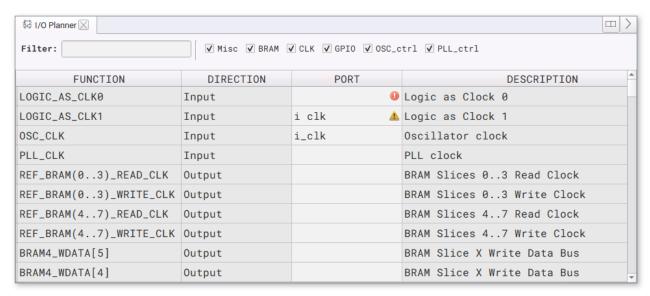

|   |      |         | Quick start        |             |        |      |      |      |    |  |  |  |      |   |      |       |     |

| 5 | Troi | ublesho | ooting             |             |        |      |      |      |    |  |  |  |      |   |      |       | 213 |

| J |      |         | Socket Test        |             |        |      |      |      |    |  |  |  | <br> |   |      |       |     |

|   |      |         |                    |             |        |      |      |      |    |  |  |  |      |   |      |       |     |

| 6 |      |         |                    |             |        |      |      |      |    |  |  |  | 215  |   |      |       |     |

|   | 6.1  | Main n  | nenu commands .    |             |        |      |      |      |    |  |  |  | <br> |   |      |       | 216 |

|   | 6.2  | Keybo   | ard and mouse co   | ntrols      |        |      |      |      |    |  |  |  | <br> |   |      |       | 218 |

|   | 6.3  | Debug   | ging Controls feat | ure availab | ility  |      |      |      |    |  |  |  | <br> |   |      |       | 221 |

|   | 6.4  |         | viations           |             |        |      |      |      |    |  |  |  |      |   |      |       |     |

|   | 6.5  | Chang   | elog               |             |        |      |      |      |    |  |  |  |      |   |      |       | 223 |

## 1 Introduction

Renesas Go Configure<sup>™</sup> Software Hub is a full-featured Integrated Development Environment (IDE) that enables a completely graphical design process, allowing you to configure, program and simulate custom circuits in minutes.

This guide provides the information for the usage of *Go Configure Software Hub*, describing the features for *Renesas* products, such as  $GreenPAK^{\mathsf{TM}}$ , AnalogPAK,  $HVPAK^{\mathsf{TM}}$ , Power GreenPAK, AutomotivePAK, and  $ForgeFPGA^{\mathsf{TM}}$  Workshop.

## 1.1 Quick start

## 1.1.1 System requirements

Minimum system requirements for Go Configure Software Hub:

➤ CPU: Dual core 2.5 GHz

> RAM: 8 GB

➤ GPU: 128 MB

> Free disk space: 2 GB

➤ OS: Windows 10/11, macOS 11 or higher, Ubuntu 22.04/24.04, Debian 12/Testing

## 1.1.2 Getting started

- 1. Download and install Go Configure Software Hub

- 2. Open the particular chip Part Number

- 3. Select the components for your project

- 4. Specify the pinout

- 5. Configure and interconnect the components

- 6. Test the design with the *Debug Tool*, using *Simulation* feature or any of the supported hardware development platforms

## 1.1.3 Support

In case you need more information about *Go Configure Software Hub*, online support is available at www.renesas.com.

You can also find *Go Configure Software Hub* on *Renesas* social media. To visit the page, go to  $Help \rightarrow Social$  in the main menu.

The latest version of the software application is available on the Renesas website, on Software page.

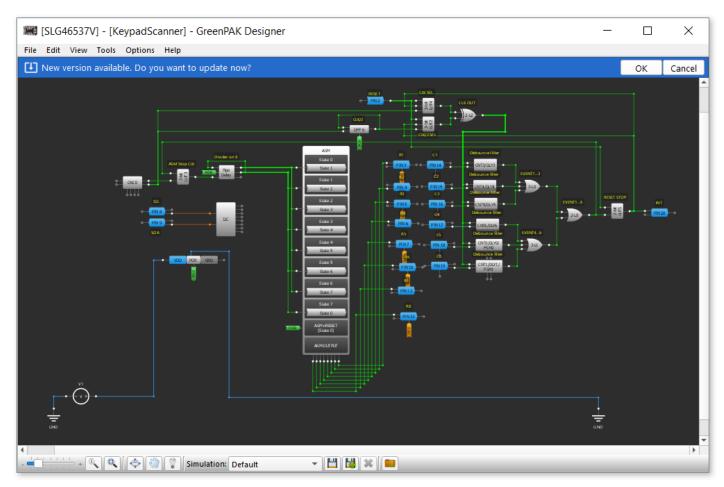

Go Configure Software Hub notifies about pending software updates. You can learn more in section 4.1 Software update.

## 2 Software overview

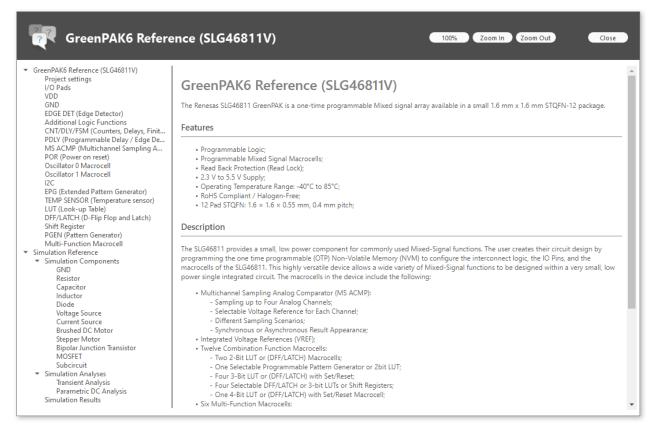

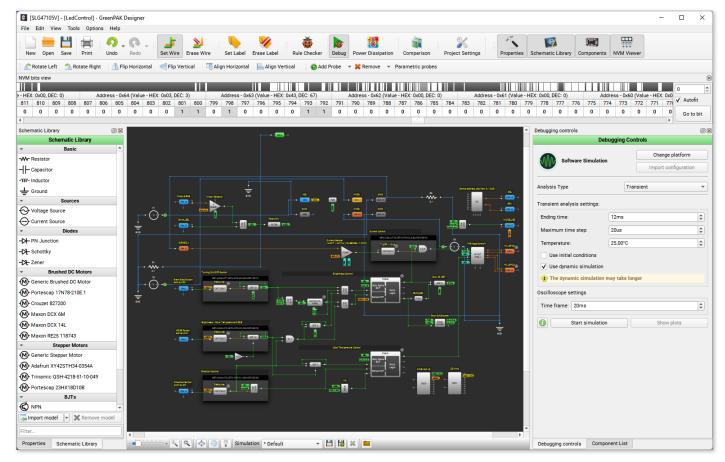

The Go Configure Software Hub was designed to provide direct access to all GreenPAK, SLG51000/1, and ForgeFPGA device features and complete control over the routing and configuration options.

In this chapter, you'll find detailed explanations for various tools to simplify your workflow. These tools allow you to program a chip with your custom design, import data from a programmed part, and simulate with external components. This chapter will also become your guide to exploring the software interface and understanding essential tools like debug tools, asynchronous state machine, software simulation, and FPGA editor, etc.

## 2.1 Design tools

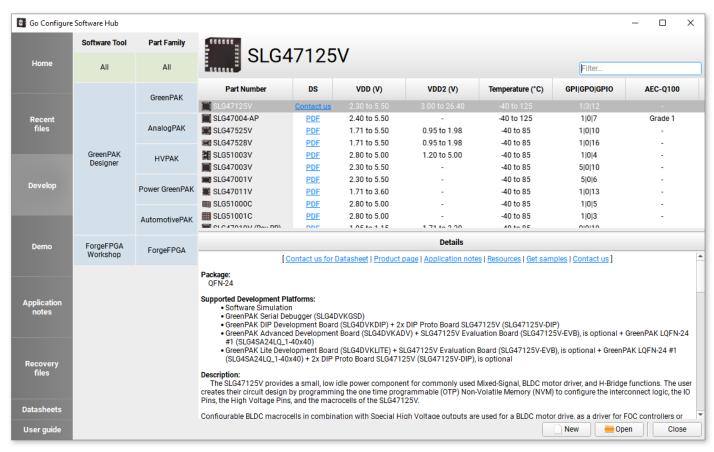

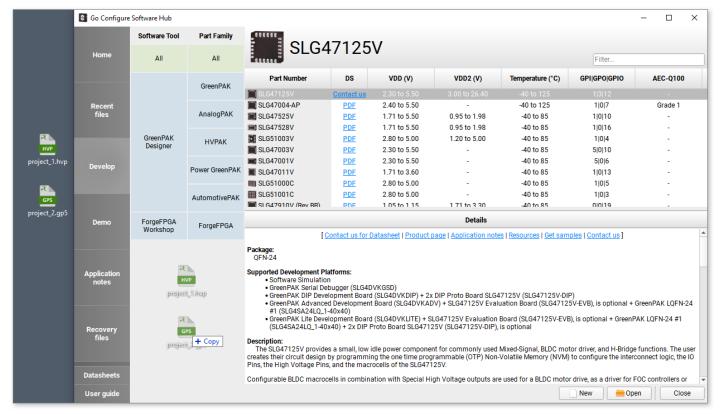

Start your project from the *Hub* window with the following sections:

- Home useful info and tips for new users

- Recent files the list of the recently opened project files

- Develop the chip Part Number selection. See the Details section to learn more about the selected chip

At the bottom of the window, you can find the *New*, *Open*, and *Close* buttons, which allow you to start a new project for a selected Part Number, open an existing project or close the *Go Configure Software Hub*. The *Datasheets* and *User Guides* buttons redirect you to the *Renesas* website, where you can download the corresponding files.

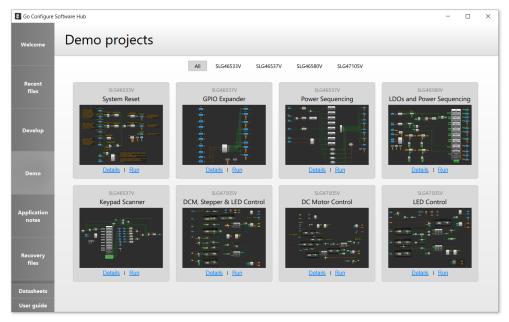

- ▶ Demo the list of Demo projects. You can use the specific Demo Board for the project debugging (read more in section 2.2.8 Demo Board and Demo mode)

- ➤ Application notes design examples for different purposes. An application note includes a design description with various Integrated Circuits (ICs) and a preconfigured circuit project, where you can make customized changes

- Recovery files restored project files after a crash or freeze. To read more refer to section 2.1.7 Settings

Go Configure Software Hub User Interface

#### 2.1.1 Interface overview

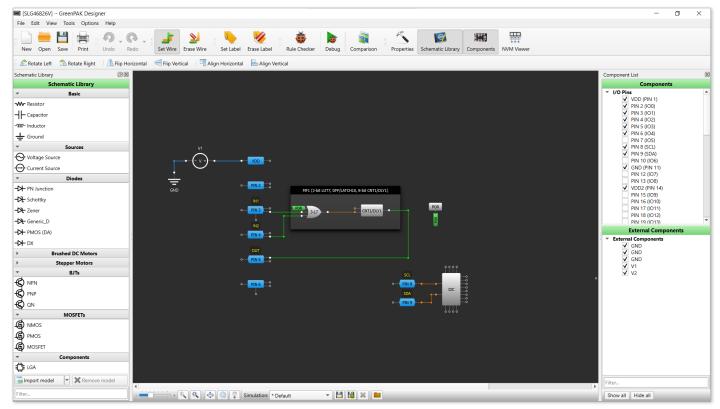

The basic interface elements are main menu, toolbar, work area, work area controls, properties panel, and component list.

#### Main menu

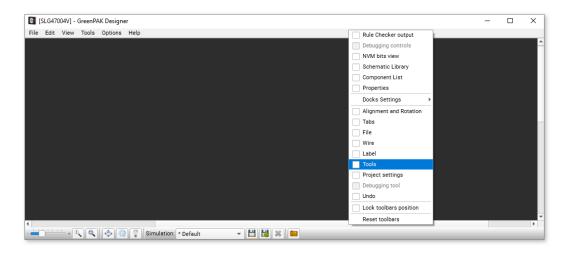

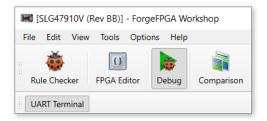

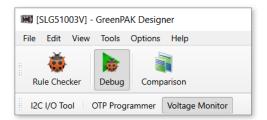

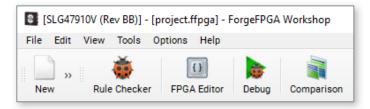

After you select the Part Number and start the project, you can see the menu bar with the following items: *File*, *Edit*, *View*, *Tools*, *Options* and *Help*. See the full description of all the menu commands in section 6.1 Main menu commands.

Main menu

#### **Toolbar**

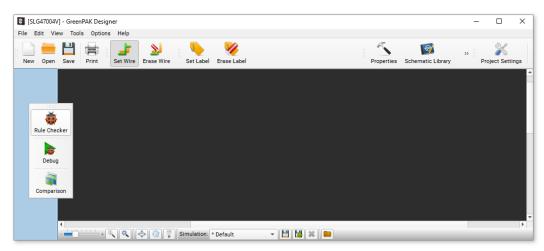

The toolbar items are located under the menu bar by default. Move, show, and hide toolbar items to customize the environment. Use *Settings* to reset the *Appearance*.

**Toolbar customization**

#### Work area

The work area displays the selected components (macrocells) from the component list and the connections between them. The Part Numbers contain different sets of macrocells, therefore the IDE's interface varies.

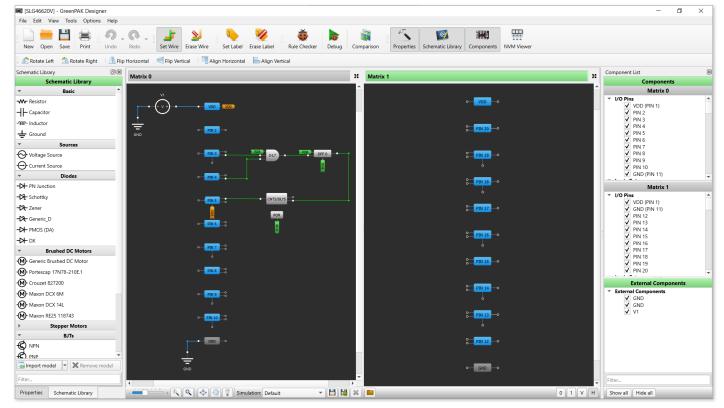

The IDE may contain one or two work areas (an example of Part Number with two work areas is SLG46620V).

Part Number with one work area

Part Number with two work areas

The Part Numbers with two work areas have several distinctive buttons, which define the matrix window placement:

Matrices' window placement

- ➤ 0 only *Matrix* 0 is displayed

- ➤ 1 only *Matrix* 1 is displayed

- V both matrices are displayed vertically (on top of each other)

- ➤ H both matrices are displayed horizontally (beside each other)

- makes one of the matrices a separate window

The *Matrix* title bar turns green when the work area is in focus.

#### Work area controls

You can find the additional work area controls on the bottom toolbar.

Work area controls

Adjust the work area (zoom, fit the work area or make it full-screen)

Enable the *Pan mode* to move the work area (click and hold the middle mouse button as an alternative)

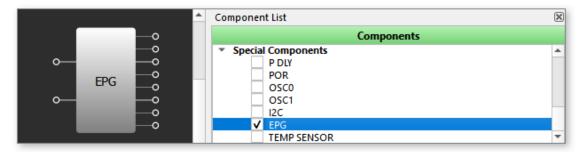

## **Component list**

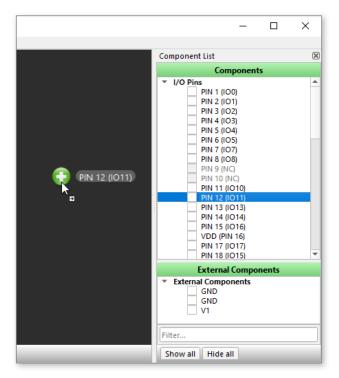

This panel contains a list of available macrocells in a chip. You can show, hide, or search for the components via the list.

Show/hide a component by using the checkbox next to its name.

Drag and drop a block from the list to the work area.

**Checkbox / Drag and Drop**

You can use filter to easily search for the required component. Show/hide all the components by using *Show all* and *Hide all* buttons.

**Note 1:** A hidden component retains the configurations set on its properties panel (see more info about the *Properties* panel).

**Note 2:** It is not possible to hide connected blocks (see sections 2.1.4 Components and 2.1.5 Connections to find out more).

#### **Properties panel**

The panel contains all settings available for a selected component. The set of properties may vary depending on the macrocell.

The Properties panel may contain:

- > Settings and parameters that can be specified for a selected block

- > Settings that control the predefined connections to a selected block

**Properties panel**

Once you change the property values, you can Apply or Revert the modifications.

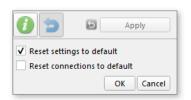

After changes are applied, it is possible to *Reset* the changes. The following options may be available: *Reset connections to default*, *Reset settings to default* or *Reset configurations to default* (the latter is available only for the components with more than one mode, e.g. LUT).

Property reset feature

You can also Reset the block via the component's context menu.

### 2.1.2 Working with project files

A project file is the latest saved state of the designed project. The file contains component configurations, connections between blocks, component location on the work area, etc.

File operations

#### Create/Save/Open a project

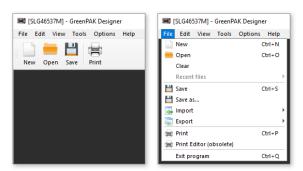

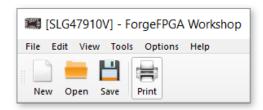

You can start a new project from the Hub window (click the Part Number  $\to New$ ) or from an opened instance (click the New icon on the toolbar or  $File \to New$ )

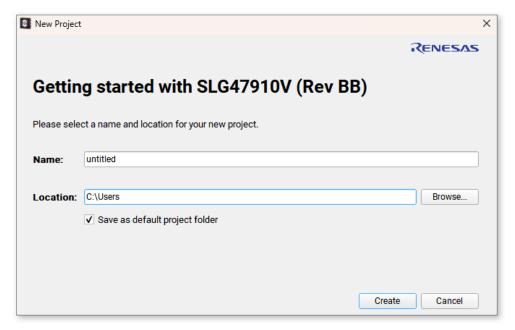

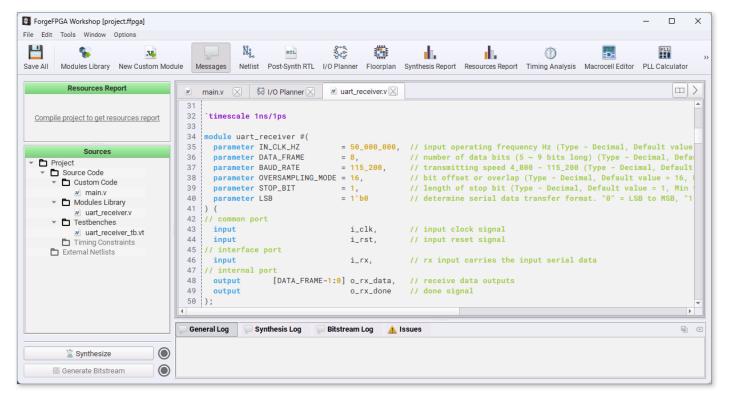

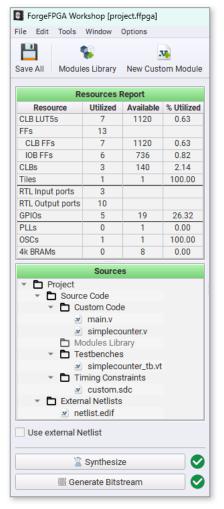

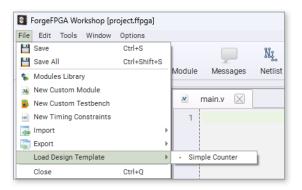

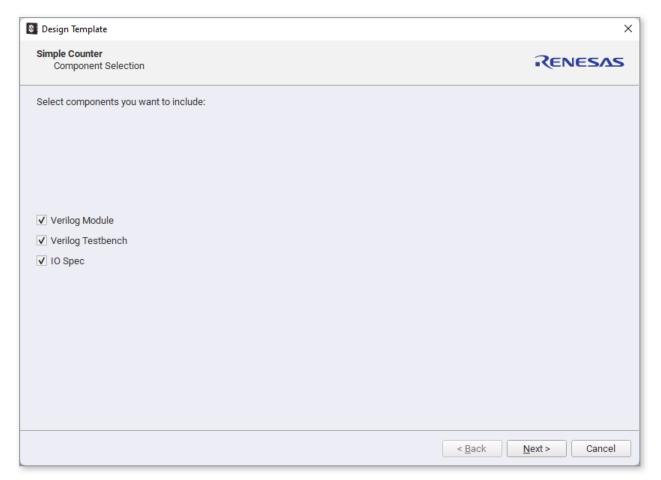

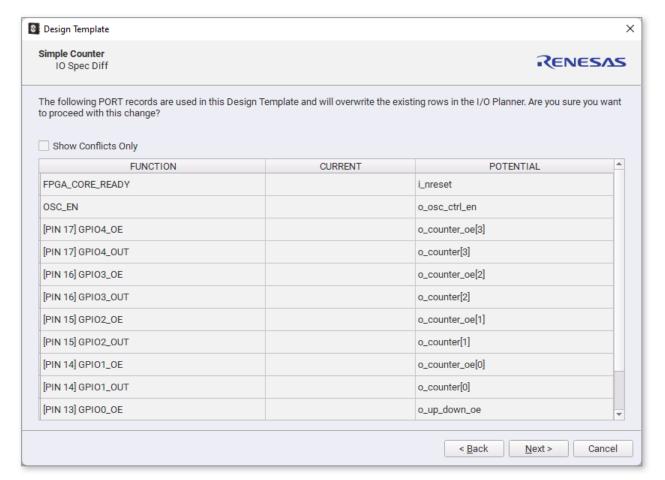

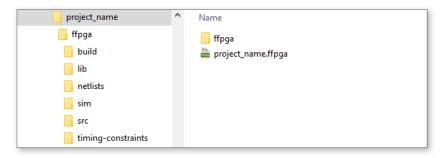

**Note:** For the *FPGA* Part Number (e.g. SLG47910), once you select it from the Part Numbers list in the *Hub* window, you will be prompted to create the project via the *New Project* window. Upon clicking *Create*, the *FPGA* project directory will appear in the specified location.

Window for FPGA project creation

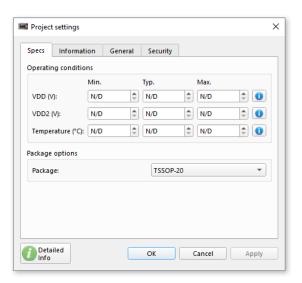

Once you start a new project, the *Project settings* window appears. You can skip this step, but once the data is needed, you'll be asked to fill it in again. Read more about *Project settings* window later in this section.

The default project (state of the work area right after you open a new project) is usually configured for minimal power consumption. That is why some components are disabled.

To save your project click the Save icon on the toolbar, or click File  $\rightarrow$  Save/Save as.

Change the folder to which the project is saved in Settings.

Project file folder

The supported project file extensions are: .aap, .can, .gp3, .gp4, .gp5, .gp6, .hvp, and .ppak (.gp1, .gp2, .gpp and .ldo are the obsolete file extensions).

There are several ways to open a project file:

- Open button on the Hub window

- ightharpoonup Open icon on the toolbar (or File ightharpoonup Open)

- ➤ Drag and drop the project file to the *Hub* window

- > Drag and drop the project file to the work area

- > Double-click the project file

It is also possible to open multiple project files at once using drag and drop feature.

Open a project file

**Note:** It is highly recommended not to make manual changes in the file to prevent from its corruption.

#### **Project settings window**

As mentioned earlier in this section, the *Project settings* window appears right after you start a new project. It contains four tabs: *Specs*, *Information*, *General*, and *Security*.

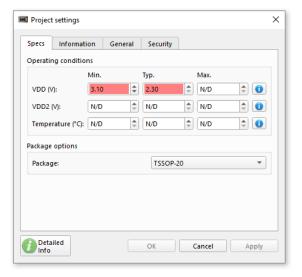

### **Specs**

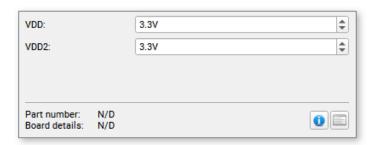

In *Specs*, you can see the fields to fill in the chip operating conditions, such as VDD and Temperature (Min., Typ. and Max). The Part Numbers may have one or multiple VDDs. Click the blue *information* button to see the recommended range within which the chip can operate safely.

The Part Numbers may support different packaging. The package can also be selected in the Specs

tab.

Project settings window examples

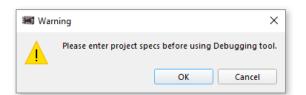

**Note:** You can close the *Project settings* window without entering the operating conditions. Working with *Simulation* or hardware development platforms in the *Debug tool* requires entering the specs. Once you click *Debug* on the toolbar while specs are not specified, a warning notification to add specs appears. Click the *OK* button on the warning window or the *Project Settings* icon on the toolbar to enter specs.

Warning to add specs to use Debug tool

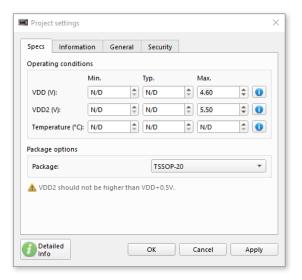

In case the improper operating conditions are filled in, a warning with the corresponding text message will appear. Some warning notifications do not stop you from applying the specs, while others require to fix them before the application. Here are the warning examples:

**Specs-related warning examples**

If e.g. Min. value is higher than Typ., and in other similar cases, the affected fields become highlighted in red. The specs cannot be applied until the issue is fixed.

Improper specs values

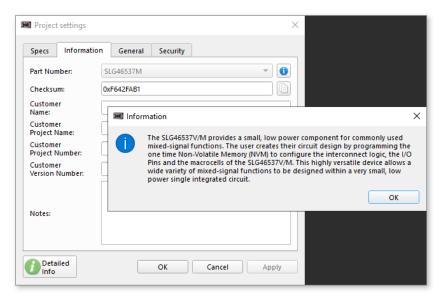

#### Information

The *Information* tab contains the short piece of information about the Part Number. To see the info, click the *Info* button.

Information tab

The checksum is a unique project identifier that can be used to distinguish between the projects. The *Checksum* field value is generated based on the project bits state in NVM. The project bits are chip configurations, such as macrocell settings, connectivity matrix and the project settings.

For *FPGA* Part Numbers (e.g. SLG47910), the OTP registers [0:191] are ignored during calculation. The FPGA core configuration bitstream is also taken into account upon computing the checksum.

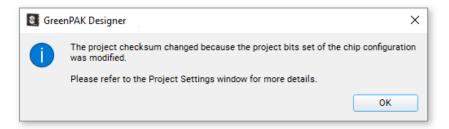

**Note:** The same project may show different checksums when opened in different software versions. The discrepancy occurs because the set of project bits used to compute the checksum, may vary between software versions. In this case, the warning will appear upon the project load. The checksum will be updated in the project file during the next save.

Project checksum update warning

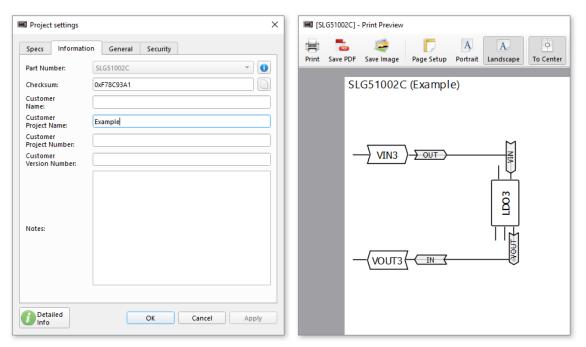

You can also see the input fields to fill in the information about the project. The entry in Customer

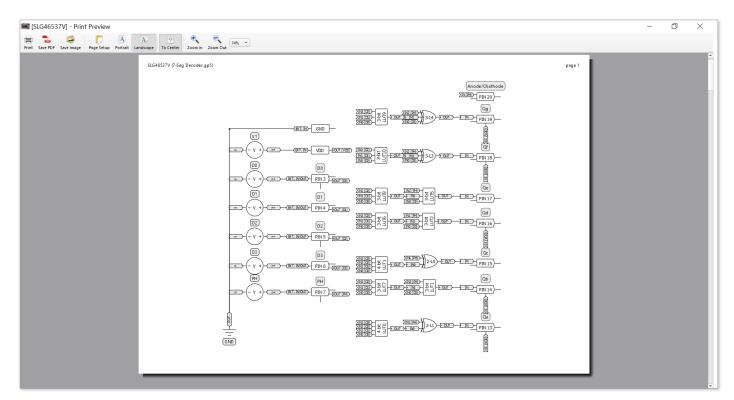

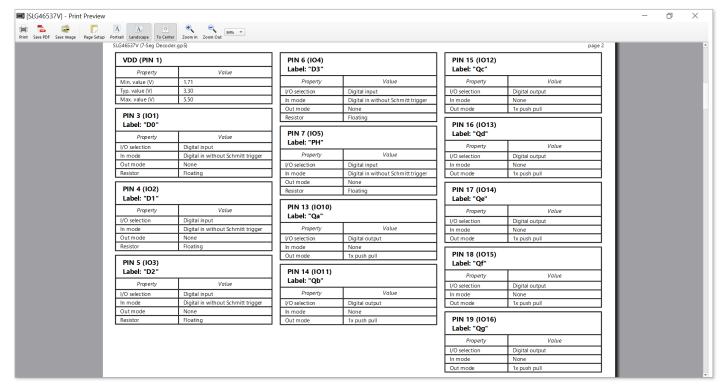

project name field is also displayed in Print Preview.

**Customer project name in Print Preview**

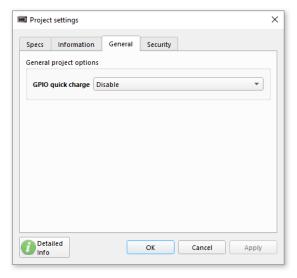

#### General

The *General* tab contains the global chip configurations. The set of settings varies depending on the Part Number.

General tab

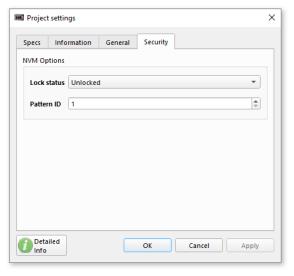

#### **Security**

Same as *General*, the *Security* tab includes global settings which typically grant access to the chip's data protection features. The common and important *Security* tab configurations are as follows:

- ➤ Lock status allows to protect read/write chip operations

- ➤ Pattern ID can be used for project versioning (the Pattern ID data can be read even for chips with read protection enabled)

Security tab

To find out more about the particular chip configurations, click the *Detailed info* button on the *Project settings* window or access the Datasheets through the *Hub* window.

**Detailed info button**

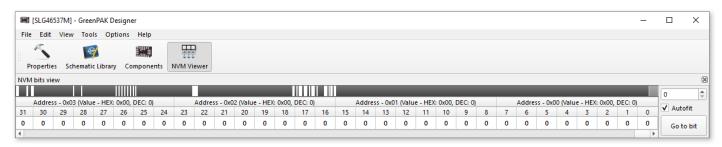

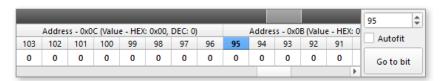

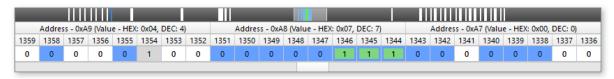

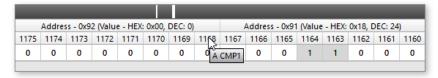

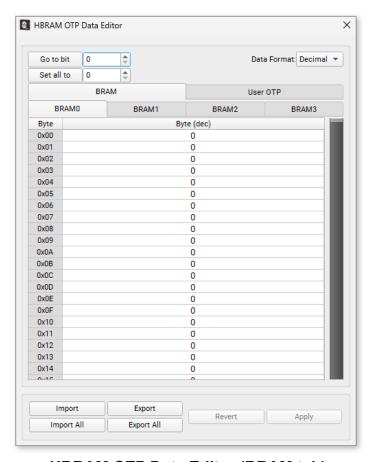

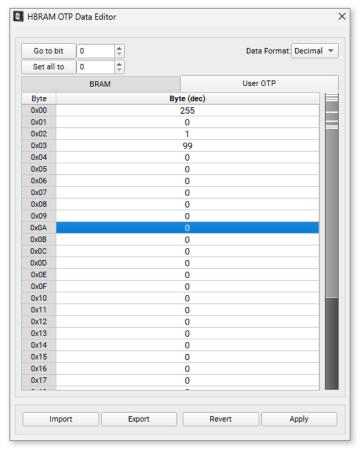

#### 2.1.3 NVM viewer

The non-volatile memory (NVM) tool represents the permanent memory of a chip. The NVM is grouped into bytes. Each byte is an 8-bit sequence. Above each byte, you can see the information about the byte's address along with its value in hexadecimal and decimal formats. NVM changes occur after modifying a macrocell's property or setting a connection between the blocks.

**NVM** viewer

NVM viewer cells can be in the following states:

- 0 bit range of a selected block

- 0 bits with 0 value

- 1 bits with 1 value

- 0 latest bit changed to 0 value

- 1 latest bit changed to 1 value

You can also use the *NVM viewer* controls for quick navigation through the bit table. Use the *Autofit* feature to jump directly to the bit range of the selected component.

**Autofit**

Click *Go to bit* once you enter a bit number (in the decimal format) to find the bit you need. The bit order number becomes highlighted after clicking a bit or using the *Go to bit* button.

Bit order number highlight

The *NVM viewer* navigation bar can also orient you to the location of selected or changed bits in the table (the color on the bar corresponds the cells color described above). In addition, black color represents 0 and white shows 1 values.

**NVM** viewer top bar

Hover the mouse cursor over the bit to see which macrocell this bit belongs to.

**NVM** hint

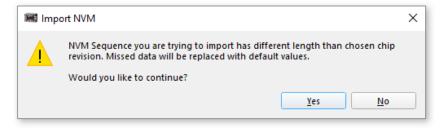

You can save or load the NVM sequence by clicking  $\textit{File} \rightarrow \textit{Import/Export}$  in the main menu (see the description of all main menu items in section 6.1 Main menu commands). If the imported file contains a different bit sequence length than the selected Part Number, the corresponding pop-up appears and it is possible to proceed with loading the data.

Import different NVM sequence length

### 2.1.4 Components

After you add a macrocell from the component list to the work area, you can choose how to interact with it. Move the component(s) using a mouse or a keyboard (see section 6.2 Keyboard and mouse controls). You can also use the toolbar widgets to rotate, flip, and align the selected block(s). To select more than one block click, hold, and drag over the components you want to select.

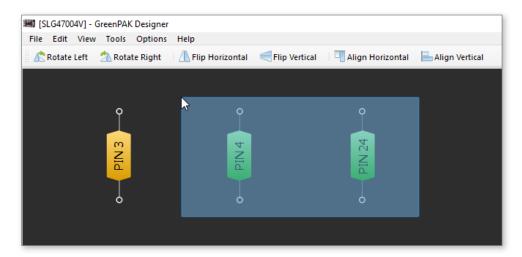

Selected block adjustment

#### **GreenPAK** chips components highlight

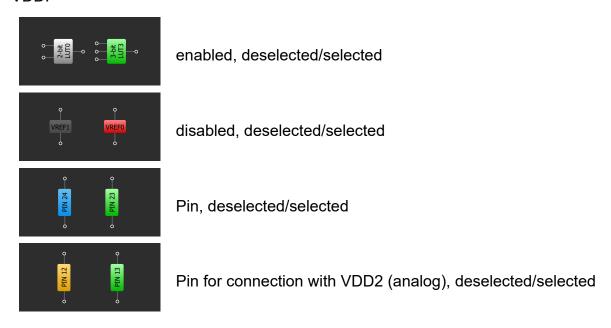

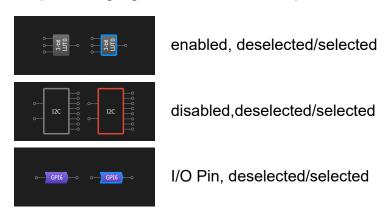

The macrocell color gives you information about its mode (enabled/disabled) and state (deselected/selected). Input/Output (I/O) Pin block's color informs about its relation to a particular VDD.

You can connect macrocells via the pins.

Hover the cursor over the block to see the pin hints. For more info about managing pin hints behavior, refer to section 2.1.7 Settings.

Pin hint

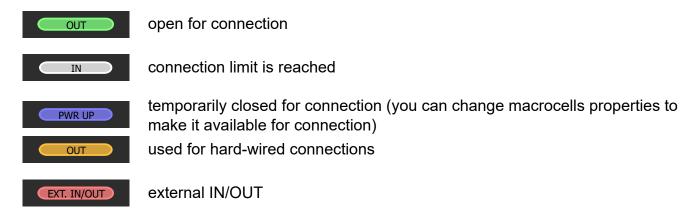

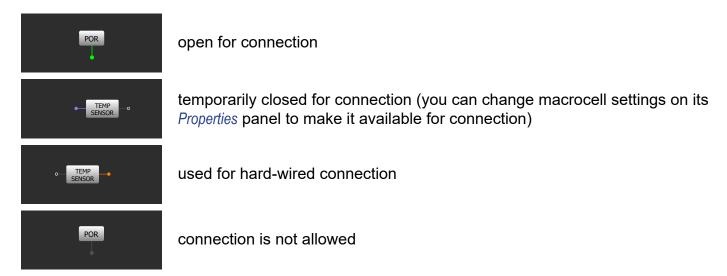

Macrocell pin hint color indicates the connection possibility between the blocks: whether a wire can or cannot be added, or which connection type can be set.

Read about connection types in section 2.1.5 Connections.

When you are in the process of setting a connection, you can see the pin highlight. Just like pin hint color, the pin color indicates the connection possibility.

#### SLG51000/1 chip components highlight

Component highlight for SLG51000/1 chips in different modes or states is as follows:

Pin and pin tip colors are the same as for chips described above.

#### 2.1.5 Connections

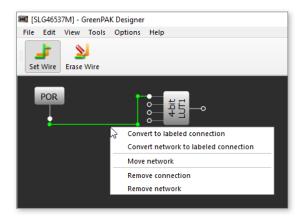

The Set Wire widget helps you to set a connection between the blocks. To add a wire, click two pins between which you are setting a connection. More than one connection set from one OUT pin is a network. You can dismiss connection creation by clicking the right mouse button.

To remove the connection, enable the Erase Wire tool and click the wire (you can also delete the

connection or network via the context menu, triggered by right-clicking the wire).

Set/Erase wire/network

## **GreenPAK chips connections highlight**

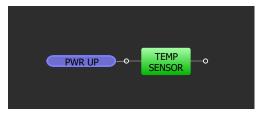

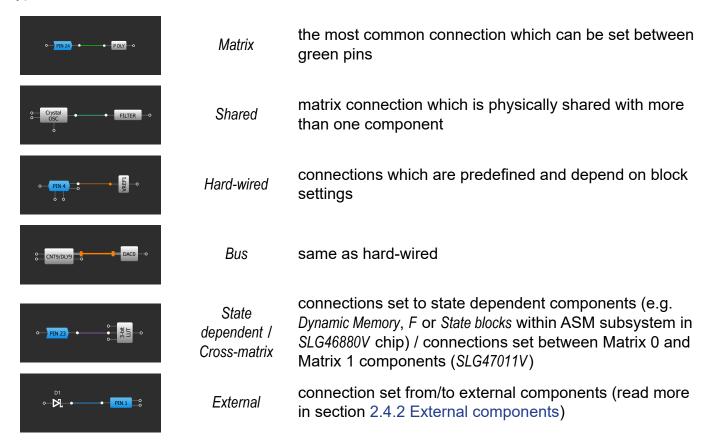

While working with different Part Numbers you may encounter the following component connection types:

#### SLG51000/1 chip connection highlight

In SLG51000/1 Part Number the connection types are as follows:

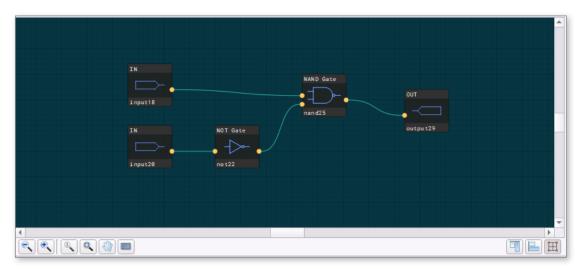

#### FPGA chip connection highlight

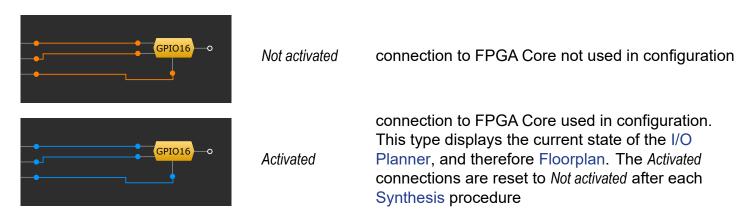

Two connection types for FPGA Part Number (SLG47910V (Rev BB)) are as follows:

## **Common connection-related behavior for all Part Numbers**

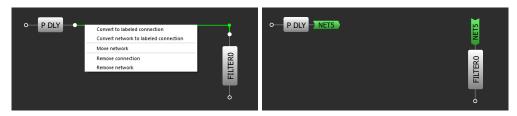

A wired connection/network can be converted to labeled one. Trigger the context menu upon rightclicking the wire to see such option.

Convert a wire to label

After conversion, the label color remains the same as its wired version (Exception: different

connection types set from one OUT. In this case, label is yellow. Applicable only to *GreenPAK* Part Numbers). Labels and pin colors during connection are also the same.

The connections can be labeled by default, but you can change them to wired upon need. You can also change the labeled connection's name. Double-click the label and enter a new name in a popup window.

After hovering the mouse over a label, it becomes highlighted along with all other parts of the same connection/network.

**Highlighted label**

You can also see the hint with the connection or network info upon hovering the cursor over the wire or label.

Connection/Network hint

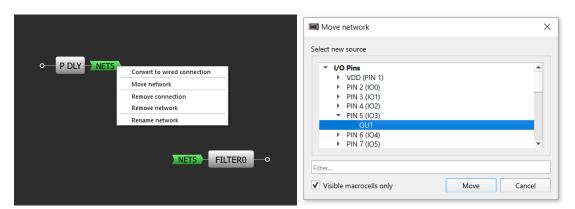

You can move the connection/network to another OUT. Select *Move network* from the context menu. Choose the new component in a *Move network* window and click *Move*.

Move connection/network

The information about the components, pins, connections colors and their description is also present in *Go Configure Software Hub*, in *Legend box*. You can read more is section 2.1.8 Legend box.

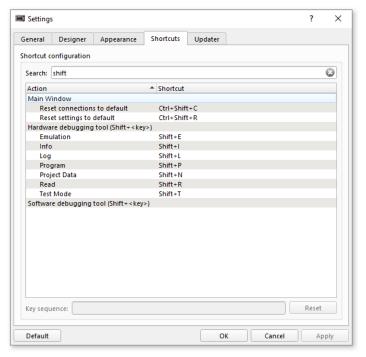

## 2.1.6 Keyboard commands

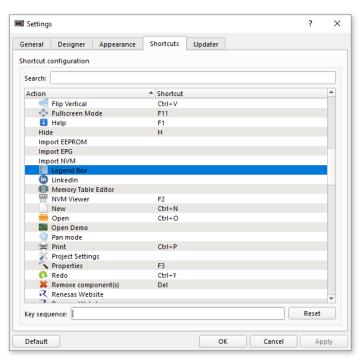

There are configurable and non-configurable keyboard commands. The configurable commands can be managed in *Settings* (for more info, see section 2.1.7 Settings). To find the command easily, use the search field.

Shortcuts table

To change or add a shortcut, double-click the action and press the key sequence on your keyboard to add it to the corresponding field. To discard changes, use the *Reset* button.

Assign/Change shortcut

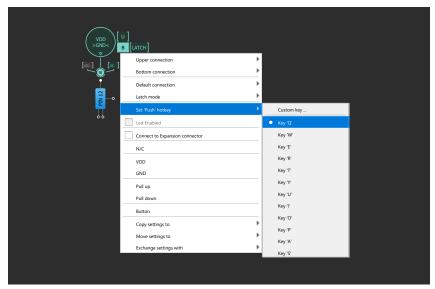

In *Debug tools*, you can assign a hotkey to some hardware sources via the context menu. Use a hotkey to change the source state (read more in section 2.2 Debug tools). Assign a hotkey from the context menu or create a custom one.

Hardware sources hotkeys

See the list of configurable and non-configurable hotkeys in section 6.2 Keyboard and mouse controls.

## 2.1.7 Settings

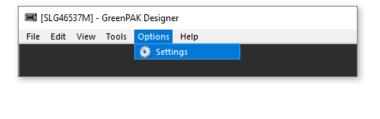

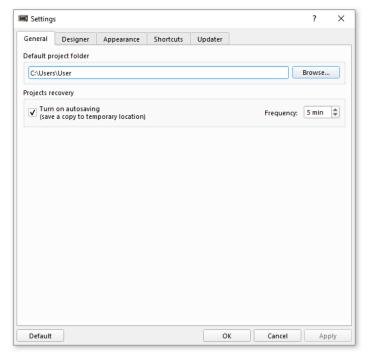

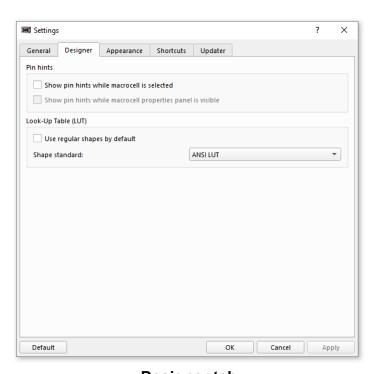

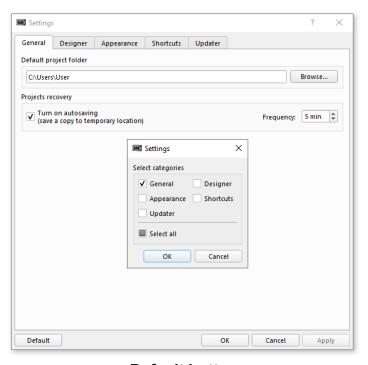

To reach the settings window open  $Options \rightarrow Settings$  (on macOS open  $App\ menu \rightarrow Preferences$ ). The window contains the following tabs: General, Designer, Appearance, Shortcuts, and Updater.

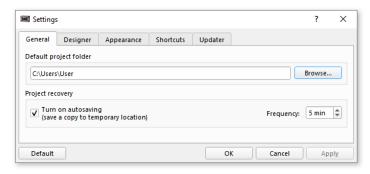

#### General

- ➤ Default projects folder define the path to your project files

- Projects recovery activate project file autosaving

This feature reduces the risk or impact of data loss in case of a crash or freeze. The project file copy is saved to a temporary location at a predefined interval. If a critical issue occurs, the file appears in the *Recovery Files* tab in the *Hub* window (see the location of the *Recovery files* tab in section 2.1 Design tools).

**General tab**

#### **Designer**

- ➤ Pin hints show pin hints while a block is selected or the properties panel of a component is visible (find out more about pin hints in section 2.1.4 Components)

- ➤ Look-Up Table (LUT) select the preferred LUT shape (regular, ANSI or IEC) using different standard gates

Designer tab

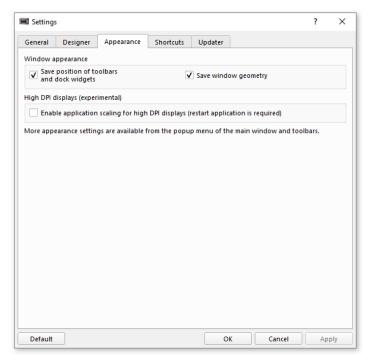

#### **Appearance**

- Window appearance save position of the toolbars/dock widgets and window geometry of the workspace

- ➤ High DPI displays enable Go Configure Software Hub scaling on high DPI displays

Appearance tab

#### **Shortcuts**

➤ Shortcuts configuration — assign/change the shortcut for the available actions

Read more about shortcuts in section 2.1.6 Keyboard commands.

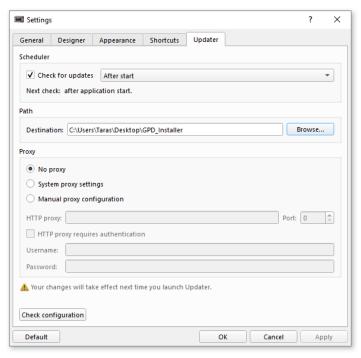

#### **Updater**

- ➤ Scheduler set frequency of the updates check

- Path define a location to download updates to

- ➤ Proxy configure a proxy for updates

- ➤ Check configuration button test the connection to the server

**Updater tab**

In order to reset the settings, click *Default* button at the bottom left corner of the *Settings* window. You can reset settings for a particular category or all categories at once.

**Default button**

### 2.1.8 Legend box

The Legend box window shows the color scheme of the components and connections-related features in Go Configure Software Hub. The Legend box view may vary depending on the Part Number. You can find it in the main menu,  $Help \rightarrow Legend$  box.

Legend box

Find out more in sections 2.1.4 Components and 2.1.5 Connections.

## 2.1.9 Help window

Help materials provide information about the IC's parameters, components, and tools. There are several ways to reach the *Help* window.

If you prefer to open the unified *Help* materials for a particular Part Number, go to the main menu

$\rightarrow$  Help  $\rightarrow$  Help (F1). Walk through the categories to find the information you need.

Help window

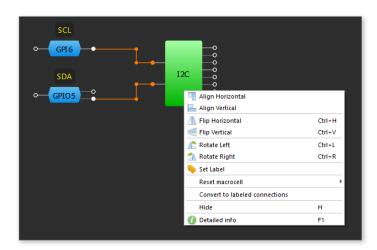

To open the *Help* window for a selected block, right-click the component and select the *Detailed info* **1** option (F1) in the context menu.

**Detailed info**

You may also see the information buttons (1) in different workspace locations, e.g., on a component's *Properties* panel or *Project settings* window. Clicking the button also opens the *Help* window.

## 2.1.10 Snipping tool

Snipping tool is a work area screenshot-maker. You can find the tool in the main menu,  $Tools \rightarrow Snipping tool$ .

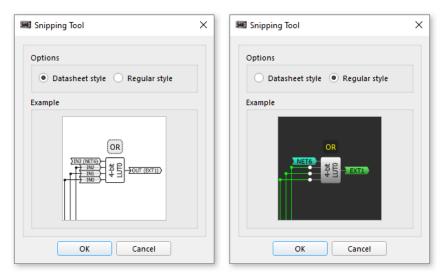

Choose between the *Datasheet* and *Regular* screenshot style (the *Datasheet* style view is the same as in *Print Preview*)

Screenshot style

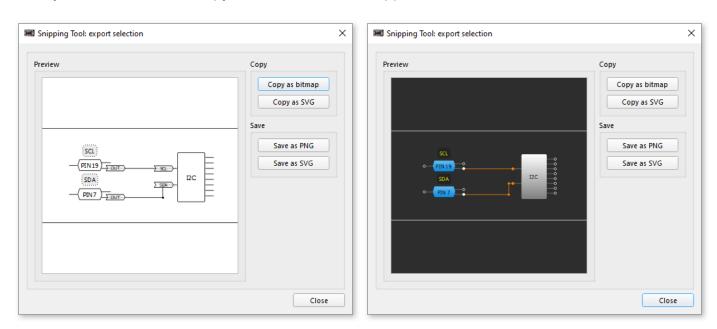

Once you select the area, copy/save the file in the supported format.

**Supported formats**

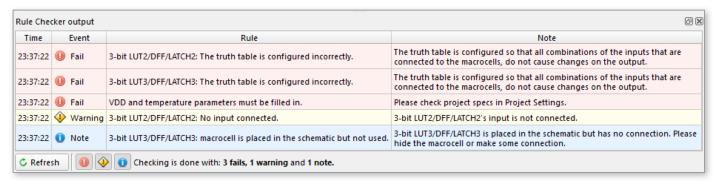

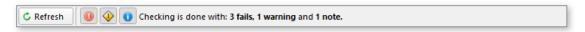

#### 2.1.11 Rule checker

The *Rule Checker* tool scans a project for errors related to incorrect block connections or settings. To check the design, click *Rule Checker* on the toolbar (also, find the tool in the main menu  $\rightarrow$  *View/Tools*).

The Rule Checker output window consists of three main columns:

- ➤ Event shows the message type (Fail, Warning, Note)

- ➤ Rule explains the essence of the issue

- > Note suggests the way to correct the error or provides more details about the issue

Rule checker window

You can use controls to sort the messages by their type. Click the *Refresh* button to see the latest events.

#### Rule checker controls

Rule Checker window shows three message types:

A critical error that may cause the project to fail is present in the design. In some cases, you can ignore this message type (the program may consider the design solution to be erroneous, but it is the correct solution for you).

The project contains improper block(s) connections or settings. This message does not necessarily imply an error, but it notifies about a potential problem and urges checking the block(s) connections and settings.

This message type suggests minor improvements in the design. The suggestions are optional and can be ignored.

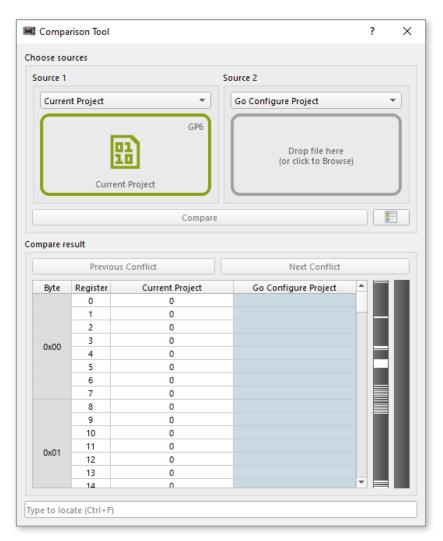

# 2.1.12 Comparison tool

The Comparison tool allows you to compare the NVM state of two projects. You can open the tool by clicking the Comparison tool widget on the toolbar or by reaching the main menu  $\rightarrow$  Tools  $\rightarrow$  Comparison tool.

**Comparison tool**

The tool consists of two main parts: Choose sources and Compare result.

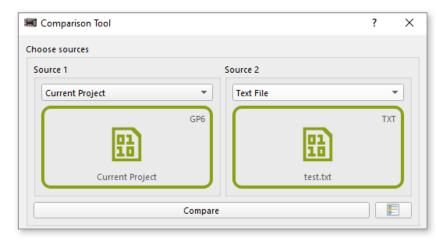

#### **Choose sources**

Here you can select the sources for the NVM comparison. Select the source types from the dropdowns. Then click the designated area to choose the file or drag and drop it. The available sources are as follows:

- Current Project current state of your design

- ➤ Go Configure Project Go Configure Software Hub project file with the following extensions: .aap, .can, .gp3, .gp4, .gp5, .gp6, .hvp, and .ppak

- ➤ Text File exported NVM file in .txt format

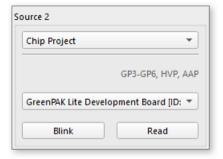

➤ Chip Project — configurations programmed on a chip

Choose sources

If you select *Chip Project* as a source, make sure you connect the supported platform with the inserted IC to your computer. The board info appears in the designated area. Click *Read* to add the programmed data to the tool. Clicking the *Blink* button triggers the blue LED on the connected platform. This feature is useful to check which board is currently detected by the *Go Configure Software Hub* instance. If multiple platforms are connected, select the desired one in the dropdown. Note that *Debug* tool should be disabled to use *Chip Project* as a source.

Chip source

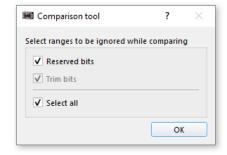

The *Compare* button becomes active once two sources are selected (for *Chip Project*, after the source is selected, click *Read*). Upon clicking *Compare*, you can see a pop-up, where you can select the ranges to ignore while counting the conflicts.

Range selection

Once the pop-up is closed, the *Comparing* window with the results appears.

## **Compare results**

After the sources are compared, you can see the table with the results. Navigate through the unmatched bits using *Previous Conflict* and *Next Conflict* buttons.

Compare results and color scheme

The table contains the information about a byte, register, and NVM of the selected sources. The vertical navigation bar indicates the location of 0 and 1 register values, along with conflicts and ignored bits. See the color explanations by clicking the *Color scheme* button.

You can also use the search field to find the particular byte or register.

Search field

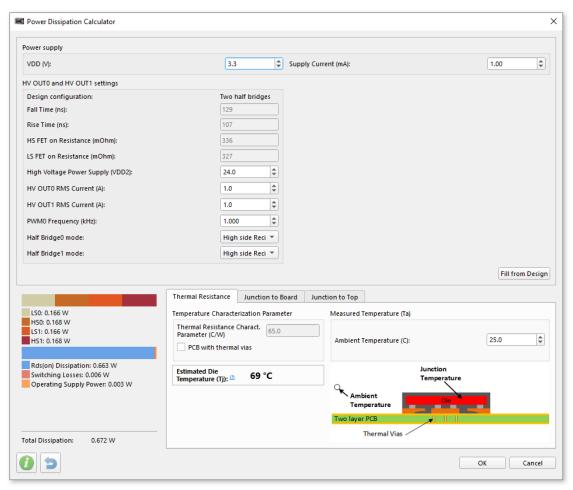

# 2.1.13 Power Dissipation Calculator

The tool helps to determine the amount of heat dissipation of the device, which is an important step in developing an effective thermal management solution. *Power Dissipation Calculator* is available only for the *HVPAK* Part Numbers and mainly applies to the HV OUT CTRL macrocell.

**Power Dissipation Calculator on the toolbar**

To launch the tool, click the *Power Dissipation* button on the toolbar or find it in the main menu, *Tools*.

**Power Dissipation Calculator preview window**

The tool consists of four main parts:

➤ Power supply — voltage applied to VDD pin and estimated current consumption parameters

**Power supply**

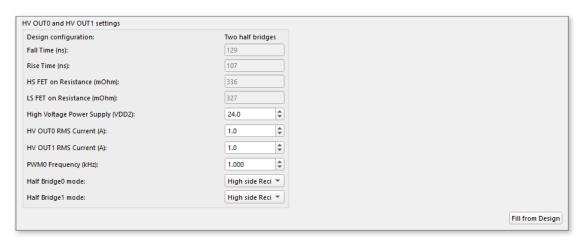

- ➤ HV OUT 0 and HV OUT 1 settings the main parameters of the power pins used in the design

- Design configuration reflects the HV OUT mode parameter selection, set on the HV OUT CTRL macrocell's Properties panel

- Fall Time/Rise Time/HS FET on resistance (mOhm)/LS FET on resistance (mOhm) configurations, which are automatically adjusted based on the conditions and configuration of the HV OUT CTRL component

- High Voltage Power Supply set the supply voltage (VDD2) for HV OUT CTRL

- HV OUT RMS responsible for the output current and cannot exceed 1.5 A per HV OUT

- PWM 0 Frequency (kHz) set the frequency at which HV OUT CTRL operates. You can set the frequency value using the PWM 0 macrocell. Additionally, you can automatically transfer the frequency value using the Fill from Design button in the lower right corner of the HV OUT 0 and HV OUT 1 settings section

HV OUT 0 and HV OUT 1 settings

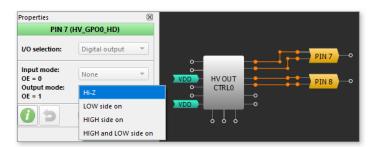

**Note:** When the output pins connected to the HV OUT CTRL macrocell are in the *Hi-Z* state, *HV OUT 0 and HV OUT 1 settings* are displayed as locked. Change the HV Pin's *Output mode* on its *Properties* panel to unlock the settings.

**HV OUT properties panel**

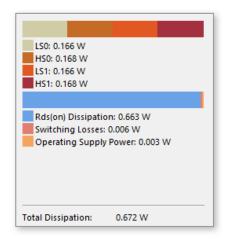

➤ Power dissipation bar — indication of the power dissipation for each transistor: LSx (low side) and HSx (high side). Below, you can see the total power dissipation, including open transistor resistance Rds(on), transistor switching losses, and the power dissipated by the chip even

when the output pins of HV OUT CTRL are in Hi-Z.

Power dissipation bar

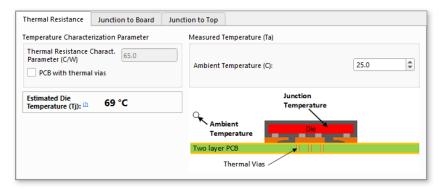

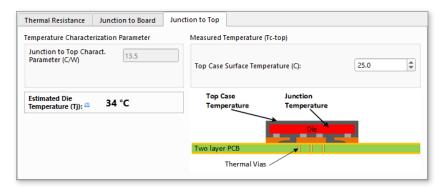

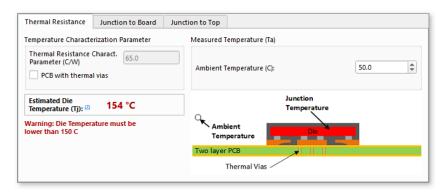

- ➤ Temperature Characterization provides three options for calculating the device Die temperature:

- Thermal Resistance you need only the ambient temperature of the device for calculations. This method is the least accurate. If the platform you are using contains thermal vias, you can tick the respective checkbox to take it into account

Thermal resistance window

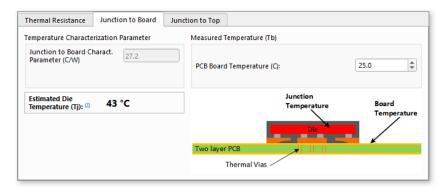

Junction to Board — the PCB temperature is used to calculate the Die temperature.

It should be measured 1 mm from the device. This method has a higher accuracy compared to Thermal Resistance

**Junction to Board window**

Junction to Top — the temperature of the Die is determined based on the upper surface temperature of the chip. This method has the highest accuracy.

**Using Junction to Top window**

Keep the *Die* temperature below 150°C to ensure the chip operates correctly. An indication of overheating appears if the temperature exceeds the limit.

Overheating warning

# 2.1.14 Acceleration Profile Configurator

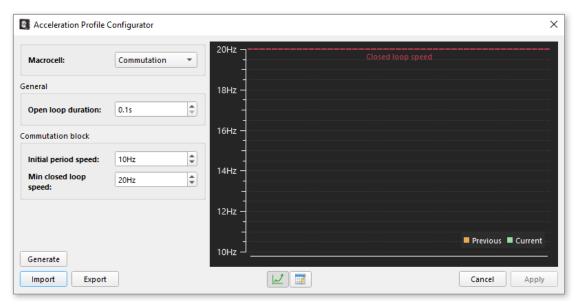

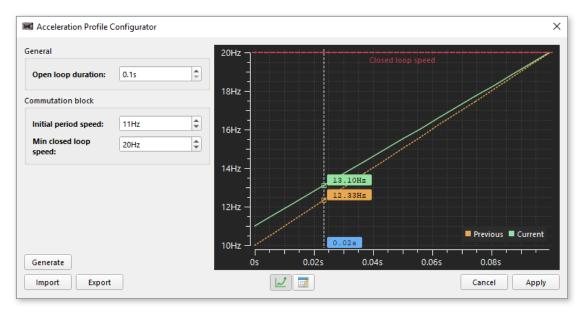

The Acceleration Profile Configurator tool is designed for linear motor speedup calculation based on specified time and motor speed range for the Commutation block. Additionally, Timer macrocells can use Acceleration Profile as a counter data source. Launch the tool by clicking the Acceleration Profile button on the toolbar or find it in the main menu, Tools.

Acceleration Profile on the toolbar

Once you select the desired macrocell, set the parameters for calculations.

**Acceleration Profile Configurator tool**

## Commutation

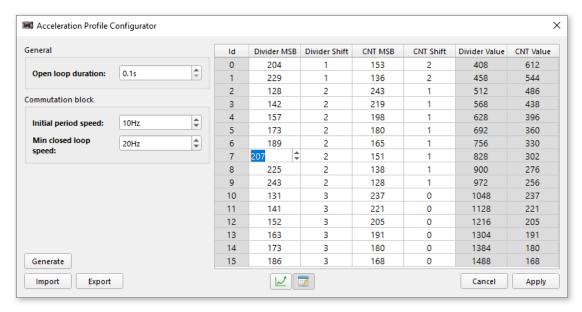

Below, you can see the parameters available for the Commutation macrocell.

- ➤ Open loop duration time interval of motor operation (x-axis on the graph)

- ➤ Initial period speed and Min closed loop speed motor rotation frequency range (y-axis on the graph). Both parameters can be configured in the tool directly or on the Commutation block Properties panel, since they are syncronized

Click the Generate button to perform the calculations on the basis of the provided data.

The results are represented in the following ways:

- Waveform graphical visualization of motor operation. It provides the following information and possibilities:

- x-axis (time interval set as Open loop duration) and y-axis (frequency range set as Initial period speed and Min closed loop speed)

- current graph (based on latest added parameter values) and previous one (based on the previously set values)

- Closed loop speed dotted line showing the upper frequency limit

- tracker with labels

- zoom by x-axis scale with Ctrl + mouse wheel

Commutation waveform

➤ Table — the table contains 16 points. Each point consists of two values: Divider Value and Counter (CNT) Value. Each value consists of two parts: MSB 8bit and shift 4bit to reduce memory space. It is also possible to manually modify the MSB and Shift cells' data by double-clicking the cell

Manual data editing for Commutation table

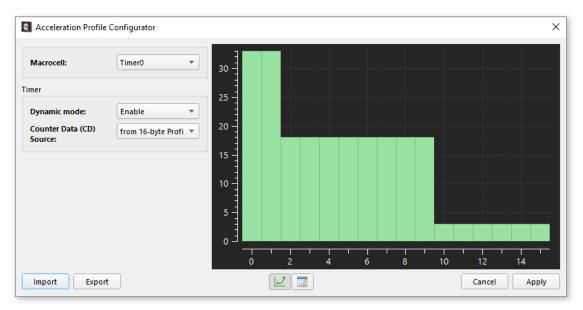

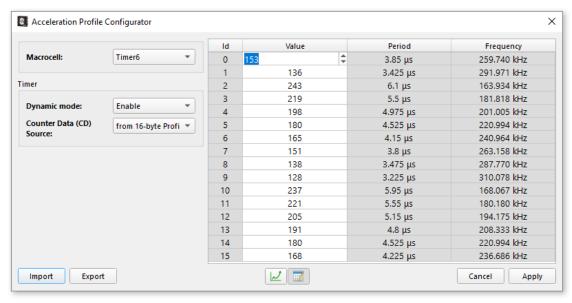

#### **Timers**

The Timer macrocell parameters in the tool are also synchronized with the ones on the Timers *Properties* panel.

- > Dynamic mode enable the mode to activate the Counter Data (CD) Source parameter

- Counter Data (CD) Source select the Timer source counter, Acceleration profile, or Scaler (where applicable) to read the counter data value from

Same as for Commutation, the Timers' data is also represented in two ways:

➤ Waveform — visualizes the counter data values

Waveform

➤ Table — the table also consists of 16 points, which can be manually entered while the Counter Data (CD) Source is set as from 16-byte Profile. Period and Frequency are calculated based on the cell value

Timer macrocell table

Import/Export the calculation results in .csv or .txt format using the respective bottom buttons.

- **Note 1:** If you wish to write the table data to NVM click the *Apply* button.

- Note 2: The Commutation and Timers table values share the same NVM bits.

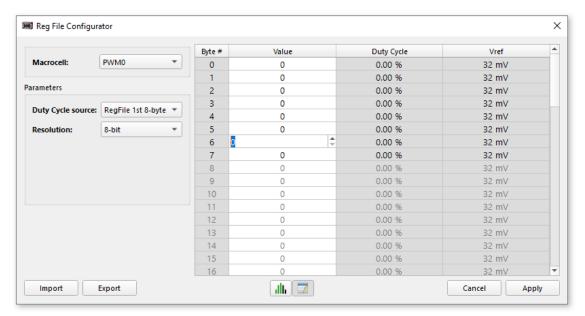

# 2.1.15 Reg File Configurator

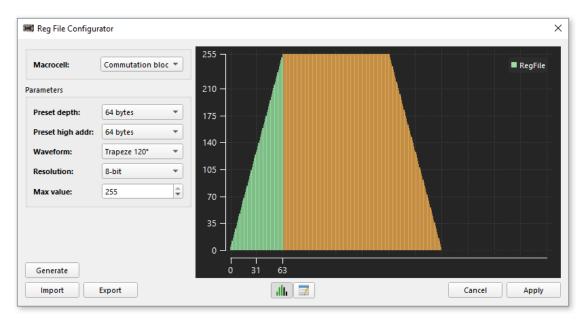

The tool interacts with Commutation block and PWM macrocells. For Commutation block, the tool provides the motor control waveform calculation according to the given amplitude and the Reg File size. For PWM, it performs the automatic fill-up of the Reg File for the specified waveform.

Start Reg File Configurator from the toolbar or find it in the main menu, Tools.

Reg File Configurator on the toolbar

The set of parameters allows you to:

- > Specify the used amount of bytes that can be read from Reg File by the selected macrocell

- Select the waveform type in which the generated data is represented (this option is available only while Commutation block macrocell is selected)

- Set the PWM resolution and the waveform amplitude

Click the *Generate* button to perform the calculations on the basis of the provided data (this option is available only while Commutation block macrocell is selected).

The tool provides two ways of data representation:

➤ Waveform — x-axis represents the amount of bytes that can be read by the selected block; y-axis is the waveform amplitude. The green part represents data stored in Ref File, while orange shows data for motor control generated automatically, based on Reg File data

**Reg File Configurator window**

➤ Table — in addition to generated values, you can also manually modify the Value column cells upon double-clicking

Manual data editing

Import/Export the calculation results in .csv or .txt format using the respective bottom buttons.

**Note:** If you wish to write the table data to NVM click the *Apply* button.

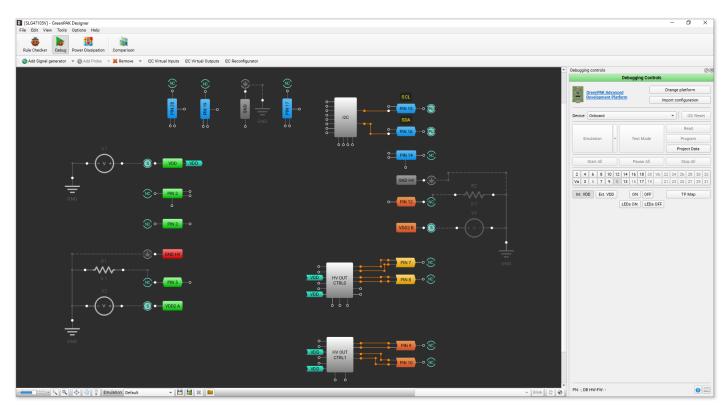

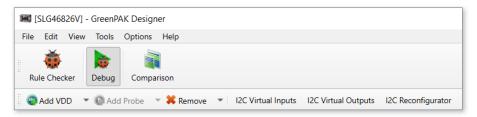

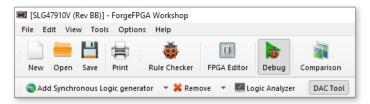

# 2.2 Debug tools

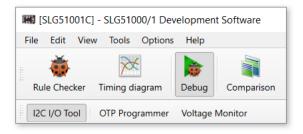

Debug tools are a set of instruments, that allow you to test and debug your design. To access Debug tools, click the Debug button on the toolbar. Since there are different hardware platforms available for a specific Part Number, select the platform most suitable for your project.

Platform selector window for SLG47105V

**Note:** You can only use the hardware in one application instance. If you wish to transfer control from one instance to another, disable *Debug tools* on the controlling instance.

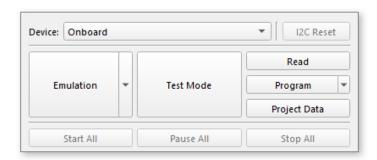

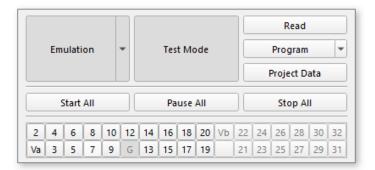

After you select a platform, the software activates a toolbar and a panel with controls for main procedures, including emulation and chip programming.

Software UI after Debug is enabled

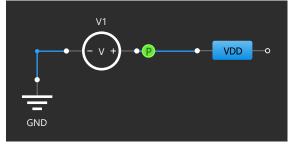

# 2.2.1 Hardware sources

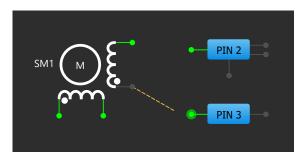

Go Configure Software Hub provides software tools to configure varied hardware sources that manage or generate input and test signals for a chip. Each signal source is connected to an external pin on a chip.

Below, you can find the complete list of all the hardware sources.

**Note:** The choice of hardware sources depends on the development platform features and chip restrictions.

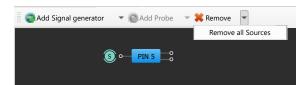

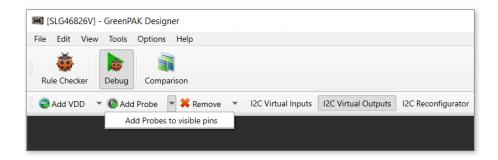

You can switch the controls on/off via the context menu or from the toolbar via the *Add Signal Generator* or *Add VDD* button (the button view depends on the available sources).

**Debug toolbar**

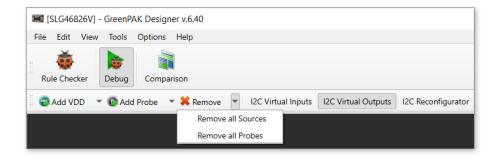

To remove the source click the *Remove* button or select *N/C* (Not Connected) in the context menu.

Remove button on Debug toolbar

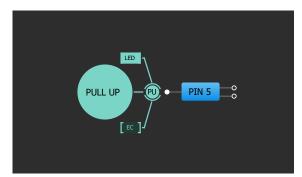

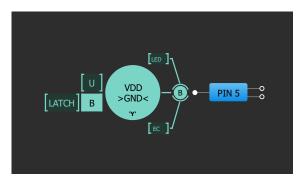

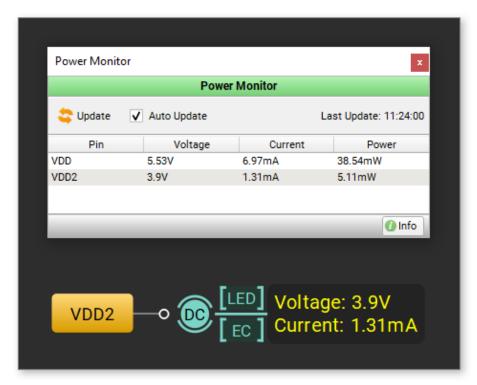

Some of the chip pins may have additional controls, such as *LED indicators* or *Expansion Connectors* (*ECs*), which are available even if a development platform is not connected yet. You can enable/disable the controls by hovering over the source and clicking the control you need.

**Buffered LED**

Power GreenPAK buffered LED

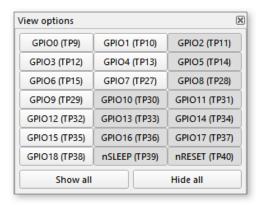

If you need to identify the chip pin connected to a specific test point on a board, use the *Test Point* (*TP*) *Map* tool. Note that the pins mapping to test points varies based on the chip type.

TP map

Hardware sources can be divided into two categories: *basic Hardware Sources* and *Generators*. *Generators* provide a comprehensive solution for creating analog or digital signals with configurable settings and are discussed in more detail in the section 2.2.2 Generators. Later in this chapter you can read about the *basic Hardware Sources*.

#### **Basic Hardware Sources**

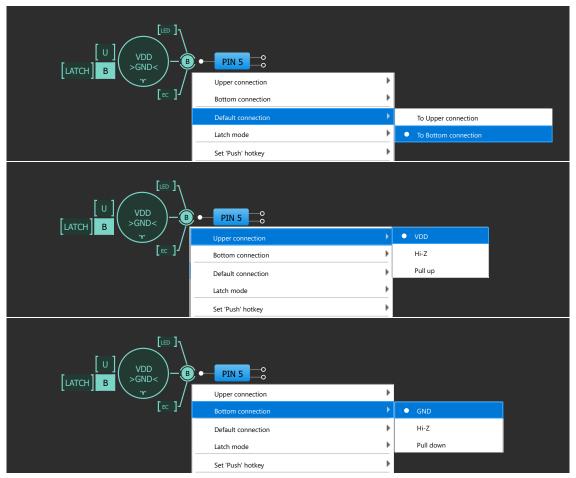

The available basic Hardware Sources are: VDD, GND, Pull up, Pull down, and Button. Unlike others, Button has more configuration possibilities (for the rest of the basic sources, all necessary information is already described above).

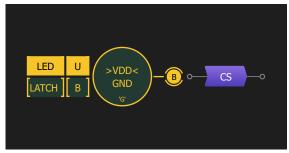

The *Button* hardware source allows quick switching between two predefined states: *Upper connection* (*U*) and *Bottom connection* (*B*). These predefined states can be set to *VDD/GND*, *High-Z*, or *Pull Up/Down*. Hover the mouse cursor over the *Button* control to see its configuration.

**Configurable Button**

The default connection can be set to either the Upper connection (U) or the Bottom connection (B).

**Default Key Connection**

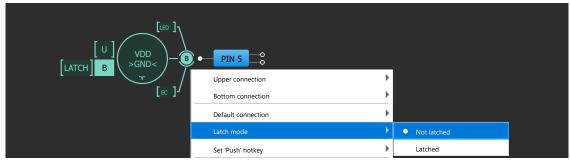

Latch control has two modes: Latched and Not latched. You can configure these modes from the context menu or by clicking the LATCH button to change the value.

In Latched mode, the Button toggles its state on click and remains in the new state until the next click.

In *Not Latched* mode, the *Button* changes its state upon the left-click and returns to its previous state after the mouse button released.

**Key Mode**

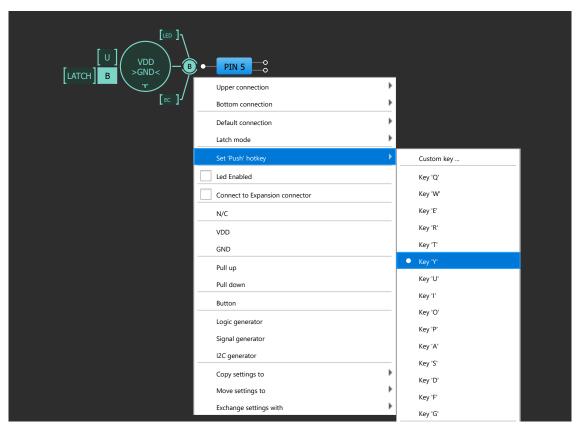

You can assign a hotkey for the *Push* action. Pressing the hotkey is equal to a mouse click.

**Choosing hotkey**

You can assign the same hotkey to multiple *Buttons*, which allows changing the states of all the *Buttons* with the same hotkey at once.

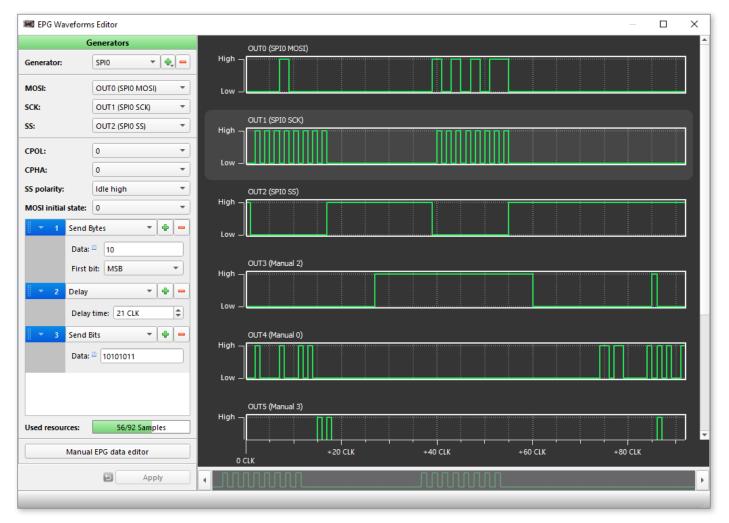

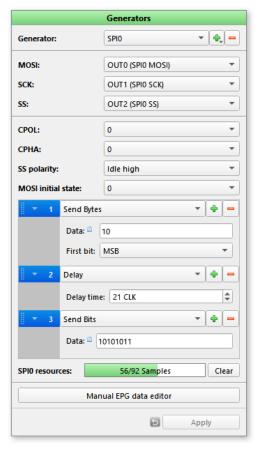

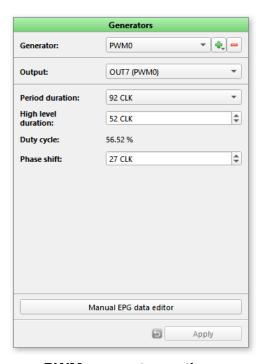

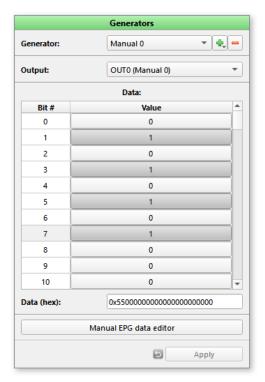

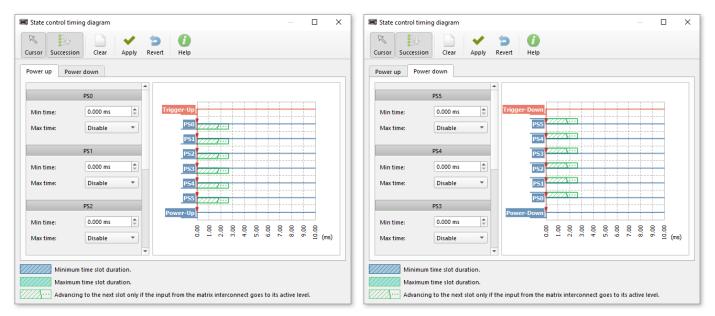

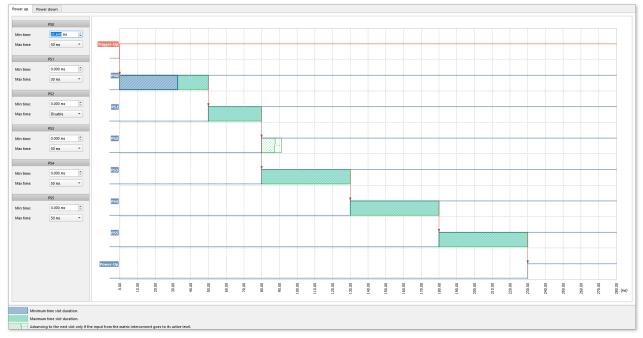

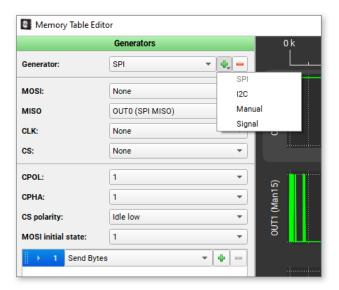

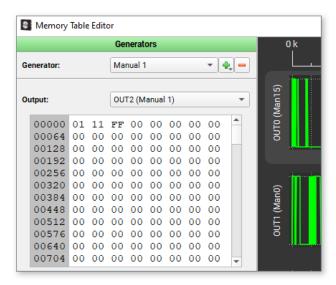

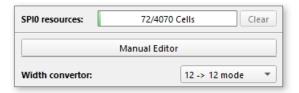

## 2.2.2 Generators

A *Generator* is a hardware source type, that produces analog or digital electronic signals onto test points on a board. *Go Configure Software Hub* allows setting up the generators in an easy and convenient way with visual control of their settings and states. You can control the *Generator* using the sticker, which appears upon hovering over the respective icon. For more advanced configurations use the *Signal Wizard* tool. To find out more refer to section 2.2.3 Signal Wizard.

## **Logic Generator**

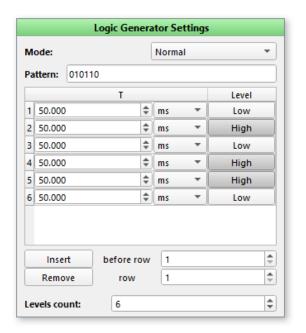

The *Logic Generator* generates logic pulses. A logic pulse is one of two voltages that correspond to two logic states (*low state* and *high state*, 0 and 1).

Logic Generator in Signal Wizard

You can export/import all *Logic Generator* settings. To do this, copy the *Pattern* field content and paste it to a text editor. The content will automatically convert to *XML* format text. You can use this feature to save your custom generators or load them from an external file.

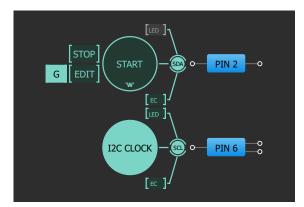

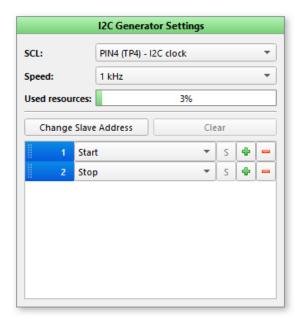

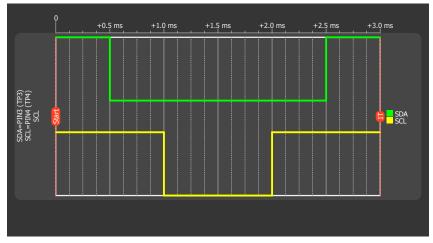

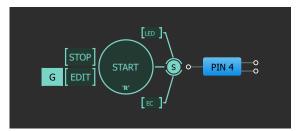

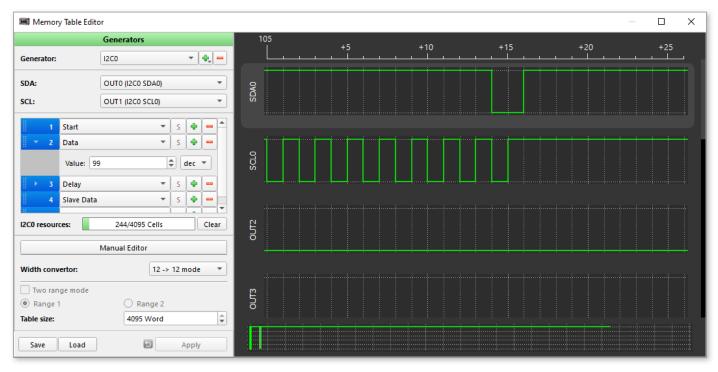

## **I2C Generator**

The *I2C Generator*'s purpose is to create *I2C* (Inter-Integrated Circuit) communication patterns based on *Logic Generators*. There are two *Logic Generators* combined as *SDA* (Serial Data) and *SCL* (Serial Clock) lines. You can combine predefined *I2C* primitives to generate a required waveform

appropriately and choose the SCL frequency.

**I2C Generator**

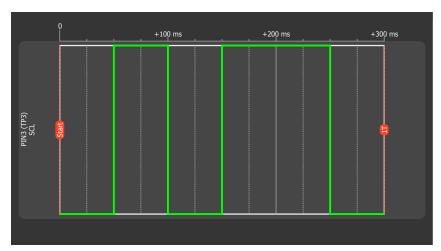

SDA signal is a special case of *Logic Generator* used for sending data via *I2C*. The *Signal Wizard* editor shows the sequence of commands.

*SCL* signal is a particular *Logic Generator* that can be used for board configuration only. The *SCL* is configured by choosing a predefined frequency. The set of these frequencies depends on the development platform.

**I2C Generator command editor**

**I2C Generator Signal Wizard**

If you decide to change a type of a command, click an arrow  $\overline{\ }$  and the drop-down menu will show the available commands.

**I2C** command list

Composite commands *Read* and *Write* may be split into a sequence of basic commands (all commands are listed in the drop-down menu above).

# Signal (Analog) Generator

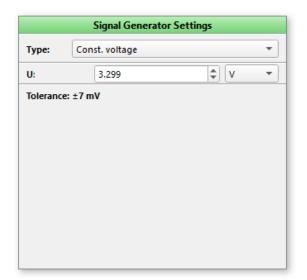

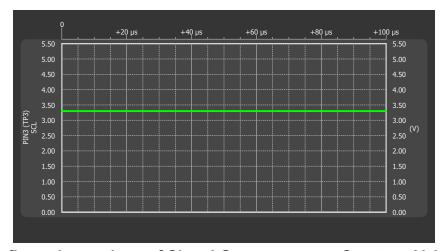

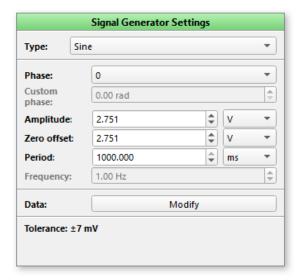

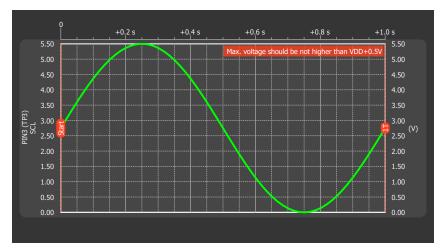

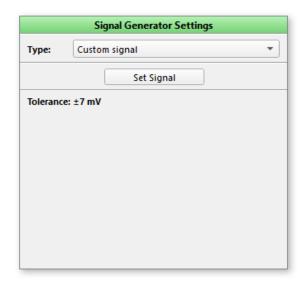

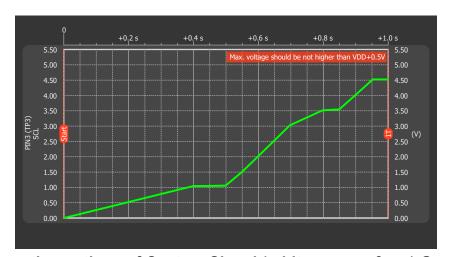

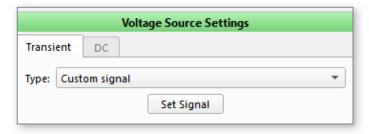

The *Signal Generator* produces the analog signal, and can be configured using one of the following pre-defined types: constant voltage, sine, trapeze, logic pattern, or custom signal.

**Signal Generator**

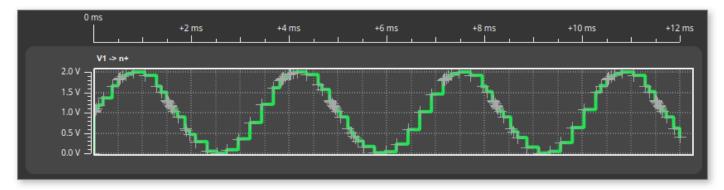

Below, you can see the Signal Wizard view for different signal types.

Constant voltage waveform type

**Configuration options of Signal Generator, type Constant Voltage**

> Sine waveform type

Configuration options of Signal Generator, type Sine

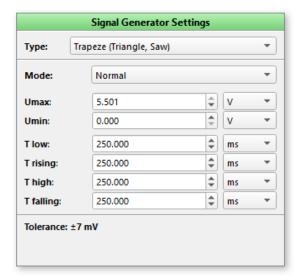

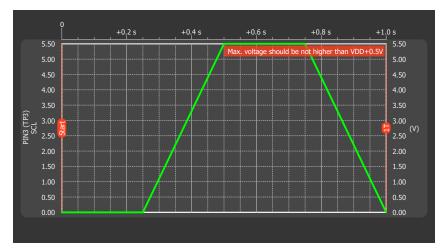

> Trapeze waveform type

Configuration options of Signal Generator, type Trapezoid (Triangle, Sawtooth)

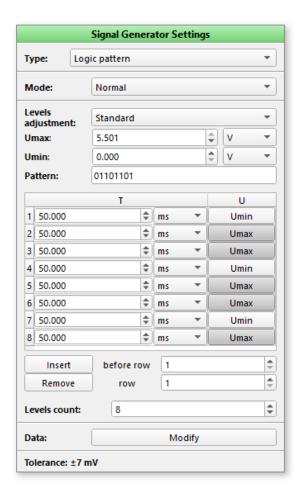

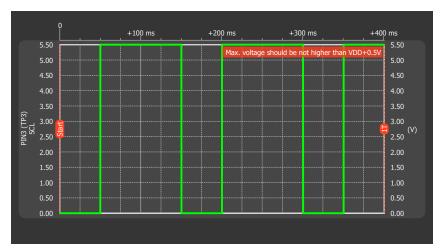

> Logic pattern waveform type

Configuration options for Signal Generator, type Logic pattern

Configuration options of Custom Signal (arbitrary waveform) Generator

The custom signal can be configured in a separate window. Find out more in section 2.2.4 Custom Signal Wizard.

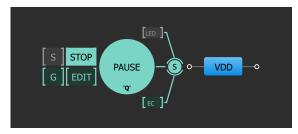

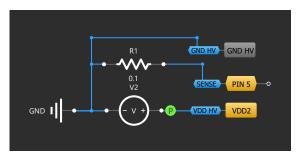

# **VDD/VDD2 Power Signal Generator**

Some Part Numbers have an additional power supply (*VDD2*); if present, it allows to interface two independent voltage domains within the same design. You can configure the pins dedicated to each power supply as inputs, outputs, or both (controlled dynamically by the internal logic) to *VDD* and *VDD2* voltage domains. Using the available macrocell, you can implement mixed-signal functions bridging both domains or pass through level translation in *HIGH* to *LOW* and *LOW* to *HIGH* directions.

**VDD/VDD2 Power Signal Generator**

If the *Sync Power Rails* [S] mode is enabled in *Signal Wizard*, *VDD* and *VDD2* share the same power settings. The option is available only for *VDD / VDD2* power generators.

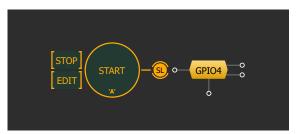

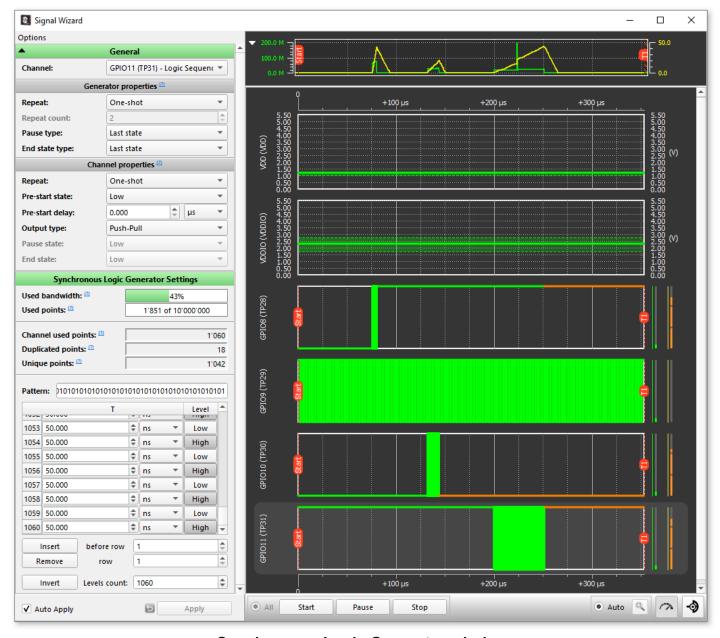

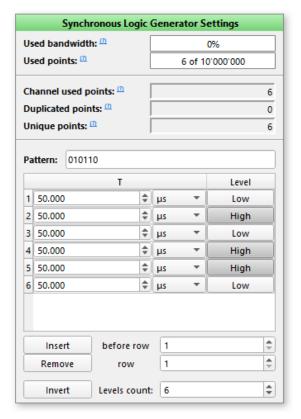

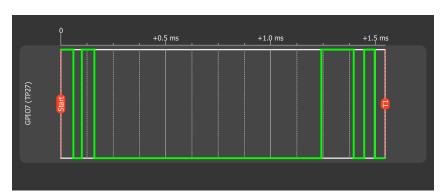

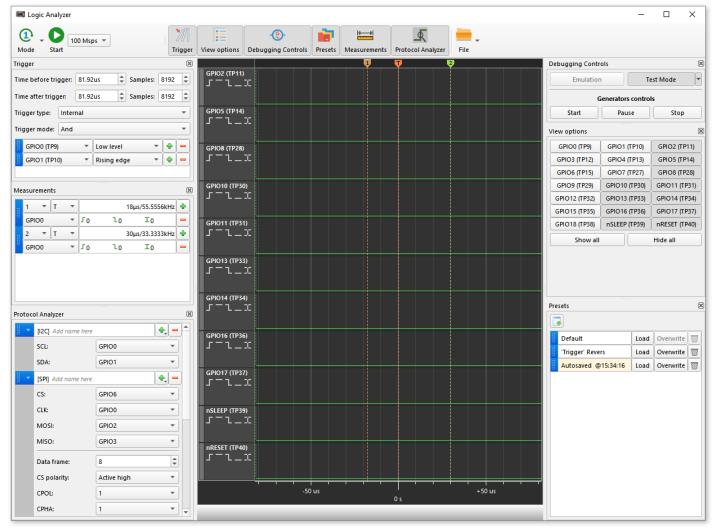

## **Synchronous Logic Generator**

The *Synchronous Logic Generator* is used for generating the logic pulses and waveforms on GPIO pins. It is a 64-channel digital pattern Generator, provided only by  $ForgeFPGA^{T}$  Deluxe Development Board.

**Synchronous Logic Generator**

You can enhance the efficiency of this generator by using the *Signal Wizard*, which offers two types of resources: *used bandwidth* and *used points*. *Used bandwidth* refers to buffer occupancy and depends on *points density*.

The top complex graph displays two metrics: a green line for *points density* (points per second) and a yellow line for *used bandwidth*. The peak value of the *used bandwidth* line correlates with the used bandwidth value in *Parametric Generator Settings*. This graph precisely summarizes resource usage in all waveforms displayed below over one period.

You can adjust your screen view and toggle the graph visibility using the button in the bottom right corner of the window.

While the graph at the top of the window represents all waveforms collectively, the indicators to the right of the generators display information for each channel individually. Each channel has two different indicators:

- ➤ Points Usage Indicator shows the number of points a channel is using.

- ➤ Resource Percentage Indicator displays the used bandwidth for each channel.

Both indicators are color-coded and will change colors depending on their values or percentages.

The legends are available for each indicator to check the value range.

Synchronous Logic Generator window

The *Used points* metric displays the cumulative number of points used by patterns across all channels. A point shows any change in the level across any of the 64 channels, including prestart delay and endstate. However, if two or more channels change levels simultaneously, it will be counted as one generator point.

The Wizard also helps to understand each channel individually.

- Channel used points combine the duplicated points and unique points in a selected channel

- Duplicated points show the total duplicated points currently used by the generator

- Unique points represent the total unique points currently used by the generator

Synchronous Logic Generator properties

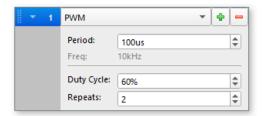

## **Parametric Generator**

The Parametric Generator generates logic pulses that follow different protocol sequences. This type is also available for  $ForgeFPGA^{TM}$  Deluxe Development Board.

**Parametric Generator**

In Signal Wizard, a special editor shows the sequence of commands.

Actions available in the command editor:

- ➤ Add or remove commands by clicking and -

- Change command parameters

- ➤ Change the order of commands by dragging the command to another position

**Parametric Generator command editor**

**Signal Wizard for the Parametric Generator**

The list of available commands:

- > PWM (Pulse Width Modulation) the PWM command editor has three input fields:

- Period a united duration of high and low states per repeat

- Duty cycle the percentage of the total duration in the high state

- Repeats pattern repeat count

**PWM** command editor

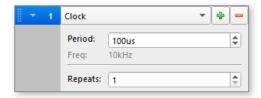

> Clock — the command generates a signal oscillating between a high and a low state. The

editor has two input fields:

- Period the united duration of high and low states per repeat

- Repeats pattern repeat count

**Clock command editor**

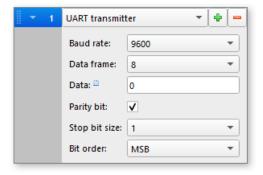

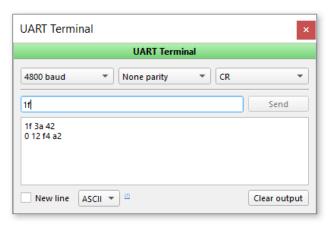

- ➤ UART Transmitter generates signal according to the UART standard:

- Baud rate signal's frequency

- Data frame number of bits allocated for user input

- Data user input in hex format. In case the data frame is lower than the bits required to represent data, more significant bits are ignored

- Parity bit create parity bit for error detection

- Stop bit size duration of the stop bit

- Bit order serial data transfer format

**UART** transmitter command editor

➤ Raw — this pattern works as a typical Logic Generator

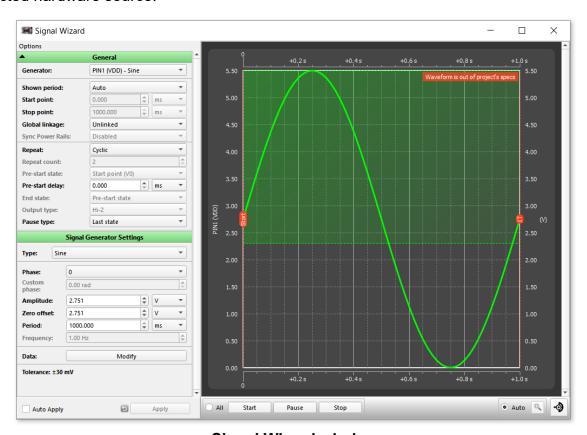

# 2.2.3 Signal Wizard

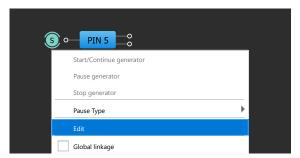

To start configuring a Generator, double-click its icon next to the pin or find Edit in its context menu.

**Opening Signal Wizard**

The Signal Wizard window contains a Generator settings panel and the plot (waveform preview). The window is common for all Generators, though different set of settings may be activated, depeding on the selected hardware source.

Signal Wizard window

*General* settings category mostly provides signal configurations related to time, period, and state. Below you can see the settings which may require more detailed description.

- Global Linkage when enabled, provides possibility to control Generator using Start/Stop/Pause buttons on the Debugging Controls panel

- > Sync Power Rails enable for VDD and VDD2 to share the same power settings. The option is available only for VDD / VDD2 Power Generators

The lower settings part is generator-specific. Read more in section 2.2.2 Generators.

## **Scaling controls**

Scaling controls are located at the bottom right corner of the *Signal Wizard*. The controls let you adjust the number of periods shown in the waveform preview.

Scaling in Signal Wizard

You can use the Cursor button to turn the mouse coordinates on/off in the timing diagrams.

- ➤ Auto scale all generators to fit the biggest period among them. Only generators with Shown period set to Auto are affected.

- ➤ Custom waveforms can be re-scaled manually. To do that, ensure that the Auto mode is OFF and then scale by Ctrl + mouse wheel.

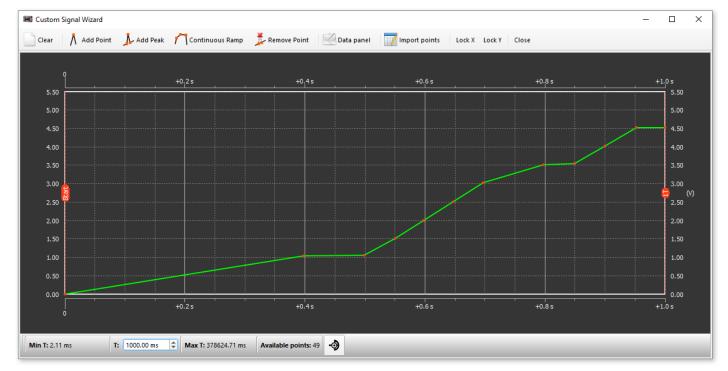

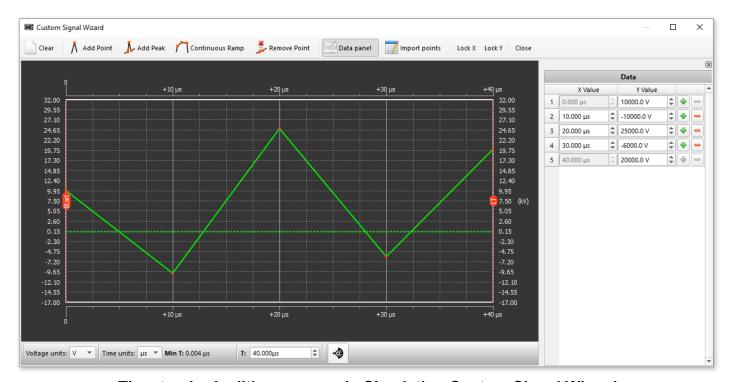

# 2.2.4 Custom Signal Wizard

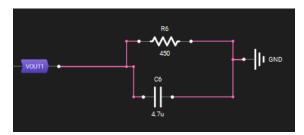

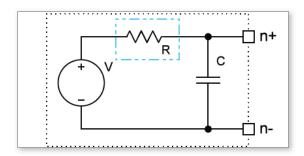

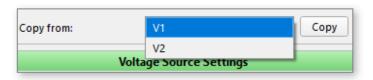

Custom Signal Wizard allows creating, importing, and editing the signal waveforms (applicable only for Signal (Analog) Generators). The signal can be created by manually adding points or importing a custom list of points from an external source.

**Drawing Signal (Arbitrary waveform)**

Use the controls on the toolbar to manipulate the waveform.

- ➤ Add Point/Peak/Continuous Ramp use the buttons to start creating the signal waveform

- ➤ Remove Point click the button to remove a selected point (or use a right-click)

- ➤ Data Panel show or hide the data table. You can remove/change values for a selected point or add a point in between

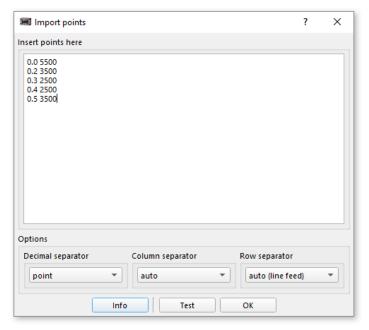

➤ Import Points — click the widget to open the Import window and insert the points' coordinates

**Import Points**

See the coordinates formatting options:

- Decimal separator: point/comma

Column separator: auto/tab/other

Row separator: auto(line feed)/tab/other

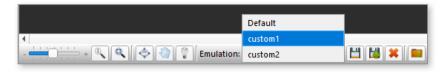

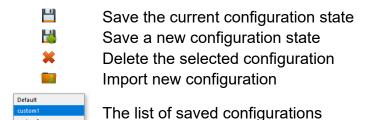

# 2.2.5 Hardware configurations

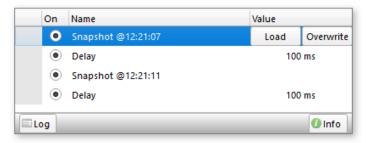

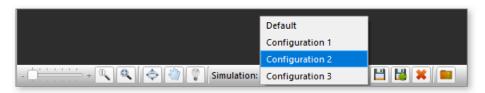

You can create configuration state snapshots to restore a previous configuration when needed. The snapshots include your hardware sources' configuration and are saved and loaded with your project file. This option is available for both *Generators* and *basic Hardware Sources*.

Saved configurations

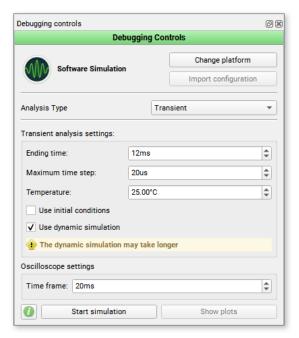

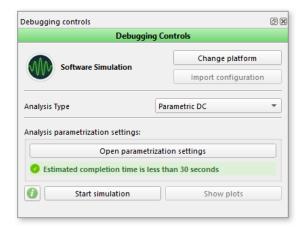

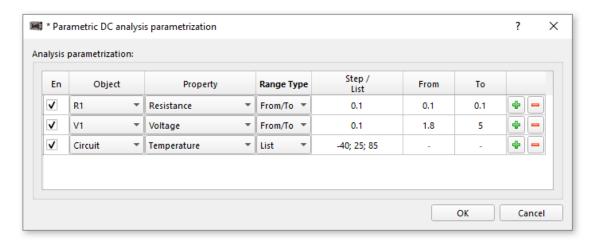

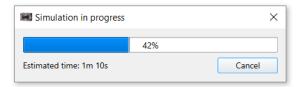

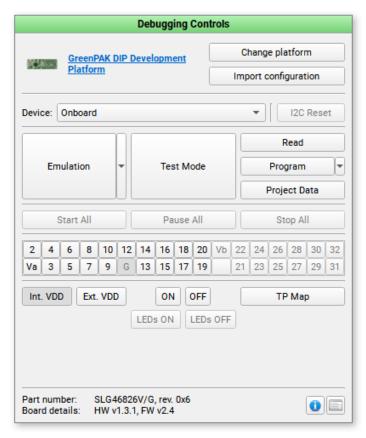

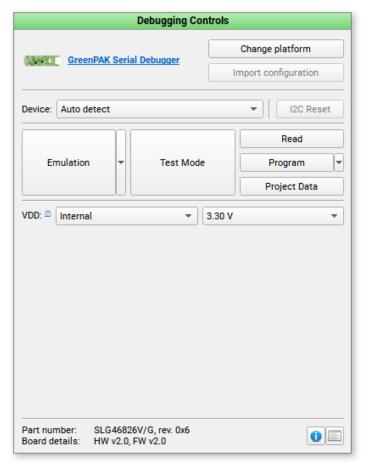

# 2.2.6 Debugging Controls

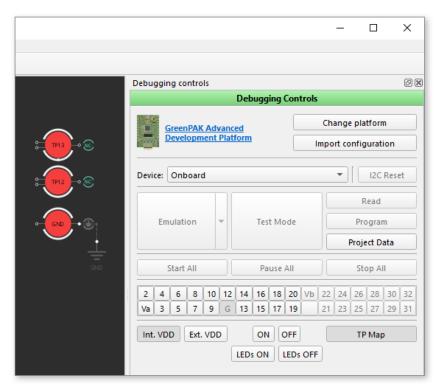

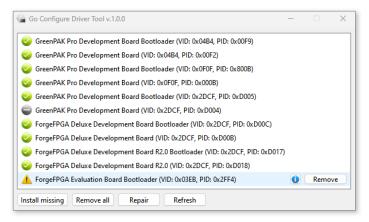

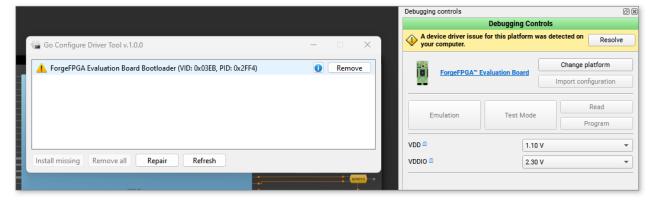

To access the required development platform through the software, click *Debug* and select the board from the list of supported platforms.

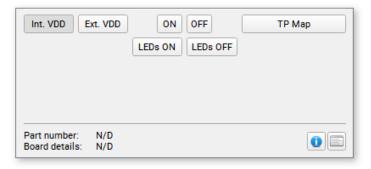

The *Debugging Controls* panel appears. It contains the UI controls for chip communication and programming, brief information about the connected devices, and other features described below.

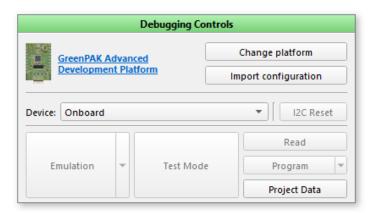

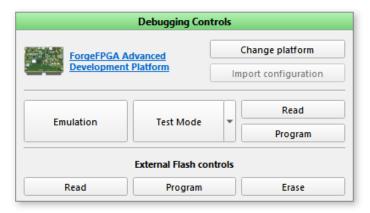

In the software you may encounter different Debugging Controls panel types.

Within the *Standard* debugging controls, we provide the built-in validation checks. The list includes, but is not limited to, the following:

- Socket connection test the software performs a validation check to confirm the chip's connection status

- ➤ IC detection check it is verified whether the correct part number/revision is placed in the socket

- ➤ Memory type verification the chip's classification as OTP (One-Time Programmable) or MTP (Multi-Time Programmable) is assessed

- ➤ Chip state analysis the software checks the current state of the chip to ensure correct execution of procedures, such as verifying whether the chip is empty/programmed or locked/unlocked, etc.

**Standard Debugging Controls panel**

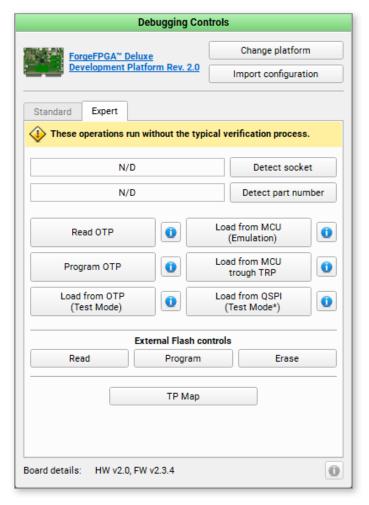

The *Expert* panel provides the same set of features without including the additional validation checks.

**Expert Debugging Controls panel**

Later in this section, you can read about all *Debugging Controls* panel UI elements you may encounter while working with different platforms and ICs. In chapter 3 Devices, you can see the supported development platforms description and the *Debugging Controls* panel for each board.

The table listing *Debugging Controls* elements availability for all boards is given in the appendix, in section 6.3 Debugging Controls feature availability.

Click the reference below to quickly find the *Debugging Controls* panel interface for the certain platform.

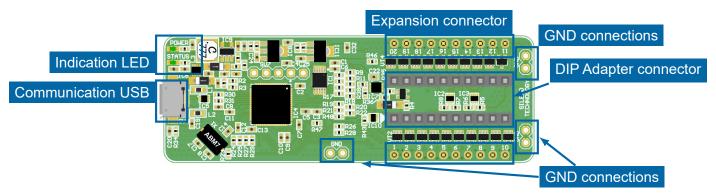

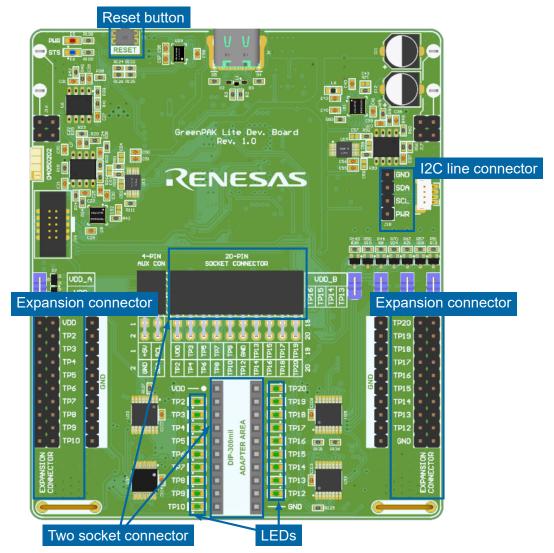

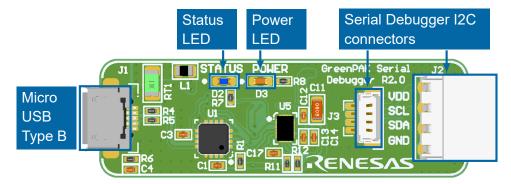

GreenPAK Advanced Dev. Platform ForgeFPGA™ Evaluation Board

GreenPAK DIP Dev. Platform Power GreenPAK Dev. Motherboard

GreenPAK Lite Dev. Platform Power GreenPAK Demo Board

GreenPAK Serial Debugger (with

SLG5100x) ForgeFPGA<sup>™</sup> Deluxe Dev. Board

## **Debug configuration**

➤ Recommended platform configuration — find information about the supported adapter, development board and the devices' ordering information. Click on the platform name link to open the Recommended platform configuration

Recommended platform configuration

- Change platform open the list of the development platforms that are supported by a Part Number

- Import configuration upload configurations from a different development platform supported by a Part Number

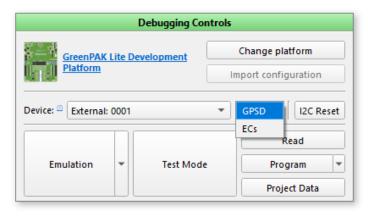

#### **Device selector**

- Onboard/Chip in socket search the device placed on the board

- ➤ External search the device on the selected I2C slave address

- ➤ Auto detect/External, connected to 'I2C OUT' search the device on all available I2C slave addresses, starting from 0 until the first one is found

**Device selector**

**Note:** Make sure you do not connect the socket to the platform and external chip at the same time.

### **External device modes**

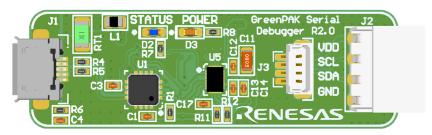

- ➤ GPSD use a separate 4-pin connector (PWR, SCL, SDA, GND) for I2C communication

- ➤ ECs use the expansion connector for I2C communication:

- VDD EC power

- SCL/SDA EC according to the chip TP map

Lite board device selector

### Chip procedures

- Test Mode debug the programmed project. Enable power and load the configured hardware sources

- ➤ Load from OTP same as Test Mode

- ➤ Emulation debug the current project. Enable power and load the design with configured hardware sources

- ➤ Load from MCU same as Emulation

- ➤ Load from through TRP same as Emulation, but the procedure sequence goes through TRP

- Emulation(sync) the project changes are automatically loaded to the chip when the control is active

- Sync load the current project to the chip once

- Read read the programmed chip and open the project in the new software instance or in the Project Data window of the current instance

- ➤ Program program the chip with the current project. For some Part Numbers, e.g. SLG47004, EEPROM programming is available

- ➤ *I2C Reset* change the I2C reset bit (from 1 to 0). This causes the device to re-enable the Power-On Reset (POR) sequence, including the reload of all registers data from NVM

# Flash procedures

Flash memory is located on the FPGA sockets. See the available controls to work with it.

- ➤ Test Mode(\*) load data from flash to the chip

- Load from QSPI same as Test Mode(\*)

- Read read the chip project from the flash memory

- Program program a flash memory with the current project

- ➤ Erase clean flash memory (erased flash memory address values will be read as 0xFF)

Flash procedures

# **Project data window**

➤ Project data — a table with NVM/EEPROM bit sequences. You can change the bit values, import/export the sequences and use data to program the chip (for more info see section 2.2.7 Project data window)

**Project data control**

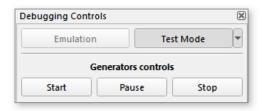

#### **Generator controls**

➤ Start/Pause/Stop All — control the generator state while Global linkage generator setting is enabled

**Generator controls**

# **Expansion Connectors (EC)**

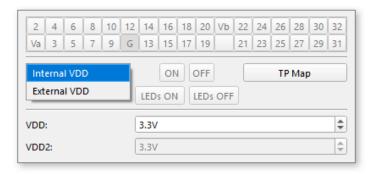

- ➤ Expansion Connectors this port was designed to connect the platform to the external circuits and apply external power, signal sources, and loads. There are several ways to connect/disconnect the expansion connectors (also, control the ECs on the work area via a hardware source):

- Connect/Disconnect all ECs by clicking ON/OFF buttons

- Connect/Disconnect a specific EC by clicking the ECs sequence number button

- Connect/Disconnect Va EC by clicking the Ext. VDD button

#### Power source selector

- ➤ Internal VDD the power is provided by the GreenPAK board

- ➤ External VDD the board measures voltage on the active power connector, and provides the same voltage level

Power source selector example

# **TP** map

➤ TP map — show the test point map on the work area to reflect the physical test points on the development platform

**Test point control**

#### LEDs ON/LEDs OFF

➤ LEDs ON/LEDs OFF — enable/disable all LEDs on the current platform (applicable only for development platforms with LED support). You can control a particular LED on the work area via a hardware source

**LEDs ON/OFF controls**

## Voltage level controls

➤ VDD — set the voltage level on the corresponding test points. If a selected value exceeds any of the board limitations, the dependent controls are blocked, and a warning is shown.

Voltage level controls

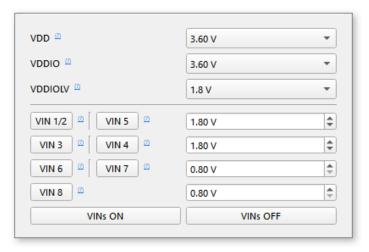

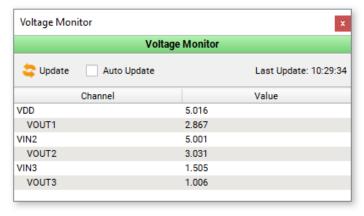

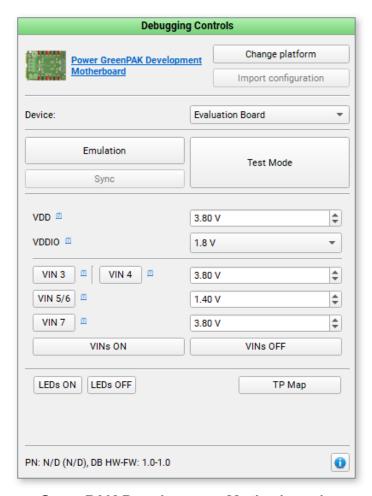

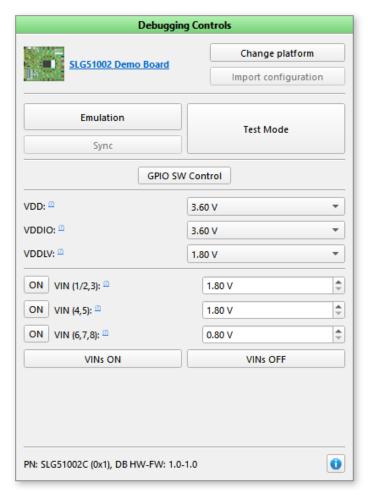

## **Power GreenPAK voltage controls**

- > VDD/VDDIO/VDDLV power supply voltage for overall chip and GPIOs

- > VIN power supply voltage on the corresponding LDO component's VINs

- ➤ VINs ON/OFF enable/disable all VINs

Power GreenPAK voltage controls

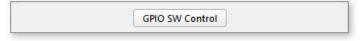

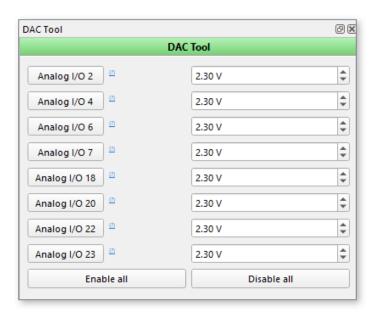

#### **GPIO SW control**

➤ GPIO SW Control — add buttons for software control of GPIOs, GPIO(SDA), GPI(SCL) and CS. Read more in section 2.2.1 Hardware sources

**Note:** the *GPIO SW Control* feature is permanently enabled in the *Power GreenPAK Development Motherboard*. For the *SLG51002CTR Demo Board*, you can activate the feature using the corresponding button in the *Debugging Controls*.

**GPIO** software control

### Info details

Brief information about the last detected chip (where e.g. V/G is a package name and e.g. 0x6 is a metal revision) and platform.

**Note:** A metal revision of a chip is an updated design that changes only the metal interconnect layers, leaving the underlying silicon unchanged.

Info details

- Information about the connected Part Number, development platform, software version, and operating system

- Show operation log

#### **Board selector**

Once the board is connected, the platform info appears on the bottom toolbar. To switch to a different platform, use the Board selector.

**Board selector**

Blink Blink with an LED of the board in use

- Update the chip and board Info details

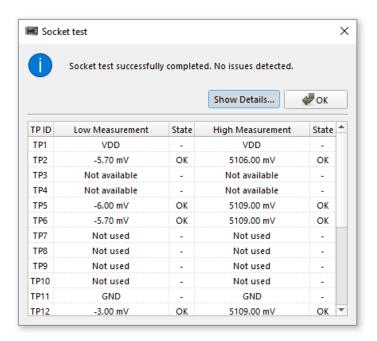

- Run the Socket Test

The Socket Test checks if the chip is successfully connected to the board. Click Show Details to get the Socket Test report.

Socket Test report

If the Socket Test fails for any reason, you can refer to the Troubleshooting section for assistance.

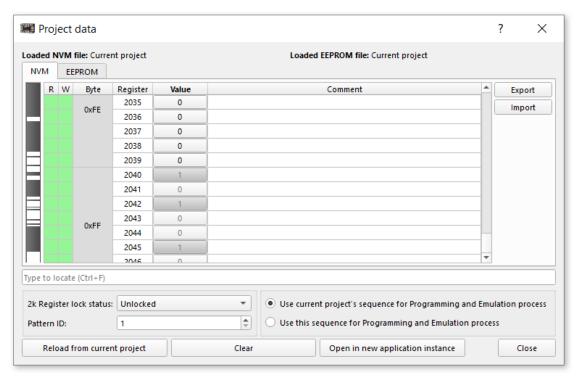

# 2.2.7 Project data window

This section contains the description of all Project data window controls.

Project data window with I2C Read/Write operations

# Project data window table:

- ➤ R and W show if a register is readable and writable

- I2C operations allowed

- I2C operations is not allowed

- ➤ Value allow to change the bit value of a register

- ➤ Comment add the notes

**Note:** The comments are stored neither in chip memory nor in the project file. However, you can *Export NVM* that includes the comments.

## Project data window controls:

- Lock status lock NVM Reading/Writing. Use this control to determine the possibility of Read /Write operations

- Pattern ID assign an ID to the current design

- ➤ Use current project's sequence for Programming and Emulation process choose the bit sequence from NVM Viewer for the programming and emulation processes

- ➤ Use this sequence for Programming and Emulation process choose the bit sequence from the Project Data table for the programming and emulation processes

- > Reload from the current project load bit sequence from the NVM Viewer to the Project Data table

- ➤ Clear set the whole Project Data table's bit range to 0

- Open in a new application instance open the bit sequence from the Project Data table in a new software instance

- Export save the bit sequence to a text file

- ➤ Import load the bit sequence from a text file

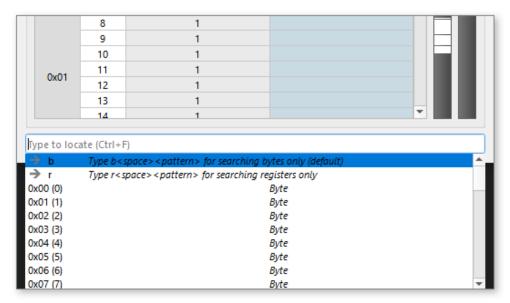

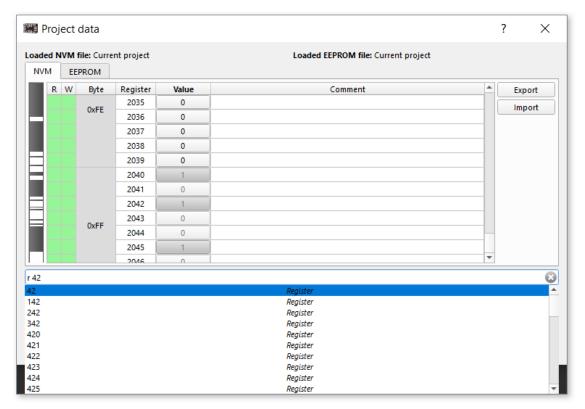

You can find the required byte or register by typing its number in the search field. To filter out bytes or registers from the search, use the following markers:

- ▶ b searching for bytes only

- r searching for registers only

Searching for registers

### 2.2.8 Demo Board and Demo mode

The *Demo* mode allows exploring possible applications of a specific Part Number. The *Demo* tab on the *Hub* window contains the list of the preconfigured projects. Click *Details* to find out more about the design. To open the project click *Run*.

Select a Demo project

To interact with the design, you can connect the specific *Demo Board*. Such board contains a soldered IC with a preprogrammed project.

Once you open the project, the workspace UI depends on whether the *Demo Board* is connected.

Waiting for the corresponding Demo Board connection

After the board detection is successful, the following controls become available:

- Write load the current project's NVM sequence to the device

- ➤ I2C Tools the following I2C Tools are available for *Demo* mode:

- I2C Virtual Inputs

- I2C Virtual Outputs

- I2C Reconfigurator

For more information refer to section 2.2.9 I2C Tools.

- ➤ 1 information about a Part Number, development platform, and operating system

- ➤ Close exit the Demo mode

**Demo Board detected**

**Note:** The *Demo* mode applies some limitations on specific features (operations with the project files, *Debug Tool*, *Simulation*). Exiting the *Demo* mode removes all limitations, yet keeps the current project open.

# 2.2.9 I2C Tools

The I2C Tools are the instruments that help to debug the project configuration by reading or writing the register data on the chip.

A chip's I2C communication macrocell allows an I2C bus master to read and write information at any moment via a serial channel directly to the registers via I2C protocol. The tool allows configuring the macrocell data on the fly.

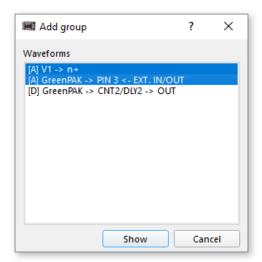

Once you enable *Debug* utility and select the platform, the following I2C Tools appear on the toolbar: *I2C Virtual Inputs*, *I2C Virtual Outputs*, and *I2C Reconfigurator*.

**Note:** To read/write data via I2C Tools, *Emulation* or *Test Mode* is required.

I2C Tools on the toolbar

## **I2C Virtual Inputs**

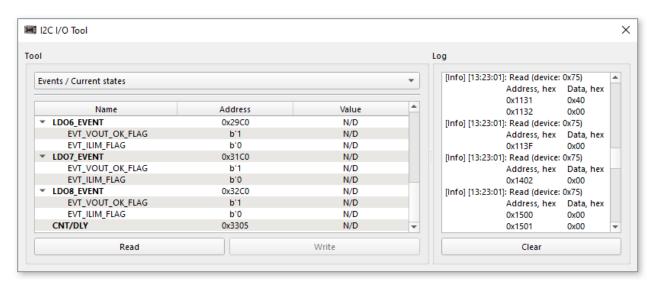

The I2C Tools contain the following instruments (the set of tools depends on the selected Part Number):

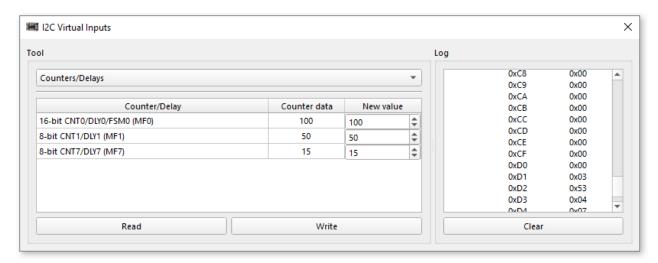

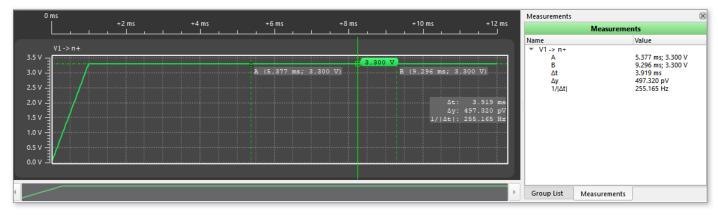

Counters/Delays — allows to read/write the counter data of a specific macrocell configured in

## CNT/DLY mode

**Managing Counters/Delays**

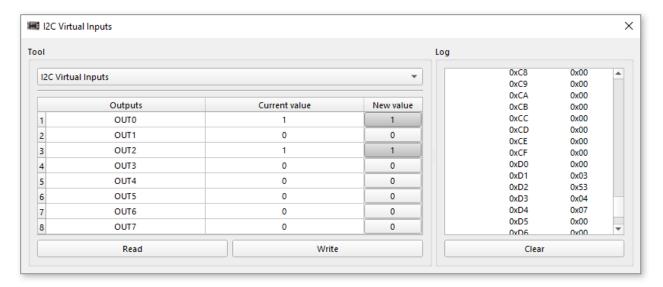

➤ I2C Virtual Inputs — allows you to read/write I2C virtual OUTs values of the I2C macrocell

**I2C Virtual Inputs**

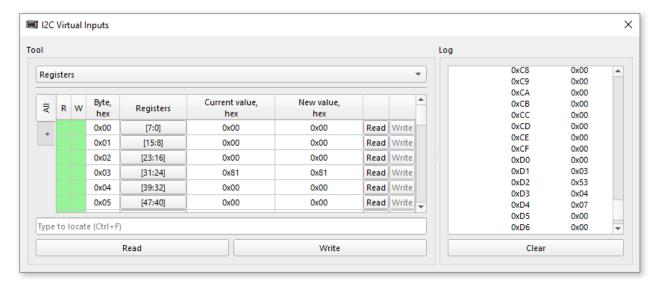

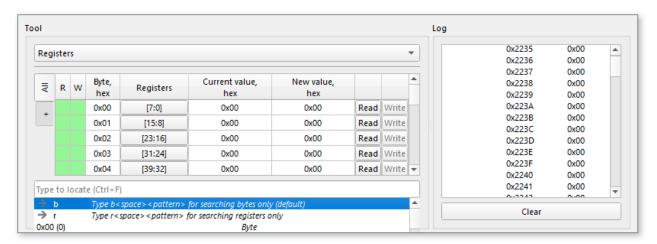

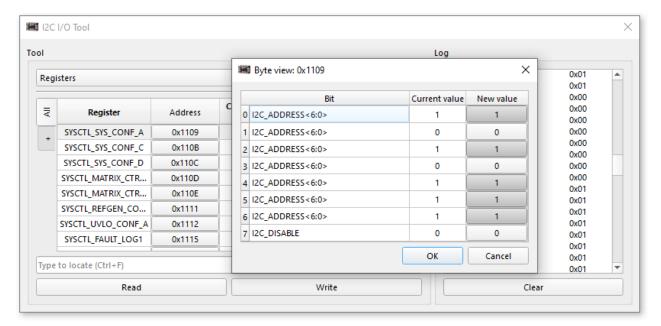

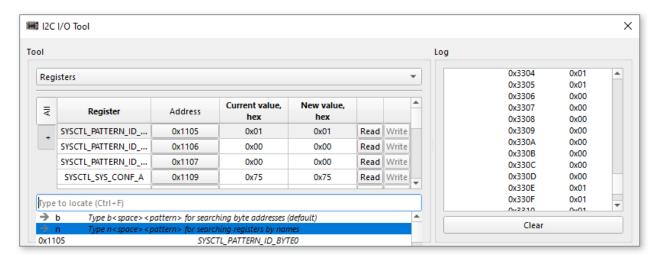

- > Registers allows you to read/write all of the chip registers data. It is possible to read/write:

- the certain register in each row

- all registers using the bottom buttons

Read/Write the registers data

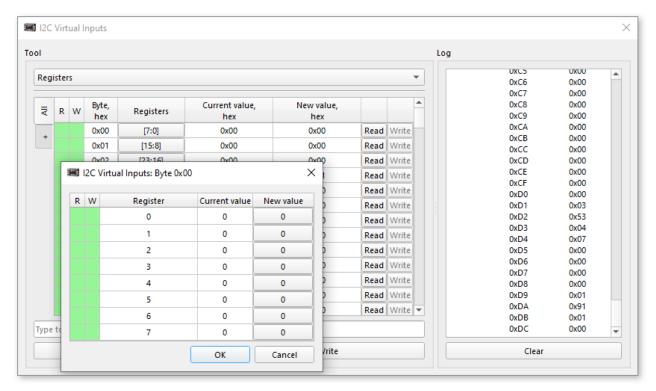

You can edit a register value in the following ways:

- enter the value in the New value column

- change the register bits by clicking a cell in the Registers column

Registers modification options

You can find a required byte or register(bit) by using the pattern below:

Filter options

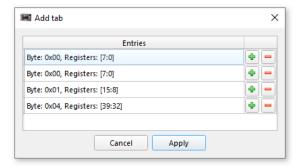

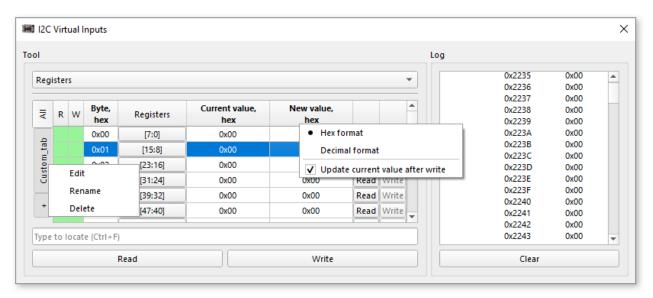

The *Registers* tool allows creating tabs with specific register ranges. Add a new tab by clicking the button under the *All* tab and the - and add entries with register ranges.

**Note:** Only the registers present under an active tab are read upon clicking the bottom *Read* button.

Add tab

You can also open the context menu for some additional options: edit, rename, or remove the tabs; switch between the hex or decimal value formats.

Remove a tick from Update current value after write checkbox if you do not wish to read the

overwritten values.

**Context menus**

The *R* and *W* columns show if a register is readable/writable:

- I2C operations are supported

- I2C operations are not supported

- I2C operations are unsupported for some bits of the register

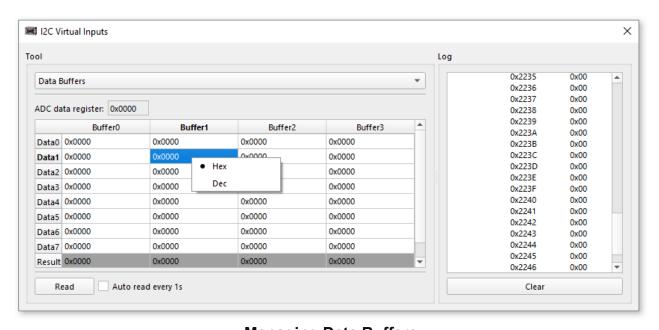

- ➤ Data Buffers allows you to read data from the Data Buffer macrocells and the ADC data register. For automatic data actualization, click Read while the Auto read every 1s option is enabled

**Managing Data Buffers**

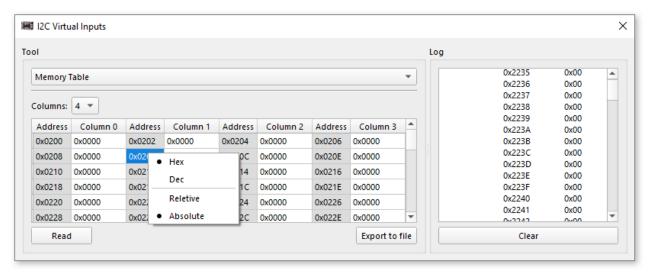

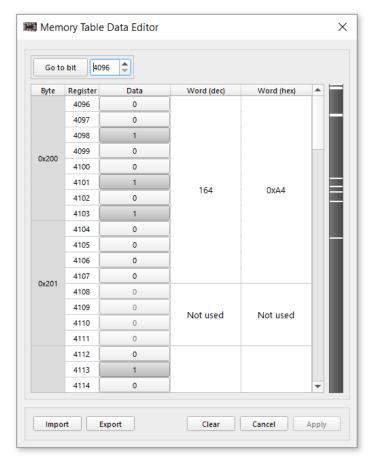

➤ Memory Table — read data from the Memory Table macrocell in the Column X section. To change the amount of displayed columns use the Columns selector. In addition to the decimal

and hexadecimal formats, applicable for both column types, the *Address* columns data view can be also changed using the following options:

- Absolute show the actual address of the register in the macrocell

- Relative show the register address starting with zero

You can save the read data in .csv format by clicking the Export to file button.

**Managing Memory Table**

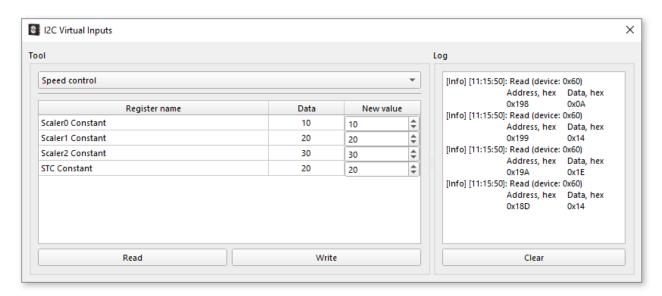

Speed control — displays and allows to read/write the constant of the Scalers and Speed/Torque Control macrocells

Speed control tool

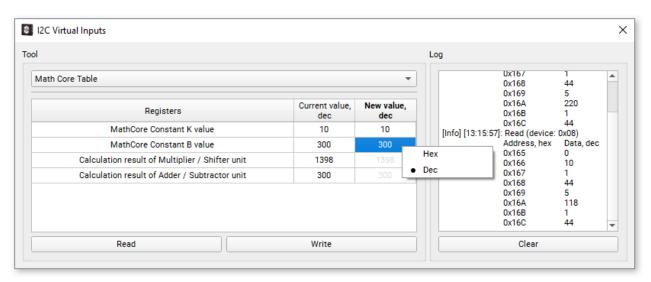

➤ Math Core Table — is designed to manage the Math Core component data from its Properties panel. You can set and read/write the K and B constants, as well as the results of mathematical operations (addition/subtraction and multiplication/division). Change the data

#### format in the context menu

**Math Core Table**

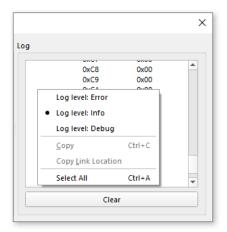

➤ Log — the results of recent read and write operations. The Log level has three severity settings, such as Debug, Error and Info displaying the most/least detailed information

Log context menu

## **I2C Virtual Outputs**

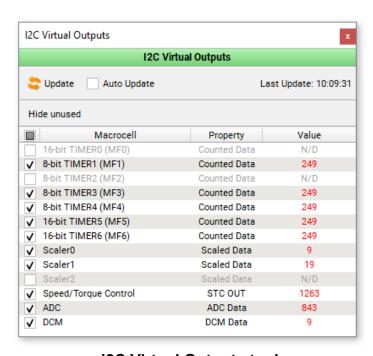

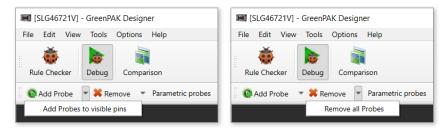

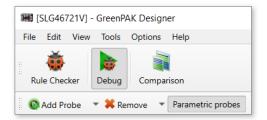

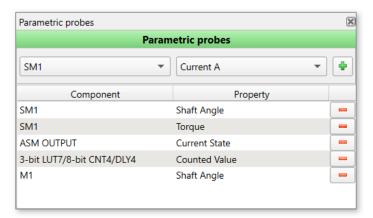

*I2C Virtual Outputs* allows you to read the state of certain macrocells. The tool includes the hardware probes, ASM state, and the current counted data of the specific counters.

➤ Probes (Matrix inputs) — reflect the current logic level on the macrocell output pins. You can add a probe by clicking Add Probe and then the required pin. Internal pins that support adding a probe are highlighted in green. Also, you can add probes to all visible pins at once by clicking

Add Probes to visible pins.

You can remove probes one by one or remove all probes at once.

➤ I2C Virtual Outputs tool — displays the current value of the selected components, such as e.g. CNT/DLY, ASM, Scaler, DCM, etc., read from the chip registers (see the Datasheet for the selected Part Number). To update the data or hide the unused blocks click the respective controls on the tool panel

**I2C Virtual Outputs tool**

## **I2C Reconfigurator**

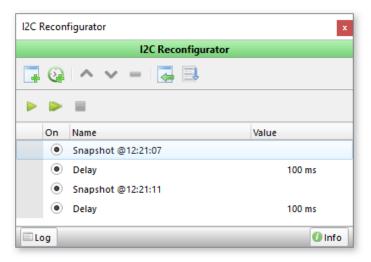

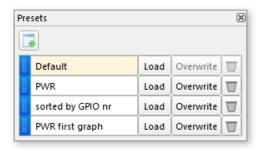

*I2C Reconfigurator* allows changing chip data dynamically by sending *NVM* snapshots to the chip. Snapshots are diff-based lists of changes. Each includes macrocell configurations and connections.

**Snapshot configuration**

You can work with the Reconfiguration scenarios using the following controls:

- add a snapshot of the work area

- add a delay between snapshots

- move the selected list item one level up

- move the selected list item one level down

- remove the selected list item

To see the list of changes which are applied, refer to Reconfiguration scenario controls:

- open a dialog with the list of changes applied; delays are included. You can also export the whole list to a file

- Import presets from a different project

Here is the list of snapshot sending controls:

- send the next snapshot to the chip and pause list execution

- send snapshots along with delays one by one continuously

- stop sending snapshots and reset the list pointer

You can also manipulate the selected snapshot using the following buttons:

➤ Load — send the configurations of the selected snapshot to the chip

Overwrite — make the desired changes and substitute the existing snapshot data

Load/Overwrite snapshot configurations

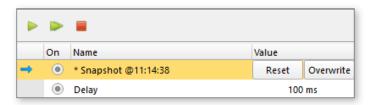

Reset — the button becomes available once you load a snapshot clicking the Send one button and make any configuration modifications afterwards. Click the button to return the snapshot to the primarily saved state

Reset snapshot configurations

The *Log* utility displays the changes applied to the chip. As delays don't imply any changes to the chip, they do not appear in the *Log*.

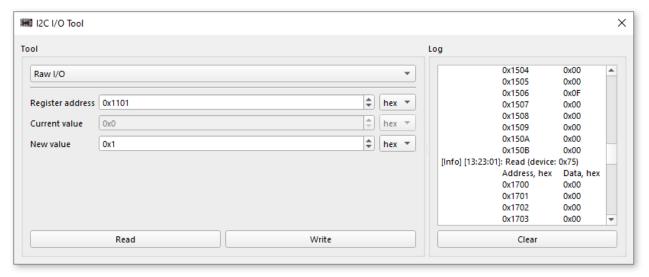

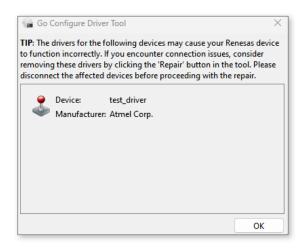

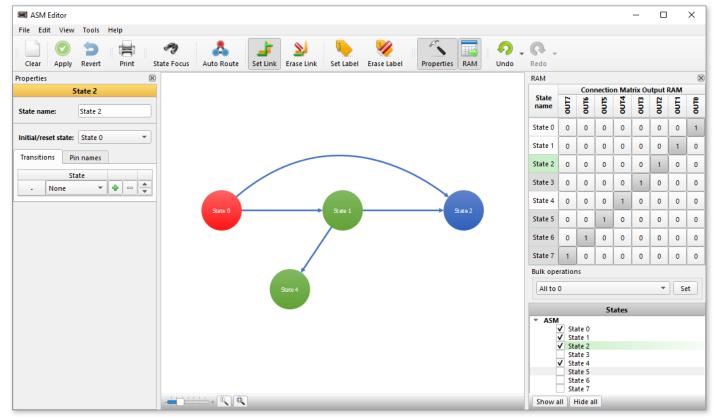

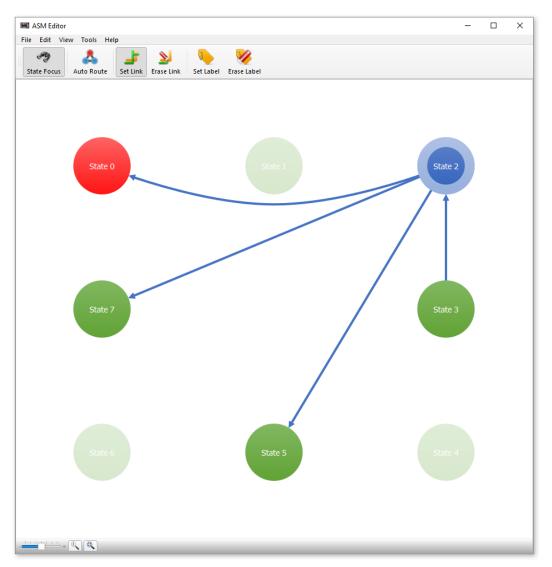

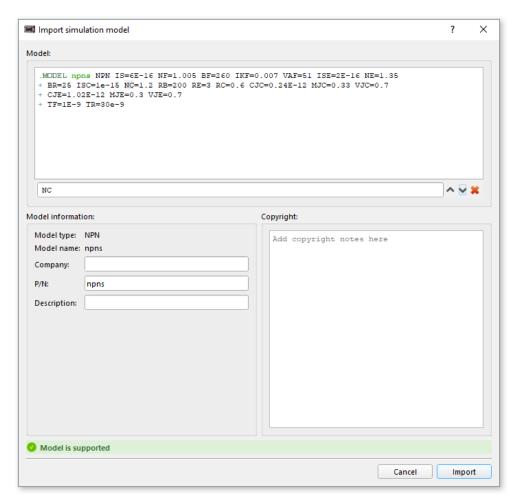

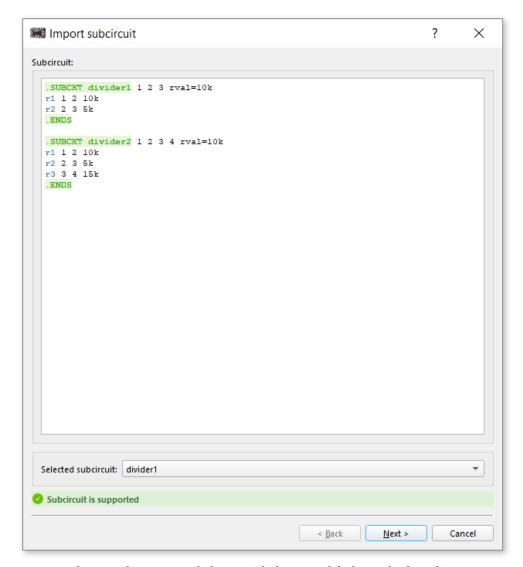

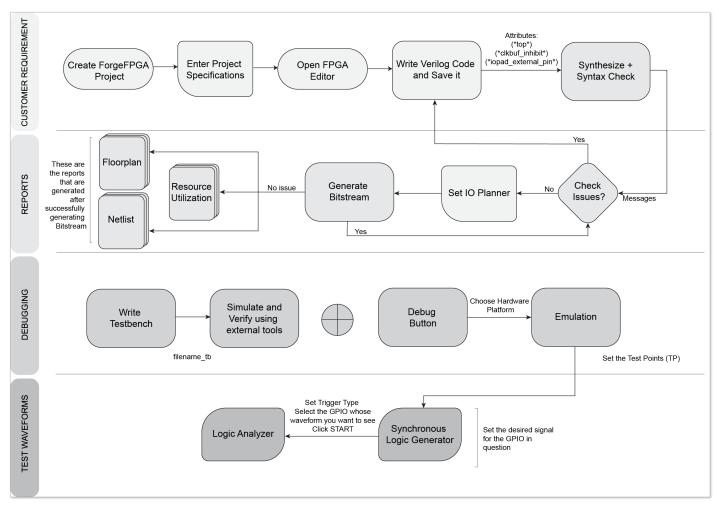

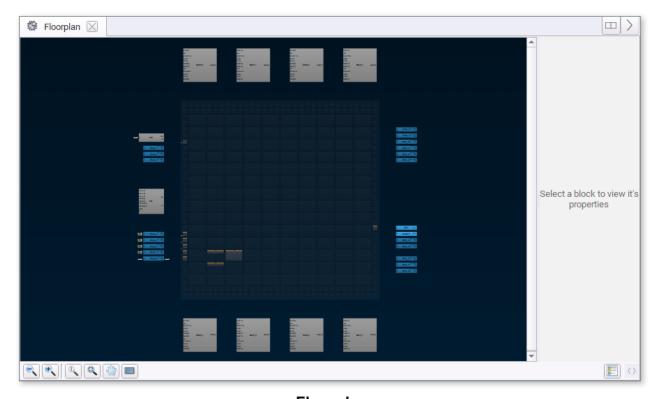

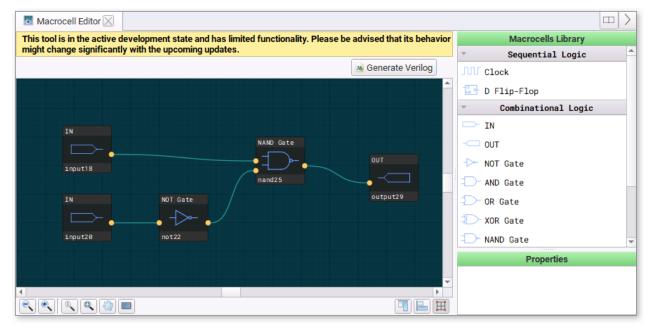

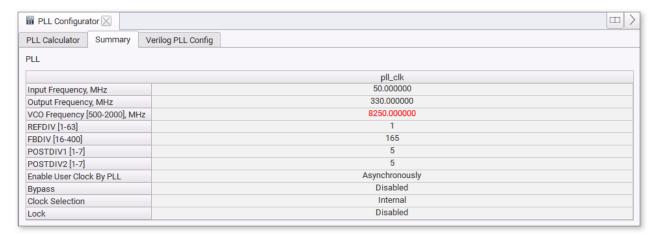

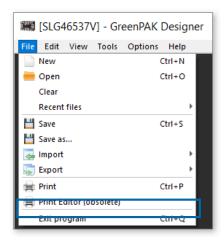

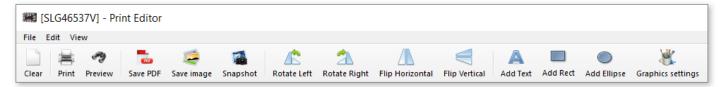

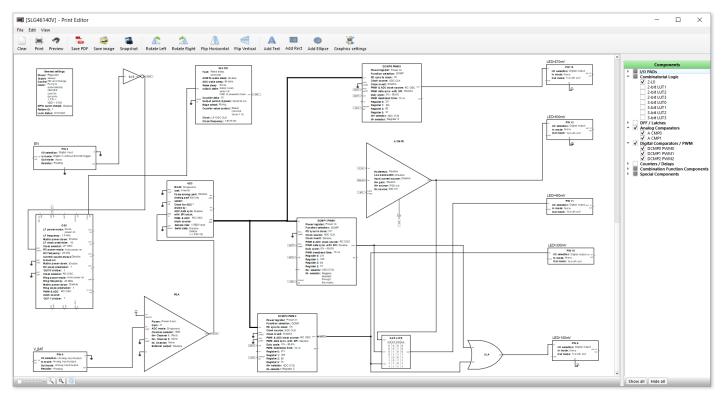

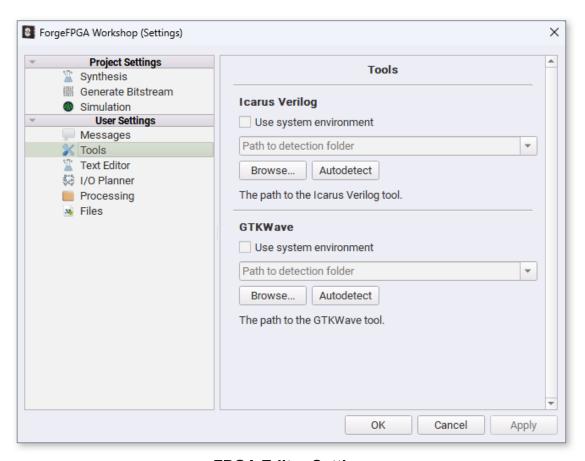

## 2.2.10 I2C I/O Tool