# Application Note I<sup>2</sup>C Bus Multiplexer AN-CM-285

## **Abstract**

This app note will explain how to build a bidirectional four-channel I<sup>2</sup>C bus multiplexer circuit and will also discuss how to use the circuit as a level shifter depending on SLG46826 IC

#### **Contents**

| Αb                       | ostract                                                    | 1                     |

|--------------------------|------------------------------------------------------------|-----------------------|

| Со                       | ontents                                                    | 2                     |

| Fiç                      | gures                                                      | 2                     |

| Та                       | ables                                                      | 2                     |

| 1                        | Terms and Definitions                                      | 3                     |

| 2                        | References                                                 | 3                     |

| 3                        | Introduction                                               | 4                     |

| 4                        | I <sup>2</sup> C Protocol                                  | 5                     |

| 5                        | I <sup>2</sup> C Bus Multiplexer                           | 6                     |

| 6                        | GreenPAK Design                                            |                       |

|                          | 6.1 SDA Line Multiplexer                                   |                       |

|                          | 6.2 SCL Line Multiplexer                                   |                       |

| 7                        | Level Shifting Feature1                                    |                       |

| 8                        | Results1                                                   |                       |

| 9                        | Conclusions 1                                              | 2                     |

|                          |                                                            |                       |

|                          |                                                            |                       |

|                          |                                                            |                       |

|                          | igurae                                                     |                       |

|                          | igures                                                     |                       |

| Fig<br>Fig<br>Fig<br>Fig | gure 1: I <sup>2</sup> C Network Diagram                   | 6<br>7<br>8<br>9<br>0 |

|                          | gure 7: I <sup>2</sup> C-LCDs Outputs After Implementation | 2                     |

|                          | able 1: Selecting Inputs States1                           |                       |

|                          | able 2: GreenPAK Pins Map of Implemented Multiplexer1      |                       |

#### 1 Terms and Definitions

I<sup>2</sup>C Inter-Integrated Circuit

SDA Serial Data Line

SCL Serial Clock Line

LUT Look-up table

NOR A digital logic gate that gives a true (1 or high) output if the two inputs are 0s

#### 2 References

For related documents and software, please visit:

GreenPAK™ Programmable Mixed-Signal Products | Renesas.

Download our free GreenPAK™ Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] Go Configure™ Software Hub | Renesas, Software Download and User Guide

- [2] AN-CM-285 I2C Bus Multiplexer.gp, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

- [5] SLG46826V, Datasheet

- [6] www.i2c.info

#### 3 Introduction

In this app note we will clarify how to build a bidirectional 2-bit mux circuit that can be used with I<sup>2</sup>C lines. The circuit also has the extra functionality of operating as a level shifter, if needed. The design is based upon the GreenPAK SLG46826V, although any GreenPAK with I<sup>2</sup>C can work for this purpose. Due to the bidirectionality of the SDA and SCL lines, this design can be utilized for single-master or multi-master I<sup>2</sup>C communication.

The SLG46826V GreenPAK is a dual-rail IC that includes all the elements needed to construct a bidirectional multiplexer circuit suiting the I<sup>2</sup>C protocol. Use of the GreenPAK IC enables a small form factor. In addition to the already-small size to implement the I<sup>2</sup>C multiplexer circuit, the GreenPAK is also able to integrate the Oscillator and Pull-up resistors needed for the circuit.

The design has been optimized for a real world application and can be easily modified to fit the requirements of the reader's system.

It has been examined by placing it within an I<sup>2</sup>C network comprised of an Arduino board and four I<sup>2</sup>C-LCD screens, wherein each screen contains the same I<sup>2</sup>C address. Each screen was individually written-to with the help of the designed GreenPAK IC.

#### 4 I<sup>2</sup>C Protocol

Connecting two or more devices to transmit and receive information requires a special path of communication, controlled by a communication protocol shared by both the sender and the receiver. An Inter-Integrated Circuit bus, also known as I<sup>2</sup>C, is a very common bidirectional communication bus, using two lines to send serial information between devices.

I<sup>2</sup>C is used to create a network of communication between a controller and a set of peripherals. It has become supported by numerous electronic sensors and actuators because it's efficient and easy to route. The I<sup>2</sup>C bus supports 7-bit and 10-bit address space device and consists of two signal lines: SCL and SDA lines, which are used to communicate with the devices. The SCL stands for 'serial clock' which carries a clock signal driven by the master. The SDA stands for 'serial data', whereupon the master and slave can both send and receive data. When there is no transfer between I<sup>2</sup>C peripherals, both SCL and SDA lines are pulled up to V<sub>DD</sub>.

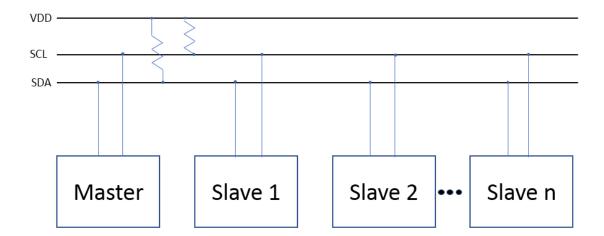

We can connect up to 128 devices using I<sup>2</sup>C protocol, all sharing the same SCL and SDA lines. A small-scale example is shown in Figure 1.

Systems often require several different supply voltages for different ICs, and peripherals today are often linked to the microcontroller with the help of an I<sup>2</sup>C bus and an I<sup>2</sup>C level shifter or I<sup>2</sup>C-bus multiplexer to resolve compatibility.

Figure 1: I<sup>2</sup>C Network Diagram

# 5 I<sup>2</sup>C Bus Multiplexer

In I<sup>2</sup>C networks every device must have a unique unrepeated address to achieve communication between the master and slave correctly, but when many sensors and peripherals are combined on the same bus it may happen that the same I<sup>2</sup>C address is allocated to more than one device. To solve this problem, we implement a unique multiplexing circuit that connects slaves having the same address to the communication buses, and we may interchange channels through the polling inputs.

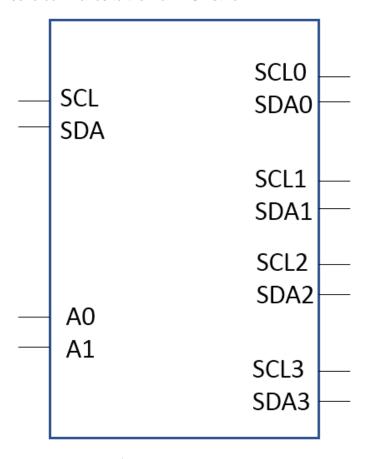

The I<sup>2</sup>C bus multiplexer circuit is a bidirectional selector for both buses SCL and SDA, designed using the SLG46826 dual-rail IC to build a four-channel output mux circuit as illustrated in Figure 2. The bi-directionality of the SCL line, though not required for a single-master system, ensures that the topology can be used in a multi-master configuration, wherein a primary master (attached to the left side of Figure 2) can arbitrate whether a secondary master (connected to address on the right-hand side of Figure 2) can send commands to the main I<sup>2</sup>C network.

Figure 2: I<sup>2</sup>C Bus Multiplexer IC Diagram

## 6 GreenPAK Design

The design consists of two main parts; the SDA line multiplexer and the SCL line multiplexer. The key behaviour of this circuit is the configuration and flexibility of the SLG46826's bi-directional pins and the OE (Output Enable) logic that configures whether a particular pin should be an input or output.

#### 6.1 SDA Line Multiplexer

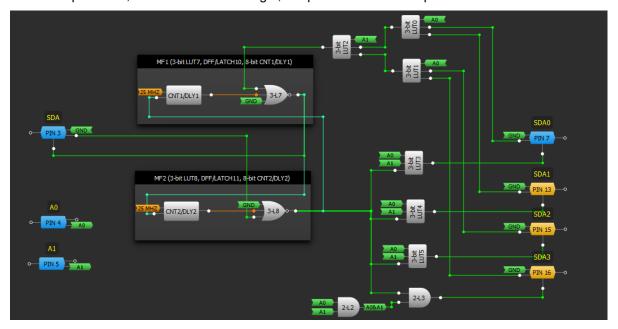

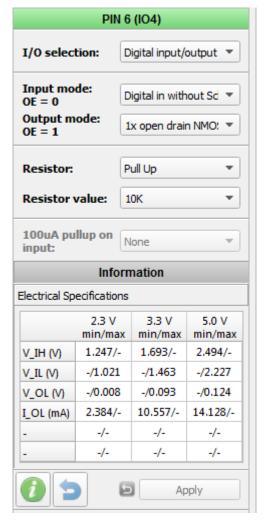

In this part, Pin 3 will be linked to one of the Pins 7, 13, 15, 16 based on the state of the inputs A0 and A1. These inputs have been configured to act as Digital input/output. The output type is Open Drain NMOS and the input is pulled up to 10 k $\Omega$  resistors. As illustrated in Figure 3 the NOR gates control OE 'Output Enable' of every pin; when OE is 'low', the pin becomes an input connected to a 10K Pull-up resistor, and when OE is at 'high', the pin becomes an output and is GND.

Figure 3: SDA Line Mux Design

The output of 3-bit LUT7 is linked to OE of Pin 3 while the output of 3L8 NOR gate will be multiplexed and connected to the OE of the Pins 7, 13, 15, 16. The time delay blocks were configured to operate as Falling Edge Delay and hence generate a time delay to NOR gates. 2-bit demultiplexer was built using the blocks 3L3, 3L4, 3L5, 2L2, and 2L3.

Thus, when [A1A0] = [00] the 3L8 output passes to Pin 7 and the active channel is 0 through 3L3, while the rest of the channels are inputs pulled up to 1. When [A1A0] = [01] the 3L8 output passes to Pin 13 through 3L4, when [A1A0] = [10] the output passes to Pin 15 through 3L5, and when [A1A0] = [11] the 3L8 output passes to Pin 16 through the two AND gates 2L3 and 2L2.

Figure 4: Pin 6 Properties

The blocks 3L0,3L1, and 3L2 were used to construct a 2-bit multiplexer circuit; it then selects one input signal coming from Pins 7, 13,15, 16 and passes it to the NOR gate in order to be later passed to Pin 3 (SDA). Pins 4 and 5 were configured to serve as inputs linked to a Pull-down resistor, then channel 0 is active as [A0A1] = [00] in the initial state.

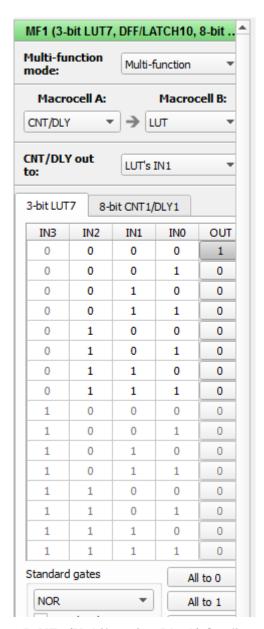

MF1 and MF2 are multifunction blocks that can be configured to carry out more than one function. They have been employed in this design to generate a time delay, in addition, to formulate NOR gate. The 'DLY IN' input for every counter is connected to a NOR gate output.

Figure 5: MF1 (Multifunction Block) Configuration

#### **Design Sequence of Events:**

When the bus is in Idle state (not transmitting or receiving) the communication pins are then linked to a Pull-up resistor (high) and all pins in an input state according to the signal passing to OE. If one of the inputs receives a LO signal, the signal is propagated through a NOR gate, causing a HI signal at the appropriate OE, based upon A0A1. This configures the pin into output and is consequently held to GND. If the input returns to HI a short time delay is generated to hold OE state to take into consideration the time the pin needs to change from LO to HI (from input to output).

To proceed with the sequence of events, consider this example:

In the initial state, there is no communication on the bus and [A1A0] = [00]. i.e. all pins are inputs, and since the Pull-up resistor is activated for the inputs, the signal HI passes into the IC from all inputs. When Pin 3 receives a LO from the master, the signal passes to 3L8, then to 3-bit LUT3 and 3L3 output is low as well for the signal low reaches OE of Pin 7 which makes Pin 7 change its state from input to output. The LO signal propagates to the external device through the bus SDA0.

When the master releases the communication bus the input becomes HI due to the existing Pull-up resistor. The HI then passes to 3L8 which reverses the signal and passes the signal low to the OE of Pin 7, causing the pin to change its state from output to input. Since the Pull-up resistor is active, the HI is passed to the external device and a time delay is applied on the falling edge in order to give sufficient time to the pin to alter its IO state prior to receiving new values.

#### 6.2 **SCL Line Multiplexer**

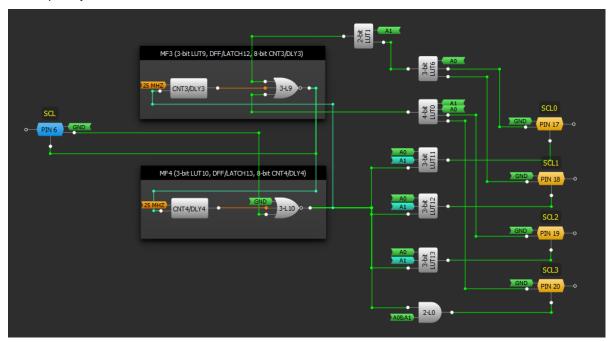

Like the design of the multiplexer circuit of SDA bus, another multiplexer circuit for SCL bus has been designed with the same configuration, where Pins 6, 17, 18, 19 and 20 were configured to operate as a Digital Input/Output and the internal Pull-up resistor was activated on the pins. Hence, the signal coming from the master through Pin 6 will be connected to one of the Pins 17, 18, 19 and 20 according to A1 and A0. The blocks 3L11, 3L12, 3L13, and 2L0 were used to build a 2-bit demultiplexer while the blocks 4L0, 3L6, and 2L1 were employed to construct a 2-bit mux and consequently the bi-directional communication.

Figure 6: SCL Line Mux Design

**Table 1: Selecting Inputs States**

| Α0 | A1 | Enabled channel |

|----|----|-----------------|

| 0  | 0  | Channel 0       |

| 1  | 0  | Channel 1       |

| 0  | 1  | Channel 2       |

| 1  | 1  | Channel 3       |

# 7 Level Shifting Feature

The SLG46826 has dual power supplies  $V_{DD}$  and  $V_{DD2}$ , which allows the design to add level shifting as another feature of the mux circuit. Pins 3, 6, and 7 are powered from  $V_{DD}$ , while Pins 13, 15, 16, 17, 18, 19, and 20 are powered from  $V_{DD2}$ . Therefore, it's possible to use this mux circuit as a level shifting circuit for channels 1, 2, 3 without channel 0. The desired voltage ( $V_{DD}$  and  $V_{DD2}$ ) can be selected from project Info.

Table 2: GreenPAK Pins Map of Implemented Multiplexer

| Power    | GreenPAK<br>Pin | Function | GreenPAK<br>Pin | Function |           | Power            |

|----------|-----------------|----------|-----------------|----------|-----------|------------------|

| $V_{DD}$ | 3               | SDA      | 7               | SDA0     | Channel 0 | $V_{DD}$         |

| $V_{DD}$ | 6               | SCL      | 17              | SCL0     |           | $V_{DD2}$        |

|          |                 |          | 13              | SDA1     | Channel 1 | $V_{DD2}$        |

|          |                 |          |                 |          |           |                  |

|          |                 |          | 18              | SCL1     |           | V <sub>DD2</sub> |

|          |                 |          | 15              | SDA2     | Channel 2 | $V_{DD2}$        |

|          |                 |          | 19              | SCL2     |           | $V_{DD2}$        |

|          |                 |          | 16              | SDA3     | Channel 3 | $V_{DD2}$        |

|          |                 |          | 20              | SCL3     |           | $V_{DD2}$        |

#### 8 Results

To make sure that the design is working as expected, the design was placed in a real-world scenario: to control four screens (I<sup>2</sup>C-LCD) all having the same static I<sup>2</sup>C address. All communications came from a single master, in this case, an Arduino board.

A program has been written for an Arduino board to operate as a master and print a different phrase on each screen through I<sup>2</sup>C protocol. The screens were interchanged on the buses by the I<sup>2</sup>C mux circuit and Arduino digital outputs to control A0 and A1. The buses were multiplexed between screens before every print instruction. Figure 7 depicts the screens output after implementing.

Figure 7: I<sup>2</sup>C-LCDs Outputs After Implementation

#### 9 Conclusions

In this app note, a 2-bit multiplexer circuit has been built using an SLG46826 IC and the GreenPAK Designer Software. A level-shifting implementation is also easily realizable with the SLG46826.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.