# DC-DC Boost & Buzzer Driver SLG47105

This application note describes how to create a Piezo Driver and Boost DC-DC Converter using one HVPAK SLG47105.

The application note comes complete with design files which can be found in the Reference section.

#### **Contents**

| 1.   | Terms and Definitions                                          | . 1 |

|------|----------------------------------------------------------------|-----|

| 2.   | References                                                     | . 2 |

| 3.   | Introduction                                                   | . 3 |

| 4.   | Operating Principle and HVPAK Design                           | . 3 |

| 5.   | Design Testing                                                 | . 5 |

| 6.   | PCB Design                                                     | . 6 |

| 7.   | BOM                                                            | . 7 |

| 8.   | Conclusion                                                     | . 7 |

| 9.   | Revision History                                               | . 8 |

| Fi   | gures                                                          |     |

|      | ure 1. DC-DC Boost & Buzzer Driver Circuit Diagram             |     |

|      | ıre 2. DC-DC Boost & Buzzer Driver HVPAK Design                |     |

|      | re 3. PIN 7 Piezo Signal (blue) & Current Consumption (yellow) |     |

| Figu | ıre 4. Boost & Buzzer Driver Demo PCB Design (Top Side)        | 6   |

| Figu | ure 5. Boost & Buzzer Driver Demo PCB Design (Bottom Side)     | 6   |

### 1. Terms and Definitions

DFF D Flip-Flop

HV High Voltage

LUT Look-up Table

MF Multi-function

OSC Oscillator

#### 2. References

For related documents and software, please visit: HVPAK™ | Renesas

Download our free Go Configure Software Hub [1] to open the .hvp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in a complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] Go Configure Software Hub, Software Download, and User Guide

- [2] AN-CM-378 DC-DC Boost & Buzzer Driver, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

- [5] SLG47105 Datasheet, Renesas Electronics

Author: Irena Zhuravchak, Renesas Electronics

#### 3. Introduction

The HVPAK SLG47105 is a flexible configurable mixed-signal IC able to combine a Boost DC-DC Converter and a Piezo Driver in a single package with a small number of external components.

The main goal of this application note is to show how to configure HVPAK to drive a 2.5 kHz Piezo and how to create a Boost DC-DC Converter from 3 V to 13 V. The whole circuit is powered with a 3V CR2032 battery. Such a schematic can be used in devices that require short-term notifications (keychains for finding things, and others). When the push button is pressed, the DC-DC Converter boosts the voltage to 13 V which powers the Piezo Driver. Then the short pattern is played, and the circuit goes to sleep mode until the button is pressed again. When the circuit is ON – it consumes nearly 15 mA, and in sleep mode less than 50 nA. This ensures up to 800 activations on one battery!

## 4. Operating Principle and HVPAK Design

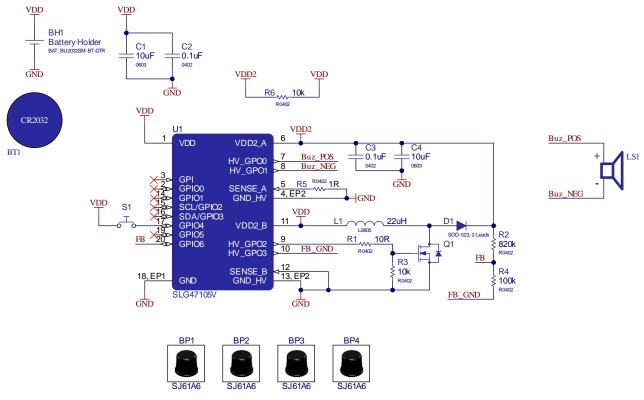

The DC-DC Boost & Buzzer Driver Circuit Diagram is shown in Figure 1.

Figure 1. DC-DC Boost & Buzzer Driver Circuit Diagram

The design consists of a DC-DC Boost Converter and Buzzer Driver parts.

For the DC-DC Boost Converter, the PWM0 forms the ~197 kHz signal. The DFF1, DFF5, and DFF6 form the clock for a soft start to reduce inrush current, which can occur when the device is first turned on. Minimum and maximum duty cycles are set by Pipe Delay and CNT4/DLY4.

The VDD and VDD2\_B are connected to a 3 V battery. VDD2\_A is connected to Boost output. To monitor this voltage, the resistors R2 and R4 form the resistive divider with a feedback signal, which goes to PIN20 (Analog Input). This feedback voltage is compared with 1024 mV Vref by ACMP1H forming the ACMP signal which goes to the CHOP input of the PWM Chopper 0. If the VDD2 exceeds 9.5 V, the ACMP signal is HIGH and chop the formed PWM signal. The PWM Chopper 0 output goes to HV OUT CTRL1 (Half Bridge) input IN0. Then PIN 9 drives an NFET of Boost Converter.

To reduce the current consumption, a resistive divider is connected to PIN 10 (Low Side ON) with a GND input.

Note: it's possible to change the ACMP1H Vref and boost the voltage up to 13 V.

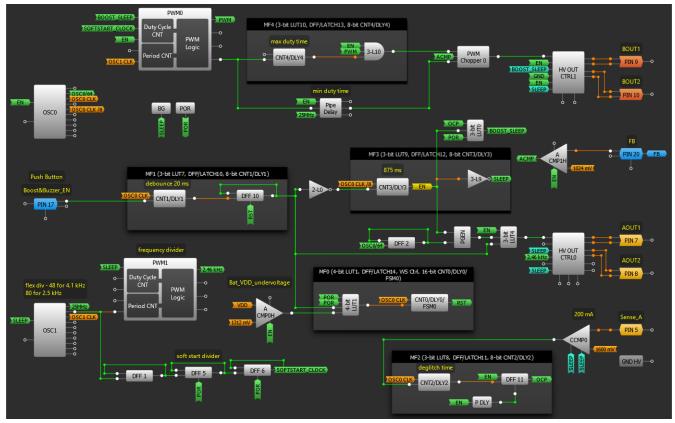

The HVPAK Design is shown in Figure 2.

Figure 2. DC-DC Boost & Buzzer Driver HVPAK Design

The HV OUT CTRL0 (Full Bridge) drives a Piezo. PWM1 is used as a frequency divider and forms a 2.5 kHz signal (resonant frequency of a piezo), this signal comes to PH input of HV OUT CTRL0.

The 3-bit LUT4 forms the EN signal for the HV OUT CTRL0. It consists of the sound pattern signal and the general EN signal. The PGEN generates the sound pattern (01010101101011). The EN signal – the general ENABLE signal for the whole design is HIGH for 875 ms (CNT3/DLY3 One Shot) if the button is pressed (MF1) and the VDD is higher than ~2.6 V (ACMP0H + MF0).

The 3-bit LUT9 inverts the EN signal forming the SLEEP signal to shut down the blocks when they are not used to reduce the power consumption.

The 3-bit LUT0 forms the BOOST\_SLEEP signal. The Boost will power down if there is no POR signal, the SLEEP signal is HIGH, or the OCP signal is HIGH. The CCMP0 monitors the piezo current and if it exceeds 200 mA, the OCP signal is HIGH (MF2).

# 5. Design Testing

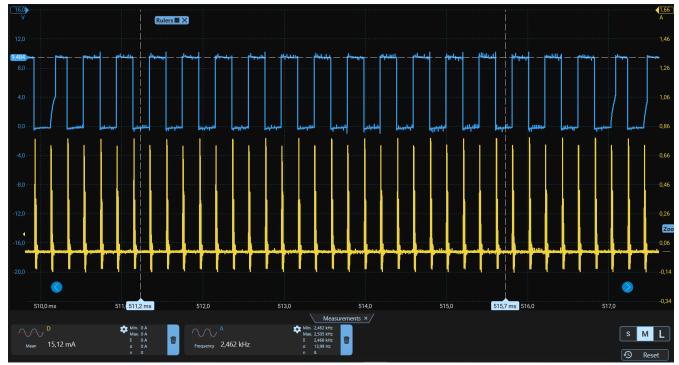

Channel 1 (blue / 1st line) - PIN 7 (Piezo).

Channel 2 (yellow / 2<sup>nd</sup> line) - GND (current).

Figure 3. PIN 7 Piezo Signal (blue) & Current Consumption (yellow)

As can be seen in Figure 3, the VDD2 level is 9.5 V as expected, and the Piezo frequency is 2.5 kHz. The average current consumption is 15 mA. The current in sleep mode is below 50 nA, which means up to 800 activations without replacing the battery!

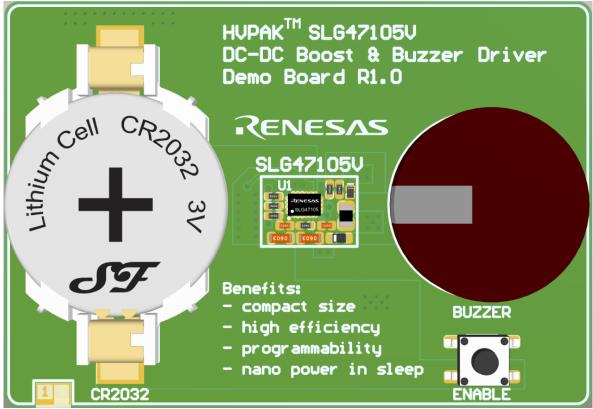

# 6. PCB Design

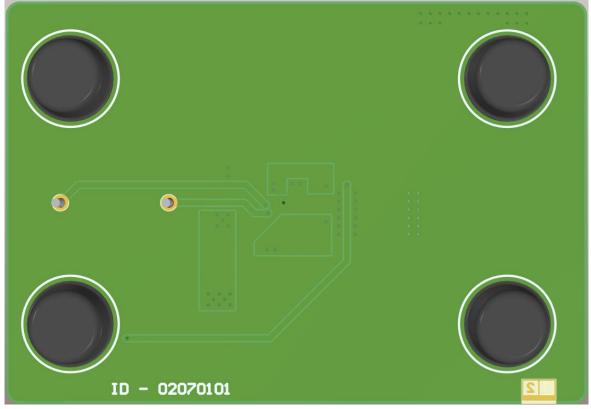

The proposed Demo PCB Design is shown in Figure 4 (top) and Figure 5 (bottom). As can be seen in Figure 4, the design is so compact that it can be placed under the buzzer.

Figure 4. Boost & Buzzer Driver Demo PCB Design (Top Side)

Figure 5. Boost & Buzzer Driver Demo PCB Design (Bottom Side)

#### **7. BOM**

| #  | Designator | Name                   | Manufacturer Part<br>Number               | Manufacturer              | Quantity |

|----|------------|------------------------|-------------------------------------------|---------------------------|----------|

| 1  | BH1        | Battery Holder         | BU2032SM-BT-GTR                           | Memory Protection Devices | 1        |

| 2  | BP1- BP4   | SJ61A6                 | 7010334512                                | 3M                        | 4        |

| 3  | BT1        | CR2032                 | CR-2032L/BN                               | Panasonic                 | 1        |

| 4  | C1, C4     | 10uF 20% 25V X5R 0603  | CL10A106MA8NRNC                           | Samsung Electro-Mechanics | 2        |

| 5  | C2, C3     | 0.1uF 10% 25V X5R 0402 | CL05A104KA5NNNC                           | Samsung Electro-Mechanics | 2        |

| 6  | D1         | RB521S30T1G            | RB521S30T1G                               | ON Semiconductor          | 1        |

| 7  | L1         | 22uH 220mA             | MLZ2012P220WT000                          | TDK                       | 1        |

| 8  | LS1        | SFN-17-B               | SFN-17-B                                  | Global Tone               | 1        |

| 9  | Q1         | MOSFET-N               | DMN2400UFB-7                              | Diodes                    | 1        |

| 10 | R1         | 10R 1% 0402            | RC0402FR-0710RL                           | YAGEO                     | 1        |

| 11 | R2         | 820k 1% 0402           | RC0402FR-07820KL                          | YAGEO                     | 1        |

| 12 | R3, R6     | 10k 1% 0402            | RC0402FR-0710KL                           | YAGEO                     | 2        |

| 13 | R4         | 100k 1% 0402           | RC0402FR-07100KL                          | YAGEO                     | 1        |

| 14 | R5         | 1R 1% 0402             | RC0402FR-071RL                            | Yageo                     | 1        |

| 15 | S1         | Sw Tactile NO          | PTS647SK38SMTR2LF<br>S                    | ITT C&K                   | 1        |

| 16 | U1         | SLG47105V              | SLG47105V Renesas Electronics America Inc |                           | 1        |

### 8. Conclusion

This application note describes how to configure the HVPAK SLG47105 to create a Boost & Buzzer Driver device that can work with a single 3 V CR2032 battery. With its extremely low current consumption, up to 800 activations without battery replacement are possible!

The flexibility of the internal resources allows adapting it to the needs of the customer without effort.

# 9. Revision History

| Revision | Date          | Description     |

|----------|---------------|-----------------|

| 1.00     | June 26, 2024 | Initial release |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.