# **Application note**

# DA9210 automotive 42 VF-BGA Layout Recommendation AN-PM-040

Application Note

#### DA9210 PCB Layout Recommendation for 42 VF-BGA

# Abstract

This application note provides recommendations for placing and routing the DA9210 device, 42 VF-BGA automotive variant. It also describes the passive components needed for proper functioning of the device. Application developers should treat this document as a guideline, not as a hard requirement, since target applications may have different requirements.

# Contents

| 1.                            | Revision history 3    |         |                                   |   |  |  |  |

|-------------------------------|-----------------------|---------|-----------------------------------|---|--|--|--|

| 2.                            | Terms and definitions |         |                                   |   |  |  |  |

| 3.                            | Refer                 | rences  |                                   |   |  |  |  |

| 4.                            | Intro                 | ductior | 1                                 | 4 |  |  |  |

| 5.                            | Layo                  | ut reco | mmendations                       | 5 |  |  |  |

|                               | 5.1                   | DA922   | 10 automotive package information | 5 |  |  |  |

|                               |                       | 5.1.1   | DA9210 ball map                   | 5 |  |  |  |

|                               |                       |         | Package outline drawing           |   |  |  |  |

|                               | 5.2                   | Multi-p | hase Buck converter               |   |  |  |  |

|                               |                       | 5.2.1   | Device grounding                  | 9 |  |  |  |

|                               |                       | 5.2.2   | Buck power supply input pins      |   |  |  |  |

|                               |                       | 5.2.3   | Buck output                       |   |  |  |  |

|                               |                       | 5.2.4   | Feedback lines                    |   |  |  |  |

|                               | 5.3                   |         | ence voltage source               |   |  |  |  |

|                               | 5.4                   |         | nunication interfaces             |   |  |  |  |

| 5.5 GPIOs and control signals |                       |         |                                   |   |  |  |  |

# **Figures**

| Figure 1: Schematic drawing                              | 4  |

|----------------------------------------------------------|----|

| Figure 2: DA9210 42VF-BGA ball map                       |    |

| Figure 3: DA9210 42 VF-BGA package drawing               |    |

| Figure 4: Example of components placement on 4-layer PCB |    |

| Figure 5: Device ground connection                       |    |

| Figure 6: Device ground connection                       | 10 |

| Figure 7: VSS_QUIET connection                           | 11 |

| Figure 8: Input capacitors, placement and routing        | 12 |

| Figure 9: Power supply capacitors                        | 13 |

| Figure 10: Inductors, placement and routing              | 14 |

| Figure 11 Parallel output trace                          | 15 |

| Figure 13 Plane structure filtering                      | 16 |

| Figure 12 Output capacitors placement                    | 16 |

| Figure 14 Feedback lines routing                         | 17 |

| Figure 15 Feedback lines shielding                       | 17 |

| Figure 16 Reference component placement and routing      | 18 |

| Figure 17 Interfaces lines                               |    |

| Figure 18 GPIO and control signals routing example       | 20 |

# 1. Revision history

| Version | Date     | Description       |

|---------|----------|-------------------|

| 1.0     | Sep 2014 | Initial revision. |

|         |          |                   |

# 2. Terms and definitions

| BGA | Ball Grid Array |

|-----|-----------------|

|-----|-----------------|

- PCB Printed Circuit Board

- PTH Plate Through-Hole

## 3. References

1. DA9210, Data sheet, Dialog Semiconductor

| Δn | nli | icati | on | N | ote |  |

|----|-----|-------|----|---|-----|--|

| κр | μ   | Lau   |    |   | Ole |  |

# 4. Introduction

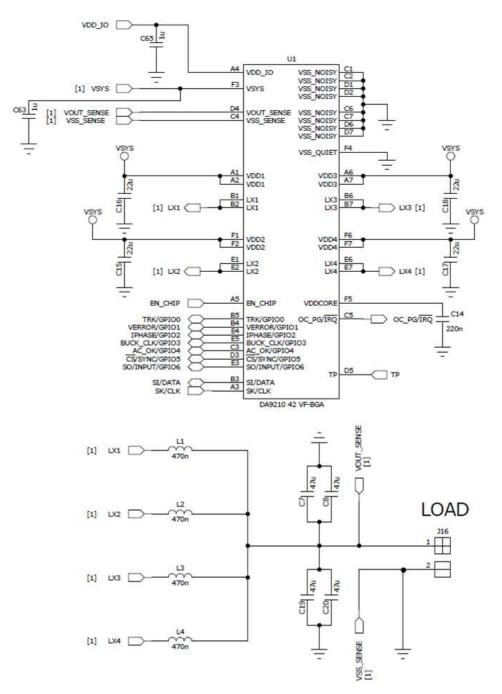

DA9210 is a 4-phase Buck converter, capable of delivering a 12 A output current with an input voltage range of 2.8 to 5.5 V and an output voltage range of 0.3 to 1.57 V. The basic recommended components and connections for single chip operation are shown in Figure 1.

The layout recommendations in section 5 are related to the schematic drawing below.

| Ap | plica | tion | Note |

|----|-------|------|------|

# 5. Layout recommendations

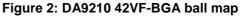

The automotive version of DA9210 is packaged in a 42-pin VF-BGA with a 0.8 mm pitch. The footprint is designed such that the PCB layout can be done using standard drilled PTH VIAs.

The PCB layout can be done with a 4-layer PCB stack-up however, when the device is part of a more complex system, the number of routing layers and other PCB parameters are determined by the ecosystem as a whole.

This chapter is divided into several sections, ranked by priority from the most important to less critical layout tasks:

- Package information, section 5.1

- Multiphase Buck convertor, section 5.2

- Reference voltage, section 5.3

- Communication interfaces, section 5.4

- GPIOs and control signals, section 5.5

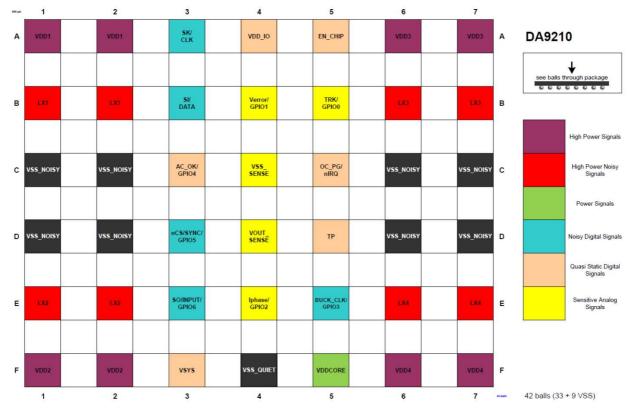

Each of the blocks has separate design rules. The ball map in section 5.1 is given as additional information to help in understanding the PCB diagrams in the remainder of the document.

#### 5.1 DA9210 automotive package information

#### 5.1.1 DA9210 ball map

```

Application Note

```

# Table 1: DA9210 42VF-BGA pin list

| Pin<br>42 VF-BGA                  | Signal name | Alternate<br>function | Туре    | Description                                                                                                   |

|-----------------------------------|-------------|-----------------------|---------|---------------------------------------------------------------------------------------------------------------|

| B1, B2                            | LX1         |                       | AO      | Switching node for phase 1                                                                                    |

| E1, E2                            | LX2         |                       | AO      | Switching node for phase 2                                                                                    |

| B6, B7                            | LX3         |                       | AO      | Switching node for phase 3                                                                                    |

| E6, E7                            | LX4         |                       | AO      | Switching node for phase 4                                                                                    |

| A1, A2                            | VDD1        |                       | PS      | Supply voltage for phase 1<br>To be connected to VSYS                                                         |

| F1, F2                            | VDD2        |                       | PS      | Supply voltage for phase 2<br>To be connected to VSYS                                                         |

| A6, A7                            | VDD3        |                       | PS      | Supply voltage for phase 3<br>To be connected to VSYS                                                         |

| F6, F7                            | VDD4        |                       | PS      | Supply voltage for phase 4<br>To be connected to VSYS                                                         |

| A5                                | EN_CHIP     |                       | DI      | IC Enable Signal                                                                                              |

| C5                                | OC_PG       | nIRQ                  | DO      | Output for Over Current Alarm and<br>Power Good signal, IRQ line towards<br>the host                          |

| A4                                | VDD_IO      |                       | PS      | I/O Voltage Rail                                                                                              |

| D4                                | VOUT_SENSE  |                       | AI      | Output and Sense node for the Buck                                                                            |

| C4                                | VSS_SENSE   |                       | AI      | Ground Sense node for the Buck                                                                                |

| F5                                | VDDCORE     |                       | AO      | Regulated supply for internal circuitry (decouple with 220 nF)                                                |

| B5                                | GPIO0       |                       | AI/DIO  | General purpose I/O                                                                                           |

| B4                                | Verror      | GPIO1                 | AIO/DIO | Error Amplifier Voltage Signal for<br>dual parallel mode, general purpose<br>I/O                              |

| E4                                | Iphase      | GPIO2                 | AIO/DIO | Current Distribution Signal for dual parallel mode, general purpose I/O                                       |

| E5                                | BUCK_CLK    | GPIO3                 | DIO     | Buck Clock Input/Output (depending<br>on slave/master function in dual<br>parallel mode), general purpose I/O |

| СЗ                                | AC_OK       | GPIO4                 | DIO     | Input from safe charger out to<br>OC_PG signaling, general purpose<br>I/O, input of external 6 MHz clock      |

| D3                                | nCS/SYNC    | GPIO5                 | DIO     | 4-WIRE chip select, DVC Interface input clock , general purpose I/O                                           |

| E3                                | SO/INPUT    | GPIO6                 | DIO     | 4-WIRE Data Output, DVC Interface input data, general purpose I/O                                             |

| B3                                | SI          | DATA                  | DIO     | 4-WIRE Data Input, 2-WIRE Data                                                                                |

| A3                                | SK          | CLK                   | DI      | 4-WIRE/2-WIRE Clock                                                                                           |

| D5                                | TP          |                       | DIO     | Test pin, connect to VSS                                                                                      |

| F3                                | VSYS        |                       | PS      | Supply for IC and input for voltage supervision                                                               |

| F4                                | VSS_QUIET   |                       | VSS     |                                                                                                               |

| C1, C2, D1, D2,<br>C6, C7, D6, D7 | VSS_NOISY   |                       | VSS     |                                                                                                               |

**Application Note**

Version 1.0

# 5.1.2 Package outline drawing

#### Figure 3: DA9210 42 VF-BGA package drawing

| - |    |    |     |     |   |    |    |

|---|----|----|-----|-----|---|----|----|

| Δ | nr | ۱i | cat | tin | n | No | te |

|   |    |    | u   |     |   |    |    |

#### 5.2 Multi-phase Buck converter

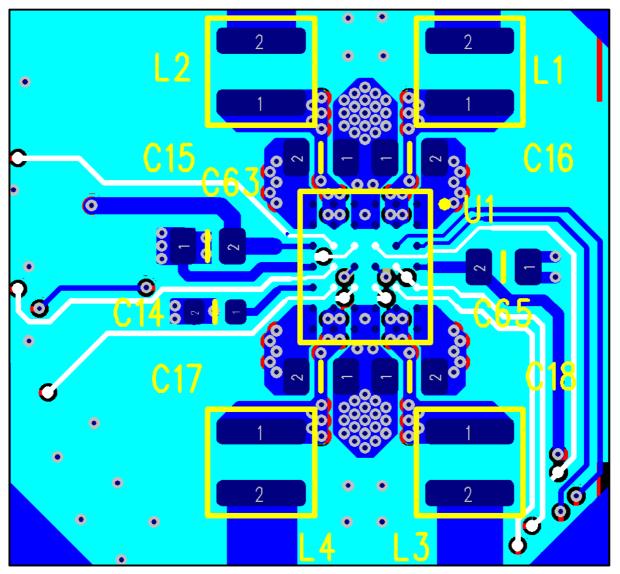

The DA9210 follows the standard Buck design procedure with output capacitors placed as close as possible to the load/processor and "remote voltage sensing". For this reason, and because of the high currents which the device can deliver, a wide output plane for minimized parasitic impedance is highly desirable.

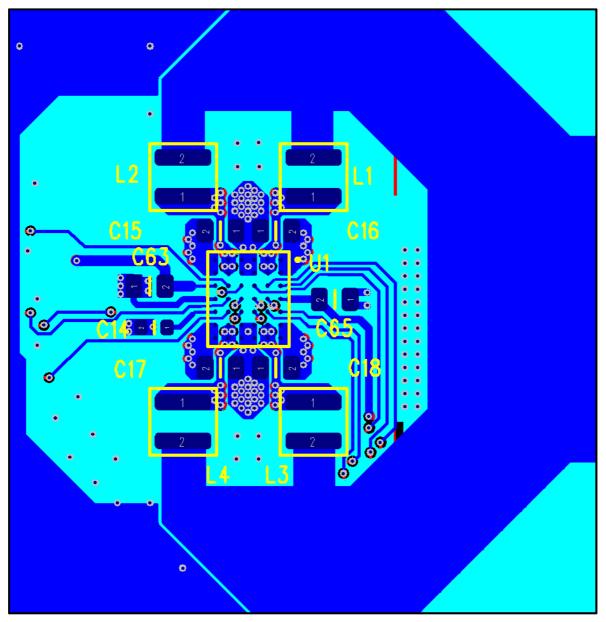

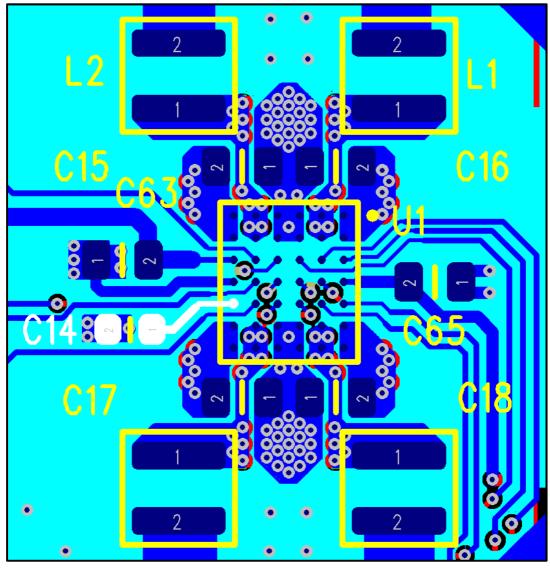

Differential feedback lines must be taken from the load point and routed back carefully to the DA9210 pins to precisely control the voltage at the load point. This is described in the next sections. As an example, a 4-layer PCB was designed using PTH via technique as shown in Figure 4.

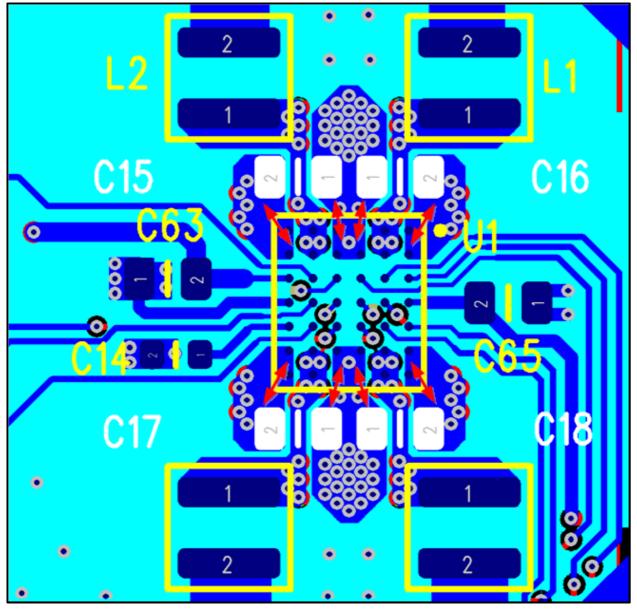

Figure 4: Example of components placement on 4-layer PCB

| -          |       |       |      |

|------------|-------|-------|------|

| An         | nlice | ation | Noto |

| <b>A</b> P | piica | ation | Note |

#### 5.2.1 Device grounding

Due to the high current levels and high performance requirements in DA9210, grounding of the device and ground patterns are fundamental aspects of the PCB layout.

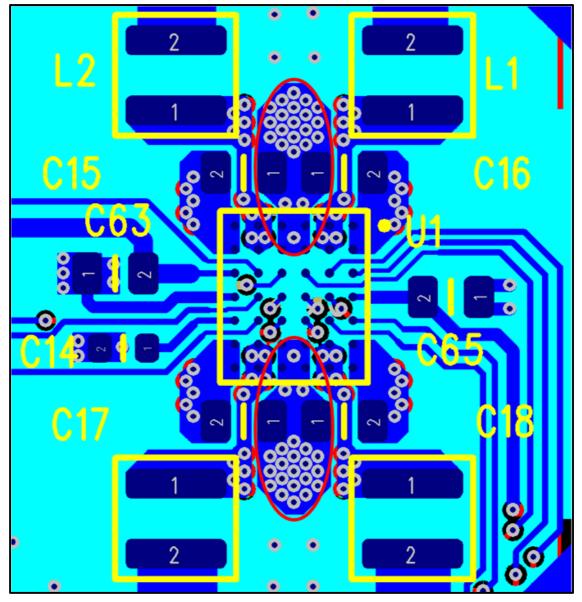

In the 42 VF-BGA, the ground terminals are placed at the periphery of the package and should be connected in the best and fastest possible way to the ground plane of the PCB. This is unlike the 48 WL-CSP package variant of DA9210, where the ground terminals are placed in the central area of the device.

It's also important that in the 42 VF-BGA, the ground signals of different phases do not include parasitic resistances and asymmetric paths.

This is achieved by placing the highest possible number of drilled PTH VIAs, as shown in Figure 5 (red circles). In this example, layer 2 of the PCB is used as ground plane. This is directly underneath the device and is probably the best choice in terms of device stability and noise reduction.

Figure 5: Device ground connection

| App            | lication | Note |  |

|----------------|----------|------|--|

| <b>* * P</b> F | noution  |      |  |

#### DA9210 PCB Layout Recommendation for 42 VF-BGA

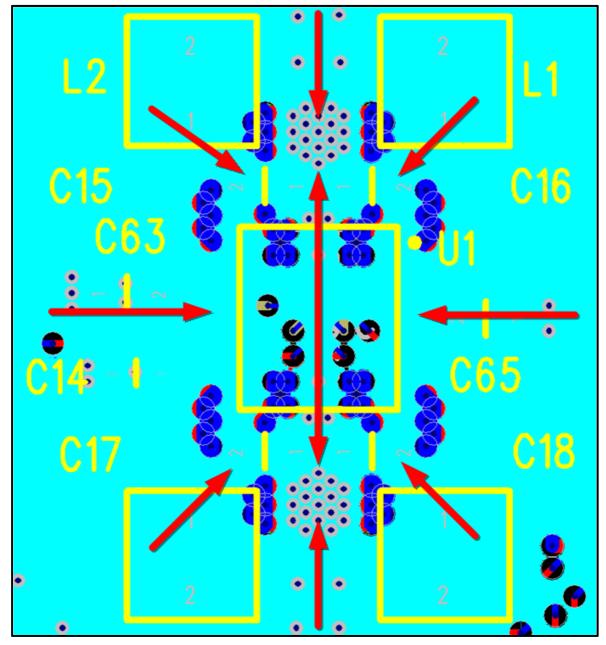

The PTH VIAs of signals other than ground must be placed carefully around the device to keep the ground copper gaps between the device ground VIAs and the internal ground planes large enough for a good, stable ground connection.

Figure 6 shows how this can be achieved.

Figure 6: Device ground connection

| Δn | nli | cati | on | N | ote |

|----|-----|------|----|---|-----|

| γγ | pii | cau  |    |   |     |

#### DA9210 PCB Layout Recommendation for 42 VF-BGA

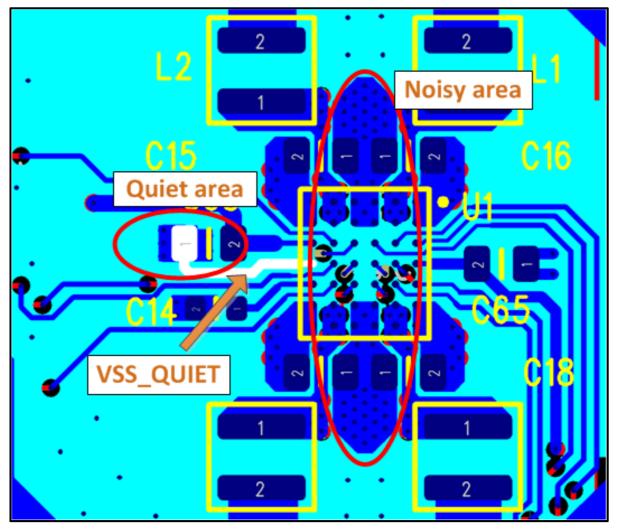

The ground pins of DA9210 are identified as VSS\_NOISY and VSS\_QUIET, where the "NOISY" pins are intended for use by the pass devices of different phases and the "QUIET" pin is connected to sensitive analogue circuits.

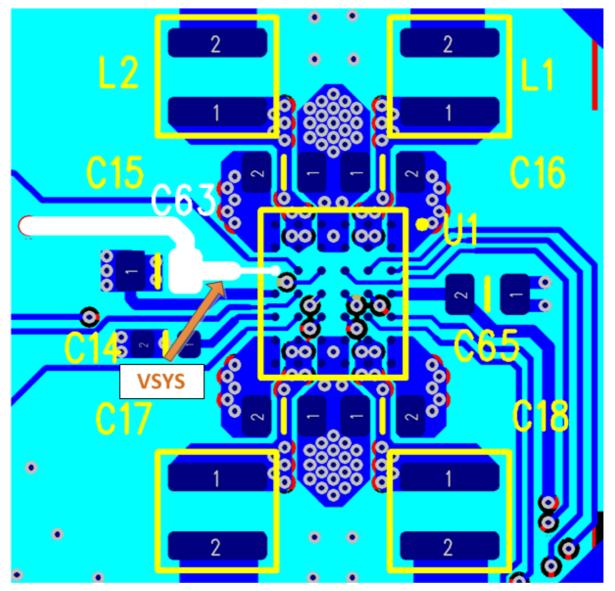

VSS\_QUIET should be connected to a quiet area of ground (GND terminal of C63) to achieve the best device performance and grant stability. Figure 7 shows how this is can be done in our example.

Figure 7: VSS\_QUIET connection

#### 5.2.2 Buck power supply input pins

As for the ground connection of the device, special attention is also required for the supply input pins.

At least four input capacitors are needed, each connected to VDD of the related phase input. Recommended capacitor values are 10 or 22  $\mu$ F, 6.3 V, 0603 footprint, X5R (C15, C16, C17 and C18 in Figure 8).

The input capacitors should be connected as close as possible to DA9210 and create an input filter directly on the top layer, as shown in Figure 8. The ground of the input capacitor can be easily shared with the VSS\_NOISY top layer area.

Note that as a good connection is required between the capacitor and the VDD plane, in our example a number of drilled PTH VIAs are placed close to the capacitor landing pad.

Figure 8: Input capacitors, placement and routing

| App         | olicatio | on Note |

|-------------|----------|---------|

| · · · · · · |          |         |

DA9210 has an additional input pin called VSYS, which is a quiet supply pin for the sensitive analogue circuits, and has a separate capacitor (C63 in Figure 9) with a recommended value of 1  $\mu$ F, 6.3 V, 0402 footprint, X5R or X7R.

This is basically the same net (power supply) as for the 4-phase Buck inputs, but a separate trace is routed from C63 to the VSYS pin and no merging with the Buck input lines or planes is allowed.

It is also recommended that the decoupling capacitor C65 (1  $\mu$ F, 6.3 V, 0402 footprint, X5R or X7R) is placed on the VDD\_IO line to suppress noise on this input.

Figure 9: Power supply capacitors

| Δn | nlic | eation | ו Not | •        |

|----|------|--------|-------|----------|

| rμ | piic | anor   | 11100 | <b>C</b> |

#### 5.2.3 Buck output

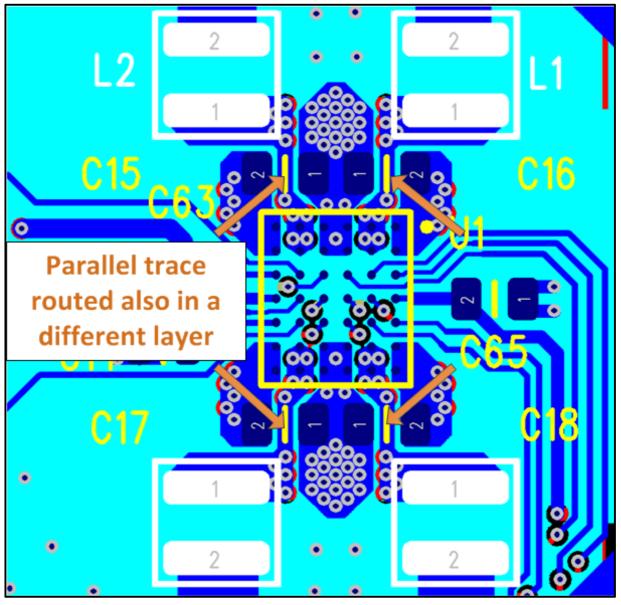

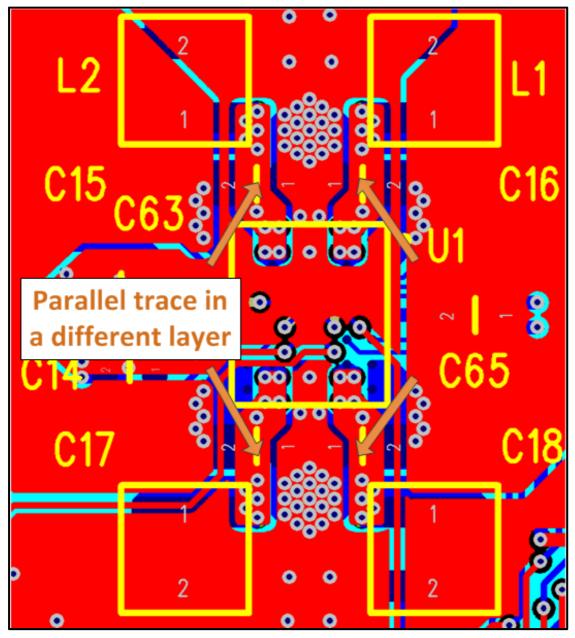

DA9210's output inductors should be placed as shown in Figure 10. Note that regarding EMI issues in system design, the traces or planes between the output LX pins and inductor terminals should be as short as possible to reduce the emission to the minimum.

Particular care must be taken when dimensioning the line width as the parasitic resistance must be reduced as much as possible - a maximum peak output current of more than 4 A can be experienced on the trace at maximum load. With the increase of parasitic trace resistances, the overall converter efficiency decreases accordingly.

Figure 10: Inductors, placement and routing

#### DA9210 PCB Layout Recommendation for 42 VF-BGA

Shielded inductors of 0.47  $\mu$ H and at least 3.5 or 4 A of saturation current are recommended. If the system design allows it, the best performance is achieved by transferring the output current directly on the top layer, without using any VIAs. However this is not possible when routing traces from chip LX nodes to output inductors because of the position of the input capacitors to reduce input impedance. A parallel trace on a different layer can be considered (as in the example in Figure 11) to minimize the resistance of the output track.

Figure 11 Parallel output trace

| Ap | pli | catio | on M | lol | te |

|----|-----|-------|------|-----|----|

| ,  |     | oun   |      |     |    |

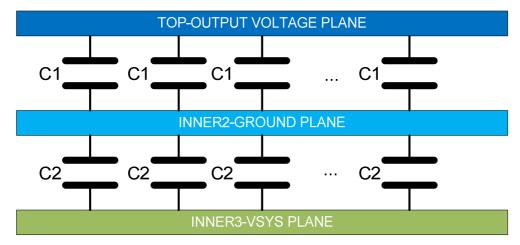

Care must be taken regarding the width of the traces or output plane, since the merged output peak current can be up to 12 A. The output plane should form another capacitor with the ground plane on layer 2, an example of how the overall system should look is shown in Figure 12.

Figure 12 Plane structure filtering

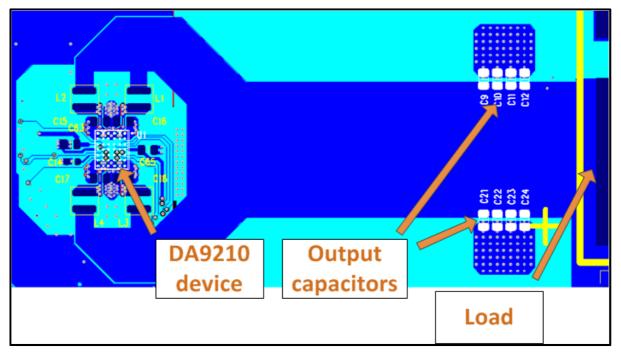

Output capacitors should be placed close to the load. The DA9210 is designed in such a way that it compensates the influence of the long distance between the inductors and output capacitors.

Figure 13 Output capacitors placement

For use as output capacitors,  $4 \times 47 \mu$ F,  $4 \vee$ , 0603 or  $4 \times 47 \mu$ F,  $4 \vee$ , 0805 footprint, X5R, or  $8 \times 22 \mu$ F, 6.3 V, 0603 footprint, X5R are recommended. System designers should decide which approach to use based on the total cost and the available space on the PCB.

#### 5.2.4 Feedback lines

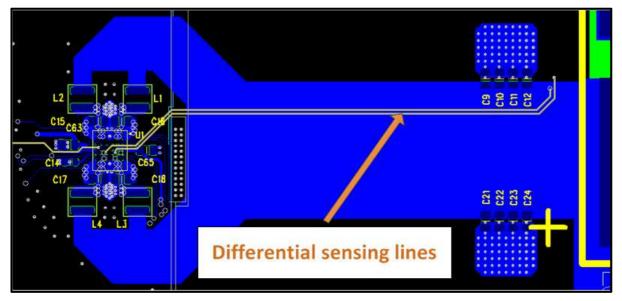

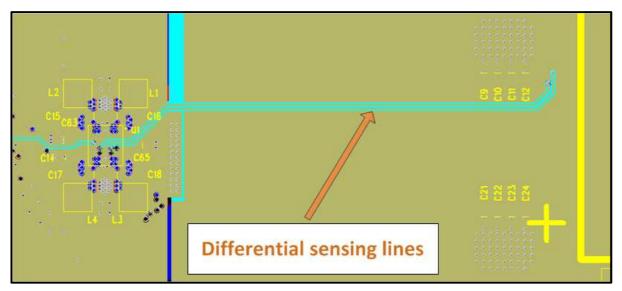

Special care has to be taken when placing the feedback lines. They must be routed far from any noise source (inductors, communication interfaces, and so on) and in a symmetric way.

The negative feedback line is at ground potential and care should be taken not to connect any part of the trace to the ground plane. The feedback lines must be routed from the load point in order to achieve the best voltage accuracy and stability at the load point. On a 4-layer PCB the recommended layer is layer 3 or layer 4 (bottom), but in general at least one insulation plane (ground or power layer) must be present between the top components and the feedback signals. Good feedback signal shielding is very important for Buck stability.

The number of used VIAs on the VOUT\_SENSE and VSS\_SENSE path should be minimised to avoid any potential noise coupling into feedback lines.

Figure 14 Feedback lines routing

#### Figure 15 Feedback lines shielding

| Application Note                 | Version 1.0 | 22-Sep-2014                  |

|----------------------------------|-------------|------------------------------|

| © 2014 Dialog Semiconductor GmbH | 17 of 21    | www.dialog-semiconductor.com |

#### DA9210 PCB Layout Recommendation for 42 VF-BGA

If it is not possible to avoid noise injection to feedback lines due to a layout limitation (for example, a long feedback pattern or noise from other device in a system), it is recommended to add a decoupling capacitor between the VOUT\_SENSE and VSS\_SENSE feedback lines close to the device. For example, capacitor 100 nF/402 can be used for filtering noise, but final selection is dependent on particular application and system.

#### 5.3 Reference voltage source

A 2.5 V precise reference voltage source (VDDCORE) is integrated in the DA9210 device. The only external component needed for proper operation is a 220 nF 0402 capacitor placed close to the device.

Reference traces must be free of noise and any longer parallel routing with noisy lines must be avoided.

Figure 16 Reference component placement and routing

|   |   |     |     | -   |   |    |   |

|---|---|-----|-----|-----|---|----|---|

| Δ | n | nli | cat | ion | N | ot | ρ |

|   | 2 |     | out |     |   |    |   |

Version 1.0

In general, designers should avoid VIAs in reference routing, since more noise can couple into the reference signal VDDCORE. When the reference capacitor is placed close to inductors (L1 to L4), we recommend that the inductors are shielded to avoid inductive coupling.

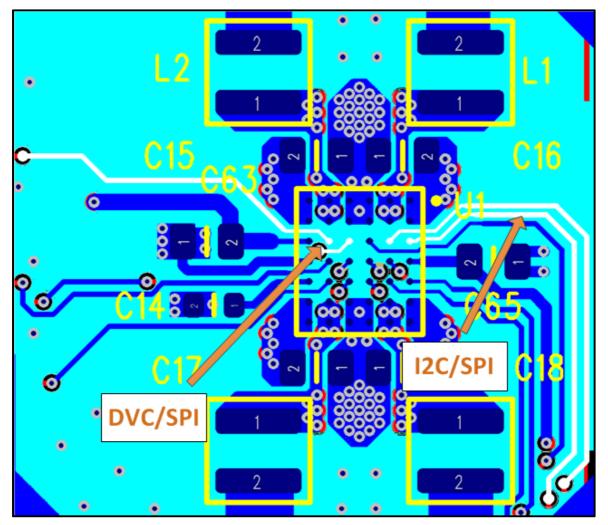

#### 5.4 Communication interfaces

There are no firm rules regarding the interface routing strategy. All related signals are digital and immune to various kinds of noise. Care must be taken regarding the noise produced by the interface signals; avoid coupling to sensitive analogue references and feedbacks. The layer is not critical, but on a 4-layer PCB it is recommended to use layer 4 or layer 1 if possible.

Figure 17 Interfaces lines

| Δr | n          | licati | on | NO | te |

|----|------------|--------|----|----|----|

|    | <b>7</b> P | loui   |    |    |    |

#### 5.5 GPIOs and control signals

Generally, GPIOs (GPIO0 to GPIO6), TP (test pin), EN\_CHIP pin and OC\_PG/nIRQ pin have the lowest routing priority. Any layer can be used for routing these signals.

In most designs and applications, pin TP should be tied to ground potential. If the device will be programmed "on-board", the routing of pin TP can be performed as shown in Figure 18.

The maximum voltage that can be applied to this pin is 7.8 V.

Figure 18 GPIO and control signals routing example

| - |    |         |     |     |

|---|----|---------|-----|-----|

| Δ | nn | licatio | n N | ote |

|   |    | nound   |     | olu |

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### Disclaimer

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, unless otherwise stated.

© Dialog Semiconductor GmbH. All rights reserved.

#### **RoHS Compliance**

Dialog Semiconductor complies to Directive 2002/95/EC of the European Parliament and of the Council of 27 January 2003 concerning Restriction of Hazardous Substances (RoHS). Dialog Semiconductor's statement on RoHS can be found on the customer portal https://support.diasemi.com/. RoHS certificates from our suppliers are available on request.

# **Contacting Dialog Semiconductor**

Germany Headquarters Dialog Semiconductor GmbH

Phone: +49 7021 805-0 United Kingdom

Dialog Semiconductor (UK) Ltd Phone: +44 1793 757700

#### The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 88 22

Email: enquiry@diasemi.com

#### **Application Note**

North America

Dialog Semiconductor Inc. Phone: +1 408 727 3200

Japan Dialog Semiconductor K. K. Phone: +81 3 5425 4567

Taiwan Dialog Semiconductor Taiwan Phone: +886 226 580 388

Web site: www.dialog-semiconductor.com

#### Singapore

Dialog Semiconductor Singapore Phone: +65 64845419

China Dialog Semiconductor China Phone: +852 2607 4271

Korea Dialog Semiconductor Korea Phone: +82 2 569 2301

#### 22-Sep-2014

© 2014 Dialog Semiconductor GmbH

21 of 21

www.dialog-semiconductor.com

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.