# Application note DA9053 2-Wire Implementation AN-PM-003

#### **Abstract**

This application note outlines a software workaround to prevent issues arising with initial I2C communication between a processor and the DA9053 2-wire interface. The workaround can be applied to any I2C slave device, and ensures that the device is in the correct idle state, ready to accept communications.

### **Contents**

| Αk | ostract                        | 1 |  |

|----|--------------------------------|---|--|

| Cc | ontents                        | 2 |  |

| 1  | Terms and definitions          | 3 |  |

| 2  | References                     | 3 |  |

| 3  | Introduction                   | 4 |  |

| 4  | NAK of the first I2C message   | 4 |  |

| 5  | SDA signal line is stuck low   | 5 |  |

|    | Workaround                     |   |  |

|    | 6.1 Code Example for the iMX53 | 5 |  |

| 7  | Further system recommendations | 8 |  |

| 8  | Conclusions                    |   |  |

| Re | evision history                | 9 |  |

#### 1 Terms and definitions

DA905x For this document this will be used to represent DA9021, DA9022, DA9052,

DA9053 and DA9057

#### 2 References

- [1] DA9053-00-IDS3a\_140114.pdf, Datasheet, Dialog Semiconductor

- [2] UM10204, I2C-bus specification and user manual, Rev .4 13 February 2012, NXP Semiconductors

#### 3 Introduction

The DA9053 I2C communication function does not receive a reset signal from an external device. During power up, the I2C function can enter an invalid state which can have one of two repercussions. The first is that the DA9053 might ignore the very first I2C message that was intended for it. The second is where the DA9053 might hold the SDA line low. Both of these can result in the I2C bus being seen as invalid or locked, preventing further communications. Both of these can be corrected in software by implementing the following workaround. This workaround is also referred to in the I2C specification.

# 4 NAK of the first I2C message

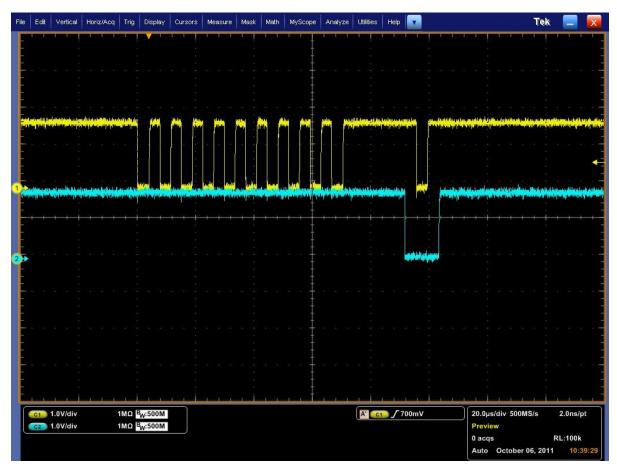

Figure 1 below shows an example of the DA9053 responding with a NAK to the first message. As seen in the oscilloscope plot, the SDA line is high for the last clock cycle. (Yellow trace = SCL and blue trace = SDA.)

This can only happen as the DA9053 starts. As the IO supply rail for the I2C pull-ups rises, the 2-wire interface logic can detect an invalid condition due to the timing of the two signals. This happens because the I2C module is already out of reset as this power rail comes up. Once in the invalid condition, it can miss the next valid START condition on the 2-wire interface and treat it as the first bit of the message. If the power rail for the I2C pull-ups is present before the DA9053 comes out of RESET then the first I2C access will be correctly handled.

The workaround suggested will prevent a NAK on the first communication. It is assumed that the software will correctly deal with any other status messages from the I2C communication.

Figure 1: Diagram Example

#### 5 SDA signal line is stuck low

This is the more serious situation whereby the invalid condition results in the DA9053 driving the SDA signal low. This will appear to the I2C host as though there is another master driving the bus and will lock the I2C bus.

This scenario can occur if the DA9053 shuts down during an I2C message whilst it is driving the bus low. If the DA9053 is shutdown in the middle of an I2C message but it is not driving SDA low, then upon the restart of the DA9053 it is possible that the first message will be answered with a NAK. This situation can arise because the I2C module in the DA9053 does not get reset: it therefore maintains its previous state and believes that it should still be driving the bus when it is switched back on. Therefore, once a shutdown command has been sent to the DA9053, no further traffic on the I2C bus should be allowed.

#### 6 Workaround

Both of the aforementioned issues can be prevented by applying a one-time software workaround before any I2C communication is attempted. The workaround is most usually placed in the boot loader.

As previously mentioned, the fix is to implement the same workaround that is described in the I2C specification. The procedure is:

- 1. Configure the I2C port pins to be GPIOs, preferably open-drain but push-pull is also acceptable.

- 2. Set the SCL line low then high nine times with at least 3 μs between changes, for example: udelay(3)

- 3. Set SDA line low. Wait at least 3 µs

- 4. Set SCL line low. Wait at least 3 µs

- 5. Set SCL line high. Wait at least 3 μs

- 6. Set SDA line high. Wait at least 3 µs

- 7. Configure the pins to be under control of I2C controller.

Note that this procedure must be made when the signal lines are being operated as GPIOs since the state of the lines may preclude use of I2C primitive controls: for example, sending START would not work if SDA were already low.

The above procedure can be seen in Figure 2 below.

#### 6.1 Code Example for the iMX53

```

reg = readl(GPIO5 BASE ADDR + 0x0);

reg &= \sim (1 << 26 \mid 1 << 27);

writel(reg, GPIO5_BASE_ADDR + 0x0);

reg = readl(GPIO5_BASE\_ADDR + 0x4);

reg &= \sim (1 << 26 \mid 1 << 27);

writel(i, GPIO5 BASE ADDR + 0x4);

udelay(200);

for (i = 10; i; i--) {

reg |= 1<<27;

writel(reg, GPIO5 BASE ADDR + 0x4);

udelay(11);

reg &= \sim (1 << 27);

writel(reg, GPIO5 BASE ADDR + 0x4);

udelay(14);

}

udelay(80);

reg |= 1<<26;

writel(reg, GPIO5_BASE_ADDR + 0x4);

udelay(11);

reg |= 1 << 27;

writel(reg, GPIO5_BASE_ADDR + 0x4);

udelay(11);

reg &= \sim (1 << 27);

writel(reg, GPIO5 BASE ADDR + 0x4);

udelay(14);

reg &= \sim (1 << 26);

writel(reg, GPIO5_BASE_ADDR + 0x4);

}

```

Figure 2: Fix for clearing the 2-wire SDA interface

The above implementation must be done before any attempt is made to communicate on the I2C bus

Note that this procedure is very similar to that defined in the UM10204 section 3.1.16 of the I2C-bus specification and user manual from NXP Semiconductors.

Also note that this procedure can be safely applied to any I2C slave device and will result in that device being placed in the idle state.

#### 7 Further system recommendations

The DA9053 contains two I2C interfaces and a 4-wire interface. In applications where the communication with the PMIC is critical to the system performance, it is recommended to use the 4-wire interface where possible. An example is a system that will use frequent DVC to continually optimise the power/performance of the processor. The 4-wire interface is faster, is more robust due to its use of an enable signal to indicate when the bus is active, and has a guaranteed lower latency as it is point-to-point and so can never suffer from bus contention.

In cases where it is not possible to use the 4-wire interface, Dialog recommends the use of the HS-2-Wire interface rather than the standard Power Manager Interface since the HS interface can be slightly more tolerant of noise on the I2C lines.

To improve the robustness of the I2C during power up/down operations, it is recommended to utilise the PD\_DIS (Power Down Disable) functionality in the DA9053 sequencer. By setting the PD\_DIS step to be early in the power down sequence, and by setting the HS-2-WIRE\_PD and PM-IF\_PD bits in the PD\_DIS register, the I2C interfaces can be disabled before any of the IO supplies are powered down, thus helping to protect against spurius edges being detected during the power down and subsequent power up procedures.

#### 8 Conclusion

A procedure has been proposed which has proven to remove the two most common causes of DA9053 2-wire interface communication issues. Both of these issues can be worked around with the software procedure outlined above. The procedure is similar to that recommended in the I2C specification.

# **Revision history**

| Revision | Date        | Description               |

|----------|-------------|---------------------------|

| 1.0      | 01-Mar-2012 | Initial version.          |

| 1.1      | 03-Jun-2015 | Update to latest template |

#### Status definitions

| Status               | Definition                                                                                                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, unless otherwise stated.

© Dialog Semiconductor. All rights reserved.

#### **RoHS Compliance**

Dialog Semiconductor complies to European Directive 2001/95/EC and from 2 January 2013 onwards to European Directive 2011/65/EU concerning Restriction of Hazardous Substances (RoHS/RoHS2).

Dialog Semiconductor's statement on RoHS can be found on the customer portal <a href="https://support.diasemi.com/">https://support.diasemi.com/</a>. RoHS certificates from our suppliers are available on request.

# **Contacting Dialog Semiconductor**

United Kingdom (Headquarters)

Dialog Semiconductor (UK) LTD Dialog Semiconductor Inc.

Phone: +44 1793 757700 Phone: +1 408 845 8500

Germany Japan

Dialog Semiconductor GmbH Dialog Semiconductor K. K. Phone: +49 7021 805-0 Phone: +81 3 5425 4567

The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822

Email:

enquiry@diasemi.com

North America Singapore

Dialog Semiconductor Inc. Dialog Semiconductor Singapore

Phone: +1 408 845 8500 Phone: +65 64 8499 29

Hong Kong

Dialog Semiconductor K. K. Dialog Semiconductor Hong Kong

Phone: +81 3 5425 4567 Phone: +852 3769 5200

Phone: +82 2 3469 8200

Taiwan Korea

Dialog Semiconductor Taiwan Dialog Semiconductor Korea

Web site: www.dialog-semiconductor.com

Phone: +886 281 786 222

China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai)

Dialog Semiconductor China Phone: +86 21 5424 9058

© 2015 Dialog Semiconductor

Application note Revision 1.1 03-Jun-2015

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.