# RENESAS

# VersaClock<sup>®</sup> 7 (VC7) Internal Capacitance Configuration

This document describes how the internal capacitance is configured within a VersaClock<sup>®</sup> 7 (VC7) device using the Renesas IC Toolbox software (RICBox). For more information about RICBox, download the *Renesas IC Toolbox Software Manual* from the <u>Renesas IC Toolbox (RICBox)</u> page.

# Contents

| 1. | Calculating Load Capacitance |                              |   |

|----|------------------------------|------------------------------|---|

| 2. | Bend                         | ch Setup for Trimming        | 3 |

|    | 2.1                          | Evaluation Board (EVB) Setup | 3 |

|    | 2.2                          | Frequency Counter Setup      | 3 |

|    | 2.3                          | RICBox Installation          | 3 |

|    | 2.4                          | Trimming the Crystal         | 3 |

| 3. | Revi                         | sion History                 | 6 |

## 1. Calculating Load Capacitance

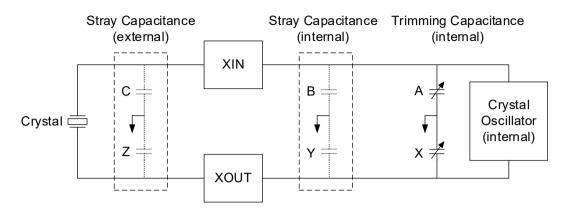

The load capacitance (CL) on the crystal can be modeled as follows:

The external stray capacitance (denoted by C and Z) is made up of the parasitic capacitance from the PCB trace and any installed load capacitors. The internal stray capacitance (denoted by B and Y) consists of the package pins and bond wires. For VC7, this value is fixed at 8.2pF. The trimming capacitance (denoted by A and X) can be set by **en\_cap\_x1** and **en\_cap\_x2** register fields. The range is 0pF to 26.46pF in 0.42pF steps.

To calculate the load capacitance, note that the external stray, internal stray, and trimming capacitance are in parallel per leg. Next, the effective capacitance on XIN and XOUT are in series. Therefore, the load capacitance can be approximated with:

$$\frac{1}{C_L} = \frac{1}{A+B+C} + \frac{1}{X+Y+Z}$$

If each respective capacitance is allowed to be equal, or A = X, B = Y, and C = Z then:

$$\frac{1}{C_L} = \frac{2}{A+B+C}$$

Solving for A:

$C_L = \frac{A + B + C}{2}$  $2C_L = A + B + C$  $A = 2C_L - B - C$

Knowing the goal  $C_L$  capacitance of the crystal, the expected trimming (A and X) capacitance can be calculated. The internal stray (B and Y) capacitance are fixed at 8.2pF. The external stray (C and Z) capacitance can be set in RICBox. The name of the fields are **xin\_pcb\_capacitance** and **xout\_pcb\_capacitance**. For the RC21012 EVB, the PCB trace capacitance is about 2.5pF and for the RC21008 EVB, the PCB trace capacitance is about 1.7pF. After these fields are set, the trim value is calculated (as shown below) and the nearest trim setting is chosen by the VC7 plugin.

$$Trim = int\left(\frac{2C_L - 8.2pF - 2.5pF}{0.42pF}\right)$$

# 2. Bench Setup for Trimming

Use the RC21008A/RC31008A Evaluation Kit (EVK) and Frequency Counter equipment for the trimming measurement. The RC21012A/RC31012A EVK may be used as well.

### 2.1 Evaluation Board (EVB) Setup

The RC21008 EVB ships with a 50MHz crystal installed. The C<sub>L</sub> required for this crystal is 8pF. Ensure that the **XIN\_DIF\_INA\_S** and **DIF\_INA#\_S** traces are not connected to a VC7 device via R11 and R19. Also, ensure C5 and C6 are not populated. Any extra stubs will add stray capacitance to XIN/XOUT. For more information, refer to the schematics in the RC210xxA/RC310xxA Evaluation Board Manual.

### 2.2 Frequency Counter Setup

Setup the counter to accept 50MHz. If the VC7 EVB has AC-coupled outputs, adjust the counter to enable  $50\Omega$  termination.

### 2.3 **RICBox Installation**

For more information on installing RICBox software for VC7, see the Renesas IC Toolbox Software Manual.

### 2.4 Trimming the Crystal

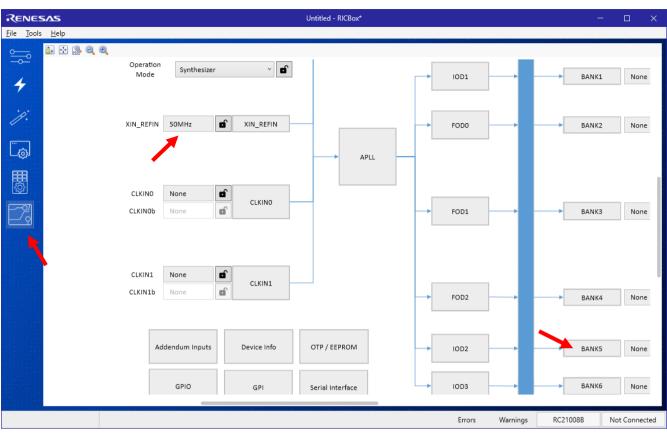

Use OUT10 to measure the crystal signal as it can be muxed out. Start RICBox and create a new project. Choose the product variant that matches the unit on the EVB. During the wizard phase, just click Finish. Next, view the block diagram. If your crystal is different from the default value, then update the XIN\_REFIN frequency (see Figure 1).

Figure 1. Block Diagram Window

From the window above, click on **Bank5** to bring up the BANK5 sub-diagram window (see Figure 2). For the frequency source, choose **XIN\_REFIN**. Set the *Desired Output Frequency* field to match the crystal frequency.

| RENESAS                  |               | BANKS                                     | - | × |

|--------------------------|---------------|-------------------------------------------|---|---|

| 🗈 💀 🍭 🍭                  |               |                                           |   |   |

| Output                   | Bank          | Output >50MHz [LPHCSL (100ohm)]           |   |   |

| Frequency Source         | XIN_REFIN 🗸 🔒 | Advanced LPHCSL (100ohm) V of OUT10 OUT10 |   |   |

| Desired Output Frequency | 50            | Disabled                                  |   |   |

| Power Down               |               | Disable Group Group0 v Group0 V           |   |   |

|                          |               |                                           |   |   |

| Is Floating              |               |                                           |   |   |

| VDD05                    | 3.3V × 🖬      |                                           |   |   |

|                          |               |                                           |   |   |

|                          |               |                                           |   |   |

Figure 2. BANK5 Sub-Diagram Window

Connect and program VC7. Use the frequency counter to measure the crystal frequency. Go back to the main block diagram and click on the **XIN\_REFIN** block to bring up its configuration window (see Figure 3). Adjust the *Load Capacitance (pf)* until the measured frequency by the counter is closest to your expected crystal frequency. Use increments of 0.1 (pF) for best results. After changing the load capacitance value, the changes are effective immediately.

|                       | N_REFIN | —          | × |

|-----------------------|---------|------------|---|

| 🗈 🕂 🔒 🔍 🔍             |         |            |   |

| Inp                   | ut Pad  |            |   |

| Mode                  | Xtal    | ~ <b>d</b> |   |

| Frequency             | 50MHz   | đ          |   |

| Load Capacitance (pF) | 8.1     | Ô          | 1 |

| PCB Stray XIN (pF)    | 1.7     | 6          |   |

| PCB Stray XOUT (pF)   | 1.7     | 6          |   |

|                       |         |            |   |

| Clock Monitor         | Div     | /ider      |   |

| XIN/REFIN             | Hd      | iv XO      |   |

|                       |         |            |   |

Figure 3. XIN\_REFIN Configuration Window

You can also use the RICBox CLI (Command Line Interface). To read/write the **XO\_CNFG** register use:

### read TOP.XO.XO\_CNFG

### write TOP.XO.XO\_CNFG 0x205D1D45

| RENESAS                                                                                                                                                                                     |                                                                                 | RICBox CLI                                                                                                                                                                                                                                                | — | × |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|

| > read TOP.XO.XO_CNF<br>TOP.XO.XO_CNFG = 0x2<br>BitSet                                                                                                                                      |                                                                                 | Value                                                                                                                                                                                                                                                     |   |   |

| xo_ib_h_div_setb<br>xo_ib_h_div<br>en_gain<br>en_cap_x2                                                                                                                                     | 0x2C[29]<br>0x2C[28:24]<br>0x2C[23:22]<br>0x2C[21:16]                           | 0x1<br>0x00<br>0x1 (1 Amplifier)<br>0x28 (16.80pF)                                                                                                                                                                                                        |   |   |

| xo_buff_dis<br>en_cap_x1<br>xo_res                                                                                                                                                          | 0x2C[14]<br>0x2C[13:8]<br>0x2C[6:4]                                             | 0x0 (XO buffer enable is controlled by the hardware)<br>0x28 (16.80pF)<br>0x4                                                                                                                                                                             |   |   |

| <pre>xo_ib_en_dc_bias<br/>sel_ib_xo<br/>xo_ib_cmos_sel<br/>xo_ib_p_n_diff_sel<br/>&gt; write TOP.XO.XO_CN<br/>Wrote 4 byte(s) to 0</pre>                                                    | FG 0x205D1D45<br>ffset 0x2C                                                     | 0x0 (Disable internal DC bias)<br>0x1 (XO)<br>0x0 (Differential input is selected)<br>0x1 (Enable NMOS input pair)                                                                                                                                        |   |   |

| <pre>&gt; read TOP.XO.XO_CNF<br/>TOP.XO.XO_CNFG = 0x2<br/>BitSet</pre>                                                                                                                      |                                                                                 | Value                                                                                                                                                                                                                                                     |   |   |

| <pre>xo_ib_h_div_setb<br/>xo_ib_h_div<br/>en_gain<br/>en_cap_x2<br/>xo_buff_dis<br/>en_cap_x1<br/>xo_res<br/>xo_ib_en_dc_bias<br/>sel_ib_xo<br/>xo_ib_cmos_sel<br/>xo_ib_p_n_diff_sel</pre> | 0x2C[14]<br>0x2C[13:8]<br>0x2C[6:4]<br>0x2C[3]<br>0x2C[2]<br>0x2C[2]<br>0x2C[1] | 0x1<br>0x00<br>0x1 (1 Amplifier)<br>0x1D (12.18pF)<br>0x0 (XO buffer enable is controlled by the hardware)<br>0x1D (12.18pF)<br>0x4<br>0x0 (Disable internal DC bias)<br>0x1 (XO)<br>0x0 (Differential input is selected)<br>0x1 (Enable NMOS input pair) |   |   |

|                                                                                                                                                                                             |                                                                                 |                                                                                                                                                                                                                                                           |   |   |

Figure 4. RICBox CLI Window

Close the **XIN\_REFIN** configuration window and go back to the BANK5 sub-diagram window (see below). Click on the blue lock icons to reset the fields back to the GUI defaults.

| RENESAS | s                     |          | BANKS                                                | — | × |

|---------|-----------------------|----------|------------------------------------------------------|---|---|

| 🎒 🕂 🕵 🍭 | e,                    |          |                                                      |   |   |

|         | Output                | Bank     | Output                                               |   |   |

|         | Frequency Source      | FOD1 -   | Advanced powered down V                              |   |   |

| Desi    | ired Output Frequency | None 🖬   | Disabled                                             |   |   |

|         | Power Down            |          | Disable Group group0 v of OUT10b Diverse down (ni-2) |   |   |

|         |                       |          |                                                      |   |   |

|         |                       |          |                                                      |   |   |

|         | VDD05                 | 3.3V ~ 🕤 |                                                      |   |   |

|         |                       |          |                                                      |   |   |

|         |                       |          |                                                      |   |   |

The onboard crystal is now trimmed.

# 3. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.00     | May 31, 2024 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.