# **ZSC31050 Application Note - Two-Wire Current-Loop Output**

## **Contents**

| Introdu                           | ction                                                                                                                                                                                             | 2                                                                                                                                                                                            |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The ZS                            | SC31050 with 4-to-20mA Current Loop Output                                                                                                                                                        | 2                                                                                                                                                                                            |

| Setup a                           | and Evaluation of Current Loop Configuration                                                                                                                                                      | 4                                                                                                                                                                                            |

| 3.1. Se                           | tup for Two-Wire Current Loop Evaluation Using the ZSC31050 SSC Evaluation Kit                                                                                                                    | 4                                                                                                                                                                                            |

| Calibra                           | tion of the Current Loop                                                                                                                                                                          | 6                                                                                                                                                                                            |

| Comm                              | unication via Current Loop for Calibration                                                                                                                                                        | 13                                                                                                                                                                                           |

| Test of                           | Communication via Current Loop                                                                                                                                                                    | 15                                                                                                                                                                                           |

| Schem                             | atics for Three-Wire Current-Loop Applications                                                                                                                                                    | 16                                                                                                                                                                                           |

| Related                           | d Documents                                                                                                                                                                                       | 17                                                                                                                                                                                           |

| Glossa                            | ry                                                                                                                                                                                                | 17                                                                                                                                                                                           |

| Docum                             | ent Revision History                                                                                                                                                                              | 18                                                                                                                                                                                           |

|                                   |                                                                                                                                                                                                   |                                                                                                                                                                                              |

| st of F                           | igures                                                                                                                                                                                            |                                                                                                                                                                                              |

| ure 2.1                           | Schematic of the ZSC31050's Current Loop Output Stage with Communication via I <sup>2</sup> C™ Interf                                                                                             | ace2                                                                                                                                                                                         |

| ure 3.1                           | Schematic of I <sup>2</sup> C <sup>™</sup> Communication with a Current Loop Output Module                                                                                                        | 4                                                                                                                                                                                            |

| ure 3.2                           | Evaluation of a Current Loop Output Module using the ZSC31050 Evaluation Board V3.0                                                                                                               | 5                                                                                                                                                                                            |

| ure 4.1                           | 4mA to 20mA Interface Fine Tuning                                                                                                                                                                 | 6                                                                                                                                                                                            |

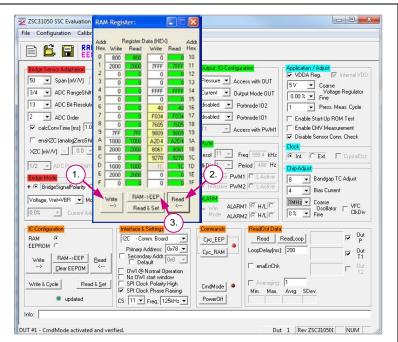

| ure 4.2                           | Step 1: Configuration and Pre-Adjustment of Current-Loop Output Mode                                                                                                                              | 8                                                                                                                                                                                            |

| ure 4.3                           | Step 2: Transfer the Pre-Adjustments to the RAM and EEPROM                                                                                                                                        | 9                                                                                                                                                                                            |

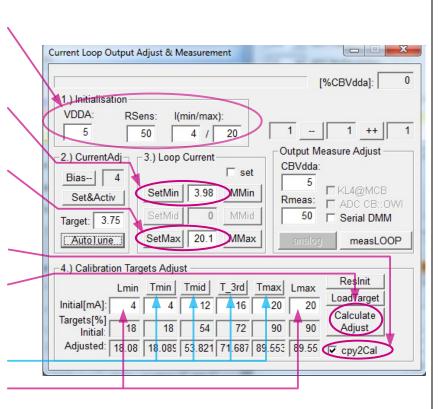

| ure 4.4                           | Step 3a: Adjustment of the External Current-Loop Circuitry                                                                                                                                        | 10                                                                                                                                                                                           |

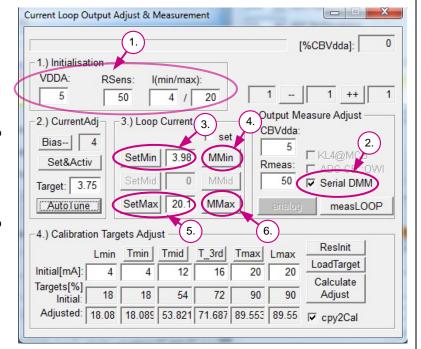

| ure 4.5                           | Step 3b: Adjustment of the External Current-Loop Circuitry with External DMM Readout                                                                                                              | 11                                                                                                                                                                                           |

|                                   |                                                                                                                                                                                                   | 12                                                                                                                                                                                           |

| ure 5.1                           | Schematic of the ZSC31050's Current Loop Output Stage with Communication via ZACwire™                                                                                                             | 13                                                                                                                                                                                           |

|                                   |                                                                                                                                                                                                   |                                                                                                                                                                                              |

| ·                                 |                                                                                                                                                                                                   | 15                                                                                                                                                                                           |

| Figure 7.1 Load Referenced to GND |                                                                                                                                                                                                   |                                                                                                                                                                                              |

| ure 7.2                           | Load Referenced to Positive Supply V <sub>S</sub>                                                                                                                                                 | 16                                                                                                                                                                                           |

| st of T                           | Tables                                                                                                                                                                                            |                                                                                                                                                                                              |

| ole 3.1                           | Settings on the Board Needed to Enable the Output Mode                                                                                                                                            | 4                                                                                                                                                                                            |

| ole 5.1                           | Signal Coding                                                                                                                                                                                     | 13                                                                                                                                                                                           |

|                                   | The ZS Setup a 3.1. Se Calibra Commit Test of Schem Related Glossa Docum  st of F ure 2.1 ure 3.1 ure 3.2 ure 4.1 ure 4.2 ure 4.3 ure 4.4 ure 4.5 ure 4.6 ure 5.1 ure 5.2 ure 6.1 ure 7.1 ure 7.2 | The ZSC31050 with 4-to-20mA Current Loop Output.  Setup and Evaluation of Current Loop Configuration.  3.1. Setup for Two-Wire Current Loop Evaluation Using the ZSC31050 SSC Evaluation Kit |

#### 1 Introduction

This application note covers the principles of a two-wire current-loop output for the ZSC31050 sensor signal conditioner IC and provides examples of output circuits and information about the calibration procedure. The analog current loop is a typical output signal configuration, especially for industrial sensors. Using only two wires, the sensor is supplied with power *and* transmits its output signal to the processing unit. This saves cost, offers a very robust signal transmission in terms of EMI, and provides a connection check of the sensor module via the "life zero" behavior of the output signal's range of 4 to 20 mA.

When the ZSC31050 is used in current-loop mode, a buffer is used in the output signal path, which is not offset-compensated. Tolerances of the required external elements cause additional errors, especially for the  $50\Omega$  current sense resistor (see Figure 2.1). An "over-all" calibration can remove such errors.

## 2 The ZSC31050 with 4-to-20mA Current Loop Output

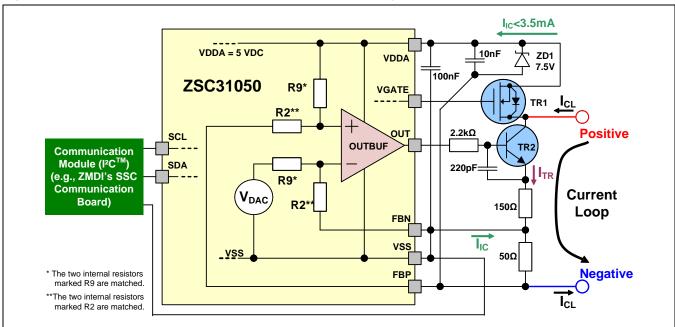

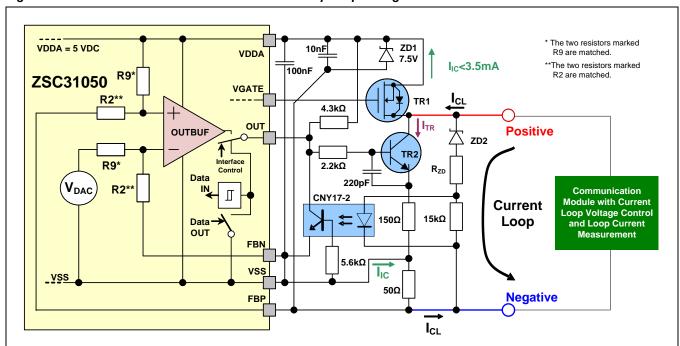

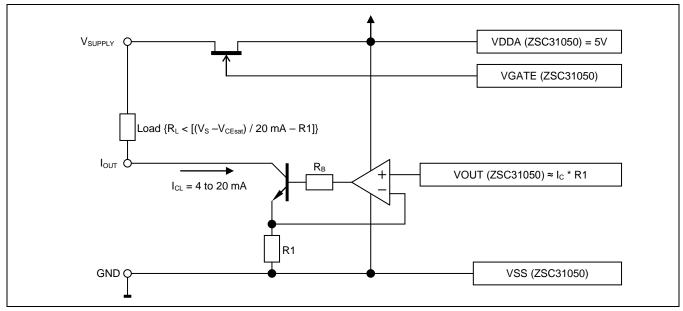

The ZSC31050's analog output stage is configurable for controlling a current-loop output signal via EEPROM settings. As a result, fewer external parts are needed and the parts are less expensive. See Figure 2.1 for an illustration of the functionality of this configuration:

Figure 2.1 Schematic of the ZSC31050's Current Loop Output Stage with Communication via I<sup>2</sup>C™ Interface

The  $2.2k\Omega$  resistor and the 220pF capacitor are not needed for the main functionality but are useful for protecting the ZSC31050's analog output OUT from over-voltage (e.g., due to ESD) and for suppressing noise. The Zener diode ZD1 (7.5V) protects the VDDA line from positive over-voltage and protects the FBP input of the ZSC31050 from negative over-voltage (e.g., caused by the response time of the internal VDDA regulator after power-on). Recommended types for TR1 include the BSS169 or DN3545; for TR2, the BCX56-10 can be used.

The communication module's power supply must be isolated from the current loop for proper operation via the  $I^2C^{TM*}$  interface.

The ZSC31050's 11-bit digital-to-analog converter (DAC) is controlled by an internal calibration microcontroller (CMC) using the *normalized and inverted* value  $(1 - P_{11}/2^{11})$  of the digital 11-bit value  $P_{11}$ , which represents the 11 MSBs of the digital 15-bit output signal P. Therefore, its analog output voltage  $V_{DAC}$  can be calculated with equation (1).

$$V_{DAC} = VDDA * \left(1 - \frac{P_{11}}{2^{11}}\right)$$

(1)

Based on this equation and on the fact that all voltages are referenced to VSS, the loop current  $I_{CL}$  can be calculated with equation (2).

$$I_{CL} = \frac{P_{11}}{2^{11}} * \left( \frac{VDDA}{9/2 * 50\Omega} \right)$$

(2)

To ensure that  $I_{\rm IC}$  < 3.5 mA (includes supply current of the transducer to be conditioned) within the operational temperature range, the ZSC31050's bias current level is adjusted during final test to the optimal value for proper operation of the analog front-end before delivery. Therefore the individual default values stored in bits 4 to 6 of EEPROM register  $C1_{\rm HEX}/28_{\rm DEC}$  must be left unchanged to ensure operation in current loop mode within specifications. For more details, refer to the ZSC31050 Techical Note – EEPROM Changes Bias Adjustment (see section 8). Adjusting the clock to a frequency of <1.2MHz is recommended to minimize the current consumption of the ZSC31050's digital section to the required level in current-loop output mode.

<sup>\*</sup> I<sup>2</sup>C™ is a trademark of NXP

## 3 Setup and Evaluation of Current Loop Configuration

The ZSC31050 current loop application can be verified with IDT's ZSC31050 SSC Evaluation Kit, user-provided customized hardware, or a combination. The user's customized ZSC31050-based sensor module can be connected directly to the kit's SSC Communication Board (SSC CB) to connect to the user's computer running the ZSC31050 Evaluation Software or user software. Alternately, the current loop configuration can be evaluated by mounting the ZSC31050 on the kit's SSC Evaluation Board (SSC EB) and communicating via the SSC CB.

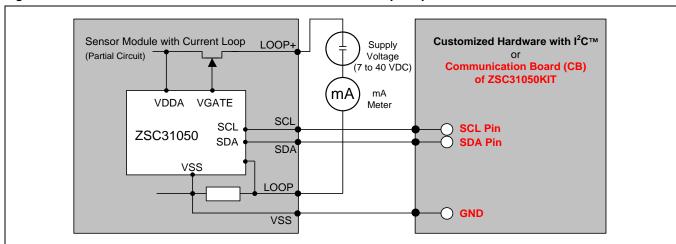

The required additional user-customized hardware can be connected to the SSC EB or the SSC CB via the interface and GND pins on the boards (see the example in Figure 3.1).

Figure 3.1 Schematic of f C™ Communication with a Current Loop Output Module

#### 3.1. Setup for Two-Wire Current Loop Evaluation Using the ZSC31050 SSC Evaluation Kit

When using the ZSC31050 Evaluation Kit, an evaluation of the current loop configuration is supported by the kit's hardware directly. Only an external current loop supply and a mA-meter are needed to setup a current loop application. Refer to Table 3.1 and Figure 3.2 for the correct setup of the jumpers and switches on the ZSC31050 SSC Evaluation Board V3.0. Table 3.1 gives an overview of the settings on the ZSC31050 SSC Evaluation Board needed to enable the output mode to be evaluated. For this application, use the "2-Wire Current Loop" settings.

| Tuble 5.7 Settings on the Board Needed to Enable the Sulput mode |              |          |                 |          |         |                        |              |             |  |

|------------------------------------------------------------------|--------------|----------|-----------------|----------|---------|------------------------|--------------|-------------|--|

| ZSC31050 Output Mode                                             | Power Supply |          | Jumper Settings |          |         |                        | Slide Switch |             |  |

| 23C31030 Output Mode                                             | CB-KS5V      | CB-KS12V | ext.            | K12      | K15     | K17                    | K19          | S1 Position |  |

| 2-Wire Current Loop (4 to 20 mA)                                 |              |          | Via KL3         | 12P-VDDA | OUT-5V  | Open                   | Shorted      | Current     |  |

| Ratiometric                                                      | Via K1       |          |                 | 5P-VDDA  | OUT-5V  | Open                   | Open         | Voltage     |  |

| Non-ratiometric (0-5)V                                           |              | Via K1   | Via KL3         | 12P-VDDA | OUT-5V  | Shorted if<br>CB-KS12V | . Open       | Voltage     |  |

| , ,                                                              |              |          |                 |          |         | Open if ext.           |              |             |  |

| Non-ratiometric (0-10)V                                          |              | Via K1   | Via KL3         | 12P-VDDA | OUT-10V | Shorted if<br>CB-KS12V | Shorted      | Voltage     |  |

| ,                                                                |              |          |                 |          |         | Open if ext.           |              |             |  |

Table 3.1 Settings on the Board Needed to Enable the Output Mode

VDDA|VDDA|VDDA|VDDA|VDDA|VDDA|VDDA KL3 screw terminal VINP VBR VINN VSS IRT FBP OUT FBN Connect external VINP VBR FBN VINN VSS IRT FBP OUT power supply for the VSS VSS VSS VSS VSS VSS VSS VSS current loop KL1/KL2 screw terminal for connecting external bridge Jumper K12 - "VDDA" Set to 12P <u>Jumper K11 – "Bridge Mode"</u> Voltage supplied Current supplied Jumper K17 - "V+ ext" Leave open Jumper K19 – "OUT" Short Pin 1 of ZSC31050 K1 connector to SSC CB Slide Switch S1 Slide Switch S2 Current output mode Communication via I<sup>2</sup>C™ □ Communication via SPI == Resistors for board ZMDI SSC Board ZSC31050 V3.0 LED for IO1 and IO2 identification VSS VSS VSS VSS VSS VSS VSS VSS Jumper K15 VDDA IN3  $V_{\mathsf{GATE}}$ 101 102 SCL SDA VDD Set to 5V IN3 IO1 102 SCL SDA VDD VDDA|  $V_{\mathsf{GATE}}$ VDDA VDDA VDDA VDDA VDDA VDDA VDDA

Figure 3.2 Evaluation of a Current Loop Output Module using the ZSC31050 Evaluation Board V3.0

### 4 Calibration of the Current Loop

The ZSC31050 calibration procedure performed via the digital interfaces removes all errors of the front-end and achieves the adaptation of gain, offset, and non-linearity correction for the sensor element within the temperature range. For calibrating a sensor module with current-loop output configuration, an additional 2-point calibration is needed to remove the tolerances of the external parts.

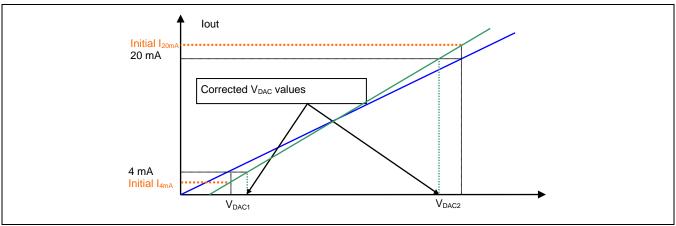

To use the same calibration method as used for the voltage-output mode, a recalculation of the calibration target values  $TG_X$  [%VDDA] for the output voltage can be used to remove the tolerances of the external parts. Figure 4.1 illustrates how to calculate these corrected target values for  $TG_X$  [%VDDA].

Figure 4.1 4mA to 20mA Interface Fine Tuning

The blue line shows the ideal function. The green line is the error line (with 2 initial measurement points:  $I_{4mA}$  and  $I_{20mA}$ ).

This transfer function for the measured currents  $I_{4mA}$  and  $I_{20mA}$  is given by equation:

$$I_{x mA} = \frac{V_{DAC} + \Delta V_{Offset}}{R + \Delta R}$$

(3)

Where

$$V_{DAC} = VDDA * \left(1 - \frac{P_{11}}{2^{11}}\right) = VDDA * TG_{X}[\%]$$

$\Delta V_{Offset}$  = Offset error

$$R = \frac{9}{2} * 50\Omega = 225\Omega$$

$\Delta R$  = Resistor and gain error

R = Current loop resistance

Both error values provide a good indication of the physical behavior of the circuitry:

- · The offset error of the uncompensated amplifier

- · The tolerance errors of the resistors

Using a VDDA voltage of 5V is recommended for the ZSC31050 current loop application. The resulting "free-oferror" target values TG<sub>4mA</sub> and TG<sub>20mA</sub> for the MIN and MAX values of the loop current I<sub>CL</sub> can be calculated by equations (4) and (5):

$$I_{CL\_min} = 4mA = \frac{V_{DAC\_4mA}}{225\Omega} = \frac{VDDA * TG_{4mA}}{225\Omega} \qquad \Rightarrow TG_{4mA} = 18\%$$

$$I_{CL\_max} = 20mA = \frac{V_{DAC\_20mA}}{225\Omega} = \frac{VDDA * TG_{20mA}}{225\Omega} \qquad \Rightarrow TG_{20mA} = 90\%$$

(5)

$$I_{CL_{\text{max}}} = 20 \, mA = \frac{V_{DAC_{\text{-}20mA}}}{225\Omega} = \frac{VDDA * TG_{20mA}}{225\Omega} \implies TG_{20mA} = 90\%$$

(5)

However, the offset of the operational amp and the tolerances of the resistors cause different values of I<sub>CL</sub> when setting the DAC of the ZSC31050 to these "free-of-error" target values via the SET\_DAC command (see the ZSC31050 Functional Description). Based on the resolution of the 11-bit DAC (DAC-IN = 0 to 2047), a decimal value of 368 at TG  $_{4mA}$  = 18% and of 1843 at TG $_{20mA}$  = 90% can be calculated. After setting the DAC to each value, the resulting currents I<sub>4mA</sub> and I<sub>20mA</sub> must be measured. Based on equation (3) and on the calculated target values of equations (4) and (5), the error values  $\Delta V_{Offset}$  and  $\Delta R$  can be determined with equations (6) and (7):

$$\Delta R = \frac{VDDA * (90\% - 18\%)}{I_{20mA} - I_{4mA}} - 225\Omega \tag{6}$$

$$\Delta V_{Offset} = (I_{4mA} * (225\Omega + \Delta R)) - 18\% * VDDA = (I_{20mA} * (225\Omega + \Delta R)) - 90\% * VDDA$$

(7)

These error values can be used to re-calculate the target values TG<sub>4mA</sub> and TG<sub>20mA</sub> via equations (8) and (9):

$$TG_{4mA} = \frac{4mA * (225\Omega + \Delta R) - \Delta V_{Offset}}{VDDA}$$

(8)

$$TG_{20mA} = \frac{20mA * (225\Omega + \Delta R) - \Delta V_{Offset}}{VDDA}$$

(9)

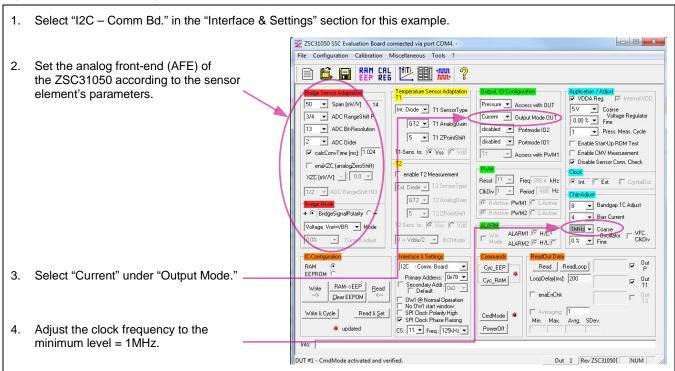

The Excel™ spreadsheet ZSC31050 Current Loop Calibration can be used to perform this calculation (see section 8). The ZSC31050 SSC Evaluation Software Revision 1.5.0.9 or higher for the ZSC31050 Evaluation Kit also supports this calibration step as demonstrated in Figure 4.2 through Figure 4.6. Refer to the ZSC31050 Evaluation Kit Description for setup instructions.

Note that references to "... Pressure" in the software are for the measurand of any sensor type, not just pressure.

Figure 4.2 Step 1: Configuration and Pre-Adjustment of Current-Loop Output Mode

Figure 4.3 Step 2: Transfer the Pre-Adjustments to the RAM and EEPROM

- Write the adjustments to RAM by clicking the "Write" button.

- Verify the WRITE\_RAM operation. (If ok, then all READ cells become green.)

- 3. Copy RAM to EEPROM by clicking the "RAM --> EEP" button.

For the third step, there is the option to use a programmable digital multimeter (DMM) to import the actual current measurement into the SSC Evaluation Software. If using a non-programmable multimeter, follow step 3a below in Figure 4.4. If using a programmable multimeter, follow step 3b in Figure 4.5 instead.

Figure 4.4 Step 3a: Adjustment of the External Current-Loop Circuitry

- Complete the fields for VDDA, RSens, I(min) and I(max) in the "Current Loop Output Adjust & Measurement" dialog menu accessed by clicking on "Current Loop Adjust" under the "Tools" menu at the top.

- Set the analog output of ZSC31050 to the "ideal" 4mA value, measure the actual loop current via a milliamp meter, and input this in the "SetMin" field.

- Set the analog output of ZSC31050 to the "ideal" 20mA value, measure the actual loop current via the milliamp meter, and input this in the "SetMax" field.

- 4. Check the "cpy2Cal" function box.

- Calculate the calibration target values based on the measured parameters of the external parts by clicking the "Calculate Adjust" button.

- Verify the calculated target values at up to four current values (Tmin, Tmid, T\_3rd, and Tmax).

- 7. Verify the limits for the loop current (Lmin and Lmax).

Figure 4.5 Step 3b: Adjustment of the External Current-Loop Circuitry with External DMM Readout

**Note:** Implementing an external digital multimeter's (DMM) readout requires a user-program that communicates with the DMM and reads out the data.

DMM readout is applicable for ZSC31050 software version 1.5.3 or later. Connect the DMM according to the manufacturer's instructions.

- Complete the fields for VDDA, RSens, I(min) and I(max) in the "Current Loop Output Adjust & Measurement" dialog menu accessed by clicking on "Current Loop Adjust" under the "Tools" menu at the top.

- Check the box to activate "Serial DMM" mode. "MMin" and "MMax" are enabled.

- 3. Set the analog output of the ZSC31050 to the "ideal" 4mA value with "SetMin."

- Read the measurement results from the DMM by clicking the "MMin" button. The result is input by the software in the correlating input field.

- 5. Set the analog output of the ZSC31050 to the "ideal" 20mA value with "SetMax."

- Read the measurement results from the DMM by clicking the "MMax" button. The result is input by the software in the correlating input field.

- 7. Continue as described for step 3a from paragraph 4.

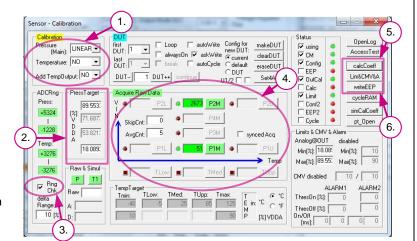

Figure 4.6 Step 4: Calibration using the Re-calculated Target Values

- Adjust the calibration setup based on the characteristics vs. measurand and temperature of the sensor element to be conditioned.

- Enter recalculated calibration "Pressure" targets (refer to step 5 illustrated in Figure 4.4 or step 4 Figure 4.5).

- Check the box to activate the "RngChk" function to avoid saturation of the ADC input.

- 4. Acquire raw values stepwise according to the adjusted setup.

- 5. Calculate coefficients (and limits and alarm values, if needed).

- 6. Write all coefficients to EEPROM.

- Start the Normal Operating Mode (NOM) based on the new EEPROM data (main software window).

### 5 Communication via Current Loop for Calibration

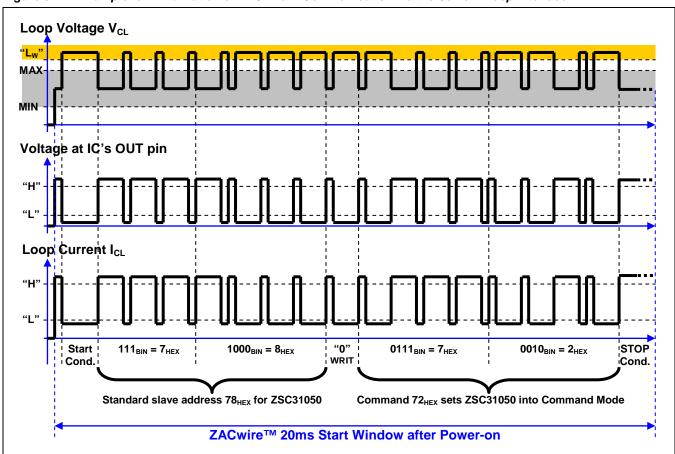

In the application, communication for configuring and calibrating the sensor module can be completed via its two terminals for the current loop while in Command Mode (not an option during Normal Operating Mode). In this case, an additional communication module with special features is needed (see Figure 5.1). A galvanic isolation is needed for external access to the ZSC31050's analog output pin for ZACwire™ communication via the current loop terminals. A common optocoupler (e.g., CNY17-2) can be used for short-circuiting the ZSC31050's analog output OUT pin to VSS (signals a logic "L" is to be written).

Figure 5.1 Schematic of the ZSC31050's Current Loop Output Stage with Communication via ZACwire™

The principle of communication is simple using the four possible signal codes shown in Table 5.1, which are color coded for the signal levels illustrated in Figure 5.2. Communication must be initiated by sending the command **72**<sub>HEX</sub> (switches the ZSC31050 into the Command Mode) within the ZACwire™ start window of 20ms after the power supply has been turned on for the circuit in Figure 5.2.

Table 5.1 Signal Coding

| Operation                | Current Loop Voltage [VDC]  | Loop Current [mA] | Remarks                   |

|--------------------------|-----------------------------|-------------------|---------------------------|

| WRITE " <mark>L</mark> " | > Maximal NOM voltage level | < 5mA             | Data from master to slave |

| WRITE "H"                | Within NOM voltage range    | > 15mA            | (coded by loop voltage)   |

| READ "L"                 | Within NOM voltage range    | < 5 mA            | Data from slave to master |

| READ "H"                 | Within NOM voltage range    | > 15 mA           | (coded by loop current)   |

The ZACwire<sup>TM</sup> communication is initiated by increasing the current loop voltage above its maximal value for the Normal Operation Mode. The WRITE "L" level is determined by the Zener voltage of **ZD2**. The  $15k\Omega$  resistor avoids unintended switching of the optocoupler caused by leakage current. Because the  $5.6k\Omega$  resistor significantly decreases the switch-OFF time of the optocoupler's transistor, a low-speed/low-cost part can be used for this application. The  $4.3k\Omega$  pull-up-resistor at the ZSC31050's OUT pin is needed for communication for the WRITE and READ "H" operations.

During normal operation, the ZSC31050's current consumption must be  $I_{IC}$  < 3.5mA (including the transducer supply current and additional pull-up-current of less than 1mA). Refer to section 2 for a detailed description.

Figure 5.2 Example for Initialization of ZACwire™ Communication via the Current Loop Interface

#### 6 Test of Communication via Current Loop

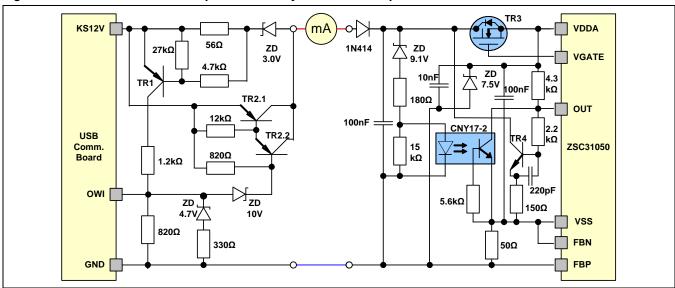

For testing ZACwire<sup>TM</sup> communication with the ZSC31050 via the two wires of the current loop, the SSC Communication Board (CB) and the application circuitry in Figure 5.1 can be used to communicate using the CB's OWI interface. To adapt the CB for signal coding (see Figure 5.2), the circuitry shown in Figure 6.1 can be used.

For WRITE operations (i.e., data from the CB to the ZSC31050), the OWI pin of the CB is driven by its internal microcontroller to 0V = ``L'' or to 5V = ``H.'' This turns the PNP-transistor TR2 on (at "L") or off (at "H") and changes the supply voltage of the sensor module from < 9VDC when off to > 11VDC when on. If the supply voltage of the sensor module is below 9VDC, then the optocoupler stays off and the collector of its NPN-transistor is at high impedance. Via the  $4.3k\Omega$  pull-up resistor, the ZSC31050's OUT pin is set to "H" potential. If the supply voltage increases approximately 11 VDC, then the optocoupler is turned on and its NPN-transistor shorts the OUT pin of the ZSC31050 to VSS, which indicates "L."

Figure 6.1 Schematic for the Adaptation Circuitry for Current Loop Communication

For READ operations (i.e., data from the ZSC31050 to the CB), the OWI pin of the CB is at high impedance ("tri-state"). The logic level "L" is determined by the  $820\Omega$  resistor relative to GND; however the voltage at OWI is approximately 1 VDC. This cannot turn on transistor TR2 because its emitter-to-base-saturation voltage is > 1VDC (Darlington transistor), so TR2 stays off during a READ operation. If the ZSC31050's ZACwire<sup>TM</sup> interface transmits a logic "L," then the voltage at the OUT pin = 0VDC. As a result, the loop current is < 5mA and the voltage drop across the  $56\Omega$  resistor is smaller than the emitter-to-base-saturation voltage of TR1. Its collector stays in the high impedance state, and the voltage at the OWI pin on the CB is 1VDC.

If the ZSC31050's ZACwire<sup>TM</sup> interface transmits a logic "H," then the voltage at the OUT pin = 5VDC. Therefore the loop current is > 15mA and the voltage drop across the  $56\Omega$  resistor becomes greater than the emitter-to-base-saturation voltage of TR1. Its collector shorts the  $1.2k\Omega$  resistor with KS12V = 12 VDC and the voltage at the OWI pin of the CB is > 4.7VDC, which indicates a logic "H."

**Important:** This circuitry is designed for the 12V supply line of IDT's Communication Board only and can be used for evaluations of the principle of ZACwire<sup>TM</sup> communication only via the current loop.

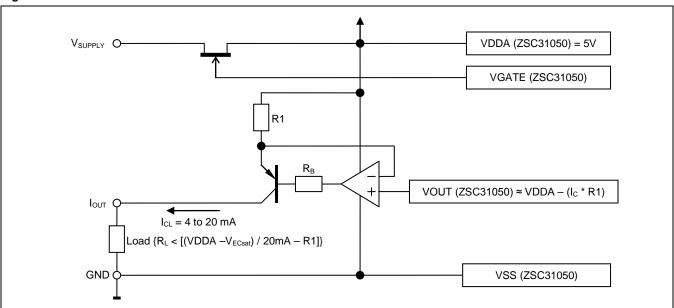

## 7 Schematics for Three-Wire Current-Loop Applications

The ZSC31050 must be configured for voltage output for three-wire current-loop applications. If the load of the current loop is referenced to GND (see Figure 7.1), then the characteristic of the output voltage must be inverted (negative gradient); otherwise, the standard characteristic must be used (see Figure 7.2). This can be achieved by setting the target values for calibration according to the required output characteristics.

Figure 7.1 Load Referenced to GND

Figure 7.2 Load Referenced to Positive Supply V<sub>S</sub>

#### 8 Related Documents

| Document                                                      |

|---------------------------------------------------------------|

| ZSC31050 Data Sheet                                           |

| ZSC31050 Functional Description                               |

| ZSC31050 Evaluation Kit Description                           |

| ZSC31050 Technical Note – EEPROM<br>Changes Bias Adjustment * |

| ZSC31050 Current Loop Calibration<br>Spreadsheet *            |

| SSC Communication Board Data Sheet **                         |

Visit the ZSC31050 product page <u>www.IDT.com/ZSC31050</u> or contact your nearest sales office for the latest version of these documents.

## 9 Glossary

| Term   | Description                                            |  |

|--------|--------------------------------------------------------|--|

| ADC    | Analog-to-Digital-Converter                            |  |

| AFE    | Analog Front-End                                       |  |

| СВ     | Communication Board                                    |  |

| CMC    | Calibration Microcontroller                            |  |

| DAC    | Digital-to-Analog-Converter                            |  |

| EEPROM | Electrically Erasable Programmable Read Only Memory    |  |

| EMI    | Electromagnetic Interference                           |  |

| ESD    | Electrostatic Discharge                                |  |

| IC     | Integrated Circuit                                     |  |

| NOM    | Normal Operation Mode                                  |  |

| MSB    | Most Significant Bit                                   |  |

| SDA    | Serial Data (I <sup>2</sup> C™ Interface)              |  |

| SCL    | Serial Clock (I <sup>2</sup> C <sup>™</sup> Interface) |  |

| SSC    | Sensor Signal Conditioner                              |  |

<sup>\*</sup> Note: Documents marked with an asterisk (\*) are available on request.

<sup>\*\*</sup>Note: Documents marked with two asterisks (\*\*) are available at www.IDT.com/SSC-COMM-BD.

## 10 Document Revision History

| Revision | Date           | Description                                                                               |

|----------|----------------|-------------------------------------------------------------------------------------------|

| 1.00     | August 8, 2011 | First release of document.                                                                |

| 1.02     | July 9, 2015   | Formula corrected on page 4.                                                              |

|          |                | Updates for SSC Evaluation Software images and references to SSC Evaluation Kit hardware. |

|          |                | Updates for procedures in Figure 4.2 through Figure 4.6.                                  |

|          |                | Minor edits for clarity.                                                                  |

|          |                | Update for contact information, related documents, and imagery.                           |

|          | April 26, 2016 | Changed to IDT branding.                                                                  |

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Disclaimer Rev.5.0-1)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>